NXP Semiconductors Application Notes

# S32K3 Memories Guide

## 1. Introduction

The purpose of this application note is to provide a guideline to the readers about the memory features included in the S32K3 Product Family. This document details the available functions and best practices for running applications considering performance improvements.

You can find four kinds of memories inside S32K3 Product Family, the Flash memory, the SRAM, the Tightly Coupled Memory (TCM) and the Cache Memory. The S32K3 Product Family also have some modules with dedicated memory such like EMAC and CAN. This document will mainly focus on Flash Memory, TCM and SRAM.

The Flash memory is dedicated for program code and store data. Also, all devices in the family has a UTEST sector of 8 KB for store important configurations or to reserve information for the application. The S32K3 Product Family has devices from 512 KB to 8 MB of Flash program memory.

The RAM is integrated by the SRAM memory and the TCM. Part of the SRAM memory is available in standby mode. This means that the content of this memory are retained after setting the MCU in standby mode. The S32K3 product family leverages the TCM feature of ARM Cortex M7 architecture, whose main purpose is to provide a deterministic access time to the cores to some important data avoiding any delay in the access. This feature can be exploited in Real Time Operating Systems.

## Contents

| 1. | Introd   | uction                                       | 1  |  |  |  |  |

|----|----------|----------------------------------------------|----|--|--|--|--|

| 2. | Features |                                              |    |  |  |  |  |

| 3. | Flash    | memory                                       | 3  |  |  |  |  |

|    | 3.1.     | Read                                         | 4  |  |  |  |  |

|    | 3.2.     | Write or Program                             | 4  |  |  |  |  |

|    | 3.3.     | Erase                                        | 5  |  |  |  |  |

|    | 3.4.     | Locking and unlocking sector or super sector | 8  |  |  |  |  |

|    | 3.5.     | UTEST sector                                 | 9  |  |  |  |  |

| 4. | Tightl   | y Coupled Memory                             | 10 |  |  |  |  |

| 5. | <u> </u> | Ă                                            |    |  |  |  |  |

|    | 5.1.     | Read                                         | 14 |  |  |  |  |

|    | 5.2.     | Write                                        | 14 |  |  |  |  |

| 6. | Use C    | ases                                         | 15 |  |  |  |  |

|    | 6.1.     | Flash vs TCM vs SRAM                         | 15 |  |  |  |  |

|    | 6.2.     | SRAM standby                                 | 21 |  |  |  |  |

| 7. | SW re    | commendations and conclusions                | 26 |  |  |  |  |

| 8. | Refere   | ences                                        | 26 |  |  |  |  |

### Features

The Cache memory is a dedicated memory for the cores. This memory is not part of the system memory and doesn't have a physical address available for the programmer. This memory serves as an intermediate buffer between the processor and the main memory to reduce memory access time for the cores.

## 2. Features

S32K3 family devices memory features can be found in the *Table 1* and 2.

| Table 1. S32K3 Memory features         |                                    |         |                                     |                                                      |               |                     |  |  |  |  |  |

|----------------------------------------|------------------------------------|---------|-------------------------------------|------------------------------------------------------|---------------|---------------------|--|--|--|--|--|

| Feature                                | S32K310                            | S32K311 | S32K341                             | S32K312                                              | S32K322       | S32K342             |  |  |  |  |  |

| Core qty                               | re qty 1 x Cortex-M7 1 x Cortex-M7 |         | 1 x Cortex-M7<br>LS 1 x Cortex-M7   |                                                      | 2 x Cortex-M7 | 1 x Cortex-M7<br>LS |  |  |  |  |  |

| Program flash<br>memory (MB)           | 512 KB                             | -       | L                                   |                                                      | 2             |                     |  |  |  |  |  |

| Data flash<br>memory (KB) <sup>1</sup> | 6                                  | 4       | 128                                 |                                                      |               |                     |  |  |  |  |  |

| Cache                                  |                                    |         | l Cach<br>D Cach                    | e 8 KB<br>ne 8 KB                                    |               |                     |  |  |  |  |  |

| Total RAM<br>(KB)                      | 128 KB (including 96 KB TCM)       |         | 256 KB<br>(including 192<br>KB TCM) | (including 192 (including 96 256 KB (including 192 K |               | ng 192 KB TCM)      |  |  |  |  |  |

| Standby RAM <sup>2</sup>               |                                    |         | 32                                  | КВ                                                   |               |                     |  |  |  |  |  |

Table 2. S32K3 Memory features

| Feature                                                                                                                                                                                                                                          | S32K314                               | S32K324                      | S32K344              | S32K328           | S32K348              | S32K338           | S32K358                             |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------|----------------------|-------------------|----------------------|-------------------|-------------------------------------|--|--|

| Core qty                                                                                                                                                                                                                                         | 1 x Cortex-<br>M7                     | 2 x Cortex-<br>M7            | 1 x Cortex-<br>M7 LS | 2 x Cortex-<br>M7 | 1 x Cortex-<br>M7 LS | 3 x Cortex-<br>M7 | 1 x Cortex-M7 LS +<br>1 x Cortex-M7 |  |  |

| Program flash 4<br>memory (MB)                                                                                                                                                                                                                   |                                       |                              | 8                    |                   |                      |                   |                                     |  |  |

| Data flash<br>memory (KB) <sup>1</sup>                                                                                                                                                                                                           | 128                                   |                              |                      |                   |                      |                   |                                     |  |  |

| Cache                                                                                                                                                                                                                                            |                                       | I Cache 8 KB<br>D Cache 8 KB |                      | TBD               |                      |                   |                                     |  |  |

| Total RAM<br>(KB)                                                                                                                                                                                                                                | 512 KB<br>(including<br>96 KB<br>TCM) | •                            | including<br>3 TCM)  | •                 | uding 192 KB<br>M)   | 1152 KB (inc      | luding 384 KB TCM)                  |  |  |

| Standby RAM <sup>2</sup> 32 KB                                                                                                                                                                                                                   |                                       |                              |                      | 64 KB             |                      |                   |                                     |  |  |

| <ol> <li>This represents the maximum available Data Flash memory. Refer to the S32K3 Reference Manual for limitations<br/>applying when HSE security firmware is installed</li> <li>The Standby RAM is also included in the Total RAM</li> </ol> |                                       |                              |                      |                   |                      |                   |                                     |  |  |

An important feature to remark is that all memories inside the S32K3 Product Family has Error Detection and Error Correction Code.

The flash memory on S32K3 devices is integrated by blocks. There are five blocks as maximum and two blocks as minimum. Detailed information is provided in the following table.

| Table 3. Flash memory architecture for 532K3              |                                           |                                           |                                           |                                           |                                           |  |  |  |  |

|-----------------------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|--|--|--|--|

| Flash Blocks                                              | S32K310                                   | S32K311<br>S32K341                        | S32K312<br>S32K322<br>S32K342             | S32K314<br>S32K324<br>S32K344             | S32K328<br>S32K338<br>S32K348<br>S32K358  |  |  |  |  |

| End<br>Address<br>UTEST<br>Start Address                  | 0x1B00_1FFF<br><b>8 KB</b><br>0x1B00_0000 |  |  |  |  |

| Address<br>Block4<br>Data Flash Memory<br>Start Address   | 0x1000_FFFF<br>64 KB<br>0x1000_0000       | 0x1000_FFFF<br>64 KB<br>0x1000_0000       | 0x1001_FFFF<br>128 KB<br>0x1000_0000      | 0x1001_FFFF<br>128 KB<br>0x1000_0000      | 0x1001_FFFF<br>128 KB<br>0x1000_0000      |  |  |  |  |

| Address<br>Block3<br>Code Flash Memory 3<br>Start Address | Not<br>Available                          | Not<br>Available                          | Not<br>Available                          | 0x007F_FFFF<br>1 MB<br>0x0070_0000        | 0x00BF_FFF<br>2 MB<br>0x00A0_0000         |  |  |  |  |

| Address<br>Block2<br>Code Flash Memory 2<br>Start Address | Not<br>Available                          | Not<br>Available                          | Not<br>Available                          | 0x006F_FFFF<br>1 MB<br>0x0060_0000        | 0x009F_FFF<br>2 MB<br>0x0080_0000         |  |  |  |  |

| Address<br>Block1<br>Code Flash Memory 1<br>Start Address | Not<br>Available                          | 0x004F_FFFF<br>512 KB<br>0x0048_0000      | 0x005F_FFFF<br>1 MB<br>0x0050_0000        | 0x005F_FFFF<br>1 MB<br>0x0050_0000        | 0x007F_FFF<br>2 MB<br>0x0060_0000         |  |  |  |  |

| Address<br>Block0<br>Code Flash Memory 0<br>Start Address | 0x0047_FFFF<br>512 KB<br>0x0040_0000      | 0x0047_FFFF<br>512 KB<br>0x0040_0000      | 0x004F_FFFF<br>1 MB<br>0x0040_0000        | 0x004F_FFFF<br>1 MB<br>0x0040_0000        | 0x005F_FFF<br>2 MB<br>0x0040_0000         |  |  |  |  |

Table 3.Flash memory architecture for S32K3

In the S32K3 Product Family the devices are available from 512 KB to 8 MB of Flash memory. The *Table 3* classifies the S32K3 Product Family devices by Flash memory size.

There are some regions inside the Flash memory that are protected to be used by the application cores. These are only available for HSE\_B core. For more information about HSE\_B refer to S32K3 Reference Manual.

There are three operations modes for the Flash memory. When the device is working in User mode the Flash memory array is accessible to execute a read, program or erase operation. The User mode is the default operating mode of the Flash memory. All the registers have read and write access. In low power mode the Flash memory is not accessible because its power source is turned off, so operations are not allowed in this mode. Finally the Utest mode is a test mode where the integrity of the Flash memory can be verified.

The Flash memory can perform multiple reads between different blocks by a single, dual or quad read feature, where in a multi-core scenario, if there are multiple threads running in parallel (on different sections/blocks of memory) those threads can occur simultaneously by a dual or quad read, this feature is controlled internally and not by the user. It also has the "Read-While-Write" (RWW) feature to be able to perform a read and a write simultaneously (applies only when operations are in different blocks); for example, in the S32K324, if the Core 0 application is performing a write process in block 0, then the Core 1 at the same time can read a data stored in the data flash block.

There are four important operations that we need to consider when we are working with the Flash memory:

- Read Flash memory

- Lock and Unlock sector or super sector

- Program Flash memory

- Erase Flash memory

## 3.1. Read

After reset, the Flash memory is in a default state which have the arrays and register available to be read by the controller. A read operation from Flash memory return a 256 bits of data length and register reads return 32 bits. For this operation is not necessary to consider a Lock or Unlock sector. The read operation is performed by the PFlash controller which is the interface between the system bus and the embedded Flash memory.

## 3.2. Write or Program

The minimum program size is 2 words (64 bits) and data must be 64 bit aligned. A maximum of 4 pages can be programmed at the same time, where 1 page are 8 words (256 bits). This mean that up to 1024 bits can be altered in a single program operation. When a program operation or write operation is made the ECC bits are calculated and stored. The ECC is handled on 64 bits doubleword. Eight bits of ECC are needed.

A program operation changes the logic value of a bit from 1 to 0, this means that a program operation from 0 to 1 is not allowed and the Flash memory needs to be erased before any program operation. When data Flash is used for EEPROM emulation, approved drivers by NXP can do an over-programming in a 64 bit ECC segment, this allows to over-program the same location up to 3 times without performing an erase operation in the sector. This feature can be used to change the record status of a data record without a previous erase which is frequently used in some EEPROM emulation techniques. It's important to remark that it is only available and usable for approved drivers by NXP, please consult the RTD software for S32K3 devices for available FEE drivers.

Before a program operations occurs the sector that contains the specified address must be unlocked. If a locked sector or super sector is attempted to be programmed, program operation will fail and an error will be reported in the MCRS[PEP] bit.

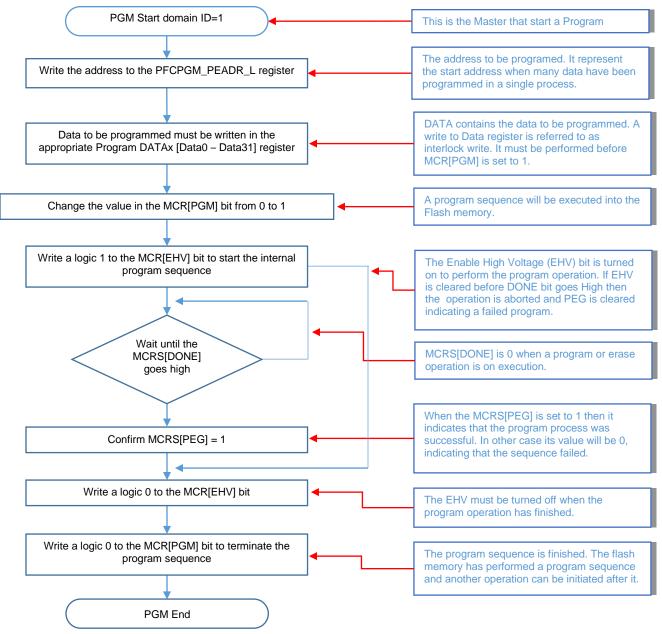

The flow diagram for the program operation is explained in the *Figure 1*.

Figure 1. Program sequence flow diagram

## 3.3. Erase

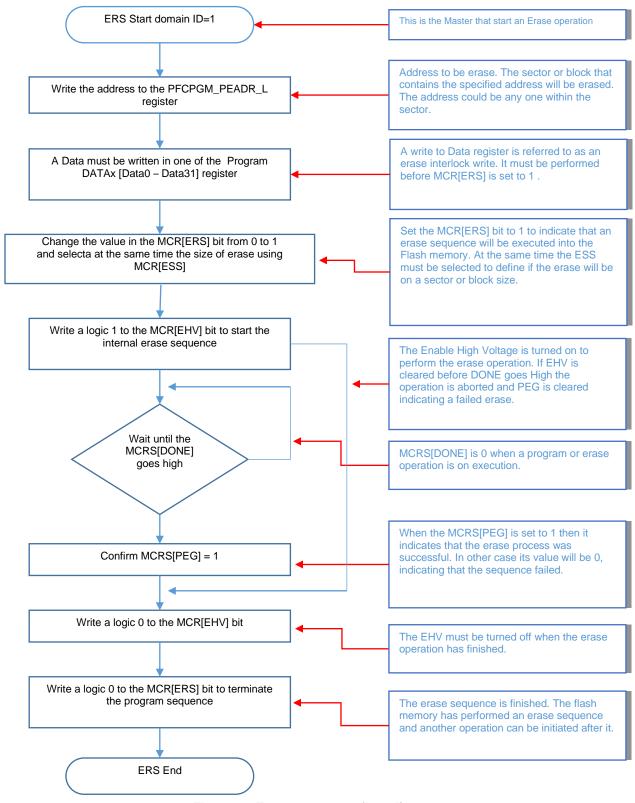

The erase operation is the process to set all bits from a sector or block to 1. The minimum erase size can be performed in a sector, where a sector size is 8 KB. To erase a sector or block it must be unlocked previously to the erase operation. The erase process also clean the ECC bits.

The following flow diagram show the erase sequence.

The following bare metal code shows the implementation of the write and erase operation, we can note that some functions are shared for both operations in the *Example 3*

S32K3 Memories Guide, Rev. 0, 11/2021

#### Example 1. Erase flash function

```

tFLASH_STATUS FLASH_ErsSector (const void *dst)

{

FLASH_InitSeq(dst);

FLASH->DATA[0] = 0UL; /* one and only one DATA register written */

return FLASH_ExecSeq(FLASH_MCR_ERS_MASK);

}

```

#### Example 2. Write flash function

```

register tFLASH_STATUS status = FLASH_PEG_ST;

register uint8_t *pDst = (uint8_t*)dst, *pSrc = (uint8_t*)src, *pTmp;

register uint32_t *pData;

uint32_t tmp;

while ((nbytes > 0L) && (status & FLASH_PEG_ST))

ł

pData = (uint32_t*)((uint32_t)&FLASH->DATA[0] + ((uint32_t)pDst & FLASH_DATAX_MASK));

FLASH_InitSeq (pDst);

do {

tmp = 0xffffffUL;

pTmp = (uint8_t*)((uint32_t)&tmp + ((uint32_t)pDst & FLASH_BYTES_MASK));

do {

*pTmp++ = *pSrc++; pDst++;

} while ((nbytes-- > 0L) && ((uint32_t)pTmp & FLASH_BYTES_MASK));

*pData++ = tmp;

} while ((nbytes > 0L) && ((uint32_t)pData & FLASH_DATAX_MASK));

status = FLASH_ExecSeq (FLASH_MCR_PGM_MASK);

}

return status:

}

```

#### Example 3. Common Erase/Write functions

```

#define FLASH WritePEADR(dst) do{ PFLASH->PFCPGM PEADR L=(uint32 t)dst; }while(0)

#define FLASH_GetPEID() ((FLASH->MCR&FLASH_MCR_PEID_MASK)>>FLASH_MCR_PEID_SHIFT)

#define FLASH_ClrStatus(mask) do{ FLASH->MCRS=mask; }while(0)

#define FLASH_GetStatus() (tFLASH_STATUS)FLASH->MCRS

#define FLASH_InitSeq(addr)

١

do{

register uint8_t domain_id = XRDC->HWCFG1;

/* entry semaphore loop

do{ FLASH_WritePEADR (addr); } while(FLASH_GetPEID () != domain_id);

/* clear any pending program & erase errors

FLASH_ClrStatus (FLASH_PES_ERR|FLASH_PEP_ERR);

}while(0)

tFLASH_STATUS FLASH_ExecSeq (register uint32_t mask)

{

register tFLASH_STATUS status;

/* initiate sequence

FLASH->MCR |= mask;

FLASH->MCR |= FLASH_MCR_EHV_MASK;

/* enable high voltage

while(!(FLASH->MCRS&FLASH_MCRS_DONE_MASK)); /* wait until MCRS[DONE]=1

/* disable high voltage

FLASH->MCR &=~FLASH_MCR_EHV_MASK;

status = FLASH_GetStatus();

/* read main interface status

/* close sequence

FLASH->MCR &=~mask;

return status;

```

{

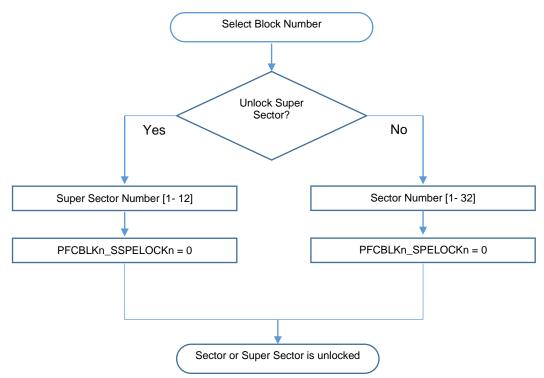

## 3.4. Locking and unlocking sector or super sector

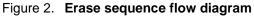

A block is integrated by sectors and super sectors with sizes of 8 KB and 64 KB respectively. These sectors can be protected from write or erase operations by using the locking feature. The last 256 KB of the block has sector protection feature, while the rest has the Super Sector protection feature. The data flash has sector protection feature and the UTEST sector has an independent sector program protection. The S32K3 Product Family has some devices where Super Sector protection is not available due to the memory size, for more information about these devices, please review the S32K3 Product Family Reference Manual.

The following figure shows the sector and super sector distribution for a 1 MB block.

Figure 3. Sector distribution inside 1MB block

The lock and unlock process is controlled by the PFCBLKn\_SSPELOCKn registers for super sectors and PFCBLKn\_SPELOCKn registers for sectors. The PFCBLKn\_SSPELOCKn register has 12 available bits, where each bit corresponds to each super sector, similarly, the PFCBLKn\_SPELOCKn register has 32 available bits for 32 available sectors. If an unlock process is desired to allow a program or erase operation, then the corresponding register PFCBLKn\_SSPELOCKn or PFCBLKn\_SPELOCKn must be changed from 1 to 0. Writing 1 to any bit of PFCBLKn\_SPELOCKn or PFCBLKn\_SSPELOCKn will lock the sector or super sector against programming and erasing operations.

The PFCBLKn\_SSPELOCKn and PFCBLKn\_SPELOCKn registers values out of reset is 1 for all the bits, this means that all sectors are protected from program and erase operations after reset.

The *Figure 4* shows the steps to unlock a sector or super sector.

Figure 4. Unlock process for Sector or Super Sector

## 3.5. UTEST sector

The 8 KB UTEST sector is available in all devices from the S32K3 Product Family. In this sector is possible to store important information about the application, for example, version number, permanent parameters, configurations (boot or applications), etc. Inside the UTEST Sector there are some regions that are reserved for the SoC and its use is reserved for NXP. For more detail about available regions please consult the S32K3xx\_DCF\_client.xlsx attached in the S32K3 Product Family Reference Manual.

The UTEST Sector is an OTP (One Time Programmable) space when the Test mode seal is written. The Test mode seal is allocated in the UTEST Sector, for security it is programmed with the value 0x5A4B3C2D, this means that only new data or configuration could be appended in the UTEST sector and erase is not allowed.

The process to write a data in the UTEST Sector is the same process used to program a data in other blocks. The unlocking process is also the same but with the difference that the UTEST sector has its own register PFCBLKU\_SPELOCK[SLCK] to lock or unlock the sector from program operations. As mentioned before, UTEST sector is an 8KB sector so there is only 1 bit to change in the PFCBLKU\_SPELOCK register. Following the sector protection logic, if the SLCK bit is set to 0 then the UTEST sector is available for program operations.

The following example is part of a baremetal code that depict how to unlock the UTEST sector, this example can be used for other blocks.

### **Tightly Coupled Memory**

```

Example 4. Unlocking UTEST sector

#define PFLASH U PFCBLKI SPELOCK COUNT

1u

typedef struct {

IO uint32_t PFCBLKU_SPELOCK[PFLASH_U_PFCBLKI_SPELOCK_COUNT]; /**< Block UTEST Sector Program Erase Lock, array

offset: 0x358, array step: 0x4 */

} PFLASH Type, *PFLASH MemMapPtr;

#define PFLASH PFCBLK5 SPELOCK

PFLASH->PFCBLKU SPELOCK[0]

#define PFLASH Unlock(blocks,ssectors,sectors)

({

register uint32_t __t1=blocks, __t2=ssectors, __t3=sectors;

if (__t1 & PFLASH_BL0) { PFLASH_PFCBLK0_SSPELOCK&=~_t2; PFLASH_PFCBLK0_SPELOCK&=~_

t3;

}

if (_

_t1 & PFLASH_BL1) { PFLASH_PFCBLK1_SSPELOCK&=~__t2; PFLASH_PFCBLK1_SPELOCK&=~__t3;

}

if (__t1 & PFLASH_BL2) { PFLASH_PFCBLK2_SSPELOCK&=~_t2; PFLASH_PFCBLK2_SPELOCK&=~_t3;

}

\

if (__t1 & PFLASH_BL3) { PFLASH_PFCBLK3_SSPELOCK&=~__t2; PFLASH_PFCBLK3_SPELOCK&=~__t3; } \

PFLASH_PFCBLK4_SPELOCK&=~__t3; } \

if (__t1 & PFLASH_BL4) {

if (__t1 & PFLASH_BL5)

PFLASH_PFCBLK5_SPELOCK&=~__t3; } \

})

unlock UTEST data flash sector

*/

PFLASH_Unlock (PFLASH_BL5, PFLASH_SS0, PFLASH_S0);

```

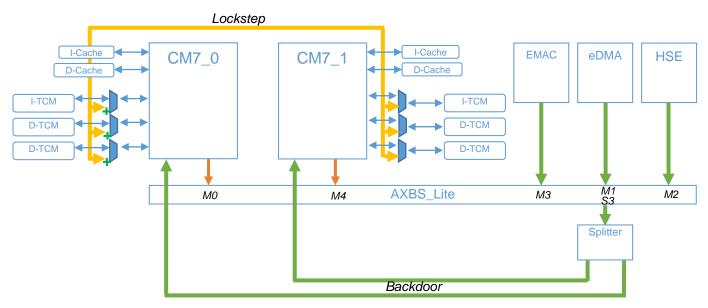

## 4. Tightly Coupled Memory

The Tightly Coupled Memory (TCM) is a memory implemented from the ARM(R) Cortex M7 architecture which main characteristic is to have a dedicated connection to the core. This memory is divided in Instruction TCM (I-TCM) and Data TCM (D-TCM). In the S32K3 Product Family there are 2 dedicated connections to the Cortex M7, one for the Instruction TCM and another for the Data TCM. Each CM7 core has an ITCM and DTCM memory available, so the sizes and addresses of the TCM memories depends on the number of cores available on the variant and its configuration (lockstep or decoupled), for more information please review the *Table 4 RAM memory architecture for S32K3*.

The TCM is memory mapped and it can be accessed by two possible buses, by the dedicated Core connection and by a backdoor access for any other Master on the AHBS bus. Each access has a defined start address for TCM and the end address is determinate by the size of the memory, for more information about the addresses please consult the *Table 4*.

For the dedicated access for the core, the I-TCM (Instruction-TCM) has a bus interface of 64 bits and the D-TCM (Data-TCM) a bus interface of 32 bits. The TCM memory can be accessed via 32 bits AHB interface by any other master, such as the eDMA, a different Core (when decoupled configuration), the EMAC and the HSE Core.

For devices in lockstep, the TCM of the secondary core is added to the Primary core so the accessible size to the primary core is augmented. In decoupling mode, the TCM is dedicate for each core.

The TCM can be used as System Memory or dedicated memory to the cores. When the TCM is used as System Memory on multicore devices all enabled cores and non-core masters can use the TCMs of the disabled core. In order to allow the usage of ITCM and DTCM of the disabled core as system memory, some register configuration is necessary. For more detail review the S32K3 Product Family reference manual and take as reference the example code in this section.

The following block diagram depicts the route that other masters use to get access to the TCM memory (S32K32x and S32K34x devices).

Figure 5. TCM memory accesses for S32K32x and S32K34x (Direct and Backdoor)

Due to the fact that the TCM is part of the memory map and it has a physical address, the user can decide the content to be stored in the TCM at compilation time. One advantage of using the TCM is that it has a deterministic access time (one clock cycle), so the TCM can be used to store critical data and code, for example, frequently updated variables, interrupt handlers, data processing, etc. This data is decided by the user and not by a control logic as the Cache memory.

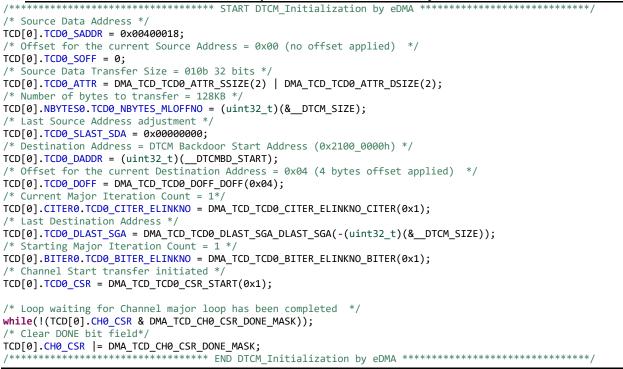

As other memories, TCM has ECC protection, and after the chip's power on reset and before using it, the user must initialized it to avoid ECC errors, this write operation is required to set up the initial ECC code words after the chip's power on reset phase. In the S32K3 Product Family the cores can initialize ITCM and DTCM via the direct and Backdoor accesses. Also, the DTCM can be initialized by the DMA via the backdoor but the DMA cannot initialize the ITCM due to the 32 bits access that the backdoor provides (ITCM needs 64 bits writes to avoid ECC error).

As an example, the next code depicts how to use the TCM as system memory, how to initialize the ITCM via the Core M7\_0, and how to initialize the DTCM via the DMA. Important notice, to initialize the DTCM the DMA needs to use the backdoor address in order to get access to the DTCM.

| /*************************************                                      | em RAM *******************************/        |

|-----------------------------------------------------------------------------|------------------------------------------------|

| <pre>MC_ME-&gt;PRTN2_COFB1_CLKEN  = MC_ME_PRTN2_COFB1_CLKEN_REQ62(1);</pre> | <pre>/* PRTN2_COFB1_CLKEN_[REQ62] = 1 */</pre> |

|                                                                             | /* Enable clock for TCM for CM7_0 */           |

| <pre>MC_ME-&gt;PRTN2_COFB1_CLKEN  = MC_ME_PRTN2_COFB1_CLKEN_REQ63(1);</pre> | /* PRTN2_COFB1_CLKEN_[REQ63] = 1 */            |

|                                                                             | /* Enable clock for TCM for CM7_1 */           |

| <pre>DCM_GPR-&gt;DCMRWF4  = DCM_GPR_DCMRWF4_cm7_0_cpuwait(1);</pre>         | /* DCMRWF4[CM7_0_CPUWAIT] = 1 */               |

|                                                                             | /* Wait Mode for CM7_0 */                      |

| <pre>DCM_GPR-&gt;DCMRWF4  = DCM_GPR_DCMRWF4_cm7_1_cpuwait(1);</pre>         | /* DCMRWF4[CM7_1_CPUWAIT] = 1 */               |

|                                                                             | /* Wait Mode for CM7_1 */                      |

| <pre>MC_ME-&gt;PRTN0_CORE0_PCONF  = MC_ME_PRTN0_CORE0_PCONF_CCE(1);</pre>   | <pre>/* PRTN0_CORE0_PCONF[CCE] = 1 */</pre>    |

|                                                                             | /* Enable Clock for CM7_0 */                   |

| <pre>MC_ME-&gt;PRTN0_CORE1_PCONF  = MC_ME_PRTN0_CORE1_PCONF_CCE(1);</pre>   | <pre>/* PRTN0_CORE1_PCONF[CCE] = 1 */</pre>    |

|                                                                             | /* Enable Clock for CM7 1 */                   |

| /*************************************                                      | RAM *****************************/             |

|                                                                             |                                                |

S32K3 Memories Guide, Rev. 0, 11/2021

####

### Example 7. DTCM initialization by eDMA

## 5. SRAM

The S32K3 Product Family devices can be integrated from 1 SRAM and up to 3 SRAM blocks. The *Table 4* shows the RAM memory blocks available for each device. Remember that the TCM memory is considered a part of the RAM memory.

### Table 4. RAM memory architecture for S32K3

| RAM                                   | S32K311<br>S32K310                         | S32K312                                    | S32K314                                   | S32K322                             | S32K324                                     | S32K328                                     | S32K342                              | S32K344                                     | S32K348                                     | S32K338                             | S32K358                                     |

|---------------------------------------|--------------------------------------------|--------------------------------------------|-------------------------------------------|-------------------------------------|---------------------------------------------|---------------------------------------------|--------------------------------------|---------------------------------------------|---------------------------------------------|-------------------------------------|---------------------------------------------|

| End Address<br>SRAM2<br>Start Address | Not Available                              | Not Available                              | Not Available                             | Not Available                       | Not Available                               | 0x204B_FFFF<br><b>256 KB</b><br>0x2048_0000 | Not Available                        | Not Available                               | 0x204B_FFFF<br><b>256 KB</b><br>0x2048_0000 | 256 KB                              | 0x204B_FFFF<br><b>256 KB</b><br>0x2048_0000 |

| End Address<br>SRAM1<br>Start Address | Not Available                              | Not Available                              | 0x2044_FFFF<br>160 KB<br>0x2042_8000      | Not Available                       | 0x2044_FFFF<br><b>160 KB</b><br>0x2042_8000 | 0x2047_FFFF<br><b>256 KB</b><br>0x2044_0000 | Not Available                        | 0x2044_FFFF<br><b>160 KB</b><br>0x2042_8000 | 0x2047_FFFF<br><b>256 KB</b><br>0x2044_0000 | 256 KB                              | 0x2047_FFF<br><b>256 KB</b><br>0x2044_0000  |

| SRAM0                                 | 0x2040_7FFF<br><b>32 KB</b><br>0x2040_0000 | 0x2041_7FFF<br><b>96 KB</b><br>0x2040_0000 | -                                         | 64 KB                               | 0x2042_7FFF<br><b>160 KB</b><br>0x2040_0000 | 256 KB                                      | 0x2040_FFFF<br>64 KB<br>0x2040_0000  | 0x2042_7FFF<br>160 KB<br>0x2040_0000        | 0x2043_FFFF<br><b>256 KB</b><br>0x2040_0000 | 256 KB                              | 0x2043_FFFF<br><b>256 KB</b><br>0x2040_0000 |

| End Address<br>DTCM2<br>Start Address | Not Available                              | Not Available                              | Not Available                             | Not Available                       | Not Available                               | Not Available                               | Not Available                        | Not Available                               | Not Available                               | -                                   | 0x2001_FFFF<br>128 KB<br>0x2000_0000        |

| End Address<br>DTCM1<br>Start Address | Not Available                              | Not Available                              | Not Available                             | 0x0000_FFFF<br>64 KB<br>0x2000_0000 | 0x0000_FFFF<br>64 KB<br>0x2000_0000         | 0x0000_FFFF<br>64 KB<br>0x2000_0000         | Not Available                        | Not Available                               | Not Available                               | 0x2000_FFFF<br>64 KB<br>0x2000_0000 | Not Available                               |

| DTCM0                                 | 0x2000_FFFF<br>64 KB<br>0x2000_0000        | 0x2000_FFFF<br>64 KB<br>0x2000_0000        | 0x2000_FFFF<br>64 KB<br>0x2000_0000       | 0x2000_FFFF<br>64 KB<br>0x2000_0000 | 0x2000_FFFF<br>64 KB<br>0x2000_0000         | 0x2000_FFFF<br>64 KB<br>0x2000_0000         | 0x2001_FFFF<br>128 KB<br>0x2000_0000 | 0x2001_FFFF<br>128 KB<br>0x2000_0000        | 0x2001_FFFF<br><b>128 KB</b><br>0x2000_0000 | -                                   | 0x2001_FFFF<br><b>128 KB</b><br>0x2000_0000 |

| End Address<br>ITCM2<br>Start Address | Not Available                              | Not Available                              | Not Available                             | Not Available                       | Not Available                               | Not Available                               | Not Available                        | Not Available                               | Not Available                               | -                                   | 0x0000_FFFF<br>64 KB<br>0x0000_0000         |

| End Address<br>ITCM1<br>Start Address | Not Available                              | Not Available                              | Not Available                             | 32 KB                               | 0x0000_7FFF<br><b>32 KB</b><br>0x0000_0000  | 0x0000_7FFF<br><b>32 KB</b><br>0x0000_0000  | Not Available                        | Not Available                               | Not Available                               | 0x0000_7FFF<br>32 KB<br>0x0000_0000 | Not Available                               |

| End Address<br>ITCMO<br>Start Address | 0x000_7FFF<br><b>32 KB</b><br>0x0000_0000  | 0x000_7FFF<br><b>32 KB</b><br>0x0000_0000  | 0x000_7FFF<br><b>32 KB</b><br>0x0000_0000 | 32 KB                               | 0x000_7FFF<br><b>32 KB</b><br>0x0000_0000   | 32 KB                                       | 0x0000_FFFF<br>64 KB<br>0x0000_0000  | 0x0000_FFFF<br>64 KB<br>0x0000_0000         | 0x0000_FFFF<br>64 KB<br>0x0000_0000         | 0x000_7FFF<br>32 KB                 | 0x0000_FFFF<br>64 KB<br>0x0000_0000         |

Each SRAM block has its own SRAM Controller (PRAMC) to support fast read/write accesses to the cores. The PRAM controller is the interface between the system bus and the integrated RAM array. The system bus supports 64 bit of data and the RAM array supports 64 bit of data + 8 bit for ECC.

Inside the SRAM memory there is a region that is available when the microcontroller is in Standby mode. The Standby SRAM is allocated at the first 32 KB of the SRAM memory. This region is sourced by the Power Domain 0, so when a standby mode is performed the information that is stored in the Standby region is retained. The rest of the SRAM memory is sourced by the Power Domain 1 and it is only available in Run Mode.

Just like the TCM memory, all the SRAM memory must be initialized to avoid ECC errors and this can be done by the core or the DMA as well. If the initialization is omitted then any read or write to the SRAM memory will generate an uncorrectable ECC error event.

### Example 8. SRAM initialization by DMA

## 5.1. Read

Read events can be configured to be completed with a zero wait state or one wait state response for any data size. The PRAM controller register Flow Trough Disable field PRCRx[FT-DIS] insert a wait state on read events prior to returning the data to the system bus. Insertions of wait states are important to consider when system frequency are greater than 120MHZ. This wait state doesn't have any effect on write events. For more information about wait states please refer to the Gasket configurations in the Clocking Chapter of the S32K3 Reference Manual.

## 5.2. Write

Write operations can be made in 64 bits or less. When an aligned 64 bits write is performed the write operation is executed in a single phase cycle with a zero wait state. When a write less than 64 bits or unaligned write is performed a Read-Modify-Write action is executed in order to perform the write and recalculate the new ECC code. The RMW action will insert some cycles to the write process and this means that aligned 64 bits writes has better performance than unaligned < 64 bits writes to the SRAM memory.

The Read-Modify-Write can be explained in the following sequence:

- The PRAMC performs a Single Error Correction (SEC)/Double Error Detection (DED) in the corresponding read data

- 2. The write data is merged with the previous read data and only bits of the write data are changed

- 3. A new ECC code is generated according to the new 64 bits

- 4. The new double word and ECC is written to RAM.

## 6. Use Cases

## 6.1. Flash vs TCM vs SRAM

One of the main features of S32K3 Product Family is the implementation of TCM memory. One of the advantages of TCM memory is a deterministic time for process task or use of data stored in this memory in order to avoid any latency in the data transfer between core with the SRAM or with the Flash Memory.

The following use case demonstrates the main difference between running code from Flash vs TCM and vs RAM memory. Also, this example helps the customer to learn how to run functions or data loaded in TCM or RAM instead of Flash memory. This use case was created for a S32K344 device and tested on the S32K3XXEVB-Q257 evaluation board, the following guidelines in this chapter are shown for S32 Design Studio with GCC toolchain, but the procedure is similar for other IDEs and toolchains.

### 6.1.1. Linker file

The first step is to check if our linker file has declared the TCM, Flash and SRAM memory regions with their corresponding size.

The memory regions on linker file should looks something like that:

### Example 9. Linker memory definition and size

We need to define some sections inside each memory regions where we want to load the function or data. For this example we are going to define the next sections:

- ITCM\_code (0x0000\_0000): section on ITCM to load and running the TCM\_Function.

- DTCM\_data (0x2000\_0000): section on DTCM to load some arrays and variables.

- SRAM\_Function will use the standard .data section from the SRAM (start address 0x2040\_8000).

- Flash functions will be loaded in the .text section by default.

### S32K3 Memories Guide, Rev. 0, 11/2021

#### **Use Cases**

The linker file will looks something like this:

```

Example 10. Sections for code and data for ITCM, DTCM and SRAM

```

```

coderom start

= .;

.ITCM_code : AT (__coderom_start__)

{

= ALIGN(8);

_coderam_start__ = .;

*(.ITCM_code*)

. = ALIGN(8);

_coderam_end__ = .;

} > ITCM

_coderom_start__ + ( __coderam_end__ - __coderam_start__ );

. =

__coderom_end__ = .;

__etext = ALIGN(8);

.DTCM_data :

{

= ALIGN(4);

_DTCM_data__ = .;

} > DTCM

.standby ram :

{

*(.standby ram)

} > SRAM0_STDBY

/* Due ECC initialization sequence __data_start__ and __data_end__ should be aligned on 8 bytes */

.data : AT (__etext)

{

. = ALIGN(8);

_data_start__ = .;

*(vtable)

*(.data)

*(.SRAM_Function)

*(.data.*)

= ALIGN(4);

/* preinit data */

PROVIDE_HIDDEN (__preinit_array_start = .);

KEEP(*(.preinit_array))

```

### 6.1.2. Startup

To avoid ECC error ITCM, DTCM and SRAM are initialized. Also, the functions code needs to be copied to ITCM and SRAM. This process is according to the linker file and processed by the startup\_code.

## Example 11. Initialization for ITCM, DTCM and SRAM to avoid ECC errors according to the table specified in the linker file

/\*\*

```

uint64_t wlen;

} __ecc_table_t;

extern const __ecc_table_t __ecc_table_start__;

extern const __ecc_table_t __ecc_table_end__;

for (__ecc_table_t const* pTable = &__ecc_table_start__; pTable < &__ecc_table_end__; ++pTable) {

for(uint64_t i=0u; i<pTable->wlen; ++i) {

pTable->dest[i] = 0xDEADBEEFFEEDCAFEUL;

}

}

```

The copy of code and data from flash to ITCM and SRAM is also processed on the startup

```

Example 12.

Copy code to ITCM, DTCM and SRAM

_STATIC_FORCEINLINE __NO_RETURN void __cmsis_start(void)

{

extern void _start(void) __NO_RETURN;

typedef struct {

uint32_t const* src;

uint32 t* dest;

uint32_t wlen;

} __copy_table_t;

typedef struct {

uint32_t* dest;

uint32_t wlen;

} zero table t;

typedef struct {

uint32_t const* src;

uint32_t* dest;

uint32_t wlen;

} __copycode_table_t;

extern const __copy_table_t __copy_table_start_

_;

extern const __copy_table_t __copy_table_end__;

extern const __zero_table_t __zero_table_start_

extern const __zero_table_t __zero_table_end__;

extern const __copycode_table_t __copycode_table_start__;

extern const __copycode_table_t __copycode_table_end__;

for (__copy_table_t const* pTable = & _copy_table_start_; pTable < & _copy_table_end_; ++pTable) {</pre>

for(uint32_t i=0u; i<pTable->wlen; ++i) {

pTable->dest[i] = pTable->src[i];

}

}

for (__zero_table_t const* pTable = &__zero_table_start__; pTable < &__zero_table_end__; ++pTable)</pre>

{

for(uint32_t i=0u; i<pTable->wlen; ++i) {

pTable->dest[i] = 0u;

}

}

for (_

_copycode_table_t const* pTable = &__copycode_table_start__;    pTable < __copycode_table_end__;

++pTable)

{

for(uint32_t i=0u; i<pTable->wlen; ++i) {

pTable->dest[i] = pTable->src[i];

}

}

_start();

```

### 6.1.3. Allocating code

The function attribute section needs to be used for the functions and data that needs to be allocated in SRAM, ITCM or DTCM

\_\_attribute\_\_((\_\_section\_\_(".Section\_Name")))

Where the Section\_Name is the section that was previously declared in the linker file.

Use this attribute before the function or variable.

```

Example 13.

Use of the attribute section to allocate functions on ITCM, DTCM and SRAM

__attribute__((__section__(".DTCM_data")))uint32_t ClkCycleCounter[18] = {0};

__attribute__((__section__(".DTCM_data")))static uint8_t Counter;

/*

ITCM Function

/* Function loaded from ITCM. This function clean pDest and pSrc and copy the

*/

/* content of the array dummy[1024] stored in flash to pDest and pSrc

/* Inputs: *pDest = Pointer to Destination array

/*

*pSrc = Pointer to Source array

.

/*

size = Array size to copy

/*

Output: ClkCycleCounter Array = Store the number of cycles taken since the

beginning of the function until the end. There are 18 positions

/*

to store all function results

*****

/********

_attribute__((__section__(".ITCM_code")))

static void TCM_Function(uint8 t *pDest, uint8 t *pSrc, uint32 t size)

{

/* Function example content */

uint32_t i;

for(i=0u; i<size; i++)</pre>

{

pSrc[i] = 0u;

pDest[i] = 0u;

for(i=0u; i<size; i++)</pre>

{

pSrc[i] = pBuffer[i];

}

}

_attribute__((__section__(".SRAM_Function")))

static void SRAM_Function(uint8_t *pDest, uint8_t *pSrc, uint32_t size)

{

/* Function example content */

uint32_t i;

for(i=0u; i<size; i++)</pre>

{

pSrc[i] = 0u;

pDest[i] = 0u;

}

for(i=0u; i<size; i++)</pre>

{

pSrc[i] = pBuffer[i];

}

```

### 6.1.4. Results

The *Table 5* shows the number of cycles taken by functions and data on different memories. It is important to notice that the number of cycles is smaller when running from ITCM in comparison to running from Flash. This advantage can be used to reduce the number of cycles and timing for tasks that require deterministic times or avoid latencies. The *Table 5* also shows the use of enable Cache, Instruction Cache and Data Cache. When the D\_Cache and I\_Cache are enabled the number of cycles is reduced significantly. This is due to the fact that the Cache fetched all the code and data in its region. Flash and SRAM can be cacheable on S32K3, the TCM memory is zero wait access so no Cache is needed for ITCM and DTCM. This is a simple code and cache is enough to store all of it. However, in real application it is unlikely to place the entire code in Cache so the characteristics of TCM can be used as advantage.

| Table 5. Number of cycles taken by functions and data on different memories. |            |          |               |                    |               |               |            |               |  |

|------------------------------------------------------------------------------|------------|----------|---------------|--------------------|---------------|---------------|------------|---------------|--|

|                                                                              |            | S        | RAM           |                    | DTCM          |               |            |               |  |

|                                                                              | Cleaning 2 | Copying  |               | Total              | Cleaning 2    | Copying       |            | Total         |  |

|                                                                              | array      | array    | Copying       | (Cleaning +        | array         | array         | Copying    | (Cleaning +   |  |

|                                                                              | buffers    | from     | array from    | Flash to SRAM      | buffers       | from          | array from | Flash to DTCM |  |

|                                                                              | (size 1024 | Flash to | SRAM to       | + SRAM to          | (size 1024    | Flash to      | DTCM to    | + DTCM to     |  |

|                                                                              | bytes)     | SRAM     | SRAM          | SRAM)              | bytes)        | DTCM          | DTCM       | DTCM)         |  |

|                                                                              |            |          | Copying 102   | 24 Bytes - Disable | Cache and no  | o optimizatio | ons        |               |  |

| <b>Running Function from</b>                                                 |            |          |               |                    |               |               |            |               |  |

| Flash                                                                        | 28780      | 36829    | 30366         | 95975              | 27510         | 36794         | 24351      | 88655         |  |

| <b>Running Function from</b>                                                 |            |          |               |                    |               |               |            |               |  |

| SRAM                                                                         | 28956      | 36682    | 32398         | 98036              | 27505         | 36746         | 27718      | 91969         |  |

| <b>Running Function from</b>                                                 |            |          |               |                    |               |               |            |               |  |

| ITCM                                                                         | 28838      | 33793    | 29687         | 92318              | 27492         | 33817         | 24300      | 85609         |  |

|                                                                              |            |          | Copying 102   | 4 Bytes - Enable   | I Cache and n | o optimizati  | ons        |               |  |

| Code is fetched to I-                                                        | 28930      | 38602    | 29720         | 97252              | 27496         | 36708         | 24321      | 88525         |  |

| Code is retched to I-                                                        | 28911      | 38581    | 29709         | 97201              | 27500         | 36708         | 24322      | 88530         |  |

| Cacilie                                                                      | 28902      | 33806    | 29687         | 92395              | 27492         | 33817         | 24300      | 85609         |  |

|                                                                              |            | Соруі    | ing 1024 Byte | s - Enable I Cache | e and D Cache | and no opti   | mizations  |               |  |

| Code and Data is                                                             | 13428      | 14792    | 11315         | 39535              | 13329         | 14392         | 11314      | 39035         |  |

| fetched to I-Cache and                                                       | 13458      | 14392    | 11314         | 39164              | 13330         | 14392         | 11314      | 39036         |  |

| D-Cache                                                                      | 13458      | 14392    | 11314         | 39164              | 13330         | 14392         | 11313      | 39035         |  |

Table 5.

Number of cycles taken by functions and data on different memories.

It can be noticed that while running code from ITCM and transferring data to DTCM we have the same result similar to the I-Cache run. This is because the TCM and core spend the same number of cycles as Cache.

## 6.2. SRAM standby

There are 32 KB of SRAM memory that are available when the MCU is in standby mode. This memory region allows to store critical data or important code that needs to be available when the MCU wakes from the standby mode. The MCU operates in two modes: Run mode and Standby mode. When it operates in run mode the MCU has available all the peripherals and modules. In Standby mode the MCU has available only a few of them because some of the power domains are disconnected from the power supply inside the chip. The purpose of this is to achieve a low power mode in order to save power consumption and wake up with an event, power on reset, destructive reset or a functional reset.

The next use case is a simple exercise that shows the Standby SRAM memory feature.

## 6.2.1. Linker file

First at all, in the linker file the SRAM Standby region need to be declared, please refer to the *Example 9. Linker memory definition and size*

As noted, the Standby SRAM is allocated at the first 32 KB of the SRAM Memory.

## 6.2.2. Main file

For the purpose of this example we are going to use three buffers:

• dummy\_array[1024]: this is an array located in Flash, its size is 1024 bytes.

```

const uint8_t dummy_array[1024UL] =

{

0x00,0x01,0x02,0x03,...

}

```

SRAM\_buffer[BUFFER\_SIZE]: this is an array that will be located in the SRAM memory in any region after 0x20408000 address.

uint8\_t SRAM\_buffer [BUFFER\_SIZE];

SRAM\_SB\_buffer[BUFFER\_SIZE]: this is an array that will be located in the Standby memory

```

__attribute((section(".standby_ram"))) uint8_t SRAM_SB_buffer [BUFFER_SIZE];

```

Where BUFFER\_SIZE has been defined as 1024

#define BUFFER\_SIZE 1024

In the main file array buffers are cleared and dummy array bytes are copied to SRAM\_buffer[] and SRAM\_SB\_buffer[].

S32K3 Memories Guide, Rev. 0, 11/2021

### Use Cases

```

Uint32_t *pDest_SRAM_SB;

pDest_SRAM_SB = &SRAM_SB_buffer;

/* Clear buffer */

for(i=0; i<BUFFER_SIZE; i++)

{

SRAM_SB_buffer[i] = 0;

SRAM_buffer[i] = 0;

}

/* Copy dummy array into SRAM_buffer and SRAM_SB_buffer*/

for(i=0u; i<BUFFER_SIZE; i++)

{

pDest_SRAM_SB[i] = dummy_array[i];

SRAM_buffer[i] = dummy_array[i];

}

```

### SRAM\_SB\_buffer[]

| Monito     | rs 🚽       | × 🕺 | 0x20400000 : 0 | x20400000 <he< th=""><th>x&gt; 🕱 🖕 N</th><th>lew Renderings.</th><th>•)</th><th></th></he<> | x> 🕱 🖕 N | lew Renderings. | •)       |          |          |

|------------|------------|-----|----------------|---------------------------------------------------------------------------------------------|----------|-----------------|----------|----------|----------|

| ۵.         | 0x20400000 |     | Address        | 0 - 3                                                                                       | 4 - 7    | 8 - B           | C - F    | ^        |          |

| 0x2040844c | 0x2040844c |     | 20400000       | 00010203                                                                                    | 04050607 | 08090A0B        | 0C0D0E0F |          |          |

|            |            |     |                |                                                                                             | 20400010 | 10111213        | 14151617 | 18191A1B | 1C1D1E1F |

|            |            |     | 20400020       | 20212223                                                                                    | 24252627 | 28292A2B        | 2C2D2E2F |          |          |

|            |            |     | 20400030       | 30313233                                                                                    | 34353637 | 38393A3B        | 3C3D3E3F |          |          |

|            |            |     | 20400040       | 40414243                                                                                    | 44454647 | 48494A4B        | 4C4D4E4F |          |          |

|            |            |     | 20400050       | 50515253                                                                                    | 54555657 | 58595A5B        | 5C5D5E5F |          |          |

|            |            |     | 20400060       | 60616263                                                                                    | 64656667 | 68696A6B        | 6C6D6E6F |          |          |

|            |            |     | 20400070       | 70717273                                                                                    | 74757677 | 78797A7B        | 7C7D7E7F | ~        |          |

Figure 6. Standby SRAM map memory

### SRAM\_buffer[ ]

| Monitors  | ÷  | × | × | 0x2040844c : 0 | x2040844C <he< th=""><th>ex&gt; 🕱 🔶 🗛</th><th>New Renderings</th><th>)</th><th></th></he<> | ex> 🕱 🔶 🗛 | New Renderings | )        |          |          |          |          |          |          |          |          |  |

|-----------|----|---|---|----------------|--------------------------------------------------------------------------------------------|-----------|----------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--|

| 0x2040000 |    |   |   | Address        | 0 - 3                                                                                      | 4 - 7     | 8 - B          | C - F    | ^        |          |          |          |          |          |          |          |  |

| Ox2040844 | 4c |   |   |                |                                                                                            |           |                |          |          |          |          | 20408440 | 00000000 | 00000000 | 00000000 | 00010203 |  |

|           |    |   |   |                |                                                                                            |           |                | 20408450 | 04050607 | 08090A0B | 0C0D0E0F | 10111213 |          |          |          |          |  |

|           |    |   |   | 20408460       | 14151617                                                                                   | 18191A1B  | 1C1D1E1F       | 20212223 |          |          |          |          |          |          |          |          |  |

|           |    |   |   | 20408470       | 24252627                                                                                   | 28292A2B  | 2C2D2E2F       | 30313233 |          |          |          |          |          |          |          |          |  |

|           |    |   |   | 20408480       | 34353637                                                                                   | 38393A3B  | 3C3D3E3F       | 40414243 |          |          |          |          |          |          |          |          |  |

|           |    |   |   | 20408490       | 44454647                                                                                   | 48494A4B  | 4C4D4E4F       | 50515253 |          |          |          |          |          |          |          |          |  |

|           |    |   |   | 204084A0       | 54555657                                                                                   | 58595A5B  | 5C5D5E5F       | 60616263 |          |          |          |          |          |          |          |          |  |

|           |    |   |   | 204084B0       | 64656667                                                                                   | 68696A6B  | 6C6D6E6F       | 70717273 | ~        |          |          |          |          |          |          |          |  |

Figure 7. SRAM map memory

After that a dummy read is performed in order to validate that the data is available from Standby SRAM and SRAM memory.

| Example 15.                                | Dummy read to Standby SRAM array and SRAM array |

|--------------------------------------------|-------------------------------------------------|

| <pre>read_SRAM_SB = *(uint32_t*) 0x2</pre> | 20400000;                                       |

| read_SRAM = *(uint32_t*) 0x2040            | ð8830;                                          |

S32K3 Memories Guide, Rev. 0, 11/2021

\_

| (x)= read_SRAM_SB | uint32_t | 0x3020100 (Hex)  |

|-------------------|----------|------------------|

| (x)= read_SRAM    | uint32_t | 0xe7e6e5e4 (Hex) |

Figure 8. Data read by dummy read

The Standby entry sequence is performed by pressing SW4 in the interrupt handler.

```

Example 16.SW4 configuration to generate an interrupt to enter to Standby/* Pin Configuration for PTB26 (SW4) */<br/>SIUL2->IREER0 &= ~SIUL2_IREER0_IREE13_MASK; /* Disable Rising Edge event */<br/>SIUL2->IFEER0 |= SIUL2_IFEER0_IFEE13_MASK; /* Enable Falling Edge event */<br/>SIUL2->IMCR[541-512] |= SIUL2_IMCR_SSS(0b010); /* Enable Source Signal EIRQ[13] */<br/>SIUL2->MSCR[58] |= SIUL2_MSCR_IBE_MASK; /* IBE=1: Input Buffer Enabled */<br/>SIUL2->DIRSR0 &= ~SIUL2_DIRSR0_DIRSR13_MASK; /* Select Interrupt Request for PTB26 */<br/>SIUL2->DISR0 = 0xFFFFFFFU; /* Clear Status Flag Interrupt */<br/>SIUL2->DIRER0 |= SIUL2_DIRER0_EIRE13_MASK; /* External Interrupt enable for EIRQ[13] */

```

```

Example 17. Interrupt routine to entry to Standby

```

```

void SIUL_1_Handler (void)

{

/* Wait until SW4 (PTB26) release */

while ((SIUL2->GPDI58 & SIUL2_GPDI58_PDI_n_MASK) == 1) { }

/* Drive low on PTB30 to turn-off LED D32 */

SIUL2->GPD030 &= ~SIUL2_GPD030_PDO_n_MASK;

Standby_Entry_Sequence();

}

```

Once Standby\_Entry\_Sequence is performed the S32K3 enters into standby mode and the debugger is disconnected.

### 6.2.3. Wakeup

The wakeup process is performed by pressing the SW5 which is configured to generate an interrupt.

Example 18. SW5 configuration to generate a wakeup from Standby

```

/* Pin Configuration for PTB19 (SW5)

// WKPU[38]

SIUL2->MSCR[51] = SIUL2_MSCR_IBE_MASK

/* IBE=1: Input Buffer Enabled */

SIUL2_MSCR_PUE_MASK;

WKPU->WIFEER_64 &= ~0x00000400; /* Disable WKPU[38] falling edge */

/* Enable WKPU[38] rising edge */

WKPU->WIREER_64 |= 0x00000400;

WKPU->WIFER 64 |= 0x00000400;

/* WKPU[38] glitch filter enabled */

WKPU->WISR_64 = 0x00000400;

/* Write 1 to Clear WKPU[38] flag */

WKPU->IRER 64 |= 0 \times 00000400;

/* Write 1 to Interrupt request WKPU[38] flag */

WKPU->NCR &= ~(WKPU_NCR_NDSS0_MASK | WKPU_NCR_NDSS1_MASK); /* NMI Destination Source Select */

WKPU->NCR |= WKPU_NCR_NWRE0_MASK | WKPU_NCR_NWRE1_MASK; /* NMI Wakeup Request Enable */

WKPU->WRER_64 | = 0 \times 0000400;

/* Enable WKPU[38] input */

```

After wakeup the MCU can be reconnected to the Debugger selecting the following remarked option in the S32DS.

### Use Cases

| 📄 Main (参 Debugger 🅟 Startup 🛛 🦃 Source) 📰 Common 🔤 SVD Support 🕮 OS Awarenes | S         |             |

|-------------------------------------------------------------------------------|-----------|-------------|

| Semihosting Settings                                                          |           | ^           |

| Enable semihosting Console routed to: 🗹 Telnet 🗌 GDB client                   |           |             |

| Enable Telnet console Telnet Port: 51794                                      |           |             |

| Load Symbols and Executable                                                   |           |             |

| ☑ Load symbols                                                                |           |             |

| Our Use project binary: S32DS3p3_S32K3XXMB_STANDBY_RAM.elf                    |           |             |

| O Use f Use C/C++ application specified in the Main tab.                      | Workspace | File System |

| Symbols offset (hex):                                                         |           |             |

| ✓ Load executable                                                             |           |             |

| Use project binary: S32DS3p3_S32K3XXMB_STANDBY_RAM.elf                        |           |             |

| O Use file:                                                                   | Workspace | File System |

| Executable offset (hex):                                                      |           |             |

| Runtime Options                                                               |           |             |

| Attach to Running Target                                                      |           |             |

| Set PC (absolute hex address or symbol):                                      |           |             |

| GDB run commands:                                                             |           |             |

|                                                                               |           | ~ V         |

|                                                                               |           |             |

|                                                                               | Reve      | ert Apply   |

Figure 9. Option to reconnect the debugger to the current code position

The interrupt handler is shown in the *Example 19*.

```

Example 19. Interrupt routine is attended after wakeup

```

```

void WKPU_Handler (void)

{

for(uint32_t i=0; i<0x02FFFFF; i++)

{

___NOP();

}

read_SRAM_SB = *(uint32_t*) 0x20400000;

read_SRAM = *(uint32_t*) 0x20408830;

while(1);

}</pre>

```

Where

| (x)= read_SRAM_SB | uint32_t | 0x3020100 (Hex) |

|-------------------|----------|-----------------|

| (x)= read_SRAM    | uint32_t | 0x0 (Hex)       |

Figure 10. Data read by dummy read

SRAM\_SB\_buffer[]

| Monitors 🚽 | 🗶 💥 0x2040000 | 0 : 0x20400000 <he< th=""><th>x&gt; 🕄 🕂 🗛</th><th>lew Renderings.</th><th colspan="2"></th></he<> | x> 🕄 🕂 🗛 | lew Renderings. |          |     |

|------------|---------------|---------------------------------------------------------------------------------------------------|----------|-----------------|----------|-----|

| 0x20400000 | Address       | 0 - 3                                                                                             | 4 - 7    | 8 - B           | C - F    | ^   |

| 0x2040844c | 204000        | 00 00010203                                                                                       | 04050607 | 08090A0B        | 0C0D0E0F |     |

|            | 204000        | 10 10111213                                                                                       | 14151617 | 18191A1B        | 1C1D1E1F |     |

|            | 204000        | 20 20212223                                                                                       | 24252627 | 28292A2B        | 2C2D2E2F | - 1 |

|            | 204000        | 30 30313233                                                                                       | 34353637 | 38393A3B        | 3C3D3E3F |     |

|            | 204000        | 40 40414243                                                                                       | 44454647 | 48494A4B        | 4C4D4E4F |     |

|            | 204000        | 50 50515253                                                                                       | 54555657 | 58595A5B        | 5C5D5E5F |     |

|            | 204000        | <b>60</b> 60616263                                                                                | 64656667 | 68696A6B        | 6C6D6E6F |     |

|            | 204000        | 70 70717273                                                                                       | 74757677 | 78797A7B        | 7C7D7E7F | ¥   |

Figure 11. Standby SRAM map memory

### SRAM\_buffer[]

| Monitors 🛛 🖕 💥 💥 |         |          | 0x2040844c : 0x2040844C <hex> 🕱 👍 New Renderings)</hex> |          |          |          | )        |   |

|------------------|---------|----------|---------------------------------------------------------|----------|----------|----------|----------|---|

| Ox2              | 0400000 |          | Address                                                 | 0 - 3    | 4 - 7    | 8 - B    | C - F    | ^ |

| ♦ 0x2040844c     |         | 20408440 | 00000000                                                | 00000000 | 00000000 | 00000000 |          |   |

|                  |         |          | 20408450                                                | 00000000 | 00000000 | 00000000 | 00000000 |   |

|                  |         |          | 20408460                                                | 00000000 | 00000000 | 00000000 | 00000000 |   |

|                  |         |          | 20408470                                                | 00000000 | 00000000 | 00000000 | 00000000 |   |

|                  |         |          | 20408480                                                | 00000000 | 00000000 | 00000000 | 00000000 |   |

|                  |         |          | 20408490                                                | 00000000 | 00000000 | 00000000 | 00000000 |   |

|                  |         |          | 204084A0                                                | 00000000 | 00000000 | 00000000 | 00000000 |   |

|                  |         |          | 204084B0                                                | 00000000 | 00000000 | 00000000 | 00000000 |   |

Figure 12. SRAM map memory

### 6.2.4. Results

As noted, the data stored in the Standby SRAM memory sourced by Standby domain is retained when the MCU is in standby mode and available after the wakeup. But the data in SRAM sourced by Run domain is not available and it needs to be initialized after the wakeup to avoid ECC errors. Is important to remark that after wakeup, the Standby SRAM doesn't need to be initialized to avoid ECC error, but the rest of the SRAM does need it, so a proper distinction should be performed in the Startup code. An example to make this distinction is depicted in the following code.

Example 20. Standby RAM initialization only after POR

```

/* Initialize STANDBY RAM if chip comes from POR */

if (MC_RGM->DES & MC_RGM_DES_F_POR_MASK)

{

/* Initialize STANDBY RAM */

cnt = (( uint32_t)(&_STDBYRAM_SIZE)) / 8U;

pDest = (uint64_t *)(&_STDBYRAM_START);

while (cnt--)

{

*pDest = (uint64_t)0xDEADBEEFCAFEFEEDULL;

pDest++;

}

MC_RGM->DES = MC_RGM_DES_F_POR_MASK; /* Write 1 to clear F_POR */

}

```

## 7. SW recommendations and conclusions

A correct use of different memories available in the S32K3 Product Family can represent a better performance of our application. The user needs to evaluate what functions and data of the application will be stored in the different memories in order to have the best performance.

The three important recommendation to get a good performance in applications are:

- Deterministic task should be considered to be inside the ITCM and DTCM because cores can avoid significant access time to other memories.

- Enable Caches has a great advantage for the applications due to it fetched code and data that cores need in a quickly time, Cache can be enabled and disabled in certain location of the code in order to have a better control of what code or data need to be fetched, is important to note that Cache needs to be invalidated before fetch new code or data, unfortunately the Cache size is small but we can use Tightly Coupled Memory to support the lack of Cache's space.

- The Standby SRAM is another advantage that can be explored in different applications because after our application wakes up from standby mode the data stored in Standby SRAM can be used without doing any other operation. A good example is sending the stored data when an external communication wakes up the MCU from standby mode.

## 8. References

- S32K3xx Reference Manual

- S32K3xx Data Sheet

- Customer Evaluation Board S32K3XXEVB-Q257

- Automotive SW S32K3 Real-Time Drivers for Cortex-M

- S32 Design Studio IDE

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein. NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C 5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm, AMBA, Arm Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and μVision are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. Arm7, Arm9, Arm11,

big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, Mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2021 NXP B.V.

Document Number: AN13388 Rev. 0 11/2021

# arm