# AN4254

# Utilizing Enhanced Software Write Protection in 24CS Series Serial EEPROMs

Author: Erik Fasnacht Microchip Technology Inc.

### INTRODUCTION

Traditional I<sup>2</sup>C Serial EEPROMs utilize hardwarebased write protection that only allows locking or unlocking the entire memory array via an external pin, which severely limits the possible ways to protect data. The 24CS Series devices address this limitation with the addition of a 16-bit Configuration register, which allows the write protection behavior to be configured for legacy hardware write protection or enhanced software write protection.

Legacy hardware write protection uses the Write Protection (WP) pin to write-protect the entire memory array when the WP pin is '1'. As the name suggests, Legacy write protection mode behaves identically to standard I<sup>2</sup>C Serial EEPROMs. However, many of today's applications can benefit from greater flexibility in managing data protection. For these applications, the 24CS provides the option to use enhanced software write protection, which allocates eight zones within the memory array that can be independently set to be write-protected. This added flexibility allows for the 24CS Series devices to provide much more granular data protection as required by the application. The desired write protection settings are set via the Configuration register, which can be accessed by sending commands to a specific device address and word address. If desired, the Configuration register can be locked so that it is set to read-only and can no longer be modified, thereby making the current data protection scheme permanent. This application note is intended to demonstrate how to utilize the 16-bit Configuration register to setup data protection in your application.

### **Configuration Register Byte 0**

The Configuration register format and bit definitions for the Most Significant Byte (MSB) is seen in Register 1. This byte contains status information along with bits for setting the current write protection behavior and locking the Configuration register.

| R-0                                                                  | U-0                      | U-0                                | U-0              | U-0              | U-0              | R/W              | R/W            |  |  |

|----------------------------------------------------------------------|--------------------------|------------------------------------|------------------|------------------|------------------|------------------|----------------|--|--|

| ECS                                                                  | —                        | —                                  | _                | _                | —                | EWPM             | LOCK           |  |  |

| bit 15                                                               |                          | •                                  |                  |                  |                  | •                | bit 8          |  |  |

|                                                                      |                          |                                    |                  |                  |                  |                  |                |  |  |

| Legend:                                                              |                          |                                    |                  |                  |                  |                  |                |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                          |                                    |                  |                  |                  |                  |                |  |  |

| -n = Value at                                                        | POR                      | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkr  | nown           |  |  |

|                                                                      |                          |                                    |                  |                  |                  |                  |                |  |  |

| bit 15                                                               | ECS: Error Co            | orrection State                    | bit              |                  |                  |                  |                |  |  |

|                                                                      |                          | iously execute                     | d read operati   | on did require   | the use of the E | Error Correction | n Code (ECC)   |  |  |

|                                                                      | scheme                   |                                    |                  |                  |                  |                  |                |  |  |

|                                                                      | 0 = The prev<br>(ECC) sc | -                                  | a read opera     | tion did not re  | quire the use o  | t the Error Co   | rrection Code  |  |  |

| bit 14-10                                                            | Unimplemen               | ted: Read as '                     | O'               |                  |                  |                  |                |  |  |

| bit 9                                                                | EWPM: Enha               | nced Software                      | Write Protect    | ion Mode bit     |                  |                  |                |  |  |

|                                                                      |                          |                                    |                  |                  | care and the n   | nemory array i   | s protected in |  |  |

|                                                                      |                          | ce with the SV                     |                  |                  |                  |                  |                |  |  |

|                                                                      |                          | Protection (fac<br>I via the WP pi |                  | Entire memor     | y array and Se   | ecurity register | contents are   |  |  |

| bit 8                                                                | LOCK: Lock (             | Configuration F                    | Register bit     |                  |                  |                  |                |  |  |

|                                                                      | 1 = The Confi            | guration regist                    | er is set to rea | id-only (perma   | nent)            |                  |                |  |  |

|                                                                      | 0 = The Confi            | guration regist                    | er can be writt  | ten to (factory  | default)         |                  |                |  |  |

|                                                                      |                          |                                    |                  |                  |                  |                  |                |  |  |

# REGISTER 1: CONFIGURATION REGISTER – BYTE 0

#### ERROR CORRECTION STATE (ECS) BIT

This bit is used when the user needs to determine whether the on-chip Error Correction Code (ECC) logic scheme has been invoked. The ECS bit will be set to logic '0' unless the previously executed read operation required the use of the ECC logic scheme. When this occurs, the ECS bit will set to logic '1'. The ECS bit will continue to read a logic '1' until another read operation is issued and the use of the ECC logic scheme was not required or a Power-on Reset (POR) event has occurred.

#### ENHANCED SOFTWARE WRITE PROTECTION MODE (EWPM) BIT

This bit is used to select between Legacy Hardware Write Protection mode (logic '0') and Enhanced Software Write Protection mode (logic '1'). Legacy Hardware Write Protection mode allows the entire memory array to be write-protected via the WP pin.

Enhanced Software Write Protection is a software write-protect feature where the memory array is divided into eight separate zones. Each zone is independent and is configured using the SWP[7:0] bits (Register 2).

#### Legacy Write Protection Mode

When the EWPM bit is set to logic '0', the 24CS Series utilizes a legacy hardware data protection scheme that allows the user to write-protect the entire memory contents when the WP pin is asserted (high). No write protection will be set if the WP pin is deasserted (low).

| WP Pin   | Protected Address Range |

|----------|-------------------------|

| 1 (high) | Full Array              |

| 0 (low)  | None                    |

#### TABLE 1: LEGACY HARDWARE WRITE PROTECTION BEHAVIOR

#### Enhanced Write Protection Mode

When the EWPM bit is set to logic '1', the 24CS Series is configured for a versatile software write protection scheme by segmenting the EEPROM array into eight independent zones. Each of the eight zones can be write-protected by programming the corresponding bit (see Register 2) in the Configuration register. The protection behavior can be made permanent by locking the Configuration register.

# LOCK CONFIGURATION REGISTER (LOCK) BIT

This bit allows the user to lock the Configuration register by setting it to read-only so that it can no longer be modified. When the LOCK bit is set to logic '1', the current data protection scheme becomes permanent.

#### **Configuration Register Byte 1**

The Configuration register format and bit definitions for the Least Significant Byte (LSB) is seen in Register 2. This byte contains the eight independent Software Write Protection Memory Zone (SWP[7:0]) bits.

#### **REGISTER 2: CONFIGURATION REGISTER – BYTE 1**

| R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W   |

|-------|------|------|------|------|------|------|-------|

| SWP7  | SWP6 | SWP5 | SWP4 | SWP3 | SWP2 | SWP1 | SWP0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### If EWPM = 1:

| bit 7                  | SWP7: Software Write Protection Memory Zone 7 bit |

|------------------------|---------------------------------------------------|

|                        | 1 = Memory Zone 7 is write-protected              |

|                        | 0 = Memory Zone 7 is not write-protected          |

| bit 6                  | SWP6: Software Write Protection Memory Zone 6 bit |

|                        | 1 = Memory Zone 6 is write-protected              |

|                        | 0 = Memory Zone 6 is not write-protected          |

| bit 5                  | SWP5: Software Write Protection Memory Zone 5 bit |

|                        | 1 = Memory Zone 5 is write-protected              |

|                        | 0 = Memory Zone 5 is not write-protected          |

| bit 4                  | SWP4: Software Write Protection Memory Zone 4 bit |

|                        | 1 = Memory Zone 4 is write-protected              |

|                        | 0 = Memory Zone 4 is not write-protected          |

| bit 3                  | SWP3: Software Write Protection Memory Zone 3 bit |

|                        | 1 = Memory Zone 3 is write-protected              |

|                        | 0 = Memory Zone 3 is not write-protected          |

| bit 2                  | SWP2: Software Write Protection Memory Zone 2 bit |

|                        | 1 = Memory Zone 2 is write-protected              |

|                        | 0 = Memory Zone 2 is not write-protected          |

| bit 1                  | SWP1: Software Write Protection Memory Zone 1 bit |

|                        | 1 = Memory Zone 1 is write-protected              |

|                        | 0 = Memory Zone 1 is not write-protected          |

| bit 0                  | SWP0: Software Write Protection Memory Zone 0 bit |

|                        | 1 = Memory Zone 0 is write-protected              |

|                        | 0 = Memory Zone 0 is not write-protected          |

| If <b>FWPM</b> = $0$ : |                                                   |

#### If EWPM = 0:

bit 7-0 Unused

# SOFTWARE WRITE PROTECTION MEMORY ZONE (SWP[7:0]) BITS

These bits divide the memory array into eight separate zones. Each zone can be set independently from the other protection zones. The corresponding SWP bit must be set to a logic '1' to write-protect that zone.

Note: In Legacy Hardware Write Protection mode (EWPM = '0'), the SWP[7:0] bits are ignored. However, a dummy value must still be sent during the write sequence to initiate the internal write operation.

#### Accessing the Register

The value of the Configuration register can be determined by executing a random read sequence to a specific word address. Changing the value of the Configuration register is accomplished with a byte write sequence with specific data sent to the device.

#### DEVICE ADDRESS REQUIREMENTS

Accessing this register requires the use of '1011b' (Bh) as the device type identifier in the device address (see Table 2). Following the device type identifier are the hardware client address bits for which the values are determined by the device address input pins A2, A1 and A0. Finally, bit 0 is the Read/Write Select (R/W) bit where a logic '1' is used for reading and a logic '0' is used for writing.

#### TABLE 2: CONFIGURATION REGISTER DEVICE ADDRESS BYTE

| Mamony Design          | [     | Device Typ | e Identifie | r     | Hardwa | Read/Write |       |       |

|------------------------|-------|------------|-------------|-------|--------|------------|-------|-------|

| Memory Region          | Bit 7 | Bit 6      | Bit 5       | Bit 4 | Bit 3  | Bit 2      | Bit 1 | Bit 0 |

| Configuration Register | 1     | 0          | 1           | 1     | A2     | A1         | A0    | R/W   |

**Note 1:** The hardware client address bits must be set to logic '0' when using the SOT-23 package.

#### WORD ADDRESS REQUIREMENTS

When accessing the Configuration register, a 16-bit word address must be sent to the device. All bits in the word address are ignored except for bits A15, A11 and A10. Bits A15 and A11 must be set to logic '1' and bit A10 must be set to logic '0'. Refer to Table 3 and Table 4 for additional information.

#### TABLE 3: CONFIGURATION REGISTER WORD ADDRESS BYTE 0

| Word Address        | A15 | A14 | A13 | A12 | A11 | A10 | A9 | <b>A</b> 8 |

|---------------------|-----|-----|-----|-----|-----|-----|----|------------|

| Word Address Byte 0 | 1   | х   | х   | х   | 1   | 0   | х  | Х          |

#### TABLE 4: CONFIGURATION REGISTER WORD ADDRESS BYTE 1

| Word Address        | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|---------------------|----|----|----|----|----|----|----|----|

| Word Address Byte 1 | х  | х  | х  | Х  | Х  | Х  | Х  | Х  |

### WRITE OPERATION

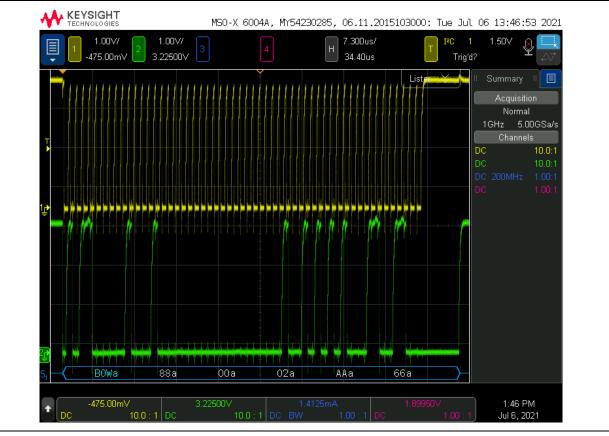

When writing the Configuration register, a write sequence must be sent to the device that includes both data bytes (Byte 0 and Byte 1), along with a valid confirmation byte. Figure 1 illustrates an example Configuration register write sequence.

#### **Confirmation Byte**

In order for the internal write process to start, both data bytes (Byte 0 and Byte 1), along with a confirmation byte, need to be sent to the device. Sending anything other than these three bytes will cause the write cycle to abort and the contents of the Configuration register will not change.

The data of the confirmation byte depends on the value being written to the LOCK bit. If the user intends to lock the Configuration register (LOCK = '1'), the confirmation byte must be 99h. If the user intends to leave the register unlocked (LOCK = '0'), the confirmation byte must be 66h. Table 5 illustrates the valid data values for the confirmation byte.

**Note:** The Configuration register cannot be unlocked once it is locked.

#### TABLE 5: CONFIGURATION REGISTER CONFIRMATION BYTE

| New LOCK Bit Value | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|--------------------|----|----|----|----|----|----|----|----|

| 1 (locked)         | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  |

| 0 (unlocked)       | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  |

#### FIGURE 1: CONFIGURATION REGISTER WRITE

## **READ OPERATION**

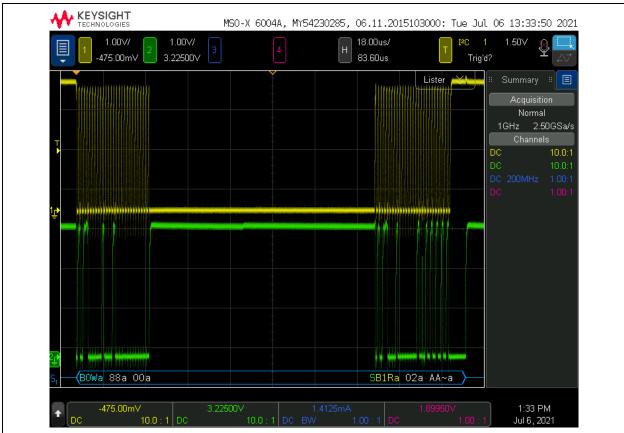

When reading the Configuration register, a random read sequence must be sent to the device.

Figure 2 illustrates an example of the Configuration register read sequence. It is not possible to read the contents of the Configuration register with a current address read sequence as the correct word address bytes must be sent to the device.

Note: The 24CS Series will automatically roll over from the second Configuration register data byte to the first data byte if the host continues to acknowledge the data bytes during the read operation.

#### FIGURE 2: CONFIGURATION REGISTER READ

# CONCLUSION

This application note gives details on the flexible write protection the  $I^2C$  Configuration register offers. Details related to  $I^2C$  Configuration register and device operation can be found in the appropriate device data sheet found at www.microchip.com.

# APPENDIX A: REVISION HISTORY

# Revision A (10/2021)

Initial release of this document.

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at https:// www.microchip.com/en-us/support/design-help/client-supportservices.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSE-QUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, Symmcom, and Trusted Time are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2021, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-5224-9102-6

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138 China - Zhuhai

Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631 India - Pune

Tel: 91-20-4121-0141 Japan - Osaka

Tel: 81-6-6152-7160 Japan - Tokyo

Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301 Korea - Seoul

Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore Tel: 65-6334-8870

Taiwan - Hsin Chu

Tel: 886-3-577-8366 **Taiwan - Kaohsiung** Tel: 886-7-213-7830

Taiwan - Taipei Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

Tel: 31-416-690399 Fax: 31-416-690340

Italy - Milan

Italy - Padova

EUROPE

Austria - Wels

Tel: 43-7242-2244-39

Tel: 45-4485-5910

Fax: 45-4485-2829

Tel: 358-9-4520-820

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching

Tel: 49-2129-3766400

Germany - Heilbronn

Germany - Karlsruhe

Tel: 49-7131-72400

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Germany - Rosenheim

Tel: 49-8031-354-560

Israel - Ra'anana

Tel: 972-9-744-7705

Tel: 39-0331-742611

Fax: 39-0331-466781

Tel: 39-049-7625286

**Netherlands - Drunen**

Tel: 49-8931-9700

Germany - Haan

Finland - Espoo

France - Paris

Fax: 43-7242-2244-393

Denmark - Copenhagen

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820