**TMAG5273** SLYS045A - JUNE 2021 - REVISED SEPTEMBER 2021

# TMAG5273 Low-Power Linear 3D Hall-Effect Sensor With I<sup>2</sup>C Interface

### 1 Features

- · Configurable power modes including:

- 2.3-mA active mode current

- 1-µA wake-up and sleep mode current

- 5-nA sleep mode current

- Selectable linear magnetic range at X, Y, or Z axis:

- TMAG5273x1: ±40 mT. ±80 mT

- TMAG5273x2: ±133 mT, ±266 mT

- Interrupt signal from user-defined magnetic and temperature threshold cross

- 5% (typical) sensitivity drift

- Integrated angle CORDIC calculation with gain and offset adjustment

- 20-kSPS single axis conversion rate

- Configurable averaging up to 32x for noise reduction

- Conversion trigger by I<sup>2</sup>C or dedicated INT pin

- Optimized I<sup>2</sup>C interface with cyclic redundancy check (CRC):

- Maximum 1-MHz I<sup>2</sup>C clock speed

- Special I<sup>2</sup>C frame reads for improved throughput

- Factory-programmed and user-configurable I<sup>2</sup>C addresses

- Integrated temperature compensation for multiple magnet types

- Built-in temperature sensor

- 1.7-V to 3.6-V supply voltage V<sub>CC</sub> range

- Operating temperature range: -40°C to +125°C

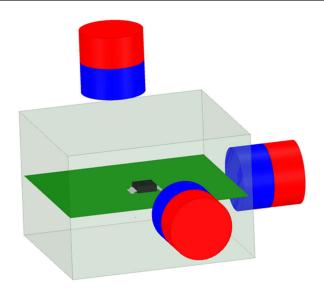

# 2 Applications

- **Electricity meters**

- Electronic smart lock

- **Smart thermostat**

- Joystick & gaming controllers

- Drone payload control

- Door & window sensor

- Magnetic proximity sensor

- Mobile robot motor control

- E-bike

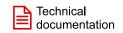

**Application Block Diagram**

# 3 Description

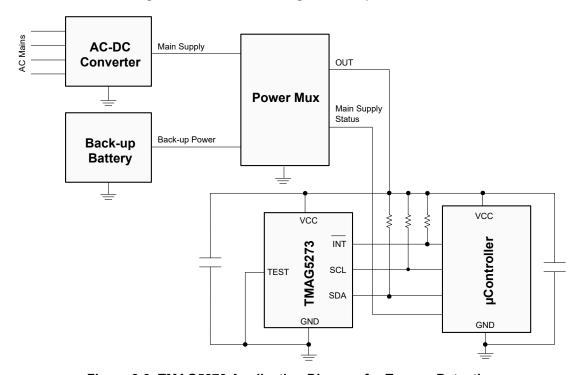

The TMAG5273 is a low-power linear 3D Hall-effect sensor designed for a wide range of industrial and personal electronics applications. This device integrates three independent Hall-effect sensors in the X, Y, and Z axes. A precision analog signalchain along with an integrated 12-bit ADC digitizes the measured analog magnetic field values. The I<sup>2</sup>C interface, while supporting multiple operating V<sub>CC</sub> ranges, ensures seamless data communication with low-voltage microcontrollers. The device has an integrated temperature sensor available for multiple system functions, such as thermal budget check or temperature compensation calculation for a given magnetic field.

The TMAG5273 can be configured through the I<sup>2</sup>C interface to enable any combination of magnetic axes and temperature measurements. Additionally, the device can be configured to various power options (including wake-up and sleep mode) allowing designers to optimize system power consumption based on their system-level needs. Multiple sensor conversion schemes and I<sup>2</sup>C read frames help optimize throughput and accuracy. A dedicated INT pin can act as a system interrupt during low power wake-up and sleep mode, and can also be used by a microcontroller to trigger a new sensor conversion.

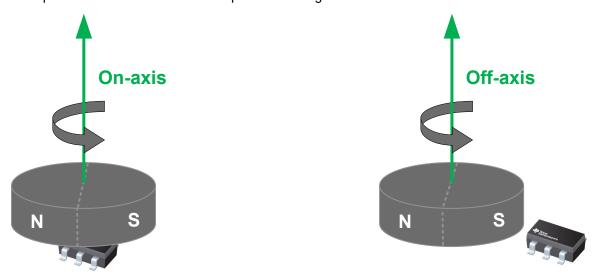

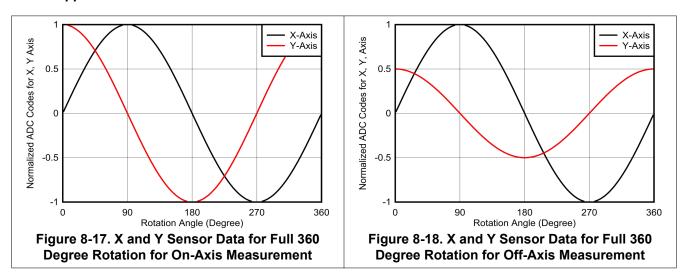

An integrated angle calculation engine (CORDIC) provides full 360° angular position information for both on-axis and off-axis angle measurement topologies. The angle calculation is performed using two user-selected magnetic axes. The device features magnetic gain and offset correction to mitigate the impact of system mechanical error sources.

The TMAG5273 is offered in four different factoryprogrammed I<sup>2</sup>C addresses. The device also supports additional I<sup>2</sup>C addresses through the modification of a user-configurable I<sup>2</sup>C address register. Each orderable part can be configured to select one of two magnetic field ranges that suits the magnet strength and component placement during system calibration.

The device performs consistently across a wide ambient temperature range of -40°C to +125°C.

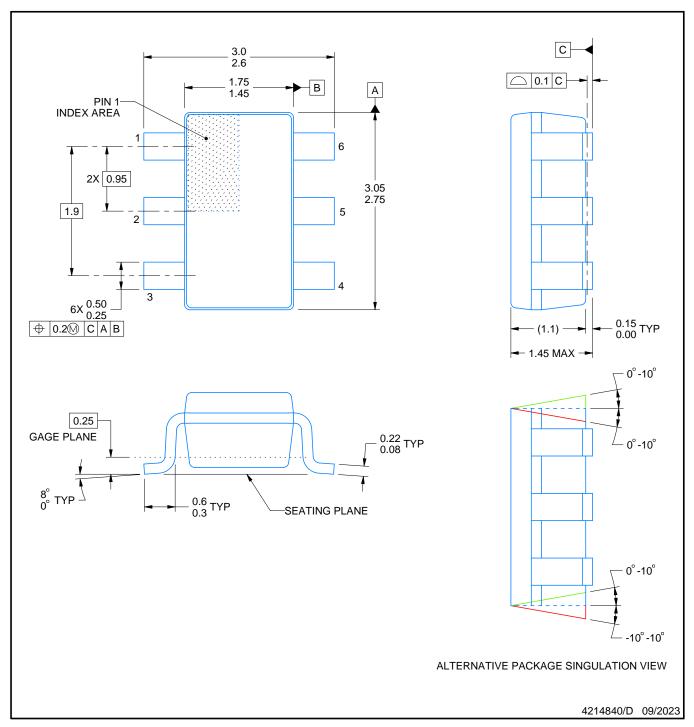

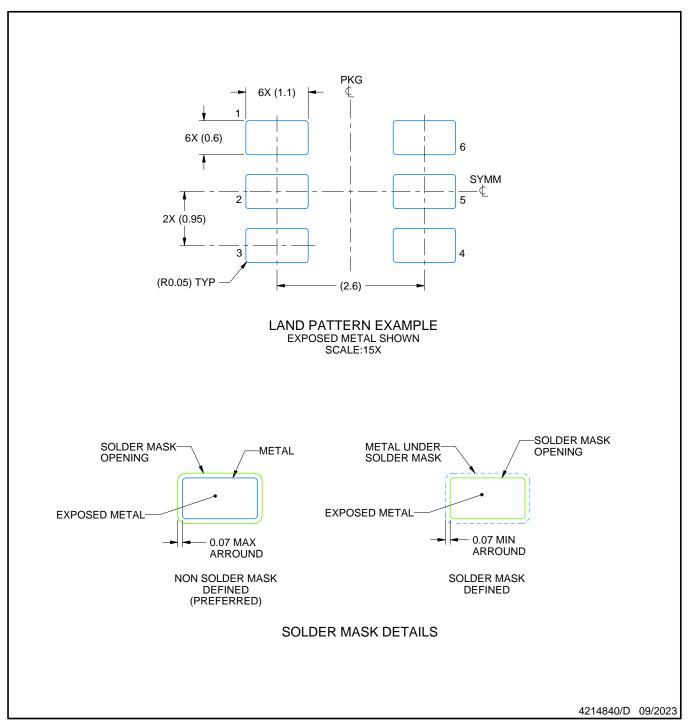

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE | BODY SIZE (NOM)   |

|-------------|---------|-------------------|

| TMAG5273    | DBV (6) | 2.90 mm × 1.60 mm |

For all available packages, see the package option addendum at the end of the data sheet.

# **Table of Contents**

| 1 Features1                                     | 7.3 Feature Description                              | .10  |

|-------------------------------------------------|------------------------------------------------------|------|

| 2 Applications1                                 | 7.4 Device Functional Modes                          | .15  |

| 3 Description1                                  | 7.5 Programming                                      | . 17 |

| 4 Revision History2                             | 7.6 Register Map                                     |      |

| 5 Pin Configuration and Functions3              | 8 Application and Implementation                     | . 36 |

| 6 Specifications4                               | 8.1 Application Information                          | 36   |

| 6.1 Absolute Maximum Ratings4                   | 8.2 Typical Application                              | 40   |

| 6.2 ESD Ratings 4                               | 8.3 What to Do and What Not to Do                    | 47   |

| 6.3 Recommended Operating Conditions4           | 9 Power Supply Recommendations                       | .48  |

| 6.4 Thermal Information4                        | 10 Layout                                            | .48  |

| 6.5 Electrical Characteristics5                 | 10.1 Layout Guidelines                               | . 48 |

| 6.6 Temperature Sensor6                         | 10.2 Layout Example                                  | . 48 |

| 6.7 Magnetic Characteristics For A16            | 11 Device and Documentation Support                  | .49  |

| 6.8 Magnetic Characteristics For A27            | 11.1 Documentation Support                           | 49   |

| 6.9 Magnetic Temp Compensation Characteristics8 | 11.2 Receiving Notification of Documentation Updates | . 49 |

| 6.10 I2C Interface Timing8                      | 11.3 Support Resources                               | 49   |

| 6.11 Power up & Conversion Time8                | 11.4 Trademarks                                      | .49  |

| 6.12 Typical Characteristics9                   | 11.5 Electrostatic Discharge Caution                 | .49  |

| 7 Detailed Description10                        | 11.6 Glossary                                        |      |

| 7.1 Overview10                                  | 12 Mechanical, Packaging, and Orderable              |      |

| 7.2 Functional Block Diagram10                  | Information                                          | . 49 |

|                                                 |                                                      |      |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | Changes from Revision * (June 2021) to Revision A (September 2021)     | Page                                   |

|---|------------------------------------------------------------------------|----------------------------------------|

| • | Changed data sheet status from Advanced Information to Production Data | ······································ |

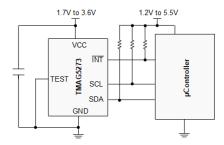

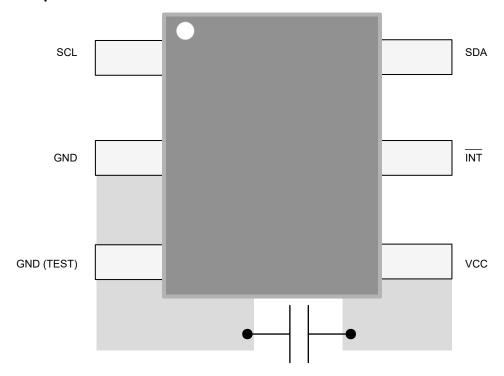

# **5 Pin Configuration and Functions**

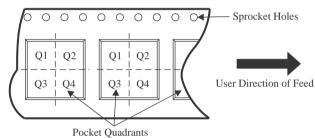

Figure 5-1. DBV Package, 6-Pin SOT-23 (Top View)

# **Table 5-1. Pin Functions**

| PIN        |     | TYPE         | DESCRIPTION                                                                       |  |  |

|------------|-----|--------------|-----------------------------------------------------------------------------------|--|--|

| NAME       | NO. | 1175         | DESCRIPTION                                                                       |  |  |

| SCL        | 1   | Ю            | Serial clock.                                                                     |  |  |

| GND        | 2   | Ground       | Ground reference.                                                                 |  |  |

| GND (TEST) | 3   | Input        | TI Test Pin. Connect to ground in application.                                    |  |  |

| VCC        | 4   | Power supply | Power supply.                                                                     |  |  |

| ĪNT        | 5   | Ю            | Interrupt input/ output. If not used and connected to ground, set MASK_INTB = 1b. |  |  |

| SDA        | 6   | Ю            | Serial data.                                                                      |  |  |

# **6 Specifications**

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                              | MIN  | MAX       | UNIT |

|------------------|------------------------------|------|-----------|------|

| V <sub>CC</sub>  | Main supply voltage          | -0.3 | 4         | V    |

| I <sub>OUT</sub> | Output current, SDA, INT     | 0    | 10        | mA   |

| V <sub>OUT</sub> | Output voltage, SDA, INT     | -0.3 | 7         | V    |

| V <sub>IN</sub>  | Input voltage, SCL, SDA, INT | -0.3 | 7         | V    |

| B <sub>MAX</sub> | Magnetic flux density        |      | Unlimited | Т    |

| TJ               | Junction temperature         | -40  | 150       | °C   |

| T <sub>stg</sub> | Storage temperature          | -65  | 170       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                     | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discrarge | Charged device model (CDM), per JEDEC specification JS-002, all pins <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted) over recommended  $V_{CC}$  range (unless otherwise noted)

|                                |                                   | MIN | NOM MAX | UNIT            |

|--------------------------------|-----------------------------------|-----|---------|-----------------|

| V <sub>CC</sub>                | Main supply voltage               | 1.7 | 3.6     | V               |

| V <sub>OUT</sub>               | Output voltage, SDA, INT          | 0   | 5.5     | V               |

| I <sub>OUT</sub>               | Output current, SDA, INT          |     | 2       | mA              |

| V <sub>IH</sub>                | Input HIGH voltage, SCL, SDA, ĪNT | 0.7 |         | V <sub>CC</sub> |

| V <sub>IL</sub>                | Input LOW voltage, SCL, SDA, INT  |     | 0.3     | V <sub>CC</sub> |

| $\Delta V_{CC}/\Delta t^{(1)}$ | Supply voltage ramp rate          | 3   |         | V/ms            |

| T <sub>A</sub>                 | Operating free air temperature    | -40 | 125     | °C              |

<sup>(1)</sup> If the VCC ramp rate is slower than the recommended supply voltage ramp rate, run a wake-up and sleep cycle after power-up or power-up reset to avoid I2C address glitch during sleep mode. This action is not required while operating in stand-by or continuous modes.

### 6.4 Thermal Information

|                       |                                            | TMAG5273     |      |

|-----------------------|--------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>              | DBV (SOT-23) | UNIT |

|                       |                                            | 6 PINS       |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance     | 162          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance  | 81.6         | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance       | 50.1         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter | 30.7         | °C/W |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

|             | THERMAL METRIC <sup>(1)</sup>                | TMAG5273     |      |

|-------------|----------------------------------------------|--------------|------|

|             | THERMAL METRIC(1)                            | DBV (SOT-23) | UNIT |

|             |                                              | 6 PINS       |      |

| $\Psi_{JB}$ | Junction-to-board characterization parameter | 49.8         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

over recommended V<sub>CC</sub> range (unless otherwise noted)

|                            | PARAMETER                                     | TEST CONDITIONS                                                                            | MIN | TYP  | MAX  | UNIT |

|----------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------|-----|------|------|------|

| SDA, ĪNT                   |                                               |                                                                                            |     |      |      |      |

| V <sub>OL</sub>            | Output LOW voltage, SDA, INT pin              | I <sub>OUT</sub> = 2mA                                                                     | 0   |      | 0.4  | V    |

| l <sub>oz</sub>            | Output leakage current, SDA, INT pin          | Output disabled, V <sub>OZ</sub> = 5.5V                                                    |     |      | ±100 | nA   |

| t <sub>FALL_ĪNT</sub>      | ĪNT output fall time                          | $R_{PU}$ =10K $\Omega$ , $C_L$ =20pF, $V_{PU}$ =1.65V to 5.5V                              |     | 6    |      | ns   |

| t <sub>INT (ĪNT)</sub>     | INT Interrupt time duration during pulse mode | INT_MODE =001b or 010b                                                                     |     | 10   |      | μs   |

| t <sub>INT (SCL)</sub>     | SCL Interrupt time duration                   | INT_MODE =011b or 100b                                                                     |     | 10   |      | μs   |

| DC POWER SEC               | CTION                                         |                                                                                            |     |      |      |      |

| VCC <sub>UV</sub> (1)      | Under voltage threshold at V <sub>CC</sub>    | V <sub>CC</sub> = 2.3V to 3.6V                                                             | 1.9 | 2.0  | 2.2  | V    |

| I <sub>ACTIVE</sub>        | Active mode current                           | X, Y, Z, or thermal sensor active conversion, LP_LN =0b                                    |     | 2.3  |      | mA   |

| I <sub>ACTIVE</sub>        | Active mode current                           | X, Y, Z, or thermal sensor active conversion, LP_LN =1b                                    |     | 3.0  |      | mA   |

| I <sub>STANDBY</sub>       | Stand-by mode current                         | Device in trigger mode, no conversion started                                              |     | 0.45 |      | mA   |

| I <sub>SLEEP</sub>         | Sleep mode current                            |                                                                                            |     | 5    |      | nA   |

| AVERAGE POW                | ER DURING WAKE-UP AND SLEEP (W                | S) MODE                                                                                    |     |      |      |      |

| I <sub>CC_DCM_1000_1</sub> | W&S mode current consumption                  | Wake-up interval 1-ms, magnetic 1-ch conversion, LP_LN =0b, V <sub>CC</sub> =3.3V          |     | 160  |      | μΑ   |

| I <sub>CC_DCM_1000_1</sub> | W&S mode current consumption                  | Wake-up interval 1-ms, magnetic 1-ch conversion, LP_LN =0b, V <sub>CC</sub> =1.8V          |     | 156  |      | μΑ   |

| I <sub>CC_DCM_1000_4</sub> | W&S mode current consumption                  | Wake-up interval 1-ms, 4-ch conversion, LP_LN =0b, V <sub>CC</sub> =3.3V                   |     | 240  |      | μΑ   |

| I <sub>CC_DCM_1000_4</sub> | W&S mode current consumption                  | Wake-up interval 1-ms, 4-ch conversion, LP_LN =0b, V <sub>CC</sub> =1.8V                   |     | 233  |      | μA   |

| I <sub>CC_DCM_0p2_1</sub>  | W&S mode current consumption                  | Wake-up interval 5000-ms,<br>magnetic 1-ch conversion, LP_LN =0b,<br>V <sub>CC</sub> =3.3V |     | 1.21 |      | μA   |

| ICC_DCM_0p2_1              | W&S mode current consumption                  | Wake-up interval 5000-ms,<br>magnetic 1-ch conversion, LP_LN =0b,<br>V <sub>CC</sub> =1.8V |     | 1.00 |      | μΑ   |

| I <sub>CC_DCM_0p2_4</sub>  | W&S mode current consumption                  | Wake-up interval 5000-ms, 4-ch conversion, LP_LN =0b, V <sub>CC</sub> =3.3V                |     | 1.22 |      | μΑ   |

| I <sub>CC_DCM_0p2_4</sub>  | W&S mode current consumption                  | Wake-up interval 5000-ms, 4-ch conversion, LP_LN =0b, V <sub>CC</sub> =1.8V                |     | 1.02 |      | μΑ   |

<sup>(1)</sup> The DIAG\_STATUS and VCC\_UV\_ER bits are not valid for  $V_{CC}$  < 2.3V

Copyright © 2023 Texas Instruments Incorporated

### **6.6 Temperature Sensor**

over operating free-air temperature range (unless otherwise noted)

over recommended V<sub>CC</sub> range (unless otherwise noted)

|                         | PARAMETER                                                                         | TEST CONDITIONS | MIN | TYP   | MAX                | UNIT   |

|-------------------------|-----------------------------------------------------------------------------------|-----------------|-----|-------|--------------------|--------|

| T <sub>SENS_RANGE</sub> | Temperature sensing range                                                         |                 | -40 |       | 170 <sup>(1)</sup> | °C     |

| T <sub>ADC_T0</sub>     | Temperature result in decimal value (from 16-bit format) for T <sub>SENS_T0</sub> |                 |     | 17508 |                    |        |

| T <sub>SENS_T0</sub>    | Reference temperature for T <sub>ADC_T0</sub>                                     |                 |     | 25    |                    | ℃      |

| T <sub>ADC_RES</sub>    | Temp sensing resolution (in 16-bit format)                                        |                 |     | 60.1  |                    | LSB/°C |

| NRMS_T                  | RMS (1 Sigma) temperature noise                                                   | CONV_AVG = 000b |     | 0.4   |                    | °C     |

| NRMS_T                  | RMS (1 Sigma) temperature noise                                                   | CONV_AVG = 101b |     | 0.2   |                    | °C     |

<sup>(1)</sup> TI recommends not to exceed the specified operating free air temperature per the Recommended Operating Conditions table

# 6.7 Magnetic Characteristics For A1

over operating free-air temperature range (unless otherwise noted)

|                               | PARAMETER                                   | TEST CONDITIONS                    | MIN TYP | MAX    | UNIT   |

|-------------------------------|---------------------------------------------|------------------------------------|---------|--------|--------|

| B <sub>IN_A1_X_Y</sub>        | Linear magnetic range                       | X_Y_RANGE =0b                      | ±40     |        | mT     |

| B <sub>IN_A1_X_Y</sub>        | Linear magnetic range                       | X_Y_RANGE =1b                      | ±80     |        | mT     |

| B <sub>IN_A1_Z</sub>          | Linear magnetic range                       | Z_RANGE =0b                        | ±40     |        | mT     |

| B <sub>IN_A1_Z</sub>          | Linear magnetic range                       | Z_RANGE =1b                        | ±80     |        | mT     |

| SENS <sub>40_A1</sub>         | Sensitivity, X, Y, or Z axis                | ±40 mT range                       | 820     |        | LSB/mT |

| SENS <sub>80_A1</sub>         | Sensitivity, X, Y, or Z axis                | ±80 mT range                       | 410     |        | LSB/mT |

| SENS <sub>ER_PC_25C_A1</sub>  | Sensitivity error, X, Y, Z axis             | TA =25C                            | ±5.0%   | ±20.0% |        |

| SENS <sub>ER_PC_TEMP_A1</sub> | Sensitivity drift from 25C, X, Y, Z axis    |                                    | ±5.0%   |        |        |

| SENS <sub>LER_XY_A1</sub>     | Sensitivity Linearity Error, X, Y-axis      | TA =25C                            | ±0.10%  |        |        |

| SENS <sub>LER_Z_A1</sub>      | Sensitivity Linearity Error, Z axis         | TA =25C                            | ±0.10%  |        |        |

| SENS <sub>MS_XY_A1</sub>      | Sensitivity mismatch among X-Y axes         | TA =25C                            | ±0.50%  |        |        |

| SENS <sub>MS_Z_A1</sub>       | Sensitivity mismatch among Y-Z, or X-Z axes | TA =25C                            | ±1.0%   |        |        |

| SENS <sub>MS_DR_XY_A1</sub>   | Sensitivity mismatch drift X-Y axes         |                                    | ±5%     |        |        |

| SENS <sub>MS_DR_Z_A1</sub>    | Sensitivity mismatch drift Y-Z, or X-Z axes |                                    | ±15%    |        |        |

| B <sub>off_A1</sub>           | Offset                                      | TA =25C                            | ±300    | ±1000  | μT     |

| B <sub>off_TC_A1</sub>        | Offset drift                                |                                    | ±3.0    | ±10.0  | μT/°C  |

| N <sub>RMS_XY_00_000_A1</sub> | RMS (1 Sigma) magnetic noise (X or Y-axis)  | LP_LN =0b, CONV_AVG = 000, TA =25C | 125     |        | μТ     |

| N <sub>RMS_XY_01_000_A1</sub> | RMS (1 Sigma) magnetic noise (X or Y-axis)  | LP_LN =1b, CONV_AVG = 000, TA =25C | 110     |        | μΤ     |

| N <sub>RMS_XY_00_101_A1</sub> | RMS (1 Sigma) magnetic noise (X or Y-axis)  | LP_LN =0b, CONV_AVG = 101, TA =25C | 22      |        | μТ     |

| N <sub>RMS_XY_01_101_A1</sub> | RMS (1 Sigma) magnetic noise (X or Y-axis)  | LP_LN =1b, CONV_AVG = 101, TA =25C | 22      |        | μТ     |

| N <sub>RMS_Z_00_000_A1</sub>  | RMS (1 Sigma) magnetic noise (Z axis)       | LP_LN =0b, CONV_AVG = 000, TA =25C | 68      |        | μТ     |

| N <sub>RMS_Z_01_000_A1</sub>  | RMS (1 Sigma) magnetic noise (Z axis)       | LP_LN =1b, CONV_AVG = 000, TA =25C | 66      |        | μТ     |

| N <sub>RMS_Z_00_101_A1</sub>  | RMS (1 Sigma) magnetic noise (Z axis)       | LP_LN =0b, CONV_AVG = 101, TA =25C | 11      |        | μТ     |

| N <sub>RMS_Z_01_101_A1</sub>  | RMS (1 Sigma) magnetic noise (Z axis)       | LP_LN =1b, CONV_AVG = 101, TA =25C | 9       |        | μТ     |

over operating free-air temperature range (unless otherwise noted)

| P                              | ARAMETER                                    | TEST CONDITIONS         | MIN T | YP MAX | UNIT   |

|--------------------------------|---------------------------------------------|-------------------------|-------|--------|--------|

| A <sub>ERR_Y_Z_101_A1_25</sub> | Y-Z Angle error in full 360 degree rotation | CONV_AVG = 101, TA =25C | ±     | 1.0    | Degree |

| A <sub>ERR_X_Z_101_A1_25</sub> | X-Z Angle error in full 360 degree rotation | CONV_AVG = 101, TA =25C | ±     | 1.0    | Degree |

| A <sub>ERR_X_Y_101_A1_25</sub> | X-Y Angle error in full 360 degree rotation | CONV_AVG = 101, TA =25C | ±     | ).5    | Degree |

# **6.8 Magnetic Characteristics For A2**

over operating free-air temperature range (unless otherwise noted)

|                                                                        | PARAMETER                                                      | TEST CONDITIONS                    | MIN TYP | MAX    | UNIT   |

|------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------|---------|--------|--------|

| B <sub>IN_A2_X_Y</sub>                                                 | Linear magnetic range                                          | X_Y_RANGE =0b                      | ±133    |        | mT     |

| B <sub>IN_A2_X_Y</sub>                                                 | Linear magnetic range                                          | X_Y_RANGE =1b                      | ±266    |        | mT     |

| B <sub>IN_A2_Z</sub>                                                   | N_A2_Z Linear magnetic range                                   |                                    | ±133    |        | mT     |

| B <sub>IN_A2_Z</sub>                                                   | Linear magnetic range                                          | Z_RANGE =1b                        | ±266    |        | mT     |

| SENS <sub>133_A2</sub>                                                 | Sensitivity, X, Y, or Z axis                                   | ±133 mT range                      | 250     |        | LSB/mT |

| SENS <sub>266_A2</sub>                                                 | Sensitivity, X, Y, or Z axis                                   | ±266 mT range                      | 125     |        | LSB/mT |

| SENS <sub>ER_PC_25C_A2</sub>                                           | Sensitivity error, X, Y, Z axis                                | TA = 25C                           | ±5.0%   | ±20.0% |        |

| SENS <sub>ER_PC_TEMP_A2</sub>                                          | Sensitivity drift from 25C, X, Y, Z axis                       |                                    | ±5.0%   |        |        |

| SENS <sub>LER_XY_A2</sub>                                              | Sensitivity Linearity Error, X, Y-axis                         | TA =25C                            | ±0.10%  |        |        |

| SENS <sub>LER_Z_A2</sub>                                               | Sensitivity Linearity Error, Z axis                            | TA =25C                            | ±0.10%  |        |        |

| SENS <sub>MS_XY_A2</sub>                                               | Sensitivity mismatch among X-Y axes                            | TA =25C                            | ±0.50%  |        |        |

| SENS <sub>MS_Z_A2</sub>                                                | Sonsitivity mismatch among V.7. or V                           |                                    | ±1.0%   |        |        |

| SENS <sub>MS_DR_XY_A2</sub>                                            | ENS <sub>MS_DR_XY_A2</sub> Sensitivity mismatch drift X-Y axes |                                    | ±5%     |        |        |

| SENS <sub>MS_DR_Z_A2</sub> Sensitivity mismatch drift Y-Z, or X-Z axes |                                                                |                                    | ±15%    |        |        |

| B <sub>off_A2</sub>                                                    | Offset                                                         | TA =25C                            | ±300    | ±1000  | μΤ     |

| B <sub>off_TC_A2</sub>                                                 | Offset drift                                                   |                                    | ±3.0    | ±10    | μT/°C  |

| N <sub>RMS_XY_00_000_A2</sub>                                          | RMS (1 Sigma) magnetic noise (X or Y-axis)                     | LP_LN =0b, CONV_AVG = 000, TA =25C | 147     |        | μΤ     |

| N <sub>RMS_XY_01_000_A2</sub>                                          | RMS (1 Sigma) magnetic noise (X or Y-axis)                     | LP_LN =1b, CONV_AVG = 000, TA =25C | 145     |        | μΤ     |

| N <sub>RMS_XY_01_101_A2</sub>                                          | RMS (1 Sigma) magnetic noise (X or Y-axis)                     | LP_LN =0b, CONV_AVG = 101, TA =25C | 24      |        | μΤ     |

| N <sub>RMS_XY_10_101_A2</sub>                                          | RMS (1 Sigma) magnetic noise (X or Y-axis)                     | LP_LN =1b, CONV_AVG = 101, TA =25C | 24      |        | μΤ     |

| N <sub>RMS_Z_00_000_A2</sub>                                           | RMS (1 Sigma) magnetic noise (Z axis)                          | LP_LN =0b, CONV_AVG = 000, TA =25C | 89      |        | μΤ     |

| N <sub>RMS_Z_10_000_A2</sub>                                           | RMS (1 Sigma) magnetic noise (Z axis)                          | LP_LN =1b, CONV_AVG = 000, TA =25C | 88      |        | μΤ     |

| N <sub>RMS_Z_00_101_A2</sub>                                           | RMS (1 Sigma) magnetic noise (Z axis)                          | LP_LN =0b, CONV_AVG = 101, TA =25C | 15      |        | μΤ     |

| N <sub>RMS_Z_10_101_A2</sub>                                           | RMS (1 Sigma) magnetic noise (Z axis)                          | LP_LN =1b, CONV_AVG = 101, TA =25C | 15      |        | μΤ     |

| A <sub>ERR_Y_Z_101_A2</sub>                                            | Y-Z Angle error in full 360 degree rotation                    | CONV_AVG = 101, TA =25C            | ±1.0    |        | Degree |

| A <sub>ERR_X_Z_101_A2</sub>                                            | X-Z Angle error in full 360 degree rotation                    | CONV_AVG = 101, TA =25C            | ±1.0    |        | Degree |

over operating free-air temperature range (unless otherwise noted)

| P                           | ARAMETER                                    | TEST CONDITIONS         | MIN | TYP   | MAX | UNIT   |

|-----------------------------|---------------------------------------------|-------------------------|-----|-------|-----|--------|

| A <sub>ERR_X_Y_101_A2</sub> | X-Y Angle error in full 360 degree rotation | CONV_AVG = 101, TA =25C |     | ±0.50 |     | Degree |

# **6.9 Magnetic Temp Compensation Characteristics**

over operating free-air temperature range (unless otherwise noted)

|       | PARAMETER                               | TEST CONDITIONS | MIN | TYP  | MAX | UNIT |

|-------|-----------------------------------------|-----------------|-----|------|-----|------|

| TC_00 | Temperature compensation (X, Y, Z-axes) | MAG_TEMPCO =00b |     | 0    |     | %/°C |

| TC_12 | Temperature compensation (X, Y, Z-axes) | MAG_TEMPCO =01b |     | 0.12 |     | %/°C |

| TC_20 | Temperature compensation (X, Y, Z-axes) | MAG_TEMPCO =11b |     | 0.2  |     | %/°C |

# 6.10 I2C Interface Timing

over operating free-air temperature range (unless otherwise noted)

|                          | PARAMETER                                      | TEST CONDITIONS                                | MIN  | TYP | MAX  | UNIT |

|--------------------------|------------------------------------------------|------------------------------------------------|------|-----|------|------|

| I2C Interface            | Fast Mode Plus (V <sub>CC</sub> =2.3V to 3.6V) |                                                |      |     |      |      |

| f <sub>I2C_fmp</sub>     | I2C clock (SCL) frequency                      | LOAD = 50 pF, V <sub>CC</sub><br>=2.3V to 3.6V |      |     | 1000 | KHz  |

| t <sub>whigh_fmp</sub>   | High time: SCL logic high time duration        |                                                | 350  |     |      | ns   |

| t <sub>wlo_wfmp</sub>    | Low time: SCL logic low time duration          |                                                | 500  |     |      | ns   |

| t <sub>su_cs_fmp</sub>   | SDA data setup time                            |                                                | 50   |     |      | ns   |

| t <sub>h_cs_fmp</sub>    | SDA data hold time                             |                                                | 120  |     |      | ns   |

| t <sub>icr_fmp</sub>     | SDA, SCL input rise time                       |                                                |      |     | 120  | ns   |

| t <sub>icf_fmp</sub>     | SDA, SCL input fall time                       |                                                |      |     | 55   | ns   |

| t <sub>h_ST_fmp</sub>    | Start condition hold time                      |                                                | 0.1  |     |      | μs   |

| t <sub>su_SR_fmp</sub>   | Repeated start condition setup time            |                                                | 0.1  |     |      | μs   |

| t <sub>su_SP_fmp</sub>   | Stop condition setup time                      |                                                | 0.1  |     |      | μs   |

| t <sub>w_SP_SR_fmp</sub> | Bus free time between stop and start condition |                                                | 0.2  |     |      | μs   |

| I2C Interface            | Fast Mode (V <sub>CC</sub> =1.7V to 3.6V)      | 1                                              |      |     |      |      |

| f <sub>I2C</sub>         | I2C clock (SCL) frequency                      | LOAD = 50 pF, V <sub>CC</sub><br>=1.7V to 3.6V |      |     | 400  | KHz  |

| t <sub>whigh</sub>       | High time: SCL logic high time duration        |                                                | 600  |     |      | ns   |

| t <sub>wlow</sub>        | Low time: SCL logic low time duration          |                                                | 1300 |     |      | ns   |

| t <sub>su_cs</sub>       | SDA data setup time                            |                                                | 100  |     |      | ns   |

| t <sub>h_cs</sub>        | SDA data hold time                             |                                                | 0    |     |      | ns   |

| t <sub>icr</sub>         | SDA, SCL input rise time                       |                                                |      |     | 300  | ns   |

| t <sub>icf</sub>         | SDA, SCL input fall time                       |                                                |      |     | 300  | ns   |

| t <sub>h_ST</sub>        | Start condition hold time                      |                                                | 0.3  |     |      | μs   |

| t <sub>su_SR</sub>       | Repeated start condition setup time            |                                                | 0.3  |     |      | μs   |

| t <sub>su_SP</sub>       | Stop condition setup time                      |                                                | 0.3  |     |      | μs   |

| t <sub>w_SP_SR</sub>     | Bus free time between stop and start condition |                                                | 0.6  | -   |      | μs   |

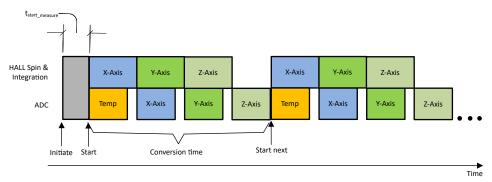

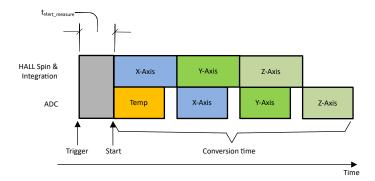

# 6.11 Power up & Conversion Time

over operating free-air temperature range (unless otherwise noted)

|                             | PARAMETER                                                                        | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------------------|----------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| t <sub>start_power_up</sub> | Time to go to stand-by mode after $V_{CC}$ supply voltage crossing $V_{CC\_MIN}$ |                 |     | 270 |     | μs   |

| t <sub>start_sleep</sub>    | Time to go to stand-by mode from sleep mode <sup>(1)</sup>                       |                 |     | 50  |     | μs   |

www.ti.com

over operating free-air temperature range (unless otherwise noted)

|                            | PARAMETER                                                  | TEST CONDITIONS                                                      | MIN | TYP | MAX | UNIT |

|----------------------------|------------------------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>start_measure</sub> | Time to go into continuous measure mode from stand-by mode |                                                                      |     | 70  |     | μs   |

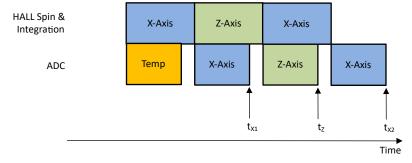

| t <sub>measure</sub>       | Conversion time <sup>(2)</sup>                             | CONV_AVG = 000b,<br>OPERATING_MODE =10b,<br>only one channel enabled |     | 50  |     | μs   |

| t <sub>measure</sub>       | Conversion time <sup>(3)</sup>                             | CONV_AVG = 101b,<br>OPERATING_MODE =10b,<br>only one channel enabled |     | 825 |     | μs   |

| t <sub>go_sleep</sub>      | Time to go into sleep mode after SCL goes high             |                                                                      |     | 20  |     | μs   |

- (1) The device will recognize the I2C communication from a primary only during stand-by or continuous measure modes. While the device is in sleep mode, a valid secondary address will wake up the device but no acknowledge will be sent to the primary. Start up time must be considered before addressing the device after wake up.

- (2) Add 25µs for each additional magnetic channel enabled for conversion with CONV\_AVG = 000b. When CONV\_AVG = 000b, the conversion time doesn't change with the T\_CH\_EN bit setting.

- (3) For conversion with CONV\_AVG =101b, each channel data is collected 32 times. If an additional channel is enabled with CONV\_AVG =101b, add 32×25μs = 800μs to the t<sub>measure</sub> to calculate the conversion time for two channels.

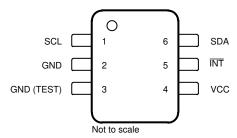

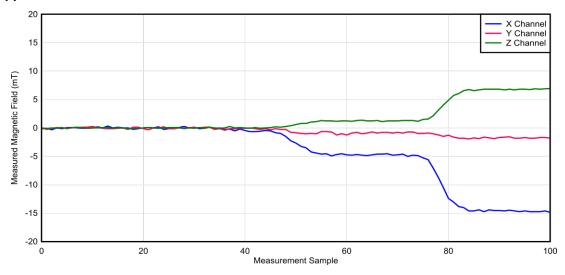

# **6.12 Typical Characteristics**

at  $T_A = 25^{\circ}$ C typical (unless otherwise noted)

# 7 Detailed Description

### 7.1 Overview

The TMAG5273 IC is based on the Hall-effect technology and precision mixed signal circuitry from Texas Instruments. The output signals (raw X, Y, Z magnetic data and temperature data) are accessible through the I<sup>2</sup>C interface.

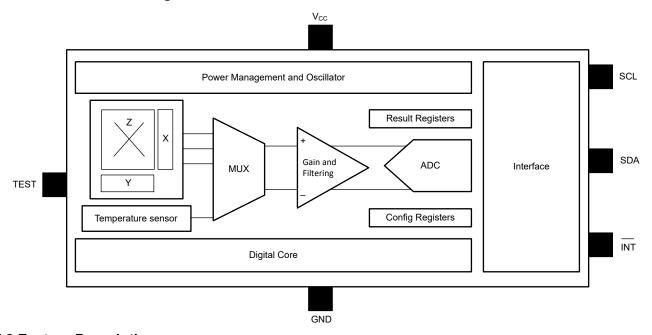

The IC consists of the following functional and building blocks:

- The Power Management & Oscillator block contains a low-power oscillator, biasing circuitry, undervoltage detection circuitry, and a fast oscillator.

- The sensing and temperature measurement block contains the Hall biasing, Hall sensors with multiplexers, noise filters, integrator circuit, temperature sensor, and the ADC. The Hall-effect sensor data and temperature data are multiplexed through the same ADC.

- The Interface block contains the I<sup>2</sup>C control circuitry, ESD protection circuits, and all the I/O circuits. The TMAG5273 supports multiple I<sup>2</sup>C read frames along with integrated cyclic redundancy check (CRC).

# 7.2 Functional Block Diagram

## 7.3 Feature Description

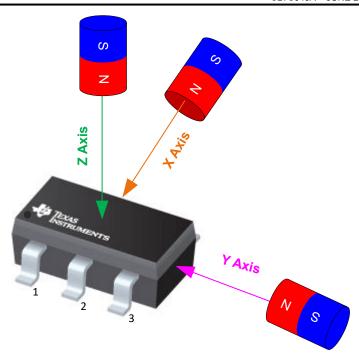

## 7.3.1 Magnetic Flux Direction

As shown in Figure 7-1, the TMAG5273 will generate positive ADC codes in response to a magnetic north pole in the proximity. Similarly, the TMAG5273 will generate negative ADC codes if magnetic south poles approach from the same directions.

Figure 7-1. Direction of Sensitivity

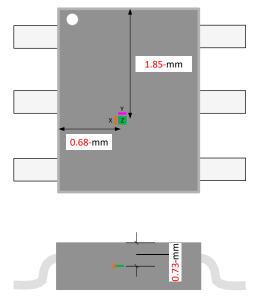

### 7.3.2 Sensor Location

Figure 7-2 shows the location of X, Y, Z hall elements inside the TMAG5273.

Figure 7-2. Location of X, Y, Z Hall Elements

# 7.3.3 Interrupt Function

The TMAG5273 supports flexible and configurable interrupt functions through either the  $\overline{\text{INT}}$  or the SCL pin. Table 7-1 shows different conversion completion events where result registers and SET\_COUNT bits update, and where they do not.

Copyright © 2023 Texas Instruments Incorporated

| Table 7-1. Result Register & SET_COUNT Update After Conversion Completion | Table 7-1 | . Result Registe | r & SET | COUNT U | Jpdate After | Conversion | Completion |

|---------------------------------------------------------------------------|-----------|------------------|---------|---------|--------------|------------|------------|

|---------------------------------------------------------------------------|-----------|------------------|---------|---------|--------------|------------|------------|

| INT_MODE | MODE                                                             | I <sup>2</sup> C BUS BUSY,<br>TO DEVICE | NOT TALKING          | I <sup>2</sup> C BUS BUSY & TALKING TO DEVICE |                   | I <sup>2</sup> C BUS NOT BUSY |                   |  |

|----------|------------------------------------------------------------------|-----------------------------------------|----------------------|-----------------------------------------------|-------------------|-------------------------------|-------------------|--|

| INT_MODE | DESCRIPTION                                                      | RESULT<br>UPDATE?                       | SET_COUNT<br>UPDATE? | RESULT<br>UPDATE?                             | SET_COUNT UPDATE? | RESULT<br>UPDATE?             | SET_COUNT UPDATE? |  |

| 000b     | No interrupt                                                     | Yes                                     | Yes                  | No                                            | No                | Yes                           | Yes               |  |

| 001b     | Interrupt<br>through INT                                         | Yes                                     | Yes                  | No                                            | No                | Yes                           | Yes               |  |

| 010b     | Interrupt<br>through INT<br>except when<br>I <sup>2</sup> C busy | Yes                                     | Yes                  | No                                            | No                | Yes                           | Yes               |  |

| 011b     | Interrupt<br>through SCL                                         | Yes                                     | Yes                  | No                                            | No                | Yes                           | Yes               |  |

| 100b     | Interrupt<br>through SCL<br>except when<br>I <sup>2</sup> C busy | No                                      | No                   | No                                            | No                | Yes                           | Yes               |  |

### Note

TI does not recommend sharing the same I2C bus with multiple secondary devices when using the SCL pin for interrupt function. The SCL interrupt may corrupt transactions with other secondary devices if present in the same I2C bus.

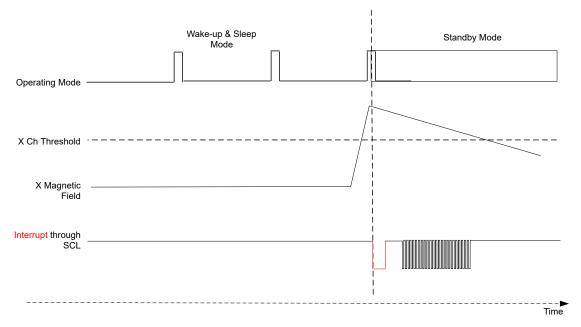

# **Interrupt Through SCL**

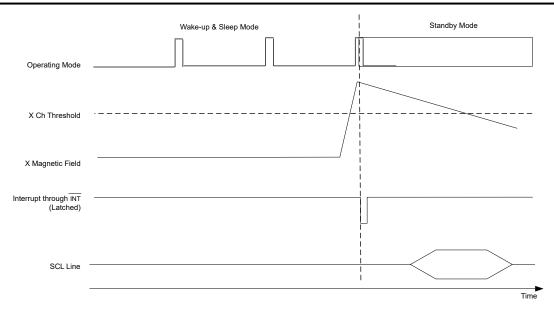

Figure 7-3 shows an example for interrupt function through the SCL pin with the device programmed to wake up and sleep mode for threshold cross at a predefined intervals. The wake-up intervals can be set through the SLEEPTIME bits. Once the magnetic threshold cross is detected, the device asserts a fixed width interrupt signal through the SCL pin, and goes back to stand-by mode.

Figure 7-3. Interrupt Through SCL

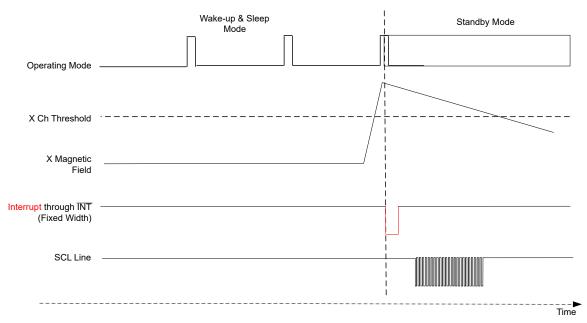

# Fixed Width Interrupt Through INT

Figure 7-4 shows an example for fixed-width interrupt function through the  $\overline{\text{INT}}$  pin. The device is programmed to be in wake-up and sleep mode to detect a magnetic threshold. The INT\_STATE register bit is set 1b. Once the magnetic threshold cross is detected, the device asserts a fixed width interrupt signal through the  $\overline{\text{INT}}$  pin, and goes back to stand-by mode.

Figure 7-4. Fixed Width Interrupt Through INT

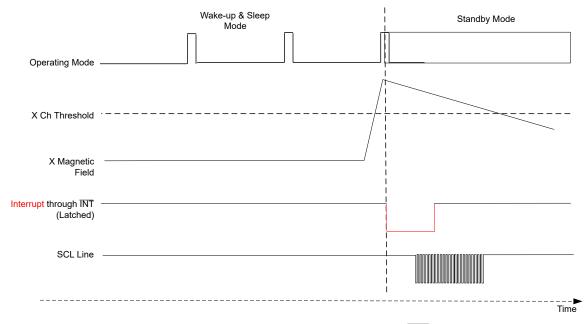

### Latched Interrupt Through INT

Figure 7-5 shows an example for latched interrupt function through the  $\overline{\text{INT}}$  pin. The device is programmed to be in wake-up and sleep mode to detect a magnetic threshold. The INT\_STATE register bit is set 0b. Once the magnetic threshold cross is detected, the device asserts a latched interrupt signal through the  $\overline{\text{INT}}$  pin, and goes back to stand-by mode. The interrupt latch is cleared only after the device receives a valid address through the SCL line.

Figure 7-5. Latched Interrupt Through INT

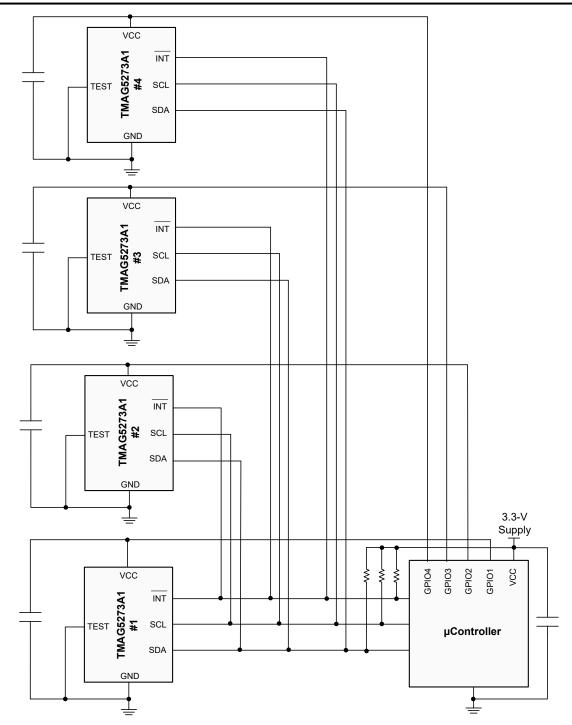

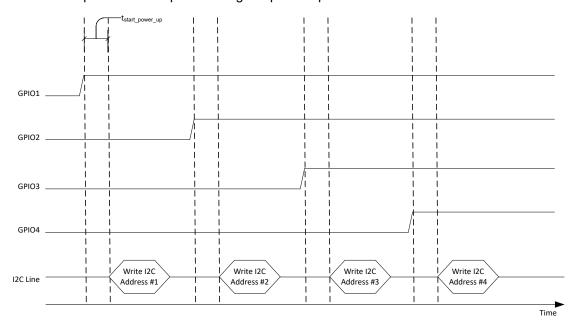

### 7.3.4 Device I<sup>2</sup>C Address

Table 7-2 shows the default factory programmed  $I^2C$  addresses of the TMAG5273. The device needs to be addressed with the factory default  $I^2C$  address after power up. If required, a primary can assign a new  $I^2C$  address through the  $I^2C$ \_ADDRESS register bits after power up.

I<sup>2</sup>C READ ADDRESS (8-**MAGNETIC DEVICE VERSION** I<sup>2</sup>C ADDRESS (7 MSB BITS) | I<sup>2</sup>C WRITE ADDRESS (8-BIT) **RANGE** BIT) TMAG5273A1 35h 6Ah 6Bh TMAG5273B1 22h 44h 45h ±40 mT, ±80 mT TMAG5273C1 78h F0h F1h TMAG5273D1 44h 88h 89h TMAG5273A2 35h 6Ah 6Bh TMAG5273B2 22h 44h 45h ±133 mT, ±266 mT TMAG5273C2 78h F0h F1h TMAG5273D2 44h 88h 89h

Table 7-2. I<sup>2</sup>C Default Address

# 7.3.5 Magnetic Range Selection

Table 7-3 shows the magnetic range selection for the TMAG5273 device. The X, Y, and Z axes range can be selected with the X\_Y\_RANGE and Z\_RANGE register bits.

**Table 7-3. Magnetic Range Selection**

|                 | RANGE REGISTER SETTING | TMAG5273A1 | TMAG5273A2 | COMMENT                |

|-----------------|------------------------|------------|------------|------------------------|

| X. Y Axis Field | X_Y_RANGE = 0b         | ±40-mT     | ±133-mT    |                        |

| X, Y AXIS FIEID | X_Y_RANGE = 1b         | ±80-mT     | ±266-mT    | Better SNR performance |

| 7 Avis Field    | Z_RANGE = 0b           | ±40-mT     | ±133-mT    |                        |

| Z Axis Field    | Z_RANGE = 1b           | ±80-mT     | ±266-mT    | Better SNR performance |

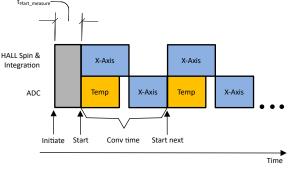

## 7.3.6 Update Rate Settings

The TMAG5273 offers multiple update rates to offer design flexibility to system designers. The different update rates can be selected with the CONV\_AVG register bits. Table 7-4 shows different update rate settings for the TMAG5273.

**Table 7-4. Update Rate Settings**

|              |                  | Table : opast       | · · · · · · · · · · · · · · · · · · · |            |                     |

|--------------|------------------|---------------------|---------------------------------------|------------|---------------------|

| OPERATING    | REGISTER SETTING | SETTING UPDATE RATE |                                       | COMMENT    |                     |

| MODE         | REGISTER SETTING | SINGLE AXIS         | TWO AXES                              | THREE AXES | COMINIENT           |

| X, Y, Z Axis | CONV_AVG = 000b  | 20.0-kSPS           | 13.3-kSPS                             | 10.0-kSPS  | Fastest update rate |

| X, Y, Z Axis | CONV_AVG = 001b  | 13.3-kSPS           | 8.0-kSPS                              | 5.7-kSPS   |                     |

| X, Y, Z Axis | CONV_AVG = 010b  | 8.0-kSPS            | 4.4-kSPS                              | 3.1-kSPS   |                     |

| X, Y, Z Axis | CONV_AVG = 011b  | 4.4-kSPS            | 2.4-kSPS                              | 1.6-kSPS   |                     |

| X, Y, Z Axis | CONV_AVG = 100b  | 2.4-kSPS            | 1.2-kSPS                              | 0.8-kSPS   |                     |

| X, Y, Z Axis | CONV_AVG = 101b  | 1.2-kSPS            | 0.6-kSPS                              | 0.4-kSPS   | Best SNR case       |

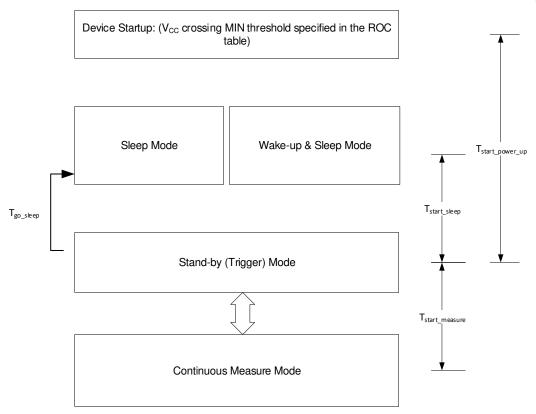

### 7.4 Device Functional Modes

The TMAG5273 supports multiple functional modes for wide array of applications as explained in Figure 7-6. A specific functional mode is selected by setting the corresponding value in the OPERATING\_MODE register bits. The device starts powering up after VCC supply crosses the minimum threshold as specified in the Recommended Operating Condition (ROC) table.

### 7.4.1 Stand-by (Trigger) Mode

The TMAG5273 goes to stand-by mode after first time powering up. At this mode the digital circuitry and oscillators are on, and the device is ready to accept commands from the primary device. Based off the commands the device can start a sensor data conversion, go to power saving mode, or start data transfer through  $I^2C$  interface. A new conversion can be triggered through  $I^2C$  command or through  $\overline{INT}$  pin. In this mode the device retains the immediate past conversion result data in the corresponding result registers. The time it takes for the device to go to stand-by mode from power up is denoted by  $T_{\text{start\_power\_up}}$ .

### 7.4.2 Sleep Mode

The TMAG5273 supports an ultra-low power sleep mode where it retains the critical user configuration settings. In this mode the device doesn't retain the conversion result data. A primary can wake up the device from sleep mode through  $I^2C$  communications or the  $\overline{INT}$  pin. The time it takes for the device to go to stand-by mode from sleep mode is denoted by  $T_{\text{start sleep}}$ .

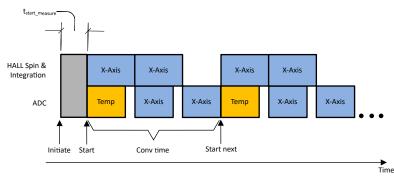

### 7.4.3 Wake-up and Sleep (W&S) Mode

In this mode the TMAG5273 can be configured to go to sleep and wake up at a certain interval, and measure sensor data based off the SLEEPTIME register bits setting. The device can be set to generate an interrupt through the INT\_CONFIG\_1 register. Once the conversion is complete and the interrupt condition is met, the TMAG5273 will exit the W&S mode and go to the stand-by mode. The last measured data will be stored in the

corresponding result registers before the device goes to the stand-by mode. If the interrupt condition isn't met, the device will continue to be in the W&S mode to wake up and measure data at the specified interval. A primary can wake up the TMAG5273 anytime during the W&S mode through  $I^2C$  bus or  $\overline{INT}$  pin. The time it takes for the device to go to stand-by mode from W&S mode is denoted by  $T_{\text{start sleep}}$ .

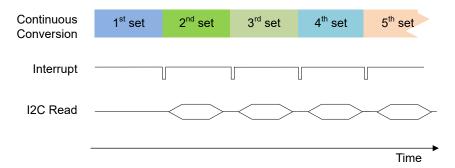

### 7.4.4 Continuous Measure Mode

In this mode the TMAG5273 continuously measures the sensor data per SENSOR\_CONFIG & DEVICE\_CONFIG register settings. In this mode the result registers can be accessed through the I2C lines. The time it takes for the device to go from stand-by mode to continuous measure mode is denoted by  $T_{\text{start measure}}$ .

Figure 7-6. TMAG5273 Power-Up Sequence

Table 7-5 shows different device operational modes of the TMAG5273.

Table 7-5. Operating Modes

| OPERATING<br>MODE          | DEVICE FUNCTION                                                                    | ACCESS<br>TO USER<br>REGISTERS | RETAIN USER CONFIGURATION | COMMENT                                                                                                                           |

|----------------------------|------------------------------------------------------------------------------------|--------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Continuous<br>Measure Mode | Continuously measuring x, y, z axis, or temperature data                           | Yes                            | Yes                       |                                                                                                                                   |

| Stand-by Mode              | Device is ready to accept I <sup>2</sup> C commands and start active conversion    | Yes                            | Yes                       |                                                                                                                                   |

| Wake-up and<br>Sleep Mode  | Wakes up at a certain interval to measure the x, y, z axis, or temperature data    | No                             | Yes                       | 1, 5, 10, 15, 20, 30, 50, 100, 500, 1000, 2000, 5000, & 20000-ms intervals supported.                                             |

| Sleep Mode                 | Device retains key configuration settings, but doesn't retain the measurement data | No                             | Yes                       | Sleep mode can be utilized by a primary device to implement other power saving intervals not supported by wake-up and sleep mode. |

# 7.5 Programming

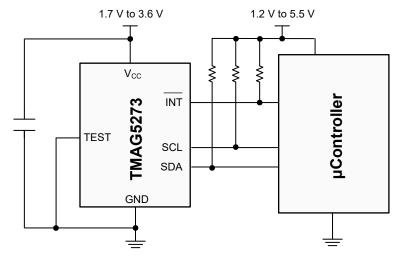

# 7.5.1 I<sup>2</sup>C Interface

The TMAG5273 offers I<sup>2</sup>C interface, a two-wire interface to connect low-speed devices like microcontrollers, A/D and D/A converters, I/O interfaces and other similar peripherals in embedded systems.

### 7.5.1.1 SCL

SCL is the clock line. It is used to synchronize all data transfers over the I<sup>2</sup>C bus.

### 7.5.1.2 SDA

SDA is the bidirectional data line for the I<sup>2</sup>C interface.

### 7.5.1.3 I<sup>2</sup>C Read/Write

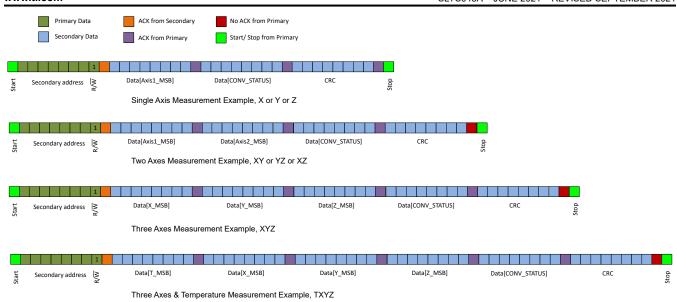

The TMAG5273 supports multiple I<sup>2</sup>C read and write frames targeting different applications. I2C\_RD and CRC\_EN bits offers multiple read frames to optimize the read time, data resolution and data integrity for a select application.

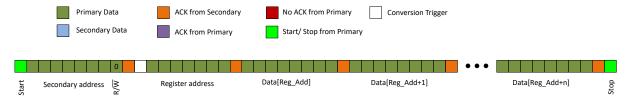

### 7.5.1.3.1 Standard I<sup>2</sup>C Write

Figure 7-7 shows an example of standard I<sup>2</sup>C two byte write command supported by TMAG5273. The starting byte contains 7-bit secondary device address and a '0' at the R/W command bit. The MSB of the second byte contains the conversion trigger bit. Writing '1' at this trigger bit will start a new conversion after the register address decoding is completed. The 7 LSB bits of the second byte contains the starting register address for the write command. After the two command bytes, the primary device starts to send the data to be written at the corresponding register address. Each successive write byte will send the data for the successive register address in the secondary device.

Figure 7-7. Standard I<sup>2</sup>C Write

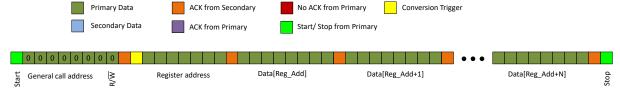

#### 7.5.1.3.2 General Call Write

Figure 7-8 shows an example of the general call I<sup>2</sup>C write command supported by the TMAG5273. This command is useful to configure multiple I<sup>2</sup>C devices in a I<sup>2</sup>C bus simultaneously. The starting byte contains 8-bit '0's. The MSB of the second byte contains the conversion trigger bit. Writing '1' at this trigger bit will start a new conversion after the register address decoding is completed. The 7 LSB bits of the second byte contains the starting register address for the write command. After the two command bytes, the primary device starts to send the data to be written at the corresponding register address of all the secondary devices in the I<sup>2</sup>C bus. Each successive write byte will send the data for the successive register address in the secondary devices.

Figure 7-8. General Call I<sup>2</sup>C Write

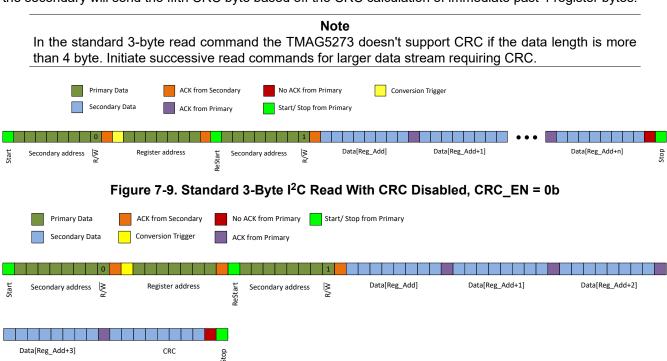

# 7.5.1.3.3 Standard 3-Byte I<sup>2</sup>C Read

Figure 7-9 and Figure 7-10 show examples of standard  $I^2C$  three byte read command supported by the TMAG5273. The starting byte contains 7-bit secondary device address and the  $R/\overline{W}$  command bit '0'. The MSB of the second byte contains the conversion trigger command bit. Writing '1' at this trigger bit will start a

new conversion after the register address decoding is completed. The 7 LSB bits of the second byte contains the starting register address for the write command. After receiving ACK signal from secondary, the primary send the secondary address once again with R/W command bit as '1'. The secondary starts to send the corresponding register data. It will send successive register data with each successive ACK from primary. If CRC is enabled, the secondary will send the fifth CRC byte based off the CRC calculation of immediate past 4 register bytes.

Figure 7-10. Standard 3-Byte I<sup>2</sup>C Read With CRC Enabled, CRC\_EN = 1b

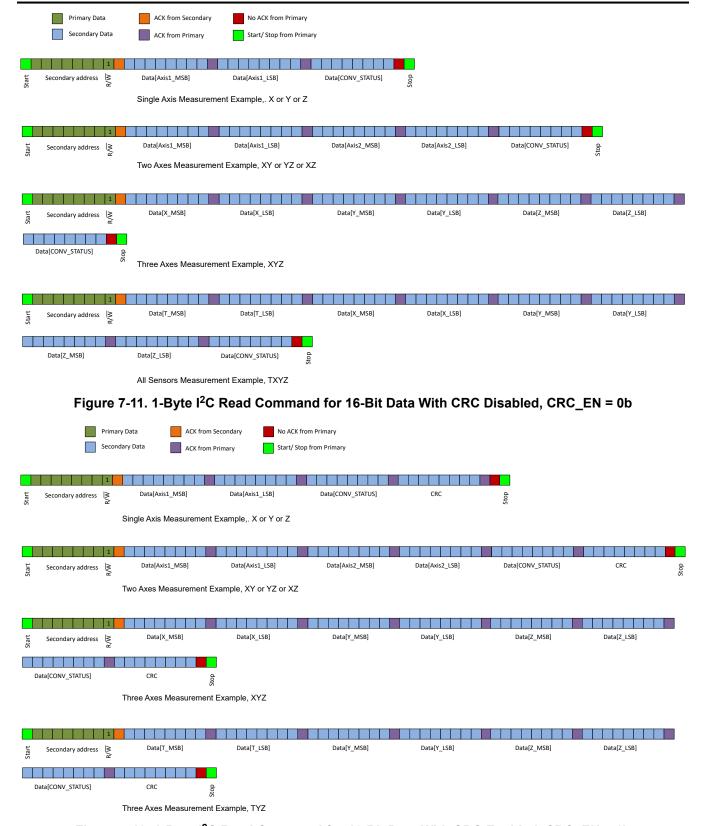

# 7.5.1.3.4 1-Byte I2C Read Command for 16-Bit Data

Figure 7-11 and Figure 7-12 show examples of 1-byte  $I^2C$  read command supported by the TMAG5273. Select  $I2C\_RD$  =01b to enable this mode. The command byte contains 7-bit secondary device address and a '1' at the  $R/\overline{W}$  bit. In this mode, per MAG\_CH\_EN and T\_CH\_EN bits setting, the device will send 16-bit data of the enabled channels and the CONV\_STATUS register data byte. If CRC is enabled, the device will send an additional CRC byte based off the CRC calculation of the command byte and the data sent in the current packet. When multiple channels are enabled, the sent data follows the T, X, Y, and Z sequence in the successive data bytes.

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: *TMAG5273*

Figure 7-12. 1-Byte I<sup>2</sup>C Read Command for 16-Bit Data With CRC Enabled, CRC\_EN = 1b

### Note

In the 1-byte read command for 16-bit data only up to 3 channels data can be sent when CRC is enabled. This restriction doesn't apply if CRC is disabled.

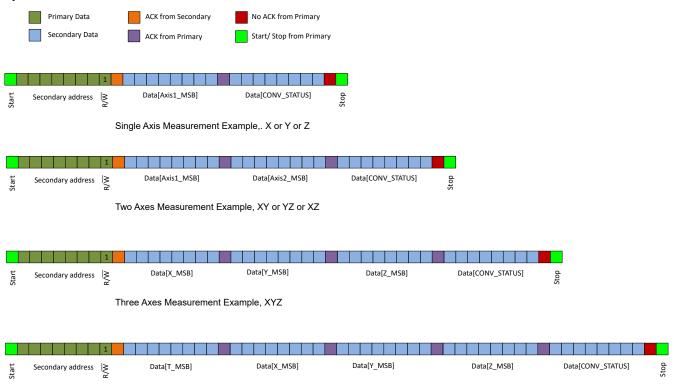

### 7.5.1.3.5 1-Byte I<sup>2</sup>C Read Command for 8-Bit Data

Figure 7-13 and Figure 7-14 show examples of 1-byte  $I^2C$  read command supported by the TMAG5273. Select  $I2C\_RD$  =10b to enable this mode. The command byte contains 7-bit secondary device address and a '1' at the  $R/\overline{W}$  bit. In this mode, per MAG\_CH\_EN and T\_CH\_EN bits setting, the device will send 8-bit data of the enabled channels and the CONV\_STATUS register data byte. If CRC is enabled, the device will send an additional CRC byte based off the CRC calculation of the command byte and the data sent in the current packet. When multiple channels are enabled, the sent data follows the T, X, Y, and Z sequence in the successive data bytes.

Figure 7-13. 1-Byte I<sup>2</sup>C Read Command for 8-Bit Data With CRC Disabled, CRC\_EN = 0b

All Sensors Measurement Example, TXYZ

Figure 7-14. 1-Byte I<sup>2</sup>C Read Command for 8-Bit Data With CRC Enabled, CRC\_EN = 1b

#### Note

In the 1-byte read command for 8-bit data any combinations of channels can be sent without restrictions.

### 7.5.1.3.6 I<sup>2</sup>C Read CRC

The TMAG5273 supports optional CRC during  $I^2C$  read. The CRC can be enabled through the CRC\_EN register bit. The CRC is performed on a data string that is determined by the  $I^2C$  read type. The CRC information is sent as a single byte after the data bytes. The code is generated by the polynomial  $x^8 + x^2 + x + 1$ . Initial CRC bits are FFh.

The following equations can be employed to calculate CRC:

The following examples show calculated CRC byte based off various input data:

I2C Data 00h : CRC = F3h I2C Data FFh : CRC = 00h I2C Data 80h : CRC = 7Ah I2C Data 4Ch: CRC = 10h I2C Data E0h : CRC = 5Dh

I2C Data 00000000h : CRC = D1h I2C Data FFFFFFFFh: CRC = 0Fh

### 7.5.2 Data Definition

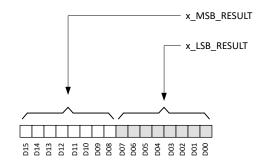

### 7.5.2.1 Magnetic Sensor Data

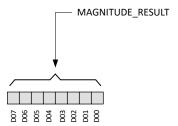

The X, Y, and Z magnetic sensor data are stored in x\_MSB\_RESULT and x\_LSB\_RESULT registers. Figure 7-15 shows that each sensor output stored in a 16-bit 2's complement format in two 8-bit registers. The data can be retrieved as 16-bit format combining both MSB and LSB registers, or as 8-bit format through the MSB register.

Figure 7-15. Magnetic Sensor Data Definition

The measured magnetic field can be calculated using Equation 10 for 16-bit data, and using Equation 11 for 8-bit data.

$$B = \frac{-(D_{15} \times 2^{15}) + \sum_{i=0}^{14} D_i \times 2^i}{2^{16}} \times 2|B_R|$$

(10)

where

- · B is magnetic field in mT.

- D<sub>i</sub> is the data bit shown in Figure 7-15.

- B<sub>R</sub> is the magnetic range in mT for the corresponding channel.

$$B = \frac{-(D_{15} \times 2^7) + \sum_{i=0}^{6} D_{i+8} \times 2^i}{2^8} \times 2|B_R|$$

(11)

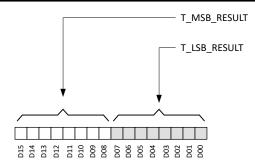

### 7.5.2.2 Temperature Sensor Data

The TMAG5273 will measure temperature from -40 °C to 170 °C. The temperature sensor data are stored in T MSB RESULT and T LSB RESULT registers. Figure 7-16 shows the sensor output stored in a 16-bit 2's complement format in two 8-bit registers. The data can be retrieved as 16-bit format combining both MSB and LSB registers, or as 8-bit format through the MSB register.

Figure 7-16. Temperature Sensor Data Definition

The measured temperature in degree Celsius can be calculated using Equation 12 for 16-bit data, and using Equation 13 for 8-bit data.

$$T = T_{SENS\_T0} + \frac{T_{ADC\_T} - T_{ADC\_T0}}{T_{ADC\_RES}}$$

(12)

### where

- T is the measured temperature in degree Celsius.

- T<sub>SENS T0</sub> as listed in the *Electrical Characteristics* table.

- T<sub>ADC</sub> RES is the change in ADC code per degree Celsius.

- T<sub>ADC</sub> T<sub>0</sub> as listed in the *Electrical Characteristics* table.

- T<sub>ADC</sub> T is the measured ADC code for temperature T.

$$T = T_{SENS\_T0} + \frac{256 \times \left( T_{ADC\_T} - \frac{T_{ADC\_T0}}{256} \right)}{T_{ADC\_RES}}$$

(13)

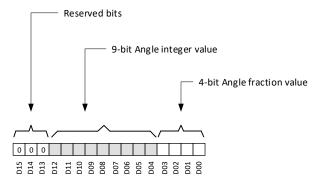

### 7.5.2.3 Angle and Magnitude Data Definition

The TMAG5273 calculates the angle from a pair of magnetic axes based off the ANGLE\_EN register bits setting. Figure 7-17 shows the angle information stored in the ANGLE\_RESULT\_MSB and ANGLE\_RESULT\_LSB registers. Bits D04-D12 store angle integer value from 0 to 360 degree. Bits D00-D03 store fractional angle value. The 3-MSB bits are always populated as b000. The angle can be calculated using Equation 14.

$$A = \sum_{i=4}^{12} D_i \times 2^{i-4} + \frac{\sum_{i=0}^{3} D_i \times 2^i}{16}$$

(14)

### where

- A is the angle measured in degree.

- D<sub>i</sub> is the data bit as shown in Figure 7-17.

For example: a 354.50 degree is populated as 0001 0110 0010 1000b and a 17.25 degree is populated as 000 0001 0100b.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

Figure 7-17. Angle Data Definition

During the angle calculation, use Equation 15 to calculate the resultant vector magnitude.

$$M = \sqrt{MADC_{Ch1}^2 + MADC_{Ch2}^2} \tag{15}$$

where

MADC<sub>Ch1</sub>, MADC<sub>Ch2</sub> are the ADC codes of the two magnetic channels selected for the angle calculation.

Figure 7-18 shows the magnitude value stored in the MAGNITUDE RESULT register. For on-axis angular measurement the magnitude value should remain constant across the full 360° measurement.

Figure 7-18. Magnitude Result Data Definition

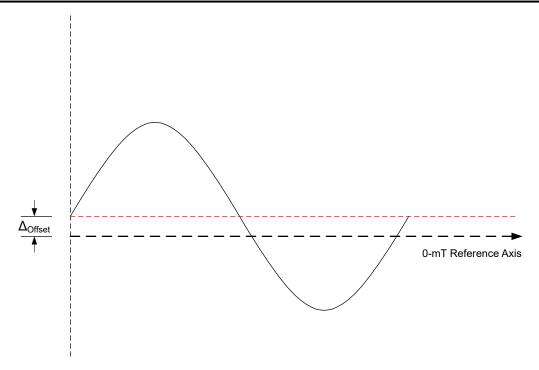

### 7.5.2.4 Magnetic Sensor Offset Correction

The TMAG5273 enables offset correction for a pair of magnetic axes (see Figure 7-19). The MAG OFFSET CONFIG 1 and MAG OFFSET CONFIG 2 registers store the offset values to be corrected in 2's complement data format. As an example, if the uncorrected waveform for a particular axis has a value that is +2 mT too high, the offset correction value of -2 mT should be entered in the corresponding offset correction register. The selection and order of the sensors are defined in the ANGLE EN register bits setting. The default value of these offset correction registers are set as zero.

Figure 7-19. Magnetic Sensor Data Offset Correction

The amount of offset for each axis can be calculated using Equation 16. As an example, with a ±40mT range, MAG\_OFFSET\_CONFIG\_1 set at 1000 0000b, and MAG\_OFFSET\_CONFIG\_2 set at 0001 0000b, the offset correction for the first axis is −2.5mT and second axis is 0.312mT.

$$\Delta_{Offset} = \frac{-(D_7 \times 2^7) + \sum_{i=0}^{6} D_i \times 2^i}{2^{12}} \times 2|B_R|$$

(16)

### where

- $\Delta_{Offset}$  is the amount of offset correction to be applied in mT.

- D<sub>i</sub> is the data bit in the MAG\_OFFSET\_CONFIG\_1 or MAG\_OFFSET\_CONFIG\_2 register.

- B<sub>R</sub> is the magnetic range in mT for the corresponding channel.

Alternately values for MAG\_OFFSET\_CONFIG\_1 or MAG\_OFFSET\_CONFIG\_2 can be calculated for a target offset correction using Equation 17.

$$MAG\_OFFSET = \frac{2^{12} \times \Delta_{Offset}}{2|B_R|}$$

(17)

### where

- MAG\_OFFSET is the decimal value to be entered in the MAG\_OFFSET\_CONFIG\_1 or MAG\_OFFSET\_CONFIG\_2 register.

- Δ<sub>Offset</sub> is the amount of offset correction to be applied in mT.

- B<sub>R</sub> is the magnetic range in mT for the corresponding channel.

### 7.6 Register Map

### 7.6.1 TMAG5273 Registers

Table 7-6 lists the TMAG5273 registers. All register offset addresses not listed in Table 7-6 should be considered as reserved locations and the register contents should not be modified.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

# **User Configuration Registers**

# Table 7-6. TMAG5273 Registers

| Go |

|----|

|    |

| Go |

|    |

Complex bit access types are encoded to fit into small table cells. Table 7-7 shows the codes that are used for access types in this section.

Table 7-7. TMAG5273 Access Type Codes

| Tuble 1 11 Thirteday of Access 13pe could |              |                                             |  |  |  |

|-------------------------------------------|--------------|---------------------------------------------|--|--|--|

| Access Type                               | Code         | Description                                 |  |  |  |

| Read Type                                 |              |                                             |  |  |  |

| R                                         | R            | Read                                        |  |  |  |

| Write Type                                | ,            |                                             |  |  |  |

| W                                         | W            | Write                                       |  |  |  |

| W1CP                                      | W<br>1C<br>P | Write 1 to clear Requires privileged access |  |  |  |

| Reset or Default Value                    |              |                                             |  |  |  |

| - n                                       |              | Value after reset or the default value      |  |  |  |

# 7.6.1.1 DEVICE\_CONFIG\_1 Register (Offset = 0h) [Reset = 0h]

DEVICE\_CONFIG\_1 is shown in Table 7-8.

Return to the Summary Table.

Table 7-8. DEVICE\_CONFIG\_1 Register Field Descriptions

| Bit | Field      | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CRC_EN     | R/W  | Oh    | Enables I2C CRC byte to be sent 0h = CRC disabled 1h = CRC enabled                                                                                                                                                                                                                                                                                                                                                                                             |

| 6-5 | MAG_TEMPCO | R/W  | 0h    | Temperature coefficient of the magnet 0h = 0% (No temperature compensation) 1h = 0.12%/ deg C (NdBFe) 2h = Reserved 3h = 0.2%/deg C (Ceramic)                                                                                                                                                                                                                                                                                                                  |

| 4-2 | CONV_AVG   | R/W  | 0h    | Enables additional sampling of the sensor data to reduce the noise effect (or to increase resolution)  0h = 1x average, 10.0-kSPS (3-axes) or 20-kSPS (1 axis)  1h = 2x average, 5.7-kSPS (3-axes) or 13.3-kSPS (1 axis)  2h = 4x average, 3.1-kSPS (3-axes) or 8.0-kSPS (1 axis)  3h = 8x average, 1.6-kSPS (3-axes) or 4.4-kSPS (1 axis)  4h = 16x average, 0.8-kSPS (3-axes) or 2.4-kSPS (1 axis)  5h = 32x average, 0.4-kSPS (3-axes) or 1.2-kSPS (1 axis) |

| 1-0 | I2C_RD     | R/W  | 0h    | Defines the I2C read mode 0h = Standard I2C 3-byte read command 1h = 1-byte I2C read command for 16bit sensor data and conversion status 2h = 1-byte I2C read command for 8 bit sensor MSB data and conversion status 3h = Reserved                                                                                                                                                                                                                            |

# 7.6.1.2 DEVICE\_CONFIG\_2 Register (Offset = 1h) [Reset = 0h]

DEVICE\_CONFIG\_2 is shown in Table 7-9.

Return to the Summary Table.

Table 7-9. DEVICE\_CONFIG\_2 Register Field Descriptions

| Bit | Field             | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|-------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

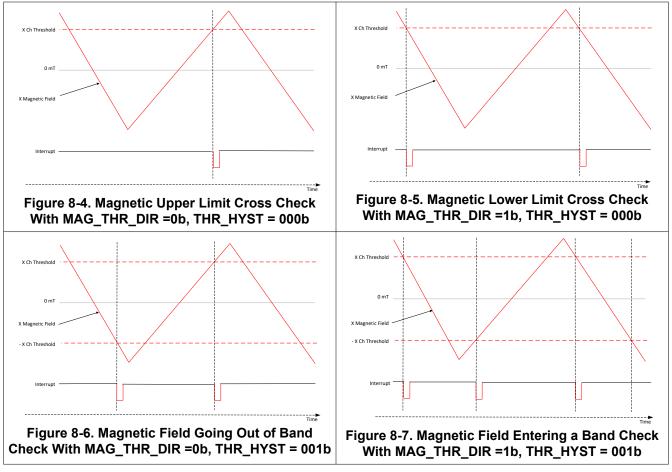

| 7-5 | THR_HYST          | R/W  | Oh    | Select thresholds for the interrupt function  Oh = Takes the 2's complement value of each x_THR_CONFIG register to create a magnetic threshold of the corresponding axis  1h = Takes the 7 LSB bits of the x_THR_CONFIG register to create two opposite magnetic thresholds (one north, and another south) of equal magnitude.  2h = Reserved 3h = Reserved 4h = Reserved 5h = Reserved 6h = Reserved 7h = Reserved |

| 4   | LP_LN             | R/W  | 0h    | Selects the modes between low active current or low-noise modes  0h = Low active current mode  1h = Low noise mode                                                                                                                                                                                                                                                                                                  |

| 3   | I2C_GLITCH_FILTER | R/W  | Oh    | I2C glitch filter 0h = Glitch filter on 1h = Glitch filter off                                                                                                                                                                                                                                                                                                                                                      |

# Table 7-9. DEVICE\_CONFIG\_2 Register Field Descriptions (continued)

| Bit | Field          | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | TRIGGER_MODE   | R/W  | Oh    | Selects a condition which initiates a single conversion based off already configured registers. A running conversion completes before executing a trigger. Redundant triggers are ignored. TRIGGER_MODE is available only during the mode explicitly mentioned in OPERATING_MODE.  0h = Conversion Start at I2C Command Bits, DEFAULT 1h = Conversion starts through trigger signal at INT pin |

| 1-0 | OPERATING_MODE | R/W  | Oh    | Selects Operating Mode and updates value based on operating mode if device transitions from Wake-up and sleep mode to Standby mode.  Oh = Stand-by mode (starts new conversion at trigger event)  1h = Sleep mode 2h = Continuous measure mode 3h = Wake-up and sleep mode (W&S mode)                                                                                                          |

# 7.6.1.3 SENSOR\_CONFIG\_1 Register (Offset = 2h) [Reset = 0h]

SENSOR\_CONFIG\_1 is shown in Table 7-10.

Return to the Summary Table.

Table 7-10. SENSOR\_CONFIG\_1 Register Field Descriptions

| Bit | Field     | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-----------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | MAG_CH_EN | R/W  | Oh    | Enables data acquisition of the magnetic axis channel(s)  0h = All magnetic channels of off, DEFAULT  1h = X channel enabled 2h = Y channel enabled 3h = X, Y channel enabled 4h = Z channel enabled 5h = Z, X channel enabled 6h = Y, Z channel enabled 7h = X, Y, Z channel enabled 8h = XYX channel enabled 9h = YXY channel enabled 9h = YXY channel enabled Ah = YZY channel enabled Bh = XZX channel enabled Ch = Reserved Dh = Reserved Fh = Reserved |

| 3-0 | SLEEPTIME | R/W  | Oh    | Selects the time spent in low power mode between conversions when OPERATING_MODE =11b  0h = 1ms 1h = 5ms 2h = 10ms 3h = 15ms 4h = 20ms 5h = 30ms 6h = 50ms 7h = 100ms 8h = 500ms 9h = 1000ms Ah = 2000ms Bh = 5000ms Ch = 20000ms                                                                                                                                                                                                                            |

# 7.6.1.4 SENSOR\_CONFIG\_2 Register (Offset = 3h) [Reset = 0h]

SENSOR\_CONFIG\_2 is shown in Table 7-11.

Return to the Summary Table.

# Table 7-11. SENSOR\_CONFIG\_2 Register Field Descriptions

| Bit | Field       | Туре | Reset | Description                                                                                                                                                                                                                                |

|-----|-------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RESERVED    | R    | 0h    | Reserved                                                                                                                                                                                                                                   |

| 6   | THRX_COUNT  | R/W  | 0h    | Number of threshold crossings before the interrupt is asserted  0h = 1 threshold crossing  1h = 4 threshold crossing                                                                                                                       |

| 5   | MAG_THR_DIR | R/W  | 0h    | Selects the direction of threshold check. This bit is ignored when THR_HYST > 001b  Oh = sets interrupt for field above the threshold  1h = sets interrupt for field below the threshold                                                   |

| 4   | MAG_GAIN_CH | R/W  | 0h    | Selects the axis for magnitude gain correction value entered in MAG_GAIN_CONFIG register  0h = 1st channel is selected for gain adjustment  1h = 2nd channel is selected for gain adjustment                                               |