### SLG47910 Datasheet

1K LUT Digital Configurable Array

The SLG47910 provides a small, LOW power component for common FPGA applications. The user creates their circuit design by programming the One Time Programmable (OTP) Non-Volatile Memory (NVM) to configure the interconnect logic, the IO pins, and the macrocells of the SLG47910. This highly versatile device allows a wide variety of FPGA applications to be designed within a very small, LOW power integrated circuit.

### **Features**

- Dense Array of Configurable Logic

- 1120 5-bit LUTs

- 1120 DFFs

- · 5 kb distributed memory

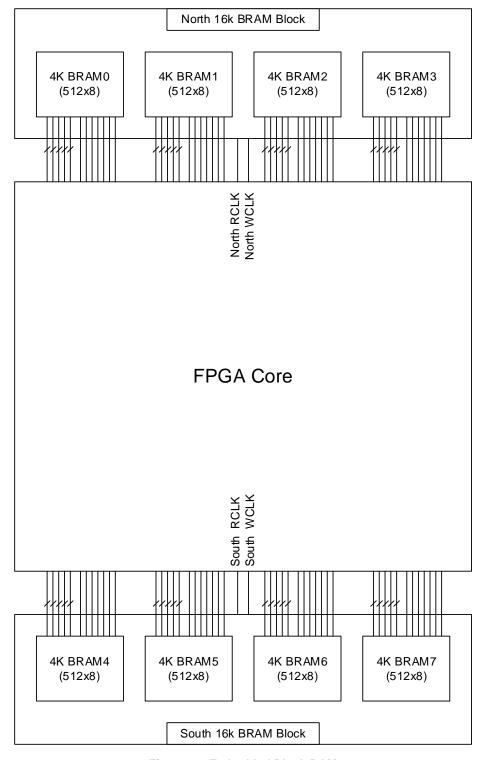

- 32 kb BRAM

- · Configurable through NVM and/or SPI interface

- 50 MHz On-chip Oscillator

- Phase-Locked Loop (PLL)

- Input from external source or internal On-Chip Oscillator

- Power Supply

- V<sub>DDIO</sub>: 1.71 V to 2.75 V

- V<sub>DDC</sub>: 1.1 V ±5%

- Power-On-Reset (POR)

- GPIO Count

- 19 GPIOs

- Bitstream Security Features

- OTP Configuration only

- Operating Temperature Range: -40 °C to +85 °C

- RoHS Compliant/Halogen-Free

- Available Package

- 24-pin STQFN: 3.0 mm x 3.0 mm x 0.55 mm, 0.4 mm pitch

## **Applications**

- Consumer Electronics

- Data Communications Equipment

- Handheld and Portable Electronics

- Notebooks and Tablet PCs

# **Contents**

| Fea | atures.     |           |                                                     | 1  |

|-----|-------------|-----------|-----------------------------------------------------|----|

| Apı | plicatio    | ons       |                                                     | 1  |

| 1.  | Over        | view      |                                                     | 6  |

|     | 1.1         | Block D   | Diagram                                             | 6  |

|     | 1.2         | Block D   | Description                                         | 7  |

| 2.  | Pin lı      | nformati  | ion                                                 | 9  |

|     | 2.1         |           | signments                                           |    |

|     | 2.2         | Pin Des   | scriptions                                          | 10 |

|     | 2.3         | Signal I  | Descriptions                                        | 10 |

|     |             | 2.3.1     | Power and Control Pins                              | 10 |

|     |             | 2.3.2     | Configuration Pins                                  | 11 |

|     |             | 2.3.3     | Global Pins                                         | 11 |

| 3.  | Spec        | ification | 18                                                  | 12 |

|     | <b>3</b> .1 |           | te Maximum Ratings                                  |    |

| 3.  | 3.2         | Recom     | nmended Operating Conditions                        | 12 |

|     | 3.3         | Electric  | cal Specifications                                  | 13 |

|     | 3.4         | IO Pull-  | -up Resistance for a Pull-up                        | 15 |

|     | 3.5         | PLL Sp    | pecifications                                       | 15 |

|     | 3.6         | Oscillat  | tor Specifications                                  | 15 |

|     | 3.7         | POR S     | pecifications                                       | 16 |

|     | 3.8         | Estimat   | ted Current Consumption Values of Supporting Blocks | 16 |

|     | 3.9         | Configu   | uration Interface Timing                            | 16 |

|     | 3.10        | Supply    | Current                                             | 17 |

|     | 3.11        |           | Characteristics                                     |    |

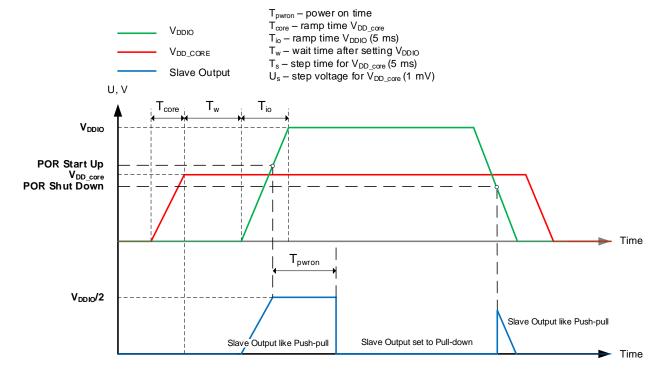

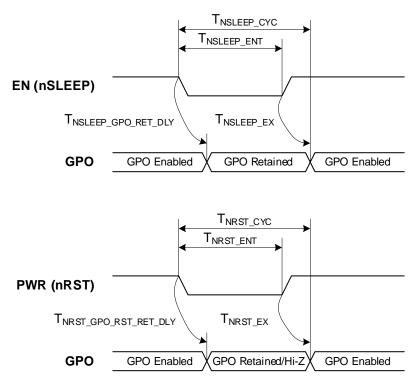

|     | 3.12        | PWR (r    | nRST) and EN (nSLEEP) Specifications                | 18 |

|     | 3.13        | Typical   | 19                                                  |    |

|     |             | 3.13.1    |                                                     |    |

|     |             | 3.13.2    | Register-to-Register Performance (LVCMOS18) [1],[2] | 19 |

| 4.  | Gene        | eral Purp | pose Input Output (GPIO) Buffers                    | 20 |

|     | 4.1         | Digital I | IO                                                  | 20 |

| 5.  | FPG/        | A Core    |                                                     | 22 |

|     | 5.1         | Introdu   | oction                                              | 22 |

|     | 5.2         | FPGA (    | Core Composition                                    | 22 |

|     | 5.3         | Configu   | urable Logic Blocks                                 | 23 |

|     |             | 5.3.1     | Configurable Logic Blocks for Logic                 | 23 |

|     |             | 5.3.2     | Configurable Logic Blocks for Memory                | 25 |

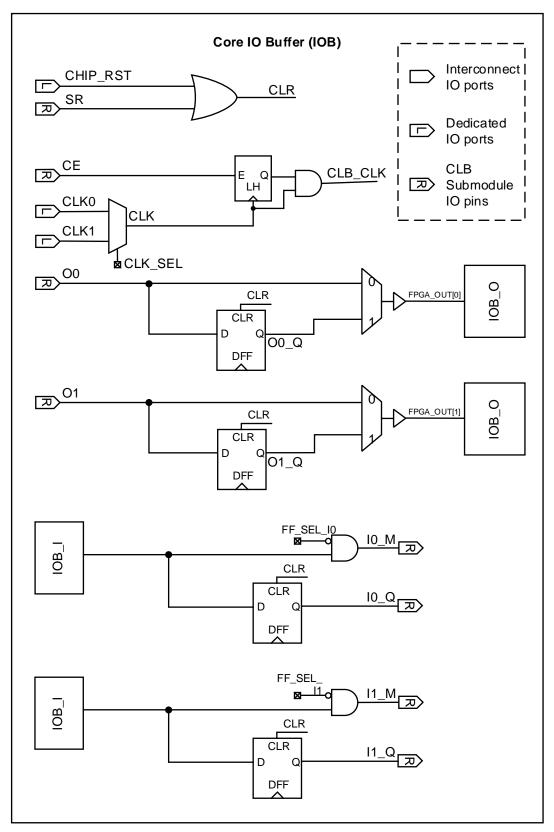

|     | 5.4         | Core IC   | D Buffers                                           | 28 |

|     |             | 5.4.1     | Typical IO Behavior During Power-up                 | 29 |

|     |             | 5.4.2     | Supported Standards                                 | 29 |

|     |             | 5.4.3     | Programmable Pull-up Resistors                      | 29 |

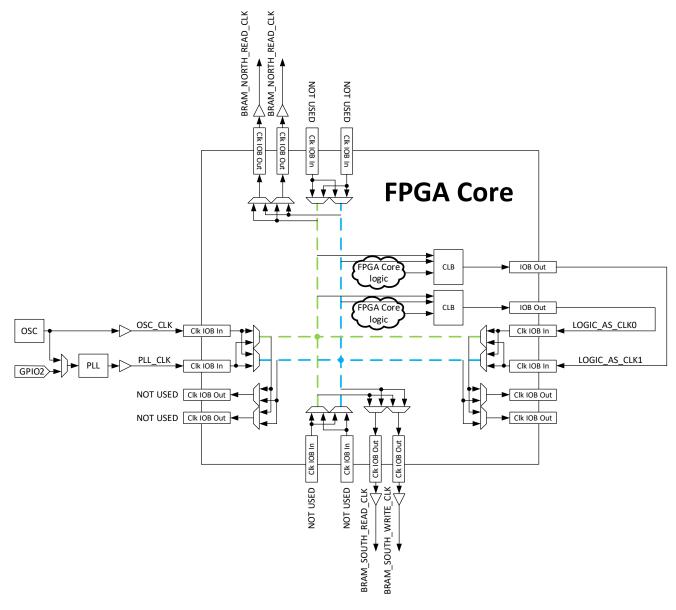

| 6.  | Cloc        | king      |                                                     | 30 |

|     | 6.1         | Clock N   | Network                                             | 30 |

## SLG47910 Datasheet

|     | 6.2    | On-chip Oscillator                                                           | 31 |

|-----|--------|------------------------------------------------------------------------------|----|

|     |        | 6.2.1 Overview                                                               | 31 |

|     |        | 6.2.2 Signal Descriptions                                                    | 31 |

|     | 6.3    | Phase-Locked Loop (PLL)                                                      | 32 |

|     |        | 6.3.1 Overview                                                               | 32 |

|     |        | 6.3.2 Signal Descriptions                                                    | 32 |

|     | 6.4    | Logic-As-Clock                                                               | 34 |

| 7.  | Powe   | er-up Sequence                                                               | 35 |

| 8.  | Conf   | iguration Modes                                                              | 38 |

| 9.  | Bloc   | « RAM                                                                        | 39 |

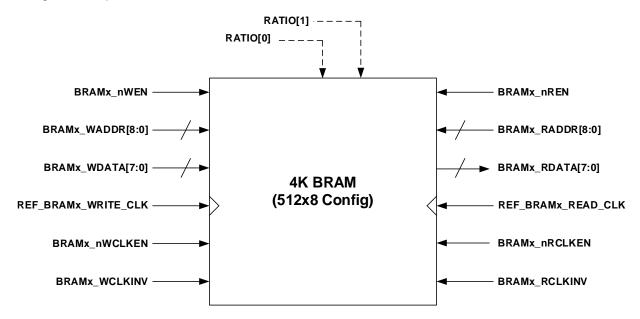

|     | 9.1    | BRAM Structure                                                               | 39 |

|     | 9.2    | BRAM Slices                                                                  | 40 |

|     |        | 9.2.1 BRAM Slice Structure                                                   | 40 |

|     | 9.3    | BRAM Considerations                                                          | 41 |

|     | 9.4    | Address Extension                                                            | 41 |

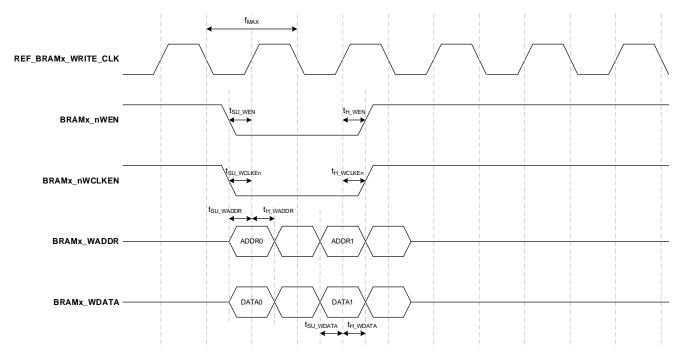

|     |        | 9.4.1 Write Operations for BRAM                                              | 42 |

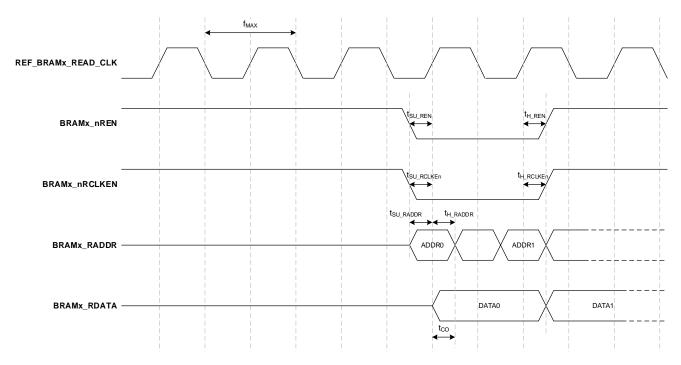

|     |        | 9.4.2 Read Operation for BRAM                                                | 43 |

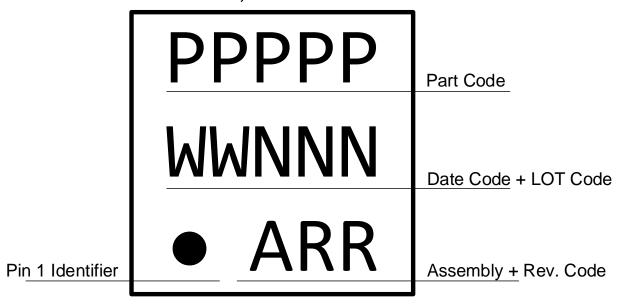

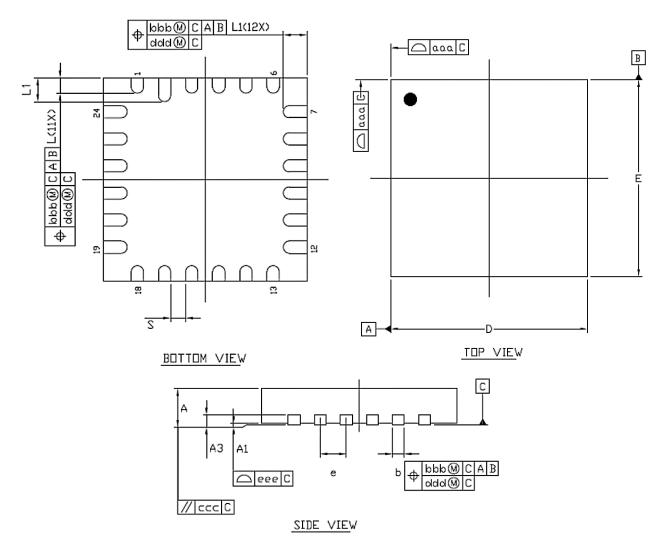

| 10. | Pack   | age Top Marking Definitions                                                  | 44 |

|     | 10.1   | STQFN 24L 3 mm x 3 mm, 0.4P FCA                                              | 44 |

| 11. | Pack   | age Information                                                              | 45 |

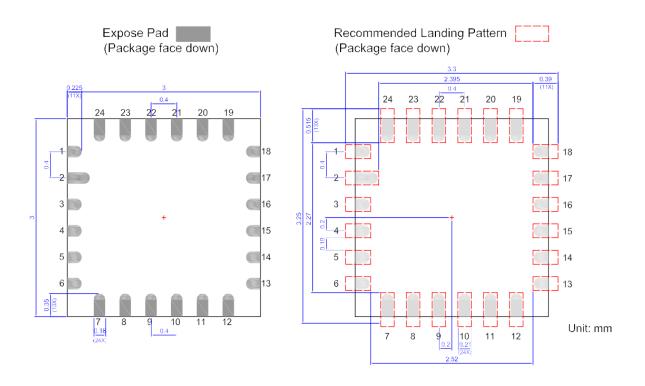

|     |        | Package Outline Drawing for STQFN 24L 3 mm x 3 mm x 0.55 mm 0.35P FC Package |    |

|     |        | Moisture Sensitivity Level                                                   |    |

|     | 11.3   | STQFN Handling                                                               | 46 |

|     | 11.4   | Soldering Information                                                        | 46 |

| 12. | Ther   | nal Guidelines                                                               | 46 |

| 13. | Layo   | ut Guidelines                                                                | 47 |

|     | 13.1   | Layout Guidelines for STQFN 24L 3 mm x 3 mm x 0.55mm 0.4P FC Package         | 47 |

| 14. | Orde   | ring Information                                                             | 48 |

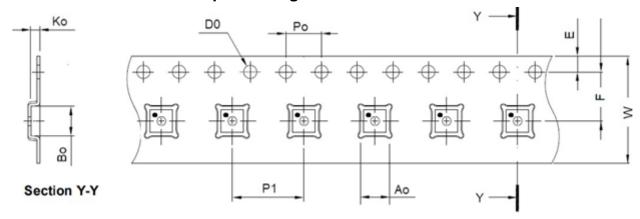

|     |        | Tape and Reel Specifications                                                 |    |

|     | 14.2   | Carrier Tape Drawing and Dimensions                                          | 48 |

|     |        | 14.2.1 STQFN 24L Carrier Tape Drawing                                        | 49 |

| Glo | ssary. |                                                                              | 50 |

| Ref | erence | 98                                                                           | 51 |

| App | endix  | : Register Definitions                                                       | 52 |

| Rev | rision | History                                                                      | 59 |

# **Figures**

| Figure 1. Block Diagram                                                     | 6  |

|-----------------------------------------------------------------------------|----|

| Figure 2. Pin Assignments for 24-pin STQFN                                  | 9  |

| Figure 3. GPIO Buffers                                                      | 20 |

| Figure 4. FPGA Core                                                         | 22 |

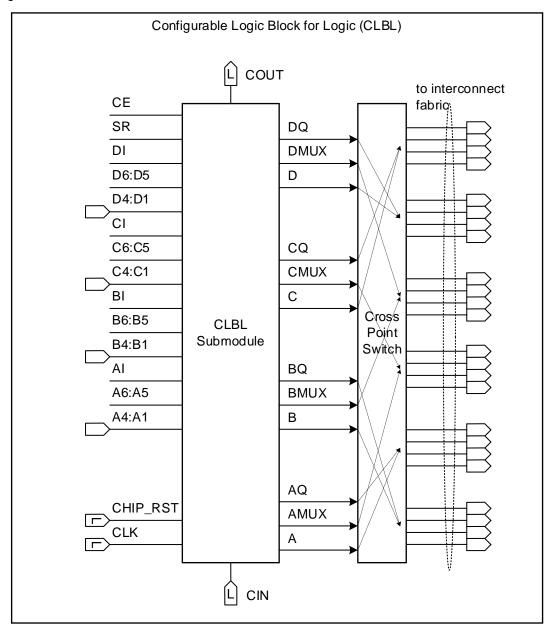

| Figure 5. Configurable Logic Blocks for Logic                               | 23 |

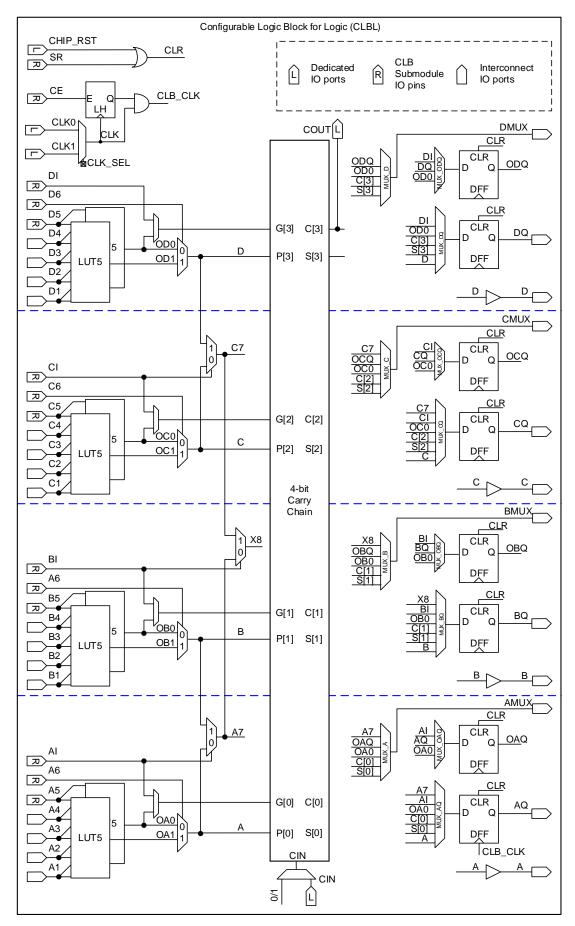

| Figure 6. Configurable Logic Blocks for Logic (cont.)                       | 24 |

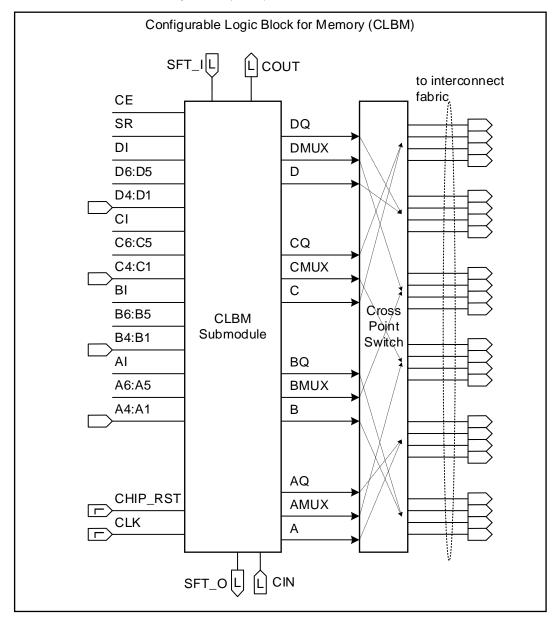

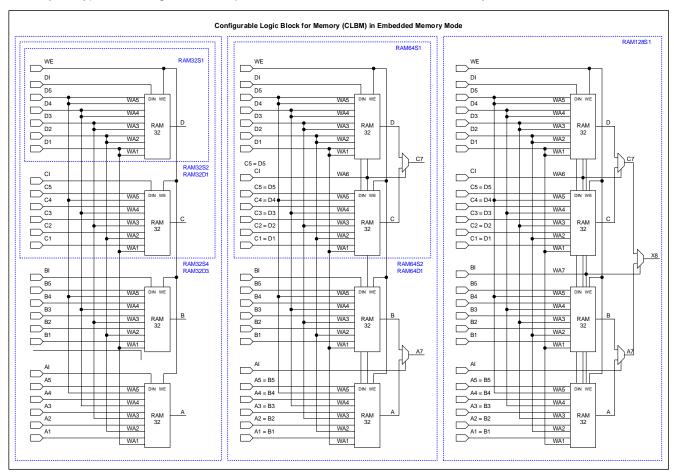

| Figure 7. Configurable Logic Blocks for Memory                              | 25 |

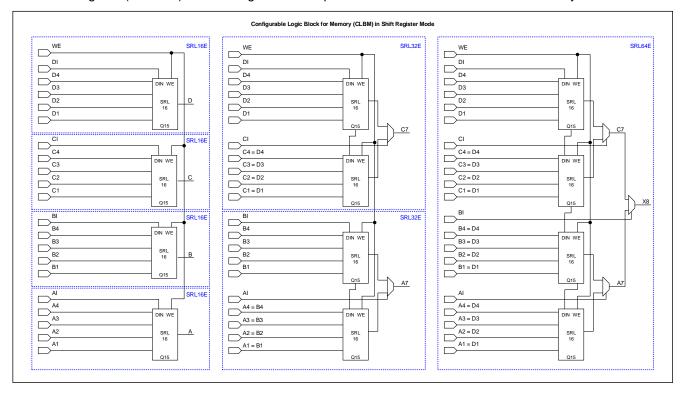

| Figure 8. Configurable Logic Blocks for Memory used in Shift Register Mode  | 26 |

| Figure 9. Configurable Logic Blocks for Memory used in Embedded Memory Mode | 27 |

| Figure 10. Core IO Buffers                                                  | 28 |

| Figure 11. Clock Network Signals and Positions                              |    |

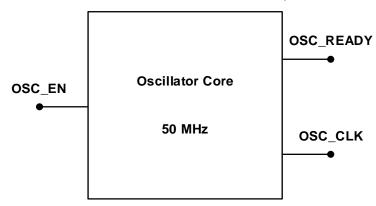

| Figure 12. On-chip Oscillator                                               | 31 |

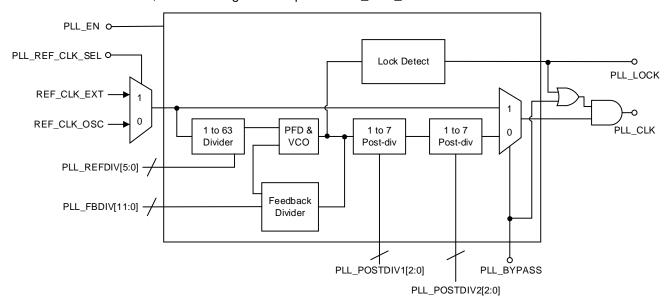

| Figure 13. Phase-Locked Loop Block Diagram                                  | 32 |

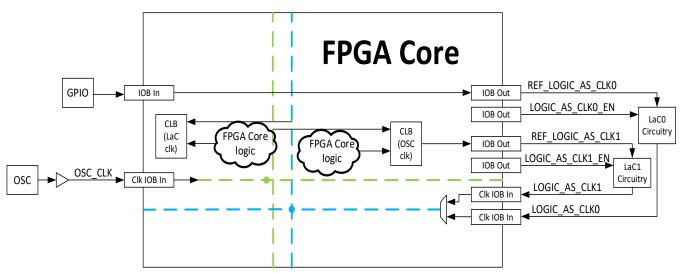

| Figure 14. Logic-As-Clock Network                                           | 34 |

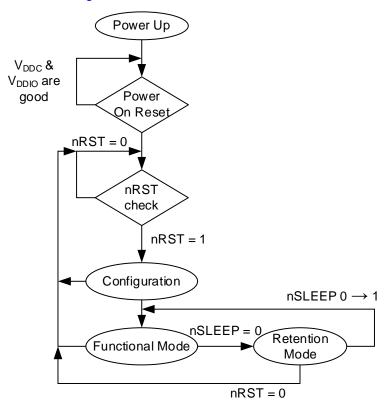

| Figure 15. Power-up Sequence                                                | 35 |

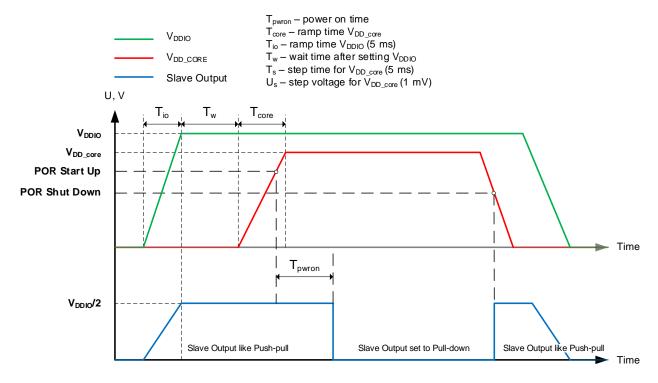

| Figure 16. POR Power ON Time with VDDC                                      | 36 |

| Figure 17. POR Power ON Time with VDDIO                                     | 36 |

| Figure 18. Device On/Off State Cycle Timing Diagram (PWR/EN Pin)            | 37 |

| Figure 19. Embedded Block RAM                                               | 39 |

| Figure 20. BRAM Slice Structure                                             | 40 |

| Figure 21. BRAM Timing Diagram for Write Operations                         | 42 |

| Figure 22. BRAM Timing Diagram for Read Operations                          | 43 |

| Figure 23. Package Top Marking STQFN-24                                     | 44 |

| Figure 24. Package Outlines Drawing STQFN 24                                | 45 |

| Figure 25. Recommended Landing Pattern for STQFN 24L                        | 47 |

| Figure 26. Carrier Tape Drawing for STQFN-24L                               | 49 |

# **Tables**

| Table 1. Block Control                                                 | 8  |

|------------------------------------------------------------------------|----|

| Table 2. STQFN-24 Pin Assignments                                      |    |

| Table 3. Pin Descriptions                                              | 10 |

| Table 4. Power and Control Pins                                        | 10 |

| Table 5. Configuration Pins                                            | 11 |

| Table 6. Global Pins                                                   | 11 |

| Table 7. GPIO Functionality                                            | 21 |

| Table 8. Supported Input/Output Standards                              | 29 |

| Table 9. Clock Network Signals & Positions                             | 31 |

| Table 10. POR Power ON Time for V <sub>DDC</sub> and V <sub>DDIO</sub> | 35 |

| Table 11. BRAM Configuration                                           | 40 |

| Table 12. Write Address Extension using bits 5-7.                      | 41 |

| Table 13. Read Address Extension using bits 2-4                        | 41 |

| Table 14. MSL Classification                                           | 46 |

| Table 15. Tape and Reel Specifications                                 | 48 |

| Table 16. Carrier Tape Drawing and Dimensions                          | 48 |

# 1. Overview

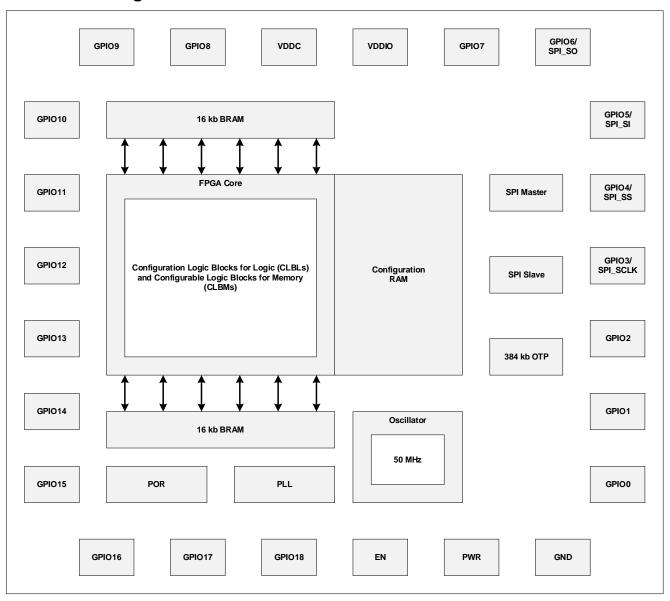

The components of the SLG47910 are shown in the Block Diagram (Figure 1).

# 1.1 Block Diagram

Figure 1. Block Diagram

## 1.2 Block Description

### **GPIO**

The GPIO pins are general purpose programmable Digital IO circuits that can be programmed as an input or an output. They contain configurable output buffers, input buffers, and IO registers. The GPIO pins connect to the FPGA Core IOBs. GPIO [6:3] are used to configure the device in SPI mode.

#### **BRAM**

The 16 kb BRAM is an SRAM block that can be programmed in different width and depth configurations. It has one write port and one read port and can be configured as a simple dual port SRAM. There are two 16 kb SRAMs that interface with the FPGA Core. The BRAM does not connect directly with the GPIO. The width and depth configurations must be the same for the write and read ports.

#### **FPGA Core**

The FPGA Core consists of the FPGA fabric and a ring of interface blocks called IOBs. The IOBs are used to communicate between the FPGA fabric and the other sub-blocks. The FPGA fabric consists of an array of Configurable Logic Blocks (CLBs). Each CLB contains LUTs, Registers, DFFs, and a clock network which are used to implement user defined logic functions. In addition, some CLBs in the Array can be configured in Embedded Memory Mode (EMM) and Shift Register Mode (SRM). These modes are used to implement distributed memories. The Configuration RAM is a volatile memory that stores the FPGA design after the chip configuration. The Configuration RAM can be loaded from the OTP or SPI Blocks.

### **OTP Block**

The 384 kb OTP is used to store user defined configurations. The 384 kb OTP is a One Time Programmable NVM block that allows users to store the FPGA design once the design has been finalized.

#### **Power-on Reset**

The POR circuit monitors the VDDIO and VDDC power supplies and keeps the SLG47910 in reset state upon power up until  $V_{\text{DDIO}}$  and  $V_{\text{DDC}}$  are within the specified voltage ranges. The POR reset will occur if power rails drop below the specified voltage range after the device has been powered up. A POR reset will tri-state all GPIOs.

#### SPI

The SPI Master and SPI Slave are dedicated circuits that allow the Configuration RAM to be programmed. The SPI Master and SPI Slave connect to GPIO3 (SPI\_SCLK), GPIO4 (SPI\_SS), GPIO5 (SPI\_SI), and GPIO6 (SPI\_SO).

### Clocking

SLG47910 has three clocking options: PLL, OSC, and LaC.

The PLL and oscillator can be used to generate internal clocks. The PLL receives clock sources from the Oscillator or GPIO2. The PLL can generate a wide range of frequencies. The Oscillator frequency is 50 MHz. The OSC, PLL, and LaCs can drive the BRAM and the FPGA Core GPIO can be used to input external Logic-As -Clock (LaC) with the help of the IO Planner in the software.

The EN (nSLEEP) and PWR (nRST) inputs are used to control the power consumption as shown in Table 1.

**Table 1. Block Control**

| PWR (nRST) | EN (nSLEEP) | Description                                                                                                                                                                                                       |

|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |             | Device Reset/Off State:                                                                                                                                                                                           |

|            |             | ■ Configuration of FPGA Core is not retained, and Array Power is gated                                                                                                                                            |

| 0          | ×           | ■ PLL, OSC, and OTP memory are disabled                                                                                                                                                                           |

|            | ^           | <ul> <li>BRAM data is not retained unless BRAM Keep Register value at Reset = 1 (see Reg[193] in<br/>Appendix: Register Definitions)</li> </ul>                                                                   |

|            |             | ■ GPIO in Hi-Z state and not retained unless REG_GPIO_KEEP = 1.                                                                                                                                                   |

|            |             | Lower Power/Retention State:                                                                                                                                                                                      |

|            |             | ■ Configuration of FPGA Core is retained, and Array Power is gated                                                                                                                                                |

|            |             | ■ PLL, OSC and OTP memory are disabled                                                                                                                                                                            |

| 1          | 0           | <ul> <li>BRAM data is retained if BRAM (03) Register Enable = 1 (see Reg[320] in Appendix: Register Definitions) and if BRAM (47) Register Enable = 1 (see Reg[321] in Appendix: Register Definitions)</li> </ul> |

|            |             | ■ GPIO is not in Hi-Z state and data is retained.                                                                                                                                                                 |

|            |             | Configuration Mode:                                                                                                                                                                                               |

|            |             | ■ From internal OTP                                                                                                                                                                                               |

| 1          | 1           | ■ From external SPI                                                                                                                                                                                               |

|            |             | ■ From MCU interface                                                                                                                                                                                              |

|            |             | ■ FPGA Core, GPIO, BRAM, PLL, and OSC are controlled by IOBs.                                                                                                                                                     |

# 2. Pin Information

# 2.1 Pin Assignments

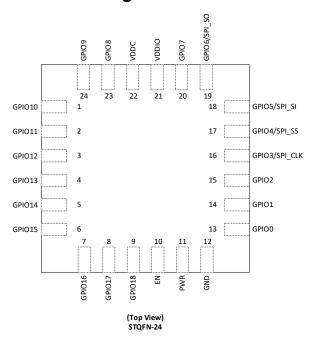

Figure 2. Pin Assignments for 24-pin STQFN

Table 2. STQFN-24 Pin Assignments

| Pin# | Signal Name   | Pin Functions                                     |

|------|---------------|---------------------------------------------------|

| 1    | GPIO10        | General Purpose IO                                |

| 2    | GPIO11        | General Purpose IO                                |

| 3    | GPIO12        | General Purpose IO                                |

| 4    | GPIO13        | General Purpose IO                                |

| 5    | GPIO14        | General Purpose IO                                |

| 6    | GPIO15        | General Purpose IO                                |

| 7    | GPIO16        | General Purpose IO                                |

| 8    | GPIO17        | General Purpose IO                                |

| 9    | GPIO18        | General Purpose IO                                |

| 10   | EN (nSLEEP)   | nSleep Mode                                       |

| 11   | PWR (nRST)    | nReset Mode                                       |

| 12   | GND           | Ground                                            |

| 13   | GPIO0         | General Purpose IO                                |

| 14   | GPIO1         | General Purpose IO                                |

| 15   | GPIO2         | General Purpose IO or refCLK                      |

| 16   | GPIO3/SPI_CLK | General Purpose IO or SPI Serial Clock            |

| 17   | GPIO4/SPI_SS  | General Purpose IO or SPI Slave Select            |

| 18   | GPIO5/SPI_SI  | General Purpose IO or SPI Serial Input            |

| 19   | GPIO6/SPI_SO  | General Purpose IO or SPI Serial<br>Output/Config |

| 20   | GPIO7         | General Purpose IO                                |

| 21   | VDDIO         | Power for IO                                      |

| 22   | VDDC          | Power for Core                                    |

| 23   | GPIO8         | General Purpose IO                                |

| 24   | GPIO9         | General Purpose IO                                |

# 2.2 Pin Descriptions

**Table 3. Pin Descriptions**

| Pin    |          | Secondary Function during Boot Sequence |               |                      |  |  |  |

|--------|----------|-----------------------------------------|---------------|----------------------|--|--|--|

| Number | Pin Name | OTP Mode                                | SPI Mode      | MCU Mode             |  |  |  |

| 1      | GPIO10   |                                         |               |                      |  |  |  |

| 2      | GPIO11   |                                         |               |                      |  |  |  |

| 3      | GPIO12   |                                         |               |                      |  |  |  |

| 4      | GPIO13   |                                         |               |                      |  |  |  |

| 5      | GPIO14   |                                         |               |                      |  |  |  |

| 6      | GPIO15   |                                         |               |                      |  |  |  |

| 7      | GPIO16   |                                         |               |                      |  |  |  |

| 8      | GPIO17   |                                         |               |                      |  |  |  |

| 9      | GPIO18   |                                         |               |                      |  |  |  |

| 10     | EN       |                                         |               |                      |  |  |  |

| 11     | PWR      |                                         |               |                      |  |  |  |

| 12     | VSS      |                                         |               |                      |  |  |  |

| 13     | GPIO0    |                                         |               |                      |  |  |  |

| 14     | GPIO1    |                                         |               |                      |  |  |  |

| 15     | GPIO2    |                                         |               |                      |  |  |  |

| 16     | GPIO3    |                                         | SPI_SCLK      | SPI_SCLK             |  |  |  |

| 17     | GPIO4    |                                         | SPI_SS        | SPI_SS               |  |  |  |

| 18     | GPIO5    |                                         | SPI_SI (MISO) | SPI_SI (MOSI)        |  |  |  |

| 19     | GPIO6    |                                         | SPI_SO (MOSI) | SPI_SO (MISO)/CONFIG |  |  |  |

| 20     | GPIO7    |                                         |               |                      |  |  |  |

| 21     | VDDIO    |                                         |               |                      |  |  |  |

| 22     | VDDC     |                                         |               |                      |  |  |  |

| 23     | GPIO8    |                                         |               |                      |  |  |  |

| 24     | GPIO9    |                                         |               |                      |  |  |  |

# 2.3 Signal Descriptions

## 2.3.1 Power and Control Pins

**Table 4. Power and Control Pins**

| Pin Name (Signal Name) | Function | Description          |

|------------------------|----------|----------------------|

| VDDC                   | Power    | Core Power Supply    |

| VDDIO                  | Power    | Power for IO in Bank |

| GND                    | Ground   | Ground               |

| EN (nSLEEP)            | Sleep    | Retention Function   |

| PWR (nRST)             | Reset    | Reset Signal         |

# 2.3.2 Configuration Pins

**Table 5. Configuration Pins**

| Signal Name |                           | Function                  | 10           | Decembries                                                                                                                                                                                                                             |  |  |

|-------------|---------------------------|---------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Primary     | Secondary                 | Function                  | Ю            | Description                                                                                                                                                                                                                            |  |  |

|             | SDI SCIK                  | Configuration<br>SPI Mode | Clock Output | In Master SPI Mode, this pin outputs the clock to external SPI memory.                                                                                                                                                                 |  |  |

| GPIO3       | SPI_SCLK                  | Configuration MCU Mode    | Clock Input  | In Slave SPI (MCU) Mode, this pin inputs the clock from external processor.                                                                                                                                                            |  |  |

| Primary     | USER_NAME                 | General IO                | Ю            | In user mode, after configuration, this pin can be programmed as general IO in user function.                                                                                                                                          |  |  |

| GPIO4       | SPI_SS                    | Configuration<br>SPI Mode | Input        | Depending on the SPI and Slave settings, the SPI_SS in is used to select programming mode SPI.                                                                                                                                         |  |  |

| GPIO4       | SPI_55                    | Configuration MCU Mode    | Output       | Depending on the SPI and Slave settings, the SPI_SS in is used to select programming MCU load mode.                                                                                                                                    |  |  |

|             | USER_NAME                 | General IO                | Ю            | In user mode, after configuration, this pin can be programmed as general IO in user function                                                                                                                                           |  |  |

|             | SPI_SO (MISO)             | Configuration<br>SPI Mode | Input        | MISO is a data pin. This pin is used to transmit data from the slave to the master. Whenever the slave sends data, that data will be collected over the MISO pin by the master.                                                        |  |  |

| GPIO5       | SPI_SI (MOSI)             | Configuration<br>MCU Mode | три          | MOSI is a data pin. This pin is used to transmit data from the master to the slave device. Whenever the master sends data, that data will be collected over the MOSI pin by the slave.                                                 |  |  |

|             | USER_NAME                 | General IO                | Ю            | In user mode, after configuration, this pin can be programmed as general IO in user function                                                                                                                                           |  |  |

|             | SPI_SO (MOSI)             | Configuration<br>SPI Mode |              | MOSI is a data pin. This pin is used to transmit data from the master to the slave device. Whenever the master sends data, that data will be collected over the MOSI pin by the slave.                                                 |  |  |

| GPIO6       | SPI_SI (MISO) /<br>CONFIG | Configuration<br>MCU Mode | Output       | MISO is a data pin. This pin is used to transmit data from the slave to the master. Whenever the slave sends data, that data will be collected over the MISO pin by the master. In MCU Mode, the CONFIG signal is flagged at this pin. |  |  |

|             | USER_NAME                 | General IO                | Ю            | In user mode, after configuration, this pin can be programmed as general IO in user function                                                                                                                                           |  |  |

# 2.3.3 Global Pins

### Table 6. Global Pins

| Signal Name Function |            | Ю                                                                                               | Description                                                                                                   |

|----------------------|------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| GPIO [1:0]           | General IO | General IO  IO In user mode, after configuration, this pin can be programm IO in user function. |                                                                                                               |

| GPIO2                | General IO | Ю                                                                                               | In user mode, after configuration, this pin can be programmed as general IO in user function.                 |

| GPIO2                | Ref CLK    | Input                                                                                           | This IO can be programmed as a reference clock for the device in user function when receiving clock from PLL. |

| GPIO [18:7]          | General IO | Ю                                                                                               | In user mode, after configuration, this pin can be programmed as general IO in user function.                 |

# 3. Specifications

# 3.1 Absolute Maximum Ratings

**Note**: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to the absolute maximum conditions for extended periods may affect the device reliability.

| Parameter                                              | Conditions                | Min  | Max  | Unit |

|--------------------------------------------------------|---------------------------|------|------|------|

| Supply Voltage (V <sub>DDC</sub> )                     | Non-operational           | -0.3 | 1.21 | V    |

| Supply Voltage (V <sub>DDIO</sub> )                    |                           | -0.3 | 2.75 | V    |

| Voltage at Digital Input Pins                          | I <sub>OL</sub> = -100 μA | -0.3 | 2.75 | V    |

|                                                        | Push-pull 1x              |      | 10   | mA   |

|                                                        | Push-pull 2x              |      | 20   | mA   |

| Maximum RMS or DC current (through single GPIO pin)    | Open-drain 1x             |      | 9    | mA   |

|                                                        | Open-drain 2x             |      | 18   | mA   |

| Current at Digital Input Pin                           |                           | -1.0 | 1.0  | mA   |

| Input Leakage Current (Absolute Value)                 |                           |      | 1000 | nA   |

| I <sub>VDDIO</sub> DC Current through VDDIO Pin [1]    |                           |      | 200  | mA   |

| I <sub>VDDC</sub> DC Current though VDDC Pin [1]       |                           |      | 200  | mA   |

| I <sub>GND</sub> DC Current through GND <sup>[1]</sup> |                           |      | 200  | mA   |

| Storage Temperature Range                              |                           | -65  | +150 | °C   |

| Junction Temperature                                   |                           |      | +140 | °C   |

| ESD Protection (Human Body Model)                      |                           | 2000 |      | V    |

| ESD Protection (Charged Device Model)                  |                           | 500  |      | V    |

| Moisture Sensitivity Level                             |                           |      | 1    | •    |

| [1] Package limits                                     | •                         | •    |      |      |

# 3.2 Recommended Operating Conditions

| Parameter                               | Min   | Тур | Max   | Unit |

|-----------------------------------------|-------|-----|-------|------|

| Supply Voltage (V <sub>DDC</sub> )      | 1.045 | 1.1 | 1.155 | V    |

| Supply Voltage (V <sub>DDIO</sub> )     | 1.710 | 2.5 | 2.750 | V    |

| Operating Temperature (T <sub>A</sub> ) | -40   | 25  | 85    | °C   |

| Capacitor Value at V <sub>DDC</sub>     | 0.1   |     |       | μF   |

# 3.3 Electrical Specifications

$T_A$  = -40 °C to +85 °C,  $V_{DDIO}$  = 1.71 V to 2.75 V,  $V_{DDC}$  = 1.1 V ±5%, unless otherwise specified.

| Parameter                                | Symbol                                             | Condition                                                                                     | Min                                                | Тур  | Max                         | Unit |

|------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------|------|-----------------------------|------|

| Input Leakage Current                    | I <sub>I_LKG</sub>                                 | $V_{DDIO} = 2.75 \text{ V}, V_{IN} = 0 \text{ to } V_{DDIO}$                                  | -370                                               |      | 370                         | nA   |

| Max Absolute Data Skew – Input Paths     | T <sub>skew_di_pin</sub>                           | V <sub>DDC</sub> = 1.1 ±5%, V <sub>DDIO</sub> = 1.71 V                                        | 1.51                                               | 3.25 | 6.23                        | ns   |

| Max Absolute Data Skew – Output<br>Paths | T <sub>skew_do_pin</sub>                           | V <sub>DDC</sub> = 1.1 ±5%, V <sub>DDIO</sub> = 1.71 V                                        | 1.65                                               | 3.62 | 7.96                        | ns   |

| Input/Output Pin Capacitance             | C <sub>IO_PIN</sub>                                | $T_{\rm J} = 25~^{\circ}{\rm C}$ $C_{\rm IO\_PIN} = C_{\rm GPIO} + C_{\rm PAD} + C_{\rm PIN}$ |                                                    | 3.6  |                             | pF   |

| $V_{DDIO} = 1.8 \text{ V } \pm 5\%$      | <del>,                                      </del> | T                                                                                             | <del>,                                      </del> | ı    | <del></del>                 |      |

| V <sub>DDIO</sub> Leakage Current        | I <sub>DDIO_LKG</sub>                              |                                                                                               |                                                    | 0.28 | 4.37                        | μΑ   |

| HIGH-level Input Voltage                 | V <sub>IH</sub>                                    | Logic Input HIGH                                                                              | 0.65 x<br>V <sub>DDIO</sub>                        | -    | 2.75 V                      | V    |

| LOW-level Input Voltage                  | V <sub>IL</sub>                                    | Logic Input LOW                                                                               | GND -<br>0.3                                       | -    | 0.35 x<br>V <sub>DDIO</sub> | V    |

|                                          |                                                    | Push-pull 1x, I <sub>OH</sub> = 0.5 mA                                                        | 0.982 x<br>V <sub>DDIO</sub>                       |      |                             | V    |

| HIGH-level Output Voltage                | V <sub>ОН</sub>                                    | Push-pull 2x, I <sub>OH</sub> = 1 mA                                                          | 0.965 x<br>V <sub>DDIO</sub>                       |      |                             | V    |

|                                          |                                                    | Push-pull 1x, I <sub>OH</sub> = 2 mA                                                          | 0.928 x<br>V <sub>DDIO</sub>                       |      |                             | V    |

|                                          |                                                    | Push-pull 2x, I <sub>OH</sub> = 0.5 mA                                                        | 0.991 x<br>V <sub>DDIO</sub>                       |      |                             | V    |

|                                          |                                                    | Push-pull 2x, I <sub>OH</sub> = 1 mA                                                          | 0.982 x<br>V <sub>DDIO</sub>                       |      |                             | V    |

|                                          |                                                    | Push-pull 2x, I <sub>OH</sub> = 2 mA                                                          | 0.963x<br>V <sub>DDIO</sub>                        |      |                             | V    |

|                                          |                                                    | Push-pull 2x, I <sub>OL</sub> = 0.5 mA                                                        |                                                    |      | 0.029                       | V    |

|                                          |                                                    | Push-pull 1x, I <sub>OL</sub> = 1 mA                                                          |                                                    |      | 0.059                       | V    |

|                                          |                                                    | Push-pull 1x, I <sub>OL</sub> = 2 mA                                                          |                                                    |      | 0.12                        | V    |

| 1000                                     | .,                                                 | Push-pull 2x, I <sub>OL</sub> = 0.5 mA                                                        |                                                    |      | 0.015                       | V    |

| LOW-level Output Voltage                 | V <sub>OL</sub>                                    | Push-pull 2x, I <sub>OL</sub> = 1 mA                                                          |                                                    |      | 0.03                        | V    |

|                                          |                                                    | Push-pull 2x, I <sub>OL</sub> = 2 mA                                                          |                                                    |      | 0.061                       | V    |

|                                          |                                                    | Open-drain 1x, I <sub>OL</sub> = 2 mA                                                         |                                                    |      | 0.121                       | V    |

|                                          |                                                    | Open-drain 2x. I <sub>OL</sub> = 2 mA                                                         |                                                    |      | 0.061                       | V    |

|                                          | _                                                  | Push-pull 1x, V <sub>OH</sub> = 1.35 V                                                        | 3.0                                                |      |                             | mA   |

| HIGH-level Output Current                | l <sub>он</sub>                                    | Push-pull 2x, V <sub>OH</sub> = 1.35 V                                                        | 9.99                                               |      |                             | mA   |

|                                          |                                                    | Push-pull 1x, V <sub>OL</sub> = 0.45 V                                                        | 4.0                                                |      |                             | mA   |

|                                          |                                                    | Push-pull 2x, V <sub>OL</sub> = 0.45 V                                                        | 11.9                                               |      |                             | mA   |

| LOW-level Output Current                 | l <sub>OL</sub>                                    | Open-drain 1x, V <sub>OL</sub> = 0.45 V                                                       | 6.1                                                |      |                             | mA   |

|                                          |                                                    | Open-drain 2x, V <sub>OL</sub> = 0.45 V                                                       | 11.9                                               |      |                             | mA   |

|                                          | F <sub>IO_MAX</sub>                                | Push-pull 1x, C <sub>LOAD</sub> = 10 pF                                                       | 50                                                 | 110  | 180                         | MHz  |

| Parameter                         | Symbol                | Condition                               | Min                          | Тур  | Max                         | Unit |

|-----------------------------------|-----------------------|-----------------------------------------|------------------------------|------|-----------------------------|------|

| Max GPIO output frequency         |                       | Push-pull 2x, C <sub>LOAD</sub> = 10 pF | 120                          | 195  | 280                         | MHz  |

| V <sub>DDIO</sub> = 2.5 V ±10%    |                       | I.                                      |                              |      | <u> </u>                    | 1    |

| V <sub>DDIO</sub> Leakage Current | I <sub>DDIO_LKG</sub> |                                         |                              | 1.44 | 6.93                        | μA   |

| HIGH-level Input Voltage          | V <sub>IH</sub>       | Logic Input HIGH                        | 0.65 x<br>V <sub>DDIO</sub>  | -    | 2.75                        | V    |

| LOW-level Input Voltage           | V <sub>IL</sub>       | Logic Input LOW                         | GND -<br>0.3                 |      | 0.35 x<br>V <sub>DDIO</sub> | V    |

|                                   |                       | Push-pull 1x, I <sub>OH</sub> = 0.5 mA  | 0.989 x<br>V <sub>DDIO</sub> |      |                             | V    |

|                                   |                       | Push-pull 1x, I <sub>OH</sub> = 1 mA    | 0.979x<br>V <sub>DDIO</sub>  |      |                             | V    |

| HIGH-level Output Voltage         | V                     | Push-pull 1x, I <sub>OH</sub> = 2 mA    | 0.958 x<br>V <sub>DDIO</sub> |      |                             | V    |

|                                   | V <sub>OH</sub>       | Push-pull 2x, I <sub>OH</sub> = 0.5 mA  | 0.994 x<br>V <sub>DDIO</sub> |      |                             | ٧    |

|                                   |                       | Push-pull 2x, I <sub>OH</sub> = 1 mA    | 0.989 x<br>V <sub>DDIO</sub> |      |                             | V    |

|                                   |                       | Push-pull 2x, I <sub>OH</sub> = 2 mA    | 0.978 x<br>V <sub>DDIO</sub> |      |                             | V    |

|                                   |                       | Push-pull 2x, I <sub>OH</sub> = 0.5 mA  |                              |      | 0.023                       | V    |

|                                   |                       | Push-pull 1x, I <sub>OL</sub> = 1 mA    |                              |      | 0.046                       | V    |

|                                   |                       | Push-pull 1x, I <sub>OH</sub> = 2 mA    |                              |      | 0.092                       | V    |

| 1000                              | .,                    | Push-pull 2x, I <sub>OH</sub> = 0.5 mA  |                              |      | 0.012                       | V    |

| LOW-level Output Voltage          | V <sub>OL</sub>       | Push-pull 2x, I <sub>OH</sub> = 1 mA    |                              |      | 0.024                       | V    |

|                                   |                       | Push-pull 2x, I <sub>OH</sub> = 2 mA    |                              |      | 0.047                       | V    |

|                                   |                       | Open-drain 1x, I <sub>OL</sub> = 2 mA   |                              |      | 0.092                       | V    |

|                                   |                       | Open-drain 2x, I <sub>OL</sub> = 2 mA   |                              |      | 0.047                       | V    |

|                                   |                       | Push-pull 1x, V <sub>OH</sub> = 1.7 V   | 10                           |      |                             | mA   |

| HIGH-level Output Current         | I <sub>OH</sub>       | Push-pull 2x, V <sub>OH</sub> = 1.7 V   | 18.9                         |      |                             | mA   |

|                                   |                       | Push-pull 1x, V <sub>OL</sub> = 0.7 V   | 11.9                         |      |                             | mA   |

| LOW-level Output Current          |                       | Push-pull 2x, V <sub>OL</sub> = 0.7 V   | 23.2                         |      |                             | mA   |

|                                   | I <sub>OL</sub>       | Open-drain 1x, V <sub>OL</sub> = 0.7 V  | 11.9                         |      |                             | mA   |

|                                   |                       | Open-drain 2x, V <sub>OL</sub> = 0.7 V  | 23.2                         |      |                             | mA   |

| W 000 : : -                       | _                     | Push-pull 1x, C <sub>LOAD</sub> = 10 pF | 75                           | 160  | 250                         | MHz  |

| Max GPIO output Frequency         | F <sub>IO_MAX</sub>   | Push-pull 2x, C <sub>LOAD</sub> = 10 pF | 165                          | 235  | 300                         | MHz  |

# 3.4 IO Pull-up Resistance for a Pull-up

$T_A$  = -40 °C to +85 °C,  $V_{DDIO}$  = 1.71 V to 2.75 V,  $V_{DDC}$  = 1.1 V ±5%, unless otherwise specified.

| Parameter                              | Symbol           | Condition                            | Min | Тур | Max | Unit |

|----------------------------------------|------------------|--------------------------------------|-----|-----|-----|------|

| Pull-up 1x (single resistor)           | 0                | V <sub>DDIO</sub> = 1.71 V to 1.98 V | 124 | 190 | 256 | kΩ   |

|                                        | R <sub>PU1</sub> | V <sub>DDIO</sub> = 2.25 V to 2.75 V | 79  | 119 | 165 | kΩ   |

| Pull-up 2x (two resistors in parallel) | R <sub>PU2</sub> | V <sub>DDIO</sub> = 1.71 V to 1.98 V | 64  | 95  | 127 | kΩ   |

|                                        |                  | V <sub>DDIO</sub> = 2.25 V to 2.75 V | 40  | 59  | 82  | kΩ   |

# 3.5 PLL Specifications

$T_A = -40$  °C to +85 °C,  $V_{DDIO} = 1.71$  V to 2.75 V,  $V_{DDC} = 1.1 \pm 5\%$ , unless otherwise specified.

| Parameter                                | Symbol                | Conditions                                                   | Min          | Тур           | Max                  | Unit   |

|------------------------------------------|-----------------------|--------------------------------------------------------------|--------------|---------------|----------------------|--------|

| Input Clock Frequency                    | f <sub>IN</sub>       | _                                                            | 5            |               | 500                  | MHz    |

| Output Clock Frequency                   | f <sub>OUT</sub>      | -                                                            | 10           |               | 2000 [1]             | MHz    |

| VCO Frequency                            | f <sub>VCO</sub>      | -                                                            | 500          |               | 2000                 | MHz    |

| Output Duty Cycle                        | f <sub>PLL_DC</sub>   | f <sub>OUT</sub> VCO at any Frequency                        | 44.2         | 48.9          | 51.6                 | %      |

| Number of PFD Cycles for PLL to Lock     |                       | Lock is defined as no cycle slips for 256 consecutive cycles |              | 600           | 900                  | cycles |

| PFD Frequency Range                      | f <sub>PFD</sub>      |                                                              | 5            |               | f <sub>VCO</sub> /16 | MHz    |

| Peak to Peak Period Jitter               | t <sub>JIT_10.2</sub> | f <sub>OUT</sub> = 10.2 MHz                                  |              | 210           | 681                  | ps     |

| Peak to Peak Period Jitter               | t <sub>JIT_55.6</sub> | f <sub>OUT</sub> = 55.6 MHz                                  |              | 106           | 307                  | ps     |

| Peak to Peak Period Jitter               | t <sub>JIT_100</sub>  | f <sub>OUT</sub> = 100 MHz                                   |              | 75            | 232                  | ps     |

| Peak to Peak Period Jitter               | t <sub>JIT_115</sub>  | f <sub>OUT</sub> = 125 MHz                                   |              | 84            | 363                  | ps     |

| [1] The PLL block can support this range | but in practic        | ce the frequency would be much lowe                          | er due to pe | ripheral logi | c limitations        | i.     |

# 3.6 Oscillator Specifications

$V_{DDIO}$  = 2.5 V ± 10%,  $V_{DDC}$  = 1.1 V ±5%, unless otherwise specified.

| Parameter                    | Symbol                  | Conditions                       | Min    | Тур    | Max    | Unit |

|------------------------------|-------------------------|----------------------------------|--------|--------|--------|------|

| Output Frequency             | f <sub>OSC_50</sub>     | T <sub>J</sub> = 25 °C           | 46.752 | 50.025 | 52.549 |      |

|                              |                         | T <sub>J</sub> = -40 °C to 85 °C | 43.495 | 50.025 | 54.110 | MHz  |

| Output Duty Cycle            | f <sub>OSC_DC_50</sub>  | T <sub>J</sub> = -40 °C to 85 °C | 35.1   | 48.2   | 61.2   | %    |

| Latin Continue Time          | f <sub>OSC_SET_50</sub> | T <sub>J</sub> = 25 °C           | 0.59   | 105    | 182    |      |

| Initial Setting Time         |                         | T <sub>J</sub> = -40 °C to 85 °C | 0.46   | 105    | 213    | ms   |

| Period Jitter (peak-to-peak) | T <sub>PJIT_50</sub>    | T <sub>J</sub> = 25 °C           | 0.1    | 0.14   | 0.22   | ns   |

|                              |                         | T <sub>J</sub> = -40 °C to 85 °C | 0.0    | 0.14   | 0.28   | ns   |

# 3.7 POR Specifications

$T_A$  = -40 °C to +85 °C,  $V_{DDIO}$  = 2.5 V ±10%,  $V_{DDC}$  = 1.1 V ±5%, unless otherwise specified.

| Parameter                                       | Symbol                       | Conditions                                                         | Min   | Тур   | Max   | Unit |

|-------------------------------------------------|------------------------------|--------------------------------------------------------------------|-------|-------|-------|------|

| V <sub>DDC</sub> power-on-reset delay           | T <sub>VDDC_POR_DELAY</sub>  | $V_{DDC}$ ramp = 300 $\mu$ s10 ms,<br>$V_{DDIO}$ = 2.5 V $\pm$ 10% | 0.921 | 1.446 | 1.888 | ms   |

| V <sub>DDIO</sub> power-on-reset delay          | T <sub>VDDIO_POR_DELAY</sub> | $V_{DDIO}$ ramp = 300 $\mu$ s10 ms,<br>$V_{DDC}$ = 1.1 $V$         | 0.829 | 1.371 | 1.872 | ms   |

| V <sub>DDC</sub> power-on threshold             | V <sub>POR_VDDC_ON</sub>     | V <sub>DDIO</sub> = 2.5 V                                          | 0.887 | 0.906 | 0.98  | V    |

| V <sub>DDC</sub> power-off threshold            | V <sub>POR_VDDC_OFF</sub>    | V <sub>DDIO</sub> = 2.5 V                                          | 0.328 | 0.693 | 0.95  | V    |

| V <sub>DDIO</sub> power-on threshold            | V <sub>POR_VDDIO_ON</sub>    | V <sub>DDC</sub> = 1.1 V                                           | 1.595 | 1.628 | 1.67  | V    |

| V <sub>DDIO</sub> power-off threshold           | V <sub>POR_VDDIO_OFF</sub>   | V <sub>DDC</sub> = 1.1 V                                           | 0.91  | 1.109 | 1.293 | V    |

| V <sub>DDC</sub> /V <sub>DDIO</sub> Supply ramp | T <sub>POR_VRAMP</sub>       | $V_{DDC} = 0$ to 1.1 V ±5%,<br>$V_{DDIO} = 0$ to (1.71 V2.75 V),   | 0.3   |       | 10    | ms   |

# 3.8 Estimated Current Consumption Values of Supporting Blocks

$T_A = +25$  °C,  $V_{DDIO} = 2.5$  V  $\pm 10\%$ ,  $V_{DDC} = 1.1$  V  $\pm 5\%$ , unless otherwise specified.

| Parameter                | Symbol           | Note                                                                                                                           | Тур    | Unit |  |  |  |

|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|--------|------|--|--|--|

|                          |                  | OSC 50 MHz                                                                                                                     | 422    | μA   |  |  |  |

|                          |                  | PLL Active Current Consumption (f <sub>VCO</sub> = 500 MHz)                                                                    | 610    | μΑ   |  |  |  |

|                          |                  | PLL Active Current Consumption (f <sub>VCO</sub> = 2000 MHz)                                                                   | 2820   | μΑ   |  |  |  |

| Current                  | I <sub>DDC</sub> | Single BRAM Block Quiescent Power (BRAM_PG = LOW)                                                                              | 5.76   | μΑ   |  |  |  |

|                          |                  | BRAM Slice Read (RCLK = 40 MHz)                                                                                                | 113.87 | μΑ   |  |  |  |

|                          |                  | BRAM Slice Write (RCLK = 40 MHz)                                                                                               | 92.922 | μΑ   |  |  |  |

|                          |                  | Average I <sub>VDDC</sub> Current consumption during FPGA Core with 90+% utilization @ 100 MHz (V <sub>DDIO</sub> = 1.8 V) [1] | 47     | mA   |  |  |  |

| [1] Device Utilization i |                  |                                                                                                                                |        |      |  |  |  |

# 3.9 Configuration Interface Timing

$T_A$  = -40 °C to +85 °C,  $V_{DDIO}$  = 2.5 V ±10%,  $V_{DDC}$  = 1.1 V ±5%, unless otherwise specified.

|                                                                                 |                       | •                                         |     |      |      |      |

|---------------------------------------------------------------------------------|-----------------------|-------------------------------------------|-----|------|------|------|

| Parameter                                                                       | Symbol                | Conditions                                | Min | Тур  | Max  | Unit |

| Input/Output                                                                    |                       |                                           |     |      |      |      |

| Configuration Time. Time from PWR (nRST). Asserted HIGH to Device configuration | t <sub>CONF_OTP</sub> | OTP Configuration Mode                    |     | 19   |      | ms   |

|                                                                                 | t <sub>CONF_MCU</sub> | MCU Configuration mode, FCLK_SPI = 16 MHz |     | 25   | 1    | ms   |

| ready                                                                           | t <sub>CONF_SPI</sub> | SPI Configuration Mode                    |     | 33   |      | ms   |

| Master Configuration (Config from SPI Fla                                       | sh Memory)            |                                           |     |      |      |      |

| Master Clock Frequency during Configuration                                     | f <sub>CLKM</sub>     | V <sub>DDIO</sub> = 1.71 V to 2.75 V      |     | 12.5 | 13.4 | MHz  |

| Master Clock Duty Cycle during Configuration                                    | CLKM <sub>DC</sub>    | V <sub>DDIO</sub> = 1.71 V to 2.75 V      | 40  | 50   | 60   | %    |

| Parameter                                                                               | Symbol                    | Conditions                                                  | Min | Тур | Max  | Unit |

|-----------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------|-----|-----|------|------|

| Delay from PWR (nRST) to SPI_SSn<br>Falling Edge                                        | t <sub>PORT_MCLK</sub>    |                                                             |     | 205 |      | μs   |

| Data In Setup Time before Clock Rising Edge                                             | t <sub>M_DI_SU</sub>      | V <sub>DDIO</sub> = 1.71 V to 2.75 V                        | 35  |     |      | ns   |

| Data In Hold Time after Clock Rising Edge                                               | t <sub>M_DI_HD</sub>      | $V_{DDIO} = 1.71 \text{ V to } 2.75 \text{ V}$              | 12  |     |      | ns   |

| Clock Rising Faling Edge to Valid Output Delay                                          | $T_{M\_CLK\_VOD}$         | V <sub>DDIO</sub> = 1.71 V to 2.75 V                        | 10  |     |      | ns   |

| SPI_SSn High Time after Wake-up<br>Command before sending the next SPI<br>FLASH command | T <sub>M_SSN_WKUP_H</sub> | V <sub>DDIO</sub> = 1.71 V to 2.75 V                        | 275 |     |      | μs   |

| SPI_SSn Setup Time before Clock Falling Edge                                            | t <sub>M_SSN_SU</sub>     | V <sub>DDIO</sub> = 1.71 V to 2.75 V                        | 75  |     |      | ns   |

| SPI_SSn Hold Time after Clock Rising Edge                                               | t <sub>M_SSN_HD</sub>     | $V_{DDIO} = 1.71 \text{ V to } 2.75 \text{ V}$              | 6   |     |      | ns   |

| Slave Configuration (Config from MCU)                                                   |                           |                                                             |     |     |      |      |

| Max Slave Clock Frequency                                                               | f <sub>CLKS_MAX</sub>     | $V_{DDIO} = 1.8 \text{ V}, V_{DDC} = 1.1 \text{ V} \pm 5\%$ |     |     | 16   | MHz  |

| Data In Setup Time before Clock Rising Edge                                             | t <sub>S_DI_SU</sub>      | V <sub>DDIO</sub> = 1.71 V to 2.75 V                        | 5   |     | -    | ns   |

| Data In Hold Time after Clock Rising Edge                                               | t <sub>S_DI_HD</sub>      | V <sub>DDIO</sub> = 1.71 V to 2.75 V                        | 15  | 1   | -    | ns   |

| SPI_SSn Setup Time before Clock Falling Edge                                            | T <sub>S_SSN_SU</sub>     | V <sub>DDIO</sub> = 1.71 V to 2.75 V                        | 60  |     | -    | ns   |

| SPI_SSn Hold Time after Clock Rising Edge                                               | T <sub>S_SSN_HD</sub>     | V <sub>DDIO</sub> = 1.71 V to 2.75 V                        | 10  |     |      | ns   |

| SPI_SSn High Time (between SigWord and Bitstream)                                       | T <sub>S_SSN_H</sub>      | V <sub>DDIO</sub> = 1.71 V to 2.75 V                        | 3   |     |      | μs   |

| Min Clock Pulse HIGH                                                                    | T <sub>S_CLKH</sub>       | V <sub>DDIO</sub> = 1.71 V to 2.75 V                        | 10  |     |      | ns   |

| Min Clock Pulse LOW                                                                     | T <sub>S_CLKL</sub>       | V <sub>DDIO</sub> = 1.71 V to 2.75 V                        | 10  |     |      | ns   |

| Typical Operation                                                                       |                           |                                                             |     |     |      |      |

| Maximum IO Fraguency                                                                    | f <sub>IO</sub>           | V <sub>DDIO</sub> =1.8 V                                    | 153 | 230 | 365  | MHz  |

| Maximum IO Frequency                                                                    |                           | $V_{DDIO} = 2.5 \text{ V}$                                  | 133 |     |      | MHz  |

|                                                                                         |                           | T <sub>A</sub> = 25 °C                                      |     |     | 2793 | MHz  |

| Global Buffer Frequency                                                                 | f <sub>GB_MAX</sub>       | T <sub>A</sub> = -40 °C                                     |     |     | 2793 | MHz  |

# 3.10 Supply Current

T = -40 °C to +85 °C,  $V_{DDIO}$  = 1.71 V to 2.75 V,  $V_{DDC}$  = 1.1 V ±5 %.

| Parameter                                                                                                                            | Symbol                     | Min | Тур   | Max    | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|-------|--------|------|

| V <sub>DDC</sub> power supply current, device in sleep mode (PWR = 1, EN = 0, BRAM_PG = HIGH (power gated))                          | $I_{	extsf{DDC\_RET}}$     |     | 14    | 171    | μΑ   |

| V <sub>DDC</sub> power supply current, device in sleep mode (PWR = 1, EN = 0, BRAM_PG = LOW (data retained))                         | I <sub>DDC_RET_BRAM</sub>  | 1   | 20.52 | 335    | μΑ   |

| $V_{DDC}$ power supply current, device in functional mode (PWR = 1, EN = 1, BRAM_PG = HIGH (power gated), FPGA core in static state) | I <sub>DDC_FUNC_STAT</sub> | I   | 52.27 | 1100   | μΑ   |

| V <sub>DDC</sub> power supply current, device in reset state                                                                         | I <sub>DDC_RST</sub>       |     | 14.13 | 169.11 | μΑ   |

| (PWR = 0, EN = X)                                                                                          |                               |        |       |       |    |

|------------------------------------------------------------------------------------------------------------|-------------------------------|--------|-------|-------|----|

| $V_{\text{DDIO}}$ power supply current, device in reset state (PWR = 0, EN = X, GPIOs are retained = HIGH) | $I_{	exttt{DDIO}\_	ext{RST}}$ |        | 0.862 | 6.8   | μΑ |

| Peak (Inrush) $I_{DDIO}$ Current during Device RESET to On-State Transition (nRESET (PWR) = LOW to HIGH)   | Iddio_pwr_pk                  | 0.072  | 1.088 | 1.820 | mA |

| Peak (Inrush) $I_{DDC}$ Current during Device RESET to On-State Transition (nRESET (PWR) = LOW to HIGH)    | $I_{DDC\_PWR\_PK}$            | 3.2624 | 13.13 | 23.54 | mA |

| V <sub>DDC</sub> Power Supply Peak Current during startup and configuration                                | I <sub>DDC_PEAK</sub>         |        |       | 8.45  | mA |

| $\ensuremath{V_{\text{DDIO}}}$ Power Supply Peak Current during startup and configuration                  | I <sub>DDIO_PEAK</sub>        | -      | -     | 5.42  | mA |

### 3.11 BRAM Characteristics

$T_A = -40$  °C to +85 °C,  $V_{DDIO} = 1.71$  V to 2.75 V,  $V_{DDC} = 1.1$  V  $\pm 5\%$ , unless otherwise specified.

Note: BRAM Setup and Hold parameters are simulated results at the BRAM boundary.

| Parameter                                    | Symbol                 | Min | Тур   | Max  | Unit |

|----------------------------------------------|------------------------|-----|-------|------|------|

| Read Max Frequency                           | f <sub>RD_MAX</sub>    |     |       | 45   | MHz  |

| Read Max Frequency, T <sub>A</sub> = +25 °C  | f <sub>RD_MAX_25</sub> |     | 86.9  |      | MHz  |

| Write Max Frequency                          | f <sub>WR_MAX</sub>    |     |       | 63.9 | MHz  |

| Write Max Frequency, T <sub>A</sub> = +25 °C | f <sub>WR_MAX_25</sub> |     | 123.5 |      | MHz  |

# 3.12 PWR (nRST) and EN (nSLEEP) Specifications

$T_A = -40$  °C to +85 °C,  $V_{DDIO} = 1.71$  V to 2.75 V,  $V_{DDC} = 1.1$  V  $\pm 5\%$ , unless otherwise specified.

| Parameter                                                                                                                                        | Symbol                          | Min | Тур   | Max   | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----|-------|-------|------|

| PWR (nRST) = (HIGH to LOW) transition to GPO Retention (or Hi-Z) state delay (when OSC_EN = 1 in Functional mode [1][2])  T_NRST_GPO_RST_RET_DLY |                                 |     | 292   | 376   | ns   |

| Note: Same is for IOB int_rst HIGH.                                                                                                              |                                 |     |       |       |      |

| PWR (nRST) = (LOW to HIGH) transition to Power-on State (start of configuration) delay                                                           | T <sub>NRST_EX</sub>            | 1   | 215.5 | 310.0 | μs   |

| PWR (nRST) = (HIGH to LOW) transition to getting in Device-off State delay                                                                       | T <sub>NRST_ENT</sub>           | 500 |       |       | μs   |

| Note: During this time PWR (nRST) should be held LOW                                                                                             |                                 |     |       |       |      |

| EN (nSLEEP) = (HIGH to LOW) transition to GPO Retention state delay (OSC_EN = 1 in Functional mode [1][2])                                       | T <sub>NSLEEP_GPO_RET_DLY</sub> |     | 40    | 157   | ns   |

| Note: Same for IOB sleep_start HIGH                                                                                                              |                                 |     |       |       |      |

| EN (nSLEEP) = (LOW to HIGH) transition to Functional State                                                                                       | T <sub>NSLEEP_EX</sub>          |     | 149   | 225   | μs   |

| PWR (nRST) = (HIGH to LOW) transition to getting into Retention State delay  Note: During this time EN (nSLEEP) should be held LOW               | T <sub>NSLEEP_ENT</sub>         | 500 |       |       | μs   |

| Max delay for user-clocks to be stopped before transition to sleep or reset                                                                      | Tusr_clk_stop_max_dly           |     |       | 5     | μs   |

<sup>[1]</sup> In the case of Functional mode OSC\_EN = 0 - these parameters should be increased by  $t_{OSC\_SET\_50}$ .

$$\begin{split} T_{NSLEEP\_CYC} & \text{ (EN (nSLEEP) pin cycle time)} = T_{NSLEEP\_ENT} + T_{NSLEEP\_EX;} \\ & T_{NRST\_CYC} & \text{ (PWR (nRST) cycle time)} = T_{NRST\_ENT} + T_{NRST\_EX}. \end{split}$$

<sup>[2]</sup> In the case of using slow external clock or Logic-as-Clock – these times would be increased by 2 periods of slowest clock up to T<sub>USR\_CLK\_STOP\_MAX\_DLY</sub> (after that delay all user clocks would be forced to LOW anyway.

Refer to Section 7 Power-up Sequence timing diagram:

# 3.13 Typical Building Block Performance

### 3.13.1 Pin-to-Pin Performance [1].[2]

| Function | Timing | Unit |

|----------|--------|------|

| 4:1 MUX  | 19.0   | ns   |

| 16:1 MUX | 25.5   | ns   |

<sup>[1]</sup> Exact performance may vary with device and tool version. The ForgeFPGA Workshop Software tool uses internal parameters that have been characterized but are not tested on every device.

## 3.13.2 Register-to-Register Performance (LVCMOS18) [1],[2]

| Function                     | Timing | Unit |

|------------------------------|--------|------|

| 16-bit Counter               | 79     | MHz  |

| 32-bit Counter               | 56     | MHz  |

| 256 x 8 Pseudo Dual Port RAM | 48     | MHz  |

| DFF to DFF                   | 212    | MHz  |

| DFF to LUT5 to DFF           | 182    | MHz  |

<sup>[1]</sup> Exact performance may vary with device and tool version. The ForgeFPGA Workshop Software tool uses internal parameters that have been characterized but are not tested on every device.

<sup>[2]</sup> Under typical operating conditions.

<sup>[2]</sup> Under typical operating conditions.

# 4. General Purpose Input Output (GPIO) Buffers

## 4.1 Digital IO

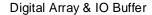

The SLG47910 includes digital GPIO pins with the structure shown in Figure 3.

Figure 3. GPIO Buffers

The SLG47910 contains 24 pins. There are 19 Digital GPIO pins. The remaining pins are VDDC, VDDIO, GND, and input only pins for EN and PWR. The elements labelled "Reg" in Figure 3 are configuration registers.

The following configuration options are available for each GPIO pin:

- Input

- Output, 1x Drive Push-pull

- Output, 2x Drive Push-pull

- Output, 1x Drive Open-drain

- Output, 2x Drive Open-drain.

The GPIO has four registered signals (2x\_PullUp\_En, 1x\_PullUp\_En, OpenDrain\_En, and 2x\_Buffer\_En) that control the drive strength as shown in Table 7. The table below represents the bits from the NVM in the software.

**Table 7. GPIO Functionality**

| 2x_Buffer_En | OpenDrain_En | 1x_PullUp_En | 2x_PullUp_En | GPIO Description           |

|--------------|--------------|--------------|--------------|----------------------------|

| 0            | 0            | 0            | 0            | 1x Push-pull               |

| 0            | 0            | 1            | X            | 1x Push-pull with Pull-up  |

| 0            | 1            | 0            | 0            | 1x Open-drain              |

| 0            | 1            | 1            | Х            | 1x Open-drain with Pull-up |

| 1            | 0            | 0            | 0            | 2x Push-pull               |

| 1            | 1            | 0            | 0            | 2x Open-drain              |

| 1            | 1            | 1            | Х            | 2x Open-drain with Pull-up |

All Input and Output options may additionally include a resistive pull-up option. The pull-up resistor values are shown in Section 3.4 IO Pull-up Resistance for a Pull-up. The values shown are dependent on V<sub>DDIO</sub> and cover process and temperature. The R Minimum, R Typical and R Maximum cover the ±10% variation of V<sub>DDIO</sub>. In Figure 3, we have two Pull-up resistors, so the resistance value from Section 3.4 IO Pull-up Resistance for a Pull-up will be divided by 2 for each resistor in parallel.

Output configuration (type and drive strength) and pull-up option are not dynamically changeable after FPGA configuration has been loaded. Output enable and digital output can be changed dynamically. Prior to release of the POR signal all GPIO are Hi-Z.

## 5. FPGA Core

### 5.1 Introduction

The FPGA Core is composed of an array of 140 Configurable Logic Blocks (CLB). At its lowest level, a 5-bit Look-up Table (LUT) is used to implement an arbitrary logic function with up to five inputs and one output. Two 5-bit LUTs are arranged in a pair, yielding a 6-bit LUT with two outputs. Each output of each of the 5-bit LUTs also has a D Flip-flop. The array of CLBs is surrounded on each side with IO Buffers (140 IOBs) to make the signal connections external to the FPGA Core resources.

Considering the total number of 140 CLB blocks in the SLG47910 with eight 5-bit LUTs (four 6-bit LUTs) with eight FFs each, the total logic count is 1120 5-bit LUTs (or in other terms 560 6-bit LUTs) and 1120 FFs.

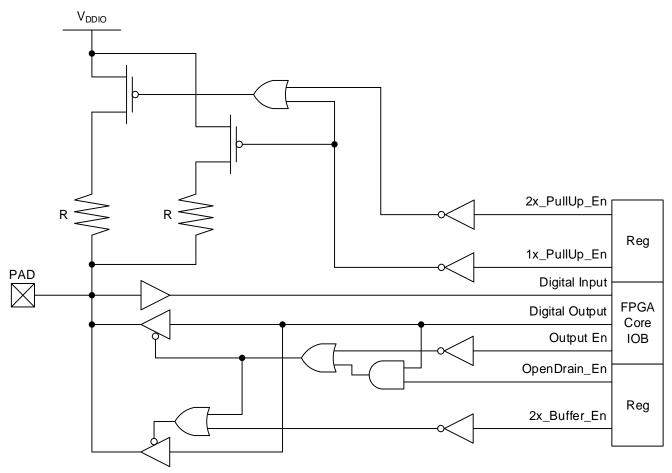

## 5.2 FPGA Core Composition

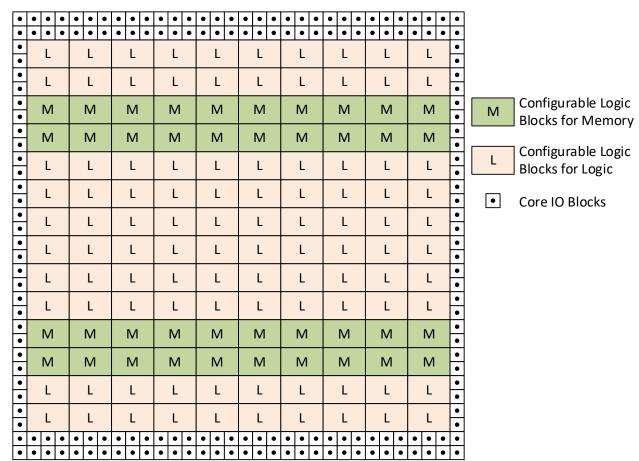

From the FPGA Core's 140 total CLBs, 100 of them are Configurable Logic Blocks for Logic (CLBLs) and 40 are Configurable Logic Blocks for Memory (CLBMs). Figure 4 below shows the manner that these CLBs are tiled across the FPGA core in each tile.

Figure 4. FPGA Core

# 5.3 Configurable Logic Blocks