# RENESAS

### ISL28022

#### Precision Digital Power Monitor

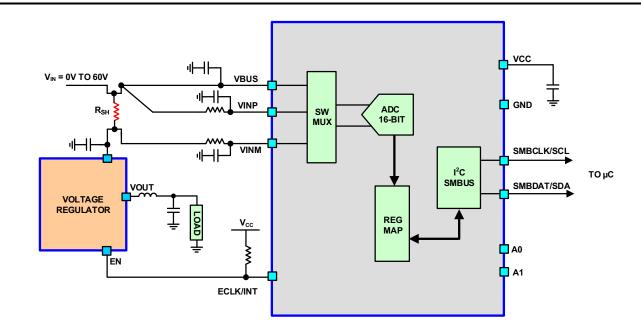

The <u>ISL28022</u> is a bidirectional high-side and low-side digital current sense and voltage monitor with serial interface. The device monitors current and voltage and provides the results digitally along with calculated power. The ISL28022 provides tight accuracy of less than 0.3% for both voltage and current monitoring over the entire input range. The digital power monitor has configurable fault thresholds and measurable ADC gain ranges.

The ISL28022 handles common-mode input voltage ranging from OV to 60V. The wide range permits the device to handle telecom, automotive and industrial applications with minimal external circuitry. Both high- and low-side ground sensing applications are easily handled with the flexible architecture.

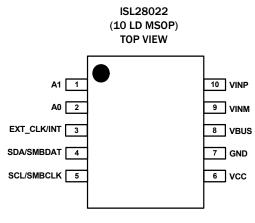

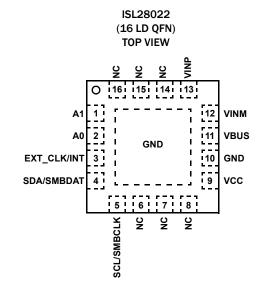

The ISL28022 consumes an average current of just  $700\mu$ A and is available in a 10 Ld MSOP package. The ISL28022 is also offered in a space saving 16 Ld QFN package. The part operates across the extended temperature range from -40°C to +125°C.

## **Related Literature**

- AN1955, "Design Ideas for Intersil Digital Power Monitors"

- <u>AN1875</u>, "ISL28022 Digital Power Monitor Evaluation Kit (ISL28022EVKIT1Z)

- AN1811, "ISL28022 Digital Power Monitor 8 Site Evaluation Kit"

# DATASHEET

FN8386 Rev 8.00 February 4, 2016

### **Features**

| ٠ | Bus voltage sense range | OV to 60V |

|---|-------------------------|-----------|

| • | Bus voltage sense range | 0V to 60V |

- 16-bit ∑∆ADC monitors current and voltage

- Handles negative system voltage

- Overvoltage/undervoltage and current fault monitoring

- I<sup>2</sup>C/SMBus interface

### **Applications**

- Routers and servers

- DC/DC, AC/DC converters

- Battery management/charging

- · Automotive power

- Power distribution

- · Medical and test equipment

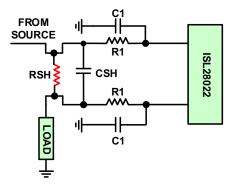

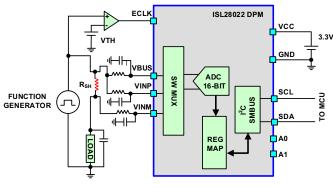

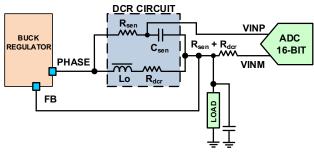

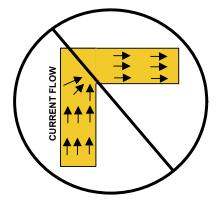

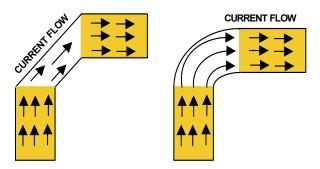

FIGURE 1. TYPICAL APPLICATION

## **Table of Contents**

| Block Diagram                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ordering Information                                                                                                                                                                      |

| Pin Configurations                                                                                                                                                                        |

| Pin Descriptions                                                                                                                                                                          |

| Absolute Maximum Ratings                                                                                                                                                                  |

| Thermal Information                                                                                                                                                                       |

| Recommended Operating Conditions                                                                                                                                                          |

| Electrical Specifications                                                                                                                                                                 |

| Typical Performance Curves                                                                                                                                                                |

| Functional Description                                                                                                                                                                    |

| Overview13Detailed Description13Functional Pin Descriptions13Register Descriptions14                                                                                                      |

| Serial Interface                                                                                                                                                                          |

| Protocol Conventions19SMBus Support19Device Addressing21Write Operation22Read Operation22Broadcast Addressing22I <sup>2</sup> C Clock Speed22                                             |

| Signal Integrity                                                                                                                                                                          |

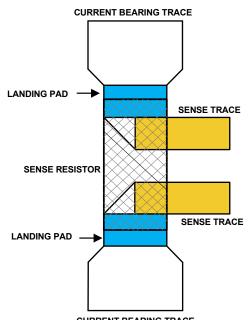

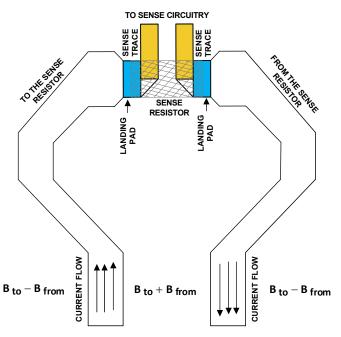

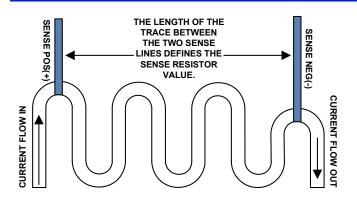

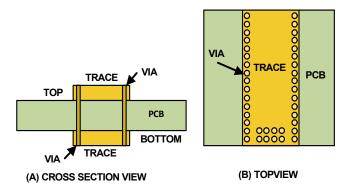

| Measurement Stability vs Acquisition Time23Fast Transients23External Clock24Over-Ranging24Shunt Resistor Selection24Lossless Current Sensing (DCR)26Layout26A Trace as a Sense Resistor28 |

| Revision History                                                                                                                                                                          |

| About Intersil                                                                                                                                                                            |

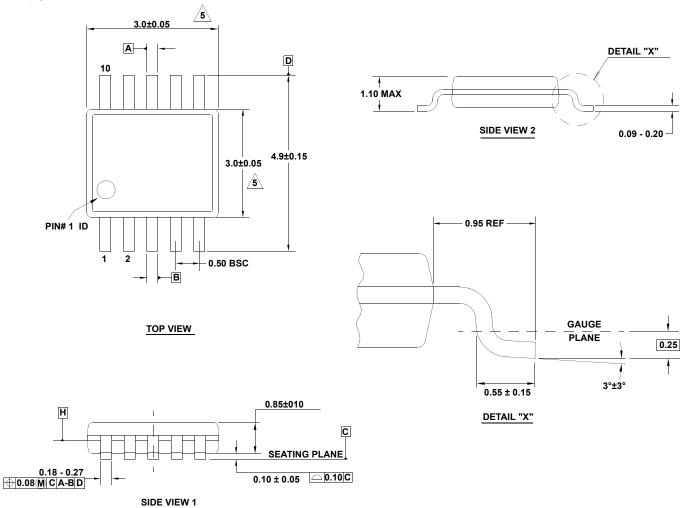

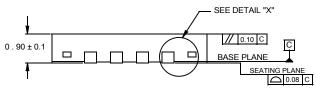

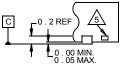

| Package Outline Drawing                                                                                                                                                                   |

| M10.118                                                                                                                                                                                   |

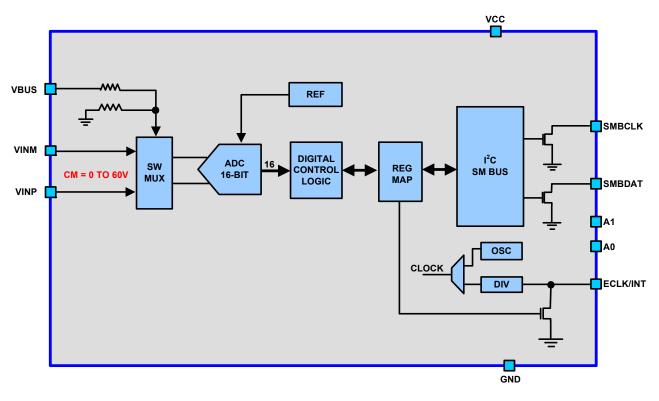

### **Block Diagram**

#### FIGURE 2. BLOCK DIAGRAM

### **Ordering Information**

| PART NUMBER<br>( <u>Notes 1, 2, 3</u> ) | PART<br>MARKING              | TEMP RANGE<br>(°C)                | PACKAGE<br>(RoHS Compliant)               | PKG.<br>DWG. # |  |  |  |  |  |

|-----------------------------------------|------------------------------|-----------------------------------|-------------------------------------------|----------------|--|--|--|--|--|

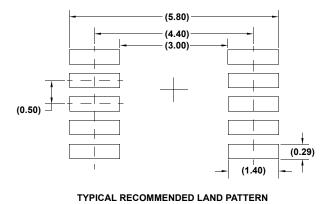

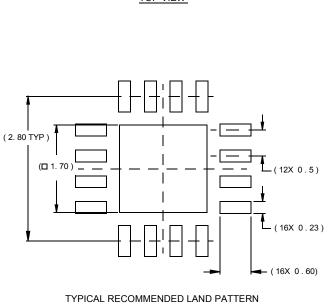

| ISL28022FUZ                             | 8022F                        | -40 to +125                       | 10 Ld MSOP                                | M10.118        |  |  |  |  |  |

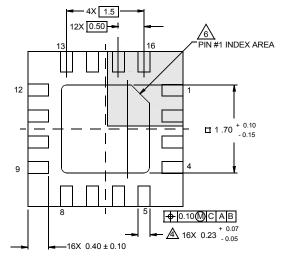

| ISL28022FRZ                             | 022F                         | -40 to +125                       | 16 Ld QFN                                 | L16.3x3B       |  |  |  |  |  |

| ISL28022EVKIT1Z                         | ISL28022 Evaluation Kit (Inc | cludes Dongle Board, Ger          | neric Evaluation Board, R <sub>LOAD</sub> | Board)         |  |  |  |  |  |

| ISL28022MBEV1Z                          | ISL28022 Generic Evaluatio   | ISL28022 Generic Evaluation Board |                                           |                |  |  |  |  |  |

| ISL28022EV1Z                            | ISL28022 8-site Evaluation   | SL28022 8-site Evaluation Board   |                                           |                |  |  |  |  |  |

NOTES:

- 1. Add "-T" suffix for QFN 6k or MSOP 2.5k units tape and reel options. Add "-T7A" suffix for 250 units tape and reel options. Please refer to <u>TB347</u> for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for ISL28022. For more information on MSL please see tech brief TB363.

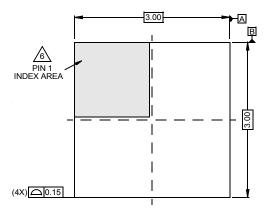

### **Pin Configurations**

## **Pin Descriptions**

| MSOP<br>PIN<br>NUMBER | QFN PIN<br>NUMBER      | PIN<br>NAME | DESCRIPTION                                                                                                                       |

|-----------------------|------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 1                     | 1                      | A1          | I <sup>2</sup> C address, Bit 1                                                                                                   |

| 2                     | 2                      | AO          | I <sup>2</sup> C address, Bit 0                                                                                                   |

| 3                     | 3                      | EXT_CLK/INT | External ADC clock input or CPU interrupt output signal. When the pin is configured as an interrupt, the output is an open drain. |

| 4                     | 4                      | SDA/SMBDAT  | I <sup>2</sup> C serial data input/output.                                                                                        |

| 5                     | 5                      | SCL/SMBCLK  | I <sup>2</sup> C clock input                                                                                                      |

| 6                     | 9                      | VCC         | Positive power pin. The positive power supply to the part.                                                                        |

| 7                     | 10                     | GND         | Negative power pin. Can be connected to ground or a negative voltage.                                                             |

| 8                     | 11                     | VBUS        | VBUS power voltage sense.                                                                                                         |

| 9                     | 12                     | VINM        | Current sense minus input.                                                                                                        |

| 10                    | 13                     | VINP        | Current sense plus input.                                                                                                         |

|                       | 6, 7, 8, 14,<br>15, 16 | NC          | No connect. No internal connection.                                                                                               |

|                       | Epad                   | GND         | Negative power pin. Can be connected to ground or a negative voltage.                                                             |

|                                 | DESCRIPTION                 | BASIC DIGITAL<br>POWER MONITOR | FULL FEATURE<br>DIGITAL POWER MONITOR | DIGITAL POWER MONITOR<br>IN TINY PACKAGE |  |  |

|---------------------------------|-----------------------------|--------------------------------|---------------------------------------|------------------------------------------|--|--|

|                                 | PART NUMBER                 | ISL28022                       | ISL28023                              | ISL28025                                 |  |  |

| PACKAGE                         |                             | MSOP10, QFN16                  | QFN24                                 | WLCSP-16                                 |  |  |

| Temperature Ran                 | ge                          | -40°C to +125°C                | -40°C to +125°C                       | -40°C to +125°C                          |  |  |

| OV to 60V Input R               | ange                        | OV to 60V                      | Opt 1: 0V to 60V<br>Opt 2: 0V to 16V  | Opt 1: 0V to 60V<br>Opt 2: 0V to 16V     |  |  |

| ADC                             |                             | 16-bit                         | 16-bit                                | 16-bit                                   |  |  |

| +25°C Gain Error                |                             | 0.30%                          | 0.25%                                 | 0.25%                                    |  |  |

| Current Measure                 | LSB Step                    | 10µV                           | 2.5µV                                 | 2.5µV                                    |  |  |

| +25°C Offset                    |                             | 75μV                           | 30µV                                  | 30µV                                     |  |  |

| Primary                         | Differential Shunt Input    | x                              | Х                                     | X                                        |  |  |

| Channel                         | Independent Bus Voltage     | x                              | Х                                     | X                                        |  |  |

| LV Aux                          | Differential Shunt Input    |                                | Х                                     |                                          |  |  |

| Channel                         | Independent Bus Voltage     |                                | Х                                     | x                                        |  |  |

| VBus LSB Step                   | Low Voltage Bus             |                                | 0.25mV                                | 0.25mV                                   |  |  |

|                                 | High Voltage Bus            | 4mV                            | 1mV/0.25mV                            | 1mV/0.25mV                               |  |  |

| External Tempera                | ture Sensor Input           |                                | Х                                     |                                          |  |  |

| HV Internal Regul               | ator (3.3V <sub>OUT</sub> ) |                                | X                                     | x                                        |  |  |

| Fast OC/OV/UV A                 | lert Outputs                |                                | 2 Outputs                             | 2 Outputs                                |  |  |

| Margin DAC                      |                             |                                | X                                     |                                          |  |  |

| Internal Temperat               | ture Sensor                 |                                | X                                     | x                                        |  |  |

| User Select Conve               | ersion Mode/Sample Rate     | x                              | X                                     | x                                        |  |  |

| Peak Min/Max Cu                 | irrent Registers            |                                | X                                     | x                                        |  |  |

| Slave Address Loo               | cations                     | 16 Addresses                   | 55 Addresses                          | 55 Addresses                             |  |  |

| I <sup>2</sup> C Level Translat | ors                         |                                | Х                                     | x                                        |  |  |

| PMBus                           |                             |                                | Х                                     | X                                        |  |  |

| I <sup>2</sup> C/SMBus          |                             | x                              | Х                                     | X                                        |  |  |

| High Speed (3.4M                | IHz) I <sup>2</sup> C Mode  | x                              | Х                                     | X                                        |  |  |

| External Clock Inp              | out                         | x                              | Х                                     | x                                        |  |  |

| Power Shutdown                  | Mode                        | X                              | Х                                     | X                                        |  |  |

#### TABLE 1. DPM PORTFOLIO COMPARISON - ISL28022 vs ISL28023 vs ISL28025

#### **Absolute Maximum Ratings**

| VCC                                                     |

|---------------------------------------------------------|

| VBUS Voltage                                            |

| Common-Mode Input Voltage (VINP, VINM)                  |

| Differential Input Voltage (VINP, VINM)±63V             |

| Input Voltage (Digital Pins) (GND - 0.3V) to 5.5V       |

| Output Voltage (Digital Pins)(GND - 0.3V) to VCC + 0.3V |

| Open-Drain Output Current 10mA                          |

| Open-Drain Voltage (Interrupt) 24V                      |

| ESD Rating                                              |

| Human Body Model (Tested per JESD22-A114) 8kV           |

| Machine Model (Tested per JESD22-A115)                  |

| Charged Device Model (Tested per JESD22-C101)           |

| Latch-Up (Tested per JESD-78B) 60V at +125°C            |

#### **Thermal Information**

| Thermal Resistance (Typical)                      | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C∕W) |  |  |  |  |  |  |

|---------------------------------------------------|------------------------|------------------------|--|--|--|--|--|--|

| 16 Ld QFN ( <u>Notes 4</u> , <u>5</u> )           | 52                     | 6.5                    |  |  |  |  |  |  |

| 10 Ld MSOP ( <u>Notes 6</u> , <u>7</u> )          | 150                    | 55                     |  |  |  |  |  |  |

| Maximum Storage Temperature Range65°C to +150     |                        |                        |  |  |  |  |  |  |

| Maximum Junction Temperature (T <sub>JMAX</sub> ) |                        | +150°C                 |  |  |  |  |  |  |

| Pb-Free Reflow Profile                            |                        | see <u>TB493</u>       |  |  |  |  |  |  |

#### **Recommended Operating Conditions**

Ambient Temperature Range (T<sub>A</sub>) .....-40°C to +125°C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

NOTES:

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief <u>TB379</u>.

- 5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 6. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 7. For  $\theta_{\text{JC}},$  the "case temp" location is taken at the package top center.

## **Electrical Specifications** $T_A = +25 \degree C$ , $V_{CC} = 3.3$ , VINP = $V_{BUS} = 12V$ , $V_{SENSE} = VINP-VINM = 32mV$ , unless otherwise specified. All voltages with respect to GND pin.

| PARAMETER                | DESCRIPTION                                                  | TEST CONDITIONS                                  | MIN<br>( <u>Note 8</u> ) | ТҮР  | MAX<br>( <u>Note 8</u> ) | UNIT  |

|--------------------------|--------------------------------------------------------------|--------------------------------------------------|--------------------------|------|--------------------------|-------|

| PUTS                     | ÷                                                            |                                                  |                          |      | 1                        |       |

| VSENSEDIFF               | Useful Full-Scale Current Sense                              | PGA gain = /1                                    | 0                        |      | ±40                      | mV    |

|                          | Differential Voltage Range (VINP-VINM)                       | PGA gain = /2                                    | 0                        |      | ±80                      | m٧    |

|                          |                                                              | PGA gain = /4                                    | 0                        |      | ±160                     | mV    |

|                          |                                                              | PGA gain = /8                                    | 0                        |      | ±320                     | mV    |

| V <sub>SHUNT</sub> _step | LSB Step Size, Shunt Voltage                                 |                                                  |                          | 10   |                          | μV    |

| V <sub>CMSENSE</sub>     | Current Sense Common-Mode<br>(VINP, VINM)                    |                                                  | 0                        |      | 60                       | v     |

| V <sub>OS</sub>          | V <sub>SENSE</sub> Offset Voltage                            | PGA gain = /1, /2, /4, /8;<br>ADC setting = 1111 |                          | ±10  | ±75                      | μV    |

| V <sub>OSTC</sub>        | V <sub>SENSE</sub> Offset Voltage Temperature<br>Coefficient |                                                  |                          | 0.15 |                          | µV∕°C |

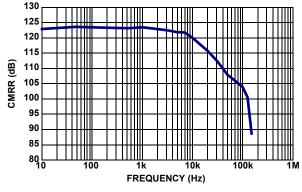

| CMRR                     | V <sub>SENSE</sub> V <sub>OS</sub> vs Common-Mode            | V <sub>BUS</sub> = 0V to 60V; BRNG = 2, 3        | 110                      | 130  |                          | dB    |

| PSRR                     | V <sub>SENSE</sub> V <sub>OS</sub> vs Power Supply           | V <sub>CC</sub> = 3V to 5V                       |                          | 105  |                          | dB    |

| A <sub>CS</sub>          | Current Sense Gain Error                                     |                                                  |                          | ±40  |                          | m%    |

| A <sub>CSTC</sub>        | Current Sense Gain Error Temperature<br>Coefficient          |                                                  |                          | ±1   |                          | m%/°0 |

| IVINACT                  | Input Leakage, VIN Pins                                      | Active mode<br>(for both VINP and VINM pins)     |                          | ±20  |                          | μA    |

| IVINACT                  | Input Leakage, VIN Pins                                      | Power-down mode<br>(for both VINP and VINM pins) |                          | ±0.1 | ±0.5                     | μA    |

| V <sub>BUS</sub>         | Useful Bus Voltage Range                                     | BRNG = 0                                         | 0                        |      | 16                       | ٧     |

|                          |                                                              | BRNG = 1                                         | 0                        |      | 32                       | V     |

|                          |                                                              | BRNG = 2, 3                                      | 0                        |      | 60                       | V     |

| V <sub>BUS</sub> _Step   | LSB Step Size, Bus Voltage                                   | BRNG = 0                                         |                          | 4    |                          | m٧    |

| V <sub>BUS</sub> _VCO    | V <sub>BUS</sub> Voltage Coefficient                         |                                                  |                          | 50   |                          | ppm/V |

| R <sub>VBACT</sub>       | Input Impedance, VBUS Pin                                    | Active mode                                      |                          | 600  |                          | kΩ    |

**Electrical Specifications**  $T_A = +25$  °C,  $V_{CC} = 3.3$ , VINP =  $V_{BUS} = 12V$ ,  $V_{SENSE} = VINP-VINM = 32mV$ , unless otherwise specified. All voltages with respect to GND pin. (Continued)

| PARAMETER                     | DESCRIPTION                                                      | TEST CONDITIONS                                                                                                             | MIN<br>( <u>Note 8</u> ) | ТҮР                    | MAX<br>( <u>Note 8</u> ) | UNIT |

|-------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|--------------------------|------|

| DC ACCURACY                   |                                                                  |                                                                                                                             |                          |                        |                          |      |

|                               | ADC Resolution (Native)                                          | PGA gain = $/1$ , V <sub>SENSE</sub> = $\pm 320$ mV                                                                         |                          | 16                     |                          | Bits |

|                               | Current Measurement Error                                        | T <sub>A</sub> = +25°C                                                                                                      |                          | ±0.2                   | ±0.3                     | %    |

|                               | Current Measurement Error                                        | T <sub>A</sub> = -40 °C to +85 °C                                                                                           |                          |                        | ±0.5                     | %    |

|                               | Over-Temperature                                                 | T <sub>A</sub> = -40 °C to +125 °C                                                                                          |                          |                        | ±1                       | %    |

|                               | Bus Voltage Measurement Error                                    | T <sub>A</sub> = +25°C                                                                                                      |                          | ±0.2                   | ±0.3                     | %    |

|                               | Bus Voltage Measurement Error                                    | T <sub>A</sub> = -40 °C to +85 °C                                                                                           |                          |                        | ±0.5                     | %    |

|                               | Over-Temperature                                                 | T <sub>A</sub> = -40 °C to +125 °C                                                                                          |                          |                        | ±1                       | %    |

| ADC TIMING SPECS              |                                                                  | I                                                                                                                           | I                        | I                      | 11                       |      |

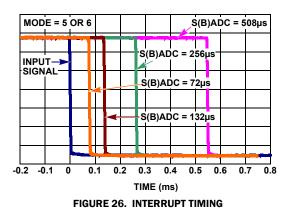

| ts                            | ADC Conversion Time                                              | ADC setting = 0000                                                                                                          |                          | 72.0                   | 79.2                     | μs   |

|                               | Mode = 5 or 6                                                    | ADC setting = 0001                                                                                                          |                          | 132.0                  | 145.2                    | μs   |

|                               |                                                                  | ADC setting = 0010                                                                                                          |                          | 258.0                  | 283.8                    | μs   |

|                               |                                                                  | ADC setting = 0011                                                                                                          |                          | 508.0                  | 558.8                    | μs   |

|                               |                                                                  | ADC setting = 1001                                                                                                          |                          | 1.01                   | 1.11                     | ms   |

|                               |                                                                  | ADC setting = 1010                                                                                                          |                          | 2.01                   | 2.21                     | ms   |

|                               |                                                                  | ADC setting = 1011                                                                                                          |                          | 4.01                   | 4.41                     | ms   |

|                               |                                                                  | ADC setting = 1100                                                                                                          |                          | 8.01                   | 8.81                     | ms   |

|                               |                                                                  | ADC setting = 1101                                                                                                          |                          | 16.01                  | 17.61                    | ms   |

|                               |                                                                  | ADC setting = 1110                                                                                                          |                          | 32.01                  | 35.21                    | ms   |

|                               |                                                                  | ADC setting = 1111                                                                                                          |                          | 64.01                  | 70.41                    | ms   |

| <sup>2</sup> C INTERFACE SPEC | IFICATIONS                                                       |                                                                                                                             |                          |                        |                          |      |

| VIL                           | SDA and SCL Input Buffer LOW Voltage                             |                                                                                                                             | -0.3                     |                        | 0.3 x V <sub>CC</sub>    | v    |

| V <sub>IH</sub>               | SDA and SCL Input Buffer HIGH Voltage                            |                                                                                                                             | 0.7 x V <sub>CC</sub>    |                        | V <sub>CC</sub> + 0.3    | v    |

| Hysteresis                    | SDA and SCL Input Buffer Hysteresis                              |                                                                                                                             |                          | 0.05 x V <sub>CC</sub> |                          | v    |

| V <sub>OL</sub>               | SDA Output Buffer LOW Voltage, Sinking<br>3mA                    | V <sub>CC</sub> = 5V, I <sub>OL</sub> = 3mA                                                                                 | 0                        | 0.02                   | 0.40                     | V    |

| C <sub>PIN</sub>              | SDA and SCL Pin Capacitance                                      | $T_A = +25 \text{°C, } f = 1MHz,$<br>$V_{CC} = 5V, V_{IN} = 0V,$<br>$V_{OUT} = 0V$                                          |                          |                        | 10                       | pF   |

| fscl                          | SCL Frequency                                                    |                                                                                                                             |                          |                        | 400                      | kHz  |

| t <sub>IN</sub>               | Pulse Width Suppression Time at SDA and SCL Inputs               | Any pulse narrower than the maximum spec is suppressed                                                                      |                          |                        | 50                       | ns   |

| t <sub>AA</sub>               | SCL Falling Edge to SDA Output Data<br>Valid                     | SCL falling edge crossing 30% of $\rm V_{CC},$ until SDA exits the 30% to 70% of $\rm V_{CC}$ window.                       |                          |                        | 900                      | ns   |

| t <sub>BUF</sub>              | Time the Bus Must be Free Before the Start of a New Transmission | SDA crossing 70% of $V_{CC}$ during a STOP condition, to SDA crossing 70% of $V_{CC}$ during the following START condition. | 1300                     |                        |                          | ns   |

| tLOW                          | Clock LOW Time                                                   | Measured at the 30% of $V_{CC}$ crossing                                                                                    | 1300                     |                        |                          | ns   |

| thigh                         | Clock HIGH Time                                                  | Measured at the 70% of $V_{CC}$ crossing                                                                                    | 600                      |                        |                          | ns   |

| <sup>t</sup> SU:STA           | START Condition Setup Time                                       | SCL rising edge to SDA falling edge<br>Both crossing 70% of V <sub>CC</sub>                                                 | 600                      |                        |                          | ns   |

| <sup>t</sup> hd:sta           | START Condition Hold Time                                        | From SDA falling edge crossing 30% of $V_{CC}$ to SCL falling edge crossing 70% of $V_{CC}$                                 | 600                      |                        |                          | ns   |

# **Electrical Specifications** $T_A = +25$ °C, $V_{CC} = 3.3$ , VINP = $V_{BUS} = 12V$ , $V_{SENSE} = VINP-VINM = 32mV$ , unless otherwise specified. All voltages with respect to GND pin. (Continued)

| PARAMETER           | DESCRIPTION                                                                                                                                                                                                                         | TEST CONDITIONS                                                                                                                                                       | MIN<br>( <u>Note 8</u> ) | ТҮР | MAX<br>( <u>Note 8</u> ) | UNIT |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|------|

| <sup>t</sup> su:dat | Input Data Setup Time                                                                                                                                                                                                               | From SDA exiting the 30% to 70% of $V_{CC}$ window, to SCL rising edge crossing 30% of $V_{CC}$                                                                       | 100                      |     |                          | ns   |

| <sup>t</sup> hd:dat | Input Data Hold Time                                                                                                                                                                                                                | From SCL falling edge crossing 30% of V <sub>CC</sub> to SDA entering the 30% to 70% of V <sub>CC</sub> window                                                        | 20                       |     | 900                      | ns   |

| <sup>t</sup> su:sto | V <sub>CC</sub> , to SDA rising edge crossing 30%<br>of V <sub>CC</sub>                                                                                                                                                             |                                                                                                                                                                       | 600                      |     |                          | ns   |

| thd:sto             | of V <sub>CC</sub> STOP Condition Hold Time From SDA rising edge to SCL falling                                                                                                                                                     |                                                                                                                                                                       | 600                      |     |                          | ns   |

| t <sub>DH</sub>     | Output Data Hold Time       From SCL falling edge crossing 30% of V <sub>CC</sub> , until SDA enters the 30% to 70% of V <sub>CC</sub> window         R       SDA and SCL Rise Time       From 30% to 70% of V <sub>CC</sub> 20 ··· |                                                                                                                                                                       | 0                        |     |                          | ns   |

| t <sub>R</sub>      | SDA and SCL Rise Time From 30% to 70% of V <sub>CC</sub>                                                                                                                                                                            |                                                                                                                                                                       | 20 + 0.1<br>x Cb         |     | 300                      | ns   |

| t <sub>F</sub>      | SDA and SCL Fall Time From 70% to 30% of V <sub>CC</sub>                                                                                                                                                                            |                                                                                                                                                                       | 20 + 0.1<br>x Cb         |     | 300                      | ns   |

| Cb                  | Capacitive Loading of SDA or SCL                                                                                                                                                                                                    | Total on-chip and off-chip                                                                                                                                            |                          | 75  |                          | pF   |

| R <sub>PU</sub>     | SDA and SCL Bus Pull-Up Resistor<br>Off-Chip                                                                                                                                                                                        | Maximum is determined by $t_R$ and $t_F$<br>For Cb = 400pF, maximum is about $2k\Omega \sim 2.5k\Omega$<br>For Cb = 40pF, maximum is about $15k\Omega \sim 20k\Omega$ | 1                        |     |                          | k    |

| WER SUPPLY          |                                                                                                                                                                                                                                     | 1                                                                                                                                                                     | · · ·                    |     |                          |      |

|                     | Operating Supply Voltage Range                                                                                                                                                                                                      |                                                                                                                                                                       | 3                        |     | 5.5                      | ۷    |

| ICCEXT              | Power Supply Current On V <sub>CC</sub> Pin, Active Mode                                                                                                                                                                            | External power supply mode,<br>V <sub>CC</sub> = 5V                                                                                                                   |                          | 0.7 | 1.0                      | mA   |

| ICCPD               | Power Supply Current On V <sub>CC</sub> Pin,<br>Power-Down Mode                                                                                                                                                                     | External power supply mode,<br>V <sub>CC</sub> = 5V                                                                                                                   |                          | 5   | 15                       | μA   |

NOTE:

8. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

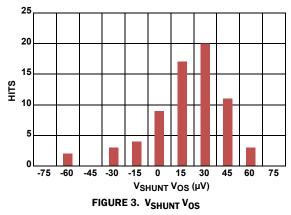

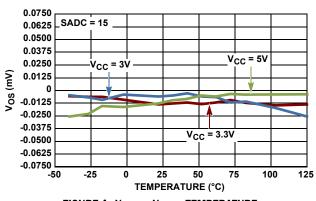

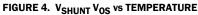

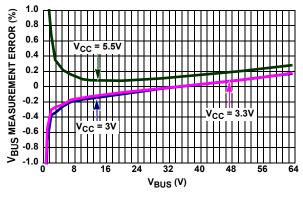

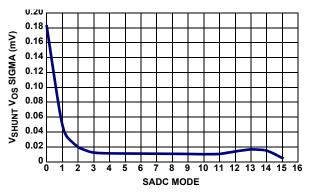

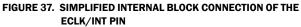

### **Typical Performance Curves** $T_A = +25 \degree C$ , $V_{CC} = 3.3V$ , VINP = $V_{BUS} = 12V$ , S(B)ADC = 15;

unless otherwise specified.

FIGURE 6. V<sub>SHUNT</sub> MEASUREMENT ERROR vs V<sub>SHUNT</sub> INPUT

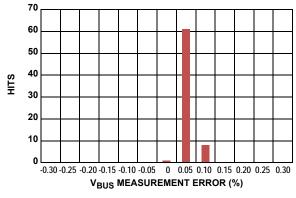

FIGURE 8. VBUS MEASUREMENT ERROR DISTRIBUTION

FIGURE 5. V<sub>SHUNT</sub> MEASUREMENT ERROR

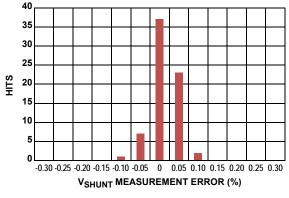

FIGURE 7. VSHUNT GAIN vs TEMPERATURE

# **Typical Performance Curves** $T_A = +25$ °C, $V_{CC} = 3.3V$ , VINP = $V_{BUS} = 12V$ , S(B)ADC = 15; unless otherwise specified. (Continued)

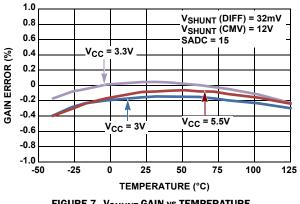

FIGURE 9. V<sub>BUS</sub> MEASUREMENT ERROR vs  $V_{BUS}$  (T<sub>A</sub> = +25°C)

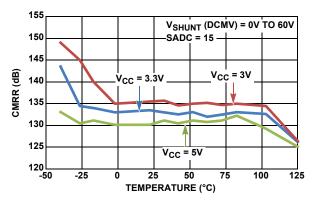

FIGURE 11. CMRR vs TEMPERATURE

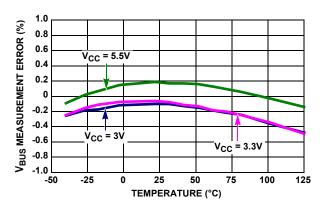

FIGURE 10. V<sub>BUS</sub> MEASUREMENT ERROR vs TEMPERATURE

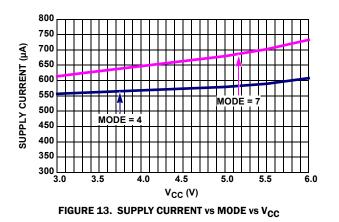

FIGURE 12. SUPPLY CURRENT vs MODE vs TEMPERATURE

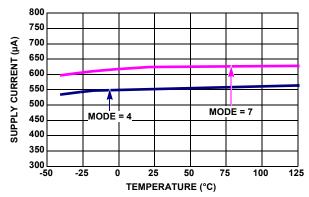

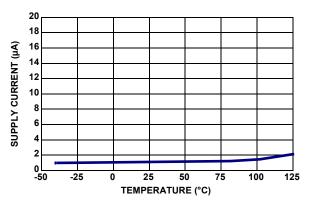

FIGURE 14. SUPPLY CURRENT vs MODE 0 vs TEMPERATURE

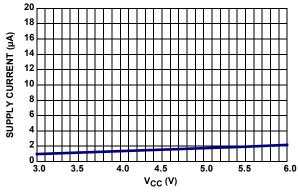

## **Typical Performance Curves** $T_A = +25 \degree C$ , $V_{CC} = 3.3V$ , VINP = $V_{BUS} = 12V$ , S(B)ADC = 15;

unless otherwise specified. (Continued)

FIGURE 15. SUPPLY CURRENT vs MODE 0 vs V<sub>CC</sub>

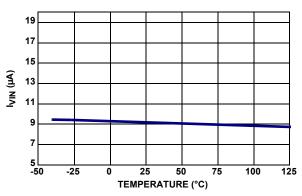

FIGURE 16. SHUNT IVIN vs TEMPERATURE (MODE 5)

FIGURE 17. SHUNT IVIN VS COMMON-MODE VOLTAGE (MODE 5)

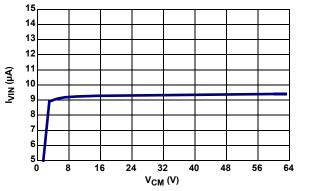

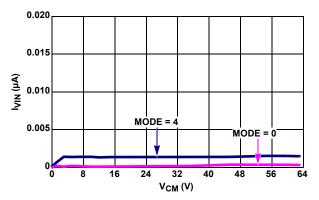

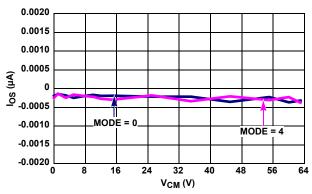

FIGURE 19. SHUNT IVIN VS COMMON-MODE VOLTAGE (MODE 0, 4)

FIGURE 18. SHUNT IVIN VS TEMPERATURE (MODE 0, 4)

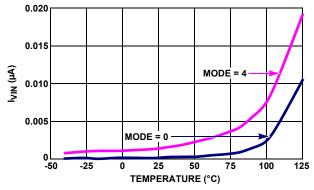

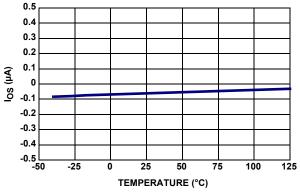

FIGURE 20. SHUNT I<sub>OS</sub> vs TEMPERATURE (MODE 5)

## **Typical Performance Curves** $T_A = +25 \degree C$ , $V_{CC} = 3.3V$ , VINP = $V_{BUS} = 12V$ , S(B)ADC = 15;

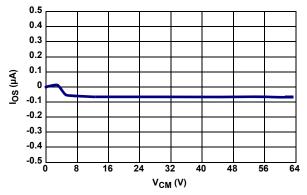

unless otherwise specified. (Continued)

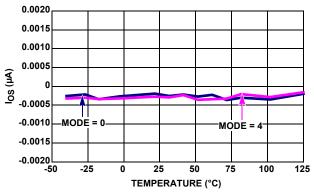

FIGURE 21. SHUNT IOS vs COMMON-MODE VOLTAGE (MODE 5)

FIGURE 23. SHUNT IOS vs COMMON-MODE VOLTAGE (MODE 0, 4)

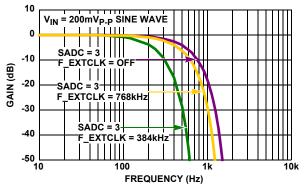

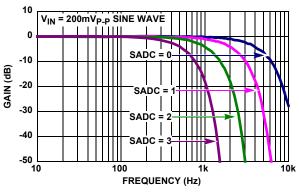

FIGURE 25. VSHUNT BANDWIDTH vs EXTERNAL CLOCK FREQUENCY

FIGURE 22. SHUNT IOS vs TEMPERATURE (MODE 0, 4)

FIGURE 24. V<sub>SHUNT</sub> BANDWIDTH vs SADC MODE

### **Functional Description**

#### **Overview**

The ISL28022 is a Digital Power Monitor (DPM) device that is capable of measuring bidirectional currents while monitoring the bus voltage.

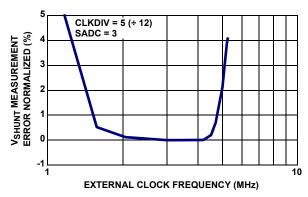

The DPM requires an external shunt resistor to enable current measurements. The shunt resistor translates the bus current to a voltage. The DPM measures the voltage across the shunt resistors and reports the measured value out digitally via an  $I^2C$  interface. A register within the DPM is reserved to store the value of the shunt resistor. The stored current sense resistor value allows the DPM to output the current value to an external digital device.

The ISL28022 measures bus voltage and current sequentially. The device has a power measurement functionality that multiplies current and voltage measured values. The power calculation is stored in a unique register. The power measurement allows the user to monitor power to or from the load in addition to current and voltage.

The ISL28022 can monitor supplies from 0V to 60V while operating on a chip supply ranging from 3V to 5.5V.

The ISL28022 ADC sample rate can be configured to an internal oscillator (500kHz) or a user can provide a synchronized clock.

#### **Detailed Description**

The ISL28022 consists of a two channel analog front end multiplexer, a 16-bit sigma delta ADC and digital signal processing/serial communication circuitry.

The main block within the device is a 3rd order Sigma Delta ADC. The input signal bandwidth is 1kHz, wide enough for power monitoring applications. The main block includes an internal 1.2V bandgap voltage reference that is used to drive the ADC.

The analog front end multiplexer selects the input to the ADC. The selection to the input of the ADC is either a single-ended  $V_{BUS}$  measurement or a fully differential measurement across a shunt resistor.

The digital block contains controllable registers, I<sup>2</sup>C serial communication circuitry and a state machine. The state machine controls the behavior of the ADC acquisition, whether the acquisition is triggered or continuous. A more detailed description of the state machine states can be found in <u>"MODE:</u> <u>Operating Mode" on page 15</u>.

#### **Functional Pin Descriptions**

#### A1

A1 is the address select pin. A1 is one of two  $I^2C/SMB$ us slave address select pins that are multilogic programmable for a total of 16 different address combinations.

There are four selectable levels for A1, VCC, GND, SCL/SMBCLK, and SDA/SMBDAT. See <u>Table 22</u> for more details in setting the slave address of the device.

#### **A0**

A0 is the address select pin. A0 is one of two I<sup>2</sup>C/SMBus slave address select pins that are multilogic programmable for a total of 16 different address combinations.

There are four selectable levels for A0, VCC, GND, SCL/SMBCLK, and SDA/SMBDAT. See <u>Table 22</u> for more details in setting the slave address of the device.

#### EXT\_CLK/INT

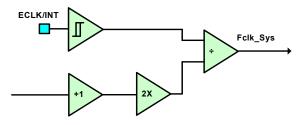

EXT\_CLK/INT is the External/Interrupt clock pin. EXT\_CLK/INT is a bidirectional pin. The pin provides a connection to the system clock. The system clock is connected to the ADC. The acquisitions rate of the ADC can be varied through the EXT\_CLK/INT pin. The pin functionality is set through a control register bit.

When the EXT\_CLK/INT pin is configured as an output, the pin functionality becomes an interrupt flag to connecting devices. EXT\_CLK/INT pin as an output requires a pull-up resistor to a power supply, up to 20V, for proper operation. The internal threshold detectors  $(OV_{sh}/UV_{sh}/OV_b/UV_b)$  signal level relative to the measured value determines the state of the INT pin.

#### SDA/SMBDAT

SDA/SMBDAT is the serial data input/output pin. SDA/SMBDAT is a bidirectional pin used to transfer data to and from the device. The pin is an open-drain output and may be wired with other open-drain/collector outputs. The open-drain output requires a pull-up resistor for proper functionality. The pull-up resistor should be connected to VCC of the device.

#### SCL/SMBCLK

SCL/SMBCLK is the serial clock input pin. The SCL/SMBCLK input is responsible for clocking in all data to and from the device.

#### VCC

VCC is the positive supply voltage pin. VCC is an analog power pin. VCC supplies power to the device.

#### GND

GND is the ground pin. All voltages internal to the chip are referenced to ground. GND should be tied to OV for single supply applications. For dual supply applications, the pin should be connected to the most negative voltage in the application.

#### VBUS

VBUS is the power bus voltage input pin. The pin should be connected to the desired power supply bus to be monitored.

#### VINP

VINP is the shunt voltage monitor positive input pin. The pin connects to the most positive voltage of the current shunt resistor.

#### VINM

VINM is the shunt voltage monitor negative input pin. The pin connects to the most negative voltage of the current shunt resistor.

| REGISTER<br>ADDRESS (HEX) | REGISTER NAME           | FUNCTION                                                                        | POWER-ON RESET VALUE<br>(HEX) | ACCESS |

|---------------------------|-------------------------|---------------------------------------------------------------------------------|-------------------------------|--------|

| 00                        | Configuration           | Power-on reset, bus and shunt ranges, ADC acquisition times, mode configuration | 799F                          | R/W    |

| 01                        | Shunt Voltage           | Shunt voltage measurement value                                                 | 0000                          | R      |

| 02                        | Bus Voltage             | Bus voltage measurement value                                                   | 0000                          | R      |

| 03                        | Power                   | Power measurement value                                                         | 0000                          | R      |

| 04                        | Current                 | Current measurement value                                                       | 0000                          | R      |

| 05                        | Calibration Register    | Register used to enable current and power measurements.                         | 0000                          | R/W    |

| 06                        | Shunt Voltage Threshold | Min/Max shunt thresholds                                                        | 7F81                          | R/W    |

| 07                        | Bus Voltage Threshold   | Min/Max V <sub>BUS</sub> thresholds                                             | FF00                          | R/W    |

| 08                        | DCS Interrupt Status    | Threshold interrupts                                                            | 0000                          | R/W    |

| 09                        | Aux Control Register    | Register to control the interrupts and external clock functionality             | 0000                          | R/W    |

#### TABLE 2. ISL28022 REGISTER DESCRIPTIONS

#### TABLE 3. CONFIGURATION REGISTER

| BIT  | D15 | D14   | D13   | D12 | D11 | D10   | D9    | D8    | D7    | D6    | D5    | D4    | D3    | D2    | D1    | DO    |

|------|-----|-------|-------|-----|-----|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME | RST | BRNG1 | BRNG0 | PG1 | PG0 | BADC3 | BADC2 | BADC1 | BADC0 | SADC3 | SADC2 | SADC1 | SADC0 | MODE2 | MODE1 | MODEO |

#### **Register Descriptions**

<u>Table 2</u> is the register map for the device. The table describes the function of each register and its respective value. The addresses are sequential and the register size is 16 bits (2 bytes) per address.

#### **CONFIGURATION REGISTER**

The configuration register (<u>Table 3</u>) controls the functionality of the chip. ADC measurable range, converter acquisition times, converter resolution and state machine modes are configurable bits within this register.

#### **RST: Reset Bit**

Configuring the reset bit (Bit 15) to a 1 generates a system reset that initializes all registers to their default values and performs a system calibration.

#### **BRNG: Bus Voltage Range**

Bits 13 and 14 of the configuration register sets the bus measurable voltage range. <u>Table 4</u> shows the BRNG bit configurations versus the allowable full-scale measurement range. The shaded row is the power-up default.

|       |       | l GETTINGO                     |

|-------|-------|--------------------------------|

| BRNG1 | BRNGO | USABLE FULL<br>SCALE RANGE (V) |

| 0     | 0     | 16                             |

| 0     | 1     | 32                             |

| 1     | 0     | 60                             |

| 1     | 1     | 60                             |

#### TABLE 4. BRNG BIT SETTINGS

#### **PG: PGA (Shunt Voltage Only)**

Bits 11 and 12 of the configuration register determines the shunt voltage measurement range. <u>Table 5</u> shows the PGA bit configurations versus the allowable full-scale measurement range. The shaded row is the power-up default.

#### TABLE 5. PGA BIT SETTINGS

| PG1 | PGO | GAIN | RANGE<br>(mV) |

|-----|-----|------|---------------|

| 0   | 0   | 1    | ±40           |

| 0   | 1   | ÷2   | ±80           |

| 1   | 0   | ÷4   | ±160          |

| 1   | 1   | ÷8   | ±320          |

#### BADC: Bus ADC Resolution/Averaging

Bits [10:7] of the configuration register sets the ADC resolution/ averaging when the ADC is configured in the V<sub>BUS</sub> mode. The ADC can be configured versus bit accuracy. The bit accuracy selections range from 12 to 15 bits. The ADC is configurable versus the number of averages. The selection ranges from 2 to 128 samples. <u>Table 6</u> shows the breakdown of each BADC setting. The shaded row is the default setting upon power-up.

#### SADC: Shunt ADC Resolution/Averaging

Bits [10:7] of the configuration register sets the ADC resolution/ averaging when the ADC is configured in the  $V_{SHUNT}$  mode. The ADC can be configured versus bit accuracy. The bit accuracy selections range from 12 to 15 bits. The ADC is configurable versus number of averages. The selection ranges from 2 to 128 samples. <u>Table 6</u> shows the breakdown of each SADC setting. The shaded row is the default setting upon power-up.

#### **MODE: Operating Mode**

Bits [2:0] of the configuration register controls the state machine within the chip. The state machine globally controls the overall functionality of the chip. <u>Table 7</u> shows the various states the chip can be configured to, as well as the mode bit definitions to achieve a desired state. The shaded row is the default setting upon power-up.

| ADC3 | ADC2 | ADC1 | ADCO | MODE/SAMPLES | CONVERSION TIME |

|------|------|------|------|--------------|-----------------|

| 0    | x    | 0    | 0    | 12-bit       | 72µs            |

| 0    | x    | 0    | 1    | 13-bit       | 132µs           |

| 0    | x    | 1    | 0    | 14-bit       | 258µs           |

| 0    | x    | 1    | 1    | 15-bit       | 508µs           |

| 1    | 0    | 0    | 0    | 15-bit       | 508µs           |

| 1    | 0    | 0    | 1    | 2            | 1.01ms          |

| 1    | 0    | 1    | 0    | 4            | 2.01ms          |

| 1    | 0    | 1    | 1    | 8            | 4.01ms          |

| 1    | 1    | 0    | 0    | 16           | 8.01ms          |

| 1    | 1    | 0    | 1    | 32           | 16.01ms         |

| 1    | 1    | 1    | 0    | 64           | 32.01ms         |

| 1    | 1    | 1    | 1    | 128          | 64.01ms         |

#### TABLE 6. ADC SETTINGS, APPLIES TO BOTH SADC AND BADC CONTROL

#### TABLE 7. OPERATING MODE SETTINGS

| MODE2 | MODE1 | MODEO | MODE                      |

|-------|-------|-------|---------------------------|

| 0     | 0     | 0     | Power-down                |

| 0     | 0     | 1     | Shunt voltage, triggered  |

| 0     | 1     | 0     | Bus voltage, triggered    |

| 0     | 1     | 1     | Shunt and bus, triggered  |

| 1     | 0     | 0     | ADC off (disabled)        |

| 1     | 0     | 1     | Shunt Voltage, continuous |

| 1     | 1     | 0     | Bus voltage, continuous   |

| 1     | 1     | 1     | Shunt and bus, continuous |

#### SHUNT VOLTAGE REGISTER 01H (READ-ONLY)

The shunt voltage register reports the measured value across the shunt pins (VINP and VINM) into the register. The shunt register LSB is independent of PGA range settings. The PGA setting for the shunt register masks the unused most significant bit with a sign bit. For lower range of PGA settings, multiple sign bits are returned by the DPM. Only one sign bit should be used to calculate the measured value.

<u>Tables 8</u> through <u>11</u> show the weights of each bit for various PGA ranges. The tables should be used to calculate the measured value across the shunt pins from the binary to decimal domains.

To calculate the measured decimal value across the shunt, first read the shunt voltage register. Assume the PGA setting is set to the 80mV range. For this example, the reading output by the chip

is 1111 1010 0000 0101. The 80mV range has three sign bits. Only one sign bit needs to be used to calculate the measured decimal value. Bits 14 and 15 are omitted from the calculation. This leaves a binary reading of 11 1010 0000 0101.

Next, multiply each bit by its respective weight. Bit0 value would be multiplied by Bit0 weight (1), Bit1 value\*Bit1 weight (2), etc.

Add all the multiplied values to equate to a single number. For the binary reading 11 1010 0000 0101 this equates to -1531.

The LSB for a shunt register is  $10\mu V$ . Multiplying the decimal value by the LSB weight yields the measured voltage across the shunt. A 1111 1010 0000 0101 reading equals -15.31mV measured across the shunt pins.

#### TABLE 8. SHUNT VOLTAGE REGISTER, PG GAIN = /8 (RANGE = 11), FULL-SCALE = ±320mV, 15 BITS WIDE

| BIT    | D15    | D14   | D13   | D12   | D11   | D10   | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | DO   |

|--------|--------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| NAME   | Sign   | Bit14 | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| WEIGHT | -32768 | 16384 | 8192  | 4096  | 2048  | 1024  | 512  | 256  | 128  | 64   | 32   | 16   | 8    | 4    | 2    | 1    |

#### TABLE 9. SHUNT VOLTAGE REGISTER, PG GAIN = /4 (RANGE = 10), FULL-SCALE = ±160mV, 14 BITS WIDE

| BIT    | D15  | D14    | D13   | D12   | D11   | D10   | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | DO   |

|--------|------|--------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| NAME   | Sign | Sign   | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| WEIGHT |      | -16384 | 8192  | 4096  | 2048  | 1024  | 512  | 256  | 128  | 64   | 32   | 16   | 8    | 4    | 2    | 1    |

#### TABLE 10. SHUNT VOLTAGE REGISTER, PG GAIN = /2 (RANGE = 01), FULL-SCALE = ±80mV, 13 BITS WIDE

| BIT    | D15  | D14  | D13   | D12   | D11   | D10   | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | DO   |

|--------|------|------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| NAME   | Sign | Sign | Sign  | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| WEIGHT |      |      | -8192 | 4096  | 2048  | 1024  | 512  | 256  | 128  | 64   | 32   | 16   | 8    | 4    | 2    | 1    |

#### TABLE 11. SHUNT VOLTAGE REGISTER, PG GAIN = /1 (RANGE = 00), FULL-SCALE = ±40mV, 12 BITS WIDE

| BIT    | D15  | D14  | D13  | D12   | D11   | D10   | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | DO   |

|--------|------|------|------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| NAME   | Sign | Sign | Sign | Sign  | Bit11 | Bit10 | Bit9 | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| WEIGHT |      |      |      | -4096 | 2048  | 1024  | 512  | 256  | 128  | 64   | 32   | 16   | 8    | 4    | 2    | 1    |

#### TABLE 12. BUS VOLTAGE REGISTER, BRNG = 10 OR 11, FULL-SCALE = 60V, 14 BITS WIDE

| BIT    | D15   | D14   | D13   | D12   | D11  | D10  | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | DO  |

|--------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|------|-----|

| NAME   | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | CNVR | OVF |

| WEIGHT | 8192  | 4096  | 2048  | 1024  | 512  | 256  | 128  | 64   | 32   | 16   | 8    | 4    | 2    | 1    |      |     |

#### TABLE 13. BUS VOLTAGE REGISTER, BRNG = 01, FULL-SCALE = 32V, 13 BITS WIDE

| BIT    | D15   | D14   | D13   | D12  | D11  | D10  | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2 | D1   | DO  |

|--------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|----|------|-----|

| NAME   | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |    | CNVR | OVF |

| WEIGHT | 4096  | 2048  | 1024  | 512  | 256  | 128  | 64   | 32   | 16   | 8    | 4    | 2    | 1    |    |      |     |

#### TABLE 14. BUS VOLTAGE REGISTER, BRNG = 00, FULL-SCALE = 16V, 12 BITS WIDE

| BIT    | D15 | D14   | D13   | D12  | D11  | D10  | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2 | D1   | DO  |

|--------|-----|-------|-------|------|------|------|------|------|------|------|------|------|------|----|------|-----|

| NAME   |     | Bit11 | Bit10 | Bit9 | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |    | CNVR | OVF |

| WEIGHT |     | 2048  | 1024  | 512  | 256  | 128  | 64   | 32   | 16   | 8    | 4    | 2    | 1    |    |      |     |

#### TABLE 15. CALIBRATION REGISTER, 05h

| BIT  | D15  | D14  | D13  | D12  | D11  | D10  | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO |

|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|

| NAME | FS15 | FS14 | FS13 | FS12 | FS11 | FS10 | FS9 | FS8 | FS7 | FS6 | FS5 | FS4 | FS3 | FS2 | FS1 | 0  |

#### **BUS VOLTAGE REGISTER 02h (READ-ONLY)**

The bus voltage register is where the DPM reports the measured value of the  $V_{BUS}$ . There are three scale ranges possible depending on the BRNG setting controlled from the configuration register (00h).

<u>Tables 12</u> through <u>14 on page 16</u> are the weight bits for each BRNG setting. The binary value recorded in the Bus Voltage register is translated to a decimal value in the same way as the shunt voltage register is converted to a decimal value.

$$V_{bus} = \left[\sum_{n=2}^{15} \left(Bit_n \cdot Bit_W eight_n\right)\right] \cdot Vbus_{LSB}$$

(EQ. 1)

<u>Equation 1</u> is the mathematical equation for converting the binary  $V_{BUS}$  value to a decimal value. N is the bit number. The LSB value for the  $V_{BUS}$  measurement equals 4mV across all bus range (BRNG) settings.

#### **CNVR: Conversion Ready (Bit 1)**

The conversion ready bit indicates when the ADC has finished a conversion and transferred the reading(s) to the appropriate register(s). The CNVR is only operable when the DPM is set to one of three trigger modes. The CNVR is at a low state when the conversion is in progress. The CNVR transitions and remains at a high state when the conversion is complete.

The CNVR bit is initialized or reinitialized in the following ways:

- 1. Writing to the configuration register.

- 2. Reading from power register.

#### **OVF: Math Overflow Flag (Bit0)**

The Math Overflow Flag (OVF) is a bit that is set to indicate the current or power data being read from the DPM is over-ranged and meaningless.

#### **CALIBRATION REGISTER 05h (READ/WRITE)**

To accurately read the current and power measurements from the chip, the calibration register needs to be programmed.

The calibration register value is calculated as follows:

Calculate the full-scale current range that is desired. This is calculated using <u>Equation 2</u>. R<sub>shunt</sub> is the value of the shunt resistor. Vshunt<sub>FS</sub> is the full-scale setting that is desired. In most cases, it is the PGA full-scale range (320mV, 160mV, 80mV and 40mV) that the DPM is programmed to.

Current FS =

$$\frac{V \text{shunt FS}}{R \text{ shunt}}$$

(EQ. 2)

2. From the current full-scale range, the current LSB is calculated using <u>Equation 3</u>. Current full-scale is the outcome from <u>Equation 2</u>. ADC<sub>res</sub> is the resolution of shunt voltage reading. The value is determined by the SADC setting in configuration register. SADC setting equal to 3 and greater will have a 15-bit resolution. The ADC<sub>res</sub> value equals 2<sup>15</sup> or 32768.

$$Current_{LSB} = \frac{Current_{FS}}{ADC_{res}}$$

3. From Equation 3, the calibration resister value is calculated using Equation 4. The resolution of the math that is processed internally in the DPM is 4096 or 12 bits of resolution. The Vshunt<sub>LSB</sub> is set to  $10\mu$ V. Equation 4 yields a 16-bit binary number that can be written to the calibration register. The calibration value can only be 15 bits due to the ADC<sub>res</sub> value. Bit 0 of the calibration register format is represented in Table 15.

$$CalReg_{val} = integer\left[\frac{Math_{res} \cdot Vshunt_{LSB}}{(Current_{LSB} \cdot R_{shunt})}\right]$$

$$CalReg_{val} = integer\left[\frac{0.04096}{(Current_{LSB} \cdot R_{shunt})}\right]$$

(EQ. 4)

#### **CURRENT REGISTER 04h (READ-ONLY)**

Once the calibration register (05h) is programmed, the output current is calculated using <u>Equation 5</u>:

$$Current = \left[\sum_{n=0}^{15} \left(Bit_{n} \cdot Bit_{n}Weight_{n}\right)\right] \cdot Current_{LSB}$$

(EQ. 5)

Bit is the returned value of each bit from the current register either 1 or a 0. The weight of each bit is represented in <u>Table 16</u>. n is the bit number. The current LSB is the value calculated from <u>Equation 3</u>.

#### **POWER REGISTER 03h (READ-ONLY)**

The Power register only has meaning if the calibration register (05h) is programmed. The units for the power register are in watts. The power is calculated using <u>Equation 6</u>:

Power =

$$\begin{bmatrix} 15 \\ n = 0 \end{bmatrix}$$

(Bit<sub>n</sub>·Bit\_Weight<sub>n</sub>) Power LSB·5000 (EQ. 6)

Bit is the returned value of each bit from the power register either 1 or a 0. The weight of each bit is represented in <u>Table 17</u>. n is the bit number. The power LSB is calculated from <u>Equation 7</u>:

Power

$$_{LSB}$$

= Current  $_{LSB}$ ·Vbus  $_{LSB}$  (EQ. 7)

If V<sub>BUS</sub> range, BRNG, is set to 60V, the power equation in <u>Equation 6</u> is multiplied by 2.

#### THRESHOLD REGISTERS

The Shunt Voltage or V<sub>BUS</sub> threshold registers are used to set the Min/Max threshold limits that will be tested versus V<sub>SHUNT</sub> or V<sub>BUS</sub> readings. Measurement readings exceeding the respective V<sub>SHUNT</sub> or V<sub>BUS</sub> limits, either above or below, will set a register flag and perhaps an external interrupt depending on the configuration of the Interrupt Enable bit (INTREN) in register 09h. The testing of the ADC reading versus the respective threshold limits occurs once per ADC conversion.

(EQ. 3)

# SHUNT VOLTAGE THRESHOLD REGISTER 06h (READ/WRITE)

The V<sub>SHUNT</sub> minimum and maximum threshold limits are set using one register. The shunt value readings are either positive or negative. D15 and D7 bits of <u>Table 18</u> are given to represent the sign of the limit. SMX bits represent the upper limit threshold. SMN represents the lower threshold limit. <u>Equation 8</u> is the calculation used to convert the V<sub>SHUNT</sub> threshold binary value to decimal. Bit is the value of each bit set in the shunt threshold register. The value is either 1 or a 0. The weight of each bit is represented in <u>Table 18</u>. n is the bit number. The shunt voltage threshold LSB is 2.56mV.

$$Vs_{thresh} = \left[\sum_{n=0}^{7} \left(Bit_{n} \cdot Bit_{n}Weight_{n}\right)\right] \cdot VsThresh_{LSB}$$

(EQ. 8)

|        |        |       |       |       |       |       | . 10. 00. |      |      | 0411 |      |      |      |      |      |      |

|--------|--------|-------|-------|-------|-------|-------|-----------|------|------|------|------|------|------|------|------|------|

| BIT    | D15    | D14   | D13   | D12   | D11   | D10   | D9        | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | DO   |

| NAME   | Bit 15 | Bit14 | Bit13 | Bit12 | Bit11 | Bit10 | Bit9      | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| WEIGHT | -32768 | 16384 | 8192  | 4096  | 2048  | 1024  | 512       | 256  | 128  | 64   | 32   | 16   | 8    | 4    | 2    | 1    |

#### TABLE 16. CURRENT REGISTER, 04h

#### TABLE 17. POWER REGISTER, 03h

| BIT    | D15   | D14   | D13  | D12  | D11  | D10  | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  |

|--------|-------|-------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| NAME   | PD15  | PD14  | PD13 | PD12 | PD11 | PD10 | PD9 | PD8 | PD7 | PD6 | PD5 | PD4 | PD3 | PD2 | PD1 | PD0 |

| WEIGHT | 32768 | 16384 | 8192 | 4096 | 2048 | 1024 | 512 | 256 | 128 | 64  | 32  | 16  | 8   | 4   | 2   | 1   |

#### TABLE 18. SHUNT VOLTAGE THRESHOLD REGISTER, 06h

| BIT    | D15  | D14  | D13  | D12  | D11  | D10  | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | DO   |

|--------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| NAME   | Sign | SMX6 | SMX5 | SMX4 | SMX3 | SMX2 | SMX1 | SMX0 | Sign | SMN6 | SMN5 | SMN4 | SMN3 | SMN2 | SMN1 | SMN0 |

| WEIGHT | -128 | 64   | 32   | 16   | 8    | 4    | 2    | 1    | -128 | 64   | 32   | 16   | 8    | 4    | 2    | 1    |

#### TABLE 19. BUS VOLTAGE THRESHOLD REGISTER, 07h

| BIT    | D15  | D14  | D13  | D12  | D11  | D10  | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | DO   |

|--------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| NAME   | BMX7 | BMX6 | BMX5 | BMX4 | BMX3 | BMX2 | BMX1 | BMX0 | BMN7 | BMN6 | BMN5 | BMN4 | BMN3 | BMN2 | BMN1 | BMN0 |

| WEIGHT | 128  | 64   | 32   | 16   | 8    | 4    | 2    | 1    | 128  | 64   | 32   | 16   | 8    | 4    | 2    | 1    |

#### TABLE 20. INTERRUPT STATUS REGISTER, 08h

| BIT    | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3   | D2   | D1   | DO   |

|--------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|------|------|------|------|

| NAME   | NA  | NA  | NA  | NA  | NA  | NA  | NA | NA | NA | NA | NA | NA | SMXW | SMNW | BMXW | BMNW |

| WEIGHT | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0    | 0    |

#### TABLE 21. AUX CONTROL REGISTER, 09h

| BIT    | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8        | D7     | D6       | D5 | D4 | D3     | D2       | D1 | DO |

|--------|-----|-----|-----|-----|-----|-----|----|-----------|--------|----------|----|----|--------|----------|----|----|

| NAME   | NA  | NA  | NA  | NA  | NA  | NA  | NA | FORCEINTR | INTREN | ExtClkEn |    |    | ExtCLK | Div[5:0] |    |    |

| WEIGHT | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0         | 0      | 0        | 0  | 0  | 0      | 0        | 0  | 0  |

## BUS VOLTAGE THRESHOLD REGISTER 07h (READ/WRITE)

The V<sub>BUS</sub> minimum and maximum threshold limits are set using one register. The V<sub>BUS</sub> value readings range from 0V to 60V. <u>Table 19 on page 18</u> shows the register configuration and bit weights for the V<sub>BUS</sub> threshold register. BMX bits represent the upper limit threshold. BMN represents the lower threshold limit. <u>Equation 9</u> is the calculation used to convert the V<sub>BUS</sub> threshold binary value to decimal. Bit is the value of each bit set in the V<sub>BUS</sub> threshold register. The value is either 1 or a 0. The weight of each bit is represented in <u>Table 19</u>. n is the bit number. The V<sub>BUS</sub> voltage threshold LSB is 256mV.

$$Vb_{thresh} = \left[\sum_{n=0}^{7} \left(Bit_{n} \cdot Bit_{n}Weight_{n}\right)\right] \cdot VbThresh_{LSB}$$

(EQ. 9)

#### INTERRUPT STATUS REGISTER 08h (READ/WRITE)

The interrupt status register consists of a series of bit flags that indicate if an ADC reading has exceeded the readings respective limit. A 1 or high reading from a warning bit indicates the reading has exceeded the limit. To clear a warning, write a 1 or high to the set warning bit. Table 20 on page 18 shows the definition of the interrupt status register.

BMNW is the Bus voltage Minimum Warning. A "1" reading for this bit indicates the bus reading is below the bus voltage minimum threshold limit.

BMXW is the Bus voltage Maximum Warning. A "1" reading for this bit indicates the bus reading is above the bus voltage maximum threshold limit.

SMNW is the Shunt voltage Minimum Warning. A "1" reading for this bit indicates the shunt reading is below the shunt voltage minimum threshold limit.

SMXW is the Shunt voltage Maximum Warning. A "1" reading for this bit indicates the shunt reading is above the shunt voltage maximum threshold limit.

#### AUX CONTROL REGISTER 09h (READ/WRITE)

The Aux control register controls the functionality of the EXTCLK/INT pin of the ISL28022. <u>Table 21 on page 18</u> shows the definition of the register.

FORCEINTR is the Force Interrupt bit. Programming a 1 to the bit will force a 0 or a low at the EXTCLK/INT pin.

INTREN is the Interrupt Enable bit. Programming a 1 to the bit will allow for a threshold measurement violation to set the state of the EXTCLK/INT pin. With the INTREN set, any flag set from the interrupt status register will change the state of the EXTCLK/INT pin from 1 to a 0.

EXCLKEN is the External Clock Enable bit. Setting the bit enables the external clock. This also changes the EXTCLK/INT pin from an output to an input. The internal oscillator will shut down when the bit is enabled.

EXTCLKDIV are the External Clock Divider bits. The bits control an internal clock divider that are useful for fast system clocks. The internal clock frequency from pin to chip is represented in Equation 10:

$$freq_{internal} = \frac{f_{EXTCLK}}{(EXTCLKDIV+1)\cdot 2}$$

(EQ. 10)

$f_{\mbox{EXTCLK}}$  is the frequency of the signal driven to the  $\mbox{EXTCLK}/\mbox{INT}$  pin.  $\mbox{EXTCLKDIV}$  is the decimal value of the clock divide bits.

### **Serial Interface**

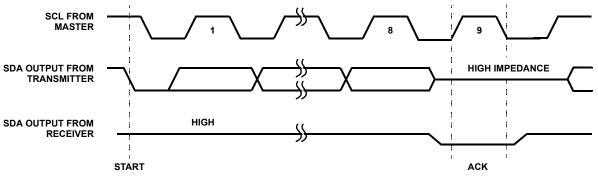

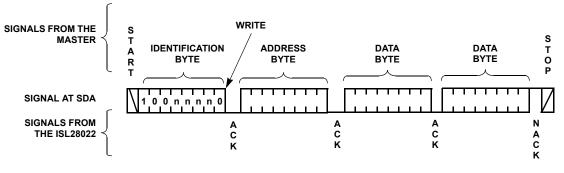

The ISL28022 supports a bidirectional bus oriented protocol. The protocol defines any device that sends data onto the bus as a transmitter and the receiving device as the receiver. The device controlling the transfer is the master and the device being controlled is the slave. The master always initiates data transfers and provides the clock for both transmit and receive operations. Therefore, the ISL28022 operates as a slave device in all applications.

The ISL28022 uses two bytes to transfer all reads and writes. All communication over the  $I^2C$  interface is conducted by sending the MSByte of each byte of data first, followed by the LSByte.

#### **Protocol Conventions**

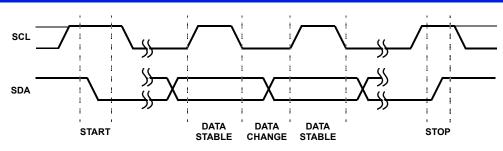

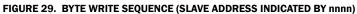

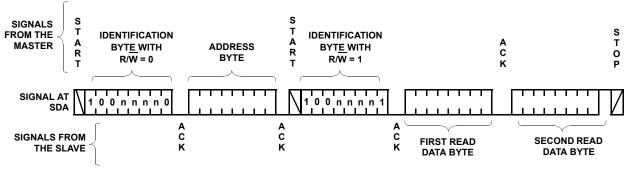

For normal operation, data states on the SDA line can change only during SCL LOW periods. SDA state changes during SCL HIGH are reserved for indicating START and STOP conditions (see <u>Figure 27</u>). On power-up of the ISL28022, the SDA pin is in the input mode.

All I<sup>2</sup>C interface operations must begin with a START condition, which is a HIGH to LOW transition of SDA while SCL is HIGH. The ISL28022 continuously monitors the SDA and SCL lines for the START condition and does not respond to any command until this condition is met (see <u>Figure 27</u>). A START condition is ignored during the power-up sequence.