## RENESAS Fast Automotive Sensor Signal Conditioner

## **Brief Description**

The ZSC31150 is a CMOS integrated circuit for highly accurate amplification and sensor-specific correction of bridge sensor signals. Digital compensation of sensor offset, sensitivity, temperature drift, and non-linearity is accomplished via an internal 16-bit RISC microcontroller running a correction algorithm, with calibration coefficients stored in an EEPROM.

The ZSC31150 is adjustable to nearly all bridge sensor types. Measured values are provided at the analog voltage output or at the digital ZACwire™ and I2C interface. The digital interface can be used for a simple PC-controlled calibration procedure in order to program a set of calibration coefficients into an on-chip EEPROM. A specific sensor and a ZSC31150 can be mated digitally: fast, precise, and without the cost overhead associated with trimming by external devices or a laser.

### **Features**

- Digital compensation of sensor offset, sensitivity, temperature drift, and non-linearity

- Adjustable to nearly all bridge sensor types

- Analog gain of up to 420

- Output options: ratiometric analog voltage output (5% to 95% maximum, 12.4-bit resolution) or ZACwire™ (digital one-wire-

- Temperature compensation: internal or external diode, bridge resistance, thermistor

- Sensor biasing by voltage or constant current

- Sample rate: up to 7.8kHz

- High voltage protection up to 33V

- Supply current: max. 5.5mA

- Reverse polarity and short-circuit protection

- Wide operation temperature depending on part number: up to -40°C to +150°C

- Traceability by user-defined EEPROM entries

- Safety and diagnostic functions

#### **Benefits**

- No external trimming components required

- Only a few external protection devices needed

- PC-controlled configuration and single pass calibration via I<sup>2</sup>C or ZACwire™ interface: simple, cost efficient, quick, and

- End-of-line calibration via I<sup>2</sup>C or ZACwire™ interface

- High accuracy (0.25% FSO at -25 to 85°C; 0.5% FSO at -40°C to 125°C)

- Excellent EMC/ESD robustness and AEC-Q100 qualification

## **Available Support**

- **Evaluation Kits**

- **Application Notes**

- Mass Calibration System

## **Physical Characteristics**

- Supply voltage: 4.5V to 5.5V

- Operation temperature: -40°C to 125°C (-40°C to +150°C extended temperature range)

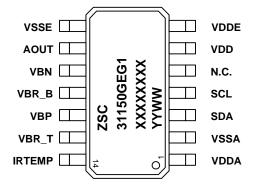

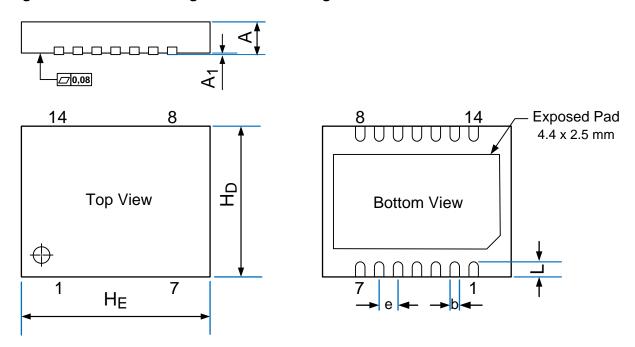

- Available as 14-DFN ( $5 \times 4$  mm; wettable flanks), SSOP14, and die

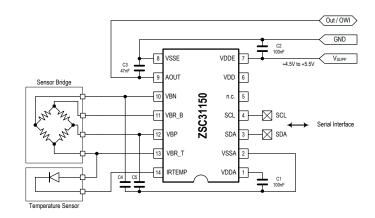

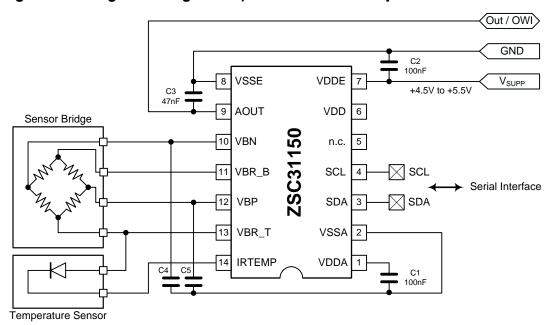

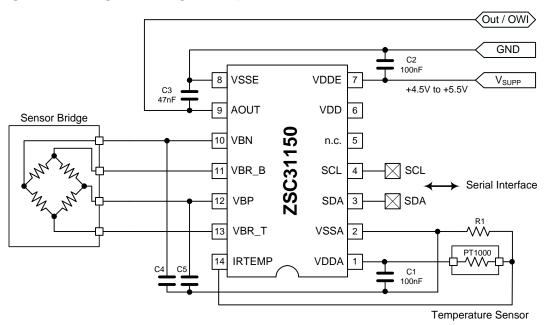

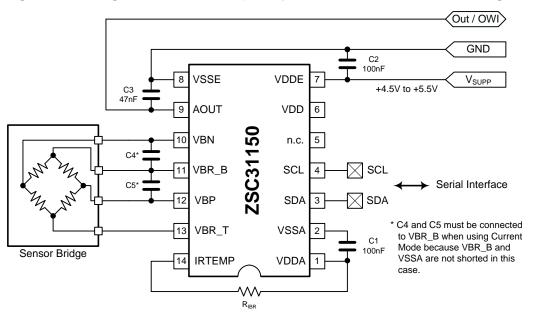

## **ZSC31150 Application Circuit**

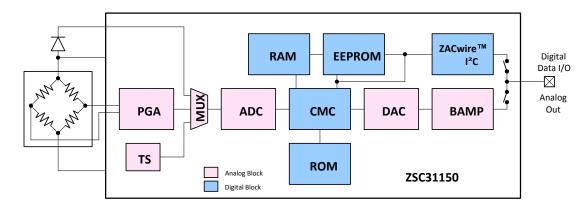

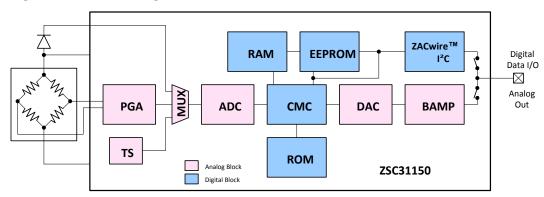

## ZSC31150 Block Diagram

## **Ordering Information**

| Sales Code      | Description                                                                                                                                                        | Package                                                                                        |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| ZSC31150GE      | ZSC31150 Die – Temperature range: -40°C to +150°C                                                                                                                  | Unsawn on Wafer: add "B" to sales code<br>Sawn on Wafer Frame: add "C"<br>Waffle Pack: add "D" |

| ZSC31150GEG2-R  | ZSC31150 14-DFN (5 $\times$ 4 mm; wettable flanks) – Temperature range: -40°C to 150°C                                                                             | Tape and Reel                                                                                  |

| ZSC31150GAG2-R  | ZSC31150 14-DFN (5 $\times$ 4 mm; wettable flanks) – Temperature range: -40°C to 125°C                                                                             | Tape and Reel                                                                                  |

| ZSC31150GAB     | ZSC31150 Die – Temperature range: -40°C to +125°C                                                                                                                  | Unsawn on Wafer                                                                                |

| ZSC31150GAC     | ZSC31150 Die – Temperature range: -40°C to +125°C                                                                                                                  | Sawn on Wafer Frame                                                                            |

| ZSC31150GEG1    | ZSC31150 14-SSOP – Temperature range: -40°C to +150°C                                                                                                              | Tube: add "-T" to sales code                                                                   |

| ZSC31150GLG1    | ZSC31150 14-SSOP – Temperature range: -40°C to +150°C (Long life: 5000h @150°C)                                                                                    | Tape & Reel: add "-R"                                                                          |

| ZSC31150GAG1    | ZSC31150 14-SSOP – Temperature range: -40°C to +125°C                                                                                                              |                                                                                                |

| ZSC31150KITV1P2 | ZSC31150 SSC Evaluation Kit V1.2: Three interconnecting boards, (software can be downloaded from product page at <a href="https://www.IDT.com/Z">www.IDT.com/Z</a> | •                                                                                              |

| ZSC31150MCSV1P1 | Modular Mass Calibration System (MSC) V1.1 for ZSC31150: MCS downloaded from product page)                                                                         | boards, cable, connectors (software can be                                                     |

## **Contents**

| 1.  | Elec | ectrical Characteristics                                             |    |

|-----|------|----------------------------------------------------------------------|----|

|     | 1.1  | 1 Absolute Maximum Ratings                                           |    |

|     | 1.2  | 2 Operating Conditions                                               |    |

|     | 1.3  | 3 Electrical Parameters                                              | 6  |

|     |      | 1.3.1 Supply Current and System Operation Conditions                 | 6  |

|     |      | 1.3.2 Analog Front-End (AFE) Characteristics                         | 6  |

|     |      | 1.3.3 Temperature Measurement [b]                                    | 6  |

|     |      | 1.3.4 Analog-to-Digital Conversion (ADC)                             |    |

|     |      | 1.3.5 Sensor Connection Check                                        |    |

|     |      | 1.3.6 Digital-to-Analog Conversion (DAC) and Analog Output (AOUT Pin | )  |

|     |      | 1.3.7 System Response                                                |    |

|     | 1.4  | 4 Interface Characteristics and EEPROM                               |    |

|     |      | 1.4.1 I <sup>2</sup> C Interface [a]                                 |    |

|     |      | 1.4.2 ZACwire™ One Wire Interface (OWI)                              |    |

|     |      | 1.4.3 EEPROM                                                         |    |

| 2.  | Circ | ircuit Description                                                   | 10 |

|     | 2.1  | 1 Signal Flow                                                        | 10 |

|     | 2.2  | 2 Application Modes                                                  | 10 |

|     | 2.3  | 3 Analog Front End (AFE)                                             | 1  |

|     |      | 2.3.1 Programmable Gain Amplifier (PGA)                              |    |

|     |      | 2.3.2 Offset Compensation                                            | 1  |

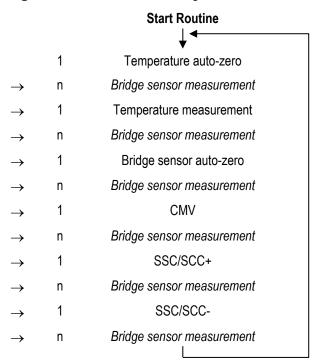

|     |      | 2.3.3 Measurement Cycle                                              | 12 |

|     |      | 2.3.4 Analog-to-Digital Converter                                    | 13 |

|     | 2.4  | 4 Temperature Measurement                                            | 15 |

|     | 2.5  | 5 System Control and Conditioning Calculation                        | 15 |

|     |      | 2.5.1 Operation Modes                                                | 15 |

|     |      | 2.5.2 Start Up Phase                                                 | 15 |

|     |      | 2.5.3 Conditioning Calculation                                       | 16 |

|     | 2.6  | 6 Analog Output AOUT                                                 | 16 |

|     | 2.7  |                                                                      |    |

|     | 2.8  | 8 Failsafe Features, Watchdog and Error Detection                    | 17 |

|     | 2.9  | -                                                                    |    |

| 3.  | Appl | oplication Circuit Examples                                          |    |

| 4.  |      | n Configuration, Latch-Up and ESD Protection                         |    |

|     |      |                                                                      |    |

|     |      | 2 ESD Protection                                                     |    |

| 5.  |      | ackage                                                               |    |

| - ' | 5.1  |                                                                      |    |

|     | 5.2  | -                                                                    |    |

|     |      |                                                                      |    |

| 6.    | Quality and Reliability                                                       | 22 |

|-------|-------------------------------------------------------------------------------|----|

| 7.    | Customization                                                                 | 22 |

| 8.    | Ordering Information                                                          | 23 |

| 9.    | Related Documents and Tools                                                   | 23 |

| 10.   | Glossary                                                                      | 24 |

| 11.   | Document Revision History                                                     | 25 |

| Lis   | st of Figures                                                                 |    |

| Figur | re 2.1 Block Diagram of the ZSC31150                                          | 10 |

| Figur | re 2.2 Measurement Cycle                                                      | 13 |

| Figur | re 3.1 Bridge in Voltage Mode, External Diode Temperature Sensor              | 18 |

| Figur | re 3.2 Bridge in Voltage Mode, External Thermistor                            | 19 |

| Figur | re 3.3 Bridge in Current Mode, Temperature Measurement via Bridge TC          | 19 |

| Figur | re 5.1 SSOP14 Pin Diagram                                                     | 21 |

| Figur | re 5.2 Outline Drawing for 14-DFN Package with Wettable Flanks                | 22 |

| Lis   | st of Tables                                                                  |    |

| Table | e 1.1 Absolute Maximum Ratings                                                | 5  |

|       | e 1.2 Operating Conditions                                                    |    |

|       | e 1.3 Electrical Parameters                                                   |    |

|       | e 1.4 Interface and EEPROM Characteristics                                    |    |

| Table | e 2.1 Adjustable Gains, Resulting Sensor Signal Spans, and Common Mode Ranges | 11 |

|       | e 2.2 Analog Zero Point Shift Ranges (XZC)                                    |    |

|       | e 2.3 Analog Output Resolution versus Sample Rate                             |    |

|       | e 3.1 Application Circuit Parameters                                          |    |

| Table | e 4.1 Pin Configuration and Latch-Up Conditions                               | 20 |

| Table | e 5.1 14-DFN Package Dimensions                                               | 22 |

### 1. Electrical Characteristics

## 1.1 Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. The ZSC31150 might not function or be operable above the recommended operating conditions. Stresses exceeding the absolute maximum ratings might also damage the device. In addition, extended exposure to stresses above the recommended operating conditions might affect device reliability. IDT does not recommend designing to the "Absolute Maximum Ratings."

Parameters apply in operation temperature range and without time limitations.

**Table 1.1 Absolute Maximum Ratings**

| No.   | Parameter                                 | Symbol                                 | Conditions                             | Min  | Max        | Unit |

|-------|-------------------------------------------|----------------------------------------|----------------------------------------|------|------------|------|

| 1.1.1 | Supply voltage [a]                        | VDDE                                   | To VSSE.                               | -33  | 33         | VDC  |

| 1.1.2 | Potential at the AOUT pin [a]             | V <sub>OUT</sub>                       | Relative to VSSE.                      | -33  | 33         | VDC  |

| 1.1.3 | Analog supply voltage [a]                 | VDDA                                   | Relative to VSSA.  VDDE - VDDA < 0.35V | -0.3 | 6.5        | VDC  |

| 1.1.4 | Voltage at all analog and digital IO pins | V <sub>A_IO</sub><br>V <sub>D_IO</sub> | Relative to VSSA.                      | -0.3 | VDDA + 0.3 | VDC  |

| 1.1.5 | Storage temperature                       | T <sub>STG</sub>                       |                                        | -55  | 150        | °C   |

<sup>[</sup>a] Refer to the ZSC31150 Technical Note – High Voltage Protection for specification and detailed conditions for high voltage protection.

## 1.2 Operating Conditions

All voltages are related to VSSA. See important table notes at the end of the table.

**Table 1.2 Operating Conditions**

| No.   | Parameter                                                                           | Symbol              | Conditions                                      | Min                    | Тур | Max | Unit |

|-------|-------------------------------------------------------------------------------------|---------------------|-------------------------------------------------|------------------------|-----|-----|------|

|       | TQE ambient temperature range for part numbers ZSC31150x <b>E</b> xx <sup>[a]</sup> | $T_{AMB\_TQE}$      | TQE                                             | -40                    |     | 150 | °C   |

| 1.2.1 | TQA ambient temperature range for part numbers ZSC31150x <b>A</b> xx <sup>[b]</sup> | $T_{AMB\_TQA}$      | TQA                                             | -40                    |     | 125 | °C   |

|       | TQI ambient temperature range for advanced performance [b]                          | $T_{AMB\_TQI}$      | TQI                                             | -25                    |     | 85  | °C   |

| 1.2.2 | Supply voltage                                                                      | VDDE                |                                                 | 4.5                    | 5.0 | 5.5 | VDC  |

| 1.2.3 | Bridge resistance—Bridge Voltage Mode [b], [c]                                      | $R_{BR\_V}$         |                                                 | 2                      |     | 25  | kΩ   |

| 1.2.4 | Bridge resistance—Bridge Current Excitation Mode [b], [c]                           | R <sub>BR_C</sub>   | See specification 1.2.6 for I <sub>BR_MAX</sub> |                        |     | 10  | kΩ   |

| 1.2.5 | Current reference resistor[b],[d]                                                   | R <sub>IBR</sub>    | $I_{BR} = VDDA / (16 * R_{IBR})$                | 0.07 * R <sub>BR</sub> |     |     | kΩ   |

| 1.2.6 | Maximum bridge current                                                              | I <sub>BR_MAX</sub> |                                                 |                        |     | 2   | mA   |

| No.   | Parameter                                    | Symbol              | Conditions                            | Min | Тур | Max                              | Unit  |

|-------|----------------------------------------------|---------------------|---------------------------------------|-----|-----|----------------------------------|-------|

| 1.2.7 | Maximum bridge top voltage                   | $V_{BR\_TOP}$       |                                       |     |     | (15/ <sub>16</sub> * VDDA) - 0.3 | V     |

| 1.2.8 | TC current reference resistor <sup>[b]</sup> | TC R <sub>IBR</sub> | Behavior influences current generated |     | 50  |                                  | ppm/K |

<sup>[</sup>a] Refer to the temperature profile description in the ZSC31150 Technical Note – Die and Package Specifications for operation in temperature range > 125°C.

#### 1.3 Electrical Parameters

All parameter values are valid for operating conditions specified in section 1.2 except as noted. All voltages related to VSSA. See important table notes at the end of the table.

**Table 1.3 Electrical Parameters**

| No.     | Parameter                                            | Symbol              | Conditions                                                                                              | Min                                                                                    | Тур  | Max                | Unit                 |  |  |  |

|---------|------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|--------------------|----------------------|--|--|--|

| 1.3.1   | 1.3.1 Supply Current and System Operation Conditions |                     |                                                                                                         |                                                                                        |      |                    |                      |  |  |  |

| 1.3.1.1 | Supply current                                       | Is                  | Without bridge and load current; $T_{AMB\_TQA}$ ; $f_{CLK} \le 3MHz$                                    |                                                                                        |      | 5.5                | mA                   |  |  |  |

| 1.3.1.2 | Clock frequency [a]                                  | fosc                | Guaranteed adjustment range (see the ZSC31150 Functional Description for details); T <sub>AMB_TQA</sub> | Guaranteed adjustment range 2 3 (see the ZSC31150 Functional Description for details); |      |                    |                      |  |  |  |

| 1.3.2 A | Analog Front-End (AFE) Character                     | istics              |                                                                                                         |                                                                                        |      |                    |                      |  |  |  |

| 1.3.2.1 | Input span                                           | V <sub>IN_SP</sub>  | Analog gain: 420 to 2.8                                                                                 | 1                                                                                      |      | 275                | mV/V                 |  |  |  |

| 1.3.2.2 | Analog offset compensation range                     |                     | Depends on gain adjust; refer to section 2.3.1                                                          | -300                                                                                   |      | 300                | % V <sub>IN_SP</sub> |  |  |  |

| 1.3.2.3 | Parasitic differential input offset                  | I <sub>IN_OFF</sub> | Within T <sub>AMB_TQE</sub>                                                                             | -10                                                                                    |      | 10                 | nA                   |  |  |  |

|         | current [a]                                          |                     | Within T <sub>AMB_TQI</sub>                                                                             | -2                                                                                     |      | 2                  | nA                   |  |  |  |

| 1.3.2.4 | Common mode input range                              | V <sub>IN_CM</sub>  | Depends on gain adjustment; no XZC; see section 2.3.1                                                   | 0.29 *<br>VDDA                                                                         |      | 0.65 *<br>VDDA     | V                    |  |  |  |

| 1.3.3 1 | emperature Measurement [b]                           |                     |                                                                                                         |                                                                                        |      |                    |                      |  |  |  |

| 1.3.3.1 | External temperature diode channel gain              | a <sub>TSED</sub>   | 300 13                                                                                                  |                                                                                        | 1300 | ppm FS<br>/ (mV/V) |                      |  |  |  |

| 1.3.3.2 | External temperature diode bias current              | I <sub>TSE</sub>    | 6 10                                                                                                    |                                                                                        | 20   | μΑ                 |                      |  |  |  |

<sup>[</sup>b] No measurement in mass production; parameter is guaranteed by design and/or quality observation.

<sup>[</sup>c] Symmetric behavior and identical electrical properties (especially with regard to the low pass characteristic) of both sensor inputs of the ZSC31150 are required. Unsymmetrical conditions of the sensor and/or external components connected to the sensor input pins of ZSC31150 can generate a failure in signal operation.

<sup>[</sup>d] See application circuit components in Table 3.1.

| No.     | Parameter                                              | Symbol                    | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Min  | Тур  | Max  | Unit               |

|---------|--------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------------------|

| 1.3.3.3 | External temperature diode input range [a]             |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0    |      | 1.5  | V                  |

| 1.3.3.4 | External temperature resistor channel gain             | a <sub>TSER</sub>         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1200 | 1200 |      | ppm FS<br>/ (mV/V) |

| 1.3.3.5 | External temperature resistor/ input voltage range [a] | V <sub>TSER</sub>         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0    |      | 600  | mV/V               |

| 1.3.3.6 | Internal temperature diode sensitivity                 | ST <sub>TSI</sub>         | Raw values – without conditioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 700  |      | 2700 | ppm FS<br>/ K      |

| 1.3.4   | Analog-to-Digital Conversion (ADC                      | C)                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      |                    |

| 1.3.4.1 | ADC resolution [a]                                     | r <sub>ADC</sub>          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13   |      | 16   | Bit                |

| 1.3.4.2 | ADC differential nonlinearity (DNL) [a]                | DNL <sub>ADC</sub>        | r <sub>ADC</sub> =13-bit; f <sub>CLK</sub> =3MHz;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |      | 0.95 | LSB                |

| 1.3.4.3 | ADC integral nonlinearity (INL) within TQA [a]         | INL <sub>ADC</sub>        | best fit, 2nd order; complete AFE; with ADC input range specified in 1.3.4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |      | 4    | LSB                |

| 1.3.4.4 | ADC INL within TQE                                     | INL <sub>ADC</sub>        | opening in the state of the sta |      |      | 5    | LSB                |

| 1.3.4.5 | ADC input range                                        | Range                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10   |      | 90   | %VDDA              |

| 1.3.5   | Sensor Connection Check                                |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      |                    |

| 1.3.5.1 | Sensor connection loss detection threshold             | R <sub>SCC_min</sub>      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100  |      |      | kΩ                 |

| 1.3.5.2 | Sensor input short check                               | R <sub>SSC_short</sub>    | Short detection guaranteed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0    |      | 50   | Ω                  |

| 1.3.5.3 | Sensor input no-short threshold                        | R <sub>SSC_pass</sub>     | A short is not indicated above this threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1000 |      |      | Ω                  |

| 1.3.6   | Digital-to-Analog Conversion (DAG                      | C) and Analo              | g Output (AOUT Pin)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |      |      |                    |

| 1.3.6.1 | DAC resolution                                         | r <sub>DAC</sub>          | Analog output, 10-90%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 12   |      | Bit                |

| 1.3.6.2 | Output current sink and source                         | I <sub>SRC/SINK_OUT</sub> | $V_{OUT}$ : 5-95%, $R_{LOAD} \ge 2k\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      | 2.5  | mA                 |

|         | for VDDE=5V                                            |                           | V <sub>OUT</sub> : 10-90%, R <sub>LOAD</sub> ≥ 1kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |      | 5    | mA                 |

| 1.3.6.3 | Short circuit current                                  | I <sub>OUT_max</sub>      | To VSSE or VDDE [0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -25  |      | 25   | mA                 |

| 1.3.6.4 | Addressable output signal                              | V <sub>SR_OUT95</sub>     | $\bigcirc$ R <sub>LOAD</sub> $\geq$ 2k $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.05 |      | 0.95 | VDDE               |

|         | range                                                  | V <sub>SR_OUT90</sub>     | $@ R_{LOAD} \ge 1k\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.1  |      | 0.9  | VDDE               |

| 1.3.6.5 | Output slew rate [a]                                   | SR <sub>OUT</sub>         | C <sub>LOAD</sub> < 50nF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.1  |      |      | V/µs               |

| 1.3.6.6 | Output resistance in diagnostic mode                   | Rout_dia                  | Diagnostic Range:<br>$<4 96>\%$ , $R_{LOAD} \ge 2k\Omega$<br>$<8 92>\%$ , $R_{LOAD} \ge 1k\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |      | 82   | Ω                  |

| 1.3.6.7 | Load capacitance [a]                                   | C <sub>LOAD</sub>         | C3 (see section 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |      | 150  | nF                 |