#### RAA215300

High Performance 9-Channel PMIC Supporting DDR Memory, with Built-In Charger and RTC

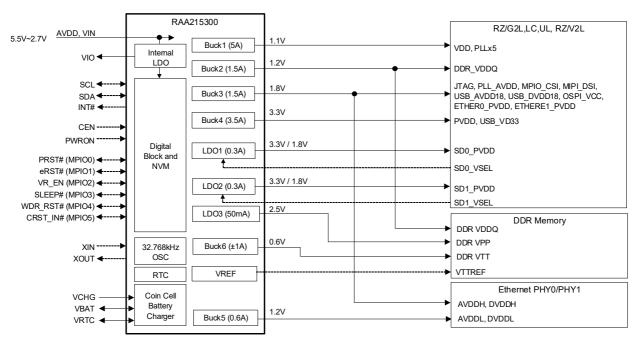

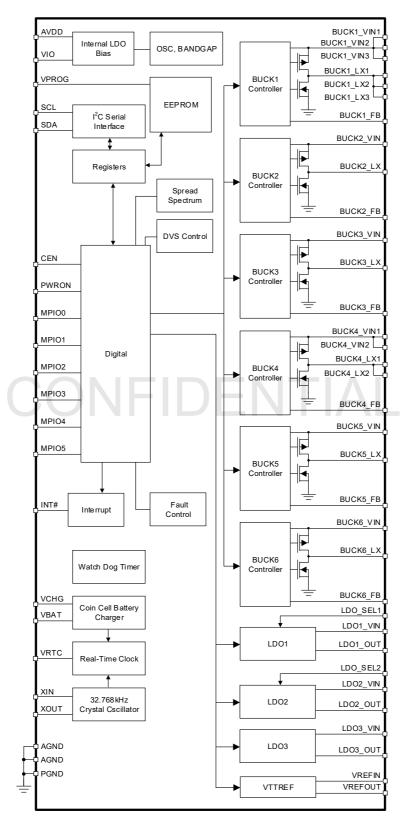

The RAA215300 is a high-performance, low-cost 9-channel PMIC designed for 32-bit and 64-bit MCU and MPU applications. It supports DDR3, DDR3L, DDR4, and LPDDR4 memory power requirements. The internally compensated regulators, built-in Real-Time Clock (RTC), 32kHz crystal oscillator, and coin cell battery charger provide a highly integrated, small footprint power solution ideal for System-On-Module (SOM) applications. A spread spectrum feature provides an ease-of-use solution for noise-sensitive audio or RF applications.

The RAA215300 has six high-efficiency buck regulators and three LDOs to provide a complete power system. The internal device registers and EEPROM can configure and optimize the RAA215300 for different application requirements, for example, power sequences, output voltages, and switching frequencies. Dynamic Voltage Scaling (DVS) and Sleep modes are supported.

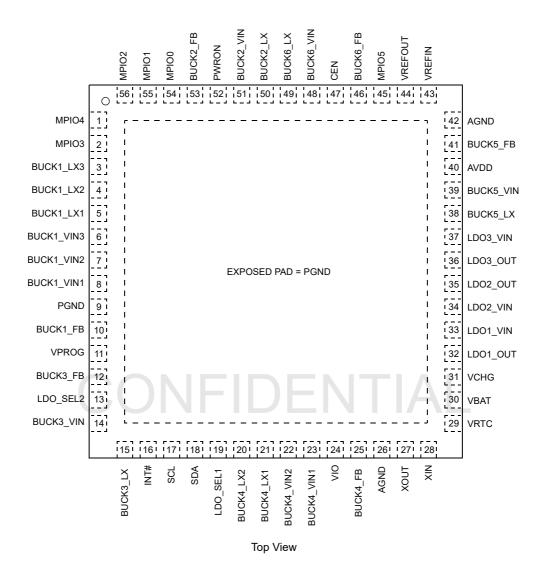

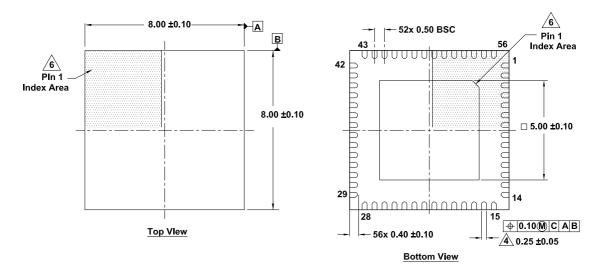

The RAA215300 is available in an 8x8mm, 0.5mm pitch thermally enhanced 56-lead QFN package and is specified for operation across a -40°C to 105°C ambient and -40°C to 125°C junction temperature range.

#### **Features**

- Input operating voltage range: 2.7V~5.5V

- 6 synchronous buck regulators (supporting 5A, 3.5A, 2x1.5A, 1A, 0.6A), with settable V<sub>OUT</sub>

- 3 LDOs (supporting 2x300mA, 50mA), with bypass mode, and settable V<sub>OUT</sub>

- Dedicated VTTREF for DDR memory

- Auto PFM/PWM, FPWM and ultrasonic modes, with selectable PWM f<sub>SW</sub>

- Built-in 32kHz crystal oscillator (with bypass), RTC, and coin cell/supercapacitor battery charger

- DVS and sleep modes

- Internally compensated

- Spread spectrum

- I<sup>2</sup>C serial interface (up to 1MHz)

- Pb-free (RoHS compliant)

### **Applications**

- MCU/MPU/SoC consumer and industrial power

- FPGA system power

- Building/factory automation system power

Figure 1. Typical Application Diagram - MPU Power

# **Contents**

| 1. | Overview 5 |                                                                                  |     |  |  |  |  |

|----|------------|----------------------------------------------------------------------------------|-----|--|--|--|--|

|    | 1.1        | Block Diagram                                                                    | . 5 |  |  |  |  |

| 2. | Pin Ir     | nformation                                                                       | . 6 |  |  |  |  |

|    | 2.1        | Pin Assignments                                                                  | . 6 |  |  |  |  |

|    | 2.2        | Pin Descriptions                                                                 |     |  |  |  |  |

| 3. | Spec       | ifications                                                                       | . 9 |  |  |  |  |

| •. | 3.1        | Absolute Maximum Ratings                                                         |     |  |  |  |  |

|    | 3.2        | ESD Ratings                                                                      |     |  |  |  |  |

|    | 3.3        | Thermal Information                                                              |     |  |  |  |  |

|    | 3.4        | Recommended Operation Conditions                                                 | 10  |  |  |  |  |

|    | 3.5        | Electrical Specifications                                                        | 10  |  |  |  |  |

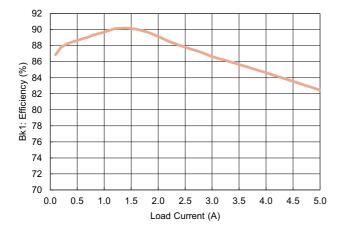

| 4. | Typic      | cal Performance Graphs                                                           | 26  |  |  |  |  |

| 5. | Seria      | al Interface                                                                     | 27  |  |  |  |  |

|    | 5.1        | I <sup>2</sup> C General Operation                                               | 27  |  |  |  |  |

|    |            | 5.1.1 Data Validity                                                              |     |  |  |  |  |

|    |            | 5.1.2 START and STOP Condition                                                   | 27  |  |  |  |  |

|    |            | 5.1.3 Byte Format                                                                | 27  |  |  |  |  |

|    |            | 5.1.4 Acknowledge (ACK)                                                          | 27  |  |  |  |  |

|    |            | 5.1.5 Not Acknowledge (NACK)                                                     |     |  |  |  |  |

|    |            | 5.1.6 Device Address and R/W Bit                                                 | 28  |  |  |  |  |

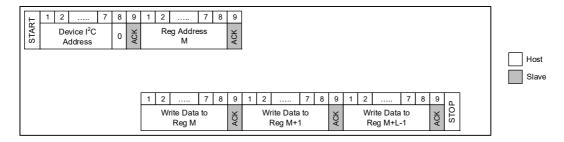

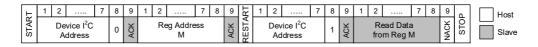

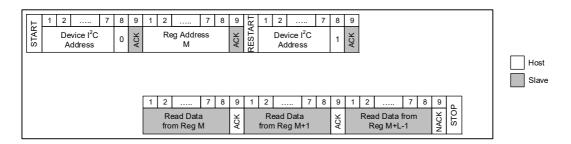

|    | 5.2        | Device Communication Protocol                                                    |     |  |  |  |  |

|    |            | 5.2.1 7-bit Device Addresses                                                     | 28  |  |  |  |  |

|    |            | 5.2.2       Register Size                                                        | 28  |  |  |  |  |

|    |            |                                                                                  |     |  |  |  |  |

|    |            | 5.2.4 I <sup>2</sup> C Read Operation                                            |     |  |  |  |  |

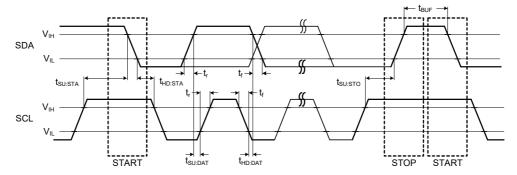

|    | <b>-</b> 0 | 5.2.5 I <sup>2</sup> C Timing                                                    |     |  |  |  |  |

|    | 5.3        | Unimplemented Registers                                                          |     |  |  |  |  |

| 6. | •          | sters and EEPROM                                                                 |     |  |  |  |  |

|    | 6.1        | EEPROM                                                                           |     |  |  |  |  |

|    |            | 6.1.1 Writing to the EEPROM                                                      |     |  |  |  |  |

|    | 0.0        | 6.1.2 Recalling the EEPROM                                                       |     |  |  |  |  |

|    | 6.2        | EEPROM Error Correction                                                          |     |  |  |  |  |

| _  | _          |                                                                                  |     |  |  |  |  |

| 7. |            | er Supplies                                                                      |     |  |  |  |  |

|    | 7.1        | Internal LDO (VIO)                                                               |     |  |  |  |  |

| _  | 7.2        | VCHG, VBAT, and VRTC                                                             |     |  |  |  |  |

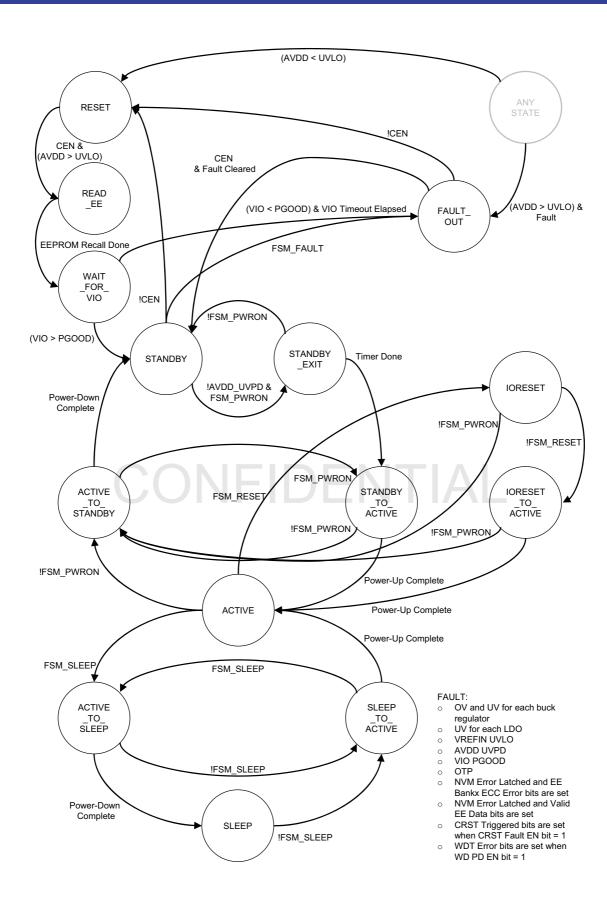

| 8. |            | rating {States} and Transition Conditions                                        |     |  |  |  |  |

|    | 8.1        | {RESET}                                                                          |     |  |  |  |  |

|    | 8.2<br>8.3 | {READ_EE}                                                                        |     |  |  |  |  |

|    | 8.4        | {\text{VVAIT_FOR_VIO} \\ \{\text{STANDBY}} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \ |     |  |  |  |  |

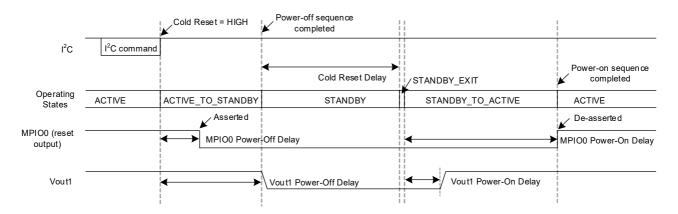

|    | J          | 8.4.1 {STANDBY_EXIT}                                                             |     |  |  |  |  |

|    |            | 8.4.2 {STANDBY_TO_ACTIVE}                                                        |     |  |  |  |  |

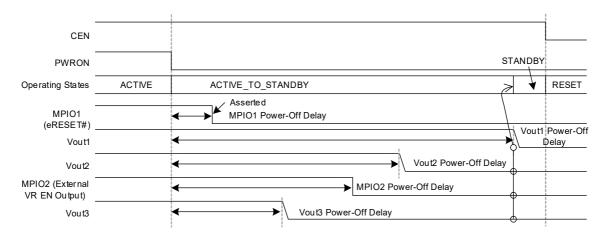

|    |            | 8.4.3 {ACTIVE_TO_STANDBY}                                                        |     |  |  |  |  |

|    | 8.5        | {ACTIVE}                                                                         | 34  |  |  |  |  |

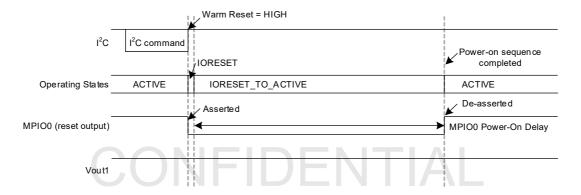

|    | 8.6        | {IORESET}                                                                        | 35  |  |  |  |  |

## RAA215300 Datasheet

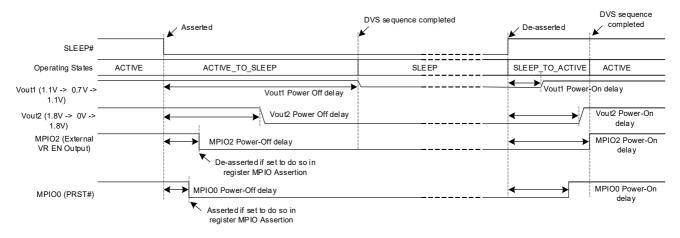

|                                        | 8.7  | 8.6.1<br>{SLEEP} | {IORESET_TO_ACTIVE}                     |          |

|----------------------------------------|------|------------------|-----------------------------------------|----------|

|                                        |      |                  | {ACTIVE_TO_SLEEP}                       |          |

|                                        |      | 8.7.2            | {SLEEP_TO_ACTIVE}                       | 35       |

|                                        | 8.8  | {FAULT_          | OUT}                                    | 35       |

| 9                                      | Func | tional Blo       | ocks and Application Information        | 37       |

| 9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9 |      |                  |                                         |          |

|                                        |      | •                | ше                                      |          |

|                                        |      |                  | pose I/O                                |          |

|                                        |      | 9.3.1            | Unused MPIOx Pin                        | 38       |

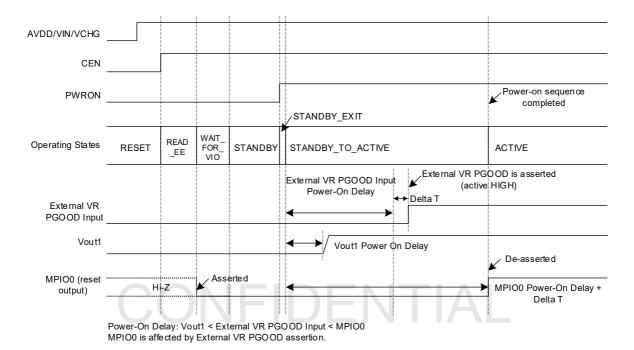

|                                        |      | 9.3.2            | External VR PGOOD Input                 | 38       |

|                                        |      | 9.3.3            | Input to I <sup>2</sup> C Register      | 40       |

|                                        |      | 9.3.4            | PGOOD Output                            | 40       |

|                                        |      | 9.3.5            | Reset Output                            | 40       |

|                                        |      | 9.3.6            | External VR EN Output                   | 40       |

|                                        |      | 9.3.7            | Output to I <sup>2</sup> C Register     | 40       |

|                                        |      | 9.3.8            | 32kHz Clock (32K_CLK)                   | 40       |

|                                        |      | 9.3.9            | SLEEP#                                  | 41       |

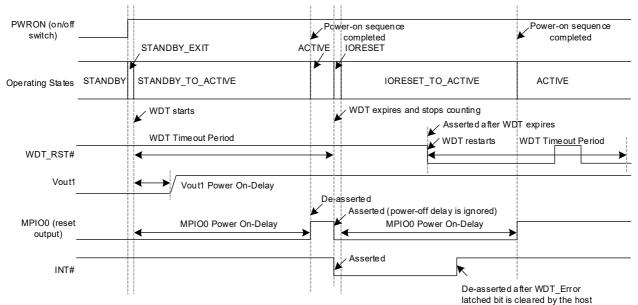

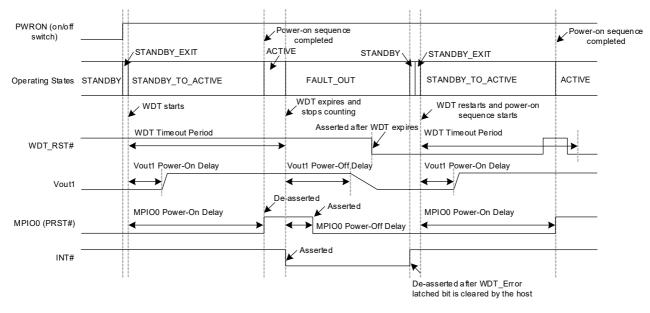

|                                        |      | 9.3.10           | WDT_RST#                                | 41       |

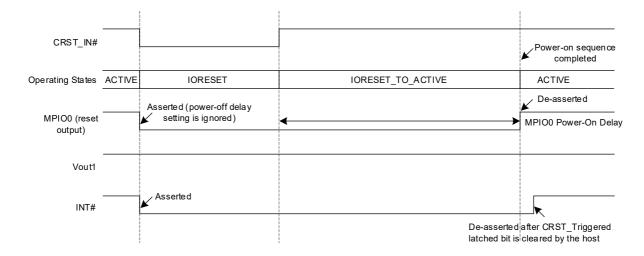

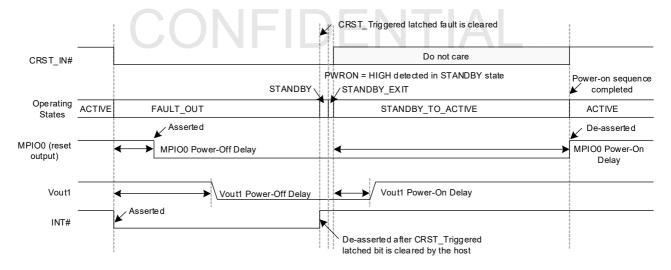

|                                        |      | 9.3.11           | CRST_IN#                                | 41       |

|                                        |      | 9.3.12           | Alternative Decodes for MPIOx functions | 43       |

|                                        | 9.4  |                  | g Timer                                 |          |

|                                        | 9.5  |                  | equencing                               |          |

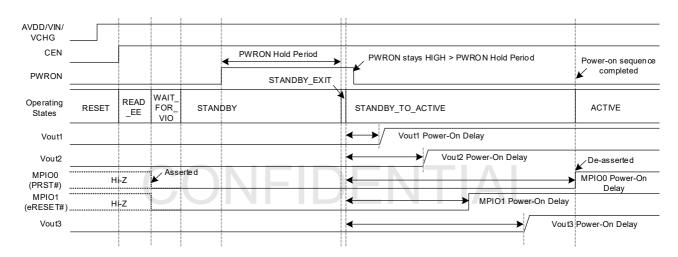

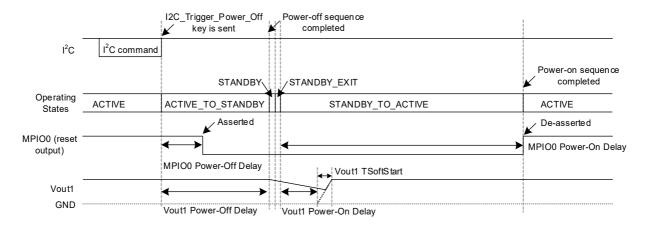

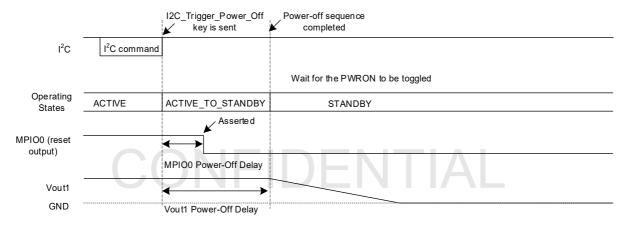

|                                        |      | 9.5.1            | Power-ON                                | 45       |

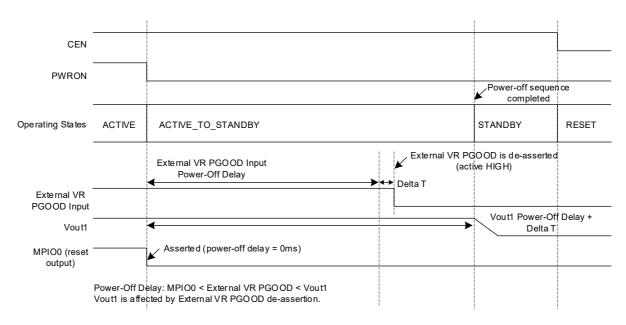

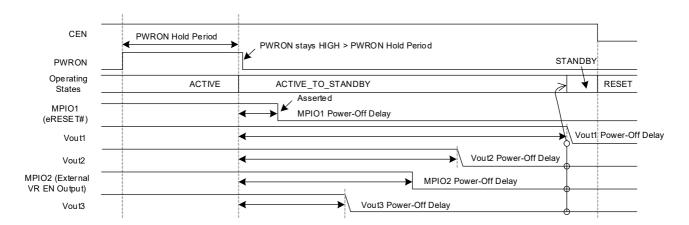

|                                        | 0.0  | 9.5.2            | Power-OFF                               | 45       |

|                                        |      | Output D         | d Cold Resetischarge                    | 48<br>40 |

|                                        |      |                  | isonarye                                |          |

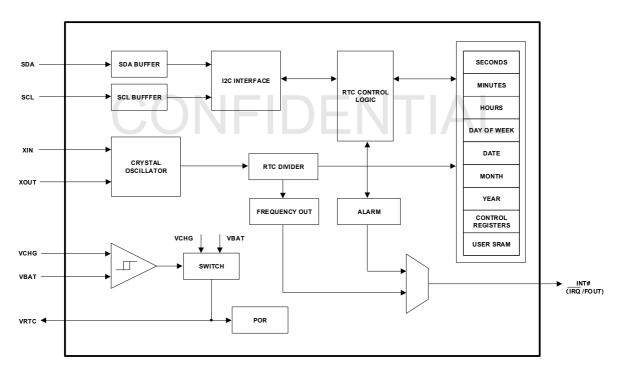

|                                        | 9.9  |                  | e Clock                                 |          |

|                                        |      | 9.9.1            | Clock                                   | 50       |

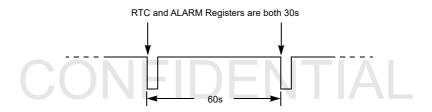

|                                        |      | 9.9.2            | Alarm                                   | 51       |

|                                        |      | 9.9.3            | Frequency Output                        |          |

|                                        |      | 9.9.4            | General Purpose User SRAM               | 52       |

|                                        |      | 9.9.5            | Power Control Operation                 | 52       |

|                                        |      | 9.9.6            | Power Failure Detection                 | 52       |

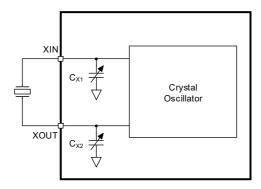

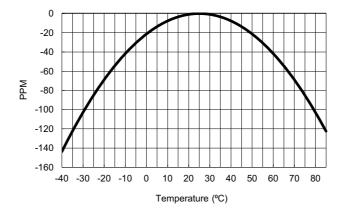

|                                        |      | 9.9.7            | Crystal Oscillator                      | 52       |

|                                        |      | 9.9.8            | Using an External Clock                 | 55       |

|                                        |      | 9.9.9            | Real-Time Clock Registers               | 55       |

|                                        | 9.10 |                  | Battery Charger                         |          |

|                                        |      | 9.10.1           | Supercapacitor Backup Time              |          |

|                                        | 9.11 | •                | gulators                                |          |

|                                        |      | 9.11.1           | Buck1                                   |          |

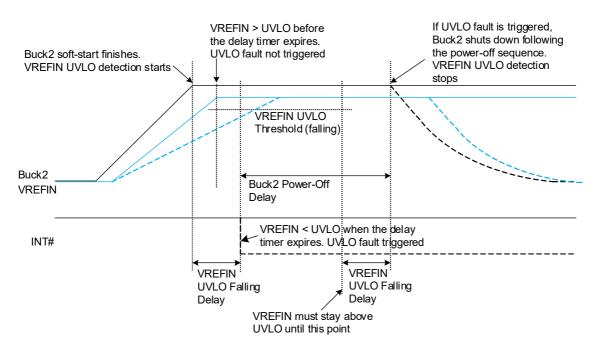

|                                        |      | 9.11.2           | Buck2                                   |          |

|                                        |      | 9.11.3           | Buck3                                   |          |

|                                        |      | 9.11.4           | Buck4                                   |          |

|                                        |      | 9.11.5           | Buck5                                   |          |

|                                        |      | 9.11.6           | Buck6                                   |          |

|                                        |      | 9.11.7<br>9.11.8 | Buck Operating Modes                    |          |

|                                        |      |                  | Ultrasonic Mode                         |          |

|                                        |      | J. 11.9          | UIIUSEU DUUN                            | υı       |

## RAA215300 Datasheet

|     |        | 9.11.10 Switching Frequency                | 61                                                                                                    |  |

|-----|--------|--------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

|     |        | 9.11.11 Spread Spectrum                    | 61                                                                                                    |  |

|     |        | 9.11.12 Phase Synchronization              | 62                                                                                                    |  |

|     | 9.12   | LDO Regulators                             | 62                                                                                                    |  |

|     |        | 9.12.1 LDO1/2                              | 62                                                                                                    |  |

|     |        | 9.12.2 LDO3                                | 62                                                                                                    |  |

|     |        | 9.12.3 LDOx Bypass                         | 63                                                                                                    |  |

|     |        | 9.12.4 Unused LDOx                         | 63                                                                                                    |  |

|     | 9.13   | VTTREF                                     |                                                                                                       |  |

|     |        | 9.13.1 Unused VTTREF                       | 63                                                                                                    |  |

|     | 9.14   | Pre-bias Startup                           |                                                                                                       |  |

|     | 9.15   | Device Monitors, Warnings, and Protections |                                                                                                       |  |

|     |        | · · · · · · · · · · · · · · · · · · ·      |                                                                                                       |  |

|     |        |                                            |                                                                                                       |  |

|     |        |                                            |                                                                                                       |  |

|     |        | , e e e e e e e e e e e e e e e e e e e    |                                                                                                       |  |

|     |        |                                            |                                                                                                       |  |

|     |        |                                            |                                                                                                       |  |

|     |        | •                                          |                                                                                                       |  |

|     |        |                                            |                                                                                                       |  |

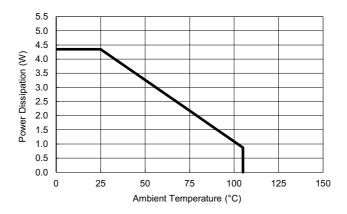

|     | 9.16   | Maximum Recommended Power Dissipation      | 68                                                                                                    |  |

| 10. | Exter  | nal Component Selection                    | read Spectrum  ase Synchronization  56 ase Synchronization  67 50 50 50 50 50 50 50 50 50 50 50 50 50 |  |

|     | 10.1   | Output Filters                             | 68                                                                                                    |  |

|     |        | 10.1.1 Inductor Selection                  | 69                                                                                                    |  |

|     |        | 10.1.2 Output Capacitor Selection          | 69                                                                                                    |  |

|     | 10.2   | Input Capacitor Selection                  | 69                                                                                                    |  |

|     | 10.3   | Recommended External Components            |                                                                                                       |  |

|     | 10.4   | Recommended Effective Capacitance          | 72                                                                                                    |  |

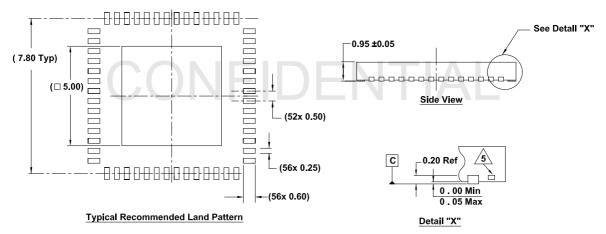

| 11. | Layo   | ut Guidelines                              | 73                                                                                                    |  |

|     | 11.1   | Power Ground (PGND)                        | 73                                                                                                    |  |

|     | 11.2   | Analog Ground (AGND)                       |                                                                                                       |  |

|     | 11.3   | Digital Ground                             | 73                                                                                                    |  |

|     | 11.4   | Exposed Pad (EPAD)                         |                                                                                                       |  |

|     | 11.5   | Buck Regulators                            |                                                                                                       |  |

|     | 11.6   |                                            |                                                                                                       |  |

|     | 11.7   | ·                                          |                                                                                                       |  |

|     | 11.8   | •                                          |                                                                                                       |  |

| 12. | _      |                                            |                                                                                                       |  |

|     | 12.1   | Register Map Detail                        | 78                                                                                                    |  |

| 13. | Pack   | age Outline Drawing                        | 24                                                                                                    |  |

| 14. | Part I | Number Differences                         | 25                                                                                                    |  |

|     |        |                                            |                                                                                                       |  |

|     |        |                                            |                                                                                                       |  |

| 1 5 | Orda   | -                                          |                                                                                                       |  |

|     |        | -                                          |                                                                                                       |  |

| 16. | Revis  | sion History     .                         | 26                                                                                                    |  |

## 1. Overview

## 1.1 Block Diagram

Figure 2. Block Diagram

## 2. Pin Information

## 2.1 Pin Assignments

# 2.2 Pin Descriptions

| Pin Number | Pin Name                  | Туре         | Description                             |

|------------|---------------------------|--------------|-----------------------------------------|

| 1          | MPIO4 <sup>[1]</sup>      | Input/Output | Multiple general purpose input-output 4 |

| 2          | MPIO3 <sup>[1]</sup>      | Input/Output | Multiple general purpose input-output 3 |

| 3          | BUCK1_LX3                 | Output       | Buck1 switch node                       |

| 4          | BUCK1_LX2                 | Output       | Buck1 switch node                       |

| 5          | BUCK1_LX1                 | Output       | Buck1 switch node                       |

| 6          | BUCK1_VIN3 <sup>[2]</sup> | Power        | Buck1 supply                            |

| 7          | BUCK1_VIN2 <sup>[2]</sup> | Power        | Buck1 supply                            |

| 8          | BUCK1_VIN1 <sup>[2]</sup> | Power        | Buck1 supply                            |

| 9          | PGND                      | Ground       | Power ground                            |

| Pin Number | Pin Name                 | Туре         | Description                                                                                                                                                    |

|------------|--------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10         | BUCK1_FB                 | Input        | Buck1 feedback                                                                                                                                                 |

| 11         | VPROG                    | Power        | High voltage supply input for EEPROM programming. Connect to ground in typical application.                                                                    |

| 12         | BUCK3_FB                 | Input        | Buck3 feedback                                                                                                                                                 |

| 13         | LDO_SEL2                 | Input        | Logic input. Select LDO2 output voltage.                                                                                                                       |

| 14         | BUCK3_VIN <sup>[2]</sup> | Power        | Buck3 supply                                                                                                                                                   |

| 15         | BUCK3_LX                 | Output       | Buck3 switch node                                                                                                                                              |

| 16         | INT#                     | Output       | Interrupt output, open-drain, active low. It can also be configured as clock signal output in Frequency Output (FOUT) mode of the RTC.                         |

| 17         | SCL                      | Input        | I <sup>2</sup> C serial clock                                                                                                                                  |

| 18         | SDA                      | Input/Output | Bidirectional I <sup>2</sup> C serial data                                                                                                                     |

| 19         | LDO_SEL1                 | Input        | Logic input. Select LDO1 output voltage.                                                                                                                       |

| 20         | BUCK4_LX2                | Output       | Buck4 switch node                                                                                                                                              |

| 21         | BUCK4_LX1                | Output       | Buck4 switch node                                                                                                                                              |

| 22         | BUCK4_VIN2[2]            | Power        | Buck4 supply                                                                                                                                                   |

| 23         | BUCK4_VIN1[2]            | Power        | Buck4 supply                                                                                                                                                   |

| 24         | VIO                      | Output       | Internal 1.8V LDO output                                                                                                                                       |

| 25         | BUCK4_FB                 | Input        | Buck4 feedback                                                                                                                                                 |

| 26, 42     | AGND                     | Ground       | Analog and digital ground                                                                                                                                      |

| 27         | XOUT                     | Output       | Crystal oscillator output. Connect to ground if not used.                                                                                                      |

| 28         | XIN                      | Input        | Crystal oscillator input. Connect to ground if not used.                                                                                                       |

| 29         | VRTC                     | Power        | Real-time clock (RTC) power supply. An output that provides power to the RTC and is generated internally from the higher of VBAT and VCHG.                     |

| 30         | VBAT                     | Power        | Charger output to coin cell battery or supercapacitor, or RTC input supply when running from coin cell battery or supercapacitor. If not used, connect to GND. |

| 31         | VCHG                     | Power        | Input Supply for VIO LDO, Coin cell battery charger and RTC input power. AVDD, VCHG, and BUCKx_VINx must be the same voltage.                                  |

| 32         | LDO1_OUT                 | Output       | LDO1 output                                                                                                                                                    |

| 33         | LDO1_VIN                 | Power        | LDO1 supply                                                                                                                                                    |

| 34         | LDO2_VIN                 | Power        | LDO2 supply                                                                                                                                                    |

| 35         | LDO2_OUT                 | Output       | LDO2 output                                                                                                                                                    |

| 36         | LDO3_OUT                 | Output       | LDO3 output                                                                                                                                                    |

| 37         | LDO3_VIN                 | Power        | LDO3 supply                                                                                                                                                    |

| 38         | BUCK5_LX                 | Output       | Buck5 switch node                                                                                                                                              |

| 39         | BUCK5_VIN <sup>[2]</sup> | Power        | Buck5 supply                                                                                                                                                   |

| 40         | AVDD                     | Power        | Analog and digital supply. AVDD, VCHG, and BUCKx_VINx must be the same voltage.                                                                                |

| 41         | BUCK5_FB                 | Input        | Buck5 feedback                                                                                                                                                 |

| 43         | VREFIN                   | Input        | Input to VTTREF block.  Note: Pin has a 1MΩ (typical) internal resistor to GND.                                                                                |

| Pin Number | Pin Name                 | Туре         | Description                                                                                   |

|------------|--------------------------|--------------|-----------------------------------------------------------------------------------------------|

| 44         | VREFOUT                  | Output       | Output from VTTREF block, with value equal to (VREFIN/2). Used as reference for VTT.          |

| 45         | MPIO5 <sup>[1]</sup>     | Input/Output | Configurable multiple purpose input-output 5                                                  |

| 46         | BUCK6_FB                 | Input        | Buck6 feedback                                                                                |

| 47         | CEN                      | Input        | Chip enable, active high                                                                      |

| 48         | BUCK6_VIN <sup>[2]</sup> | Power        | Buck6 supply                                                                                  |

| 49         | BUCK6_LX                 | Output       | Buck6 switch node                                                                             |

| 50         | BUCK2_LX                 | Output       | Buck2 switch node                                                                             |

| 51         | BUCK2_VIN <sup>[2]</sup> | Power        | Buck2 supply                                                                                  |

| 52         | PWRON                    | Input        | Regulator output enable                                                                       |

| 53         | BUCK2_FB                 | Input        | Buck2 feedback                                                                                |

| 54         | MPIO0 <sup>[1]</sup>     | Input/Output | Configurable multiple purpose input-output 0                                                  |

| 55         | MPIO1 <sup>[1]</sup>     | Input/Output | Configurable multiple purpose input-output 1                                                  |

| 56         | MPIO2 <sup>[1]</sup>     | Input/Output | Configurable multiple purpose input-output 2                                                  |

| -          | EPAD                     | Ground       | Exposed thermal pad. Power ground. All regulator PGNDs are internally downbonded to the EPAD. |

- 1. See Multi Purpose I/O for pin function mapping.

- 2. All buck supplies (BUCKx\_VINx) = AVDD = VCHG.

# 3. Specifications

## 3.1 Absolute Maximum Ratings

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                 | Minimum | Maximum | Unit |  |  |  |  |

|-------------------------------------------|---------|---------|------|--|--|--|--|

| Voltage (to PGND unless otherwise stated) |         |         |      |  |  |  |  |

| BUCKx_VINx, AVDD, VCHG                    | -0.3    | 6       | V    |  |  |  |  |

| VBAT                                      | -0.3    | 6       | V    |  |  |  |  |

| BUCKx_FB                                  | -0.3    | 6       | V    |  |  |  |  |

| BUCKx_LXx                                 | -0.3    | 6       | V    |  |  |  |  |

| BUCKx_LXx <sup>[1]</sup>                  |         | 6.7     | V    |  |  |  |  |

| AGND, PGND                                | -0.3    | 0.3     | V    |  |  |  |  |

| VPROG                                     | -0.3    | 24      | V    |  |  |  |  |

| All other pins                            | -0.3    | 6       | V    |  |  |  |  |

<sup>1. ≤20</sup>ns duration

## 3.2 ESD Ratings

| ESD Model/Test                                  | Rating | Unit |

|-------------------------------------------------|--------|------|

| Human Body Model (Tested per JS-001-2017)       | ±2     | kV   |

| Charged Device Model (Tested per JS-002-2018)   | ±500   | V    |

| Latch-Up (Tested per JESD78E; Class 2, Level A) | 100    | mA   |

## 3.3 Thermal Information

| Thermal Resistance (Typical) | θ <sub>JA</sub> (°C/W) <sup>[1]</sup> | θ <sub>JC</sub> (°C/W) <sup>[2]</sup> |

|------------------------------|---------------------------------------|---------------------------------------|

| 56LD, 8x8mm QFN Package      | 23                                    | 0.7                                   |

θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features. See TB379.

<sup>2.</sup> For  $\theta_{\text{JC}}$ , the case temperature location is the center of the exposed metal pad on the package underside.

| Parameter                                           | Minimum | Maximum   | Unit |

|-----------------------------------------------------|---------|-----------|------|

| Maximum Junction Temperature (T <sub>J</sub> )      |         | +150      | °C   |

| Maximum Storage Temperature Range (T <sub>S</sub> ) | -65     | +150      | °C   |

| Pb-Free Reflow Profile                              |         | see TB493 |      |

## 3.4 Recommended Operation Conditions

Voltages referred to PGND unless otherwise stated.

| Parameter                                             | Minimum | Maximum | Unit |

|-------------------------------------------------------|---------|---------|------|

| Ambient Operating Temperature Range (T <sub>A</sub> ) | -40     | +105    | °C   |

| Operating Junction Temperature (T <sub>J</sub> )      |         | +125    | °C   |

| BUCKx_VINx, AVDD, VCHG                                | 2.7     | 5.5     | V    |

| VBAT                                                  | 1.8     | 5.5     | V    |

| MPIOx                                                 | -       | 5       | V    |

| CEN, PWRON                                            | -       | 5       | V    |

| VPROG                                                 | 0       | 23      | V    |

| SCL, SDA                                              | 0       | 3.3     | V    |

## 3.5 Electrical Specifications

| Parameter                                               | Symbol                   | Test Conditions <sup>[1]</sup>                                                                       | Min <sup>[2]</sup> | Тур  | Max <sup>[2]</sup> | Unit |  |  |

|---------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------|--------------------|------|--------------------|------|--|--|

| Input Supply                                            | nput Supply              |                                                                                                      |                    |      |                    |      |  |  |

| AVDD Input Operating Range                              | AVDD <sub>OP</sub>       | AVDD = VCHG = BUCKx_VINx                                                                             | 2.7                | 5    | 5.5                | V    |  |  |

| BUCK Input Operating<br>Range                           | BUCK <sub>OP</sub>       | BUCKx_VINx                                                                                           | 2.7                | 5    | 5.5                | V    |  |  |

| LDO Input Operating Range                               | LDO <sub>OP</sub>        | LDOx_VIN                                                                                             | 2.7                | 3.3  | 5.5                | V    |  |  |

| VCHG Input<br>Operating Range                           | VCHG <sub>OP</sub>       | AVDD = VCHG = BUCKx_VINx                                                                             | 2.7                | 5    | 5.5                | V    |  |  |

| VCHG Falling Slew<br>Rate <sup>[3]</sup>                | VCHG <sub>FALL</sub>     | To ensure POR operation of RTC do not exceed the maximum falling slew rate. AVDD = VCHG = BUCKx_VINx |                    |      | 5                  | V/ms |  |  |

|                                                         | $AVDD_{UVLO_R}$          | Rising threshold                                                                                     |                    | 2.3  |                    | V    |  |  |

| AVDD Undervoltage                                       | AVDD <sub>UVLO_F</sub>   | Falling threshold                                                                                    |                    | 2.1  |                    | V    |  |  |

| Lockout Threshold                                       | AVDD <sub>UVLO_HYS</sub> | AVDD <sub>UVLO_HYS</sub> = AVDD <sub>UVLO_R</sub> <sub>-</sub><br>AVDD <sub>UVLO_F</sub>             |                    | 200  |                    | mV   |  |  |

| AVDD Undervoltage                                       |                          | Falling AVDD, 2.7V setting                                                                           |                    | 2.7  |                    |      |  |  |

| Power Down                                              | 9                        | Falling AVDD, 3.0V setting                                                                           |                    | 3.0  |                    | V    |  |  |

| Threshold                                               |                          | Falling AVDD, 4.25V setting                                                                          |                    | 4.25 |                    |      |  |  |

| AVDD Undervoltage<br>Power Down<br>Threshold Accuracy   | AVDD <sub>UVPD_ACC</sub> | Falling AVDD                                                                                         | -3                 |      | 3                  | %    |  |  |

| AVDD Undervoltage<br>Power Down<br>Threshold Hysteresis | AVDD <sub>UVPD_HYS</sub> | AVDD <sub>UVPD_HYS</sub> = AVDD <sub>UVPD_R</sub> <sub>-</sub><br>AVDD <sub>UVPD_F</sub>             |                    | 100  |                    | mV   |  |  |

| Parameter                                  | Symbol                    | Test Conditions <sup>[1]</sup>                                                                                                                                                                                 | Min <sup>[2]</sup> | Тур | Max <sup>[2]</sup> | Unit |

|--------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| AVDD UVPD Delay                            | AVDD <sub>UVPD_DLY</sub>  | Falling AVDD                                                                                                                                                                                                   |                    | 100 |                    | μs   |

| Operating Bias Curren                      | t                         |                                                                                                                                                                                                                | 1                  | l   | 1                  | I    |

| {SHUTDOWN} Supply<br>Current               | I <sub>SHDN_AVDD</sub>    | Current into AVDD, CEN = LOW,<br>T <sub>A</sub> = 25°C                                                                                                                                                         |                    | <1  | 7                  | μA   |

| {SHUTDOWN} Supply<br>Current               | I <sub>SHDN_VCHG</sub>    | Current into VCHG, VBAT < VCHG CEN = LOW, T <sub>A</sub> = 25°C                                                                                                                                                |                    | 400 | 950                | nA   |

| RTC Battery Supply<br>Current              | I <sub>BAT</sub>          | VBAT = 3V, AVDD = VCHG = 0V.<br>RTC is enabled in 0x6C[6]. Internal<br>oscillator is enabled in 0x07[6] with<br>external crystal.                                                                              |                    | 400 |                    | nA   |

|                                            |                           | VBAT = 3V, Shipping mode (RTC is disabled in 0x6C[6])                                                                                                                                                          |                    | 120 |                    |      |

| {STANDBY} Supply<br>Current                | I <sub>OP_STANDY</sub>    | Total input current.  CEN = HIGH, AVDD > UVLO,  PWRON = LOW. RTC off.                                                                                                                                          |                    | 360 | 470                | μΑ   |

| {ACTIVE} Supply<br>Current                 | I <sub>OP_ACTIVE</sub>    | Total input current.  CEN = HIGH, AVDD > UVLO,  PWRON = HIGH  All bucks enabled, auto PFM/PWM  mode, no load, not switching.  All LDOs enabled, no load.  RTC on.  I <sup>2</sup> C on and idle, MPIOx static. | IA                 | 3.2 | 4.8                | mA   |

| RTC State Supply<br>Current                | lop_rtc                   | Total input current, VBAT.  VBAT = 3.3V,  BUCKx_VINx = AVDD = VCHG = 0V,  RTC is enabled and clocking, FOUT is enabled at INT#                                                                                 |                    |     | 5                  | μА   |

| VIO LDO                                    |                           |                                                                                                                                                                                                                |                    |     |                    |      |

| VIO LDO Output<br>Voltage                  | VIO <sub>OUT</sub>        | Not in dropout, no external loading                                                                                                                                                                            | 1.62               | 1.8 | 1.96               | V    |

| VIO LDO Current<br>Capability              | VIO <sub>IOUT_RNG</sub>   | Additional external loading <sup>[4]</sup>                                                                                                                                                                     |                    | 20  |                    | mA   |

| VIO LDO Current<br>Limit                   | VIO <sub>ILIM</sub>       | VIO = 90% * VIO <sub>OUT</sub>                                                                                                                                                                                 | 24                 |     | 41                 | mA   |

| VIO Load Transient<br>Response             | VIO <sub>LOAD_TR</sub>    | Step: 0 to 20mA in 1µs<br>Step: 20mA to 0 in 1µs                                                                                                                                                               | -3                 |     | 3                  | %    |

| VIO LDO Power-Good<br>Rising Threshold     | VIO <sub>PGOOD_Rise</sub> | VIO rising.<br>Percentage of VIO <sub>OUT</sub>                                                                                                                                                                | -10                | -5  | -2                 | %    |

| VIO LDO Power-Good<br>Falling Threshold    | VIO <sub>PGOOD_Fall</sub> | VIO falling.<br>Percentage of VIO <sub>OUT</sub>                                                                                                                                                               | -15                | -10 | -7                 | %    |

| VIO LDO Power-Good<br>Threshold Hysteresis | VIO <sub>PGOOD_HYS</sub>  | VIO <sub>PGOOD_HYS</sub> = VIO <sub>PGOOD_Rise</sub> - VIO <sub>PGOOD_Fall</sub>                                                                                                                               |                    | 5   |                    | %    |

| Parameter                                                    | Symbol                  | Test Conditions <sup>[1]</sup>                                                                                  | Min <sup>[2]</sup> | Тур    | Max <sup>[2]</sup> | Unit   |

|--------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------|--------|--------------------|--------|

| EEPROM                                                       | l                       |                                                                                                                 |                    |        |                    |        |

| EEPROM Endurance                                             | EE <sub>ENDR</sub>      | Programming cycles                                                                                              | 1000               |        |                    | Cycles |

| Loading EEPROM<br>Data to Registers at<br>Power-On           | t <sub>EE_LOAD</sub>    | AVDD valid. CEN = HIGH                                                                                          |                    |        | 10                 | ms     |

| EEPROM<br>Programming Cycle<br>Time                          | t <sub>EE_WRITE</sub>   | Total time for writing customer banks                                                                           |                    | 216    | 238                | ms     |

| BUCK1 (5A) Components as describ                             | ed in Recommended Ex    | cternal Components. Additional application                                                                      | on details in      | Buck1. |                    |        |

| Buck1 Output Voltage<br>Target Resolution                    | BK1 <sub>RES</sub>      |                                                                                                                 |                    | 4      |                    | bits   |

| Buck1 Output Voltage<br>Range                                | BK1 <sub>OUT</sub>      | BUCK1_FB                                                                                                        | 0.8                |        | 1.5                | V      |

| Buck1 Output Voltage<br>Step                                 | BK1 <sub>STEP</sub>     | BUCK1_FB                                                                                                        |                    | 50     |                    | mV     |

| Buck1 Output Voltage<br>DC Accuracy                          | BK1 <sub>ACC</sub>      | BUCK1_FB. PWM operation,<br>I <sub>OUT</sub> = 5mA, V <sub>OUT</sub> = 1.1V                                     | -1                 |        | 1                  | %      |

| Buck1 Output Voltage<br>Ripple FPWM                          | BK1 <sub>RIP_FPWM</sub> | I <sub>OUT</sub> = 100mA, FPWM mode                                                                             | IA                 | 10     |                    | mVpp   |

| Buck1 Maximum<br>Output Current<br>Capability <sup>[5]</sup> | BK1 <sub>IOUT_MAX</sub> |                                                                                                                 | 5                  |        |                    | А      |

| Buck1 Output Load<br>Regulation                              | BK1 <sub>LOAD_REG</sub> | FPWM, VOUT = 1.1V,<br>Over I <sub>OUT</sub> = 100mA to 5A range                                                 |                    | ±0.1   |                    | %      |

| Buck1 Output Line<br>Regulation                              | BK1 <sub>LINE_REG</sub> | FPWM, BUCK1_VINx = $4.5V \leftrightarrow 5.5V$ ,<br>VOUT = $1.1V$ ,<br>$I_{OUT} = BK1_{IOUT\_MAX}$              |                    | ±0.1   |                    | %      |

| Buck1 Peak Efficiency                                        | BK1 <sub>EFF</sub>      | Peak efficiency, L = default,<br>BK1 <sub>FSW</sub> set to default <sup>[6]</sup> , maximum<br>V <sub>OUT</sub> |                    | 92     | -                  | %      |

|                                                              |                         | BUCK1_FB. Slow setting enabled                                                                                  | 35                 | 50     | 65                 | Ω      |

| Buck1 Discharge<br>Resistance                                | BK1 <sub>RDCHG</sub>    | BUCK1_FB. Medium setting enabled                                                                                | 26                 | 37.5   | 49                 | Ω      |

|                                                              |                         | BUCK1_FB. Fast setting enabled                                                                                  | 17.5               | 25     | 32.5               | Ω      |

| Buck1 High-Side<br>MOSFET Current<br>Limit                   | BK1 <sub>ILIM_HS</sub>  | PWM operation, sourcing (supplying)                                                                             | 6.1                | 7      | 7.7                | А      |

| Buck1 Low-Side                                               | BK1 <sub>ILIM_LS</sub>  | PWM operation, sourcing (supplying)                                                                             |                    | 7.5    |                    | _      |

| MOSFET Current<br>Limit                                      | BK1 <sub>ILIMNEG</sub>  | FPWM mode, sinking (receiving)                                                                                  |                    | -0.7   |                    | Α      |

| Parameter                                                    | Symbol                           | Test Conditions <sup>[1]</sup>                                                               | Min <sup>[2]</sup> | Тур    | Max <sup>[2]</sup> | Unit  |

|--------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------|--------------------|--------|--------------------|-------|

|                                                              |                                  |                                                                                              | 3.6                | 4.6    | 5.6                |       |

| Buck1 High-Side                                              | DIZ4                             | Docietar cettable values [5]                                                                 | 4.4                | 5.4    | 6.4                | ,     |

| Overcurrent Warning Threshold Range                          | BK1 <sub>IHC</sub>               | Register settable values <sup>[5]</sup>                                                      | 4.7                | 5.7    | 6.7                | A     |

|                                                              |                                  |                                                                                              | 5.1                | 6.1    | 7.1                |       |

| Buck1 High-Side<br>Overcurrent Warning<br>Threshold Accuracy | BK1 <sub>IHC_ACC</sub>           | default BK1 <sub>IHC</sub> setting                                                           | -1                 |        | +1                 | А     |

| Buck1 PWM<br>Switching Frequency                             | BK1 <sub>FSW</sub>               | FPWM mode, 1.11MHz (default) setting                                                         |                    | 1.11   |                    | MHz   |

| Buck1 PWM<br>Switching Frequency<br>Accuracy                 | BK1 <sub>FSW_ACC</sub>           | FPWM mode, I <sub>OUT</sub> = 0mA,<br>default frequency                                      | -10                |        | +10                | %     |

| Buck1 Soft-Start Slew<br>Rate Range                          | BK1 <sub>SS_SR_RNG</sub>         | BUCK1_FB                                                                                     | 0.5                | 1      | 4                  | ms    |

| Buck1 Shutdown Slew<br>Rate Range                            | BK1 <sub>SHTDN</sub> _<br>SR_RNG | BUCK1_FB                                                                                     | 0.5                | 1      | 4                  | ms    |

| Buck1 DVS Slew Rate<br>Range                                 | BK1 <sub>DVS_SR_RNG</sub>        | BUCK1_FB. Applies to both DVS up and down ramps.                                             | 2                  | 8      | 16                 | mV/μs |

| Buck1 High-Side<br>PMOS On-resistance                        | BK1 <sub>RDSON_HS</sub>          | BUCK1_VINx to BUCK1_LXx, I <sub>LX</sub> = -150mA                                            | IA                 | 40     |                    | mΩ    |

| Buck1 Low-Side<br>NMOS On-Resistance                         | BK1 <sub>RDSON_LS</sub>          | BUCK1_LXx to PGND,<br>I <sub>LX</sub> = 150mA                                                |                    | 28     |                    | mΩ    |

| BUCK2 (1.5A) Components as describ                           | ed in Recommended Ex             | cternal Components. Additional application                                                   | on details in      | Buck2. | •                  |       |

| Buck2 Output Voltage<br>Target Resolution                    | BK2 <sub>RES</sub>               |                                                                                              |                    | 4      |                    | bits  |

| Buck2 Output Voltage<br>Range                                | BK2 <sub>OUT</sub>               | BUCK2_FB                                                                                     | 1.1                | -      | 1.85               | ٧     |

| Buck2 Output Voltage<br>Step                                 | BK2 <sub>STEP</sub>              | BUCK2_FB                                                                                     |                    | 50     |                    | mV    |

| Buck2 Output Voltage<br>DC Accuracy                          | BK2 <sub>ACC</sub>               | BUCK2_FB. PWM operation,<br>I <sub>OUT</sub> = 5mA, V <sub>OUT</sub> = 1.2V                  | -1                 | -      | 1                  | %     |

| Buck2 Output Voltage<br>Ripple FPWM                          | BK2 <sub>RIP_FPWM</sub>          | I <sub>OUT</sub> = 100mA, FPWM mode                                                          |                    | 10     | -                  | mVpp  |

| Buck2 Maximum<br>Output Current<br>Capability <sup>[5]</sup> | BK2 <sub>IOUT_MAX</sub>          |                                                                                              | 1.5                |        |                    | А     |

| Buck2 Output Load<br>Regulation                              | BK2 <sub>LOAD_REG</sub>          | FPWM, VOUT = 1.2V,<br>Over I <sub>OUT</sub> = 100mA to 1.5A range                            |                    | ±0.15  |                    | %     |

| Buck2 Output Line<br>Regulation                              | BK2 <sub>LINE_REG</sub>          | BUCK2_VINx = $4.5V \leftrightarrow 5.5V$ ,<br>VOUT = $1.2V$ ,<br>$I_{OUT} = BK2_{IOUT\_MAX}$ |                    | ±0.15  |                    | %     |

| Parameter                                                    | Symbol                           | Test Conditions <sup>[1]</sup>                                                                                  | Min <sup>[2]</sup> | Тур    | Max <sup>[2]</sup> | Unit  |

|--------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------|--------|--------------------|-------|

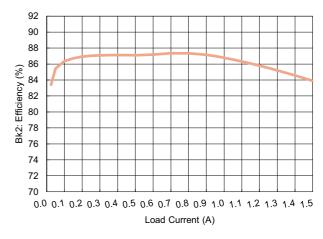

| Buck2 Peak Efficiency                                        | BK2 <sub>EFF</sub>               | Peak efficiency, L = default,<br>BK2 <sub>FSW</sub> set to default <sup>[6]</sup> , maximum<br>V <sub>OUT</sub> |                    | 90     |                    | %     |

|                                                              |                                  | BUCK2_FB. Slow setting                                                                                          | 35                 | 50     | 65                 |       |

| Buck2 Discharge<br>Resistance                                | BK2 <sub>RDCHG</sub>             | BUCK2_FB. Medium setting                                                                                        | 26                 | 37.5   | 49                 | Ω     |

|                                                              |                                  | BUCK2_FB. Fast setting                                                                                          | 17.5               | 25     | 32.5               |       |

| Buck2 High-Side<br>MOSFET Current<br>Limit                   | BK2 <sub>ILIM_HS</sub>           | PWM operation, sourcing (supplying)                                                                             | 2.27               | 2.5    | 2.78               | A     |

| Buck2 Low-Side                                               | BK2 <sub>ILIM_LS</sub>           | PWM operation, sourcing (supplying)                                                                             |                    | 3      |                    | Α     |

| MOSFET Current<br>Limit                                      | BK2 <sub>ILIMNEG</sub>           | FPWM mode, sinking (receiving)                                                                                  |                    | -0.66  |                    | Α     |

| Buck2 PWM<br>Switching Frequency                             | BK2 <sub>FSW</sub>               | FPWM mode, 0.769MHz (default) setting                                                                           |                    | 0.769  |                    | MHz   |

| Buck2 PWM<br>Switching Frequency<br>Accuracy                 | BK2 <sub>FSW_ACC</sub>           | FPWM mode, I <sub>OUT</sub> = 0mA,<br>default frequency                                                         | -10                |        | +10                | %     |

| Buck2 Soft-start Slew<br>Rate Range                          | BK2 <sub>SS_SR_RNG</sub>         | BUCK2_FB                                                                                                        | 0.5                | 1      | 4                  | ms    |

| Buck2 Shutdown Slew<br>Rate Range                            | BK2 <sub>SHTDN</sub> _<br>SR_RNG | BUCK2_FB                                                                                                        | 0.5                | 1      | 4                  | ms    |

| Buck2 DVS Slew Rate<br>Range                                 | BK2 <sub>DVS_SR_RNG</sub>        | BUCK2_FB. Applies to both DVS up and down ramps.                                                                | 2                  | 8      | 16                 | mV/μs |

| Buck2 High-Side<br>PMOS On-Resistance                        | BK2 <sub>RDSON_HS</sub>          | BUCK2_VINx to BUCK2_LXx, I <sub>LX</sub> = -150mA                                                               |                    | 120    |                    | mΩ    |

| Buck2 Low-Side<br>NMOS On-Resistance                         | BK2 <sub>RDSON_LS</sub>          | BUCK2_LXx to PGND,<br>I <sub>LX</sub> = 150mA                                                                   |                    | 70     |                    | mΩ    |

| BUCK3 (1.5A) Components as describ                           | ed in Recommended Ex             | xternal Components. Additional application                                                                      | on details in      | Buck3. | •                  |       |

| Buck3 Output Voltage<br>Target Resolution                    | BK3 <sub>RES</sub>               |                                                                                                                 |                    | 4      |                    | bits  |

| Buck3 Output Voltage<br>Range                                | BK3 <sub>OUT</sub>               | BUCK3_FB                                                                                                        | 1.8                |        | 3.3                | V     |

| Buck3 Output Voltage<br>Step                                 | BK3 <sub>STEP</sub>              | BUCK3_FB                                                                                                        |                    | 100    |                    | mV    |

| Buck3 Output Voltage<br>DC Accuracy                          | BK3 <sub>ACC</sub>               | BUCK3_FB. PWM operation,<br>I <sub>OUT</sub> = 5mA, V <sub>OUT</sub> = 1.8V                                     | -1                 |        | 1                  | %     |

| Buck3 Output Voltage<br>Ripple FPWM                          | BK3 <sub>RIP_FPWM</sub>          | I <sub>OUT</sub> = 100mA, FPWM mode                                                                             |                    | 10     |                    | mVpp  |

| Buck3 Maximum<br>Output Current<br>Capability <sup>[5]</sup> | BK3 <sub>IOUT_MAX</sub>          |                                                                                                                 | 1.5                |        |                    | А     |

| Parameter                                    | Symbol                           | Test Conditions <sup>[1]</sup>                                                                                       | Min <sup>[2]</sup> | Тур    | Max <sup>[2]</sup> | Unit  |

|----------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------|--------|--------------------|-------|

| Buck3 Output Load<br>Regulation              | BK3 <sub>LOAD_REG</sub>          | FPWM, VOUT = 1.8V,<br>Over I <sub>OUT</sub> = 100mA to 1.5A range                                                    |                    | ±0.1   |                    | %     |

| Buck3 Output Line<br>Regulation              | BK3 <sub>LINE_REG</sub>          | BUCK3_VINx = $4.5V \leftrightarrow 5.5V$ ,<br>VOUT = $1.8V$ ,<br>$I_{OUT} = BK3_{IOUT\_MAX}$                         |                    | ±0.1   |                    | %     |

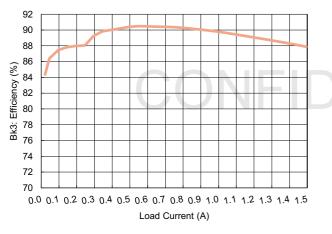

| Buck3 Peak Efficiency                        | BK3 <sub>EFF</sub>               | Peak efficiency, L = default,<br>BK3 <sub>FSW</sub> set to default <sup>[6]</sup> , maximum<br>V <sub>OUT</sub>      |                    | 92     |                    | %     |

|                                              |                                  | BUCK3_FB. Slow setting                                                                                               | 35                 | 50     | 75                 |       |

| Buck3 Discharge<br>Resistance                | BK3 <sub>RDCHG</sub>             | BUCK3_FB. Medium setting                                                                                             | 26                 | 37.5   | 49                 | Ω     |

|                                              |                                  | BUCK3_FB. Fast setting                                                                                               | 17.5               | 25     | 32.5               |       |

| Buck3 High-Side<br>MOSFET Current<br>Limit   | BK3 <sub>ILIM_HS</sub>           | PWM mode, sourcing (supplying)                                                                                       | 2.12               | 2.5    | 3                  | А     |

| Buck3 Low-Side                               | BK3 <sub>ILIM_LS</sub>           | PWM operation, sourcing (supplying)                                                                                  |                    | 3      |                    | А     |

| MOSFET Current<br>Limit                      | BK3 <sub>ILIMNEG</sub>           | FPWM mode, sinking (receiving)                                                                                       |                    | -0.55  |                    |       |

| Buck3 PWM<br>Switching Frequency             | BK3 <sub>FSW</sub>               | FPWM mode, 1.54MHz (default) setting                                                                                 | ΊΛ                 | 1.54   |                    | MHz   |

| Buck3 PWM<br>Switching Frequency<br>Accuracy | BK3 <sub>FSW_ACC</sub>           | FPWM mode, I <sub>OUT</sub> = 0mA, default frequency                                                                 | -10                |        | +10                | %     |

| Buck3 Soft-Start Slew<br>Rate Range          | BK3 <sub>SS_SR_RNG</sub>         | BUCK3_FB                                                                                                             | 0.5                | 1      | 4                  | ms    |

| Buck3 Shutdown Slew<br>Rate Range            | BK3 <sub>SHTDN</sub> _<br>SR_RNG | BUCK3_FB                                                                                                             | 0.5                | 1      | 4                  | ms    |

| Buck3 DVS Slew Rate<br>Range                 | BK3 <sub>DVS_SR_RNG</sub>        | BUCK3_FB. Applies to both DVS up and down ramps.                                                                     | 2                  | 8      | 16                 | mV/μs |

| Buck3 High-Side<br>PMOS On-Resistance        | BK3 <sub>RDSON_HS</sub>          | BUCK3_VINx to BUCK3_LXx,<br>I <sub>LX</sub> = -150mA                                                                 |                    | 93     |                    | mΩ    |

| Buck3 Low-Side<br>NMOS On-Resistance         | BK3 <sub>RDSON_LS</sub>          | BUCK3_LXx to PGND,<br>I <sub>LX</sub> = 150mA                                                                        |                    | 57     |                    | mΩ    |

| BUCK4 (3.5A) Components as describe          | ed in Recommended E              | external Components. Additional application                                                                          | on details in      | Buck4. |                    |       |

| Buck4 Output Voltage<br>Target Resolution    | BK4 <sub>RES</sub>               |                                                                                                                      |                    | 4      |                    | bits  |

| Buck4 Output Voltage<br>Range                | BK4 <sub>OUT</sub>               | BUCK4_FB<br>0.8V, 0.85V, 0.9V, 0.95V, 1V,1.05V,<br>1.1V, 1.15V, 1.2V, 1.5V, 1.6V 1.8V,<br>1.85V, 2.2V, 2.5V and 3.3V | 0.8                |        | 3.3                | V     |

| Buck4 Output Voltage<br>DC Accuracy          | BK4 <sub>ACC</sub>               | BUCK4_FB. PWM operation,<br>I <sub>OUT</sub> = 5mA, V <sub>OUT</sub> = 3.3V                                          | -1                 |        | 1                  | %     |

| Parameter                                                    | Symbol                           | Test Conditions <sup>[1]</sup>                                                                                  | Min <sup>[2]</sup> | Тур    | Max <sup>[2]</sup> | Unit  |

|--------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------|--------|--------------------|-------|

| Buck4 Output Voltage<br>Ripple FPWM                          | BK4 <sub>RIP_FPWM</sub>          | I <sub>OUT</sub> = 100mA, FPWM mode                                                                             |                    | 15     |                    | mVpp  |

| Buck4 Maximum<br>Output Current<br>Capability <sup>[5]</sup> | BK4 <sub>IOUT_MAX</sub>          |                                                                                                                 | 3.5                |        |                    | А     |

| Buck4 Output Load<br>Regulation                              | BK4 <sub>LOAD_REG</sub>          | FPWM, VOUT = 3.3V,<br>Over I <sub>OUT</sub> = 100mA to 3.5A range                                               |                    | ±0.1   |                    | %     |

| Buck4 Output Line<br>Regulation                              | BK4 <sub>LINE_REG_3V3</sub>      | BUCK4_VINx = $4.5V \leftrightarrow 5.5V$ ,<br>VOUT = $3.3V$ ,<br>$I_{OUT} = BK4_{IOUT\_MAX}$                    |                    | ±0.1   |                    | %     |

| Buck4 Peak Efficiency                                        | BK4 <sub>EFF</sub>               | Peak efficiency, L = default,<br>BK4 <sub>FSW</sub> set to default <sup>[6]</sup> , maximum<br>V <sub>OUT</sub> |                    | 95     |                    | %     |

|                                                              |                                  | BUCK4_FB. Slow setting                                                                                          | 35                 | 50     | 65                 |       |

| Buck4 Discharge<br>Resistance                                | ance BK4 <sub>RDCHG</sub> B      | BUCK4_FB. Medium setting                                                                                        | 26                 | 37.5   | 49                 | Ω     |

|                                                              |                                  | BUCK4_FB. Fast setting                                                                                          | 17.5               | 25     | 32.5               |       |

| Buck4 High-Side<br>MOSFET Current<br>Limit                   | BK4 <sub>ILIM_HS</sub>           | PWM operation, sourcing (supplying)                                                                             | 4                  | 4.5    | 5                  | А     |

| Buck4 Low-Side                                               | BK4 <sub>ILIM_LS</sub>           | PWM operation, sourcing (supplying)                                                                             | IA                 | 5      |                    | _     |

| MOSFET Current<br>Limit                                      | BK4 <sub>ILIMNEG</sub>           | FPWM mode, sinking (receiving)                                                                                  |                    | -0.675 |                    | Α     |

| Buck4 PWM<br>Switching Frequency                             | BK4 <sub>FSW</sub>               | FPWM mode, 1.54MHz (default) setting                                                                            |                    | 1.54   |                    | MHz   |

| Buck4 PWM<br>Switching Frequency<br>Accuracy                 | BK4 <sub>FSW_ACC</sub>           | FPWM mode, I <sub>OUT</sub> = 0mA,<br>default frequency                                                         | -10                |        | +10                | %     |

| Buck4 Soft-Start Slew<br>Rate Range                          | BK4 <sub>SS_SR_RNG</sub>         | BUCK4_FB                                                                                                        | 0.5                | 1      | 4                  | ms    |

| Buck4 Shutdown Slew<br>Rate Range                            | BK4 <sub>SHTDN</sub> _<br>SR_RNG | BUCK4_FB                                                                                                        | 0.5                | 1      | 4                  | ms    |

| Buck4 DVS Slew Rate<br>Range                                 | BK4 <sub>DVS_SR_RNG</sub>        | BUCK4_FB. Applies to both DVS up and down ramps.                                                                | 2                  | 8      | 16                 | mV/μs |

| Buck4 High-Side<br>PMOS On-Resistance                        | BK4 <sub>RDSON_HS</sub>          | BUCK4_VINx to BUCK4_LXx,<br>I <sub>LX</sub> = -150mA                                                            |                    | 60     |                    | mΩ    |

| Buck4 Low-Side<br>NMOS On-Resistance                         | BK4 <sub>RDSON_LS</sub>          | BUCK4_LXx to PGND,<br>I <sub>LX</sub> = 150mA                                                                   |                    | 30     |                    | mΩ    |

| BUCK5 (0.6A) Components as describe                          | ed in Recommended E              | xternal Components. Additional application                                                                      | on details in      | Buck5. |                    |       |

| Buck5 Output Voltage<br>Target Resolution                    | BK5 <sub>RES</sub>               |                                                                                                                 |                    | 3      |                    | bits  |

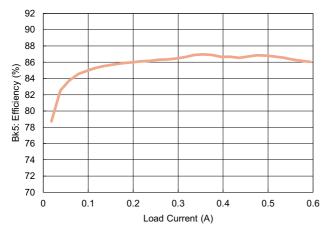

| Buck5 Output Voltage<br>Range                                | BK5 <sub>OUT</sub>               | BUCK5_FB                                                                                                        | 1.2                | -      | 3.3                | V     |

| Parameter                                                    | Symbol                           | Test Conditions <sup>[1]</sup>                                                                                  | Min <sup>[2]</sup> | Тур          | Max <sup>[2]</sup> | Unit  |