## QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 887 14-BIT, 6-CHANNEL, 600KSPS SIMULTANEOUS ADC

LTC 1408

### DESCRIPTION

Demonstration circuit 887 features the LTC1408 6-channel, 14-Bit, simultaneous sampling ADC. Total throughput is 600KSPS; 100KSPS per channel, with a typical channel-to-channel aperture skew of 200ps. The board is designed to be used with the DC890B Fast DAACS data collection board to show the AC performance of the LTC1408. Alternatively, the board

can be directly connected to an application to evaluate the ADC's performance.

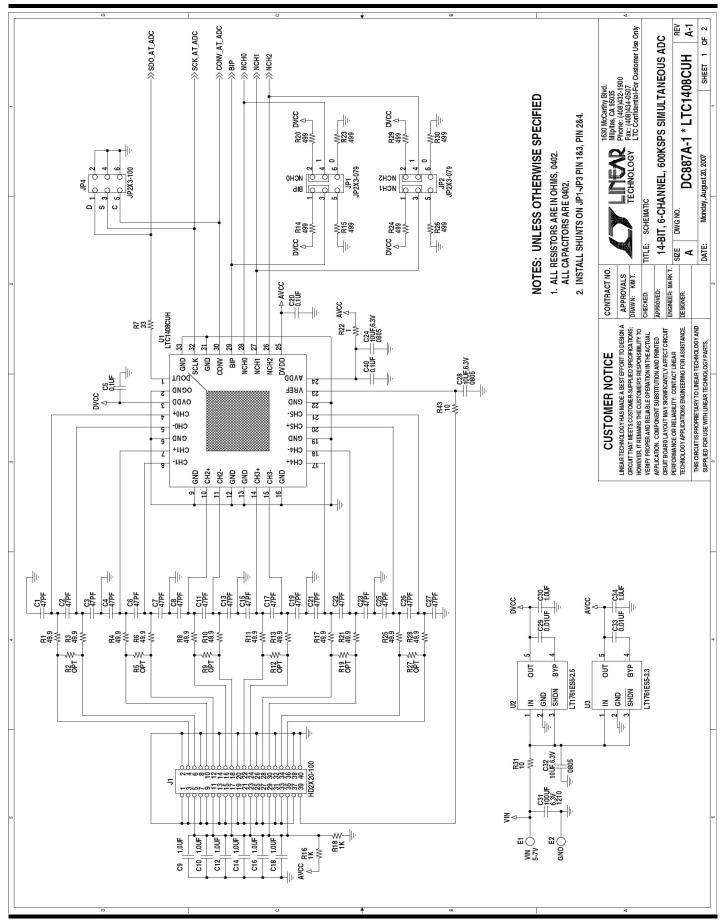

Design files for this circuit board are available. Call the LTC factory.

LTC is a trademark of Linear Technology Corporation

## **QUICK START PROCEDURE**

#### **BASIC CONNECTIONS**

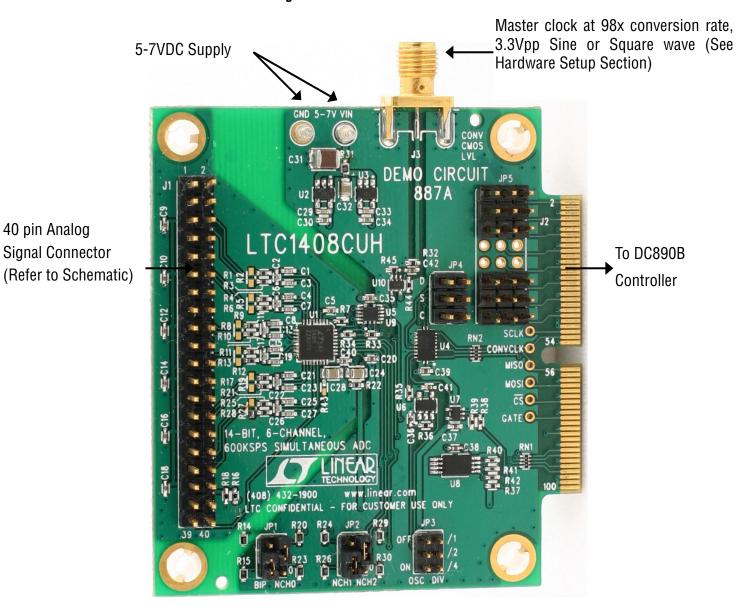

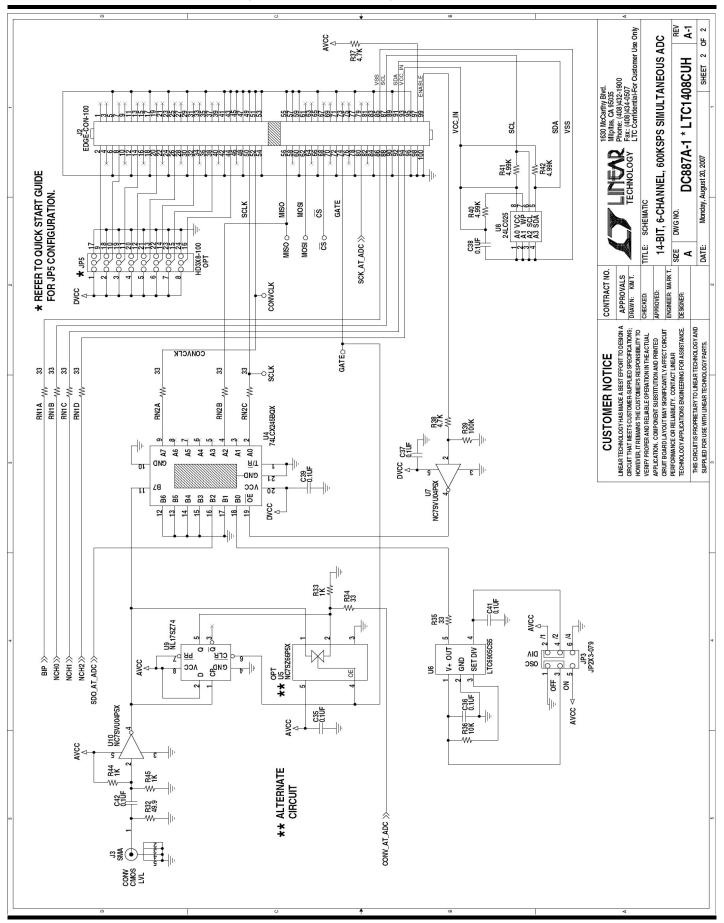

Connect DC887 to a DC890B USB High Speed Data Collection Board using connector J2. Connect DC890B to a host PC with a standard USB A/B cable. Apply 5-7V DC to the VIN and GND terminals. Apply a 10MHz 3.3Vp-p sine wave or square wave to connector J3. Note that J3 has a 50 Ohms termination resis-

tor to ground. CH0-CH5 are provided through connector J1 (See schematic for details.). Run the QuickEval II (Pscope.exe) evaluation software supplied with DC890 or download it from www.linear.com/software.

1

Figure 1. CONNECTION DIAGRAM

Scope K49-08 BETA Apr 19 2007 13:33:31 - UsrCfg (User Configure) File View Tools Configure Help Page 1 Page 2 Page 3 Page 4 Channel 2 fs 0.255000 Msps 12000 F1 99.951782227 KHz 8000 BinW 31.128 Hz F1Bin 3211 400 F1amp -0.502 dBFS 3500 SNR -86.94 dBc 74.43 dB F2 SINAD 73.51 dB F3 -81.99 dBc 14000 -80.71 dB -101.01 dBc 12000 10000 SFDR 81.99 dB F5 -102.92 dBc 8000 ENOB 11.92 bits F6 Absent 6000 429 F7 -111.23 dBc Mincode 4000 Maxcode 15897 F8 Absent **DCLev** 8162.5 F9 -104.96 dBc 3000 3500 4000 4500 5000 5500 6000 6500 Flor -111.05 dBFS -124.09 dBc Nyq Ch 2 Fourier Trans Msps 0.255 -0.0 Collect 10.0 Size 8192 -20.0 ✓ Repeat Blkmn-Harris 92dB 🕶 -30.0-40.0 ADC Full Scale -50.0 AutoDetect -60.0 -70.0 Status Messages -80.0 Data-collection timeout -90.0 Data-collection timeout Data-collection timeout 100.0 Data-collection timeout -110.0 Data-collection timeout 120.0 Data-collection timeout 130.0 Data-collection timeout Data-collection timeout 140.0 150.0 160.0 600 800 1000 1200 1400 1600 1800 2000 2200 2400 2600 2800 3000 3200 3400 3600 3800

Figure 2. SOFTWARE SCREENSHOT

Figure 3. CONFIGURE MENUS

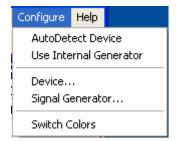

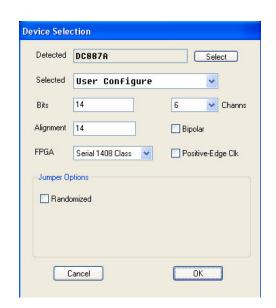

### **SOFTWARE CONFIGURATION**

### **CONFIGURE DEVICE**

The Pscope software should automatically configure itself after detecting the demo board. To change from Bipolar to Unipolar mode it will be necessary to manually configure the software. In the CONFIGURE menu (See Figure 3) select Device, which will bring up another window. In this window, select User Configure and adjust the other settings as follows:

Bits: 14

Alignment: 14

Bipolar: Checked if BIP jumper is set high, Un-Checked if BIP jumper is set to low. (Default is

checked)

Channels: 6

Positive Edge Clk: UN-Checked

FPGA: Serial 1408 Class.

#### **CONFIGURE SOFTWARE SCREEN**

The software interface is highly configurable and displays any combination of time domain data, frequency domain data, primitive wave and performance parameters (SNR, THD, SINAD, etc.). The screen can be broken into multiple panes as shown in Figure 2. Complete documentation on configuring PSCOPE can be found in the help file.

Click the COLLECT button to begin acquiring data.

Complete software documentation is available from the Help menu item, as features may be added periodically.

### HARDWARE SET-UP

### **JUMPERS**

JP1, JP2 - Select number of channels to convert and Unipolar / Bipolar selection. NCH2, NCH1, NCH0 are set to 111 which selects all six channels. These switches should be left in this position when running Pscope software. UNI/BIP selection applies to all channels. Refer to Figure 4.

**JP3** – Enable Oscillator and Oscillator Division. Presently not used. This may be used in the future as serial clock, to allow a convert signal at 1X the conversion rate.

JP4 – Digital Interface Header. Provides direct connection to the LTC1408 CONV, SDO, and SCK pins. This can be used to either monitor signals with a logic analyzer or to drive the LTC1408 directly from the customer's test equipment or prototype circuitry. DC890B should be disconnected before driving the LTC1408 externally with JP4. Note that R34 should be removed if the CONV signal is being driven externally.

JP5 - Currently not used

### SIGNAL CONNECTIONS

**J1** – 40 pin connector with CHO-CH5 differential inputs, multiple grounds, a mid-supply bias voltage and Vref. Refer to schematic for pin out. The mid-supply bias voltage can be used to bias the minus ADC inputs for bipolar conversions.

**J2** – Data connections to DC890B collection board.

J3 – Conversion Clock Input. This input has a 50 ohm termination resistor, and is intended to be driven by a 3.3Vpp sine or square wave. This clock is divided by 98 in the DC890B collection board to control the serial interface and convert pulse. To run the LTC1408 at maximum conversion rate, apply a 10MHz signal to this input.

#### **GROUNDING AND POWER CONNECTION**

Connect a 5V to 7V power supply to the Vin and GND turret posts. For optimum performance, this supply should be floating with respect to any signal generators connected to the analog inputs.

Figure 4 – JP1, JP2 CONFIGURATION

# QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 887 14-BIT, 6-CHANNEL, 600KSPS SIMULTANEOUS ADC

# QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 887 14-BIT, 6-CHANNEL, 600KSPS SIMULTANEOUS ADC

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

DC887A