### 600mV to 5.5V Input, 2A Boost Converter with True Shutdown

#### **FEATURES**

- ► 500nA Quiescent Supply Current from Output

- ► Output Short-Circuit Protection

- ► True Shutdown Mode

- In A Shutdown Current

- ► Output Disconnects from Input

- ► No Reverse-Current with Any Voltage on V<sub>OUT</sub>

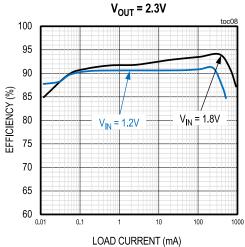

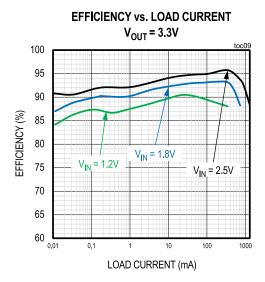

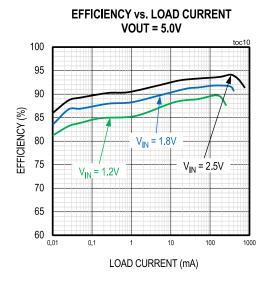

- ▶ 96% Peak Efficiency, 90% or Higher at 500µA

- Typical 800mA Output Current at 5.0V ( $V_{IN} = 3.0V$ )

- ► 600mV to 5.5V Input Range, Up to 5.35V in Regulation

- ▶ 900mV Minimum Startup Voltage

- ► Single Resistor-Adjustable Output Voltage

- 2.3V to 5.2V Output Voltage Range with 100mV

- ► 5.5V Output Voltage Setting Available

- 2A Peak Inductor Current Limit

- ► Thermal Shutdown Protection

- ► Multiple Package Options

- ► 1.58mm x 0.89mm, 0.4mm Pitch, 6-Bump (3 x 2) **WLP**

- 2mm x 2mm, 8-Pin TDFN

- ► -40°C to +125°C Operating Temperature Range

#### **GENERAL DESCRIPTION**

The ADPL20502® is a boost converter capable of delivering a peak inductor current up to 2A with True Shutdown<sup>™</sup>, cycle-by-cycle inductor current limit, short circuit, and thermal protection. During shutdown, only 1nA is drawn from the input pin. The ADPL20502 offers ultra-low quiescent current, small total solution size, and operates at a high efficiency throughout the load and line range. The ADPL20502 is ideal for batterypowered applications where long battery life is a must and high efficiency is required at all power levels.

The ADPL20502 utilizes an adjustable on-time, pulsefrequency modulation (PFM) control scheme that consumes ultra-low quiescent current. The ADPL20502 features True Shutdown mode where the output disconnects from the input with no forward or reversecurrent. This saves precious energy from the battery for systems that dynamically turn on and off by having the ability to startup into a precharged output capacitor. The ADPL20502 is offered in a space-saving and cost effective 1.58mm x 0.89mm, 6-bump WLP (3 x 2, 0.4mm pitch) and 8-pin, 2mm x 2mm TDFN packages. The operating temperature range is from -40°C to +125°C.

#### **APPLICATIONS**

- ► Consumer: WiFi Module, Near-Band IoT, Wearable

- Industrial: Emergency Lighting, IoT Sensors

- Medical: Clinical Instrumentation

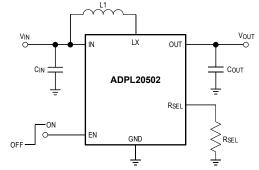

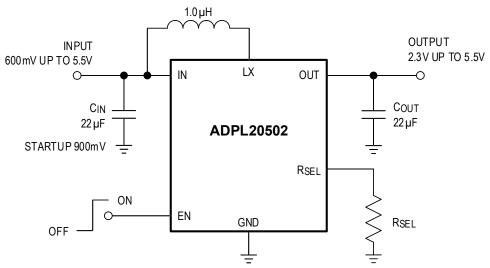

## SIMPLIFIED APPLICATION DIAGRAM

Figure 1. Simplified Application Diagram

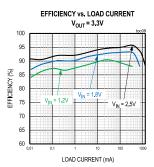

Figure 2. Efficiency vs. Load Current (Figure 5 Circuit)

# **TABLE OF CONTENTS**

| Features                                     | 1  |

|----------------------------------------------|----|

| General Description                          | 1  |

| Applications                                 | 1  |

| Simplified Application Diagram               | 1  |

| Revision History                             | 2  |

| Specifications                               | 3  |

| Absolute Maximum Ratings                     | 5  |

| Pin Configurations and Function Descriptions | 6  |

| Pin Configurations                           | 6  |

| Pin Descriptions                             | 7  |

| Typical Operating Characteristics            | 8  |

| FUNCTIONAL DIAGRAMS                          | 14 |

| Detailed Description                         | 15 |

| Control Scheme                               | 15 |

| Output Voltage Selection                     | 17 |

| Fixed-Output Voltage Version | 18 |

|------------------------------|----|

| Features                     | 18 |

| Enable                       | 18 |

| Soft-Start Control           | 18 |

| Short-Circuit Protection     | 19 |

| Thermal Shutdown             | 19 |

| Design Procedure             | 20 |

| Inductor Selection           | 20 |

| Input Capacitor              | 20 |

| Output Capacitor             | 20 |

| PCB Layout Guidelines        | 20 |

| Thermal Considerations       | 21 |

| TYPICAL APPLICATION CIRCUIT  | 22 |

| Outline Dimensions           | 23 |

| Ordering GUIDE               | 26 |

## **REVISION HISTORY**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 12/23         | Initial Release | -                |

analog.com Rev 0 | 2 of 27

## **SPECIFICATIONS**

#### **Table 1. Electrical Characteristics**

$(V_{IN} = 1.5V, R_{SEL} = 191k\Omega, V_{OUT} = 3.3V, T_{J} = -40^{\circ}\text{C}$  to +125°C, typical values are at  $T_{J} = +25^{\circ}\text{C}, C_{IN} = 22\mu\text{F}, C_{OUT} = 22\mu\text{F}, unless otherwise noted.})$

| PARAMETER                            | SYMBOL                | CONDITION                                                                                                      | IS/COMMENTS                           | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------|------|-------|

| Minimum Input Voltage                | $V_{IN_{MIN}}$        | Runs from output after startup, I <sub>OUT</sub> = 1mA                                                         |                                       |      | 600  |      | mV    |

| Input Voltage Range                  | V <sub>IN</sub>       | Guaranteed by LX Maximum On-<br>Time, V <sub>OUT</sub> > V <sub>IN</sub> + 150mV while in<br>regulation        |                                       | 0.95 |      | 5.5  | V     |

| Minimum Startup Input<br>Voltage     | V <sub>IN_START</sub> | $R_L \ge 3k\Omega$ , <i>Typical</i> $T_J = +25^{\circ}C$                                                       | Application Circuit,                  |      | 0.9  | 0.95 | V     |

| Output Voltage Range                 | $V_{OUT\_RANGE}$      | See . For $V_{IN} < V_{OU}$                                                                                    | <sub>т</sub> target. ( <del>²</del> ) | 2.3  |      | 5.5  | V     |

| Output Accuracy, LPM                 | $V_{ACC\_LPM}$        | V <sub>OUT</sub> Falling (₃)                                                                                   |                                       | -1.2 |      | +1.2 | %     |

| Output Accuracy, ULPM                | $V_{ACC\_ULPM}$       | V <sub>OUT</sub> Rising, when (4)                                                                              | LX stops switching                    | +1.5 | +2.7 | +4.6 | %     |

| DC Load Regulation                   | $ACC_LOAD$            | Load from 20mA<br>Peak Inductor Cu                                                                             |                                       |      | -1.2 |      | %     |

| DC Line Regulation                   | ACC <sub>LINE</sub>   | Duty Cycle varied<br>Maximum                                                                                   | from 25% to                           |      | -1.2 |      | %     |

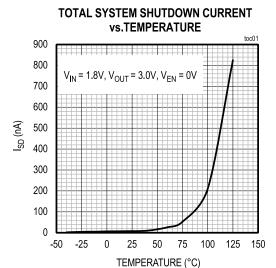

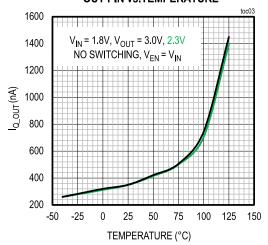

| Input Shutdown Current               | I <sub>SD_IN</sub>    | $V_{EN} = 0V, V_{OUT} = 0V$                                                                                    | /, T <sub>J</sub> = +25°C             |      | 1    | 120  | nA    |

| Quiescent Supply<br>Current Into IN  | I <sub>Q_IN</sub>     | $V_{EN} = V_{IN}$ , not switching, $V_{OUT} = 105\%$<br>of target voltage, $T_J = +25$ °C, $R_{SEL} =$<br>Open |                                       |      | 15   |      | nA    |

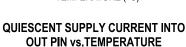

| Quiescent Supply<br>Current Into OUT | I <sub>Q_OUT</sub>    | $V_{EN} = V_{IN}$ , not switching, $V_{OUT} = 105\%$<br>of target voltage, $T_J = +25$ °C, $R_{SEL} =$<br>Open |                                       |      | 500  | 800  | nA    |

| Maximum LX On-Time                   | t <sub>ONMAX</sub>    | $T_J = -40^{\circ}\text{C to } +125^{\circ}$                                                                   | 5°C                                   | 1.0  | 1.75 | 2.2  | μs    |

|                                      |                       |                                                                                                                | T <sub>J</sub> =+25°C                 | 580  | 620  | 660  |       |

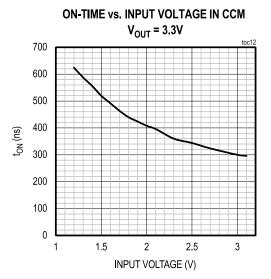

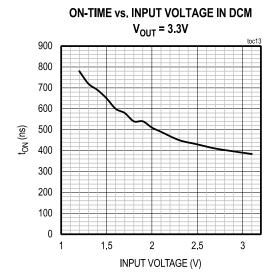

| LX On-Time in CCM                    | $t_{\text{ON\_1.2V}}$ | V <sub>IN</sub> = 1.2V                                                                                         | $T_J = -40$ °C to $+125$ °C           | 500  | 620  | 740  | ns    |

|                                      | t <sub>ON_3.0V</sub>  | V <sub>IN</sub> = 3.0V                                                                                         | T <sub>J</sub> = +25°C                | 240  | 300  | 360  |       |

|                                      |                       | $R_{SEL} = 10k\Omega, V_{IN} = 1.2V, T_{J} = +25^{\circ}C(5)$                                                  |                                       | 80   | 86   |      |       |

| LX Maximum Duty Cycle                | DC                    | $R_{SEL} = 10k\Omega, V_{IN} = 1.2V$ (5)                                                                       |                                       | 74   | 86   |      | %     |

|                                      |                       | $R_{SEL} = 191k\Omega, V_{IN} = 3.0V(\frac{5}{2})$                                                             |                                       | 65   | 75   |      |       |

| LX Leakage Current                   | I <sub>LEAK_LX</sub>  | $V_{LX} = V_{IN} = 5.5V,$<br>$V_{OUT} = V_{EN} = 0V$                                                           | T <sub>J</sub> = +25°C                |      | 1    | 100  | nA    |

| IN Current Limit                     | I <sub>IN_PT</sub>    | $V_{IN} = V_{EN} = 3.3V, V_{C}$                                                                                | <sub>DUT</sub> = 2.3V                 |      | 1.1  |      | Α     |

|                                      | I <sub>PEAK_LX</sub>  | $V_{OUT} = 3.3V, (6)$                                                                                          | T <sub>J</sub> = +25°C                | 1.9  | 2.0  | 2.1  | Α     |

analog.com Rev 0 | 3 of 27

$(V_{IN} = 1.5V, R_{SEL} = 191k\Omega, V_{OUT} = 3.3V, T_{J} = -40^{\circ}\text{C}$  to +125°C, typical values are at  $T_{J} = +25^{\circ}\text{C}, C_{IN} = 22\mu\text{F}, C_{OUT} = 22\mu\text{F}, unless otherwise noted.})$  (1)

| PARAMETER                            | SYMBOL                         | CONDITIONS/COMMENTS                          |                                     | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------|--------------------------------|----------------------------------------------|-------------------------------------|------|------|------|-------|

| Inductor Peak Current<br>Limit       |                                | V <sub>OUT</sub> = 3.3V                      | T <sub>J</sub> = -40°C to<br>+125°C | 1.8  | 2.0  | 2.2  |       |

| High-Side R <sub>DSON</sub>          | $R_{DS\_H}$                    | V <sub>OUT</sub> = 3.3V                      |                                     |      | 105  | 175  | mΩ    |

| Low-Side R <sub>DSON</sub>           | $R_{DS\_L}$                    | V <sub>OUT</sub> = 3.3V                      |                                     |      | 55   | 100  | mΩ    |

| Zero Crossing Threshold              | I <sub>ZX_LX</sub>             | ( <u>6</u> )                                 |                                     | 25   | 50   | 75   | mA    |

| Soft Start Rate                      | t <sub>ss_rate</sub>           | Target V <sub>OUT</sub> = 5.0V               |                                     |      | 3    |      | V/ms  |

| Enable Input Leakage                 | I <sub>LEAK_EN</sub>           | $T_J = +25$ °C, $V_{EN} = 5.5$ V             |                                     |      | 0.3  | 100  | nA    |

| Enable Voltage                       | $V_{EN\_IH}$                   | V <sub>EN</sub> Rising, LX begins switching  |                                     |      | 0.6  | 0.95 | V     |

| Threshold                            | $V_{EN\_IL}$                   | V <sub>EN</sub> Falling, LX stops switching  |                                     | 0.15 | 0.55 |      | V     |

| Required Select Resistor<br>Accuracy | ACC <sub>RSEL</sub>            | Note: Use the resistor from <i>Table 4</i> . |                                     | -1   |      | +1   | %     |

| Select Resistor<br>Detection Time    | $t_{\scriptscriptstyle{RSEL}}$ | C <sub>RSEL</sub> < 2pF ( <sup>7</sup> )     |                                     | 240  | 600  | 1320 | μs    |

| Thermal Shutdown                     | $T_{SHUT}$                     | OUT disabled                                 | T <sub>J</sub> Rising               |      | 165  |      | °C    |

| Threshold                            | ' SHUT                         | OUT disabled                                 | T <sub>J</sub> Falling              |      | 150  |      |       |

Limits over the specified operating temperature and supply voltage range are guaranteed by design and characterization, and production tested at room temperature only.

analog.com Rev 0 | 4 of 27

<sup>&</sup>lt;sup>2</sup> Guaranteed by the Required Select Resistor Accuracy parameter.

Output Accuracy in Low-Power mode when I<sub>OUT</sub> > I<sub>OUT\_TRANSITION</sub> and inductor current is not in Continuous Conduction mode. This accuracy does not include load, line, or ripple.

<sup>&</sup>lt;sup>4</sup> Output Accuracy in Ultra-Low-Power mode when I<sub>OUT</sub> < I<sub>OUT\_TRANSITION</sub>. This accuracy does not include load, line, or ripple.

<sup>&</sup>lt;sup>5</sup> Guaranteed by measuring LX frequency and duty cycle. Maximum duty cycle is a function of input voltage since LX on time varies with V<sub>IN</sub>.

$<sup>^6</sup>$   $\,$  This is static measurement. The actual peak current limit depends on  $V_{IN}$  and L due to propagation delays.

$<sup>^{\</sup>rm 7}$   $\,$  This is the time required to acquire the  $\rm R_{\rm SEL}$  value. This time adds to the startup time.

### **ABSOLUTE MAXIMUM RATINGS**

**Table 2. Absolute Maximum Ratings**

| PARAMETER                                                                                   | RATING                                              |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------|

| IN, EN, RSEL, OUT to GND                                                                    | -0.3V to +6V                                        |

| LX RMS Current                                                                              | -1.6A <sub>RMS</sub> to +1.6A <sub>RMS</sub>        |

| IN RMS Current                                                                              | -0.8A <sub>RMS</sub> to +0.8A <sub>RMS</sub>        |

| LX to GND                                                                                   | -0.3V to (V <sub>OUT</sub> + 0.3V) ( <sup>1</sup> ) |

| Output Short-Circuit Duration                                                               | Continuous                                          |

| Continuous Power Dissipation - WLP ( $T_A = +70^{\circ}C$ ) (Derate 10.51mW/°C above +70°C) | 840mW                                               |

| Continuous Power Dissipation - TDFN ( $T_A$ = +70°C) (Derate 11.7mW/°C above 70°C)          | 937.9mW                                             |

| Operating Junction Temperature Range                                                        | -40°C to +125°C                                     |

| Maximum Junction Temperature                                                                | +150°C                                              |

| Storage Temperature Range                                                                   | -65°C to +150°C                                     |

LX pin has internal clamps to GND and OUT. These diodes may be forward biased during switching transitions. During these transitions, the max LX current should be within the Max RMS Current rating for safe operation.

Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

analog.com Rev 0 | 5 of 27

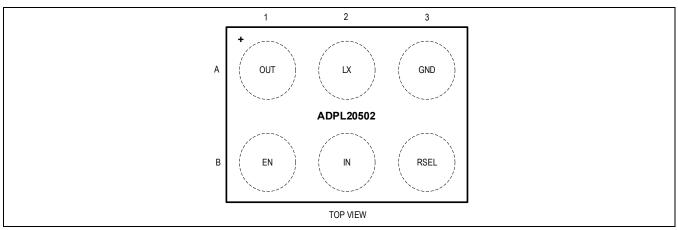

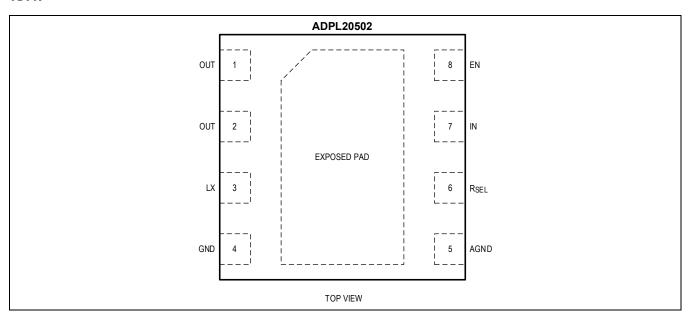

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

# **Pin Configurations**

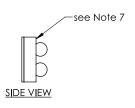

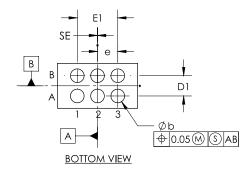

WLP

**TDFN**

analog.com Rev 0 | 6 of 27

# **Pin Descriptions**

## Table 3. Pin Descriptions

| PIN |      | NAME | DESCRIPTION                                                                                                                                                                                                                                                                                 |

|-----|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WLP | TDFN | NAME | DESCRIPTION                                                                                                                                                                                                                                                                                 |

| A1  | 1,2  | OUT  | Output Pins. Connect a 22µF X7R ceramic capacitor to ground.                                                                                                                                                                                                                                |

| A2  | 3    | LX   | Switching Node. Connect a 1.0µH inductor from LX to IN.                                                                                                                                                                                                                                     |

| A3  | 4    | GND  | Power Ground Pin. Connect to GND. In the TDFN package, applications connect to the exposed pad (EP) externally in the PCB layout at a single point.                                                                                                                                         |

| _   | 5    | AGND | Analog Ground Pin. Connect to the EP externally in the PCB layout at a single point.                                                                                                                                                                                                        |

| В3  | 6    | RSEL | Output Voltage Select Pin. Connect a resistor from RSEL to GND based on the desired output voltage. See <i>Table 4</i> . RSEL floats in shutdown. Care must be taken that the total capacitance on this pin should be less than 2pF. See <i>PCB Layout Guidelines</i> for more information. |

| B2  | 7    | IN   | Input Pin. Connect a 22µF X7R ceramic capacitor to ground. Depending on the specific application requirements, more capacitance may be needed.                                                                                                                                              |

| B1  | 8    | EN   | Enable Input Pin. Force this pin to larger than 0.6V to enable the boost converter. Force this pin below 0.55V to disable the part and enter the True Shutdown mode.                                                                                                                        |

| _   | EP   | EP   | Exposed Pad. Connect the EP to GND. Functionally connected to AGND. Connect the GND and AGND pins to EP externally in the PCB layout with short traces under the device.                                                                                                                    |

analog.com Rev 0 7 of 27

### TYPICAL OPERATING CHARACTERISTICS

$(ADPL20502AANT+, IN = 1.5V, OUT = 3.3V, L = 1.0\mu H, C_{IN} = 22\mu F, C_{OUT} = 22\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

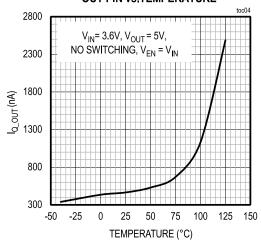

# TOTAL SYSTEM SHUTDOWN CURRENT vs.TEMPERATURE

# QUIESCENT CURRENT INTO OUT PIN vs.TEMPERATURE

analog.com Rev 0 8 of 27

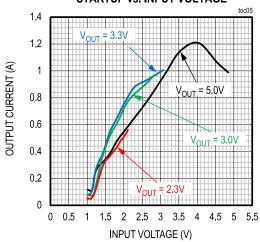

# MAXIMUM OUTPUT CURRENT DURING STARTUP vs. INPUT VOLTAGE

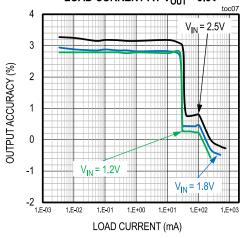

# OUTPUT VOLTAGE ACCURACY vs. LOAD CURRENT AT V<sub>OUT</sub> = 3.3V

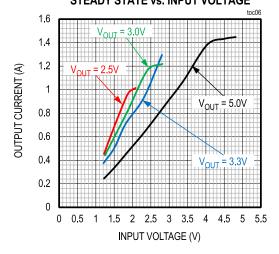

# MAXIMUM OUTPUT CURRENT AT STEADY STATE vs. INPUT VOLTAGE

# EFFICIENCY vs. LOAD CURRENT

analog.com Rev 0 9 of 27

analog.com Rev 0 | 10 of 27

analog.com Rev 0 | 11 of 27

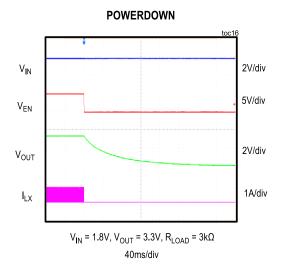

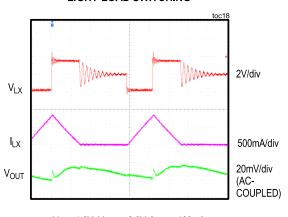

#### **ULTRA LIGHT-LOAD SWITCHING**

#### ......

2µs/div

#### **LIGHT-LOAD SWITCHING**

$V_{IN}$  = 1.8V,  $V_{OUT}$  = 3.3V,  $I_{OUT}$  = 100mA 400ns/div

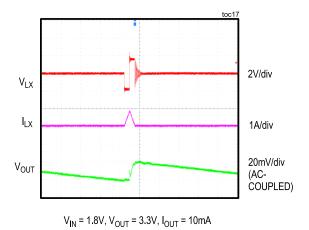

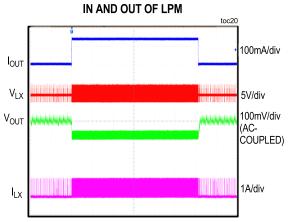

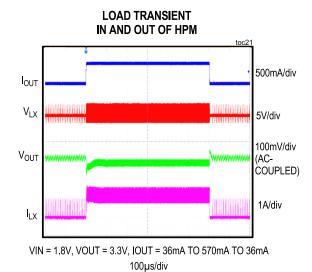

# LOAD TRANSIENT

$V_{IN}$  = 1.8V,  $V_{OUT}$  = 3.3V,  $I_{OUT}$  = 10mA TO 120mA TO 10mA 800 $\mu$ s/div

analog.com Rev 0 12 of 27

analog.com Rev 0 | 13 of 27

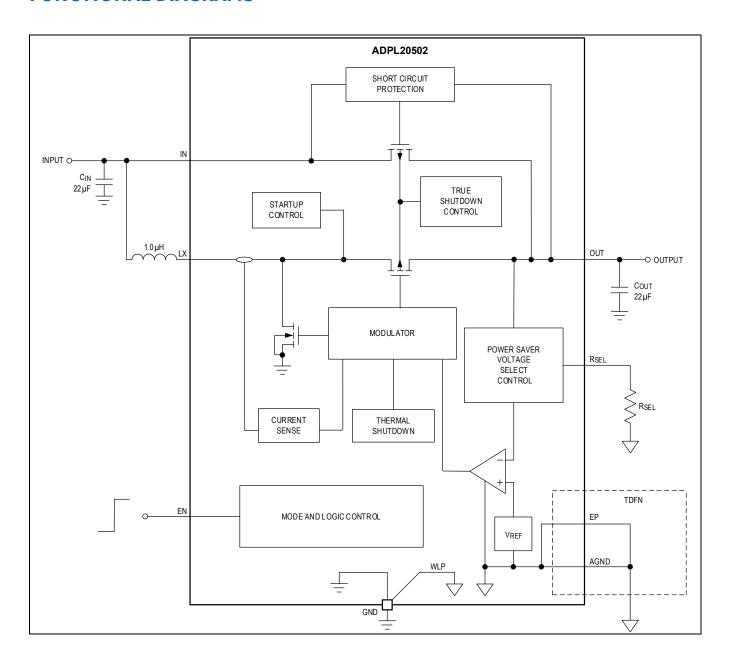

## **FUNCTIONAL DIAGRAMS**

analog.com Rev 0 14 of 27

#### **DETAILED DESCRIPTION**

The ADPL20502 is an ultra-low  $I_Q$  synchronous step-up converter optimized for battery-powered systems requiring long battery running time, high efficiency across wide load range, and small solution size. The device can operate across a wide input voltage ranging from 0.6V to 5.5V. The ADPL20502 consumes only 500nA of current, output referred while in regulation. The output voltage is programmed in the range between 2.3V to 5.2V with 100mV resolution using a single resistor connected from the RSEL pin to ground. 5.4V and 5.5V output target levels are available. However, the device does not support ultra-low-power mode when the target output voltage is either 5.4V or 5.5V.

The ADPL20502 utilizes an adaptive on-time PFM control scheme that allows ultra-low quiescent current and high efficiency over a wide output current range. The peak inductor current is set by on-time or by cycle-by-cycle 2A current limit. The device provides the True Shutdown feature where the load is completely disconnected from the input minimizing leakage current. The ADPL20502 features short-circuit and thermal protection.

#### **Control Scheme**

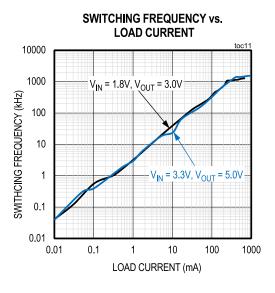

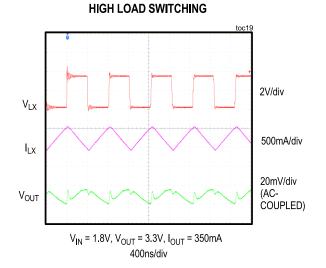

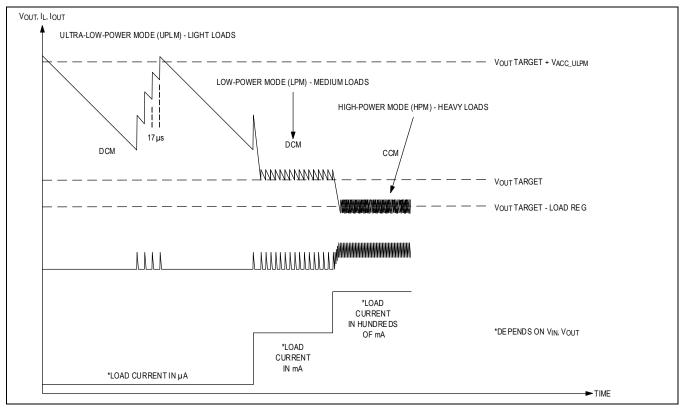

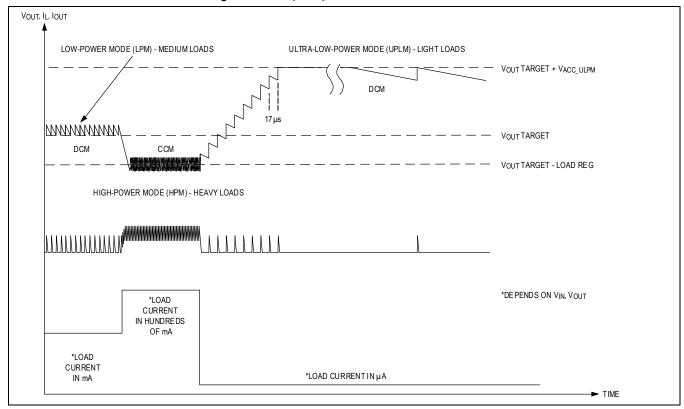

The ADPL20502 boost converter is controlled by a unique, adaptive on-time pulse frequency modulation scheme that allows very high-efficiency operation across full load current range. The ADPL20502 automatically switches between the Ultra-Low-Power mode (ULPM), Low-Power mode (LPM) and High-Power mode (HPM) of operation, depending on the load current. *Figure 3* and *Figure 4* show typical waveforms while in each mode. On-time is a function of  $V_{\rm IN}$  with typical performance shown in *Typical Operating Characteristics*.

The output voltage is regulated 2.7% higher while in ULPM ( $V_{ACC\_ULPM}$ ). This reduces the effective skip frequency, significantly improving the system's efficiency. In addition, operating marginally above the regulation threshold, the device has an excellent transient response when a large load transient event occurs. The device will typically be in ULPM when the system is in standby state. Once the output voltage exceeds the ULPM regulation level, the device will go into sleep mode, consuming very low quiescent current. It will wake up to resume switching when the output voltage falls below the threshold. While in this mode, the device will regulate output while consuming only 500nA of current. Such a low current consumption translates into great performance, achieving 90% efficiency at 10 $\mu$ A load current.

The ADPL20502 will transition to LPM once the load current is high enough that it forces the device to switch faster than  $17\mu s$ . The load current level at which this transition happens is a function on the operating condition and component selection. The user can calculate the value of the load current where ULPM transitions to LPM using the equation below:

$$I_{OUT\_TRANSITION} = \left(\frac{(t_{ON})^2}{2 \times L}\right) \times \left(\frac{V_{IN}}{\frac{V_{OUT}}{V_{IN}} - 1}\right) \times \left(\frac{n}{17\mu s}\right)$$

For example, for  $V_{IN}$  = 1.2V,  $V_{OUT}$  = 3V and L = 1.0 $\mu$ H, assuming 85% efficiency the UPLM to LPM transition current happens at approximately 11.3mA.

The ADPL20502 enters HPM when the inductor current transitions from DCM to CCM. The inductor current ripple will be reduced in the CCM operation in order to assure proper mode transitions. The voltage is regulated by an error amplifier that compares the output voltage to the internal reference and adjusts inductor current accordingly achieving great load regulation performance of 1.2%.

analog.com Rev 0 | 15 of 27

Figure 3. ULPM, LPM, HPM Transition Waveforms

Figure 4. LPM, HPM, ULPM Transition Waveforms

analog.com Rev 0 | 16 of 27

#### **Output Voltage Selection**

The ADPL20502 has a unique single resistor output selection method where one can select 32 different voltage selections from 2.3V to 5.5V, as shown in *Table 4*.

At startup, the ADPL20502 sources up to  $200\mu A$  during the select resistor detection time, typically for  $600\mu s$  (tRSEL), to read the  $R_{SEL}$  value.

Care must be taken that the total capacitance on this pin should be less than 2pF. See *PCB Layout Guidelines* for more information.

The R<sub>SEL</sub> output voltage selection method has many benefits:

- In conventional boost converters, current is drawn from output continuously through a feedback resistor-divider. In the ADPL20502, 200μA current is drawn from output only during startup, which helps to increase efficiency at light loads.

- ► Lower cost and smaller size, since only one resistor is needed versus the two resistors needed in typical feedback connections.

- ► The R<sub>SEL</sub> feature allows customers to stock just one part in their inventory system and use it in multiple projects with different output voltages just by changing a single standard 1% resistor.

- ► The R<sub>SEL</sub> feature allows much higher internal feedback resistors instead of lower impedance external feedback resistors to enable for ultra-low-power applications.

Select the R<sub>SEL</sub> resistor value by choosing the desired output voltage in the *Table 4*.

**Table 4. R<sub>SEL</sub> Selection Table**

| TARGET OUTPUT VOLTAGE VOUT (V) | RSEL STANDARD RESISTOR 1% (kΩ) |

|--------------------------------|--------------------------------|

| 2.3                            | OPEN                           |

| 2.4                            | 909                            |

| 2.5                            | 768                            |

| 2.6                            | 634                            |

| 2.7                            | 536                            |

| 2.8                            | 452                            |

| 2.9                            | 383                            |

| 3.0                            | 324                            |

| 3.1                            | 267                            |

| 3.2                            | 226                            |

| 3.3                            | 191                            |

| 3.4                            | 162                            |

| 3.5                            | 133                            |

| 3.6                            | 113                            |

| 3.7                            | 95.3                           |

| 3.8                            | 80.6                           |

| 3.9                            | 66.5                           |

| 4.0                            | 56.2                           |

| 4.1                            | 47.5                           |

| 4.2                            | 40.2                           |

| 4.3                            | 34.0                           |

analog.com Rev 0 | 17 of 27

| 4.4  | 28.0            |

|------|-----------------|

| 4.5  | 23.7            |

| 4.6  | 20.0            |

| 4.7  | 16.9            |

| 4.8  | 14.0            |

| 4.9  | 11.8            |

| 5.0  | 10.0            |

| 5.1  | 8.45            |

| 5.2  | 7.15            |

| 5.4* | 4.99            |

| 5.5* | SHORT TO GROUND |

<sup>\*</sup> Indicates ULPM disabled.

### **Fixed-Output Voltage Version**

In applications where board space is at a premium, contact a Maxim Integrated representative to order fixed-output versions that don't require the  $R_{\text{SEL}}$  resistor to program the output voltage. The RSEL pin must be left floating for fixed output versions. The output voltage can be preprogrammed in the range from 2.3V to 5.2V with 100mV resolution. 5.3V, 5.4V, and 5.5V output target levels are available. The output target levels programmed to 5.3V, 5.4V, and 5.5V will have the ULPM disabled.

#### **Features**

#### **Enable**

The ADPL20502 includes an enable input pin (EN). Connect EN pin to IN pin or drive it to more than 0.6V ( $V_{EN\_IH}$ ) for normal operation. When EN pin goes below 0.55V ( $V_{EN\_IL}$ ), ADPL20502 enters True Shutdown mode. The device will consume 1nA (ISD\_IN) of current from  $V_{IN}$  while in this mode.

In shutdown, the output is truly disconnected from the input. In conventional boost circuits, the body diode of the synchronous rectifier is forward biased in shutdown and allows current flow from the battery to the output. If the load cannot be shut down, a load switch is required to avoid depleting the battery during the shutdown. A proprietary design in the ADPL20502 allows the synchronous rectifier to provide True Shutdown with no additional components. True Shutdown on the ADPL20502 allows the output to be biased at any voltage or grounded without consuming any current from IN or OUT pins other than pin leakage currents.

#### **Soft-Start Control**

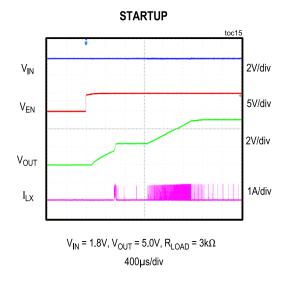

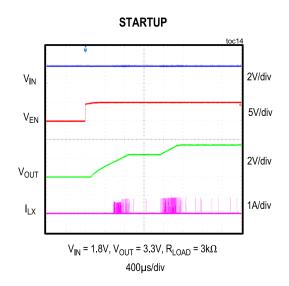

After the EN pin goes above its raising threshold (V<sub>EN IH</sub>), the ADPL20502 begins the startup.

When the output capacitor is fully discharged prior to the device being enabled, the startup follows the below steps:

When  $V_{IN}$  is at its final level, for example, 3V, the ADPL20502 ramps the output to the level where  $V_{OUT}$  starts approaching  $V_{IN}$ , at which point switching is enabled. It then acquires the RSEL pin voltage level to determine the output target level. Then, the output is ramped up to its target voltage level, for example, 5.0V following a 3V/ms slew rate. This controls the amount of inrush current into the output capacitor.

The ADPL20502 starts with a 0.9V input voltage and a load resistance of  $3k\Omega$  or larger. Enabling the device when  $V_{IN}$  is between 0.9V and 2.0V will be load current limited. If the load current is heavy such that it does not allow the ADPL20502 to charge the output above 1.5V, the device cannot reach its output target level until  $V_{IN}$  is increased or the load current is reduced.

analog.com Rev 0 | 18 of 27

Data Sheet ADPL20502

The ADPL20502 initiates a controlled soft start when supply voltage is applied at high dV/dt rate, for example, during installation of a fresh battery. While in regulation, if  $V_{IN}$  steps abruptly above  $V_{OUT}$  for more than 1V, the device resets. In this case, output voltage droop will be a function of the load current, output capacitance, and time required for soft-start to complete, which is typically 1.6ms.

For maximum load conditions during soft start, see the *Typical Operating Characteristics* section.

#### **Short-Circuit Protection**

The ADPL20502 is protected from an output short-circuit condition by current and thermal overload circuits. If the output voltage is detected 1V lower than the input voltage during operation, the ADPL20502 enters the short-circuit protection mode. Once the short-circuit event is detected, the synchronous rectifier and its body diode are disconnected from the output, and the short-circuit protection block gets engaged. The short-circuit current  $(I_{IN\_PT})$  is limited to 1.1A. Under this condition, the part will heat up due to high power dissipation in the short-circuit protection device, and likely enter thermal shutdown.

#### **Thermal Shutdown**

The ADPL20502 features thermal shutdown. The converter and short circuit protection device turn off when the junction temperature exceeds +165°C. Once the device cools by 15°C, the converter will resume operation. If the fault condition is not removed, the regulator will cycle on and off.

analog.com Rev 0 | 19 of 27

## **Design Procedure**

#### **Inductor Selection**

It is recommended to use a  $1.0\mu H$  inductor. This inductor value provides the best size and efficiency trade-off in most applications.

#### **Input Capacitor**

Input capacitors reduce current peaks from the input supply and increase efficiency. For the input capacitor, choose a ceramic capacitor because they have the lowest equivalent series resistance (ESR), smallest size, and lowest cost. Other capacitor types can be used as well but will have larger ESR. The biggest downside of ceramic capacitors is their capacitance derating with higher DC bias and, because of this, at minimum a standard  $22\mu F$  ceramic capacitor is recommended at the input for all applications. For applications which use batteries that have a high source impedance greater than  $1\Omega$ , more capacitance may be needed. A good starting point is to use the same capacitance value at the input as well as output. In applications where  $V_{IN}$  is approaching  $V_{OUT}$ , more input capacitance will be required to minimize input voltage ripple.

At a minimum, a standard 22µF X7R ceramic capacitor is recommended for all applications. Due to DC bias effects the effective capacitance can be 80% lower than the nominal capacitor value. The capacitor data sheet needs to be consulted for proper DC bias, AC ripple, and temperature capacitance derating.

#### **Output Capacitor**

A  $22\mu F$  ceramic capacitor is recommended for all applications. The output capacitor ( $C_{OUT}$ ) is required to keep the output voltage ripple small and to ensure loop stability.  $C_{OUT}$  must have low impedance at the switching frequency. Ceramic capacitors are recommended due to their small size and low ESR. Make sure the minimum effective capacitance is  $11\mu F$  over temperature, DC bias, and AC ripple capacitor data sheet specifications. Capacitors with X7R temperature characteristics typically perform well. In applications where  $V_{IN}$  is approaching  $V_{OUT}$ , more output capacitance is required to minimize the output voltage ripple.

#### **PCB Layout Guidelines**

Careful PCB layout is important, especially in DC-DC converters. Poor layout can affect the IC performance, causing electromagnetic interference (EMI) and electromagnetic compatibility (EMC) issues, ground bounce, and voltage drops, etc. Poor layout can also affect regulation and stability.

A good layout is implemented using the following rules:

- ▶ Place the inductor, input capacitor, and output capacitor close to the IC using short traces. These components carry high switching currents, and long traces act like antennas. The output capacitor placement is the most important in the PCB layout and make sure it is placed directly next to the IC. The inductor and input capacitor placement are secondary to the output capacitor's placement but should remain close to the IC.

- ► The connection from the bottom plate of the output capacitor and the ground pin of the device must be extremely short, as should be that of the input capacitor.

- ▶ Similarly, the top plate of output capacitor and the OUT pin of the device must be short as well.

- ▶ Minimize the surface area used for LX since this is the noisiest node.

- ▶ Keep the main power path from IN, LX, OUT, and GND as tight and short as possible.

- ▶ Route the output voltage path away from the inductor and LX\_ switching node to minimize noise and magnetic interference.

- ▶ Maximize the size of the ground metal on the component side to help with thermal dissipation. Use a ground plane with several vias connecting to the component-side ground to further reduce noise interference on sensitive circuit nodes.

analog.com Rev 0 | 20 of 27

► Lastly, the trace used for RSEL should neither be too long nor should produce a capacitance of more than 2pF. It is recommended to consult the **ADPL20502 Evaluation board layout**.

#### **Thermal Considerations**

In most applications, the IC does not dissipate much heat due to its high efficiency. But in applications where the IC runs at high ambient temperature with heavy loads, the heat dissipated may cause the temperature to exceed +125°C or the maximum junction temperature of the part. If the junction temperature reaches approximately +165°C (TJ Rising), the thermal-overload protection is activated. The maximum power dissipation depends on the thermal resistance of the IC package and the application circuit board.

The power dissipated (PD) in the device is:

$$P_D = P_{IN} - P_{OUT} - P_{IND}$$

where  $P_{IND}$  is power dissipated in the inductor that includes DC, AC, and core losses;  $P_{OUT}$  is power delivered to the load.

The maximum allowed power dissipation is:

$$P_{D\_MAX} = \frac{T_{JMAX} - T_A}{\theta_{JA}}$$

where  $(T_{JMAX} - T_A)$  is the temperature difference between the ADPL20502 maximum rated junction temperature (+125°C) and the surrounding ambient temperature, and  $\theta_{JA}$  is the thermal resistance of the junction through the package, PCB, copper traces, and other materials to the surrounding ambient temperature.

analog.com Rev 0 | 21 of 27

# **TYPICAL APPLICATION CIRCUIT**

Figure 5. Typical Application Circuit

analog.com Rev 0 22 of 27

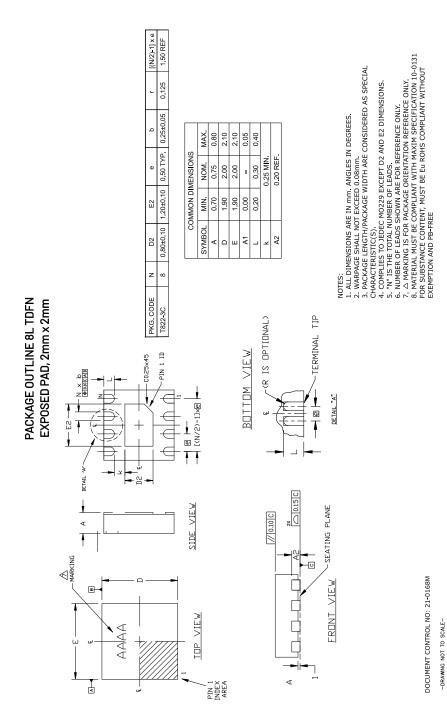

### **OUTLINE DIMENSIONS**

Table 5. Thermal Resistance of 8 TDFN-EP

| Thermal Resistance, Four-Layer Board <sup>9</sup>      |          |  |  |  |

|--------------------------------------------------------|----------|--|--|--|

| Junction-to-Ambient ( $\theta_{JA}$ )                  | 85.3°C/W |  |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 8.9°C/W  |  |  |  |

Table 6. Thermal Resistance of 6-bump WLP

| Thermal Resistance, Four-Layer Board $^{	ilde{2}}$     |           |  |  |  |

|--------------------------------------------------------|-----------|--|--|--|

| Junction-to-Ambient ( $\theta_{JA}$ )                  | 95.15°C/W |  |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | N/A       |  |  |  |

<sup>&</sup>lt;sup>9</sup> Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board.

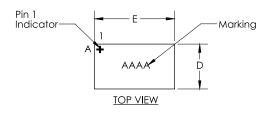

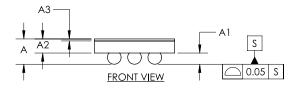

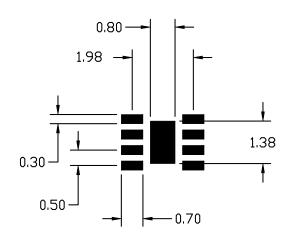

#### PACKAGE OUTLINE 6-Bumps THIN WLP, 0.4mm PITCH

| COMMON DIMENSIONS |                      |  |  |  |

|-------------------|----------------------|--|--|--|

| Α                 | 0.50 MAX             |  |  |  |

| A1                | 0.19 ±0.03           |  |  |  |

| A2                | 0.28 REF             |  |  |  |

| А3                | 0.04 BASIC           |  |  |  |

| b                 | Ø0.27 ±0.03          |  |  |  |

| D                 | 0.888 ±0.025         |  |  |  |

| Е                 | 1.578 ±0.025         |  |  |  |

| D1                | 0.40 BASIC           |  |  |  |

| Εl                | 0.80 BASIC           |  |  |  |

| е                 | 0.40 BASIC           |  |  |  |

| SD                | 0.20 BASIC           |  |  |  |

| SE                | 0.00 BASIC           |  |  |  |

| DEPC<br>NON       | OPULATED BUMPS:<br>E |  |  |  |

|                   |                      |  |  |  |

- NOTES:

1. Terminal pitch is defined by terminal center to center value.

2. Outer dimension is defined by center lines between scribe lines.

3. All dimensions in millimeter.

- All dimensions in millimeters.

Marking shown is for package orientation reference only.

Tolerance is ± 0.02 unless specified otherwise.

All dimensions apply to PbFree (+) package codes only.

Front side finish can be either Black or Clear.

DOCUMENT CONTROL No.: 21-100390A

For Land Pattern details Refer to Application Note 1891

- DRAWING NOT TO SCALE -

Rev 0 23 of 27 analog.com

analog.com Rev 0 | 24 of 27

#### PACKAGE LAND PATTERN 8L TDFN, 2mm x 2mm

PKG. CODE [T822-3C]

#### NOTES:

- 1. REFERENCE PKG. DUTLINE: 21-0168

- 2. LAND PATTERN COMPLIES TO: IPC7351A.

- 3. TOLERANCE: +/- 0.02 MM.

- 4. ALL DIMENSIONS APPLY TO BOTH LEADED (-) AND POFREE (+) PKG. CODES.

- 5. ALL DIMENSIONS IN MM.

-DRAWING NOT TO SCALE-

DOCUMENT CONTROL NO .- 90-0065E

This document (including dimensions notes & specs) is a recoomendation based on typical circuit baord manufaturing parameters. Since land pattern design depend on many factors unknown to Analog (eg. user's board manufacturing specs), user must determine sutability for use. This document is subject to change without notice. Contact technical support at https://www.analog.com/en/support/technical-support

analog.com Rev 0 | 25 of 27

Data Sheet ADPL20502

## **ORDERING GUIDE**

**Table 7. Ordering Guide**

| PART NUMBER    | TEMPERATURE RANGE | PIN-PACKAGE |

|----------------|-------------------|-------------|

| ADPL20502AANT+ | -40°C to +125°C   | 6-bump WLP  |

| ADPL20502AATA+ | -40°C to +125°C   | 8-pin TDFN  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

analog.com Rev 0 26 of 27

T = Tape and reel.

ALL INFORMATION CONTAINED HEREIN IS PROVIDED "AS IS" WITHOUT REPRESENTATION OR WARRANTY. NO RESPONSIBILITY IS ASSUMED BY ANALOG DEVICES FOR ITS USE, NOR FOR ANY INFRINGEMENTS OF PATENTS OR OTHER RIGHTS OF THIRD PARTIES THAT MAY RESULT FROM ITS USE. SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. NO LICENCE, EITHER EXPRESSED OR IMPLIED, IS GRANTED UNDER ANY ADI PATENT RIGHT, COPYRIGHT, MASK WORK RIGHT, OR ANY OTHER ADI INTELLECTUAL PROPERTY RIGHT RELATING TO ANY COMBINATION, MACHINE, OR PROCESS WHICH ADI PRODUCTS OR SERVICES ARE USED. TRADEMARKS AND REGISTERED TRADEMARKS ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS.

analog.com Rev 0 27 of 27

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Analog Devices Inc.:

ADPL20502EVKIT# ADPL20502AANT+T ADPL20502AATA+T