## A<sup>2</sup>B Transceiver

**AD2437**

#### A<sup>2</sup>B BUS FEATURES

#### Line topology

Single main node, up to 16 subordinate nodes

Up to 30 m between nodes and up to 300 m overall cable length

#### Communication over distance

Synchronous data

Multichannel I<sup>2</sup>S/TDM to I<sup>2</sup>S/TDM

Clock synchronous, phase aligned in all nodes

Low latency node to node communication

Control and status information I<sup>2</sup>C to I<sup>2</sup>C

**GPIO** over distance

Bus power or local power subordinate nodes

Configurable with SigmaStudio+ graphical software tool

#### **BASELINE A<sup>2</sup>B TRANSCEIVER FEATURES**

Configurable as A<sup>2</sup>B bus main node or subordinate node Programmable via I<sup>2</sup>C and SPI interfaces

8-bit to 32-bit multichannel I<sup>2</sup>S/TDM interface

I<sup>2</sup>S/TDM/PDM programmable data rate

Up to 51 channels of 16-bit data or 32 channels of 24-bit data between nodes

PDM inputs for up to 4 high dynamic range microphones on main or subordinate nodes

Support for receiving I<sup>2</sup>S/TDM and PDM data on the same node

Unique ID register for each transceiver

Support for crossover or straight-through cabling

#### **AD2437 TRANSCEIVER ENHANCEMENTS**

#### **Mixed Signal**

ADC monitoring of supply voltages

Supports 3.3 V input at VIN in Low Voltage Input (LVI)

#### Digital

High speed SPI (up to 10 Mbps) over distance

**Dedicated hardware reset pin**

I<sup>2</sup>S/TDM crossbar switch

Flexible mapping of Tx/Rx TDM channel data to A<sup>2</sup>B slot

Support for I<sup>2</sup>C fast mode plus (1 MHz)

**Support for LED lighting control using 4 PWM outputs**

8 GPIO pins with configurable pin mapping

#### **APPLICATIONS**

Conference room transducer nodes Musical instrument connectivity Distributed audio systems Personal audio zones

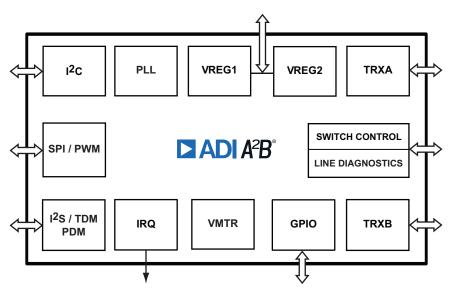

Figure 1. Functional Block Diagram

A<sup>2</sup>B and the A<sup>2</sup>B logo are registered trademarks of Analog Devices, Inc.

#### Rev. 0 Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### **TABLE OF CONTENTS**

| A <sup>2</sup> B Bus Features                  |

|------------------------------------------------|

| Baseline A <sup>2</sup> B Transceiver Features |

| AD2437 Transceiver Enhancements                |

| Applications                                   |

| Table of Contents                              |

| Revision History                               |

| General Description                            |

| A <sup>2</sup> B Bus Details                   |

| I <sup>2</sup> C Interface                     |

| I <sup>2</sup> S/TDM Interface                 |

| Pulse Density Modulation (PDM) Interface 6     |

| Data Slot Exchange Between Subordinate Nodes 6 |

| I <sup>2</sup> S TX/RX Crossbar                |

| Serial Peripheral Interface (SPI)              |

| Pulse Width Modulation (PWM) Interface 7       |

| GPIO Over Distance                             |

| Mailboxes                                      |

| Line Diagnostics                               |

| Clock Sustain State                            |

| Dedicated Interrupt                            |

| Support for Parallel A <sup>2</sup> B Buses    |

| Voltage Monitor (VMTR) ADC                     |

| Power on Reset                                 |

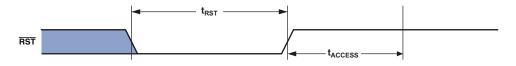

| Hardware Reset                                 |

| Low Voltage Input (LVI) Mode                   |

| Power Configurations                           |

| Standby Mode                                |

|---------------------------------------------|

| Unique ID                                   |

| Support for Cabling                         |

| Additional Information                      |

| Specifications                              |

| Operating Conditions                        |

| Electrical Characteristics                  |

| VMTR ADC Specifications                     |

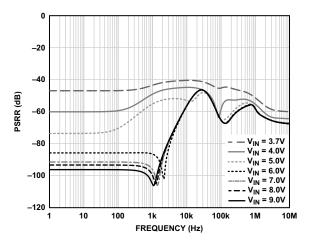

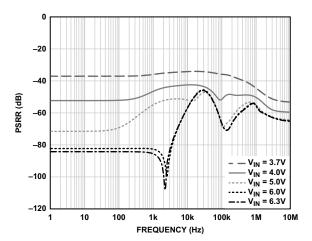

| Power Supply Rejection Ratio (PSRR)         |

| Timing Specifications                       |

| A <sup>2</sup> B Bus System Specification   |

| Power-Up Sequencing Restrictions            |

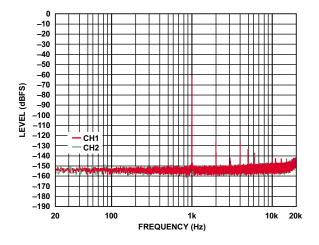

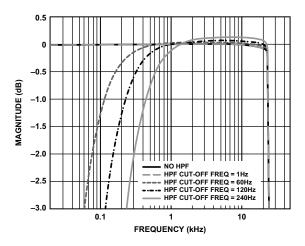

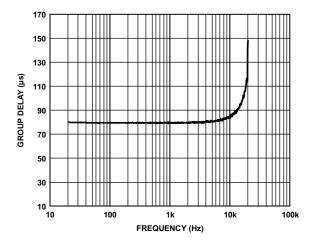

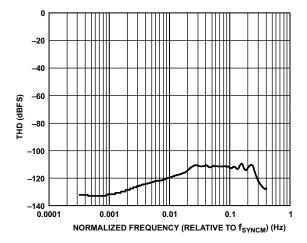

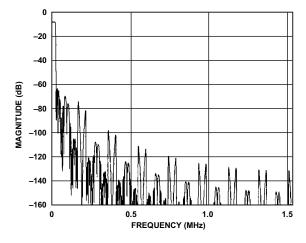

| PDM Typical Performance Characteristics     |

| Absolute Maximum Ratings                    |

| ESD Caution                                 |

| Thermal Characteristics                     |

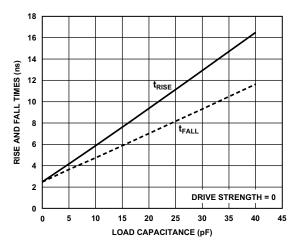

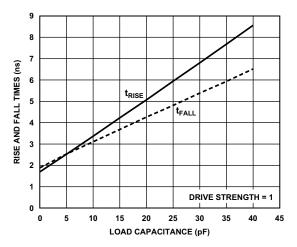

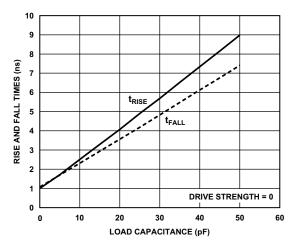

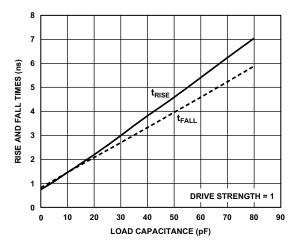

| Test Circuits and Switching Characteristics |

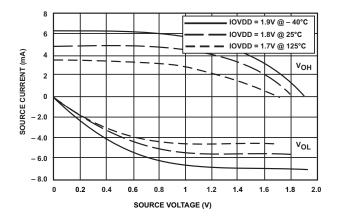

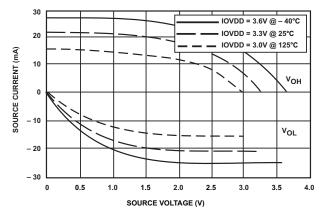

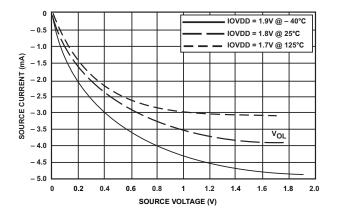

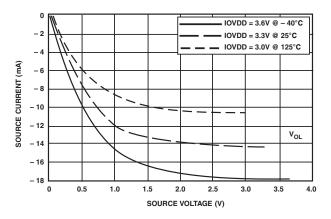

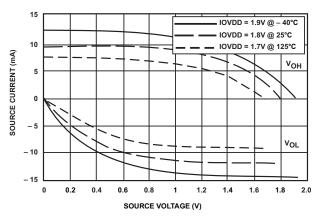

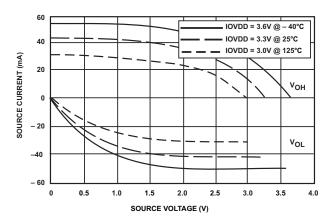

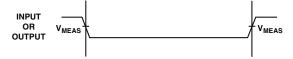

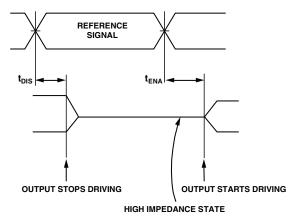

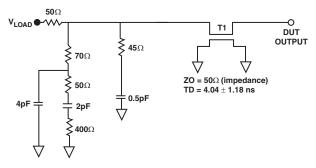

| Output Drive Currents                       |

| Test Conditions                             |

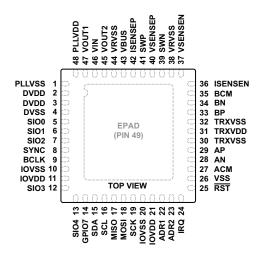

| Pin Configuration and Function Descriptions |

| Designer Reference                          |

| PCB Layout                                  |

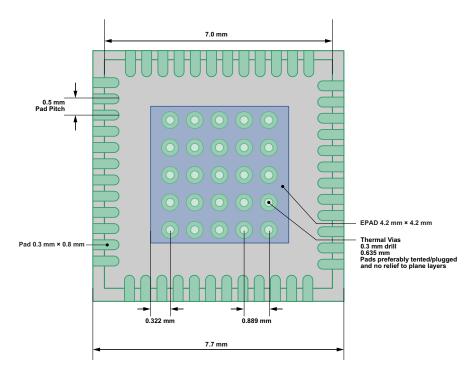

| Recommended PCB Footprint                   |

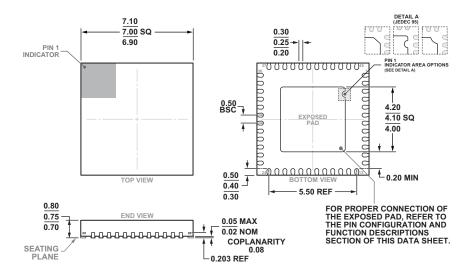

| Outline Dimensions                          |

| Ordering Guide                              |

#### **REVISION HISTORY**

#### 7/2023—Revision 0: Initial Version

Analog Devices is in the process of updating documentation to provide terminology and language that is culturally appropriate. This is a process with a wide scope and will be phased in as quickly as possible. Thank you for your patience.

### **GENERAL DESCRIPTION**

The AD2437  $A^2B^{\otimes}$  transceiver provides a multichannel,  $I^2S/TDM$  link over distances of up to 30 m between nodes. It embeds bidirectional synchronous pulse-code modulation (PCM) data (for example, digital audio), clock, and synchronization signals onto a single-pair differential cable.  $A^2B$  supports a direct point to point connection and allows multiple, daisy-chained nodes at different locations to contribute and/or consume time division multiplexed channel content.

A<sup>2</sup>B is a single main node, multiple subordinate node system where the transceiver at the host controller is the main node. The main node generates clock, synchronization, and framing for all subordinate nodes. The main A<sup>2</sup>B transceiver is programmable over a control port (I<sup>2</sup>C/SPI) for configuration and read back. An extension of the control port protocol is embedded in the A<sup>2</sup>B data stream. This allows direct access to registers and status information on subordinate transceivers, as well as I<sup>2</sup>C to I<sup>2</sup>C, SPI to I<sup>2</sup>C, or SPI to SPI communication from the host to a peripheral in a subordinate node. SPI to SPI communication between subordinate nodes can be performed directly and does not need to involve the main node.

The transceiver can connect directly to general-purpose digital signal processors (DSPs), field-programmable gate arrays (FPGAs), application specific integrated circuits (ASICs), digital microphones, analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and codecs through a multichannel I<sup>2</sup>S/TDM interface. It also provides a pulse density modulation (PDM) interface for direct connection of up to four PDM digital microphones.

The transceiver supports a bus power feature, where the main node supplies voltage and current to the subordinate nodes over the same daisy-chained, single-pair wire or XLR/DMX cable as used for the communication link.

The transceiver also supports a broad spectrum of Ethernet cables in which the A<sup>2</sup>B occupies only one pair of a category (CAT) cable. This frees up the remaining CAT cable pairs for power delivery.

**Table 1. Product Features**

| Feature                         | AD2437     |

|---------------------------------|------------|

| Main node capable               | Yes        |

| Functional TRX blocks           | A + B      |

| I <sup>2</sup> S/TDM support    | Yes        |

| PDM microphone inputs           | 4 mics     |

| A <sup>2</sup> B bus power      | Up to 50 W |

| Nominal bus bias voltage (VBUS) | 24 V       |

| SPI over distance               | Yes        |

| Power configuration             | CFG-4      |

#### A<sup>2</sup>B BUS DETAILS

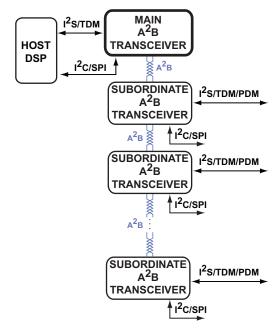

Figure 2 shows a single main node, multiple subordinate node A<sup>2</sup>B communications system with the main transceiver controlled by the host. The host generates a periodic synchronization signal on the I<sup>2</sup>S/TDM interface at a fixed frequency (typically 48 kHz) to which all A<sup>2</sup>B nodes synchronize.

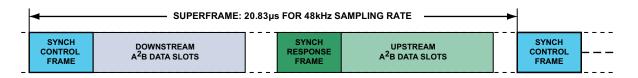

Communications along the  $A^2B$  bus occur in periodic superframes. The superframe frequency is the same as the synchronization signal frequency, and data is transferred at a bit rate that is 1024 times faster (typically 49.152 MHz). Each superframe is divided into periods of downstream transmission, upstream transmission, and no transmission (where the bus is not driven). Data is exchanged over the  $A^2B$  bus in equal width slots for both upstream and downstream transmissions. Up to 32 bidirectional slots can be configured at 24 bits, while up to 51 slots can be configured at 16 bits.

Figure 2. Communication System Block Diagram

The A<sup>2</sup>B bus also communicates the following control and status information between nodes:

- I<sup>2</sup>C to I<sup>2</sup>C or SPI to I<sup>2</sup>C/SPI communication

- General-purpose input/output (GPIO)

- Interrupts

In Figure 3, a superframe is shown with an initial period of downstream transmission and a later period of upstream transmission.

All signals on the A<sup>2</sup>B bus are line coded, and the main node forwards the synchronization signal downstream from the main transceiver to the last subordinate node transceiver in the form

of a synchronization preamble. This preamble is followed by control data to build a synchronization control frame (SCF). Downstream, TDM synchronous data and SPI tunnel data are added directly after the control frame. Every subordinate node can use or consume some of the downstream data and add data for downstream nodes. The last subordinate node transceiver responds after the response time with a synchronization response frame (SRF). Upstream TDM synchronous data and SPI tunnel data are added by each node directly after the response frame. Each node can also use or consume upstream data.

The embedded control and response frames allow the host to individually address each subordinate transceiver in the system. The host also enables access to remote peripheral devices that are connected to the subordinate transceivers via the I<sup>2</sup>C or SPI ports for I<sup>2</sup>C to I<sup>2</sup>C, SPI to SPI, and SPI to I<sup>2</sup>C communication over distance between multiple nodes.

All nodes in an A<sup>2</sup>B system are sampled synchronously in the same A<sup>2</sup>B superframe. Synchronous I<sup>2</sup>S/TDM downstream data from the nodes arrives at all downstream subordinate nodes in the same A<sup>2</sup>B superframe, and every node's upstream audio data arrives synchronously in the same I<sup>2</sup>S/TDM frame at any upstream node. I<sup>2</sup>S/TDM to I<sup>2</sup>S/TDM communication over distance does not require involvement of the main node and can be performed directly between subordinate nodes. The remaining audio phase differences between subordinate nodes can be compensated for by register-programmable fine adjustment of the SYNC pin signal delay.

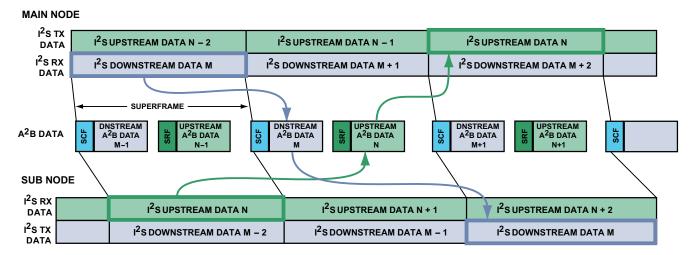

There is a sample delay incurred for data moving between the A<sup>2</sup>B bus and the I<sup>2</sup>S/TDM interfaces because data is received and transmitted over the I<sup>2</sup>S/TDM every sample period (typically 48 kHz). This timing relationship between samples over the A<sup>2</sup>B bus is shown in Figure 4. It shows the data transfer between the main node and a subordinate node, but would be similar for data transfer between any two subordinate nodes as well.

Figure 3. A<sup>2</sup>B Superframe

Figure 4. A<sup>2</sup>B Bus Synchronous Data Exchange

Note in Figure 4, both downstream and upstream samples are named for the frame where they enter the A<sup>2</sup>B system as follows:

- I<sup>2</sup>S/TDM data received by the main node transceiver in superframe M creates downstream data M and is transmitted over the A<sup>2</sup>B bus in the next superframe.

- 1<sup>2</sup>S/TDM data received by the subordinate node transceivers in superframe N creates upstream data N and is transmitted over the A<sup>2</sup>B bus in the next superframe.

- Data received via the A<sup>2</sup>B bus is transmitted on the I<sup>2</sup>S/TDM interface of an A<sup>2</sup>B transceiver in the following superframe.

- Data transmitted across the A<sup>2</sup>B bus (from any node to any node) has two frames of latency plus any internal delay that has accumulated in the transceivers, as well as delays due to wire length. Therefore, overall latency is slightly over two samples (<50 µs at 48 kHz sample periods) from the I<sup>2</sup>S/TDM interface in one A<sup>2</sup>B transceiver to the I<sup>2</sup>S/TDM interface of another A<sup>2</sup>B transceiver.

To support and extend the A<sup>2</sup>B bus functions and performance, the transceivers have additional features, as described in the following sections.

#### I<sup>2</sup>C INTERFACE

The I<sup>2</sup>C interface in the transceiver provides access to the internal registers. It has the following features:

- Target functionality in the A<sup>2</sup>B main node

- Controller or target functionality in the A<sup>2</sup>B subordinate node

- Multi-controller support in the A<sup>2</sup>B subordinate node

- 100 kbps, 400 kbps, or 1Mbps rate operation

- 7-bit addressing

- Single-word and burst mode read and write operations

- Clock stretching

Table 2. SIO Pin Mapping<sup>1</sup>

All transceivers can be accessed by a locally connected processor using the 7-bit I²C device address (BASE\_ADDR) established by the logic levels applied to the ADR2 and ADR1 pins at power-on reset, thus providing for up to four I²C controller devices connecting to the same I²C bus. A subordinate configured transceiver recognizes only this I²C device address. A main configured transceiver, however, also recognizes a second I²C device address for remote access to subordinate nodes and remote peripherals over the A²B bus (BUS\_ADDR). The least significant bit (LSB) of the 7-bit device address determines whether an I²C data exchange uses the BASE\_ADDR (bit 1 = 0) to access the local transceiver or BUS\_ADDR (bit 1 = 1) to access a bus node subordinate transceiver and remote peripherals through a main configured transceiver. See the *AD2437 A²B Transceiver Technical Reference* for details.

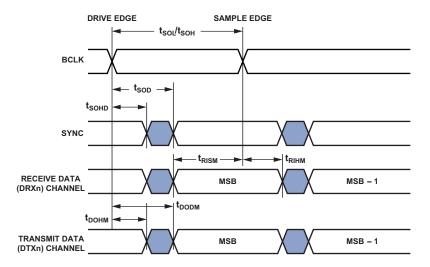

#### I<sup>2</sup>S/TDM INTERFACE

The I<sup>2</sup>S/TDM serial port operates in full-duplex mode, where both the transmitter and receiver operate simultaneously using the same critical timing bit clock (BCLK) and synchronization (SYNC) pins. A<sup>2</sup>B main transceivers receive the timing signals from BCLK and SYNC pins driven by the host device. A<sup>2</sup>B subordinate transceivers generate the timing signals on the BCLK and SYNC output pins. The I<sup>2</sup>S/TDM port features:

- Programmable clock and frame sync timing and polarity

- Numerous TDM operating modes

- 16- or 32-bit data width

- I<sup>2</sup>S TX/RX crossbar to associate specific TDM data channels with specific A<sup>2</sup>B slots

- Simultaneous operation with PDM port

The I<sup>2</sup>S/TDM/PDM port includes five programmable data pins (SIO0-SIO4) which can be configured to exchange any combination of up to two PDM streams (SIO0/1 only) and up to five I<sup>2</sup>S/TDM streams, with a maximum of four I<sup>2</sup>S/TDM streams in the same direction (see Table 2).

|      | A2B_PDMCTL.PDM1EN /PDM0EN |            |            |            |  |  |

|------|---------------------------|------------|------------|------------|--|--|

| Pin  | 00                        | 01         | 10         | 11         |  |  |

| SIO0 | DRX0                      | PDM0       | DRX0       | PDM0       |  |  |

| SIO1 | DRX1, DTX3                | DRX0, DTX3 | PDM1       | PDM1       |  |  |

| SIO2 | DRX2, DTX2                | DRX1, DTX2 | DRX1, DTX2 | DRX0, DTX2 |  |  |

| SIO3 | DRX3, DTX1                | DRX2, DTX1 | DRX2, DTX1 | DRX1, DTX1 |  |  |

| SIO4 | DTX0                      | DTX0       | DTX0       | DTX0       |  |  |

<sup>&</sup>lt;sup>1</sup> Pin mapping of I<sup>2</sup>S/TDM DTXn and DRXn depends on A2B\_PDMCTL and A2B\_I2SCFG registers. See the *AD2437 A<sup>2</sup>B Transceiver Technical Reference* for details on pin mappings.

#### I<sup>2</sup>S Reduced or Increased Rate

Subordinate transceivers can run the  $I^2S/TDM/PDM$  interface at a reduced or increased rate frequency, with respect to the superframe rate. The reduced rate frequency is derived by dividing the superframe rate from a programmable set of values. The subordinate transceiver also supports increased sampling rates of  $2\times$  and  $4\times$  superframe rates ( $f_{SYNCM}$ ). Each subordinate node transceiver can be configured to run at a different  $I^2S/TDM$  rate.

In reduced rate mode, the transceiver provides an option for a processor to track the full rate audio frame, which contains new reduced rate samples. The GPIO7 pin can be used as a strobe, and the direction can be configured as an input or output.

#### PULSE DENSITY MODULATION (PDM) INTERFACE

PDM microphones can directly interface to the SIO0/1 pins of the A<sup>2</sup>B transceiver. The PDM block on the transceiver converts a PDM input stream into pulse code modulated (PCM) data for transmission over the A<sup>2</sup>B bus, to the local device through the I<sup>2</sup>S/TDM port, or both. The PDM interface is available on both main and subordinate transceivers. It supports high dynamic range microphones with high signal-to-noise ratio (SNR) and extended maximum sound pressure level (SPL). The output rate of the PDM demodulators is controllable at the superframe (SFF), SFF/2, or SFF/4 rates. In addition, reduced rate modes support frame rates of SFF/2, SFF/4, SFF/8, SFF/12, SFF/16, SFF/20, SFF/24, SFF/28, SFF/32, and SFF/128 (for example, down to 375 Hz for a superframe rate of 48 kHz).

The PDM block supports high pass filtering of the input with a selectable cut-off frequency including 1, 60, 120, and 240 Hz. A register setting selects whether rising edge data or falling edge data is sampled first.

On a subordinate node, either BCLK or GPIO7 can clock PDM microphones. If GPIO7 is the clock, the BCLK frequency can be set to a different frequency using the I<sup>2</sup>S/TDM registers. In this case, GPIO7 is the PDM clock (PDMCLK) capturing PDM input on SIO0/SIO1. The clock rate from PDMCLK is 64× the SYNC frequency. BCLK and GPIO7 can also work concurrently to clock PDM microphones at the same frequency and phase alignment, but with opposite polarity.

On a main node, BCLK is always an input, so the clock to PDM microphones attached to a main node typically come from GPIO7. It is possible to use BCLK to drive the PDM clock inputs on a main node, but this restricts the possible TDM settings because BCLK is required to fall within the specification in Table 8.

## DATA SLOT EXCHANGE BETWEEN SUBORDINATE NODES

On the DTX pins of the I<sup>2</sup>S/TDM interface, subordinate transceivers can selectively output upstream data and downstream data that originates from other nodes without the need for data slots routed through the main node. Similarly, RX data channels from an I<sup>2</sup>S/TDM frame can become upstream and/or downstream slots on the A<sup>2</sup>B bus and can be received by any node.

#### I<sup>2</sup>S TX/RX CROSSBAR

The I<sup>2</sup>S crossbar provides flexible mapping between channels in the I<sup>2</sup>S/TDM interface and slots on the A<sup>2</sup>B bus.

When a node receives data over the  $A^2B$  bus and sends it to the  $I^2S/TDM$  interface, by default, there is a one-to-one mapping. For example, the first received slot is mapped to the first channel on the  $I^2S/TDM$  interface, and so on. Using the  $I^2S/TX$  crossbar, the channels on the  $I^2S/TDM$  interface can be reordered to map to an  $A^2B$  bus slot for each TDM channel.

Similarly, when a node receives data from the I<sup>2</sup>S/TDM interface and sends it over the A<sup>2</sup>B bus, by default, all the received I<sup>2</sup>S/TDM channels (defined in the A2B\_SLOT registers) are mapped one-to-one on the A<sup>2</sup>B bus. Using the I<sup>2</sup>S RX crossbar, the TDM channels can be individually selected to send data over A<sup>2</sup>B bus slots. For example, only TDM channels marked as valid are put onto the A<sup>2</sup>B bus and channels not in use are masked. See the *AD2437A<sup>2</sup>B Transceiver Technical Reference* for details.

#### **SERIAL PERIPHERAL INTERFACE (SPI)**

The SPI interface in the transceiver has the following features:

- Master or slave configurable

- Supports up to 3 slave-select outputs

- Up to 12.288 MHz operation

- Programmable clock phase (CPHA) and polarity (CPOL)

- · Subordinate transceiver register access

- · Local register access

SPI transactions take place between SPI ports of connected transceivers or between the SPI port and the I<sup>2</sup>C port of connected transceivers over the A<sup>2</sup>B bus. The transceiver provides the ability for SPI communication to occur over the A<sup>2</sup>B bus between multiple nodes in a system. The SPI interface is enabled by default and the transceiver is configured as an SPI slave. To use the alternative pin functionality, the SPI interface must be disabled by writing the value 0x02 to the A2B SPICFG register.

#### **SPI Over Distance**

An SPI tunnel is an extension to the A<sup>2</sup>B protocol where SPI control and data are exchanged between A<sup>2</sup>B nodes using dedicated slots on the A<sup>2</sup>B bus. SPI tunnels are configured and allocated by the host. SPI over distance supports the following features:

- Full-duplex read/writes between master and slave

- Up to 256 bytes of pipelined reads

- Extended full-duplex mode with pipelined reads for more than 256 bytes of data

- · Atomic SPI transfer

- Bulk SPI to SPI writes

- Extended bulk SPI writes

#### **PULSE WIDTH MODULATION (PWM) INTERFACE**

The PWM interface has the following features:

- Support for LED lighting control. The PWM output sends the clock at a fixed frequency and modulates the duty cycle (high/low time) for brighter or dimmer lights.

- Support for 3 PWM outputs and 1 output enable (OE) master dimmer. Each output rises on a different phase to limit instantaneous current draw.

- Two PWM frequency generators that can be programmed to frequencies 192 kHz, 96 kHz, 48 kHz, 24 kHz, 12 kHz, 3 kHz, 1.5 kHz, 750 Hz, 375 Hz, or 187.5 Hz.

- Supports independent blink rates of 0, 0.25, 0.5, 0.75, and 1.0 seconds (blink period) for PWM and OE channels with a blink duty cycle fixed at 50%.

The PWM block also supports a frequency hopping scheme. The PWM frequency hopper randomly selects frequencies from 187.5 Hz to 3 kHz to spread the PWM emissions over a range of frequencies.

The PWM outputs are shared with the SPI pins. Disable SPI functionality when PWM channels are enabled.

#### **GPIO OVER DISTANCE**

The transceiver supports general-purpose input/output (GPIO) communication over the A<sup>2</sup>B bus between multiple nodes without host intervention after initial programming. The host is required only for initial setup of the GPIO bus ports. I/O pins of different nodes can be logically OR or AND gate combined.

#### **MAILBOXES**

The transceiver supports interrupt driven, bidirectional message exchange between I<sup>2</sup>C/SPI controller devices (microcontrollers) at different subordinate nodes and the host connected to the main node transceiver using two dedicated mailboxes per subordinate node. The mailboxes can be used to customize handshaking among numerous nodes in a system to coordinate system events, such as synchronizing audio.

#### **LINE DIAGNOSTICS**

The line diagnostic block of the transceiver with XLR/DMX and CAT cables can detect mainly two types of fault conditions occurring on the A<sup>2</sup>B bus. These include:

- Open wire fault (A<sup>2</sup>B cable between nodes is disconnected or a node drops from the A<sup>2</sup>B bus)

- · Overcurrent condition

And, the line diagnostic block of the transceiver with a single-pair wire can detect, isolate, and indicate the following type of cable line faults occurring on the  $A^2B$  bus:

- · Positive terminal of cable shorted to VBAT

- · Positive terminal of cable shorted to ground

- Negative terminal of cable shorted to VBAT

- Negative terminal of cable shorted to ground

- Positive terminal of cable shorted to the negative terminal of the cable

- Open wire fault (A<sup>2</sup>B cable between the node is disconnected or the node drops from the A<sup>2</sup>B bus)

- Wrong port (adjacent A<sup>2</sup>B nodes are not connected to the correct A<sup>2</sup>B ports)

- Reverse wires (positive terminal of the cable at one node is connected to the negative terminal of the next node and conversely)

- Defective node (node is not responding)

These line faults are detected during and after discovery in the system run time. When a fault is detected during discovery, the switches that enable the bias current to the next-in-line node are disconnected automatically. The main node indicates the fault condition to the host controller via the interrupt (IRQ) pin. See the  $AD2437 \ A^2B \ Transceiver \ Technical \ Reference$  for details.

#### **CLOCK SUSTAIN STATE**

In the clock sustain state, audio signals of locally powered subordinate nodes are attenuated in the event of lost bus communication. When the bus loses communication and a reliable clock cannot be recovered by the subordinate node, the subordinate node transceiver enters the sustain state and, if enabled, signals this event on a GPIO pin.

In the clock sustain state, the phase-locked loop (PLL) of the subordinate transceiver continues to run for 1024 SYNC periods, while gradually attenuating the negative values to zero and the positive values to  $-109~\mathrm{dB}$  on the enabled I²S SIOn data pins. After the 1024 SYNC periods, the subordinate node transceiver resets and reenters the power-up state.

#### **DEDICATED INTERRUPT**

The transceiver features a dedicated interrupt pin (IRQ) to signal:

- Bit errors on the bus

- A line fault on the bus

- An interrupt from GP input pins

- Mailbox interrupts

- SPI and VMTR interrupts

Once the IRQ pin is asserted, the host controller checks the type and source of the interrupt. This pin can be configured active high or active low.

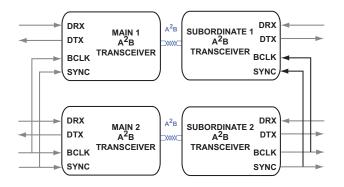

#### SUPPORT FOR PARALLEL A<sup>2</sup>B BUSES

This feature allows for parallel  $A^2B$  buses to exist between nodes in a system, thereby doubling the possible  $A^2B$  bandwidth between two nodes. The parallel  $A^2B$  main nodes are  $I^2S$  targets and share BCLK and SYNC. On the  $A^2B$  subordinate node, one of the  $A^2B$  transceivers is configured as an  $I^2S$  target and the other remains the  $I^2S$  controller (default behavior). BCLK and SYNC are shared between the two  $A^2B$  bus subordinate nodes and any attached peripherals.

Figure 5. Parallel A<sup>2</sup>B Bus Diagram

#### **VOLTAGE MONITOR (VMTR) ADC**

The voltage monitor ADC is a multichannel successive approximation ADC. It allows software to monitor the health of key voltages on A<sup>2</sup>B bus nodes. The VMTR:

- Selectively monitors VIN, VBUS, DVDD, TRXVDD, and IOVDD supply voltages and high/low side downstream

- Features an on-chip analog front end that conditions input to the ADC

- Uses an internal reference voltage

- Features an option to enable interrupts based on a maximum and minimum threshold

- Provides measured voltages and interrupts that are available in the next superframe

#### **POWER ON RESET**

The transceiver remains in reset state until all the supplies (VIN, IOVDD, DVDD, and TRXVDD) are stable. Refer to Operating Conditions for chip reset assertion and deassertion voltage specifications.

#### HARDWARE RESET

The transceiver features a dedicated active low hardware reset pin to reset the device. The reset pin can be deasserted after all the power domains are stable, thereby eliminating the need for power-up sequencing.

#### **LOW VOLTAGE INPUT (LVI) MODE**

The transceiver supports a low voltage input mode in which VIN can be 3.3V. In this mode, only VOUT1 is available. VOUT2 must be connected to the VIN pin. In LVI mode, there is no restriction on VBUS—any voltage within the respective specified range can be used.

#### **POWER CONFIGURATIONS**

The transceiver supports one power configuration:

CFG-4 — Supports up to 50 W depending on cable and connector configuration.

The operating power configuration of the transceiver can be identified by reading the A2B\_SWSTAT2.HPSW\_CFG\_ DET bit field. With the single-pair cable configuration, an external NMOS is used on both the high side and low side to deliver power along each of the data wire to the sub node. When using the XLR/DMX cables, only one NMOS is used at the high side to send power over both the data wires. When using the RJ45 connector, only one NMOS is used at the high side to deliver power to the sub node, but over the non-data wire pairs of the 8P8C modular connector.

Refer to Table 1, Product Features, for the bus power capabilities.

#### **STANDBY MODE**

Standby is a low power mode in which only a minimal (19-bit) SCF exists to keep all of the subordinate node transceivers synchronized. There is no downstream or upstream data traffic on the A<sup>2</sup>B bus and there is no SRF field. Standby mode can be exited and system traffic can be resumed without the need for rediscovery of the A<sup>2</sup>B node transceiver again. The GPIO settings retain their values while the transceiver is in standby mode.

#### **UNIQUE ID**

Each transceiver contains a 5-byte unique ID, which can be read from registers using software.

#### **SUPPORT FOR CABLING**

By default, the A<sup>2</sup>B transceiver is configured for use with crossover cables with single-pair cables. Straight-through, single-pair cables can also be used by swapping the connections of the dc bias inductors at the connector side. With RJ45 connectors, it is recommended to use straight-through CAT cables (T568 wiring standard) with the A<sup>2</sup>B transceivers. Straight-through CAT cabling is enabled using a register programming feature that allows polarity reversal on the B-side transceiver. With XLR/DMX cables, standard 3-pin XLR/DMX cables are used.

Contact Analog Devices for the latest reference schematic detailing implementation.

#### **ADDITIONAL INFORMATION**

Contact Analog Devices to request the  $AD2437 A^2B$  Transceiver Technical Reference, which provides detailed information about the AD2437 transceivers.

### **SPECIFICATIONS**

Specifications are subject to change without notice. For information about product specifications, contact your Analog Devices, Inc. representative.

#### **OPERATING CONDITIONS**

All specifications and characteristics apply across the entire operating conditions range unless otherwise noted.

| Parameter                            |                                              | Conditions                                 | Min                    | Nominal      | Max                    | Unit   |

|--------------------------------------|----------------------------------------------|--------------------------------------------|------------------------|--------------|------------------------|--------|

| Power Supp                           | olies                                        |                                            |                        |              |                        |        |

| $V_{DVDD}$                           | Digital Core Logic Supply Voltage            |                                            | 1.70                   | 1.90         | 1.98                   | V      |

| $V_{IOVDD}$                          | Digital Input/Output (I/O) Supply<br>Voltage | 3.3 V I/O<br>1.8 V I/O                     | 3.00<br>1.70           | 3.30<br>1.90 | 3.63<br>1.98           | V<br>V |

| $V_{PLLVDD}$                         | Phased-Locked Loops (PLL) Supply Voltage     |                                            | 1.70                   | 1.90         | 1.98                   | V      |

| $V_{TRXVDD}$                         | Transceiver Supply Voltage                   |                                            | 3.00                   | 3.30         | 3.45                   | V      |

| $V_{VIN}^{-1}$                       | Input Supply Voltage                         | Normal Mode, LVI Mode = 0                  | 3.7                    |              | 9.0                    | V      |

|                                      |                                              | LVI Mode = 1 (VIN and VOUT2 are connected) | 3.17                   |              | 3.45                   | V      |

| V <sub>VBUS</sub> <sup>2, 3, 4</sup> | Bus Bias Supply Voltage                      |                                            | 12.0                   |              | 24.0                   |        |

| VBUS Syste                           | m Operating Conditions                       |                                            |                        |              |                        |        |

| I <sub>VBUS_SYS_HP</sub>             | Bus Current                                  | $V_{VBUS} = 12 \text{ V to } 24 \text{ V}$ |                        |              | 2.1                    | Α      |

| Digital I/O                          |                                              |                                            |                        |              |                        |        |

| $V_{IH}^{5}$                         | High Level Input Voltage                     | $V_{IOVDD} = 1.98 \text{ V}$               | $0.7 \times V_{IOVDD}$ |              |                        | V      |

|                                      |                                              | $V_{IOVDD} = 3.63 \text{ V}$               | 2.2                    |              |                        | V      |

| $V_{IL}^{5}$                         | Low Level Input Voltage                      | $V_{IOVDD} = 1.70 \text{ V}$               |                        |              | $0.3 \times V_{IOVDD}$ | V      |

|                                      |                                              | $V_{IOVDD} = 3.00 \text{ V}$               |                        |              | 0.8                    | V      |

| $V_{IH\_I2C}^{6}$                    |                                              | V <sub>IOVDD</sub> = 3.63 V, 1.98 V        | $0.7 \times V_{IOVDD}$ |              |                        | V      |

| $V_{IL\_I2C}^{6}$                    |                                              | V <sub>IOVDD</sub> = 3.00 V, 1.70 V        |                        |              | $0.3 \times V_{IOVDD}$ | V      |

| CONSUMER                             | RGRADE                                       |                                            |                        |              |                        |        |

| T <sub>J</sub>                       | Junction Temperature                         |                                            | 0                      |              | 105                    | °C     |

| INDUSTRIA                            | L GRADE                                      |                                            |                        |              |                        |        |

| T <sub>J</sub>                       | Junction Temperature                         |                                            | -40                    |              | +105                   | °C     |

$<sup>^{1}</sup>$  V<sub>VIN</sub> must be  $\leq$  (V<sub>VBUS</sub> + 0.6 V).

<sup>&</sup>lt;sup>2</sup> Bus bias must be stable after discovery.

<sup>&</sup>lt;sup>3</sup> Refer to Line Power Switch section of the Electrical Characteristics table for the maximum bus current specification.

<sup>&</sup>lt;sup>4</sup> Ensure that the last subordinate node meets the minimum  $V_{VBUS}$  requirement. If line fault diagnostics are not required on the B-port of a last subordinate node operating in LVI mode, nominal  $V_{VBUS} = V_{IN} = 3.3 \text{ V}$ .

$<sup>^5</sup>$  Applies to ADR1, ADR2, SCK, MISO, MOSI, SIOn, BCLK, SYNC,  $\overline{RST},$  and GPIO7 pins.

<sup>&</sup>lt;sup>6</sup> Applies to SDA and SCL pins.

### **ELECTRICAL CHARACTERISTICS**

All specifications and characteristics apply across the entire operating conditions range unless otherwise noted.

| Parameter                |                                       | Conditions                                                           | Min   | Тур   | Max   | Unit |

|--------------------------|---------------------------------------|----------------------------------------------------------------------|-------|-------|-------|------|

| Supply Current           |                                       |                                                                      |       |       |       |      |

| Digital Core Logic Su    | upply Currents                        |                                                                      |       |       |       |      |

| I <sub>DVDD_OP</sub>     | V <sub>DVDD</sub> Operating Current   | $V_{DVDD} = 1.98 V$                                                  | 10.0  | 14.1  | 16.5  | mA   |

| I <sub>DVDD_RST</sub>    | V <sub>DVDD</sub> Reset Current       | $\overline{RST} = 0  V$                                              | 1.2   | 1.7   | 2.5   | mA   |

| I <sub>DVDD_STBY</sub>   | V <sub>DVDD</sub> Standby Current     | A2B_DATCTL = 0x80                                                    | 8.5   | 10.7  | 12.5  | mA   |

| PLL Supply Currents      |                                       |                                                                      |       |       |       |      |

| I <sub>PLLVDD_OP</sub>   | V <sub>PLLVDD</sub> Operating Current | $V_{PLLVDD} = 1.98 V$                                                | 0.45  | 0.68  | 0.92  | mA   |

| I <sub>PLLVDD_RST</sub>  | V <sub>PLLVDD</sub> Reset Current     | $\overline{RST} = 0  V$                                              | 0.02  | 0.06  | 0.12  | mA   |

| I <sub>PLLVDD_STBY</sub> | V <sub>PLLVDD</sub> Standby Current   | A2B_DATCTL = 0x80                                                    | 0.45  | 0.68  | 0.92  | mA   |

| Transceiver Supply C     |                                       |                                                                      |       |       |       |      |

| $I_{TRXVDD\_OP}$         | V <sub>TRXVDD</sub> Operating Current | TX enabled, RX disabled,                                             | 12.5  | 15.0  | 16.5  | mA   |

|                          |                                       | 100% duty cycle ( $I_{TXVDD}$ ), $V_{TRXVDD} = 3.45 \text{ V}$       |       |       |       |      |

|                          |                                       | TX disabled, RX enabled,                                             | 1.75  | 2.75  | 3.25  | mA   |

|                          |                                       | 100% duty cycle ( $I_{RXVDD}$ ), $V_{TRXVDD} = 3.45 \text{ V}$       |       |       |       |      |

| I <sub>TRXVDD_RST</sub>  | V <sub>TRXVDD</sub> Reset Current     | $\overline{RST} = 0  V$                                              | 1.7   | 2.8   | 4.0   | mA   |

| I <sub>TRXVDD_STBY</sub> | V <sub>TRXVDD</sub> Standby Current   | A2B_DATCTL = 0x80                                                    | 2.1   | 3.3   | 4.5   | mA   |

| IOVDD Supply Curre       | ents <sup>2</sup>                     |                                                                      |       |       |       |      |

| $I_{IOVDD\_RST}$         | V <sub>IOVDD</sub> Reset Current      | $\overline{RST} = 0  V$                                              | 65.0  | 92.0  | 115.0 | μΑ   |

| I <sub>IOVDD_STBY</sub>  | V <sub>IOVDD</sub> Standby Current    | A2B_DATCTL = 0x80                                                    | 75.0  | 99.0  | 125.0 | μΑ   |

| VBUS Supply Curren       | ts                                    |                                                                      |       |       |       |      |

| I <sub>VBUS_OP</sub>     | V <sub>VBUS</sub> Operating Current   | $V_{VBUS} = 24 V$                                                    | 0.68  | 0.79  | 0.90  | mA   |

| I <sub>VBUS_RST</sub>    | V <sub>VBUS</sub> Reset Current       | $\overline{RST} = 0  V,  VBUS = 24  V$                               | 0.68  | 0.79  | 0.90  | mA   |

| I <sub>VBUS_STBY</sub>   | V <sub>VBUS</sub> Standby Current     | A2B_DATCTL = 0x80, VBUS = 24 V                                       | 0.68  | 0.79  | 0.90  | mA   |

| VIN Supply Currents      |                                       |                                                                      |       |       |       |      |

| I <sub>VIN_OP</sub>      | V <sub>VIN</sub> Operating Current,   | $V_{VIN} = 9 V$ ,                                                    | 38.96 | 46.08 | 50.72 | mA   |

|                          | LVI Mode = 0                          | $I_{VOUT1} = 17.4 \text{ mA}^3,$                                     |       |       |       |      |

|                          |                                       | $I_{VOUT2} = 31.5 \text{ mA}^3$                                      |       |       |       |      |

|                          | V <sub>VIN</sub> Operating Current,   | $V_{VIN} = 3.45 V,$                                                  | 11.00 | 15.43 | 18.32 | mA   |

|                          | LVI Mode = 1                          | $I_{VOUT1} = 17.4 \text{ mA},$                                       |       |       |       |      |

|                          |                                       | $I_{VOUT2} = 0 \text{ mA}$                                           |       |       |       |      |

| $I_{VIN\_RST}$           | V <sub>VIN</sub> Reset Current,       | $\overline{RST} = 0 \text{ V},$                                      | 5.23  | 7.92  | 10.53 | mA   |

|                          | LVI Mode = 0                          | $V_{VIN} = 9 \text{ V}, V_{DVDD} = 1.98 \text{ V},$                  |       |       |       |      |

|                          |                                       | $V_{PLLVDD} = 1.98 \text{ V},$                                       |       |       |       |      |

|                          |                                       | $V_{TRXVDD} = 3.45 \text{ V},$ $V_{IOVDD} = 3.63 \text{ V}$          |       |       |       |      |

|                          | V <sub>VIN</sub> Reset Current,       | $\frac{V_{\text{OVDD}} - 3.03 \text{ V}}{\text{RST} = 0 \text{ V},}$ | 1.67  | 2.37  | 3.52  | mA   |

|                          | LVI Mode = 1                          | $V_{VIN} = Maximum V_{TRXVDD} = 3.45 V,$                             | 1.07  | 2.57  | ۵.۵∠  | 1117 |

|                          | LVI MOGE - 1                          | $V_{DVDD} = 1.98 \text{ V},$                                         |       |       |       |      |

|                          |                                       | V <sub>PLLVDD</sub> = 1.98 V,                                        |       |       |       |      |

|                          |                                       | V <sub>IOVDD</sub> = 3.63 V                                          |       |       |       |      |

| Parameter                       |                                    | Conditions                                                   | Min  | Тур  | Max              | Unit |

|---------------------------------|------------------------------------|--------------------------------------------------------------|------|------|------------------|------|

| Bus Voltage                     |                                    |                                                              |      |      |                  |      |

| Chip Reset Assertion            | Voltage Threshold <sup>4</sup>     |                                                              |      |      |                  |      |

| $V_{RST\_VIN}$                  |                                    | $V_{VIN}$ dropping, LVI Mode = 0, 1                          | 2.49 |      | 2.73             | ٧    |

| $V_{RST\_DVDD}$                 |                                    | V <sub>DVDD</sub> dropping                                   | 1.1  |      | 1.5              | ٧    |

| $V_{RST\_IOVDD}$                |                                    | V <sub>IOVDD</sub> dropping                                  | 1.0  |      | 1.5              | ٧    |

| $V_{RST\_TRXVDD}$               |                                    | $V_{TRXVDD}$ dropping, LVI Mode = 0, 1                       | 2.2  |      | 2.8              | ٧    |

| Chip Reset Deasserti            | on Voltage Threshold <sup>5</sup>  |                                                              |      |      |                  |      |

| $V_{RSTN\_VIN}$                 |                                    | $V_{VIN}$ rising, LVI Mode = 0, 1                            | 2.76 |      | 3.10             | ٧    |

| $V_{RSTN\_DVDD}$                |                                    | V <sub>DVDD</sub> rising                                     | 1.50 |      | 1.65             | ٧    |

| $V_{RSTN\_IOVDD}$               |                                    | V <sub>IOVDD</sub> rising                                    | 1.20 |      | 1.62             | ٧    |

| $V_{RSTN\_TRXVDD}$              |                                    | $V_{TRXVDD}$ rising, LVI Mode = 0, 1                         | 2.53 |      | 3.05             | ٧    |

| Voltage Regulator (             | VREG1, VREG2)                      |                                                              |      |      |                  |      |

| $V_{VOUT1}$                     | V <sub>REG1</sub> Output Voltage   |                                                              | 1.80 | 1.90 | 1.98             | ٧    |

| $V_{VOUT2}$                     | V <sub>REG2</sub> Output Voltage   |                                                              | 3.15 | 3.30 | 3.45             | ٧    |

| I <sub>VOUT1</sub> <sup>6</sup> | V <sub>REG1</sub> Output Current   |                                                              |      |      | 100 <sup>7</sup> | mA   |

| I <sub>VOUT2</sub> <sup>6</sup> | V <sub>REG2</sub> Output Current   |                                                              |      |      | 100 <sup>7</sup> | mA   |

| $I_{VOUT1} + I_{VOUT2}$         |                                    |                                                              |      |      | 130 <sup>7</sup> | mA   |

| $\Delta V_{OUT1\_LNREG}$        | V <sub>VOUT1</sub> Line Regulation | $V_{VIN} = 3.13 \text{ V to } 3.47 \text{ V},$               |      |      | 5                | mV   |

|                                 |                                    | $I_{VOUT1} = 100 \text{ mA, LVI\_MODE} = 1$                  |      |      |                  |      |

| $\Delta V_{\text{OUT1\_LNREG}}$ | V <sub>VOUT1</sub> Line Regulation | $V_{VIN} = 3.7 V \text{ to } 4.9 V,$                         |      |      | 5                | mV   |

|                                 |                                    | $I_{VOUT1} = 100 \text{ mA}$                                 |      |      |                  |      |

| $\Delta V_{\text{OUT2\_LNREG}}$ | V <sub>VOUT2</sub> Line Regulation | $V_{VIN} = 3.7 \text{ V to } 6.3 \text{ V,}$                 |      |      | 15               | mV   |

|                                 |                                    | $I_{VOUT2} = 100 \text{ mA}$                                 |      |      |                  |      |

| $\Delta V_{OUT1\_LNREG}$        | V <sub>VOUT1</sub> Line Regulation | $V_{VIN} = 3.7 \text{ V to 9 V},$                            |      |      | 6                | mV   |

|                                 |                                    | I <sub>VOUT1</sub> = 40 mA                                   |      |      | _                | l    |

| $\Delta V_{OUT2\_LNREG}$        | V <sub>VOUT2</sub> Line Regulation | $V_{VIN} = 3.7 \text{ V to 9 V},$                            |      |      | 8                | mV   |

| A\/                             | V Load Regulation                  | $I_{VOUT2} = 50 \text{ mA}$ $V_{VIN} = 3.13 \text{ V},$      |      |      | 33               | m)/  |

| $\Delta V_{OUT1\_LDREG}$        | V <sub>VOUT1</sub> Load Regulation | $I_{VOUT1} = 1 \text{ mA to } 100 \text{ mA, LVI\_MODE} = 1$ |      |      | 33               | mV   |

| $\Delta V_{OUT1\_LDREG}$        | V <sub>VOUT1</sub> Load Regulation | $V_{VIN} = 3.7 \text{ V},$                                   |      |      | 15               | mV   |

| △VOUT1_LDREG                    | V <sub>VOUT1</sub> Load Regulation | $I_{VOUT1} = 1 \text{ mA to } 40 \text{ mA}$                 |      |      | 13               | IIIV |

| $\Delta V_{OUT2\_LDREG}$        | V <sub>VOUT2</sub> Load Regulation | V <sub>VIN</sub> = 3.7 V,                                    |      |      | 25               | mV   |

|                                 | 1 V0012 2000 110g diation          | $I_{VOUT2} = 1 \text{ mA to } 50 \text{ mA}$                 |      |      |                  |      |

| $\Delta V_{OUT1\_LDREG}$        | V <sub>VOUT1</sub> Load Regulation | $V_{VIN} = 3.7 \text{ V},$                                   |      |      | 33               | mV   |

| OUT_EDILEG                      | , com                              | I <sub>VOUT1</sub> = 1mA to 100 mA                           |      |      |                  |      |

| $\Delta V_{\text{OUT2\_LDREG}}$ | V <sub>VOUT2</sub> Load Regulation | $V_{VIN} = 3.7 V$ ,                                          |      |      | 42               | mV   |

|                                 | -                                  | $I_{VOUT2} = 1 \text{mA to } 100 \text{ mA}$                 |      |      |                  |      |

| $C_{Load1}$                     | V <sub>REG1</sub> Load Capacitance |                                                              | 1.8  |      | 26               | μF   |

| $C_{Load2}$                     | V <sub>REG2</sub> Load Capacitance |                                                              | 3.9  |      | 26               | μF   |

| Parameter                                         |                                           | Conditions                                            | Min  | Тур  | Max  | Unit |

|---------------------------------------------------|-------------------------------------------|-------------------------------------------------------|------|------|------|------|

| Digital I/O                                       |                                           |                                                       |      |      |      |      |

| I <sub>IH</sub> <sup>8</sup>                      | Input Leakage, High                       | $V_{IOVDD} = 3.63 \text{ V}, V_{IN} = 3.63 \text{ V}$ |      |      | 10.0 | μΑ   |

| I <sub>IL</sub> <sup>8</sup>                      | Input Leakage, Low                        | $V_{IOVDD} = 3.63 \text{ V}, V_{IN} = 0 \text{ V}$    |      |      | 10.0 | μΑ   |

| V <sub>OH1.9</sub> <sup>8</sup>                   | High Level Output Voltage                 | $V_{IOVDD} = 1.70 \text{ V}, I_{OH} = 1 \text{ mA}$   | 1.35 |      |      | ٧    |

| V <sub>OH3.3</sub> <sup>8</sup>                   | High Level Output Voltage                 | $V_{IOVDD} = 3.00 \text{ V, } I_{OH} = 1 \text{ mA}$  | 2.40 |      |      | ٧    |

| $V_{OL}^{8}$                                      | Low Level Output Voltage                  | $V_{IOVDD} = 3.00 \text{ V}, I_{OL} = 1 \text{ mA}$   |      |      | 0.40 | ٧    |

| $V_{OL}^{8}$                                      | Low Level Output Voltage                  | $V_{IOVDD} = 1.70 \text{ V}, I_{OL} = 1 \text{ mA}$   |      |      | 0.40 | ٧    |

| $V_{OL\_I2C}^{9}$                                 | I <sup>2</sup> C Low Level Output Voltage | $V_{IOVDD} = 3.00 \text{ V}, I_{OL} = 3.0 \text{ mA}$ |      |      | 0.40 | ٧    |

| $V_{OL\_I2C}^{10}$                                | I <sup>2</sup> C Low Level Output Voltage | $V_{IOVDD} = 1.70 \text{ V}, I_{OL} = 1.0 \text{ mA}$ |      |      | 0.40 | ٧    |

| $C_PD$                                            | Pin Capacitance                           |                                                       |      |      | 5    | рF   |

| Line Power Switch                                 |                                           |                                                       |      |      |      |      |

| Internal VSENSEP Currents                         |                                           |                                                       |      |      |      |      |

| I <sub>VSENSEP</sub>                              | $V_{VSENSEP}$                             | $V_{VSENSEP} = V_{VBUS} = 24 \text{ V}$               |      |      | 400  | μΑ   |

| Internal ISENSEP Current                          |                                           |                                                       |      |      |      |      |

| I <sub>ISENSEP</sub>                              | V <sub>ISENSEP</sub>                      | $V_{VBUS} - V_{ISENSEP} = 100 \text{ mV}$             | 13.0 | 18.0 | 22.5 | μΑ   |

| SWN Leakage Current                               |                                           |                                                       |      |      |      |      |

| $I_{SWN\_LKG}$                                    | $V_{SWN\_LGKG}$                           | $V_{SWN} = 3.3 \text{ V}$                             |      |      | 3.2  | mA   |

| Current Thresholds                                |                                           |                                                       |      |      |      |      |

| $\Delta V_{HSNS\_LM} = V_{VBUS} - V_{ISENSEP}$    | High Side Current Limit Threshold         | ON State                                              | 100  | 150  | 182  | mV   |

| $\Delta V_{LSNS\_CF} = V_{ISENSEN} - V_{VSENSEN}$ | Low Side Current Fault Threshold          | ON State, V <sub>VSENSEN</sub> = 0.1 V                | 115  | 150  | 160  | mV   |

| External High Side NFET Gat                       | e Drive                                   |                                                       |      |      |      |      |

| $V_{SWP} - V_{VSENSEP}$                           |                                           | ON State, $V_{VSENSEP} = V_{VBUS}$                    | 4.5  | 4.7  | 5.1  | ٧    |

| SWP Slew Rate With Soft Sta                       | rt Enabled <sup>11</sup>                  |                                                       |      |      |      |      |

| $\Delta V_{SWP}/dt$                               |                                           | $CAP_DLY = 0$ , $V_{VBUS} = 7 V$                      | 1.9  | 2.2  | 2.5  | V/ms |

|                                                   |                                           | $CAP_DLY = 1$ , $V_{VBUS} = 7$ V                      | 9.5  | 11.6 | 12.8 | V/ms |

| External Low Side NFET Gate                       | e Drive                                   |                                                       |      |      |      |      |

| $V_{\sf SWN}$                                     |                                           | ON State, 220k pull-down to GND on SWN                | 4.1  |      |      | V    |

<sup>&</sup>lt;sup>1</sup> Main node and last subordinate node only consume half the transceiver current because only one of the two transceivers is used.

$<sup>^2</sup>$ I<sub>IOVDD</sub> operational current depends on switching currents on digital I/O pins such as BCLK, SYNC, ADR1, ADR2, SCK, MISO, MOSI, SIOn, and GPIO7. Customers can calculate the dynamic current using the formula: Output Dynamic Current =  $(C_{PD} + C_L) \times V_{IOVDD} \times S$ witching Frequency.

$<sup>^3</sup>$  I<sub>VOUT1</sub> = Max I<sub>DVDD</sub> + Max I<sub>PLIVDD</sub> and I<sub>VOUT2</sub> = Max I<sub>TRXVDD</sub> + Typ I<sub>IOVDD</sub>. The typical IOVDD current for I<sup>2</sup>S at 25 MHz is 15 mA, with a standard capacitive load of 6 pF (average) on all pins.

<sup>&</sup>lt;sup>4</sup> The chip reset signal is asserted when any supply voltage drops below the reset assertion threshold.

<sup>&</sup>lt;sup>5</sup>The transceiver comes out of reset when all the power supply and the reset pin voltages are above the reset deassertion threshold.

$<sup>^6</sup>$   $I_{VOUT1}$  +  $I_{VOUT2}$  < 30 mA when  $V_{IN}$  is bus powered by a current limiting device like the ADP2360 from the upstream node.

<sup>&</sup>lt;sup>7</sup> Refer to the VREG Safe Operating Area section.

<sup>&</sup>lt;sup>8</sup> Applies to ADR1, ADR2, SCK, MISO, MOSI, SIOn, BCLK, SYNC, IRQ, and GPIO7 pins.

<sup>&</sup>lt;sup>9</sup> Applies to SDA and SCL pins in standard mode, fast mode, and fast mode plus.

<sup>&</sup>lt;sup>10</sup>Applies to SDA and SCL pins in fast mode and fast mode plus.

<sup>&</sup>lt;sup>11</sup>Applies when not in current limit with large capacitor bus loading.

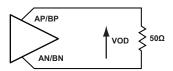

Table 3. LVDS Input/Output Characteristics

| Parameter  |                                       | Conditions     | Min   | Тур | Max   | Unit |

|------------|---------------------------------------|----------------|-------|-----|-------|------|

| LVDS       |                                       |                |       |     |       |      |

| $ V_{OD} $ | Differential Output Voltage Magnitude | See Figure 27. | 0.455 |     | 0.630 | V    |

| Receiver   |                                       |                |       |     |       |      |

| $V_{TH}$   | Differential Input Threshold Voltage  |                | -85   |     | +85   | mV   |

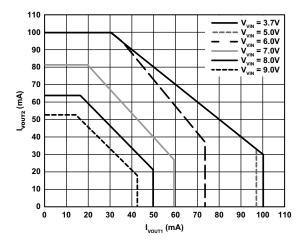

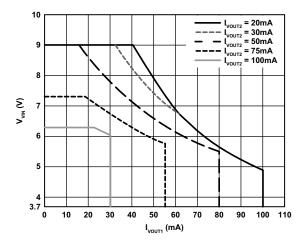

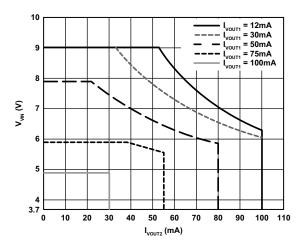

#### **VREG Safe Operating Area**

Figure 6 through Figure 8 show the safe operating area for VREG VOUT1 and VOUT2. These specifications are supported only when the  $V_{\rm IN}$  supply can provide sufficient input current. For instance,  $V_{\rm IN}$  on RJ45 bus-powered subordinate nodes is sourced from a current-limited supply. See footnote 6 in Electrical Characteristics.

Note that the safe operating area graphs are supported over the specified junction temperature  $(T_J)$  of the device. Perform thermal simulation and/or thermal measurement to meet the  $T_J$  specification.

Figure 6. VREG VOUT1 Safe Operating Area, LVI\_MODE = 0

Figure 7.  $VREG\ VOUT2\ Safe\ Operating\ Area,\ LVI\_MODE=0$

Figure 8. VREG VOUT1 and VOUT2 Safe Operating Area, LVI\_MODE = 0

### **VMTR ADC SPECIFICATIONS**

All specifications and characteristics apply across the entire operating conditions range unless otherwise noted.

| Parameter                                                       | Conditions                         | Min   | Тур | Max  | Unit |

|-----------------------------------------------------------------|------------------------------------|-------|-----|------|------|

| VMTR ACTIVE CURRENT                                             |                                    |       |     |      |      |

| I <sub>DD_VMTR_</sub> ACTIVE                                    |                                    | 35    |     | 58   | μΑ   |

| Resolution                                                      |                                    |       | 8   |      | Bits |

| DC ACCURACY                                                     |                                    |       |     |      |      |

| Applicable for A2B_VMTR_VLTG0 to<br>A2B_VMTR_VLTG4 <sup>1</sup> |                                    |       |     |      |      |

| Integral Nonlinearity (INL)                                     |                                    | -0.82 |     | 0.84 | LSB  |

| Differential Nonlinearity (DNL)                                 |                                    | -0.70 |     | 0.83 | LSB  |

| Offset Error                                                    |                                    | -2    |     | 2    | LSB  |

| Gain Error                                                      |                                    | -4    |     | 4    | LSB  |

| Applicable to A2B_VMTR_VLTG5 <sup>1</sup>                       |                                    |       |     |      |      |

| Integral Nonlinearity (INL)                                     | A2B_VMTR_VLTG5 range = 0 to 150 mV | -0.90 |     | 0.91 | LSB  |

| Differential Nonlinearity (DNL)                                 | A2B_VMTR_VLTG5 range = 0 to 150 mV | -0.77 |     | 0.77 | LSB  |

| Offset Error                                                    | A2B_VMTR_VLTG5 range = 0 to 150 mV | -2    |     | 2    | LSB  |

| Gain Error                                                      | A2B_VMTR_VLTG5 range = 0 to 150 mV | -5    |     | 5    | LSB  |

| Applicable to A2B_VMTR_VLTG6 <sup>1</sup>                       |                                    |       |     |      |      |

| Integral Nonlinearity (INL)                                     | A2B_VMTR_VLTG6 range = 0 to 150 mV | -0.89 |     | 0.84 | LSB  |

| Differential Nonlinearity (DNL)                                 | A2B_VMTR_VLTG6 range = 0 to 150 mV | -0.73 |     | 0.78 | LSB  |

| Offset Error                                                    | A2B_VMTR_VLTG6 range = 0 to 150 mV | -2    |     | 2    | LSB  |

| Gain Error                                                      | A2B_VMTR_VLTG5 range = 0 to 150 mV | -4    |     | 4    | LSB  |

$<sup>^1</sup>$  See the Voltage Monitor ADC section in the AD2437  $A^2B$  Transceiver Technical Reference for details.

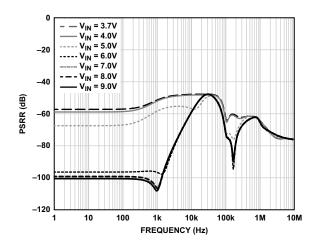

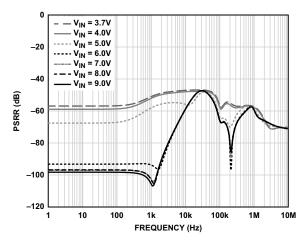

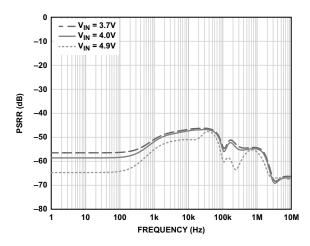

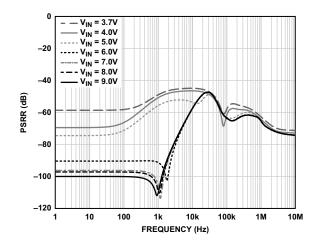

#### **POWER SUPPLY REJECTION RATIO (PSRR)**

Typical PSRR at  $T_I = 40$ °C.

Figure 9. VOUT1 PSRR,  $I_{VOUT1}$  = 10 mA,  $C_{LOAD}$  = 4.7  $\mu$ F  $\parallel$  0.1  $\mu$ F

Figure 10. VOUT1 PSRR,  $I_{VOUT1}$  = 40 mA,  $C_{LOAD}$  = 4.7  $\mu$ F  $\parallel$  0.1  $\mu$ F

Figure 11. VOUT1 PSRR,  $I_{VOUT1} = 100$  mA,  $C_{LOAD} = 4.7 \mu$ F  $\parallel$  0.1  $\mu$ F

Figure 12. VOUT2 PSRR,  $I_{VOUT2}$  = 10 mA,  $C_{LOAD}$  = 6.8  $\mu$ F  $\parallel$  0.1  $\mu$ F

Figure 13. VOUT2 PSRR,  $I_{VOUT2}$  = 50 mA,  $C_{LOAD}$  = 6.8  $\mu$ F  $\parallel$  0.1  $\mu$ F

Figure 14. VOUT2 PSRR,  $I_{VOUT2}$  = 100 mA,  $C_{LOAD}$  = 6.8  $\mu$ F  $\parallel$  0.1  $\mu$ F

#### **TIMING SPECIFICATIONS**

All specifications and characteristics apply across the entire operating conditions range unless otherwise noted.

#### **Clock and Reset Timing**

Table 4 and Figure 15 describe clock and reset operations.

Table 4. Clock and Reset Timing

| Parame                              | Parameter                                                                |      | Тур                      | Max               | Unit               |

|-------------------------------------|--------------------------------------------------------------------------|------|--------------------------|-------------------|--------------------|

| Timing F                            | Requirements                                                             |      |                          |                   |                    |

| $f_{\text{SYNCM}}$                  | SYNC Pin Input Frequency Continuous Clock                                |      |                          |                   |                    |

|                                     | 44.1 kHz SYNC Input                                                      | 43.7 | 44.1                     | 44.5              | kHz                |

|                                     | 48 kHz SYNC Input                                                        | 47.5 | 48.0                     | 48.5              | kHz                |

| t <sub>SYNCIJ1</sub>                | SYNC Pin Input Jitter RMS TIE <sup>1</sup>                               |      |                          | 1.0               | ns                 |

| t <sub>MCLKIJ1</sub>                | Main Node Bit Clock Input Jitter RMS TIE <sup>1</sup>                    |      |                          | 1.0               | ns                 |

| t <sub>ACCESS</sub>                 | Device Access Time After Reset <sup>2</sup>                              | 1.5  |                          |                   | ms                 |

| $t_{RST}$                           | Reset Width <sup>3</sup>                                                 | 10   |                          |                   | μs                 |

| t <sub>DNSYNCR</sub> <sup>4</sup>   | Delay From First Missed SYNC Input to Reset (A <sup>2</sup> B Main Node) | 31   | 32                       | 33                | t <sub>SYNCM</sub> |

| t <sub>DNSCFR</sub> <sup>4, 5</sup> | Delay From First Missed SCF to Reset (A <sup>2</sup> B Subordinate Node) | 31   | 32                       | 33                | t <sub>SYNCM</sub> |

| $t_{\text{PLK}}$                    | PLL Lock Time                                                            |      | 7.5                      |                   | ms                 |

| $f_{SYSBCLK}$                       | A <sup>2</sup> B Bus Clock                                               |      | $1024 \times f_{SYNCM}$  |                   | kHz                |

| t <sub>SYSBCLK</sub>                | Bit-Period of A <sup>2</sup> B Bus Clock                                 |      | $1/(1024 \times f_{SY})$ | <sub>'NCM</sub> ) | ns                 |

$<sup>^{1}</sup>$  Maximum allowed jitter which does not degrade THD + N performance in the last subordinate node.

<sup>&</sup>lt;sup>5</sup> Add 1024 if SUSTAIN = 1.

Figure 15. Reset Timing

#### I<sup>2</sup>C Port Timing

The transceiver conforms to the I<sup>2</sup>C specification v2.1.

$<sup>^2</sup>$ The time it takes to access local registers via  $^2$ C/SPI once the reset pin is deasserted and the power supplies are stable.

$<sup>^3</sup>$  Valid only when all the power supplies are stable. See Figure 15 for  $t_{\text{RST}}.$

<sup>&</sup>lt;sup>4</sup>Only consecutive missed SYNC or SCF transitions for the specified duration result in a reset.

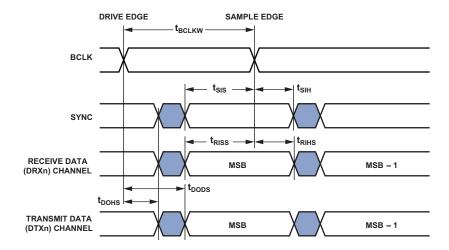

#### I<sup>2</sup>S/TDM Port Timing

Table 5, Table 6, Figure 16, and Figure 17 describe I<sup>2</sup>S/TDM port operations. Note the following:

- The SIO0-SIO4 data pins on the I<sup>2</sup>S/TDM port can be configured for up to two PDM streams and up to five I<sup>2</sup>S/TDM streams, with a maximum of four I<sup>2</sup>S/TDM streams in the same direction. DTXn includes the DTX0, DTX1, DTX2, and DTX3 pins; and DRXn includes DRX0, DRX1, DRX2, and DRX3 in Table 5.

- The I<sup>2</sup>S/TDM target timing applies to the A<sup>2</sup>B main transceiver and the A<sup>2</sup>B subordinate transceiver operating in parallel bus mode.

- The I<sup>2</sup>S/TDM controller timing applies to the A<sup>2</sup>B subordinate transceiver.

Table 5. I<sup>2</sup>S/TDM Port—Controller Timing

|                                 |                                          | IOV | /DD = 1.8 V | IOV | /DD = 3.3 V |                    |

|---------------------------------|------------------------------------------|-----|-------------|-----|-------------|--------------------|

| Paramete                        | er                                       | Min | Max         | Min | Max         | Unit               |

| Timing Re                       | quirements                               |     |             |     |             |                    |

| $t_{RISM}$                      | DRXn Input Setup Before BCLK Sample Edge | 1.0 |             | 1.5 |             | ns                 |

| $t_{\text{RIHM}}$               | DRXn Input Hold After BCLK Sample Edge   | 5.5 |             | 2.0 |             | ns                 |

| Switching                       | Characteristics                          |     |             |     |             |                    |

| $f_{\text{BCLKM}}$              | BCLK Output Frequency <sup>1</sup>       |     | 25.0        |     | 50.0        | MHz                |

| $t_{\text{BCLKMOJ}}$            | BCLK Output Jitter (RMS Cycle to Cycle)  |     |             |     |             |                    |

|                                 | at $f_{BCLKSM} = 12.288 \text{ MHz}$     |     | 100         |     | 100         | ps                 |

|                                 | at $f_{BCLKSM} = 24.576 \text{ MHz}$     |     | 100         |     | 100         | ps                 |

| $t_{\text{SOL}}/t_{\text{SOH}}$ | Transmit or Receive BCLK Duty Cycle      | 49% | 51%         | 49% | 51%         | t <sub>BCLKM</sub> |

| $t_{\text{SOJ}}$                | SYNC Output Jitter (RMS Cycle to Cycle)  |     |             |     |             |                    |

|                                 | Normal Mode 48 kHz                       |     | 2.25        |     | 2.25        | ns                 |

|                                 | Increased Data Rate 2× SYNC              |     | 1.25        |     | 1.25        | ns                 |

|                                 | Increased Data Rate 4× SYNC              |     | 1.00        |     | 1.00        | ns                 |

| $t_{SOD}$                       | SYNC Output Delay After BCLK Drive Edge  |     | 9.75        |     | 9.75        | ns                 |

| $t_{SOHD}$                      | SYNC Output Hold After BCLK Drive Edge   | 3.0 |             | 4.5 |             | ns                 |

| $t_{DODM}$                      | DTXn Output Delay After BCLK Drive Edge  |     | 10.25       |     | 9.75        | ns                 |

| $t_{DOHM}$                      | DTXn Output Hold After BCLK Drive Edge   | 5.5 |             | 6.0 |             | ns                 |

<sup>&</sup>lt;sup>1</sup> When V<sub>IOVDD</sub> = 3.3 V, the setup and hold timing at the 50 MHz maximum bit clock rate can be violated when interfacing with other I<sup>2</sup>S devices. The timing violations are observed when the subordinate transceiver I<sup>2</sup>S/TDM port is receiving and the main transceiver I<sup>2</sup>S/TDM port is transmitting. In this case, the maximum BCLK frequency of 50 MHz cannot be achieved.

Figure 16. I<sup>2</sup>S/TDM Port—Controller Timing

Table 6. I<sup>2</sup>S/TDM Port—Target Timing

|                    |                                          | IOV  | DD = 1.8 V | IOV  | /DD = 3.3 V |      |

|--------------------|------------------------------------------|------|------------|------|-------------|------|

| Paramet            | ter                                      | Min  | Max        | Min  | Max         | Unit |

| Timing R           | equirements                              |      |            |      |             |      |

| t <sub>BCLKW</sub> | BCLK Width                               | 19.5 |            | 9.5  |             | ns   |

| t <sub>BCLKS</sub> | BCLK Period                              | 39.0 |            | 19.0 |             | ns   |

| $t_{SIS}$          | SYNC Input Setup Before BCLK Sample Edge | 2.25 |            | 2.25 |             | ns   |

| t <sub>SIH</sub>   | SYNC Input Hold After BCLK Sample Edge   | 2.0  |            | 2.5  |             | ns   |

| $t_{\text{RISS}}$  | DRXn Input Setup Before BCLK Sample Edge | 2.0  |            | 1.5  |             | ns   |

| $t_{\text{RIHS}}$  | DRXn Input Hold After BCLK Sample Edge   | 1.5  |            | 0.5  |             | ns   |

| Switchin           | g Characteristics                        |      |            |      |             |      |

| $t_{DODS}$         | DTXn Output Delay After BCLK Drive Edge  |      | 16.5       |      | 12.0        | ns   |

| $t_{\text{DOHS}}$  | DTXn Output Hold After BCLK Drive Edge   | 3.0  |            | 3.0  |             | ns   |

Figure 17. I<sup>2</sup>S/TDM Port—Target Timing

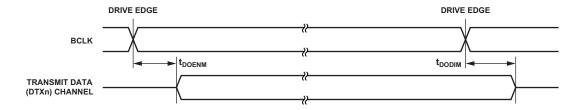

Table 7. I<sup>2</sup>S Target (A<sup>2</sup>B Main Node) DTXn Enable and Three-State Timing

|                                        |                                               |     | IOVDD = 1.8 V |     | IOVDD = 3.3 V |      |

|----------------------------------------|-----------------------------------------------|-----|---------------|-----|---------------|------|

| Paramet                                | ter                                           | Min | Max           | Min | Max           | Unit |

| Switching Characteristics <sup>1</sup> |                                               |     |               |     |               |      |

| t <sub>DOENM</sub>                     | DTXn Data Enable Delay After BCLK Drive Edge  | 5.0 |               | 4.0 |               | ns   |

| $t_{DODIM}$                            | DTXn Data Disable Delay After BCLK Drive Edge |     | 14.5          |     | 10.5          | ns   |

<sup>&</sup>lt;sup>1</sup> Refer to the A2B\_TXOFFSET register for three-state programming details.

Figure 18. 1<sup>2</sup>S Target (A<sup>2</sup>B Main Node) DTXn Enable and Three-State Timing

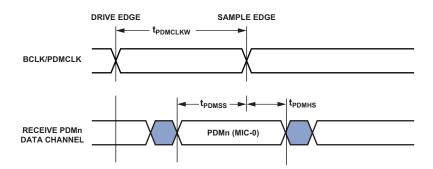

Table 8. Pulse Density Modulation (PDM) Microphone Input Timing

|                       |                                                            | IOV   | /DD = 1.8 V | IOV   | DD = 3.3 V |      |

|-----------------------|------------------------------------------------------------|-------|-------------|-------|------------|------|

| Parameter             |                                                            | Min   | Max         | Min   | Max        | Unit |

| Timing Re             | equirements                                                |       |             |       |            |      |

| t <sub>PDMSS</sub>    | PDMn Input Setup Before BCLK/PDMCLK                        | 17.5  |             | 12.0  |            | ns   |

| t <sub>PDMHS</sub>    | PDMn Input Hold After BCLK/PDMCLK                          | 0     |             | 0     |            | ns   |

| Switching             | Characteristics                                            |       |             |       |            |      |

| $f_{PDMCLK}$          | BCLK/PDMCLK Output Frequency at f <sub>SYNC</sub> = 48 kHz | 3.040 | 3.104       | 3.040 | 3.104      | MHz  |

| t <sub>PDMCLKOJ</sub> | BCLK/PDMCLK Output Jitter RMS Cycle to Cycle               |       | 150         |       | 150        | ps   |

| t <sub>PDMCLKW</sub>  | BCLK/PDMCLK Output Pulse Width                             | 161.0 |             | 162.5 |            | ns   |

Figure 19. PDM Timing

### **GPIO** and **CLKOUT** Timing

Table 9 describes GPIO and CLKOUT operations.

Table 9. GPIO and CLKOUT Timing

| Paramete               | er                                    | Min                      | Тур | Max  | Unit |

|------------------------|---------------------------------------|--------------------------|-----|------|------|

| Timing Red             | quirement                             |                          |     |      |      |

| $t_{\text{GIPW}}$      | GPIO Input Pulse Width                | t <sub>SYSBCLK</sub> + 5 |     |      | ns   |

| Switching              | Characteristics                       |                          |     |      |      |

| $t_{GOPW}$             | GPIO Output Pulse Width               | t <sub>SYSBCLK</sub> – 1 |     |      | ns   |

| t <sub>CLKOUTJ</sub> 1 | CLKOUT Jitter RMS TIE for 48 kHz SYNC |                          |     |      |      |

|                        | at $f_{CLKOUT} = 12.288 \text{ MHz}$  |                          | 1.0 | 1.90 | ns   |

|                        | at $f_{CLKOUT} = 24.576 \text{ MHz}$  |                          | 1.0 | 1.95 | ns   |

<sup>&</sup>lt;sup>1</sup> Jitter measured at Subordinate Node 0.

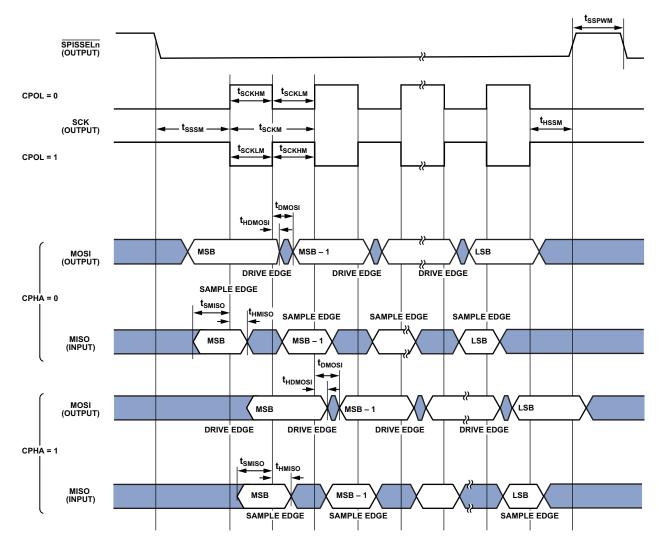

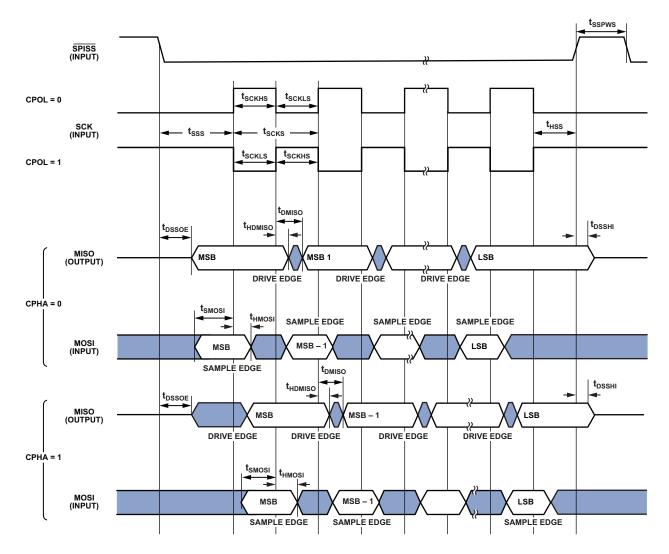

#### Serial Peripheral Interface (SPI) Port—Master Timing

Table 10 and Figure 20 describe serial peripheral interface (SPI) port master operations.

Table 10. Serial Peripheral Interface (SPI) Port—Master Timing

|                                 |                                                              | IOVI  | DD = 1.8 V | IOVI  | DD = 3.3 V |      |