| REV STATUS<br>OF PAGES    REV    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                | SIZE<br>A<br>REV | COD    | IDE IDE |       | o.<br>236 |   |            |     | G NO.<br>E 1 |      | <b>V</b><br>18 | <b>62</b> | /19  | 614 | 1      |        |        |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|------------------|--------|---------|-------|-----------|---|------------|-----|--------------|------|----------------|-----------|------|-----|--------|--------|--------|----|

| REV      Image: Checked BY YY MM DD      Image: Checked BY Phu H. Nguyen      Image: Phu H. Nguyen      I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19-                 | -07-24         |                  | Th     | nomas   |       |           |   |            | REF | ERE          |      |                |           |      |     |        | N      |        |    |

| REV    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Uriginal da<br>YY N |                |                  |        |         |       |           |   | MIC<br>CH/ | ROC | EL, L        | OW I | NOIS           | E, L      | OW I | POW |        | 24-E   | BIT,   |    |

| REV    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Original da         | ate of drawing |                  |        |         |       |           |   |            |     |              |      |                |           |      |     |        |        |        |    |

| REV    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I    I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PMIC N/A            |                | PREPARI          |        |         | Nguye | en        |   |            |     |              | COL  | UMB            | US, (     | оню  | 432 | 218-3  | 990    |        |    |

| REV    Image: Second s | OF PAGES            | S PA           |                  |        |         | 3     | 4         | 5 | 6          | 7   | 8            |      |                |           |      |     |        |        | 16     | 17 |

| REV    Image: Sector of the s | REV STAT            | rus Re         | EV               |        |         |       |           |   |            |     |              |      |                |           |      |     |        |        |        |    |

| REV    Image: Sector S |                     | 18             |                  |        |         |       |           |   |            |     |              |      |                |           |      |     |        |        |        |    |

| REV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                |                  |        |         |       |           |   |            |     |              |      |                |           |      |     |        |        |        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                |                  |        |         |       |           |   |            |     |              |      |                |           |      |     |        |        |        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Prepared in         | n accordance   | e with ASME      | Y14.24 |         |       |           |   |            |     |              |      |                |           |      | V   | ′endor | item ( | drawir | ng |

REVISIONS

DESCRIPTION

LTR

DATE

APPROVED

# 1. SCOPE

1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance 4-Channel, Low Noise, Low Power, 24-Bit, Sigma-Delta ADC with PGA and Reference microcircuit, with an operating temperature range of -55°C to +125°C.

1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| V62/19614<br>Drawing<br>number | - <u>01</u><br>Device type<br>(See 1.2.1) | X<br>Case outline<br>(See 1.2.2) | E<br>Lead finish<br>(See 1.2.3)                     |  |

|--------------------------------|-------------------------------------------|----------------------------------|-----------------------------------------------------|--|

| 1.2.1 Device type(s).          |                                           |                                  |                                                     |  |

| Device type                    | Generic                                   | <u>Cir</u>                       | cuit function                                       |  |

| 01                             | AD7124-4-EP                               |                                  | el, Low Noise, Low Power<br>elta ADC with PGA and R |  |

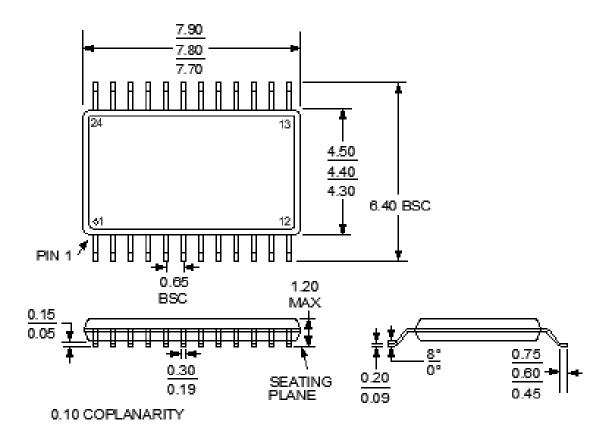

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95    | Package style                             |

|----------------|----------------|-----------------|-------------------------------------------|

| х              | 24             | JEDEC MO-153-AD | Thin Shrink Small Outline Package (TSSOP) |

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator               | <u>Material</u>                                                                                                          |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| A<br>B<br>C<br>D<br>E<br>F<br>Z | Hot solder dip<br>Tin-lead plate<br>Gold plate<br>Palladium<br>Gold flash palladium<br>Tin-lead alloy (BGA/CGA)<br>Other |

|                                 |                                                                                                                          |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/19614</b> |  |

|-----------------------|------|----------------|--------------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |  |

|                       |      | REV            | PAGE 2                   |  |

### 1.3 Absolute maximum ratings. 1/

| AV <sub>DD</sub> to AV <sub>SS</sub><br>IOV <sub>DD</sub> to DGND<br>IOV <sub>DD</sub> to AV <sub>SS</sub><br>AVV <sub>SS</sub> to DGND<br>Analog Input Voltage to AV <sub>SS</sub> .<br>Reference Input Voltage to AV <sub>SS</sub> .<br>Digital Input Voltage to DGND.<br>Digital Output Voltage to DGND<br>AINx/Digital Input Current<br>Operating temperature range:<br>Storage temperature range<br>Maximum Junction temperature<br>Lead temperature, Soldering Reflow | $\begin{array}{c} -0.3 \ V \ to \ +3.96 \ V \\ -0.3 \ V \ to \ +5.94 \ V \\ -1.98 \ V \ to \ +0.3 \ V \\ -0.3 \ V \ to \ AV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ AV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \\ -0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ V \ to \ IOV_{DD} \ + \ 0.3 \ V \ to \ IOV_{DD} \ + \ V \ to \ to$ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ESD Ratings:<br>Human Body Model (HBM)<br>Field-Induced Charged Device Model (FICDM)<br>Machine Model                                                                                                                                                                                                                                                                                                                                                                       | 1250 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### 1.4 Thermal characteristics.

Thermal resistance

| Case outline <u>2</u> / | θ <sub>JA</sub> | θις | Unit |

|-------------------------|-----------------|-----|------|

| Case X                  | 128             | 42  | °C/W |

### 2. APPLICABLE DOCUMENTS

JEDEC – SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEP95 – Registered and Standard Outlines for Semiconductor Devices

JESD51 – Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device).

(Applications for copies should be addressed to the Electronic Industries Alliance, 3103 North 10th Street, Suite 240–S, Arlington, VA 22201-2107 or online at <a href="https://www.jedec.org">https://www.jedec.org</a>)

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |  |

|-----------------------|------|----------------|-----------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/19614 |  |

|                       |      | REV            | PAGE 3    |  |

<sup>&</sup>lt;u>1</u>/ Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

<sup>2/</sup> Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board. See JEDEC JESD51.

#### 3. REQUIREMENTS

3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

3.4 <u>Design, construction, and physical dimension</u>. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

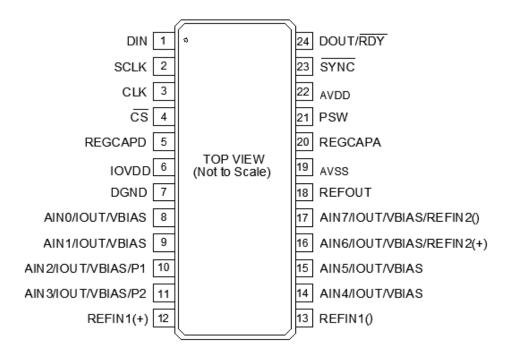

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

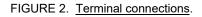

- 3.5.3 <u>Terminal function</u>. The terminal function shall be as shown in figure 3.

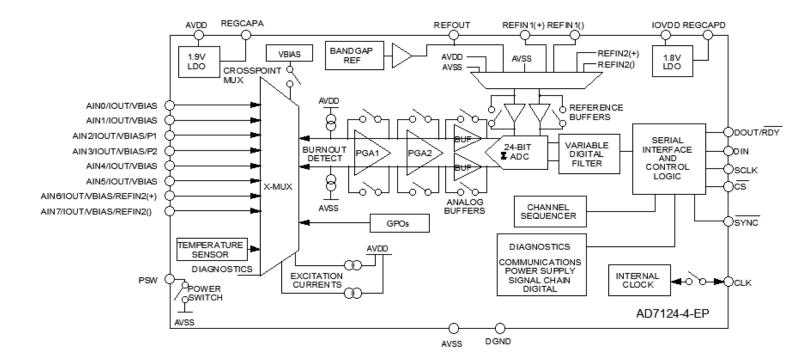

- 3.5.4 <u>Functional block diagram</u>. The functional block diagram shall be as shown in figure 4.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/19614</b> |  |

|-----------------------|------|----------------|--------------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |  |

|                       |      | REV            | PAGE 4                   |  |

| TABLE I.      Electrical performance characteristics.      1/ |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| Test                                          | Symbol | Test conditions                             |         | Limits   |         |        |

|-----------------------------------------------|--------|---------------------------------------------|---------|----------|---------|--------|

|                                               |        | <u>2/</u> 3/                                | Min     | Тур      | Max     |        |

| ADC                                           |        |                                             |         |          |         |        |

| Output Data Rate,                             | fADC   |                                             |         |          |         |        |

| Low Power Mode                                |        |                                             | 1.17    |          | 2400    | SPS    |

| Mid Power Mode                                |        |                                             | 2.34    |          | 4800    | SPS    |

| Full Power Mode                               |        |                                             | 9.38    |          | 19200   | SPS    |

| No Missing Codes <u>4</u> /                   |        | FS <u>5</u> / > 2, sinc <u>6</u> / 4 filter | 24      |          |         | Bits   |

|                                               |        | FS $5/$ > 8, sinc $5/$ filter               | 24      |          |         |        |

| Resolution                                    |        |                                             |         |          |         |        |

| RMS Noise and Update Rates                    |        |                                             |         |          |         |        |

| Integral Nonlinearity (INL)                   |        | Gain = 1 <u>4</u> /                         | -4      | ±1       | +4      | ppm of |

| <b>č</b>                                      |        | Gain > 1 <u>6</u> /                         | -15     | ±2       | +15     | FSR    |

|                                               |        | _                                           |         |          |         | ppm of |

|                                               |        |                                             |         |          |         | FSR    |

| Offset Error <u>7</u> /                       |        |                                             |         |          |         |        |

| Before Calibration                            |        | Gain = 1 to 8                               |         | ±15      |         | μV     |

|                                               |        | Gain = 16 to 128                            |         | 200/gain |         | μV     |

| After Internal Calibration/System             |        |                                             |         | In order |         |        |

| Calibration                                   |        |                                             |         | of noise |         |        |

| Offset Error Drift vs. Temperature <u>8</u> / |        |                                             |         |          |         |        |

| Low Power Mode                                |        | Gain = 1 or gain > 16                       |         | 10       |         | nV/°C  |

|                                               |        | Gain = 2 to 8                               |         | 80       |         | nV/°C  |

|                                               |        | Gain = 16                                   |         | 40       |         | nV/°C  |

| Mid Power Mode                                |        | Gain = 1 or gain > 16                       |         | 10       |         | nV/°C  |

|                                               |        | Gain = 2 to 8                               |         | 40       |         | nV/°C  |

|                                               |        | Gain = 16                                   |         | 20       |         | nV/°C  |

| Full Power Mode                               |        |                                             |         | 10       |         | nV/°C  |

| Gain Error <u>7</u> / <u>9</u> /              |        |                                             |         |          |         |        |

| Before Internal Calibration                   |        | Gain = 1, TA = 25°C                         | -0.0025 |          | +0.0025 | %      |

|                                               |        | Gain > 1                                    |         | -0.3     |         | %      |

| After Internal Calibration                    |        | Gain = 2 to 8, TA = 25°C                    | -0.016  | +0.004   | +0.016  | %      |

|                                               |        | Gain = 16 to 128                            |         | ±0.025   |         | %      |

| After System Calibration                      |        |                                             |         | In order |         |        |

|                                               |        |                                             |         | of noise |         |        |

| Gain Error Drift vs. Temperature              |        |                                             |         | 1        | 2       | ppm/°C |

| Power Supply Rejection                        |        | AIN = 1 V/gain, external                    |         |          |         |        |

| Low Power Mode                                |        | reference                                   | 87      |          |         | dB     |

|                                               |        | Gain = 2 to 16                              | 96      |          |         | dB     |

| Mid Power Mode <u>4</u> /                     |        | Gain = 1 or gain > 16                       | 92      |          |         | dB     |

|                                               |        | Gain = 2 to 16                              | 100     |          |         | dB     |

| Full Power Mode                               |        | Gain = 1 or gain > 16                       | 99      |          |         | dB     |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | 16236          | <b>V62/19614</b> |

|                       |      | REV            | PAGE 5           |

| Test                                               | Test conditions                                                  |                            | Limits |     | Unit |

|----------------------------------------------------|------------------------------------------------------------------|----------------------------|--------|-----|------|

|                                                    |                                                                  | Min                        | Тур    | Max |      |

| ADC – Continued.                                   |                                                                  |                            |        |     |      |

| Common-Mode Rejection <u>10</u> /                  |                                                                  |                            |        |     |      |

| At DC <u>4</u> /                                   | AIN = 1 V, gain = 1                                              | 85                         | 90     |     | dB   |

|                                                    | AIN = 1 V/gain, gain 2 or 4                                      | 105                        | 115    |     | dB   |

|                                                    | AIN = 1 V/gain, gain 2 or 4                                      | 102 <u>11</u> / <u>4</u> / |        |     | dB   |

|                                                    | AIN = 1 V/gain, gain ≥ 8                                         | 115                        | 120    |     | dB   |

|                                                    | AIN = 1 V/gain, gain ≥ 8                                         | 105 <u>11</u> / <u>4</u> / |        |     | dB   |

| Sinc <u>5</u> /, Sinc <u>6</u> / Filter <u>4</u> / |                                                                  |                            |        |     |      |

| At 50 Hz, 60 Hz                                    | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                               | 120                        |        |     | dB   |

| At 50 Hz                                           | 50 SPS, 50 Hz ± 1 Hz                                             | 120                        |        |     | dB   |

| At 60 Hz                                           | 60 SPS, 60 Hz ± 1 Hz                                             | 120                        |        |     | dB   |

| Fast Settling Filters <u>4</u> /                   |                                                                  |                            |        |     |      |

| At 50 Hz                                           | First notch at 50 Hz, 50 Hz ± 1 Hz                               | 115                        |        |     | dB   |

| At 60 Hz                                           | First notch at 60 Hz, 60 Hz ± 1 Hz                               | 115                        |        |     | dB   |

| Post Filters <u>4</u> /                            |                                                                  |                            |        |     |      |

| At 50 Hz, 60 Hz                                    | 20 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                               | 130                        |        |     | dB   |

|                                                    | 25 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                               | 130                        |        |     | dB   |

| Normal Mode Rejection 4/                           |                                                                  |                            |        |     |      |

| Sinc <u>6</u> / Filter                             |                                                                  |                            |        |     |      |

| External Clock                                     |                                                                  |                            |        |     |      |

| At 50 Hz, 60 Hz                                    | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                               | 120                        |        |     | dB   |

|                                                    | 50 SPS, REJ60 = 1 <u>12</u> / , 50 Hz ± 1 Hz, 60 Hz ± 1 Hz       | 80                         |        |     | dB   |

| At 50 Hz                                           | 50 SPS, 50 Hz ± 1 Hz                                             | 120                        |        |     | dB   |

| At 60 Hz                                           | 60 SPS, 60 Hz ± 1 Hz                                             | 120                        |        |     | dB   |

| Internal Clock                                     |                                                                  | _                          |        |     |      |

| At 50 Hz, 60 Hz                                    | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                               | 98                         |        |     | dB   |

|                                                    | 50 SPS, REJ6010 = 1, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                  | 66                         |        |     | dB   |

| At 50 Hz                                           | 50 SPS, 50 Hz ± 1 Hz                                             | 92                         |        |     | dB   |

| At 60 Hz                                           | 60 SPS, 60 Hz ± 1 Hz                                             | 92                         |        |     | dB   |

| Sinc 5/ Filter                                     |                                                                  | 02                         |        |     |      |

| External Clock                                     |                                                                  |                            |        |     |      |

| At 50 Hz, 60 Hz                                    | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                               | 100                        |        |     | dB   |

|                                                    | 50 SPS, REJ60 = 1 $\underline{12}$ /, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz | 65                         |        |     | dB   |

| At 50 Hz                                           | 50 SPS, 50 Hz $\pm$ 1 Hz                                         | 100                        |        |     | dB   |

| At 60 Hz                                           | 60 SPS, 60 Hz ± 1 Hz                                             | 100                        |        |     | dB   |

| Internal Clock                                     |                                                                  |                            |        |     |      |

| At 50 Hz, 60 Hz                                    | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                               | 73                         |        |     | dB   |

|                                                    | 50 SPS, REJ6010 = 1, 50 Hz $\pm$ 1 Hz, 60 Hz $\pm$ 1 Hz          | 52                         |        |     | dB   |

| At 50 Hz                                           | 50 SPS, 50 Hz ± 1 Hz                                             | 68                         |        |     | dB   |

| At 60 Hz                                           | 60 SPS, 60 Hz ± 1 Hz                                             | 68                         |        |     | dB   |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | 16236          | V62/19614 |

|                       |      | REV            | PAGE 6    |

| Test                                               | Test conditions                        |             | Limits     |                         | Unit    |

|----------------------------------------------------|----------------------------------------|-------------|------------|-------------------------|---------|

|                                                    |                                        | Min         | Тур        | Max                     |         |

| ADC – Continued.                                   |                                        |             |            |                         |         |

| Normal Mode Rejection - Continued <u>4</u> /       |                                        |             |            |                         |         |

| Fast Settling Filters                              |                                        |             |            |                         |         |

| External Clock                                     |                                        |             |            |                         |         |

| At 50 Hz                                           | First notch at 50 Hz, 50 Hz ± 0.5 Hz   | 40          |            |                         | dB      |

| At 60 Hz                                           | First notch at 60 Hz, 60 Hz ± 0.5 Hz   | 40          |            |                         | dB      |

| Internal Clock                                     |                                        |             |            |                         |         |

| At 50 Hz                                           | First notch at 50 Hz, 50 Hz ± 0.5 Hz   | 24.5        |            |                         | dB      |

| At 60 Hz                                           | First notch at 60 Hz, 60 Hz ± 0.5 Hz   | 24.5        |            |                         | dB      |

| Post Filters                                       |                                        |             |            |                         |         |

| External Clock                                     |                                        |             |            |                         |         |

| At 50 Hz, 60 Hz                                    | 20 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz     | 86          |            |                         | dB      |

|                                                    | 25 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz     | 62          |            |                         | dB      |

| Internal Clock                                     |                                        |             |            |                         |         |

| At 50 Hz, 60 Hz                                    | 20 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz     | 67          |            |                         | dB      |

|                                                    | 25 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz     | 50          |            |                         | dB      |

|                                                    |                                        |             |            |                         |         |

| ANALOG INPUTS <u>13</u> /                          | •                                      |             |            |                         |         |

| Differential Input Voltage Ranges 14/              | $V_{REF} = REFINx(+) - REFINx(-)$ , or |             | ±VREF/gain |                         |         |

|                                                    | internal reference                     |             |            |                         |         |

| Absolute A <sub>IN</sub> Voltage Limits <u>4</u> / |                                        |             |            |                         |         |

| Gain = 1 (Unbuffered)                              |                                        | AVss - 0.05 |            | AV <sub>DD</sub> + 0.05 | V       |

| Gain = 1 (Buffered)                                |                                        | AVss + 0.1  |            | AV <sub>DD</sub> - 0.1  | V       |

| Gain > 1                                           |                                        | AVss - 0.05 |            | AV <sub>DD</sub> + 0.05 | V       |

| Analog Input Current                               |                                        |             |            |                         |         |

| Gain > 1 or Gain = 1 (Buffered)                    |                                        |             |            |                         |         |

| Low Power Mode                                     |                                        |             |            |                         |         |

| Absolute Input Current                             |                                        |             | ±1         |                         | nA      |

| Differential Input Current                         |                                        |             | ±0.2       |                         | nA      |

| Analog Input Current Drift                         |                                        |             | 25         |                         | pA/°    |

| Mid Power Mode                                     |                                        |             |            |                         | P. 4    |

| Absolute Input Current                             |                                        |             | ±1.2       |                         | nA      |

| Differential Input Current                         |                                        |             | ±0.4       |                         | nA      |

| Analog Input Current Drift                         |                                        |             | 25         |                         | pA/°    |

| Full Power Mode                                    |                                        |             | 20         |                         | p/0 \$  |

| Absolute Input Current                             |                                        |             | ±3.3       |                         | nA      |

| Differential Input Current                         |                                        |             | ±1.5       |                         | nA      |

| Analog Input Current Drift                         |                                        |             | 25         |                         | pA/°    |

| Gain = 1 (Unbuffered)                              | Current varies with input voltage      |             | 20         |                         |         |

| Absolute Input Current                             |                                        |             | ±2.65      |                         | μA/\    |

| Analog Input Current Drift                         |                                        |             | 1.1        |                         | nA/V/   |

| See footnote at end of table.                      |                                        |             | 1.1        |                         | 10 4 47 |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/19614</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV            | PAGE 7                   |

| Test                                     | Test conditions               |                         | Limits |                         | Unit   |

|------------------------------------------|-------------------------------|-------------------------|--------|-------------------------|--------|

|                                          |                               | Min                     | Тур    | Max                     |        |

| REFERENCE INPUT                          |                               |                         |        |                         |        |

| Internal Reference                       |                               |                         |        |                         |        |

| Initial Accuracy                         | TA = 25°C                     | 2.5 - 0.2%              | 2.5    | 2.5 + 0.2%              | V      |

| Drift                                    |                               |                         | 2      | 10                      | ppm/°C |

| Output Current                           |                               |                         |        | 10                      | mA     |

| Load Regulation                          |                               |                         | 50     |                         | μV/mA  |

| Power Supply Rejection                   |                               |                         | 85     |                         | dB     |

| External Reference                       |                               |                         |        |                         |        |

| External REFIN Voltage <u>4</u> /        | REFIN = REFINx(+) - REFINx(-) | 0.5                     | 2.5    | AV <sub>DD</sub>        | V      |

| Absolute REFIN Voltage Limits <u>4</u> / | Unbuffered                    | AV <sub>SS</sub> - 0.05 |        | AV <sub>DD</sub> + 0.05 | V      |

|                                          | Buffered                      | AV <sub>SS</sub> + 0.1  |        | AV <sub>DD</sub> - 0.1  | V      |

| Reference Input Current                  |                               |                         |        |                         |        |

| Buffered                                 |                               |                         |        |                         |        |

| Low Power Mode                           |                               |                         |        |                         |        |

| Absolute Input Current                   |                               |                         | ±0.5   |                         | nA     |

| Reference Input Current Drift            |                               |                         | 10     |                         | pA/°C  |

| Mid Power Mode                           |                               |                         |        |                         |        |

| Absolute Input Current                   |                               |                         | ±1     |                         | nA     |

| Reference Input Current Drift            |                               |                         | 10     |                         | pA/°C  |

| Full Power Mode                          |                               |                         |        |                         |        |

| Absolute Input Current                   |                               |                         | ±3     |                         | nA     |

| Reference Input Current Drift            |                               |                         | 10     |                         | pA/°C  |

| Unbuffered                               |                               |                         |        |                         |        |

| Absolute Input Current                   |                               |                         | ±12    |                         | nA     |

| Reference Input Current Drift            |                               |                         | 6      |                         | pA/°C  |

| Normal Mode Rejection                    | Same as for analog inputs     |                         |        |                         |        |

| Common-Mode Rejection                    |                               |                         | 100    |                         | dB     |

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE CODE IDENT NO.<br>A 16236 |     | DWG NO. <b>V62/19614</b> |  |

|-----------------------------------------|--------------------------------|-----|--------------------------|--|

|                                         |                                | REV | PAGE 8                   |  |

| Test                            | Test conditions                                            |                         | Limits                                                         |                         | Unit     |  |

|---------------------------------|------------------------------------------------------------|-------------------------|----------------------------------------------------------------|-------------------------|----------|--|

|                                 |                                                            | Min                     | Min Typ                                                        |                         |          |  |

| <b>EXCITATION CURRENT SOURC</b> | ES (IOUT0/IOUT1) (Available on any an                      | alog input pin)         |                                                                |                         |          |  |

| Output Current                  |                                                            |                         | 50/100/250/<br>500/750/1000                                    |                         | μA       |  |

| Initial Tolerance               |                                                            |                         | ±4                                                             |                         | %        |  |

| Drift                           |                                                            |                         | 50                                                             |                         | ppm/°C   |  |

| Current Matching                | Matching between IOUT0 and IOUT1, V <sub>OUT</sub> = 0 V   |                         | ±0.5                                                           |                         | %        |  |

| Drift Matching <u>4</u> /       |                                                            |                         | 5                                                              | 30                      | ppm/°C   |  |

| Line Regulation (AVDD)          | AVDD = 3 V ± 5%                                            |                         | 2                                                              |                         | %/V      |  |

| Load Regulation                 |                                                            |                         | 0.2                                                            |                         | %/V      |  |

| Output Compliance <u>4</u> /    | 50 μA/100 μA/250 μA/500 μA<br>current sources, 2% accuracy | AV <sub>SS</sub> – 0.05 |                                                                | AV <sub>DD</sub> - 0.37 | V        |  |

|                                 | 750 μA and 1000 μA current sources, 2% accuracy            | AVss - 0.05             |                                                                | AV <sub>DD</sub> - 0.48 | V        |  |

| BIAS VOLTAGE (VBIAS) GENER      | RATOR (Available on any analog input                       | pin)                    |                                                                |                         |          |  |

| VBIAS                           |                                                            |                         | AV <sub>SS</sub> + (AV <sub>DD</sub><br>- AV <sub>SS</sub> )/2 |                         | V        |  |

| VBIAS Generator Start-Up Time   | Dependent on the capacitance connected to AI               |                         | 6.7                                                            |                         | µs/nF    |  |

| TEMPERATURE SENSOR              | <u>.</u>                                                   |                         |                                                                |                         | •        |  |

| Accuracy                        |                                                            |                         | ±0.5                                                           |                         | °C       |  |

| Sensitivity                     |                                                            |                         | 13,584                                                         |                         | Codes/°C |  |

| LOW-SIDE POWER SWITCH           |                                                            |                         |                                                                |                         |          |  |

| On Resistance                   |                                                            |                         | 7                                                              | 10                      | Ω        |  |

| Allowable Current <u>4</u> /    | Continuous current                                         |                         |                                                                | 30                      | mA       |  |

| BURNOUT CURRENTS                | •                                                          |                         | •                                                              |                         | •        |  |

| A <sub>IN</sub> Current         | Analog inputs must be buffered                             |                         | 0.5/2/4                                                        |                         | μA       |  |

| DIGITAL OUTPUTS (P1 AND P       | 2)                                                         |                         |                                                                |                         |          |  |

| Output Voltage                  |                                                            |                         |                                                                |                         |          |  |

| High, V <sub>OH</sub>           | Isource = 100 µA                                           | AV <sub>DD</sub> – 0.6  |                                                                |                         | V        |  |

| Low, Vol                        | Isinκ = 100 μA                                             |                         |                                                                | 0.4                     | V        |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/19614</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV            | PAGE 9                   |

| Test                                | Test conditions                                                |                          | Limits   |                         | Unit |

|-------------------------------------|----------------------------------------------------------------|--------------------------|----------|-------------------------|------|

|                                     |                                                                | Min                      | Тур      | Max                     |      |

| DIAGNOSTICS                         |                                                                |                          |          |                         |      |

| Power Supply Monitor Detect Level   |                                                                |                          |          |                         |      |

| Analog Low Dropout Regulator (ALDO  | ) $AV_{DD} - AV_{SS} \ge 2.7 V$                                |                          |          | 1.6                     | V    |

| Digital LDO (DLDO)                  | IOV <sub>DD</sub> ≥ 1.75 V                                     |                          |          | 1.55                    | V    |

| Reference Detect Level              | REF_DET_ERR bit active if<br>VREF < 0.7 V                      | 0.7                      |          | 1                       | V    |

| AINM/AINP Overvoltage Detect Level  |                                                                | AV <sub>DD</sub> + 0.04  |          |                         | V    |

| AINM/AINP Undervoltage Detect Level |                                                                |                          |          | AV <sub>SS</sub> - 0.04 | V    |

| INTERNAL/EXTERNAL CLOCK             |                                                                |                          |          |                         |      |

| Internal Clock                      |                                                                |                          |          |                         |      |

| Frequency                           |                                                                | 614.4 - 5%               | 614.4    | 614.4 + 5%              | kHz  |

| Duty Cycle                          |                                                                |                          | 50:50    |                         | %    |

| External Clock                      |                                                                |                          |          |                         |      |

| Frequency                           | Internal divide by 4                                           |                          | 2.4576   |                         | MH   |

| Duty Cycle                          |                                                                |                          | 45:55 to |                         | %    |

|                                     |                                                                |                          | 55:45    |                         |      |

| LOGIC INPUTS <u>4</u> /             |                                                                |                          | 1        |                         |      |

| Input Voltage                       |                                                                |                          |          |                         |      |

| Low, V <sub>INL</sub>               | 1.65 V ≤ IOV <sub>DD</sub> < 1.9 V                             |                          |          | 0.3 × IOV <sub>DD</sub> | V    |

|                                     | $1.9 \text{ V} \leq \text{IOV}_{\text{DD}} < 2.3 \text{ V}$    |                          |          | $0.35 \times IOV_{DD}$  | V    |

|                                     | $2.3 V \le IOV_{DD} \le 3.6 V$                                 |                          |          | 0.7                     | V    |

| High, V <sub>INH</sub>              | $1.65 \text{ V} \le \text{IOV}_{\text{DD}} < 1.9 \text{ V}$    | 0.7 × IOV <sub>DD</sub>  |          |                         | V    |

|                                     | $1.9 \text{ V} \leq \text{IOV}_{\text{DD}} < 2.3 \text{ V}$    | 0.65 × IOV <sub>DD</sub> |          |                         | V    |

|                                     | $2.3 V \leq IOV_{DD} \leq 2.7 V$                               | 1.7                      |          |                         | V    |

|                                     | $2.7 \text{ V} \leq \text{IOV}_{\text{DD}} \leq 3.6 \text{ V}$ | 2                        |          |                         | V    |

| Hysteresis                          | $1.65 V \le IOV_{DD} \le 3.6 V$                                | 0.2                      |          | 0.6                     | V    |

| Input Currents                      | $VI_N = IOV_{DD} \text{ or } GND$                              | -1                       | 4.5      | +1                      | μA   |

| Input Capacitance                   | All digital inputs                                             |                          | 10       |                         | pF   |

| LOGIC OUTPUTS (INCLUDING CLK)       |                                                                |                          | 1        |                         |      |

| Output Voltage <u>4</u> /           |                                                                |                          |          |                         |      |

| High, Voн                           | Isource = $100 \mu A$                                          | IOV <sub>DD</sub> - 0.35 |          | <u> </u>                | V    |

| Low, Vol                            | Isinκ = 100 μA                                                 |                          |          | 0.4                     | V    |

| Floating State Leakage Current      |                                                                | -1                       |          | +1                      | μA   |

| Floating State Output Capacitance   |                                                                |                          | 10       |                         | pF   |

| Data Output Coding                  |                                                                |                          | Offset   |                         |      |

|                                     |                                                                |                          | binary   |                         |      |

# TABLE I. Electrical performance characteristics - Continued. 1/

| DLA LAND AND MARITIME | SIZE CODE IDENT NO. |     | DWG NO.   |

|-----------------------|---------------------|-----|-----------|

| COLUMBUS, OHIO        | A 16236             |     | V62/19614 |

|                       |                     | REV | PAGE 10   |

| Test                                                                  | Test conditions                                                                             |            | Limits |           | Unit |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------|--------|-----------|------|

|                                                                       |                                                                                             | Min        | Тур    | Max       |      |

| SYSTEM CALIBRATION <u>4</u> ,                                         |                                                                                             |            |        |           |      |

| Calibration Limit                                                     |                                                                                             |            |        |           |      |

| Full Scale (FS)                                                       |                                                                                             |            |        | 1.05 × FS | V    |

| Zero Scale                                                            |                                                                                             | −1.05 × FS |        |           | V    |

| Input Span                                                            |                                                                                             | 0.8 × FS   |        | 2.1 × FS  | V    |

| POWER SUPPLY VOLTAGES FOR ALL POWE                                    | R MODES                                                                                     |            |        |           |      |

| AVDD to AVSS                                                          |                                                                                             |            |        |           |      |

| Low Power Mode                                                        |                                                                                             | 2.7        |        | 3.6       | V    |

| Mid Power Mode                                                        |                                                                                             | 2.7        |        | 3.6       | V    |

| Full Power Mode                                                       |                                                                                             | 2.9        |        | 3.6       | V    |

| IOV <sub>DD</sub> to GND                                              |                                                                                             | 1.65       |        | 3.6       | V    |

| AVss to GND                                                           |                                                                                             | -1.8       |        | 0         | V    |

| IOV <sub>DD</sub> to AV <sub>SS</sub>                                 |                                                                                             |            |        | 5.4       | V    |

| POWER SUPPLY CURRENTS <u>13</u> / <u>15</u> /                         | ·                                                                                           |            |        |           |      |

| I <sub>AVDD</sub> , External Reference                                |                                                                                             |            |        |           |      |

| Low Power Mode                                                        |                                                                                             |            |        |           |      |

| Gain = 1 <sup>2</sup>                                                 | All buffers off                                                                             |            | 125    | 140       | μA   |

| Gain = 1 I <sub>AVDD</sub> Increase per AINx Buffer <u>4</u> /        |                                                                                             |            | 15     | 25        | μA   |

| Gain = 2 to 8                                                         |                                                                                             |            | 205    | 250       | μA   |

| Gain = 16 to 128                                                      |                                                                                             |            | 235    | 300       | μA   |

| IA <sub>VDD</sub> Increase per Reference Buffer <u>4</u> /            | All gains                                                                                   |            | 10     | 20        | μA   |

| Mid Power Mode                                                        |                                                                                             |            |        |           |      |