#### MAX77840

### 3A Buck Charger with ModelGauge m5 Fuel Gauge and USB BC1.2 Detection

#### **General Description**

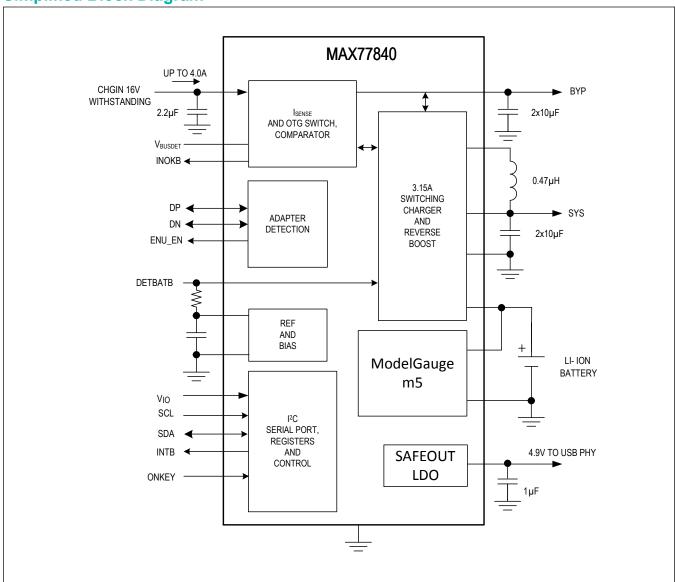

The MAX77840 is a 3.15A switched-mode charger and ModelGauge™ m5 fuel gauge with integrated USB BC1.2 detection for Li-ion batteries and a SAFEOUT LDO.

The charger integrates all switches and operates at either 4MHz or 2MHz (programmable) switching frequency, allowing selection of the smallest external components or achieving lowest heat dissipation. The MAX77840 is ideally suited for devices such as mobile point-of-sale devices, portable medical electronics, or other handheld devices. It includes the USB BC1.2 detection function to recognize common USB adapters and set the input current limit automatically. The MAX77840 can supply up to 1.5A OTG current with proprietary MAXOTG protection, that limits the OTG output current to prevent system voltage from collapsing under heavy OTG loads.

The ModelGauge m5 provides accurate battery fuel gauging and operates with extremely low battery current (25 $\mu$ A, typ) during standby or sleep mode to extend battery life. The interaction between the ModelGauge m5 and the charger provides end users a superior charging experience in a single IC.

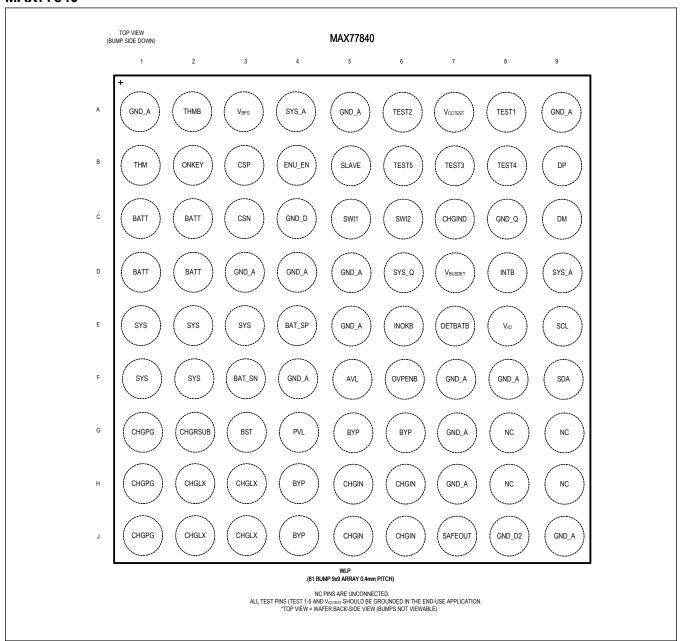

Shipping mode is built into the MAX77840 to minimize battery drain when the device is not in use. The MAX77840 features an  $I^2C$  3.0 compatible serial interface. It is offered in a 3.87mm x 3.96mm, 9 x 9 bump array wafer-level package (WLP) with 0.4mm pitch.

#### **Applications**

- Industrial PCs

- Portable Medical Devices

- Mobile Point-of-Sale Devices

- Wireless Speakers

- E-Cigarettes

- Smart Home Automation, Sensors

- Internet of Things (IoT)

#### **Benefits and Features**

- Single-Input Switch Mode Charger

- Up to 16V Protection

- Up to 13.4V Input Operating Range

- Up to 4.0A Input Current Limit with Adaptive Input Current Limiting (AICL)

- Up to 3.15A Battery Charging Current Limit

- CC, CV, and Die Temperature Control

- Small Inductor: 0.47µH or 1µH Package

- High Efficiency

- Supports USB-OTG Reverse Boost, up to 1.5A Current Limit (Programmable)

- Integrated Battery True-Disconnect FET

- $R_{DS(ON)} = 12.8 m\Omega$

- Rated Up to 9A<sub>RMS</sub>, Discharge Current Limit (Programmable, default 4.5A)

- Adapter Type Detection

- D+/D- Detection for USB port, USB DCP, and USB HVDCP

- BC 1.2 Compliant

- ModelGauge m5 Battery Fuel Gauge

- ±1% SOC Accuracy, No Calibration Cycles, Very Low I<sub>Q</sub>

- Time-to-Empty and Time-to-Full Prediction

- One Safeout LDO

- Control Functions

- · Shipping Mode with ONKEY Pressing Clear

- · True Hardware Reset with ONKEY

- I<sup>2</sup>C 3.0 Compatible Interface with Interrupt Output

- 3.87mm x 3.96mm, 9 x 9 Array WLP with 0.4mm Pitch

Ordering Information appears at end of data sheet.

ModelGauge is a trademark of Maxim Integrated Products, Inc. Smart Power Selector is a trademark of Maxim Integrated Products, Inc. Cycle+ is a trademark of Maxim Integrated Products, Inc.

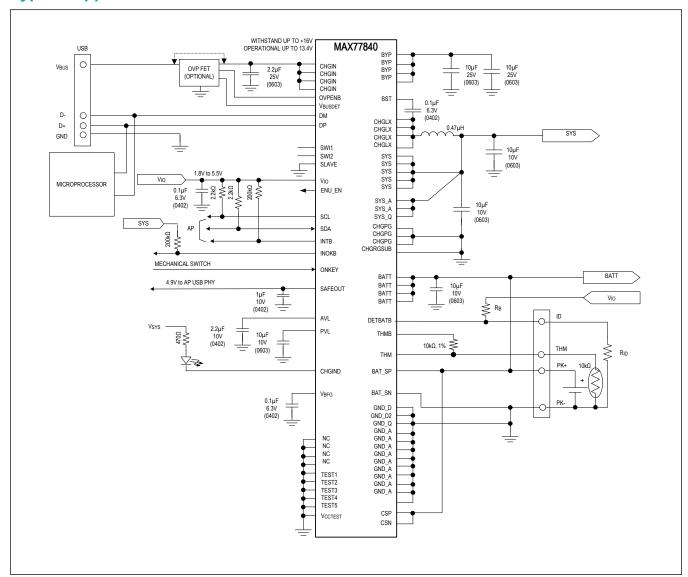

#### **Simplified Block Diagram**

#### **TABLE OF CONTENTS**

| General Description                                 |    |

|-----------------------------------------------------|----|

| Applications                                        | 1  |

| Benefits and Features                               | 1  |

| Simplified Block Diagram                            | 2  |

| Absolute Maximum Ratings                            | 11 |

| Package Information                                 | 11 |

| 21- WLP0775                                         | 11 |

| Electrical Characteristics                          | 12 |

| Electrical Characteristics—SAFEOUT LDO              | 23 |

| Electrical Characteristics—ModelGauge m5 Fuel Gauge | 24 |

| Pin Configuration                                   | 25 |

| MAX77840                                            | 25 |

| Pin Description                                     | 26 |

| Detailed Description                                | 28 |

| Switching Charger                                   | 28 |

| USB Data Contact Detection                          | 29 |

| Features                                            | 30 |

| DP and DM Detection Functions                       | 30 |

| Data Contact Detection Registers                    | 31 |

| CHGDET_INT (0x01)                                   | 31 |

| CHGDET_STATUS (0x02)                                | 32 |

| CHGDET_INT_MASK (0x03)                              | 32 |

| CHGDET_CHGIN_ILIM (0x04)                            |    |

| CHGDET_CNTRL1 (0x05)                                |    |

| CHGDET_CNTRL2 (0x06)                                |    |

| CHGDET_CNTRL3 (0x07)                                | 34 |

| CHGDET_QCNTRL (0x08)                                | 35 |

| ModelGauge m5 Fuel Gauge                            | 35 |

| Detailed Description—Charger                        | 36 |

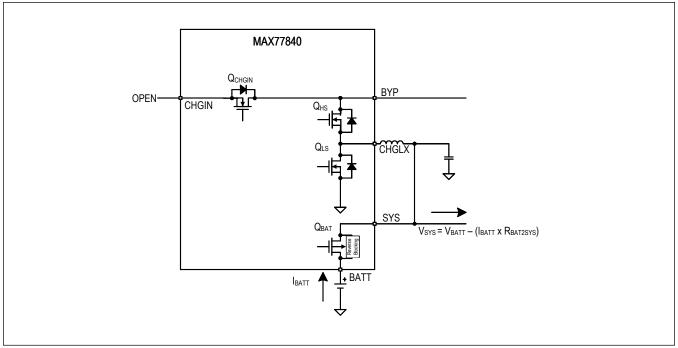

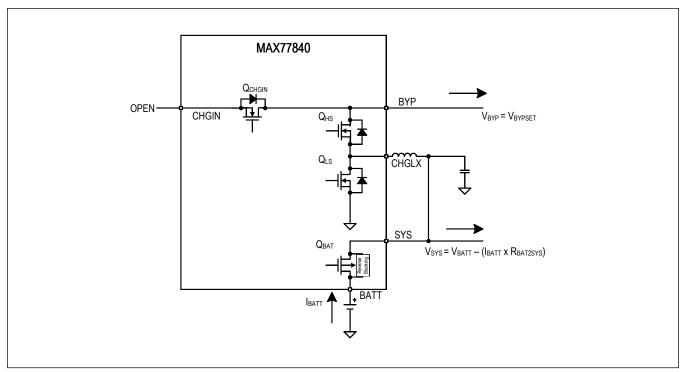

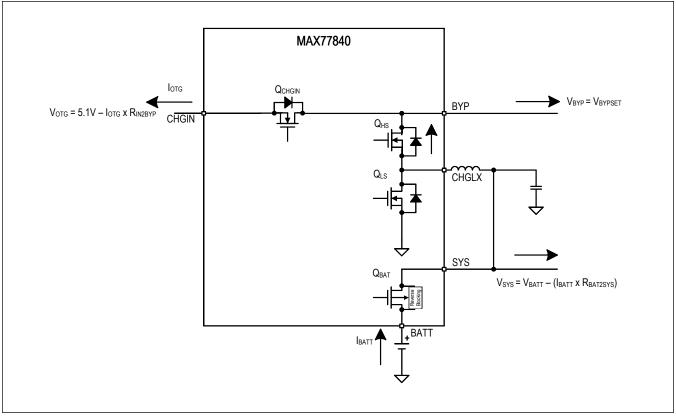

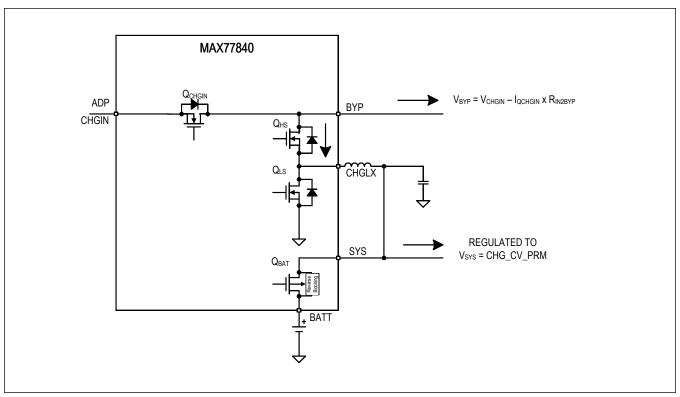

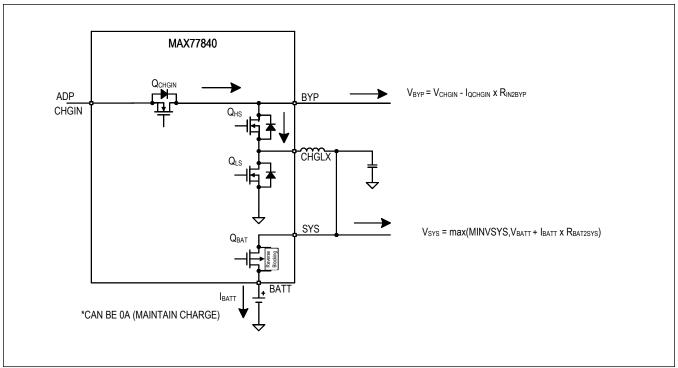

| Smart Power Selector (SPS) <sup>TM</sup>            | 36 |

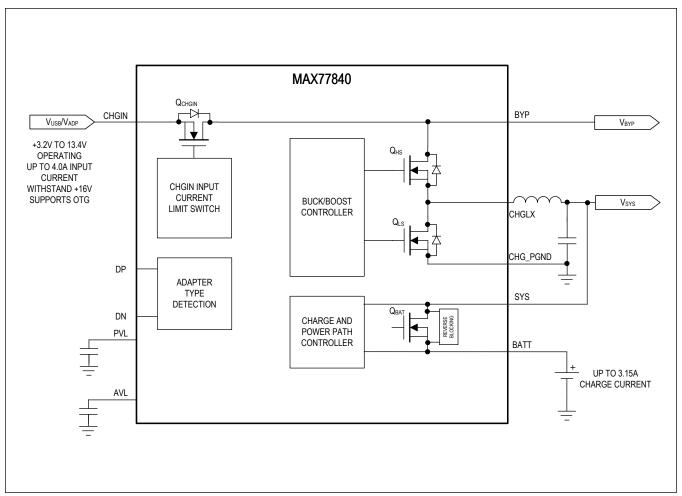

| Switch and Control Loop Descriptions                | 36 |

| Control Bits                                        | 36 |

| Energy Distribution Priority                        | 36 |

| BYP Regulation Voltage                              | 36 |

| SYS Regulation Voltage                              | 36 |

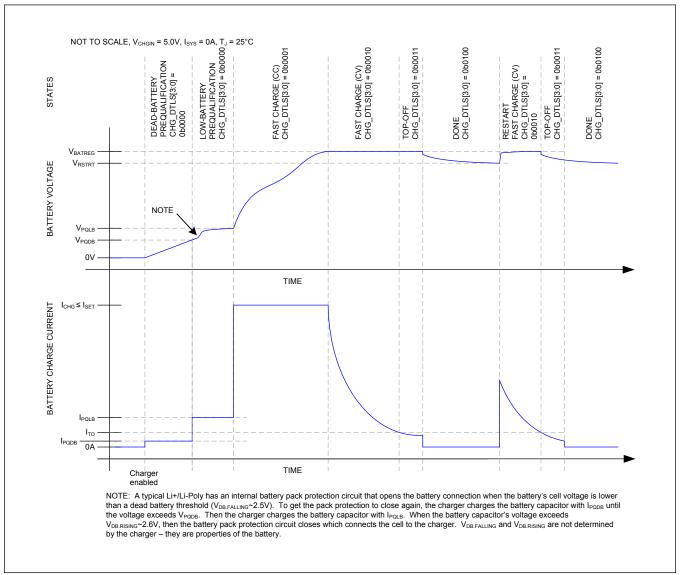

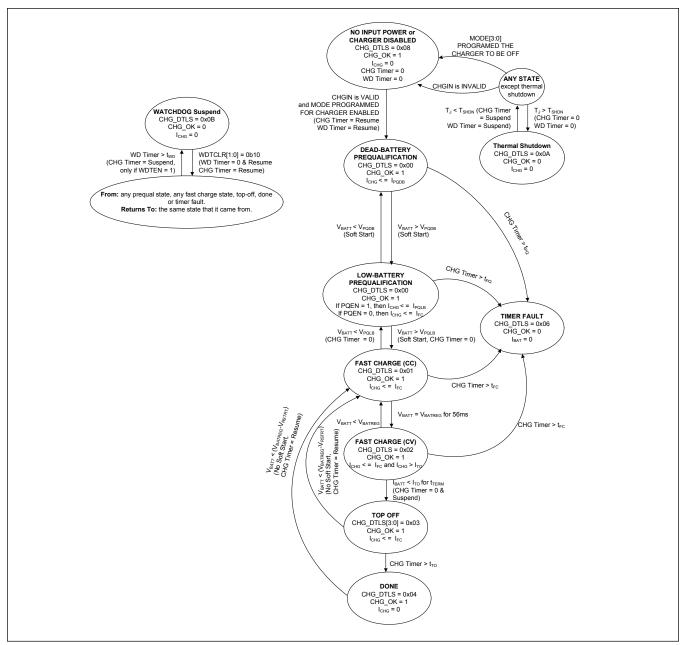

| Charger States                                      | 37 |

| No Input Power or Charger Disabled State            |    |

| Dead-Battery Prequalification State                 | 39 |

| Fast-Charge Constant Current State                  | 39 |

#### TABLE OF CONTENTS (CONTINUED)

| Fast-Charge Constant Voltage State                            | . 39 |

|---------------------------------------------------------------|------|

| TOP-OFF State                                                 | . 39 |

| DONE State                                                    | . 39 |

| Timer Fault State                                             | . 40 |

| Thermal Shutdown State                                        | . 40 |

| Power States                                                  | . 40 |

| Watchdog Timer                                                | . 45 |

| Battery Differential Voltage Sense                            | . 45 |

| Reverse Boost and On-the-Go (OTG) Modes                       | . 45 |

| Input Validation                                              | . 46 |

| Input Current Limit                                           | . 46 |

| Input Voltage Regulation Loop                                 | . 46 |

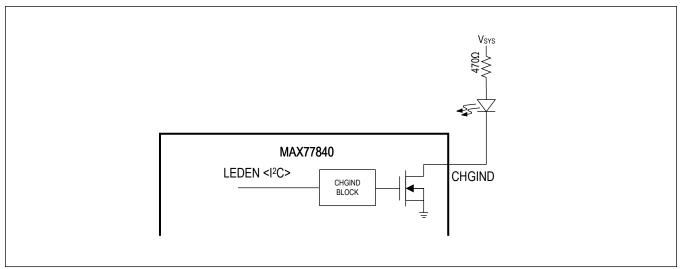

| Charging Status Indicator (CHGIND)                            | . 46 |

| Dead Battery Charging State                                   | . 47 |

| Battery Prequalification Charging State                       | . 47 |

| Fast-Charge Constant Current State                            | . 47 |

| Fast-Charge Constant Voltage State                            | . 47 |

| Top-Off State                                                 | . 47 |

| DONE State                                                    | . 47 |

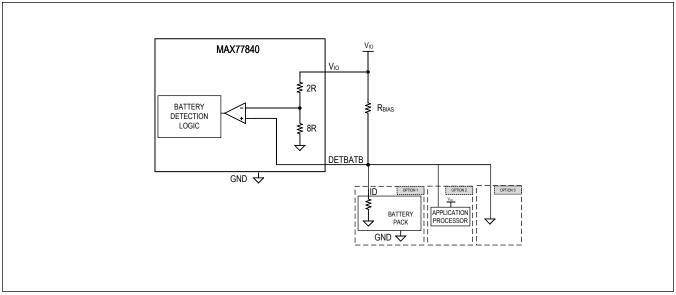

| Battery Detect Input Pin (DETBATB)                            | . 47 |

| Interrupt Pin (INTB)                                          | . 48 |

| System Protections                                            |      |

| V <sub>SYS</sub> Undervoltage Lockout (V <sub>SYSUVLO</sub> ) | . 48 |

| V <sub>SYS</sub> Overvoltage Lockout (V <sub>SYSOVLO</sub> )  | . 49 |

| Battery Overvoltage Protection                                | . 49 |

| Battery Overcurrent Protection During System Power-Up         | . 49 |

| Battery Overcurrent Protection Due to Fault                   |      |

| Battery Thermistor for Charge and Discharge                   | . 49 |

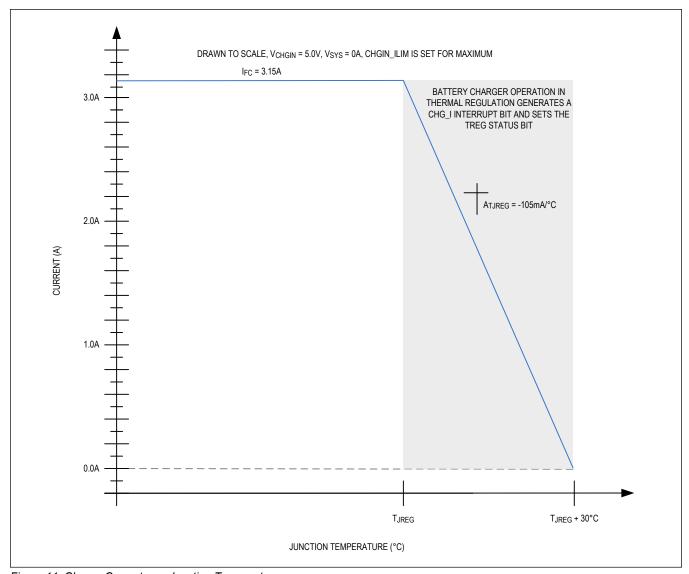

| Thermal Foldback                                              | . 49 |

| Analog Low-Noise Power Input (AVL) and PVL                    | . 50 |

| Charger Register Details                                      | . 51 |

| Register Protection                                           | . 51 |

| Interrupt Mask, Okay and Detail Registers                     | . 51 |

| CHG_INT Register Bit Description                              | . 52 |

| CHG_INT_MASK Register Bit Description (0xB1)                  | . 52 |

| CHG_INT_OK Register Bit Description (0xB2)                    | . 53 |

| CHG_DETAILS_00 Register Bit Description (0xB3)                | . 53 |

| CHG_DETAILS_01 Register Bit Description (0xB4)                | . 54 |

| CHG_DETAILS_02 Register Bit Description (0xB5)                | . 55 |

#### TABLE OF CONTENTS (CONTINUED)

| CHG_CNFG_00 Register Bit Description (0xB7)                                        | 56 |

|------------------------------------------------------------------------------------|----|

| CHG_CNFG_01 Register Bit Description (0xB8)                                        | 57 |

| CHG_CNFG_02 Register Bit Description (0xB9)                                        | 58 |

| CHG_CNFG_03 Register Bit Description (0xBA)                                        | 59 |

| CHG_CNFG_04 Register Bit Description (0xBB)                                        | 30 |

| CHG_CNFG_06 Register Bit Description (0xBD)                                        | 30 |

| CHG_CNFG_07 Register Bit Description (0xBE)                                        | 31 |

| CHG_CNFG_09 Register Bit Description (0xC0)                                        | 32 |

| CHG_CNFG_10 Register Bit Description (0xC1)                                        | 33 |

| CHG_CNFG_11 Register Bit Description (0xC2)                                        | 34 |

| CHG_CNFG_12 Register Bit Description (0xC3)                                        | 35 |

| Detailed Description—I <sup>2</sup> C Interface                                    | 35 |

| I <sup>2</sup> C Interface                                                         | 35 |

| Slave Addresses                                                                    | 35 |

| I <sup>2</sup> C Communication Pins                                                | 35 |

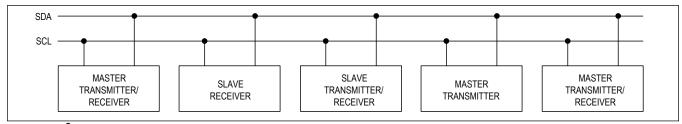

| I <sup>2</sup> C System Configuration                                              | 36 |

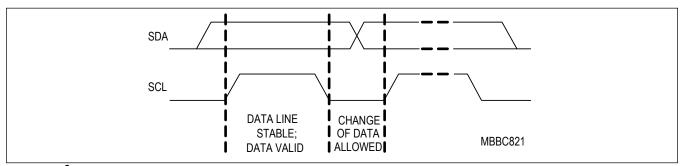

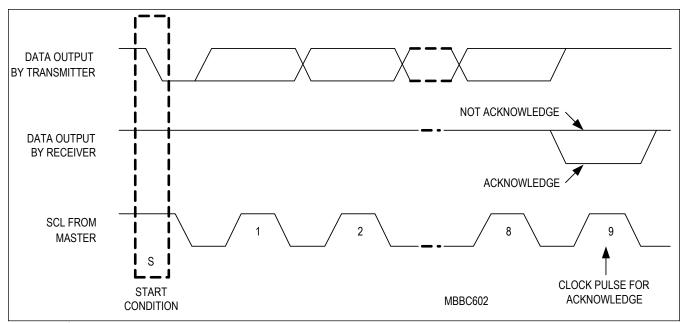

| I <sup>2</sup> C Bit Transfer                                                      | 36 |

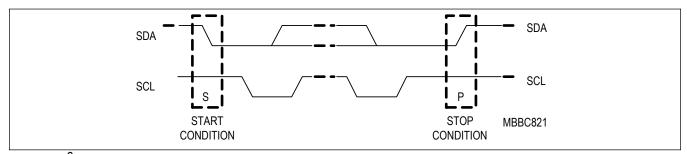

| I <sup>2</sup> C Start and Stop Conditions                                         | 36 |

| I <sup>2</sup> C Acknowledge6                                                      | 36 |

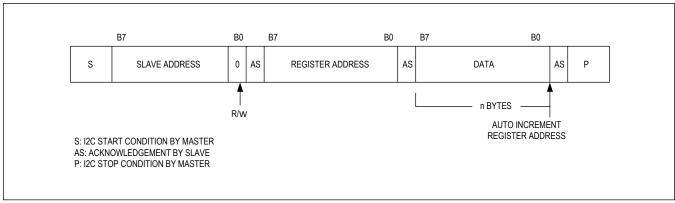

| Master Transmits (Write Mode)6                                                     | 37 |

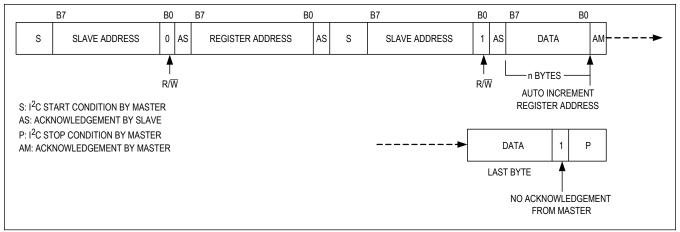

| Master Reads After Setting Register Address (Write Register Address and Read Data) | 37 |

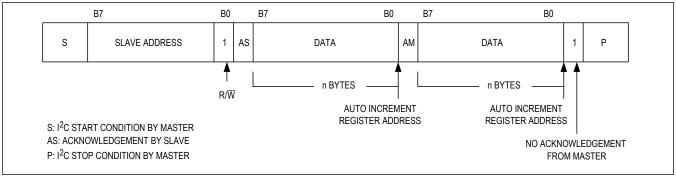

| Master Reads Register Data Without Setting Register Address (Read Mode)            | 38 |

| Register Reset Conditions6                                                         | 38 |

| I <sup>2</sup> C Register Details                                                  | 39 |

| PMIC ID Register (0x00)                                                            | 39 |

| Interrupt Source (0x22)                                                            | 39 |

| Interrupt Source Mask (0x23)                                                       | 39 |

| SYSTEM Interrupt (0x24)                                                            | 70 |

| SYSTEM Interrupt Source Mask (0x26)                                                | 70 |

| Top SYS Status Register (0x28)                                                     | 71 |

| Low SYS Detection Configuration (0x2B)                                             | 71 |

| SAFEOUT Control Register (0xC6)                                                    | 72 |

| Soft-Reset Register (0x50)                                                         | 72 |

| Detailed Description—ONKEY                                                         | 73 |

| ONKEY                                                                              |    |

| Detailed Description—SAFEOUT LDO                                                   | 73 |

| Detailed Description—ModelGauge m5 Fuel Gauge                                      | 73 |

| ModelGauge m5 Details                                                              | 73 |

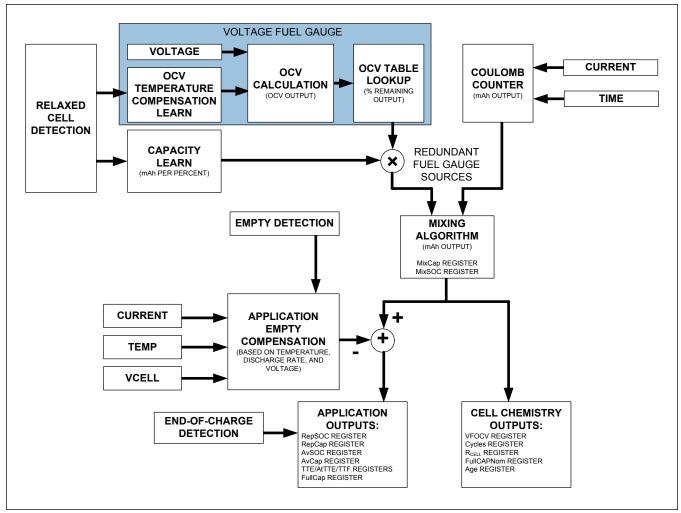

| ModelGauge m5 Algorithm                                                            | 74 |

#### TABLE OF CONTENTS (CONTINUED)

| OCV Estimation and Coulomb-Count Mixing   | . 75 |

|-------------------------------------------|------|

| Fuel-Gauge Empty Compensation             | . 75 |

| Fuel-Gauge Learning                       |      |

| Determining Fuel-Gauge Accuracy           | . 76 |

| Initial Accuracy                          | . 76 |

| Cycle+ Charger Control                    | . 76 |

| End-of-Charge Detection                   |      |

| Power-Up and Power-On Reset               |      |

| Save and Restore Registers                |      |

| Cell Insertion (IC Already Powered)       | . 77 |

| Cell Removal                              |      |

| Fast Detection of Cell Removal            | . 77 |

| Modes of Operation                        |      |

| ALRT Function                             |      |

| IC Memory Map                             |      |

| ModelGauge m5 Registers                   |      |

| Register Details                          |      |

| JEITA Charging Registers                  |      |

| TAIrtTh (0x02)                            |      |

| TAIrtTh2 (0xB2)                           |      |

| JEITA_Volt (0xD9)                         |      |

| JEITA_Curr (0xDA)                         |      |

| ChargeState(0-7) (0xD1 – 0xD8)            |      |

| SmartChgCfg (0xDB)                        | . 82 |

| Status and Configuration Registers        |      |

| Status (0x00)                             |      |

| Status2 (0xB0)                            |      |

| VAIrtTh (0x01)                            |      |

| SAIrtTh (0x03)                            |      |

| AtRate (0x04)                             |      |

| Config (0x1D)                             | . 84 |

| Config2 (0xBB)                            | . 85 |

| DevName (0x21)                            | . 86 |

| LearnCfg (0x28)                           | . 86 |

| FilterCfg (0x29)                          | . 86 |

| RelaxCfg (0x2A)                           | . 86 |

| TGain (0x2C) / TOff (0x2D) / Curve (0xB9) | . 87 |

| TGain (0x2C)                              | . 87 |

| TOff (0x2D)                               | . 87 |

#### TABLE OF CONTENTS (CONTINUED)

| · · · · · · · · · · · · · · · · · · ·         |        | _ |

|-----------------------------------------------|--------|---|

| Curve (0xB9)                                  | <br>87 | 7 |

| Register Settings for Common Thermistor Types | <br>87 | 7 |

| COff (0x2F)                                   | <br>87 | 7 |

| RippleCfg (0xBD)                              | <br>87 | 7 |

| Measurement Registers                         |        |   |

| Vcell (0x09)                                  |        |   |

| AvgVCell (0x19)                               | <br>   | 3 |

| MaxMinVolt (0x1B)                             | <br>   | 3 |

| Current (0x0A)                                | <br>   | 3 |

| AvgCurrent (0x0B)                             |        |   |

| MaxMinCurr (0x1C)                             |        |   |

| Temp (0x08)                                   |        |   |

| AvgTA (0x16)                                  |        |   |

| MaxMinTemp (0x1A)                             |        |   |

| AIN0 (0x27)                                   |        |   |

| Timer (0x3E)                                  |        |   |

| ShdnTimer (0x3F)                              |        |   |

| QH0 (0x4C)                                    |        |   |

| VRipple (0xBC).                               |        |   |

| TimerH (0xBE)                                 |        |   |

| ModelGauge m5 Configuration Registers         |        |   |

| QRTable00 (0x12)                              |        |   |

| QRTable10 (0x22)                              |        |   |

| QRTable20 (0x32)                              |        |   |

| QRTable30 (0x42)                              |        |   |

| FullSocThr (0x13)                             |        |   |

| IChgTerm (0x1E)                               |        |   |

| FullCapNom (0x23)                             |        |   |

| DesignCap (0x18)                              |        |   |

| IAvgEmpty (0x36)                              |        |   |

| RComp0 (0x38)                                 |        |   |

| TempCo (0x39)                                 |        |   |

| VEmpty (0x3A)                                 |        |   |

| ConvgCfg (0x49)                               | <br>91 | İ |

| TTF_CFG (0xB5)                                |        |   |

| CV_MixCap (0xB6)                              |        |   |

| CV_HalfTime (0xB7)                            |        |   |

| ModelGauge m5 Output Registers                | <br>92 | 2 |

| RenCan (0x05)                                 | 92     | ) |

#### TABLE OF CONTENTS (CONTINUED)

| F          | RepSOC (0x06)       | 92 |

|------------|---------------------|----|

| A          | Age (0x07)          | 92 |

| (          | QResidual (0x0C)    | 92 |

| ľ          | MixCap (0x0F)       | 92 |

| ľ          | MixSOC (0x0D)       | 92 |

| A          | AvCap (0x1F)        | 93 |

| A          | AvSOC (0x0E)        | 93 |

| F          | FullCap (0x10)      | 93 |

| ٦          | TTE (0x11)          | 93 |

| F          | Rslow (0x14)        | 93 |

| (          | Cycles (0x17)       | 93 |

| ٦          | TTF (0x20)          | 93 |

| F          | FullCapRep (0x35)   | 93 |

| C          | dQAcc (0x45)        | 94 |

| C          | dPAcc (0x46)        | 94 |

| \          | VFRemCap (0x4A)     | 94 |

| A          | AtQresidual (0xDC)  | 94 |

| A          | AtAvSOC (0xDE)      | 94 |

| A          | AtAvCap (0xDF)      | 94 |

| \          | VFOCV (0xFB)        | 94 |

| Typical Ap | oplication Circuits | 95 |

| Ordering I | nformation          | 95 |

| Revision F | History !           | 96 |

#### MAX77840

## 3A Buck Charger with ModelGauge m5 Fuel Gauge and USB BC1.2 Detection

#### LIST OF FIGURES

| Figure 1. Switching Charger Block Diagram                 | 29 |

|-----------------------------------------------------------|----|

| Figure 2. MAX77840 Typical Charging Profile               | 37 |

| Figure 3. MAX77840 Charger State Diagram                  | 38 |

| Figure 4. Battery-Only                                    | 41 |

| Figure 5. Battery-Boost                                   | 42 |

| Figure 6. Battery-Boost (OTG)                             | 43 |

| Figure 7. No Charge-Buck                                  | 44 |

| Figure 8. Charge-Buck                                     | 45 |

| Figure 9. Charging Indicator Circuit                      | 47 |

| Figure 10. Battery Present Detection Circuit              | 48 |

| Figure 11. Charge Currents vs. Junction Temperature       | 50 |

| Figure 12. I <sup>2</sup> C System Configuration          | 66 |

| Figure 13. I <sup>2</sup> C Bit Transfer                  |    |

| Figure 14. I <sup>2</sup> C Start and Stop                | 66 |

| Figure 15. I <sup>2</sup> C Acknowledge                   | 67 |

| Figure 16. Master Write Operation                         | 67 |

| Figure 17. Master Read Operation with Register Addresses  | 68 |

| Figure 18. Master Read Operation without Register Address |    |

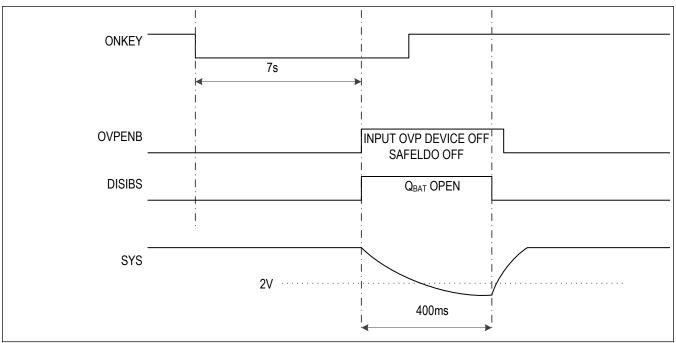

| Figure 19. ONKEY Timing Diagram                           |    |

|                                                           | 75 |

#### MAX77840

# 3A Buck Charger with ModelGauge m5 Fuel Gauge and USB BC1.2 Detection

| LIST OF TABLES                            |  |

|-------------------------------------------|--|

| Table 1. Supported Adapter Types          |  |

| Table 2. Data Contact Detection Registers |  |

| Table 3. ModelGauge m5 Registers          |  |

#### **Absolute Maximum Ratings**

| Switching Charger            |                     |

|------------------------------|---------------------|

| CHGIN to GND_A               | 0.3V to +16V        |

| BYP to GND_A                 | 0.3V to +16V        |

| PVL to GND_A                 | 0.3V to +6V         |

| AVL to GND_A                 | 0.3V to +6V         |

| BAT_SP to GND_A              | 0.3V to +6V         |

| BAT_SN to GND_A              | 0.3V to +0.3V       |

| BATT to GND_A                | 0.3V to +6V         |

| SYS to GND_A                 | 0.3V to +6V         |

| DETBATB to GND_A             | 0.3V to +6V         |

| V <sub>BUSDET</sub> to GND_A | 0.3V to +20V        |

| OVPENB to GND_A              |                     |

| BST to AVL                   | 0.3V to +16V        |

| BST to CHGLX                 | 0.3V to +6V         |

| INOKB to GND_A               |                     |

| CHGPG to GND_A               | 0.3V to +0.3V       |

| CHGLX Continuous Current     | 3.5A <sub>RMS</sub> |

| CHGPG Continuous Current     | 3.5A <sub>RMS</sub> |

| SYS Continuous Current       | 4.5A <sub>RMS</sub> |

| BATT Continuous Current      | 4.5A <sub>RMS</sub> |

| BYP Continuous Current       | 3.0A <sub>RMS</sub> |

| CSP to GND_A                 | 0.3V to BATT + 0.3V |

| CSN to GND_A                         | 0.3V to BATT + 0.3V   |

|--------------------------------------|-----------------------|

| SLAVE to GND_A                       | 0.3V to SYS_A + 0.3V  |

| Battery Overvoltage Protection to 0  |                       |

| ,                                    | 0.3V                  |

| SWI1, SWI2 to GND_A                  | 0.3V to SYS A + 0.3V  |

| GND_D to GND_A                       |                       |

| Safeout LDO                          |                       |

| SAFEOUT to GND_A                     | 0.3V to VCCINT + 0.3V |

| Fuel Gauge                           |                       |

| V <sub>BFG</sub> to GND_A            | 0.3V to +2.2V         |

| THMB, THM to GND_A                   | 0.3V to BATT + 0.3V   |

| I <sup>2</sup> C and Logic Interface |                       |

| V <sub>IO</sub> to GND_A             | 0.3V to +6V           |

| SDA, SCL to GND_A                    |                       |

| SYS_A to GND_A                       | 0.3V to +6V           |

| SYS_Q to GND_A                       |                       |

| INTB to GND_A                        |                       |

| CHGIND to GND_A                      | 0.3V to +6V           |

| TEST_, V <sub>CCTEST</sub> to GND_A  |                       |

| GND_D2 to GND_A                      |                       |

| GND_Q to GND_A                       |                       |

|                                      |                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### 21-WLP0775

| Package Code        | W813C3+1                       |

|---------------------|--------------------------------|

| Outline Number      | <u>21-0775</u>                 |

| Land Pattern Number | Refer to Application Note 1891 |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{SYS} = +3.7V, V_{CHGIN} = 5V \text{ to } V_{CHGIN-OVLO}, V_{IO} = 1.8V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}. V_{SYS} = V_{SYS}\_X = 3.6V, CHGIN = 0V, V_{IO} = 1.8V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, unless otherwise specified. Typical values are at } T_A = +25^{\circ}\text{C}.)$

| PARAMETER                                              | SYMBOL                | CONDITIONS                                                                                                | MIN                      | TYP                       | MAX                      | UNITS |

|--------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|--------------------------|---------------------------|--------------------------|-------|

| GENERAL INFORMATIO                                     | N                     |                                                                                                           |                          |                           |                          | •     |

| Shutdown Supply<br>Current (BATT and<br>VBATTFG)       | I <sub>SHDN</sub>     | All circuits off, BATT = V <sub>BATTFG</sub> = 3.6V                                                       |                          | 25                        | 50                       | μА    |

| No Load Supply Current (BATT and V <sub>BATTFG</sub> ) | I <sub>NL</sub>       | Fuel Gauge is ON, all other circuits off; BATT = V <sub>BATTFG</sub> = 3.6V                               |                          | 50                        | 100                      | μA    |

| SYS INPUT RANGE                                        |                       |                                                                                                           |                          |                           |                          |       |

| V <sub>SYS</sub> Operating Voltage                     | V <sub>SYS</sub>      | Guaranteed by V <sub>SYS_UVLO</sub> and V <sub>SYS_OVLO</sub>                                             | 2.5                      |                           | 5.5                      | V     |

| V <sub>SYS</sub> Undervoltage<br>Lockout Threshold     | V <sub>SYS_UVLO</sub> | V <sub>BATT</sub> falling, 200mV hysteresis                                                               | 2.45                     | 2.5                       | 2.55                     | V     |

| SYS Overvoltage<br>Lockout Threshold                   | V <sub>SYS_OVLO</sub> | V <sub>BATT</sub> rising, 200mV hysteresis                                                                | 5.20                     | 5.36                      | 5.52                     | V     |

| Low SYS Thresholds                                     |                       | Range programmable using the LSDAC register, V <sub>SYS</sub> falling, production tested at 3.60V setting |                          | 3.6                       |                          | V     |

| Low SYS Hysteresis                                     |                       | Range programmable using the LSHYST register, production tested at 100mV setting                          |                          | 100                       |                          | mV    |

| THERMAL SHUTDOWN                                       |                       |                                                                                                           |                          |                           |                          |       |

| Thermal<br>ShutdownThreshold                           | T <sub>SHDN</sub>     | T <sub>J</sub> rising                                                                                     |                          | 165                       |                          | °C    |

| Thermal Shutdown<br>Hysteresis                         |                       |                                                                                                           |                          | 15                        |                          | °C    |

| LOGIC AND CONTROL INPUTS                               |                       |                                                                                                           |                          |                           |                          |       |

| SCL, SDA Input Low<br>Level                            |                       | T <sub>A</sub> = +25°C                                                                                    |                          |                           | 0.3 ×<br>V <sub>IO</sub> | V     |

| SCL, SDA Input High<br>Level                           |                       | T <sub>A</sub> = +25°C                                                                                    | 0.7 ×<br>V <sub>IO</sub> |                           |                          | V     |

| SCL, SDA Input<br>Hysteresis                           |                       | T <sub>A</sub> = +25°C                                                                                    |                          | 0.05 ×<br>V <sub>IO</sub> |                          | V     |

| SCL, SDA Logic Input<br>Current                        |                       | V <sub>IO</sub> = +3.6V                                                                                   | -10                      |                           | +10                      | μA    |

| SCL, SDA Input<br>Capacitance                          |                       | (Note 1)                                                                                                  |                          | 10                        |                          | pF    |

| SDA Output Low<br>Voltage                              |                       | Sinking 20mA                                                                                              |                          |                           | 0.4                      | V     |

| Output Low Voltage<br>INTB                             |                       | I <sub>SINK</sub> = 1mA                                                                                   |                          |                           | 0.4                      | V     |

| Output High Leakage                                    |                       | V <sub>SYS</sub> = 5.5V, T <sub>A</sub> = +25°C                                                           | -1                       | 0                         | +1                       |       |

| INTB                                                   |                       | V <sub>SYS</sub> = 5.5V, T <sub>A</sub> = +85°C                                                           |                          | 0.1                       |                          | μA    |

| Interrupt Debounce<br>Filter Timer                     |                       | LOWSYS                                                                                                    |                          | 16                        |                          | ms    |

$(V_{SYS}$  = +3.7V,  $V_{CHGIN}$  = 5V to  $V_{CHGIN-OVLO}$ ,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C.  $V_{SYS}$  =  $V_{SYS}$ \_X = 3.6V, CHGIN = 0V,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C, unless otherwise specified. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                                                  | SYMBOL              | CONDITIONS                    | MIN  | TYP | MAX  | UNITS |

|----------------------------------------------------------------------------|---------------------|-------------------------------|------|-----|------|-------|

| I <sup>2</sup> C INTERFACE FOR ST                                          | ANDARD, FAST        | , AND FAST-MODE PLUS (Note 1) |      |     |      |       |

| Clock Frequency                                                            | f <sub>SCL</sub>    |                               |      |     | 1000 | kHz   |

| Hold Time (Repeated)<br>START Condition                                    | t <sub>HD;STA</sub> |                               | 0.26 |     |      | μs    |

| CLK Low Period                                                             | t <sub>LOW</sub>    |                               | 0.5  |     |      | μs    |

| CLK High Period                                                            | tHIGH               |                               | 0.26 |     |      | μs    |

| Setup Time Repeated START Condition                                        | tsu;sta             |                               | 0.26 |     |      | μs    |

| DATA Hold Time                                                             | thd:dat             |                               | 0    |     |      | μs    |

| DATA Valid Time                                                            | t <sub>VD:DAT</sub> |                               |      |     | 0.45 | μs    |

| DATA Valid<br>Acknowledge Time                                             | t <sub>VD:ACK</sub> |                               |      |     | 0.45 | μs    |

| DATA Setup Time                                                            | t <sub>SU;DAT</sub> |                               | 50   |     |      | ns    |

| Setup Time for STOP<br>Condition                                           | tsu;sto             |                               | 0.26 |     |      | μs    |

| Bus-Free Time Between START and STOP                                       | t <sub>BUF</sub>    |                               | 0.5  |     |      | μs    |

| Pulse Width of Spikes<br>that must be<br>Suppressed by the Input<br>Filter |                     | (Note 1)                      |      | 50  |      | ns    |

| I <sup>2</sup> C INTERFACE FOR HS                                          | -MODE PLUS (C       | B = 100pF) (Note 1)           |      |     |      |       |

| Clock Frequency                                                            | f <sub>SCL</sub>    | CB = 100pF                    |      |     | 3.4  | MHz   |

| Hold Time (Repeated)<br>START Condition                                    | t <sub>HD;STA</sub> |                               | 160  |     |      | ns    |

| Setup Time Repeated START Condition                                        | t <sub>SU;STA</sub> |                               | 160  |     |      | ns    |

| CLK Low Period                                                             | t <sub>LOW</sub>    |                               | 160  |     |      | ns    |

| CLK High Period                                                            | tHIGH               |                               | 60   |     |      | ns    |

| DATA Hold Time                                                             | thd:dat             |                               | 0    |     |      | ns    |

| DATA Setup Time                                                            | t <sub>VD:DAT</sub> |                               | 10   |     |      | ns    |

| Setup Time for STOP Condition                                              | t <sub>SU;STO</sub> |                               | 160  |     |      | ns    |

| Pulse Width of Spikes<br>that must be<br>Suppressed by the Input<br>Filter |                     | (Note 1)                      |      | 10  |      | ns    |

| I <sup>2</sup> C INTERFACE FOR HS                                          | -MODE PLUS (C       | B = 400pF) (Note 1)           |      |     |      |       |

| Clock Frequency                                                            | f <sub>SCL</sub>    | CB = 400pF                    |      |     | 1.7  | MHz   |

| Hold Time (Repeated)<br>START Condition                                    | t <sub>HD;STA</sub> |                               | 160  |     |      | ns    |

| Setup Time Repeated START Condition                                        | tsu;sta             |                               | 160  |     |      | ns    |

#### **Electrical Characteristics (continued)**

$(V_{SYS}$  = +3.7V,  $V_{CHGIN}$  = 5V to  $V_{CHGIN-OVLO}$ ,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C.  $V_{SYS}$  =  $V_{SYS}$ \_X = 3.6V, CHGIN = 0V,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C, unless otherwise specified. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                                                    | SYMBOL                         | CONDITIONS                                                                                                                      | MIN                     | TYP                     | MAX                     | UNITS |

|------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|-------|

| CLK Low Period                                                               | t <sub>LOW</sub>               |                                                                                                                                 | 320                     |                         |                         | ns    |

| CLK High Period                                                              | <sup>t</sup> HIGH              |                                                                                                                                 | 120                     |                         |                         | ns    |

| DATA Hold Time                                                               | thd:dat                        |                                                                                                                                 | 0                       |                         |                         | ns    |

| DATA Setup Time                                                              | t <sub>VD:DAT</sub>            |                                                                                                                                 | 10                      |                         |                         | ns    |

| Setup Time for STOP<br>Condition                                             | tsu;sto                        |                                                                                                                                 | 160                     |                         |                         | ns    |

| Pulse Width of Spikes<br>that must be<br>Suppressed by the Input<br>Filter   |                                | (Note 3)                                                                                                                        |                         | 10                      |                         | ns    |

| CHGIN INPUT                                                                  |                                |                                                                                                                                 |                         |                         |                         |       |

| Operating Voltage                                                            |                                |                                                                                                                                 | 3.2                     |                         | $V_{OVLO}$              | V     |

| CHGIN Overvoltage<br>Threshold (Note 2)                                      | V <sub>CHGIN-OVLO</sub>        | V <sub>CHGIN</sub> rising                                                                                                       | 13.4                    | 13.7                    | 14                      | V     |

| CHGIN Overvoltage-<br>Threshold Hysteresis                                   | V <sub>CHGINH</sub> -<br>OVLO  | V <sub>CHGIN</sub> falling                                                                                                      |                         | 300                     |                         | mV    |

| CHGIN Overvoltage<br>Delay (Note 1)                                          | Т                              | V <sub>CHGIN</sub> rising, 100mV overdrive, not production tested                                                               |                         | 10                      |                         | 110   |

|                                                                              | T <sub>D-OVLO</sub>            | V <sub>CHGIN</sub> falling, 100mV overdrive, not production tested                                                              |                         | 20                      |                         | μs    |

| V <sub>BUSDET</sub> to GND<br>Minimum Turn-On<br>Threshold Range (Note<br>2) | V <sub>VBUSDET_</sub> UV<br>LO | V <sub>VBUSDET</sub> rising, 200mV hysteresis, programmable at 4.5V, 4.9V, 5.0V, and 5.1V (Note 2)                              | 4.5                     |                         | 5.1                     | V     |

| V <sub>BUSDET</sub> to GND<br>Minimum Turn-On<br>Threshold Accuracy          | V <sub>VBUSDET_UV</sub><br>LO  | V <sub>VBUSDET</sub> rising, 4.5V setting                                                                                       | 4.4                     | 4.5                     | 4.6                     | V     |

| V <sub>BUSDET</sub> to SYS<br>Minimum Turn-On<br>Threshold (Note 2)          | V <sub>VBUSDET2SY</sub><br>S   | V <sub>VBUSDET</sub> rising, 50mV hysteresis when valid V <sub>BUSDET</sub> input is detected                                   | V <sub>SYS</sub> + 0.12 | V <sub>SYS</sub> + 0.20 | V <sub>SYS</sub> + 0.28 | V     |

| V <sub>BUSDET</sub> Turn-On<br>Threshold Delay                               | T <sub>D-UVLO</sub>            | Not production tested                                                                                                           |                         | 10                      |                         | μs    |

| CHGIN Adaptive<br>Current Regulation<br>Threshold Range (Note<br>3)          | V <sub>CHGIN_REG</sub>         | Programmable at 4.2V, 4.6V, 4.7V, and 4.8V (Note 3)                                                                             | 4.2                     |                         | 4.8                     | V     |

| CHGIN Current Limit<br>Range                                                 |                                | Programmable, 500mA default, factory programmable option of 100mA, production tested at 500mA, 1800mA, and 4000mA settings only | 0.1                     |                         | 4                       | А     |

|                                                                              | I <sub>IN</sub>                | $V_{CHGIN}$ = 2.4V, the input is undervoltage and $R_{INSD}$ is the only loading                                                |                         | 0.075                   |                         |       |

| CHGIN Supply Current                                                         | ",                             | V <sub>CHGIN</sub> = 5.0V, Charger disabled                                                                                     |                         | 0.17                    | 0.5                     | mA    |

| CHGIN Supply Current                                                         | I <sub>IN</sub>                | V <sub>CHGIN</sub> = 5.0V, Charger enabled, V <sub>SYS</sub> = V <sub>BATT</sub> = 4.5V, (no switching, battery charged)        |                         | 2.7                     | 4                       | - INA |

$(V_{SYS}$  = +3.7V,  $V_{CHGIN}$  = 5V to  $V_{CHGIN-OVLO}$ ,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C.  $V_{SYS}$  =  $V_{SYS}$ \_X = 3.6V, CHGIN = 0V,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C, unless otherwise specified. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                                  | SYMBOL                 | CONDITIONS                                                                                                                                                                     | MIN   | TYP    | MAX  | UNITS |

|------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|------|-------|

|                                                            |                        | V <sub>CHGIN</sub> = 5.0V, Charger enabled, V <sub>BATT</sub> = 3.8V, 500mA input current setting, T <sub>A</sub> = +25°C                                                      | 462.5 | 487.5  | 500  |       |

|                                                            |                        | $V_{CHGIN}$ =5.0V, Charger enabled, $V_{BATT}$ = 3.8V, 1800mA input current setting, $T_A$ = +25°C                                                                             | 1710  | 1755   | 1800 |       |

| V <sub>CHGIN</sub> Input Current<br>Limit                  | I <sub>INLIMIT</sub>   | V <sub>CHGIN</sub> = 5.0V, Charger enabled, V <sub>BATT</sub> = 3.8V, 1800mA input current setting, T <sub>A</sub> = 0°C to +85°C                                              | 1667  | 1755   | 1843 | mA    |

|                                                            |                        | V <sub>CHGIN</sub> = 5.0V, Charger enabled, V <sub>BATT</sub> = 3.8V, 4000mA input current setting, T <sub>A</sub> = +25°C                                                     | 3800  | 3900   | 4000 |       |

|                                                            |                        | V <sub>CHGIN</sub> = 5.0V, Charger enabled, V <sub>BATT</sub> = 3.8V, 4000mA input current setting, T <sub>A</sub> = 0°C to +85°C                                              | 3705  | 3900   | 4095 | 1095  |

| CHGIN Self-Discharge<br>Down to UVLO Time                  | t <sub>INSD</sub>      | Time required for the charger input to cause a 10µF input capacitor to decay from 6.0V to 4.3V                                                                                 |       | 100    |      | ms    |

| CHGIN Input Self-<br>Discharge Resistance                  | R <sub>INSD</sub>      |                                                                                                                                                                                |       | 35     |      | kΩ    |

| CHGINOK to start switching                                 | Tstart                 |                                                                                                                                                                                |       | 26     |      | ms    |

| CHGIN Adaptive<br>Voltage Regulation<br>Threshold Accuracy | V <sub>CHGIN_REG</sub> | 4.8V setting                                                                                                                                                                   | 4.7   | 4.8    | 4.9  | V     |

| SWITCH IMPEDANCES                                          | AND LEAKAGE            | CURRENTS                                                                                                                                                                       |       |        |      |       |

| CHGIN to BYP<br>Resistance                                 | R <sub>IN2BYP</sub>    | Bidirectional                                                                                                                                                                  |       | 0.0144 | 0.04 | Ω     |

| CHGLX High-Side<br>Resistance                              | R <sub>HS</sub>        |                                                                                                                                                                                |       | 0.0327 | 0.1  | Ω     |

| CHGLX Low-Side<br>Resistance                               | R <sub>LS</sub>        |                                                                                                                                                                                |       | 0.0543 | 0.14 | Ω     |

| BATT to SYS Dropout<br>Resistance                          | R <sub>BAT2SYS</sub>   |                                                                                                                                                                                |       | 0.0128 | 0.04 | Ω     |

| CHGIN to BATT<br>Dropout Resistance                        | R <sub>IN2BAT</sub>    | Calculation estimates a $0.04\Omega$ inductor resistance (R <sub>L</sub> ) R <sub>IN2BAT</sub> = R <sub>IN2BYP</sub> + R <sub>HS</sub> + R <sub>L</sub> + R <sub>BAT2SYS</sub> |       | 0.0999 |      | Ω     |

| CHGLX Leakage                                              |                        | CHGLX = CHGPG or BYP, T <sub>A</sub> = +25°C                                                                                                                                   |       | 0.01   | 10   |       |

| Current                                                    |                        | CHGLX = CHGPG or BYP, T <sub>A</sub> = +85°C                                                                                                                                   |       | 1      |      | μA    |

| BST Leakage Current                                        |                        | BST = 5.5V, T <sub>A</sub> = +25°C                                                                                                                                             |       | 0.01   | 10   |       |

| DOT LEARAGE CUITETT                                        |                        | BST = 5.5V, T <sub>A</sub> = +85°C                                                                                                                                             |       | 1      |      | μA    |

| BYP Leakage Current                                        |                        | $V_{BYP}$ = 5.5V, $V_{CHGIN}$ = 0V, $V_{CHGLX}$ = 0V, charger disabled, $T_A$ = +25°C                                                                                          |       | 0.01   | 10   |       |

|                                                            |                        | $V_{BYP}$ = 5.5V, $V_{CHGIN}$ = 0V, $V_{CHGLX}$ = 0V, charger disabled, $T_A$ = +85°C                                                                                          |       | 1      |      | μΑ    |

$(V_{SYS}$  = +3.7V,  $V_{CHGIN}$  = 5V to  $V_{CHGIN-OVLO}$ ,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C.  $V_{SYS}$  =  $V_{SYS}$ \_X = 3.6V, CHGIN = 0V,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C, unless otherwise specified. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                                             | SYMBOL              | CONDITIONS                                                                                                                                                                                | MIN         | TYP  | MAX | UNITS |

|-----------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-----|-------|

| SYS Leakage Current                                                   |                     | V <sub>SYS</sub> = 0V, V <sub>BATT</sub> = 4.2V, charger disabled, T <sub>A</sub> = +25°C                                                                                                 |             | 0.01 | 10  | μA    |

| STS Leakage Current                                                   |                     | V <sub>SYS</sub> = 0V, V <sub>BATT</sub> = 4.2V, charger disabled, T <sub>A</sub> = +85°C                                                                                                 |             | 1    |     | μA    |

|                                                                       |                     | $V_{CHGIN}$ = 0V, $V_{SYS}$ = 0V, $V_{BATT}$ = 4.2V, external $Q_{BAT}$ is off, $T_A$ = +25°C                                                                                             |             | 20   | 30  |       |

|                                                                       |                     | $V_{CHGIN}$ = 0V, $V_{SYS}$ = 0V, $V_{BATT}$ = 4.2V, external $Q_{BAT}$ is off, $T_A$ = +85°C                                                                                             |             | 20   |     |       |

|                                                                       |                     | $V_{CHGIN}$ = 0V, $V_{BATT}$ = 4.2V, external $Q_{BAT}$ is on, main-battery overcurrent protection disabled, $T_A$ = +25°C                                                                |             | 15.3 |     |       |

|                                                                       | <sup>I</sup> МВАТ   | $V_{CHGIN}$ = 0V, $V_{BATT}$ = 4.2V, external $Q_{BAT}$ is on, main-battery overcurrent protection disabled, $T_A$ = +85°C                                                                |             | 15.3 |     |       |

|                                                                       |                     | V <sub>CHGIN</sub> = 0V, V <sub>BATT</sub> = 4.2V, external Q <sub>BAT</sub> is on, main-battery overcurrent protection enabled, T <sub>A</sub> = +25°C                                   |             | 20   |     |       |

| BATT Quiescent Current (I <sub>SYS</sub> = 0A, I <sub>BYP</sub> = 0A) |                     | V <sub>CHGIN</sub> = 0V, V <sub>BATT</sub> = 4.2V, external QBAT is on, main-battery overcurrent protection enabled, T <sub>A</sub> = +85°C                                               |             | 20   |     | μA    |

|                                                                       |                     | V <sub>SYS</sub> = 4.2V, V <sub>BATT</sub> = 0V, charger disabled, T <sub>A</sub> = +25°C                                                                                                 |             | 0.01 | 10  |       |

|                                                                       |                     | $V_{SYS}$ = 4.2V, $V_{BATT}$ = 0V, charger disabled, $T_A$ = +85°C                                                                                                                        |             | 1    |     |       |

|                                                                       | l                   | V <sub>CHGIN</sub> = 5V, V <sub>BATT</sub> = 4.2V, Q <sub>BAT</sub> is off, main-battery overcurrent protection disabled, Charger is enabled but in its done mode, T <sub>A</sub> = +25°C |             | 3    | 10  |       |

|                                                                       | I <sub>MBDN</sub>   | V <sub>CHGIN</sub> = 5V, V <sub>BATT</sub> = 4.2V, Q <sub>BAT</sub> is off, main-battery overcurrent protection disabled, Charger is enabled but in its done mode, T <sub>A</sub> = +85°C |             | 3    |     |       |

| CHARGER DC-DC BUCK                                                    |                     |                                                                                                                                                                                           | · · · · · · |      |     |       |

| Minimum ON Time                                                       | t <sub>ON-MIN</sub> |                                                                                                                                                                                           |             | 75   |     | ns    |

| Minimum OFF Time                                                      | toff                |                                                                                                                                                                                           |             | 75   |     | ns    |

$(V_{SYS}$  = +3.7V,  $V_{CHGIN}$  = 5V to  $V_{CHGIN-OVLO}$ ,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C.  $V_{SYS}$  =  $V_{SYS}$ \_X = 3.6V, CHGIN = 0V,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C, unless otherwise specified. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                            | SYMBOL                    | CONDITIONS                                                                                                                                                   | MIN  | TYP  | MAX  | UNITS |  |

|------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

|                                                      |                           | $T_A$ = 0°C to +85°C, LSEL = 0 (0.47 $\mu$ H inductor option), production tested at $I_{LIM}$ = 00 setting, $I_{LIM}$ = 00 (3.00A out) (Note 4)              | 4.15 | 5.05 | 5.95 |       |  |

|                                                      |                           | $T_A$ = 0°C to +85°C, LSEL = 0 (0.47 $\mu$ H inductor option), production tested at $I_{LIM}$ = 00 setting, $I_{LIM}$ = 01 (2.75A out) (Note 4)              |      | 4.75 |      |       |  |

|                                                      |                           | $T_A$ = 0°C to +85°C, LSEL = 0 (0.47µH inductor option), production tested at $I_{LIM}$ = 00 setting, $I_{LIM}$ = 10 (2.50A out) (Note4)                     |      | 4.45 |      |       |  |

| Current Limit (Note 5)                               | lina                      | $T_A$ = 0°C to +85°C, LSEL = 0 (0.47µH inductor option), production tested at I <sub>LIM</sub> = 00 setting, I <sub>LIM</sub> = 11 (2.25A out) (Note 4)      |      | 4.15 |      | A     |  |

| Current Limit (Note 5)                               | I <sub>LIM</sub>          | $T_A$ = 0°C to +85°C, LSEL = 1 (1.0 $\mu$ H inductor option), production tested at I <sub>LIM</sub> = 11 setting, I <sub>LIM</sub> = 00 (3.00A out) (Note 4) |      | 4.6  |      |       |  |

|                                                      |                           | $T_A$ = 0°C to +85°C, LSEL = 1 (1.0 $\mu$ H inductor option), production tested at I <sub>LIM</sub> = 11 setting, I <sub>LIM</sub> = 01 (2.75A out) (Note 4) |      | 4.3  |      |       |  |

|                                                      |                           | $T_A$ = 0°C to +85°C, LSEL = 1 (1.0 $\mu$ H inductor option), production tested at I <sub>LIM</sub> = 11 setting, I <sub>LIM</sub> = 10 (2.50A out) (Note 4) |      | 4    |      |       |  |

|                                                      |                           | $T_A$ = 0°C to +85°C, LSEL = 1 (1.0μH inductor option), production tested at I <sub>LIM</sub> = 11 setting, I <sub>LIM</sub> = 11 (2.25A out) (Note 4)       | 3    | 3.7  | 4.4  |       |  |

| REVERSE BOOST                                        |                           |                                                                                                                                                              |      |      |      |       |  |

| BYP Voltage Adjustment                               |                           | Adjustable from 3V to 5.5V, min                                                                                                                              |      | 3    |      | V     |  |

| Range                                                |                           | Adjustable from 3V to 5.5V, max (Note 1)                                                                                                                     |      | 5.5  |      | -     |  |

| Reverse Boost<br>Quiescent Current                   | I <sub>BYP</sub>          | Not switching: output forced 200mV above its target regulation voltage                                                                                       |      | 1150 |      | μA    |  |

| Reverse Boost<br>Converter Maximum<br>Output Current |                           | 3.6V <v<sub>BATT production tested BATT = 3.6V</v<sub>                                                                                                       | 2    |      |      | А     |  |

| Reverse Boost BYP<br>Voltage in OTG Mode             | V <sub>BYP.OTG</sub>      | 5.1V setting                                                                                                                                                 | 4.94 | 5.1  | 5.26 | V     |  |

|                                                      |                           | 3.4V, T <sub>A</sub> = +25°C, OTG_ILIM = 00                                                                                                                  | 500  |      | 550  |       |  |

| CHGIN Output Current                                 | I <sub>CHGIN.OTG.LI</sub> | 3.4V, T <sub>A</sub> = +25°C, OTG_ILIM = 01                                                                                                                  | 900  |      | 990  | mA    |  |

| Limit                                                | M CHGIN.OTG.LI            | 3.4V, T <sub>A</sub> = +25°C, OTG_ILIM = 10                                                                                                                  | 1200 |      | 1320 |       |  |

|                                                      |                           | 3.4V, T <sub>A</sub> = +25°C, OTG_ILIM = 11                                                                                                                  | 1500 |      | 1650 |       |  |

#### **Electrical Characteristics (continued)**

$(V_{SYS}$  = +3.7V,  $V_{CHGIN}$  = 5V to  $V_{CHGIN-OVLO}$ ,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C.  $V_{SYS}$  =  $V_{SYS}$ \_X = 3.6V, CHGIN = 0V,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C, unless otherwise specified. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                          | SYMBOL                                                                                | CONDITIONS                                                                                                                                                       | MIN   | TYP  | MAX   | UNITS |

|----------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Reverse Boost Output                               |                                                                                       | Discontinuous inductor current (i.e., skip mode) (Note 1)                                                                                                        |       | ±150 |       | mV    |

| Voltage Ripple (Note 1)                            |                                                                                       | Continuous inductor current (Note 1)                                                                                                                             |       | ±150 |       |       |

| CHARGER                                            |                                                                                       |                                                                                                                                                                  |       |      |       | •     |

| BATT Regulation<br>Voltage Range                   | V <sub>BATTREG</sub>                                                                  | Programmable in 25mV steps (4-bits), production tested at 3.65V and 4.4V only                                                                                    | 3.65  |      | 4.7   | V     |

| BATT Regulation                                    |                                                                                       | 3.65V and 4.7V settings, T <sub>A</sub> = +25°C                                                                                                                  | -0.75 |      | +0.75 |       |

| Voltage Accuracy                                   |                                                                                       | 3.65V and 4.7V settings, T <sub>A</sub> = 0°C to +85°C                                                                                                           | -1    |      | +1    | %     |

| Fast-Charge Current<br>Program Range               |                                                                                       | 100mA to 3.15A in 50mA steps;<br>production tested at 500mA and 3000mA<br>settings                                                                               | 0.1   |      | 3.15  | А     |

|                                                    |                                                                                       | Programmed currents ≥ 500mA, V <sub>BATT</sub> > V <sub>SYSMIN</sub> (short mode); production tested at 500mA and 3000mA settings, T <sub>A</sub> = +25°C        | -4    |      | +4    |       |

| Fast-Charge Current<br>Accuracy                    |                                                                                       | Programmed currents ≥ 500mA, V <sub>BATT</sub> > V <sub>SYSMIN</sub> (short mode); production tested at 500mA and 3000mA settings, T <sub>A</sub> = 0°C to +85°C | -5    |      | +5    | %     |

|                                                    |                                                                                       | Programmed currents ≥ 500mA, V <sub>BATT</sub> < V <sub>SYSMIN</sub> (LDO mode); production test at 800mA                                                        | -10   |      | +10   |       |

| Fast-Charge Currents                               | T <sub>A</sub> = +25°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 3.0A | 3120                                                                                                                                                             | - mA  |      |       |       |

| r ast-charge currents                              | l <sub>FC</sub>                                                                       | $T_A$ = +25°C, $V_{BATT} > V_{SYSMIN}$ , programmed for 0.5A                                                                                                     | 480   | 500  | 520   | IIIA  |

| Low-Battery<br>Prequalification<br>Threshold       | $V_{PQLB}$                                                                            | V <sub>BATT</sub> rising                                                                                                                                         | 2.8   | 2.9  | 3     | V     |

| Dead-Battery<br>Prequalification<br>Threshold      | $V_{PQDB}$                                                                            | V <sub>BATT</sub> rising                                                                                                                                         | 1.9   | 2    | 2.1   | V     |

| Prequalification<br>Threshold Hysteresis           | V <sub>PQ-H</sub>                                                                     | Applies to both V <sub>PQLB</sub> and V <sub>PQDB</sub>                                                                                                          |       | 100  |       | mV    |

| Low-Battery<br>Prequalification Charge<br>Current  | I <sub>PQLB</sub>                                                                     | Default setting = disabled                                                                                                                                       | 187.5 | 250  | 350   | mA    |

| Dead-Battery<br>Prequalification Charge<br>Current | I <sub>PQDB</sub>                                                                     |                                                                                                                                                                  | 40    | 55   | 80    | mA    |

| Charger Restart<br>Threshold Range                 | V <sub>RSTRT</sub>                                                                    | Adjustable, 100, 150, and 200                                                                                                                                    | 100   | 150  | 200   | mV    |

| Charger Restart<br>Deglitch Time                   |                                                                                       | 10mV overdrive, 100ns rise time                                                                                                                                  |       | 130  |       | ms    |

$(V_{SYS}$  = +3.7V,  $V_{CHGIN}$  = 5V to  $V_{CHGIN-OVLO}$ ,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C.  $V_{SYS}$  =  $V_{SYS}$ \_X = 3.6V, CHGIN = 0V,  $V_{IO}$  = 1.8V,  $T_A$  = -40°C to +85°C, unless otherwise specified. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                                              | SYMBOL              | CONDITIONS                                                                                                                                                                 | MIN | TYP   | MAX  | UNITS |

|------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|-------|

| Top-Off Current<br>Program Range                                       |                     | Programmable from 100 to 350mA                                                                                                                                             | 100 |       | 350  | mA    |

| Top-Off Current<br>Accuracy - Gain (Note<br>1)                         |                     | Gain (Note 1)                                                                                                                                                              |     |       | 5    | %     |

| Top-Off Current<br>Accuracy - Offset (Note<br>1)                       |                     | Offset (Note 1)                                                                                                                                                            |     |       | 20   | mA    |

| Charge Termination<br>Deglitch Time                                    | t <sub>TERM</sub>   | 2mV overdrive, 100ns rise/fall time                                                                                                                                        |     | 30    |      | ms    |

| Charger State Change<br>Interrupt Deglitch Time                        | tscidg              | Excludes transition to timer fault state, watchdog timer state                                                                                                             |     | 30    |      | ms    |

| Charger Soft Start Time                                                | t <sub>SS</sub>     | (Note 1)                                                                                                                                                                   |     | 1.5   |      | ms    |

| BAT TO SYS FET DRIVE                                                   | R                   |                                                                                                                                                                            | •   |       |      |       |

|                                                                        |                     | I <sub>BATT</sub> = 10mA                                                                                                                                                   |     | 30    |      | mV    |

| BATT to SYS Reverse                                                    | V <sub>BSREG</sub>  | I <sub>BATT</sub> = 1A                                                                                                                                                     |     | 60    |      | IIIV  |

| Regulation Voltage                                                     | BSREG               | Load regulation during the reverse regulation mode                                                                                                                         |     | 30    |      | mV/A  |

| MINSYS Voltage<br>Accuracy                                             | V <sub>SYSMIN</sub> | Programmable from 3.4V to 3.7V in 100mV steps, V <sub>BATT</sub> = 2.8V; tested at 3.4V and 3.7V settings                                                                  | -3  |       | +3   | %     |

|                                                                        |                     | The maximum system voltage:  V <sub>SYSMAX</sub> = V <sub>BATREG</sub> + R <sub>BAT2SYS</sub> x  I <sub>BATT</sub> ,  V <sub>BATREG</sub> = 4.2V, I <sub>BATT</sub> = 3.0A |     | 4.245 | 4.32 | - v   |

| Maximum SYS Voltage                                                    | Vsysmax             | The maximum system voltage:  VSYSMAX = VBATREG + RBAT2SYS X  IBATT,  VBATREG = 4.7V, IBATT = 3.0A                                                                          |     | 4.745 | 4.82 |       |

| WATCHDOG TIMER                                                         |                     | 5                                                                                                                                                                          |     |       |      |       |

| Watchdog Timer Period                                                  | t <sub>WD</sub>     |                                                                                                                                                                            | 80  |       |      | s     |

| Watchdog Timer<br>Accuracy                                             |                     |                                                                                                                                                                            | -20 | 0     | +20  | %     |

| CHARGE TIMER                                                           |                     |                                                                                                                                                                            |     |       |      |       |

| Prequalification Time                                                  | t <sub>PQ</sub>     | Applies to both low-battery prequalification and dead-battery prequalification modes                                                                                       |     | 35    |      | min   |

| Fast-Charge Constant<br>Current + Fast-Charge<br>Constant Voltage Time | t <sub>FC</sub>     | Adjustable from 4hrs to 16hrs in 2 hour steps including a disable setting (production test at 4hrs and 16hrs)                                                              |     | 8     |      | hrs   |