### **General Description**

The MAX4810/MAX4811/MAX4812 integrated circuits generate high-voltage, high-frequency, unipolar or bipolar pulses from low-voltage logic inputs. These dual pulsers feature independent logic inputs, independent high-voltage pulser outputs with active clamps and independent high-voltage supply inputs.

The MAX4810/MAX4811/MAX4812 feature a  $9\Omega$  output impedance for the high-voltage outputs, and a  $27\Omega$ impedance for the active clamp. The high-voltage outputs are guaranteed to provide 1.3A output current.

All devices use three logic inputs per channel to control the positive and negative pulses and active clamp. Also included are two independent enable inputs. Disabling EN ensures the output MOSFETs are not accidentally turned on during fast power-supply ramping. This allows for faster ramp times and smaller delays between pulsing modes. A low-power shutdown mode reduces power consumption to less than 1µA. All digital inputs are CMOS compatible.

The MAX4810 includes clamp output overvoltage protection, while the MAX4811 features both pulser output and clamp output overvoltage protection. The MAX4812 does not provide overvoltage protection. See the Ordering Information/Selector Guide.

The MAX4810/MAX4811/MAX4812 are available in a 56-pin (7mm x 7mm), TQFN exposed-pad package and are specified over the 0°C to +70°C commercial temperature range.

#### **Applications**

| Ultrasound Medical | Flaw Detection        |  |  |  |  |

|--------------------|-----------------------|--|--|--|--|

| Imaging            | Piezoelectric Drivers |  |  |  |  |

| Cleaning Equipment | Tast Instruments      |  |  |  |  |

### Ordering Information/ **Selector Guide**

| PART         | PROTECTED<br>OUTPUTS    | OUTPUT<br>CURRENT<br>(A) | PIN-<br>PACKAGE |

|--------------|-------------------------|--------------------------|-----------------|

| MAX4810CTN+  | OCP_, OCN_              | 1.3                      | 56 TQFN-EP**    |

| MAX4811CTN+  | OCP_, OCN_,<br>OP_, ON_ | 1.3                      | 56 TQFN-EP**    |

| MAX4812CTN+* | None                    | 1.3                      | 56 TQFN-EP**    |

**Note:** All devices are specified over the 0°C to +70°C operating temperature range.

- +Denotes a lead-free/RoHS-compliant package.

- \*Future product—contact factory for availability.

- \*\*EP = Exposed pad.

**Features**

- ♦ Highly Integrated, High-Voltage, High-Frequency Unipolar/Bipolar Pulser

- ♦ 9Ω Output Impedance and 1.3A (min) Output Current

- ♦ 27Ω Active Clamp

- **♦ Pulser and Clamp Overvoltage Protection** (MAX4810/MAX4811)

- ♦ 0 to +220V Unipolar or ±110V Bipolar Outputs

- ♦ Matched Rise/Fall Times and Matched **Propagation Delays**

- **♦ CMOS-Compatible Logic Inputs**

- ♦ 56-Pin, 7mm x 7mm, TQFN Package

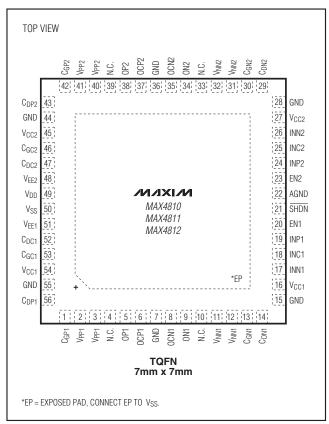

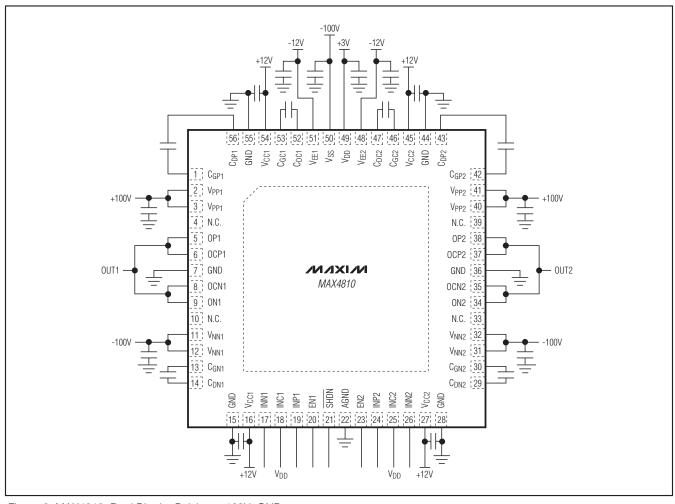

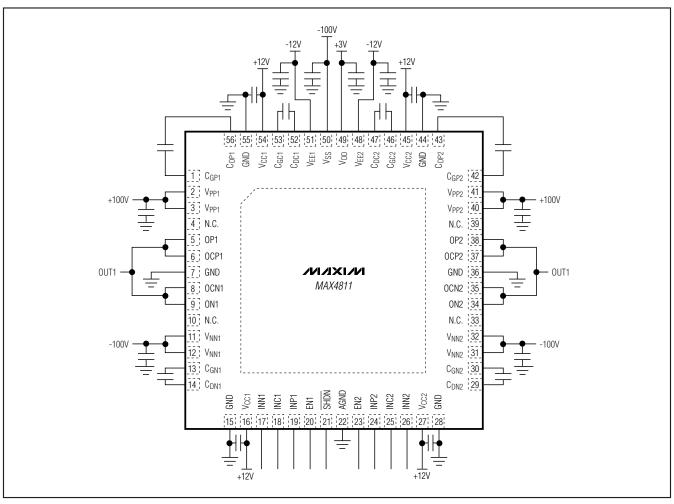

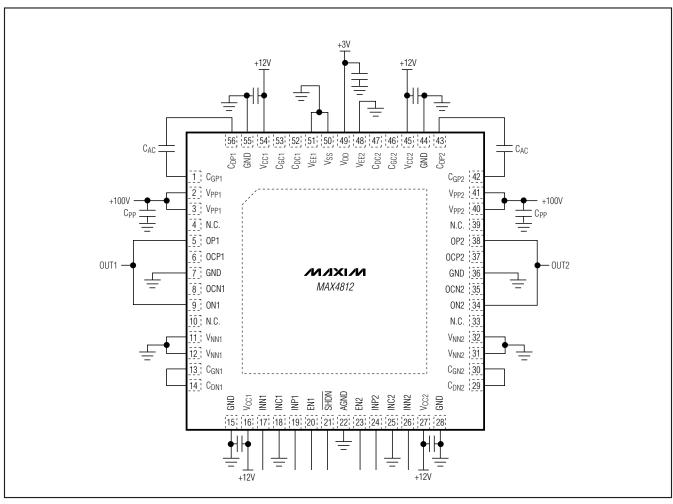

### Pin Configuration

Warning: The MAX4810/MAX4811/MAX4812 are designed to operate with high voltages. Exercise caution.

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to GND.)                                                                         |

|-------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> Logic Supply Voltage0.3V to +6V                                                       |

| V <sub>CC</sub> Output Driver Positive Supply Voltage0.3V to +15V                                     |

| VEE_Output Driver Negative Supply Voltage15V to +0.3V                                                 |

| VPP_High Positive Supply Voltage0.3V to +230V                                                         |

| V <sub>NN</sub> _ High Negative Supply Voltage230V to +0.3V                                           |

| Vss Voltage(Vpp 250V) to V <sub>NN_</sub>                                                             |

| V <sub>PP1</sub> - V <sub>NN1</sub> , V <sub>PP2</sub> - V <sub>NN2</sub> Supply Voltage0.6V to +250V |

| INP_, INN_, INC_, EN_, SHDN Logic Input0.3V to V <sub>DD</sub> + 0.3V                                 |

| Op_, Ocp_, Oln_, On(-0.3V + Vnn_) to (-0.3V to Vpp_)                                                  |

| C <sub>GN</sub> _ Voltage(-0.3V + V <sub>NN</sub> _) to (+15V + V <sub>NN</sub> _)                    |

| C <sub>GP</sub> _ Voltage(+0.3V + V <sub>PP</sub> _) to (-15V + V <sub>PP</sub> _)                    |

| C <sub>GC_</sub> Voltage15V to +15V                                                                   |

|                                                                                                       |

| CDC , CDP , CDN Voltage                                   | 0.3V to V <sub>C</sub> C |

|-----------------------------------------------------------|--------------------------|

| Peak Current per Output Channel                           | 3.0Ā                     |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) (No |                          |

| 56-Pin TQFN (derate 40mW/°C above +70°C                   | )3200mW                  |

| Thermal Resistance (Note 2)                               |                          |

| hetaJA                                                    | 25°C/W                   |

| θJC                                                       |                          |

| Operating Temperature Range                               | 0°C to +70°C             |

| Junction Temperature                                      | +150°C                   |

| Storage Temperature Range                                 |                          |

| Lead Temperature (soldering, 10s)                         | +300°C                   |

|                                                           |                          |

- **Note 1:** This specification is based on the thermal characteristic of the package, the maximum junction temperature, and the setup described by JEDEC 51. The maximum power dissipation for the MAX4810/MAX4811/MAX4812 might be limited by the thermal protection included in the device.

- **Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +2.7V \text{ to } +6V, V_{CC} = +4.75V \text{ to } +12.6V, V_{EE} = -12.6V \text{ to } -4.75V, V_{NN} = -200V \text{ to } 0, V_{PP} = 0 \text{ to } (V_{NN} + 200V), V_{SS} \le \text{the lower of } V_{NN1} \text{ or } V_{NN2}, T_A = T_J = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.) \text{ (Note 3) (See Figures 8, 9, and 10.)}$

| PARAMETER                                        | SYMBOL                                | CONDITIONS                                                                                                                                                                                                                                            | MIN   | TYP | MAX                     | UNITS  |

|--------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------------------------|--------|

| POWER SUPPLY (VDD, VCC_, V                       | / <sub>EE_</sub> , V <sub>PP_</sub> , | V <sub>NN</sub> _)                                                                                                                                                                                                                                    |       |     |                         |        |

| Logic Supply Voltage                             | V <sub>DD</sub>                       |                                                                                                                                                                                                                                                       | +2.7  | +3  | +6                      | V      |

| Positive Drive Supply Voltage                    | V <sub>CC</sub> _                     |                                                                                                                                                                                                                                                       | +4.75 | +12 | +12.6                   | V      |

| Negative Drive Supply Voltage                    | V <sub>EE</sub> _                     |                                                                                                                                                                                                                                                       | -12.6 | -12 | -4.75                   | V      |

| High-Side Supply Voltage                         | V <sub>PP</sub> _                     |                                                                                                                                                                                                                                                       | 0     |     | V <sub>NN</sub> _ + 220 | V      |

| Low-Side Supply Voltage                          | V <sub>NN</sub> _                     |                                                                                                                                                                                                                                                       | -200  |     | 0                       | V      |

| V <sub>PP</sub> V <sub>NN</sub> _ Supply Voltage |                                       |                                                                                                                                                                                                                                                       | 0     |     | +220                    | V      |

| SUPPLY CURRENT (Single Ch                        | annel)                                |                                                                                                                                                                                                                                                       |       |     |                         |        |

|                                                  |                                       | $V_{INN}/V_{INP} = 0$ , $V_{\overline{SHDN}} = 0$                                                                                                                                                                                                     |       |     | 1                       |        |

| V <sub>DD</sub> Supply Current                   | I <sub>DD</sub>                       | $V_{EN} = V_{DD}$ , $V_{\overline{SHDN}} = V_{DD}$ , $V_{INC} = 0$ or $V_{DD}$ , $V_{INN} = V_{\overline{INP}}$ , $f = 5MHz$                                                                                                                          |       | 100 | 200                     | μΑ     |

|                                                  |                                       | V <sub>SHDN</sub> = 0, CH1 and CH2                                                                                                                                                                                                                    |       |     | 1                       |        |

|                                                  |                                       | V <sub>EN_</sub> = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , CH1 and CH2                                                                                                                                                                |       | 130 | 200                     | μA     |

| V <sub>CC</sub> _Supply Current                  | Icc_                                  | V <sub>EN_</sub> = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC_</sub> = 0 or V <sub>DD</sub> ,<br>V <sub>INN_</sub> = V <sub>INP_</sub> , f = 5MHz, V <sub>CC_</sub> = 5V, V <sub>DD</sub> = 3V,<br>only one channel switching |       | 15  |                         | mA     |

|                                                  |                                       | $V_{EN\_} = V_{DD}, V_{\overline{SHDN}} = V_{DD}, V_{INC\_} = 0 \text{ or } V_{DD}, V_{INN\_} = V_{\overline{INP\_}}, f = 5MHz, V_{CC\_} = 12V, V_{DD} = 3V, only one channel switching$                                                              |       | 36  |                         | I IIIA |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7 \text{V to } +6 \text{V}, V_{CC} = +4.75 \text{V to } +12.6 \text{V}, V_{EE} = -12.6 \text{V to } -4.75 \text{V}, V_{NN} = -200 \text{V to } 0, V_{PP} = 0 \text{ to } (V_{NN} + 200 \text{V}), V_{SS} \leq \text{the lower of } V_{NN1} \text{ or } V_{NN2}, T_A = T_J = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25 ^{\circ}\text{C.}) \text{ (Note 3) (See Figures 8, 9, and 10.)}$

| PARAMETER                        | SYMBOL            | CONDITIONS                                                                                                                                                                                                                       | MIN                       | TYP | MAX                       | UNITS |  |

|----------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|---------------------------|-------|--|

|                                  |                   | VSHDN = 0, CH1 and CH2                                                                                                                                                                                                           |                           |     | 25                        |       |  |

|                                  |                   | V <sub>EN_</sub> = V <sub>DD</sub> , V <del>SHDN</del> = V <sub>DD</sub> , CH1 and CH2                                                                                                                                           |                           |     | 1                         | ļ     |  |

| V <sub>EE</sub> _ Supply Current | I <sub>EE</sub> _ | V <sub>EN_</sub> = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , V <sub>INC_</sub> = 0 or V <sub>DD</sub> ,<br>V <sub>INN_</sub> = V <sub>INP_</sub> , f = 5MHz, V <sub>EE_</sub> = -5V,<br>only one channel switching |                           |     | 200                       | μΑ    |  |

|                                  |                   | $V_{EN\_} = V_{DD}$ , $V_{\overline{SHDN}} = V_{DD}$ , $V_{INC\_} = 0$ or $V_{DD}$ , $V_{INN\_} = V_{\overline{INP\_}}$ , $f = 5MHz$ , $V_{EE\_} = -12V$ , only one channel switching                                            |                           |     | 200                       |       |  |

|                                  |                   | VSHDN = 0, CH1 and CH2                                                                                                                                                                                                           |                           |     | 1                         |       |  |

|                                  |                   | V <sub>EN_</sub> = V <sub>DD</sub> , V <sub>SHDN</sub> = V <sub>DD</sub> , CH1 and CH2                                                                                                                                           |                           | 90  | 160                       | μΑ    |  |

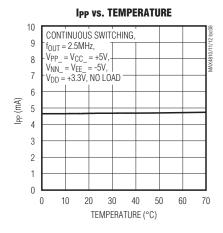

| V <sub>PP_</sub> Supply Current  | I <sub>PP</sub> _ | VEN_ = VDD, VSHDN = VDD, VINC_ = 0 or VDD, VINN_ = VINP_, f = 5MHz, VPP_ = +5V, VNN_ = -5V, no load, only one channel switching                                                                                                  |                           | 9   |                           |       |  |

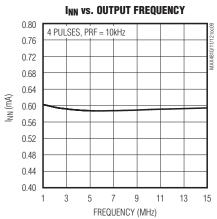

|                                  |                   | VEN_ = VDD, VSHDN = VDD, VINC_ = 0 or VDD,<br>VPP_ = +80V, VNN_ = -80V, pulse repetition<br>frequency = 10kHz, f = 10MHz, 4 periods,<br>no load, only one channel switching                                                      |                           | 0.6 |                           | mA    |  |

|                                  |                   | VSHDN = 0, CH1 and CH2                                                                                                                                                                                                           |                           |     | 1                         |       |  |

|                                  |                   | V <sub>EN</sub> _ = V <sub>DD</sub> , V <del>SHDN</del> = V <sub>DD</sub> , CH1 and CH2                                                                                                                                          |                           | 40  | 80                        | μA    |  |

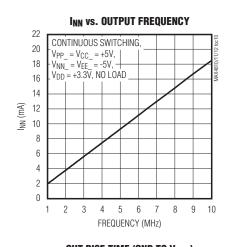

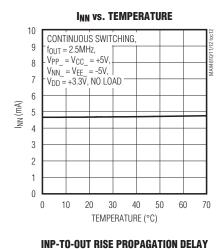

| V <sub>NN</sub> _ Supply Current | INN_              | VEN_ = VDD, VSHDN = VDD, VINC_ = 0 or VDD, VINN_ = VINP_, f = 5MHz, VNN_ = -5V, VPP_ = +5V, no load, only one channel switching                                                                                                  | 9                         |     |                           |       |  |

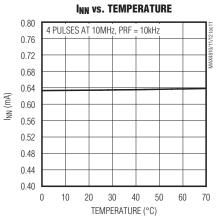

|                                  |                   | VEN_ = VDD, VSHDN = VDD, VINC_ = 0 or VDD, VPP_ = +80V, VNN_ = -80V, pulse repetition frequency = 10kHz, f = 10MHz, 4 periods, no load, only one channel switching                                                               |                           | 0.6 |                           | mA    |  |

| LOGIC INPUTS (EN_, SHDN, IN      | IN_, INP_, II     | NC_)                                                                                                                                                                                                                             | •                         |     |                           |       |  |

| Low-Level Input Voltage          | VIL               |                                                                                                                                                                                                                                  |                           |     | 0.25 x<br>V <sub>DD</sub> | V     |  |

| High-Level Input Voltage         | VIH               |                                                                                                                                                                                                                                  | 0.75 x<br>V <sub>DD</sub> |     |                           | V     |  |

| Logic-Input Capacitance          | CIN               |                                                                                                                                                                                                                                  |                           | 5   |                           | рF    |  |

| Logic-Input Leakage              | I <sub>IN</sub>   | $V_{IN} = 0$ or $V_{DD}$                                                                                                                                                                                                         |                           |     | ±1                        | μΑ    |  |

| OUTPUT (OUT_)                    |                   |                                                                                                                                                                                                                                  |                           |     |                           |       |  |

|                                  |                   | No load at OUT_                                                                                                                                                                                                                  | V <sub>NN</sub> _         |     | V <sub>PP</sub> _         |       |  |

| OUT_ Output-Voltage Range        | Vout_             | Unprotected outputs (see the <i>Ordering Information/Selector Guide</i> ), 100mA load                                                                                                                                            | V <sub>NN</sub> _ + 1.5   |     | V <sub>PP</sub><br>1.5    | V     |  |

|                                  |                   | Protected outputs (see the <i>Ordering Information/Selector Guide</i> ), 100mA load                                                                                                                                              | V <sub>NN</sub> _ + 2.5   |     | V <sub>PP</sub><br>2.5    |       |  |

| Low-Side Small-Signal Output     |                   | I <sub>OP</sub> _ = -100mA, V <sub>CC</sub> _ = +12V ±5%, DC-coupled                                                                                                                                                             |                           | 9   | 17                        |       |  |

| Impedance                        | Rols              | I <sub>OP</sub> _ = -100mA, V <sub>CC</sub> _ = +5V ±5%, DC-coupled                                                                                                                                                              |                           | 9.5 | 18                        | Ω     |  |

|                                  |                   |                                                                                                                                                                                                                                  |                           |     |                           |       |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7 \text{V to } +6 \text{V}, V_{CC} = +4.75 \text{V to } +12.6 \text{V}, V_{EE} = -12.6 \text{V to } -4.75 \text{V}, V_{NN} = -200 \text{V to } 0, V_{PP} = 0 \text{ to } (V_{NN} + 200 \text{V}), V_{SS} \leq \text{the lower of } V_{NN1} \text{ or } V_{NN2}, T_A = T_J = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25 ^{\circ}\text{C.}) \text{ (Note 3) (See Figures 8, 9, and 10.)}$

| PARAMETER                                             | PARAMETER SYMBOL CONDITIONS |                                                                                                 |                                                                                                      |     |      | MAX | UNITS |

|-------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| High-Side Small-Signal Output                         |                             | I <sub>OP</sub> _ = -100mA, V <sub>CC</sub> _ = +12V ±5%, [                                     | DC-coupled                                                                                           |     | 10.5 | 17  |       |

| Impedance                                             | Rohs                        | I <sub>OP</sub> _ = -100mA, V <sub>CC</sub> _ = +5V ±5%, DC-coupled                             |                                                                                                      |     | 12   | 18  | Ω     |

| Low-Side Output Current                               | loL                         | V <sub>CC</sub> = +12V ±5%, V <sub>OUT</sub> - V <sub>NN</sub> =                                |                                                                                                      | 1.3 |      |     | А     |

| High-Side Output Current                              | I <sub>OH</sub>             | V <sub>CC</sub> = +12V ±5%, V <sub>OUT</sub> - V <sub>PP</sub> =                                | : 100V                                                                                               | 1.3 |      |     | А     |

|                                                       |                             | OP_, ON_, OCP_ and OCN_                                                                         | MAX4810                                                                                              |     | 45   |     |       |

| Off-Output Capacitance                                | C <sub>O(OFF)</sub>         | connected together,<br>VPP_ = +100V, V <sub>NN</sub> _ = -100V                                  | MAX4811                                                                                              |     | 75   |     | рF    |

| Off-Output Leakage Current                            | I <sub>LK</sub>             | V <sub>NN</sub> _ = -100V, V <sub>PP</sub> _ = 100V, EN_ = OUT = -100V to +100V                 | : 0,                                                                                                 | -1  |      | +1  | μΑ    |

| Low-Side Signal-Clamp Output                          | -                           | I <sub>OCN_</sub> = -100mA, DC-coupled, V <sub>CC</sub><br>V <sub>EE_</sub> = -V <sub>CC_</sub> | _ = +12V ±5%,                                                                                        |     | 22   | 50  |       |

| Impedance                                             | Rcls                        | I <sub>OCN_</sub> = -100mA, DC-coupled, V <sub>CC</sub><br>V <sub>EE_</sub> = -V <sub>CC_</sub> | C_ = +5V ±5%,                                                                                        |     | 24   | 65  | Ω     |

| High-Side Signal-Clamp Output                         |                             | I <sub>OCP</sub> _ = -100mA, DC-coupled, V <sub>CC</sub> _<br>VEE_ = -V <sub>CC</sub> _         | _ = +12V ±5%,                                                                                        |     | 28   | 50  |       |

| Impedance                                             | R <sub>CHS</sub>            | I <sub>OCP</sub> = -100mA, DC-coupled, V <sub>CC</sub><br>V <sub>EE</sub> = -V <sub>CC</sub>    |                                                                                                      | 38  | 65   | Ω   |       |

| Low-Side Gate Short                                   | _                           | V <sub>CC</sub> _ = +12V ±5%, V <sub>EE</sub> _ = -V <sub>CC</sub> _,<br>EN_ = 0                |                                                                                                      |     | 100  | Ω   |       |

| Impedance                                             | R <sub>LSH</sub>            | V <sub>CC</sub> _ = +12V ±5%, V <sub>EE</sub> _ = -V <sub>CC</sub> _,<br>EN_ = V <sub>DD</sub>  | 5                                                                                                    | 7.5 | 10   | kΩ  |       |

| High-Side Gate Short                                  | ligh-Side Gate Short        |                                                                                                 | V <sub>CC</sub> = +12V ±5%, V <sub>EE</sub> = -V <sub>CC</sub> , I <sub>CGN</sub> = 10mA,<br>EN_ = 0 |     |      | 100 | Ω     |

| Impedance                                             | R <sub>HSH</sub>            | V <sub>CC</sub> _ = +12V ±5%, V <sub>EE</sub> _ = -V <sub>CC</sub> _,<br>EN_ = V <sub>DD</sub>  | 5                                                                                                    | 7.5 | 10   | kΩ  |       |

| THERMAL SHUTDOWN                                      |                             |                                                                                                 |                                                                                                      |     |      |     |       |

| Thermal Shutdown                                      | T <sub>SHDN</sub>           | Junction temperature rising                                                                     |                                                                                                      |     | 150  |     | °C    |

| Thermal-Shutdown Hysteresis                           |                             |                                                                                                 |                                                                                                      |     | 20   |     | °C    |

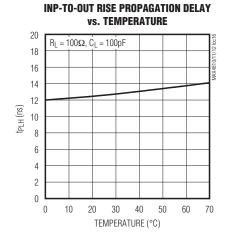

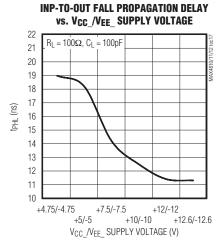

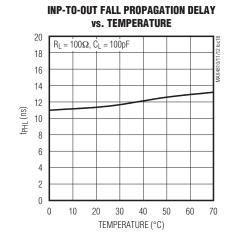

| DYNAMIC CHARACTERISTICS                               | $(R_L = 100\Omega$          | $C_{\rm L}$ = 100pF, unless otherwise no                                                        | oted)                                                                                                |     |      |     |       |

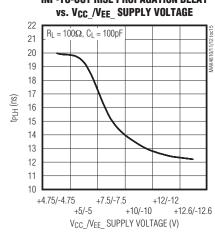

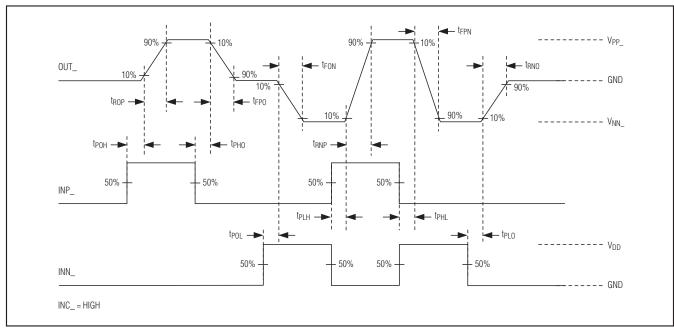

| Logic Input to Output Rise<br>Propagation Delay       | tpLH                        | V <sub>CC</sub> _ = +12V, V <sub>PP</sub> _ = +5V, V <sub>NN</sub> _ =                          | V <sub>CC</sub> _ = +12V, V <sub>PP</sub> _ = +5V, V <sub>NN</sub> _ = -5V, Figure 4                 |     | 15   |     | ns    |

| Logic Input to Output Fall<br>Propagation Delay       | tphl                        | V <sub>CC</sub> _ = +12V, V <sub>PP</sub> _ = +5V, V <sub>NN</sub> _ = -5V, Figure 4            |                                                                                                      |     | 15   |     | ns    |

| Logic Input to Output Rise<br>Propagation Delay       | tpOH                        | V <sub>CC</sub> _ = +12V, V <sub>PP</sub> _ = +5V, V <sub>NN</sub> _ = -5V, Figure 4            |                                                                                                      |     | 15   |     | ns    |

| Logic Input to Output Fall Propagation Delay          | t <sub>POL</sub>            | V <sub>CC</sub> _ = +12V, V <sub>PP</sub> _ = +5V, V <sub>NN</sub> _ = -5V, Figure 4            |                                                                                                      |     | 15   |     | ns    |

| Logic Input to Output-Rise<br>Propagation Delay Clamp | tpLO                        | V <sub>CC</sub> _ = +12V, V <sub>PP</sub> _ = +5V, V <sub>NN</sub> _ =                          | -5V, Figure 4                                                                                        |     | 15   |     | ns    |

4 \_\_\_\_\_\_*NIXI/*M

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7 \text{V to } +6 \text{V}, V_{CC} = +4.75 \text{V to } +12.6 \text{V}, V_{EE} = -12.6 \text{V to } -4.75 \text{V}, V_{NN} = -200 \text{V to } 0, V_{PP} = 0 \text{ to } (V_{NN} + 200 \text{V}), V_{SS} \leq \text{the lower of } V_{NN1} \text{ or } V_{NN2}, T_A = T_J = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25 ^{\circ}\text{C.}) \text{ (Note 3) (See Figures 8, 9, and 10.)}$

| PARAMETER                                               | SYMBOL                                                          | CONDITIONS                                                                                                                            | MIN | TYP  | MAX  | UNITS |  |

|---------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|--|

| Logic Input to Output-Fall<br>Propagation Delay Clamp   | t <sub>PHO</sub>                                                | V <sub>CC</sub> _ = +12V, V <sub>PP</sub> _ = +5V, V <sub>NN</sub> _ = -5V, Figure 4                                                  |     | 15   |      | ns    |  |

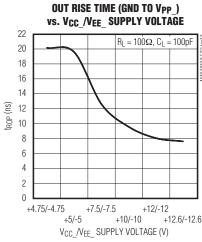

| OUT_ Rise Time (GND to V <sub>PP</sub> _)               | tROP                                                            | V <sub>PP</sub> = +100V, V <sub>NN</sub> = -100V, V <sub>CC</sub> = +12V ± 5%,<br>V <sub>EE</sub> = -V <sub>CC</sub> , Figure 4       |     | 9    | 20   | ns    |  |

| OUT_ Rise Time (V <sub>NN</sub> _ to GND)               | t <sub>RN0</sub>                                                | V <sub>PP</sub> _ = +100V, V <sub>NN</sub> _ = -100V, V <sub>CC</sub> _ = +12V ± 5%, V <sub>EE</sub> _ = -V <sub>CC</sub> _, Figure 4 |     | 17   | 35   | ns    |  |

| OUT_ Rise Time (V <sub>NN</sub> _ to V <sub>PP</sub> _) | t <sub>RNP</sub>                                                | V <sub>PP</sub> _ = +100V, V <sub>NN</sub> _ = -100V, V <sub>CC</sub> _ = +12V ± 5%, V <sub>EE</sub> _ = -V <sub>CC</sub> _, Figure 4 |     | 10.5 | 35   | ns    |  |

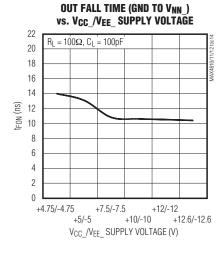

| OUT_ Fall Time (GND to V <sub>NN_</sub> )               | tFON                                                            | V <sub>PP</sub> = +100V, V <sub>NN</sub> = -100V, V <sub>CC</sub> = +12V ± 5%,<br>V <sub>EE</sub> = -V <sub>CC</sub> , Figure 4       |     | 9    | 20   | ns    |  |

| OUT_ Fall Time (VPP_ to GND)                            | t <sub>FP0</sub>                                                | V <sub>PP</sub> = +100V, V <sub>NN</sub> = -100V, V <sub>CC</sub> = +12V ± 5%,<br>V <sub>EE</sub> = -V <sub>CC</sub> , Figure 4       |     | 17   | 35   | ns    |  |

| OUT_ Fall Time (V <sub>PP</sub> _ to V <sub>NN</sub> _) | t <sub>FPN</sub>                                                | V <sub>PP</sub> = +100V, V <sub>NN</sub> = -100V, V <sub>CC</sub> = +12V ± 5%,<br>V <sub>EE</sub> = -V <sub>CC</sub> , Figure 4       |     | 10.5 | 35   | ns    |  |

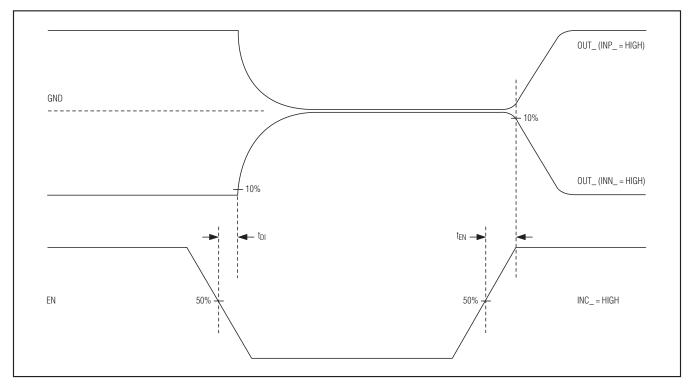

| OUT Enable Time from EN (Figure 5)                      | V <sub>CC</sub> = +12V ± 5%, V <sub>EE</sub> = -V <sub>CC</sub> |                                                                                                                                       | 100 |      | ns   |       |  |

|                                                         |                                                                 | V <sub>CC</sub> = +5V ± 5%, V <sub>EE</sub> = -V <sub>CC</sub><br>V <sub>CC</sub> = +12V ± 5%, V <sub>EE</sub> = -V <sub>CC</sub>     |     |      | 150  |       |  |

| OUT Disable Time from EN (Figure 5)                     | t <sub>DI</sub>                                                 | VCC_ = +5V ± 5%, VEE_ = -VCC_                                                                                                         |     |      | 150  | ns    |  |

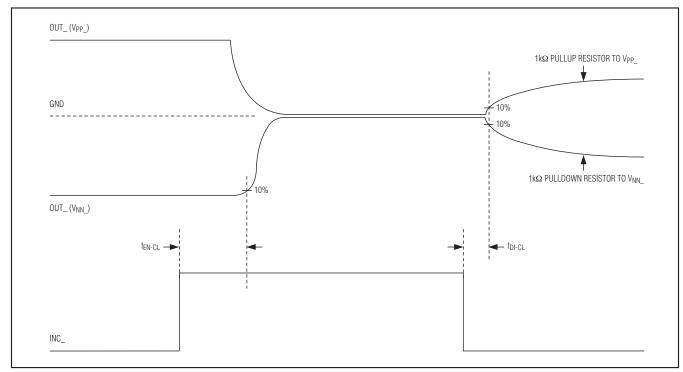

| Clamp Enable Time from INC                              |                                                                 | V <sub>CC</sub> = +12V ± 5%, V <sub>EE</sub> = -V <sub>CC</sub>                                                                       |     |      | 150  |       |  |

| (Figure 6)                                              | tEN-CL                                                          |                                                                                                                                       |     | 180  | ns   |       |  |

| Clamp Disable Time from INC                             |                                                                 | V <sub>CC</sub> = +5V ± 5%, V <sub>EE</sub> = -V <sub>CC</sub><br>V <sub>CC</sub> = +12V ± 5%, V <sub>EE</sub> = -V <sub>CC</sub>     |     |      | 150  | 1     |  |

| (Figure 6)                                              | tDI-CL                                                          | V <sub>CC</sub> _ = +5V ± 5%, V <sub>EE</sub> _ = -V <sub>CC</sub> _                                                                  |     |      | 150  | ns    |  |

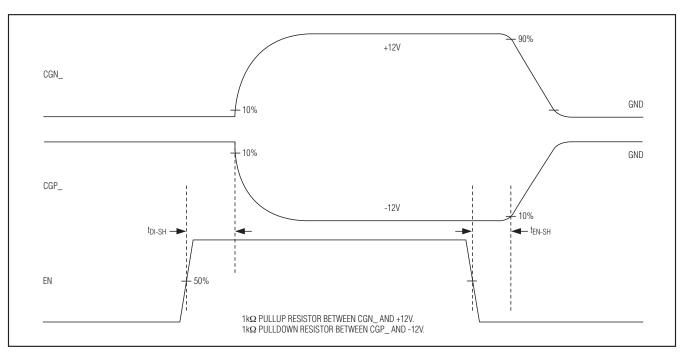

| Short Enable Time from EN                               | t=o                                                             | VPP_ = 12V, V <sub>NN</sub> _ = 0, V <sub>CC</sub> _ = +12V ± 5%,<br>VEE_ = -V <sub>CC</sub> _                                        |     |      | 1000 |       |  |

| (Figure 7)                                              | tEN_SH                                                          | V <sub>PP</sub> _ = 5V, V <sub>NN</sub> _ = 0, V <sub>CC</sub> _ = +5V ± 5%,<br>V <sub>EE</sub> _ = -V <sub>CC</sub> _                |     | 1000 |      | ns    |  |

| Short Disable Time from EN                              |                                                                 | VPP_ = 12V, V <sub>NN</sub> _ = 0, V <sub>CC</sub> _ = +12V ± 5%,<br>VEE_ = -V <sub>CC</sub> _                                        |     |      | 250  |       |  |

| (Figure 7)                                              | tDI_SH                                                          | VPP_ = 5V, V <sub>NN</sub> _ = 0, V <sub>CC</sub> _ = +5V ± 5%,<br>VEE_ = -V <sub>CC</sub> _                                          | 250 |      | ns   |       |  |

| INP_ to INN_ Overlap Tolerance                          |                                                                 |                                                                                                                                       |     | 131  |      | ns    |  |

| Crosstalk                                               |                                                                 | VPP_ = VCC_ = +5V, V <sub>NN</sub> _ = V <sub>EE</sub> _ = -5V,<br>f = 5MHz                                                           |     | 69   | _    | dB    |  |

| 2nd Harmonic Distortion                                 | 2HD                                                             | V <sub>PP</sub> _ = V <sub>NN</sub> _ = 100V, f <sub>OUT</sub> = 5MHz, V <sub>CC</sub> _ = 12V                                        |     | -48  |      | dB    |  |

| RMS Output Jitter                                       | t∪                                                              | V <sub>CC</sub> _ = 12V                                                                                                               |     | 9    |      | ps    |  |

|                                                         |                                                                 |                                                                                                                                       |     |      |      |       |  |

**Note 3:** Specifications are guaranteed for the stated global conditions, unless otherwise noted and are 100% production tested at  $T_A = +25^{\circ}C$  and  $T_A = +70^{\circ}C$ . Specifications at  $T_A = 0^{\circ}C$  are guaranteed by design.

Note 4: 100% production tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design.

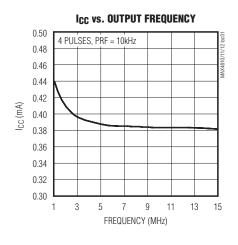

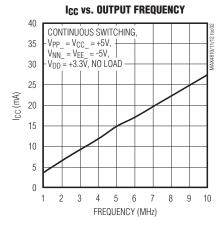

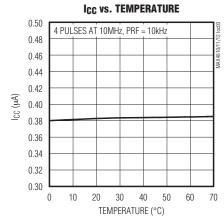

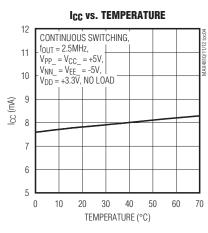

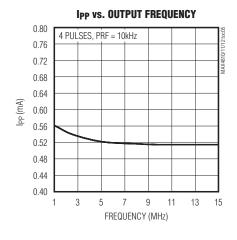

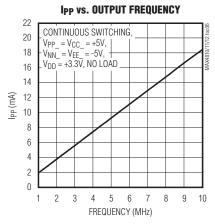

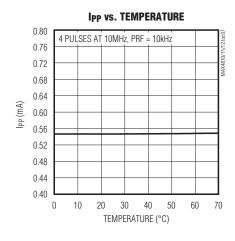

### **Typical Operating Characteristics**

$(V_{DD} = +3.3V, V_{CC\_} = +12V, V_{EE\_} = -12V, V_{SS} = -100V, V_{PP\_} = +100V, V_{NN\_} = -100V, f_{OUT} = 5MHz, T_{A} = +25^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

$(V_{DD} = +3.3V, V_{CC} = +12V, V_{EE} = -12V, V_{SS} = -100V, V_{PP} = +100V, V_{NN} = -100V, f_{OUT} = 5MHz, T_A = +25^{\circ}C$ , unless otherwise noted.)

### **Pin Description**

| PIN                      | NAME             | FUNCTION                                                                                                                                                                                                                                               |

|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | C <sub>GP1</sub> | Channel 1 High-Side Gate Input. Connect a 1nF to 10nF capacitor between C <sub>DP1</sub> and C <sub>GP1</sub> as close as possible to the device.                                                                                                      |

| 2,3                      | V <sub>PP1</sub> | Channel 1 High-Side Positive Supply Voltage Input. Bypass V <sub>PP1</sub> to GND with a 0.1µF as close as possible to the device. See the <i>Power Supplies and Bypassing</i> section. Depending on the output, additional bypassing may be required. |

| 4, 10, 33,<br>39         | N.C.             | No Connection. Not connected internally.                                                                                                                                                                                                               |

| 5                        | OP1              | Channel 1 High-Side Drain Output                                                                                                                                                                                                                       |

| 6                        | OCP1             | Channel 1 High-Side Clamp Output                                                                                                                                                                                                                       |

| 7, 15, 28,<br>36, 44, 55 | GND              | Ground                                                                                                                                                                                                                                                 |

| 8                        | OCN1             | Channel 1 Low-Side Clamp Output                                                                                                                                                                                                                        |

| 9                        | ON1              | Channel 1 Low-Side Drain Output                                                                                                                                                                                                                        |

| 11, 12                   | V <sub>NN1</sub> | Channel 1 High-Side Negative Supply Voltage Input. Bypass V <sub>NN1</sub> to GND with a 0.1µF as close as possible to the device. See the <i>Power Supplies and Bypassing</i> section. Depending on the output, additional bypassing may be required. |

| 13                       | C <sub>GN1</sub> | Channel 1 Low-Side Gate Input. Connect a 1nF to 10nF capacitor between C <sub>DN1</sub> and C <sub>GN1</sub> as close as possible to the device.                                                                                                       |

| 14                       | C <sub>DN1</sub> | Channel 1 Low-Side Driver Output. Connect a 1nF to 10nF capacitor between C <sub>DN1</sub> and C <sub>GN1</sub> as close as possible to the device.                                                                                                    |

| 16, 54                   | Vcc1             | Channel 1 Gate-Drive Supply Voltage Input. Bypass V <sub>CC1</sub> to GND with a 0.1µF as close as possible to the device. See the <i>Power Supplies and Bypassing</i> section. Depending on the output, additional bypassing may be required.         |

| 17                       | INN1             | Channel 1 Low-Side Logic Input (Table 1)                                                                                                                                                                                                               |

| 18                       | INC1             | Channel 1 Clamp Logic Input. Clamps OCP1 and OCN1 are turned on when INC1 is high and when INP1 and INN1 are low (see Table 1).                                                                                                                        |

| 19                       | INP1             | Channel 1 High-Side Logic Input (Table 1)                                                                                                                                                                                                              |

| 20                       | EN1              | Channel 1 Enable Logic Input. Drive EN1 high to enable OP1 and ON1. Pull EN1 low to turn on the gate-source short circuit (see Table 1).                                                                                                               |

| 21                       | SHDN             | Shutdown Logic Input (Table 1)                                                                                                                                                                                                                         |

| 22                       | AGND             | Analog Ground. Must be connected to common GND.                                                                                                                                                                                                        |

| 23                       | EN2              | Channel 2 Enable Logic Input. Drive EN2 high to enable OP2 and ON2. Pull EN2 low to turn on the gate-source short circuit. See Table 1.                                                                                                                |

| 24                       | INP2             | Channel 2 High-Side Logic Input (Table 1)                                                                                                                                                                                                              |

| 25                       | INC2             | Channel 2 Clamp Logic Input. Clamps OCP2 and OCN2 are turned on when INC2 is high and when INP2 and INN2 are low. See Table 1.                                                                                                                         |

| 26                       | INN2             | Channel 2 Low-Side Logic Input (Table 1)                                                                                                                                                                                                               |

| 27, 45                   | V <sub>CC2</sub> | Channel 2 Gate-Drive Supply Voltage Input. Bypass V <sub>CC2</sub> to GND with a 0.1µF as close as possible to the device. See the <i>Power Supplies and Bypassing</i> section. Depending on the output, additional bypassing may be required.         |

| 29                       | C <sub>DN2</sub> | Channel 2 Low-Side Driver Output. Connect a 1nF to 10nF capacitor between C <sub>DN2</sub> and C <sub>GN2</sub> as close as possible to the device.                                                                                                    |

| 30                       | C <sub>GN2</sub> | Channel 2 Low-Side Gate Input. Connect a 1nF to 10nF capacitor between C <sub>DN2</sub> and C <sub>GN2</sub> as close as possible to the device.                                                                                                       |

### Pin Description (continued)

| PIN    | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                  |

|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31, 32 | V <sub>NN2</sub> | Channel 2 High-Side Negative Supply Voltage Input. Bypass V <sub>NN2</sub> to GND with a 0.1µF as close as possible to the device. See the <i>Power Supplies and Bypassing</i> section. Depending on the output, additional bypassing may be required.                                                    |

| 34     | ON2              | Channel 2 Low-Side Drain Output                                                                                                                                                                                                                                                                           |

| 35     | OCN2             | Channel 2 Low-Side Clamp Output                                                                                                                                                                                                                                                                           |

| 37     | OCP2             | Channel 2 High-Side Clamp Output                                                                                                                                                                                                                                                                          |

| 38     | OP2              | Channel 2 High-Side Drain Output                                                                                                                                                                                                                                                                          |

| 40, 41 | V <sub>PP2</sub> | Channel 2 High-Side Supply Voltage Input. Bypass V <sub>PP2</sub> to GND with a 0.1µF as close as possible to the device. See the <i>Power Supplies and Bypassing</i> section. Depending on the output, additional bypassing may be required.                                                             |

| 42     | C <sub>GP2</sub> | Channel 2 High-Side Gate Input. Connect a 1nF to 10nF capacitor between CDP2 and CGP2 as close as possible to the device.                                                                                                                                                                                 |

| 43     | C <sub>DP2</sub> | Channel 2 High-Side Driver Output. Connect a 1nF to 10nF capacitor between C <sub>DP2</sub> and C <sub>GP2</sub> as close as possible to the device.                                                                                                                                                      |

| 46     | C <sub>GC2</sub> | Channel 2 High-Side Clamp Gate Input. Connect a 1nF to 10nF capacitor between C <sub>DC2</sub> and C <sub>GC2</sub> as close as possible to the device.                                                                                                                                                   |

| 47     | C <sub>DC2</sub> | Channel 2 High-Side Clamp Driver Output. Connect a 1nF to 10nF capacitor between C <sub>DC2</sub> and C <sub>GC2</sub> as close as possible to the device.                                                                                                                                                |

| 48     | V <sub>EE2</sub> | Channel 2 Negative Supply Input. $ V_{EE2}  \le V_{CC2}$ . Gate Drive Supply Voltage for the OCP clamp. Bypass $V_{EE2}$ to GND with a $0.1\mu F$ as close as possible to the device. See the <i>Power Supplies and Bypassing</i> section. Depending on the output, additional bypassing may be required. |

| 49     | V <sub>DD</sub>  | Logic Supply Voltage Input. Bypass V <sub>DD</sub> to GND with a 0.1µF as close as possible to the device. See the <i>Power Supplies and Bypassing</i> section. Depending on the output, additional bypassing may be required.                                                                            |

| 50     | V <sub>SS</sub>  | Substrate Voltage. Connect $V_{SS}$ to a voltage equal to or more negative than the more negative of $V_{NN1}$ or $V_{NN2}$ .                                                                                                                                                                             |

| 51     | V <sub>EE1</sub> | Channel 1 Negative Supply Input. $ V_{EE1}  \le V_{CC1}$ . Gate Drive Supply Voltage for the OCP clamp. Bypass $V_{EE1}$ to GND with a $0.1\mu F$ as close as possible to the device. See the <i>Power Supplies and Bypassing</i> section. Depending on the output, additional bypassing may be required. |

| 52     | C <sub>DC1</sub> | Channel 1 High-Side Clamp Driver Output. Connect a 1nF to 10nF capacitor between C <sub>DC1</sub> and C <sub>GC1</sub> as close as possible to the device.                                                                                                                                                |

| 53     | C <sub>GC1</sub> | Channel 1 High-Side Clamp Gate Input. Connect a 1nF to 10nF capacitor between C <sub>DC1</sub> and C <sub>GC1</sub> as close as possible to the device.                                                                                                                                                   |

| 56     | C <sub>DP1</sub> | Channel 1 High-Side Driver Output. Connect a 1nF to 10nF capacitor between C <sub>DP1</sub> and C <sub>GP1</sub> as close as possible to the device.                                                                                                                                                      |

| _      | EP               | Exposed Pad. EP must be connected to Vss. Do not use EP as the only Vss connection for the device.                                                                                                                                                                                                        |

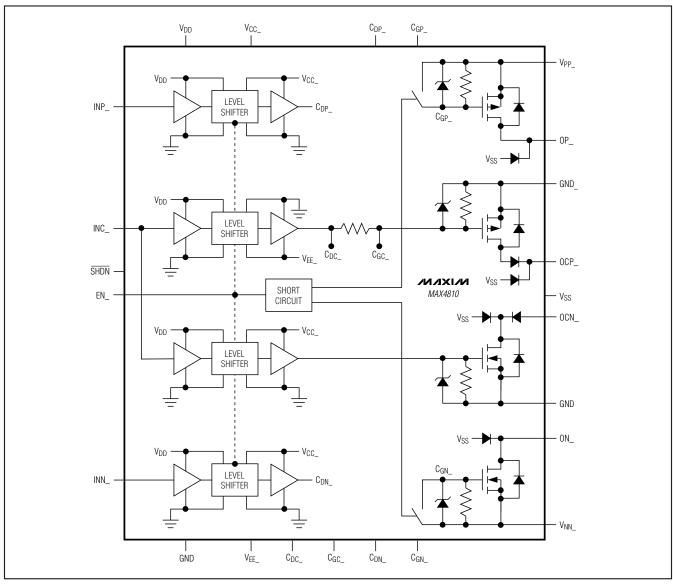

### Detailed Description

The MAX4810/MAX4811/MAX4812 are dual high-voltage, high-speed pulsers that can be independently configured for either unipolar or bipolar pulse outputs. These devices have independent logic inputs for full pulse control and independent active clamps. The clamp input, INC\_, can be set high to activate the

clamp automatically when the device is not pulsing to the positive or negative high-voltage supplies.

Logic Inputs (INP\_, INN\_, INC\_, EN\_, SHDN)

The MAX4810/MAX4811/MAX4812 have a total of nine logic input signals. SHDN controls power-up and power-down of the device. There are two sets of INP\_, INN\_, INC\_, and EN\_ signals: one for each channel. INP\_

**Table 1. Truth Table**

|      | II  | NPUTS |      |      | OUTPUTS           |                                                                  |                |                                                              |

|------|-----|-------|------|------|-------------------|------------------------------------------------------------------|----------------|--------------------------------------------------------------|

| SDHN | EN_ | INP_  | INN_ | INC_ | OP_               | ON_                                                              | OCP_,<br>OCN_  | STATE                                                        |

| 0    | Х   | Х     | Х    | 0    | High impedance    | High impedance                                                   |                |                                                              |

| 0    | Х   | Х     | Х    | 1    | High impedance    | High impedance                                                   | GND            | Powered down, INP_/INN_ disabled, gate-source short disabled |

| 1    | 0   | Х     | Х    | 0    | High impedance    | High impedance                                                   | High impedance | Powered up, INP_/INN_ disabled, gate-source short enabled    |

| 1    | 0   | Х     | Х    | 1    | High impedance    | High impedance GND Powered up, INP_/INN_ disabled, gate-senabled |                | Powered up, INP_/INN_ disabled, gate-source short enabled    |

| 1    | 1   | 0     | 0    | 0    | High impedance    |                                                                  |                | Powered up, all inputs enabled, gate-source short disabled   |

| 1    | 1   | 0     | 0    | 1    | High impedance    | High impedance                                                   | GND            | Powered up, all inputs enabled, gate-source short disabled   |

| 1    | 1   | 0     | 1    | Х    | High impedance    | V <sub>NN</sub> _                                                | High impedance | Powered up, all inputs enabled, gate-source short disabled   |

| 1    | 1   | 1     | 0    | Х    | V <sub>PP</sub> _ | High impedance                                                   | High impedance | Powered up, all inputs enabled, gate-source short disabled   |

| 1    | 1   | 1     | 1    | Х    | V <sub>PP</sub> _ | V <sub>NN</sub> _                                                | High impedance | Not allowed (3ns maximum overlap)                            |

X = Don't care.

controls the on and off states of the high side FET, INN\_controls the on and off states of the low side FET, INC\_controls the active clamp and EN\_controls the gate to source short. These signals give complete control of the output stage of each driver (see Table 1 for all logic combinations).

The MAX4810/MAX4811/MAX4812 logic inputs are CMOS logic compatible and the logic level are referenced to V<sub>DD</sub> for maximum flexibility. The low 5pF (typ) input capacitance of the logic inputs reduces loading and increases switching speed.

# High-Voltage Output Protection (MAX4811 Only)

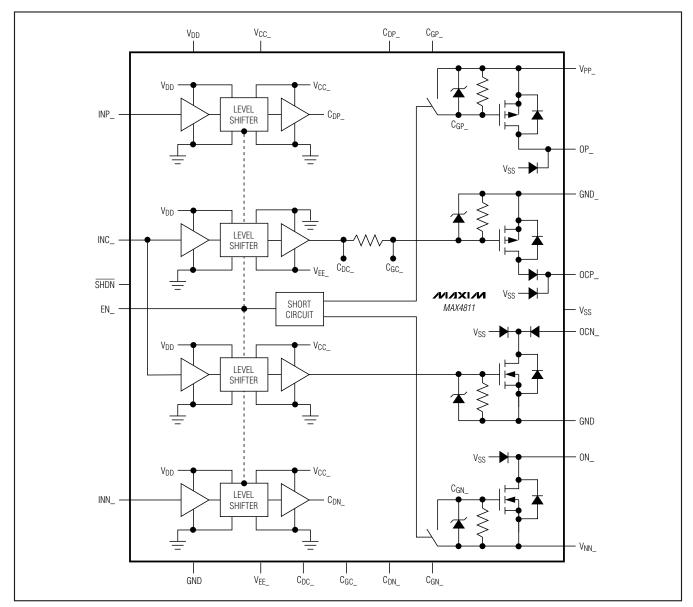

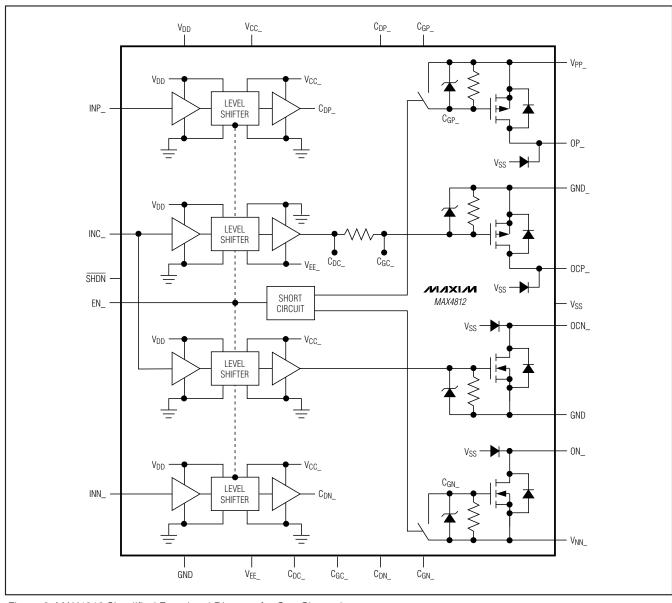

The high-voltage outputs of the MAX4811 feature an integrated overvoltage protection circuit that allows the user to implement multilevel pulsing by connecting the outputs of multiple pulser channels in parallel. Internal diodes in series with the ON\_ and OP\_ outputs prevent the body diode of the high-side and low-side FETs from switching on when a voltage greater than V<sub>NN\_</sub> or V<sub>PP\_</sub> is present on the output. See Figure 2.

#### **Active Clamps**

The MAX4810/MAX4811/MAX4812 feature an active clamp circuit to improve pulse quality and reduce 2nd harmonic output. The clamp circuit consists of an Nchannel (DC-coupled) and a P-channel (AC and DC delay coupled) high-voltage FETs that are switched on or off by the logic clamp input (INC\_). The MAX4810/ MAX4811 feature protected clamp devices, allowing the clamp circuit to be used in bipolar pulsing circuits (see Figures 1 and 2). A diode in series with the OCN\_ output prevents the body diode of the low-side FET from turning on when a voltage lower than GND is present. Another diode in series with the OCP\_ output prevents the body diode of the high-side FET from turning on when a voltage higher than ground is present. The MAX4812 does not have diode protection on the clamp outputs. Thus, the device is suitable for use in circuits where only unipolar pulsing is required.

The user can connect the active clamp input (INC\_) to a logic-high voltage and drive only the INP\_ and INN\_ inputs to minimize the number of signals used to drive the

10 \_\_\_\_\_\_ /I/XI/M

<sup>0 =</sup> Logic-low.

<sup>1 =</sup> Logic-high.

device. In this case, whenever both the INP\_ and INN\_ inputs are low and the INC\_ input is high, the active clamp circuit pulls the output to GND through the OCP\_ and OCN\_ outputs (see Table 1 for more information).

# Power-Supply Ramping and Gate-Source Short Circuit

The MAX4810/MAX4811/MAX4812 include a gate-source short circuit that is controlled by the enable input (EN\_). When  $\overline{SHDN}$  is high and EN is low, a  $60\Omega$  switch shorts together the gate and source of the high-side output FET. At the same time, a similar switch shorts the gate and source of the low-side output FET (Table 1). The gate-source short circuit prevents accidental turn-on of the output FETs due to the ramping voltage on VPP\_ and VNN\_, and allows for faster ramping rates and smaller delay times between pulsing modes.

#### **Shutdown Mode**

SHDN is common to both channel 1 and channel 2 and powers up or down the device. Drive SHDN low to power down all internal circuits (except the clamp circuits). When SHDN is low, the device is in the lowest power state (1µA) and the gate-source short circuit is disabled. The device takes 1µs (typ) to become active when SHDN is disabled.

#### **Thermal Protection**

A thermal shutdown circuit with a typical threshold of  $+150^{\circ}\text{C}$  prevents damage due to excessive power dissipation. When the junction temperature exceeds T<sub>J</sub> =  $+150^{\circ}\text{C}$ , all outputs are disabled. Normal operation typically resumes after the IC's junction temperature drops below  $+130^{\circ}\text{C}$ .

## Applications Information

#### **AC-Coupling Capacitor Selection**

The value of all AC-coupling capacitors (between CDP\_ and CGP, and between CDN\_ and CGN\_) should be between 1nF to 10nF. The voltage rating of the capacitor should be at least as high as VPP\_. The capacitors should be placed as close as possible to the device.

Because INP\_ and part of INC\_ are AC-coupled to the output devices, they cannot be driven high indefinitely when the device is active.

#### **Power Dissipation**

The power dissipation of the MAX4810/MAX4811/ MAX4812 consists of three major components caused by the current consumption from  $V_{CC}$ ,  $V_{PP}$ , and  $V_{NN}$ . The sum of these components ( $P_{VCC}$ ,  $P_{VPP}$  and

P<sub>VNN</sub>\_) must be kept below the maximum power-dissipation limit. See the *Typical Operating Characteristics* section for more information on typical supply currents versus switching frequencies.

The device consumes most of the supply current from  $V_{CC}$  supply to charge and discharge internal nodes such as the gate capacitance of the high-side FET (C<sub>P</sub>) and the low-side FET (C<sub>N</sub>). Neglecting the small quiescent supply current and a small amount of current used to charge and discharge the capacitances at the internal gate clamp FETs, the power consumption can be estimated as follows:

$$\begin{aligned} P_{VCC} &= \left[ \left( C_{N} \times V_{CC} \right)^{2} \times f_{|N} \right) + \left( C_{P} \times V_{CC} \right)^{2} \times f_{|N} \right] \times \left( BRF \times BTD \right) \\ f_{|N} &= f_{|NN} + f_{|NP} \end{aligned}$$

Where  $f_{INN}$  and  $f_{INP}$  are the switching frequency of the inputs INN, INP respectively, and where BRF is the burst repitition frequency and BTD is the burst time duration. The typical value of the gate capacitances of the power FET are  $C_N = 0.2nF$ ,  $C_P = 0.4nF$ .

For an output load that has a resistance of  $R_L$  and capacitance of  $C_L$ , the MAX4810/MAX4811/MAX4812 power dissipation can be estimated as follows (assume square wave output and neglect the resistance of the switches):

$$\mathsf{P}_{\mathsf{VPP}} = \left\{ \left[ \left( \mathsf{C}_{\mathsf{O}} + \mathsf{C}_{\mathsf{L}} \right) \times \mathfrak{f}_{\mathsf{IN}} \times \left( \mathsf{V}_{\mathsf{PP}_{-}} - \mathsf{V}_{\mathsf{NN}_{-}} \right)^{2} \right] + \left[ \frac{\mathsf{V}_{\mathsf{PP}_{-}}^{2}}{\mathsf{R}_{\mathsf{L}}} \times \frac{1}{2} \right] \times \left( \mathsf{BRF} \times \mathsf{BTD} \right) \right\}$$

where Co is the output capacitance of the device.

#### **Power Supplies and Bypassing**

The MAX4810/MAX4811/MAX4812 operate from independent supply voltage sets (only V<sub>DD</sub> and V<sub>SS</sub> are common to both channels). The logic input circuit operates from a +2.7V to +6V single supply (V<sub>DD</sub>). The level-shift driver dual supplies, V<sub>CC</sub>/V<sub>EE</sub>\_ operate from  $\pm 4.75V$  to  $\pm 12.6V$ .

The V<sub>PP</sub>\_/V<sub>NN</sub>\_ high-side and low-side supplies are driven from a single positive supply up to +220V, from a single negative supply up to -200V, or from  $\pm 110$ V dual supplies. Either V<sub>PP</sub>\_ or V<sub>NN</sub>\_ can be set at 0. Bypass each supply input to ground with a 0.1 $\mu$ F capacitor as close as possible to the device.

Depending on the load of the input, additional bypassing may be needed to keep the output of  $V_{NN}$  and  $V_{PP}$  stable during output transitions. For example, with

Figure 1. MAX4810 Simplified Functional Diagram for One Channel

$C_{OUT}$  = 100pF and  $R_{OUT}$  = 100 $\Omega$  load, additional 10µF (typ) capacitor is recommended. VSS is the substrate voltage and must be connected to a voltage equal to or more negative than the more negative voltage of  $V_{NN1}$  or  $V_{NN2}.$

#### **Exposed Pad and Layout Concerns**

The MAX4810/MAX4811/MAX4812 provide an exposed pad (EP) underneath the TQFN package for improved thermal performance. EP is internally connected to Vss. Connect EP to Vss externally and do not run traces

under the package to avoid possible short circuits. To aid heat dissipation, connect EP to a similarly sized pad on the component side of the PCB. This pad should be connected through to the solder-side copper by several plated holes to a large heat spreading copper area to conduct heat away from the device.

The MAX4810/MAX4811/MAX4812 high-speed pulsers require low-inductance bypass capacitors to their supply inputs. High-speed PCB trace design practices are recommended. Pay particular attention to minimize

\_\_ /VIXI/VI

Figure 2. MAX4811 Simplified Functional Diagram for One Channel

trace lengths and use sufficient trace width to reduce inductance. Use of surface-mount components is recommended.

#### **Supply Sequencing**

Vss must be lower than or equal to the more negative voltage of  $V_{NN1}$  or  $V_{NN2}$  at all times. No other power-supply sequencing is required for the MAX4810/MAX4811/MAX4812.

#### **Typical Application Circuits**

Figures 8, 9, and 10 show typical applications for the MAX4810/MAX4811/MAX4812. Figure 8 shows the MAX4810 used in a bipolar pulsing connection. Figure 9 shows the MAX4811 in a five-level pulsing application, and Figure 10 shows the MAX4812 used in a unipolar application.

Figure 3. MAX4812 Simplified Functional Diagram for One Channel

Figure 4. Detailed Timing ( $R_L = 100\Omega$ ,  $C_L = 100pF$ )

Figure 5. Enable Timing ( $R_L = 100\Omega$ ,  $C_L = 100pF$ )

Figure 6. Active Clamp Timing

Figure 7. Short-Circuit Timing

Figure 8. MAX4810: Dual Bipolar Pulsing, ±100V, GND

Figure 9. MAX4811: Five-Level Pulsing, ±100V, ±50V, GND

Figure 10. MAX4812: Dual Unipolar Pulsing, +100V, GND

## Package Information

For the latest package outline information and land patterns, go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 56 TQFN      | T5677-1      | <u>21-0144</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

is a registered trademark of Maxim Integrated Products, Inc.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

MAX4810CTN+ MAX4810CTN+T