### General Description

The MAX4588 low-voltage, dual 4-channel multiplexer is designed for RF and video signal processing at frequencies up to 180MHz in  $50\Omega$  and  $75\Omega$  systems. A flexible digital interface allows control of on-chip functions through either a parallel interface or an SPI™/ MICROWIRE™ serial port.

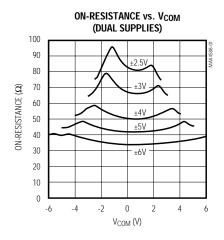

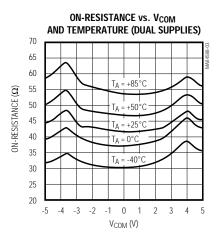

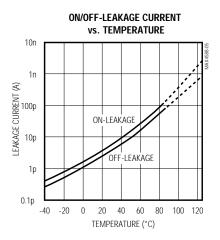

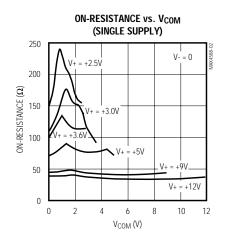

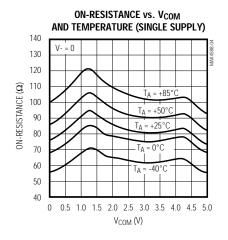

Each channel of the MAX4588 is designed using a "T" switch configuration, ensuring excellent high-frequency off-isolation. The MAX4588 has low on-resistance of  $60\Omega$  max, with an on-resistance match across all channels of  $4\Omega$  max. Additionally, on-resistance is flat across the specified signal range ( $2\Omega$  max). The offleakage current is under 1nA at  $T_A = +25$ °C, and less than 10nA at  $T_A = +85$ °C.

The MAX4588 operates from single +2.7V to +12V or dual ±2.7V to ±6V supplies. When operating with a +5V supply, the inputs maintain TTL- and CMOS-level compatibility. The MAX4588 is available in 28-pin narrow DIP, wide SO, and space-saving SSOP packages.

## **Applications**

RF Switching Automatic Test Equipment Video Signal Routing Networking High-Speed Data Acquisition

## **Features**

- ♦ Low Insertion Loss: -2.5dB up to 100MHz

- ♦ High Off-Isolation: -74dB at 10MHz

- ♦ Low Crosstalk: -70dB up to 10MHz

- ♦ 16MHz -0.1dB Signal Bandwidth

- ♦ 180MHz -3dB Signal Bandwidth

- ♦ 60Ω (max) On-Resistance with ±5V Supplies

- ♦ 4Ω (max) On-Resistance Matching with ±5V

- ♦ 2Ω (max) On-Resistance Flatness with ±5V Supplies

- ♦ +2.7V to +12V Single Supply ±2.7V to ±6V Dual Supplies

- ♦ Low Power Consumption: <20μW

- ♦ Rail-to-Rail<sup>®</sup>, Bidirectional Signal Handling

- **♦** Parallel or SPI/MICROWIRE-Compatible Serial Interface

- ♦ >±2kV ESD Protection per Method 3015.7

- ♦ TTL/CMOS-Compatible Inputs with V<sub>L</sub> = +5V

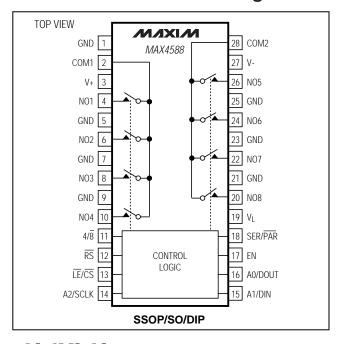

### Pin Configuration

## **Ordering Information**

| PART       | TEMP. RANGE    | PIN-PACKAGE           |

|------------|----------------|-----------------------|

| MAX4588CAI | 0°C to +70°C   | 28 SSOP               |

| MAX4588CWI | 0°C to +70°C   | 28 Wide SO            |

| MAX4588CPI | 0°C to +70°C   | 28 Narrow Plastic DIP |

| MAX4588EAI | -40°C to +85°C | 28 SSOP               |

| MAX4588EWI | -40°C to +85°C | 28 Wide SO            |

| MAX4588EPI | -40°C to +85°C | 28 Narrow Plastic DIP |

| MAX4588EPI | -40°C to +85°C | 28 Narrow Plastic DIP |

SPI is a trademark of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp. Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to GND) V+0.3V to +13.0V                                 | ESD per Method 3015.7±2kV<br>Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| V <sub>L</sub> 0.3V to (V+ + 0.3V) or 7V (whichever is lower) V13.0V to +0.3V | SSOP (derate 9.52mW/°C above +70°C)                                                |

| V+ to V0.3V to +13.0V                                                         | Plastic DIP (derate 14.29mW/°C above +70°C)1.14W                                   |

| V <sub>NO</sub> , V <sub>COM</sub> (Note 1)(V 0.3V) to (V+ + 0.3V)            | Operating Temperature Ranges                                                       |

| 4/8, RS, LE/CS, A2/SCLK, A1/DIN,                                              | MAX4588C_I0°C to +70°C                                                             |

| A0/DOUT, EN, SER/PAR to GND0.3V to (V+ + 0.3V)                                | MAX4588E_ I40°C to +85°C                                                           |

| Continuous Current into Any Terminal±20mA                                     | Storage Temperature Range65°C to +150°C                                            |

| Peak Current into Any Terminal                                                | Lead Temperature (soldering, 10sec)+300°C                                          |

| (pulsed at 1ms, 10% duty cycle)±40mA                                          |                                                                                    |

**Note 1:** Voltages on these pins exceeding V+ or V- are clamped by internal diodes. Limit forward diode current to maximum current rating.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS—Dual Supplies**

$(V + = V_L = +4.5V \text{ to } +5.5V, V_{-} = -4.5V \text{ to } -5.5V, V_{INH} = +2.4V, V_{INL} = +0.8V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$ ,  $V_{+} = V_L = +5V$ ,  $V_{-} = -5V$ .) (Note 2)

| PARAMETER                                     | SYMBOL                 | CONDITIONS                                                    | TA            | MIN                | TYP  | MAX         | UNITS |  |

|-----------------------------------------------|------------------------|---------------------------------------------------------------|---------------|--------------------|------|-------------|-------|--|

| ANALOG SWITCH                                 | •                      |                                                               |               |                    |      |             |       |  |

| Analog Signal Range<br>(Note 3)               | V <sub>COM_</sub> ,    |                                                               |               | V-                 |      | V+          | V     |  |

| On-Resistance                                 | Ron                    | $V + = 5V, V - = -5V, V_{NO} = \pm 2V,$ $I_{COM} = 4mA$       | +25°C<br>C, E |                    | 40   | 60<br>75    | Ω     |  |

| On Desistant Matala Datum                     |                        |                                                               | +25°C         |                    | 1    | 4           |       |  |

| On-Resistance Match Between Channels (Note 4) | ΔRon                   | $V + = 5V$ , $V - = 5V$ , $V_{NO} = \pm 2V$ , $I_{COM} = 4mA$ | C, E          |                    | 1    | <del></del> | Ω     |  |

| On-Resistance Flatness                        | 5                      | V = 5V: V = 5V: VNO = 1V 0 1V:                                | +25°C         |                    | 0.5  | 2.5         | -     |  |

| (Note 5)                                      | R <sub>FLAT</sub> (ON) | I <sub>COM</sub> _ = 1mA                                      | C, E          |                    |      | 3           | Ω     |  |

| NO_ Off-Leakage Current                       | luc (0.55)             | V+ = 5.5V, V- = -5.5V,                                        | +25°C         | -1                 | 0.01 | 1           | nA    |  |

| (Note 6)                                      | INO_(OFF)              | $V_{COM} = \pm 4.5V, V_{NO} = \mp 4.5V$                       | C, E          | -10                |      | 10          | IIA   |  |

| COM_ Off-Leakage Current                      | ICOM_(OFF)             | V+ = 5.5V, V- = -5.5V,                                        | +25°C         | -2                 | 0.01 | 2           | nA    |  |

| (Note 6)                                      |                        | $V_{COM} = \pm 4.5V, V_{NO} = \mp 4.5V$                       | C, E          | -20                |      | 20          | IIA   |  |

| COM_ On-Leakage Current                       | ICOM (ON)              | $V + = 5.5V$ , $V - = -5.5V$ , $V_{COM} = \pm 4.5V$ ,         | +25°C         | -2                 | 0.01 | 2           | nA    |  |

| (Note 6)                                      | ICOM_(ON)              | $V_{NO}$ = ±4.5V or floating                                  | C, E          | -20                |      | 20          | 1 IIA |  |

| LOGIC INPUTS (4/8, RS, LE/CS                  | , A2/SCLK,             | A1/DIN, A0/DOUT, EN, SER/PAR)                                 |               |                    |      |             |       |  |

| Input Logic Threshold High                    | VINH                   |                                                               | C, E          | 2.4                | 1.7  |             | V     |  |

| Input Logic Threshold Low                     | VINL                   |                                                               | C, E          |                    | 1.5  | 0.8         | V     |  |

| Input Threshold Hysteresis                    |                        |                                                               |               |                    | 0.2  |             | V     |  |

| Input Current                                 | I <sub>IN</sub>        | V <sub>IN</sub> _ = 0 or V <sub>L</sub>                       | C, E          | -1                 | 0.03 | 1           | μΑ    |  |

| LOGIC OUTPUT (SERIAL INTE                     | RFACE)                 |                                                               |               |                    |      |             |       |  |

| DOUT Logic Low Output                         | V <sub>OL</sub>        | I <sub>SINK</sub> = 3.2mA                                     | C, E          |                    |      | 0.4         | V     |  |

| DOUT Logic High Output                        | V <sub>OH</sub>        | I <sub>SOURCE</sub> = -1mA                                    | C, E          | V <sub>L</sub> - 1 |      |             | V     |  |

## **ELECTRICAL CHARACTERISTICS—Dual Supplies (continued)**

$(V+ = V_L = +4.5V \text{ to } +5.5V, V- = -4.5V \text{ to } -5.5V, V_{INH} = +2.4V, V_{INL} = +0.8V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$ ,  $V+ = V_L = +5V$ , V- = -5V.) (Note 2)

| PARAMETER                                           | SYMBOL                | COND                                                            | ITIONS                   | TA      | MIN | TYP | MAX  | UNITS  |  |

|-----------------------------------------------------|-----------------------|-----------------------------------------------------------------|--------------------------|---------|-----|-----|------|--------|--|

| SWITCH DYNAMIC CHARACTE                             | RISTICS               |                                                                 |                          | 1       |     |     |      |        |  |

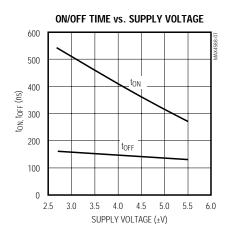

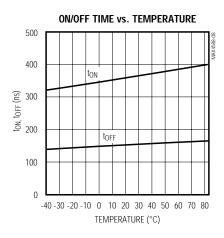

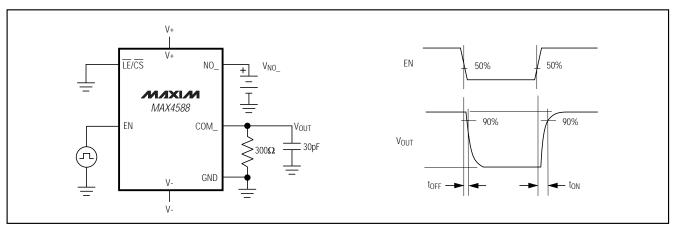

| Turne Or Time                                       |                       | $V_{NO} = 3V, V_{+} = 4$                                        | 1.5V, V- = -4.5V,        | +25°C   |     | 380 | 550  |        |  |

| Turn-On Time                                        | ton                   | Figure 1                                                        |                          | C, E    |     |     | 600  | ns     |  |

| Turn-Off Time                                       | torr                  | V <sub>NO</sub> _ = 3V, V+ = 4                                  | 1.5V, V- = -4.5V,        | +25°C   |     | 150 | 300  | nc     |  |

| Turn-On Time                                        | toff                  | Figure 1                                                        | Figure 1                 |         |     |     | 350  | ns     |  |

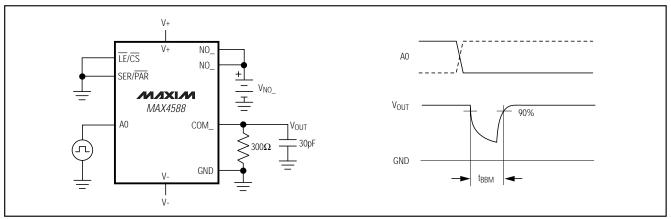

| Break-Before-Make Time Delay (Note 3)               | t <sub>BBM</sub>      | $V_{NO_{-}} = \pm 3V, V_{+} = Figure 2$                         | 5.5V, V- = -5.5V,        | C, E    | 10  | 180 |      | ns     |  |

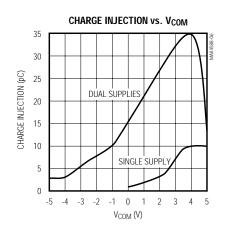

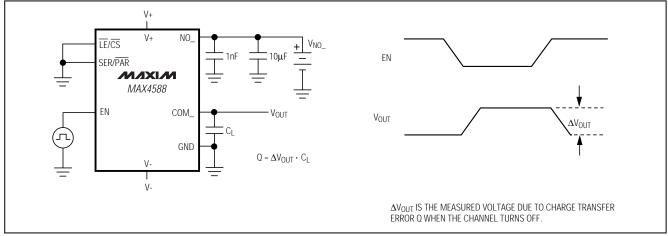

| Charge Injection                                    | Q                     | C <sub>L</sub> = 1.0nF, V <sub>NO</sub> _<br>Figure 3           | = 0, R <sub>S</sub> = 0, | +25°C   |     | 15  |      | рС     |  |

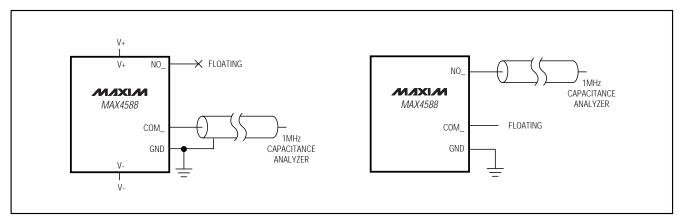

| NO_ Off-Capacitance                                 | C <sub>NO</sub> (OFF) | $V_{NO} = 0$ , $f_{IN} = 1$                                     |                          | +25°C   |     | 2   |      | pF     |  |

| COM_ Off-Capacitance                                | CCOM_(OFF)            | $V_{COM_{-}} = 0$ , $f_{IN} = 1$                                | MHz, Figure 4            | +25°C   |     | 4   |      | pF     |  |

| COM_ On-Capacitance                                 | CCOM_(ON)             | $V_{COM} = 0$ , $f_{IN} = 1$                                    | MHz, Figure 4            | +25°C   |     | 7   |      | pF     |  |

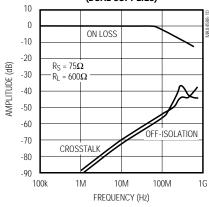

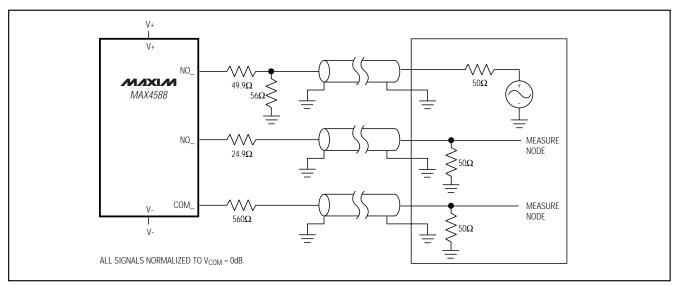

| Off-Isolation (Note 7)                              | V <sub>ISO</sub>      | V <sub>NO_</sub> = 1V <sub>RMS</sub> , f = all channels off, Fi | : 10MHz,<br>gure 5       | +25°C   |     | -74 |      | dB     |  |

| Channel-to-Channel Crosstalk                        | VcT                   | V <sub>NO</sub> _ = 1V <sub>RMS</sub> , f =                     | 10MHz, Figure 5          | +25°C   |     | -70 |      | dB     |  |

| -3dB Bandwidth                                      | BW                    | Figure 5                                                        | 4-channel mode           | +25°C   |     | 180 |      | MHz    |  |

| -3db balldwidth                                     | DVV                   | rigure 5                                                        | 8-channel mode           | 1 +25 C |     | 140 |      | IVIIIZ |  |

| -0.1dB Bandwidth                                    | BW                    | Figure 5                                                        | 4-channel mode           | +25°C   |     | 16  |      | MHz    |  |

| 0. Tab Banawatii                                    | DW.                   | rigare 5                                                        | 8-channel mode           | 123 0   |     | 11  |      | IVIIIZ |  |

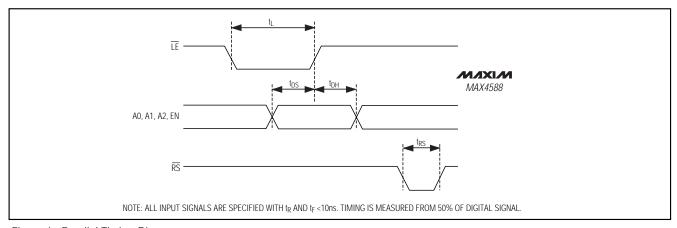

| PARALLEL-INTERFACE TIMIN                            | G                     |                                                                 |                          |         |     |     |      |        |  |

| A_, EN to LE Rise Setup Time                        | t <sub>DS</sub>       | Figure 6                                                        |                          | C, E    | 80  |     |      | ns     |  |

| A_, EN to $\overline{\text{LE}}$ Rise Hold Time     | tDH                   | Figure 6                                                        |                          | C, E    | 0   |     |      | ns     |  |

| LE Low Pulse Width                                  | tL                    | Figure 6                                                        |                          | C, E    | 80  |     |      | ns     |  |

| RS Low Pulse Width                                  | t <sub>RS</sub>       | Figure 6                                                        |                          | C, E    | 80  |     |      | ns     |  |

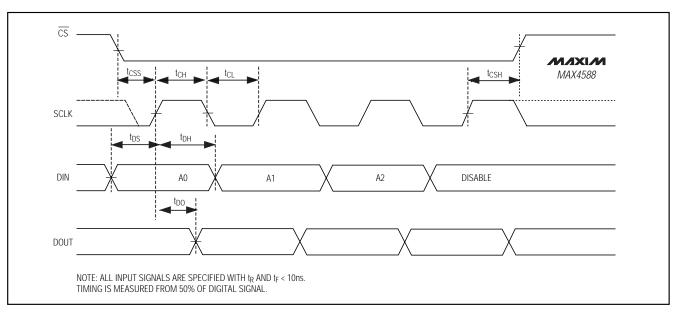

| SERIAL-INTERFACE TIMING                             |                       |                                                                 |                          |         |     |     |      |        |  |

| Operating Frequency                                 | fCLK                  | Figure 7                                                        |                          | C, E    |     |     | 6.25 | MHz    |  |

| SCLK Pulse Width High                               | t <sub>CH</sub>       | Figure 7                                                        |                          | C, E    | 80  |     |      | ns     |  |

| SCLK Pulse Width Low                                | t <sub>CL</sub>       | Figure 7                                                        |                          | C, E    | 80  |     |      | ns     |  |

| DIN to SCLK Rise Setup Time                         | t <sub>DS</sub>       | Figure 7                                                        |                          | C, E    | 60  |     |      | ns     |  |

| DIN to SCLK Rise Hold Time                          | tDH                   | Figure 7                                                        |                          | C, E    | 0   |     |      | ns     |  |

| $\overline{\text{CS}}$ Fall to SCLK Rise Setup Time | t <sub>CSS0</sub>     | Figure 7                                                        | C, E                     | 50      |     |     | ns   |        |  |

| SCLK Rise to DOUT Valid                             | t <sub>DO</sub>       | $C_L = 50pF$ , Figure                                           | C, E                     |         |     | 150 | ns   |        |  |

| $\overline{\text{CS}}$ Rise to SCLK Rise Hold Time  | tCSH1                 | Figure 7                                                        |                          | C, E    | 0   |     |      | ns     |  |

| CS Rise to SCLK Rise Setup<br>Time                  | tcss1                 | Figure 7                                                        | C, E                     | 80      |     |     | ns   |        |  |

| CS Fall to SCLK Rise Hold Time                      | tcss1                 | Figure 7                                                        |                          | C, E    | 80  |     |      | ns     |  |

| RS Low Pulse Width                                  | t <sub>RS</sub>       | Figure 6                                                        |                          | C, E    | 80  |     |      | ns     |  |

|                                                     |                       |                                                                 |                          |         |     |     |      |        |  |

### **ELECTRICAL CHARACTERISTICS—Dual Supplies (continued)**

$(V+=V_L=+4.5V\ to\ +5.5V,\ V-=-4.5V\ to\ -5.5V,\ V_{INH}=+2.4V,\ V_{INL}=+0.8V,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C,\ V+=V_L=+5V,\ V-=-5V.$ ) (Note 2)

| PARAMETER                     | SYMBOL | CONDITIONS                               | TA    | MIN  | TYP    | MAX | UNITS |

|-------------------------------|--------|------------------------------------------|-------|------|--------|-----|-------|

| POWER SUPPLY                  |        |                                          |       |      |        |     |       |

| Power-Supply Range            | V+, V- |                                          |       | ±2.7 |        | ±6  | V     |

| rower-supply Karige           | VL     |                                          |       | 2.7  |        | V+  | V     |

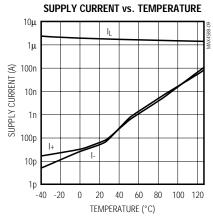

| V+ Supply Current             | 1+     | V+ = 5.5V, V- = -5.5V                    | +25°C | -1   | 0.0001 | 1   | μА    |

| v+ Supply Current             | 1+     | V+ = 5.5V, V- = -5.5V                    | C, E  | -10  |        | 10  |       |

| V - Supply Current            | 1      | V+ = 5.5V, V- = -5.5V                    | +25°C | -1   | 0.0001 | 1   | μА    |

| v - Supply Current            | l-     | V+ = 5.5V, V- = -5.5V                    | C, E  | -10  |        | 10  | μΑ    |

| V <sub>L</sub> Supply Current | ΙL     | $V_L = 5.5V$ , all $V_{IN} = 0$ or $V_L$ | C, E  | -10  | 2      | 10  | μΑ    |

## **ELECTRICAL CHARACTERISTICS—Single +5V Supply**

$(V+=V_L=+4.5V$  to +5.5V, V-=0,  $V_{INH}=+2.4V$ ,  $V_{INL}=+0.8V$ ,  $T_A=T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A=+25^{\circ}C$ ,  $V+=V_L=+5V$ .) (Note 2)

| PARAMETER                    | SYMBOL                 | CONDITIONS                                            | TA    | MIN                | TYP   | MAX | UNITS |

|------------------------------|------------------------|-------------------------------------------------------|-------|--------------------|-------|-----|-------|

| ANALOG SWITCH                | <b>'</b>               |                                                       | 1     |                    |       |     |       |

| Analog Signal Range (Note 3) | V <sub>COM_</sub> ,    |                                                       |       | 0                  |       | V+  | V     |

| On-Resistance                |                        | V. EV V. 2V last 4mA                                  | +25°C |                    | 80    | 120 | Ω     |

| On-Resistance                | Ron                    | $V + = 5V$ , $V_{NO} = 3V$ , $I_{COM} = 4mA$          | C, E  |                    |       | 150 | ] 12  |

| On-Resistance Match Between  | ΔRON                   | V+ = 5V, V <sub>NO</sub> = 3V, I <sub>COM</sub> = 4mA | +25°C |                    | 1     | 8   | Ω     |

| Channels (Note 4)            | ARON                   | V+ = 3V, VNO_ = 3V, ICOM_ = 4IIIA                     | C, E  |                    |       | 10  | 32    |

| On-Resistance Flatness       | R <sub>FLAT</sub> (ON) | $V + = 5V, I_{COM} = 4mA,$                            | +25°C |                    | 4     | 10  | Ω     |

| (Note 5)                     | TFLAT(ON)              | $V_{NO} = 2V, 3V, 4V$                                 | C, E  |                    |       | 12  | 32    |

| NO_ Off Leakage Current      | INO (OFF)              | $V + = 5.5V; V_{COM} = 4.5V, 1V;$                     | +25°C | -1                 | 0.005 | 1   | nA    |

| (Notes 6, 9)                 | I <sub>NO_(OFF)</sub>  | $V_{NO_{-}} = 1V, 4.5V$                               | C, E  | -10                |       | 10  | 117 ( |

| COM_ Off Leakage Current     | ICOM(OFF)              | V+ = 5.5V; V <sub>COM</sub> _ = 4.5V, 1V;             | +25°C | -2                 | 0.005 | 2   | nA    |

| (Notes 6, 9)                 |                        | $V_{NO} = 1V, 4.5V$                                   | C, E  | -20                |       | 20  |       |

| COM_ On Leakage Current      | Icon (ON)              | $V + = 5.5V; V_{COM} = 4.5V, 1V;$                     | +25°C | -2                 | 0.005 | 2   | nA    |

| (Notes 6, 9)                 | ICOM_(ON)              | $V_{NO} = 4.5V$ , 1V, or floating                     | C, E  | -20                |       | 20  | IIA   |

| LOGIC INPUTS (4/8, RS, LE/C  | S, A2/SCLK,            | A1/DIN, A0/DOUT, EN, SER/PAR)                         |       |                    |       |     |       |

| Input Logic Threshold High   | V <sub>INH</sub>       |                                                       | C, E  | 2.4                | 1.7   |     | V     |

| Input Logic Threshold Low    | VINL                   |                                                       | C, E  |                    | 1.5   | 0.8 | V     |

| Input Threshold Hysteresis   |                        |                                                       |       |                    | 0.2   |     | V     |

| Input Current                | I <sub>IN</sub>        | $V_{IN} = 0$ or $V_L$                                 | C, E  | -1                 |       | 1   | μΑ    |

| LOGIC OUTPUT (SERIAL INTE    | RFACE)                 |                                                       |       |                    |       |     |       |

| DOUT Logic Low Output        | V <sub>OL</sub>        | I <sub>SINK</sub> = 3.2mA                             | C, E  |                    |       | 0.4 | V     |

| DOUT Logic High Output       | Voh                    | ISOURCE = -1mA                                        | C, E  | V <sub>L</sub> - 1 |       |     | V     |

## **ELECTRICAL CHARACTERISTICS—Single +5V Supply (continued)**

$(V+ = V_L = +4.5V \text{ to } +5.5V, V- = 0, V_{INH} = +2.4V, V_{INL} = +0.8V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$ ,  $V+ = V_L = +5V$ .) (Note 2)

| PARAMETER                                       | SYMBOL           | СО                                                       | NDITIONS                              | TA      | MIN | TYP | MAX  | UNITS   |  |

|-------------------------------------------------|------------------|----------------------------------------------------------|---------------------------------------|---------|-----|-----|------|---------|--|

| SWITCH DYNAMIC CHARACTE                         | RISTICS          | ı                                                        |                                       |         |     |     |      | 1       |  |

| Turn On Times                                   | +                |                                                          | 4 EV. Eiguro 1                        | +25°C   |     | 550 | 800  | 200     |  |

| Turn-On Time                                    | ton              | $VNO_{-} = 3V, V+$                                       | = 4.5V, Figure 1                      | C, E    |     |     | 900  | ns      |  |

| Turn Off Times                                  | +                | Maria 201 Maria                                          | 4 EV. Figure 1                        | +25°C   |     | 150 | 300  | no.     |  |

| Turn-Off Time                                   | toff             | VNO_ = 3V, V+                                            | $V_{NO} = 3V, V_{+} = 4.5V, Figure 1$ |         |     |     | 350  | ns      |  |

| Break-Before-Make Time Delay (Note 3)           | t <sub>BBM</sub> | V <sub>NO</sub> _ = 3V, V+                               | = 5.5V, Figure 2                      | C, E    | 10  | 200 |      | ns      |  |

| Charge Injection                                | Q                | C <sub>L</sub> = 1.0nF, V <sub>N</sub><br>Figure 3       | o_ = 2.5V, R <sub>S</sub> = 0,        | +25°C   |     | 5   |      | рС      |  |

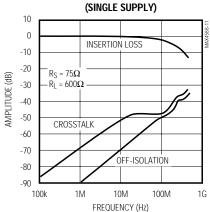

| Off-Isolation                                   | V <sub>ISO</sub> | V <sub>NO</sub> _ = 1V <sub>RMS</sub> , all channels off | f = 10MHz,<br>Figure 5                | +25°C   |     | -65 |      | dB      |  |

| Channel-to-Channel Crosstalk                    | V <sub>C</sub> T | V <sub>NO</sub> _ = 1V <sub>RMS</sub>                    | f = 10MHz, Figure 5                   | +25°C   |     | -70 |      | dB      |  |

| 2dD Dandwidth                                   | DW               | Figure F                                                 | 4-channel mode                        | +25°C   |     | 100 |      | N 41 1- |  |

| -3dB Bandwidth                                  | BW               | Figure 5                                                 | 8-channel mode                        | 1 +25 C |     | 75  |      | MHz     |  |

| -0.1dB Bandwidth                                | BW               | Figure 5                                                 | 4-channel mode                        | +25°C   |     | 10  |      | MHz     |  |

| -0. IOB Ballowidti                              | DVV              | rigule 5                                                 | 8-channel mode                        | 1 +25 C |     | 7   |      | IVITZ   |  |

| PARALLEL-INTERFACE TIMING                       | G                |                                                          |                                       |         |     |     |      |         |  |

| A_, EN to LE Rise Setup Time                    | t <sub>DS</sub>  | Figure 6                                                 |                                       | C, E    | 80  |     |      | ns      |  |

| A_, EN to $\overline{\text{LE}}$ Rise Hold Time | tDH              | Figure 6                                                 |                                       | C, E    | 0   |     |      | ns      |  |

| LE Low Pulse Width                              | tL               | Figure 6                                                 |                                       | C, E    | 80  |     |      | ns      |  |

| RS Low Pulse Width                              | t <sub>RS</sub>  | Figure 6                                                 |                                       | C, E    | 80  |     |      | ns      |  |

| SERIAL-INTERFACE TIMING                         |                  |                                                          |                                       |         |     |     |      |         |  |

| Operating Frequency                             | fcLK             | Figure 7                                                 |                                       | C, E    |     |     | 6.25 | MHz     |  |

| SCLK Pulse Width High                           | tcH              | Figure 7                                                 |                                       | C, E    | 80  |     |      | ns      |  |

| SCLK Pulse Width Low                            | t <sub>CL</sub>  | Figure 7                                                 |                                       | C, E    | 80  |     |      | ns      |  |

| DIN to SCLK Rise Setup Time                     | t <sub>DS</sub>  | Figure 7                                                 |                                       | C, E    | 60  |     |      | ns      |  |

| DIN to SCLK Rise Hold Time                      | t <sub>DH</sub>  | Figure 7                                                 |                                       | C, E    | 0   |     |      | ns      |  |

| CS Fall to SCLK Rise Setup Time                 | tcsso            | Figure 7                                                 |                                       | C, E    | 50  |     |      | ns      |  |

| CS Fall to SCLK Rise Hold Time                  | tcss1            | Figure 7                                                 |                                       | C, E    | 80  |     |      | ns      |  |

| CS Rise to SCLK Rise Hold Time                  | tCSH1            | Figure 7                                                 |                                       | C, E    | 0   |     |      | ns      |  |

| CS Rise to SCLK Rise Setup<br>Time              | tCSS1            | Figure 7                                                 |                                       | C, E    | 80  |     |      | ns      |  |

| SCLK Rise to DOUT Valid                         | t <sub>DO</sub>  | C <sub>L</sub> = 50pF, Fig                               | ure 7                                 | C, E    |     |     | 150  | ns      |  |

| RS Low Pulse Width                              | t <sub>RS</sub>  | Figure 6                                                 | C, E                                  | 80      |     |     | ns   |         |  |

## **ELECTRICAL CHARACTERISTICS—Single +5V Supply (continued)**

$(V_+ = V_L = +4.5V \text{ to } +5.5V, \ V_- = 0, \ V_{INH} = +2.4V, \ V_{INL} = +0.8V, \ T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C, \ V_+ = V_L = +5V.) \ (Note 2)$

| PARAMETER                     | SYMBOL   | CONDITIONS                               | TA    | MIN | TYP | MAX | UNITS |

|-------------------------------|----------|------------------------------------------|-------|-----|-----|-----|-------|

| POWER SUPPLY                  | <u>.</u> |                                          | •     |     |     |     |       |

|                               | V+       |                                          |       | 2.7 |     | 12  |       |

| Power-Supply Range            | VI       | V+ ≤ 6.5V                                |       | 2.7 |     | V+  | V     |

|                               | \ \v_    | V+ > 6.5V                                |       | 2.7 |     | 6.5 |       |

| V+ Supply Current             | 1+       | $V + = 5.5V$ , $V_{IN} = 0$ or $V_L$     | +25°C | -1  |     | 1   | μА    |

| v+ Supply Current             | 1+       | V+ - 3.3V, V N - 0 01 VL                 | C, E  | -10 |     | 10  | μΑ    |

| V <sub>L</sub> Supply Current | ΙL       | $V_L = 5.5V$ , all $V_{IN} = 0$ or $V_L$ | C, E  | -10 | 2   | 10  | μΑ    |

### **ELECTRICAL CHARACTERISTICS—Single +3V Supply**

$(V+=V_L=+2.7V \text{ to } +3.6V, V-=0, V_{INH}=+2V, V_{INL}=+0.5V, T_A=T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A=+25^{\circ}C, V+=V_L=+3.0V.)$

| PARAMETER                             | SYMBOL              | CONDITIONS                                    | TA    | MIN | TYP | MAX  | UNITS |

|---------------------------------------|---------------------|-----------------------------------------------|-------|-----|-----|------|-------|

| ANALOG SWITCH                         |                     |                                               |       |     |     |      |       |

| Analog Signal Range                   | V <sub>COM_</sub> , |                                               |       | 0   |     | V+   | V     |

| On-Resistance                         | Dou                 | V+ = 2.7V, V <sub>NO</sub> _ = 1V,            | +25°C |     | 240 | 350  | Ω     |

| On-Resistance                         | Ron                 | I <sub>COM</sub> _ = 1mA                      | C, E  |     |     | 450  | 52    |

| LOGIC INPUTS (4/8, RS, LE/CS          | , A2/SCLK,          | A1/DIN, A0/DOUT, EN, SER/PAR)                 |       |     |     |      |       |

| Input Logic Threshold High            | V <sub>INH</sub>    |                                               | C, E  | 2.0 |     |      | V     |

| Input Logic Threshold Low             | VINL                |                                               | C, E  |     |     | 0.5  | V     |

| Input Current                         | I <sub>IN</sub>     | V <sub>IN</sub> _ = 0 or V <sub>L</sub>       | C, E  | -1  |     | 1    | μA    |

| SWITCH DYNAMIC CHARACTE               | ERISTICS            |                                               |       |     |     |      |       |

| Turn-On Time                          | ton                 | V <sub>NO</sub> = 1.5V, V+ = 2.7V, Figure 1   | +25°C |     | 700 | 1000 | ns    |

| Turn-On Time                          | ton                 | VNO_ = 1.5V, V+ = 2.7V, Figure 1              | C, E  |     |     | 200  | 113   |

| Turn-Off Time                         | toff                | V <sub>NO</sub> = 1.5V, V+ = 2.7V, Figure 1   | +25°C |     | 250 | 400  | ns    |

|                                       | UFF                 | VNO_ = 1.3V, V+ = 2.7V, Figure 1              | C, E  |     |     | 500  | 113   |

| Break-Before-Make Time Delay (Note 3) | t <sub>BBM</sub>    | V <sub>NO</sub> _ = 1.5V, V+ = 3.6V, Figure 2 | +25°C | 10  | 350 |      | ns    |

| PARALLEL-INTERFACE TIMIN              | G                   |                                               |       |     |     |      |       |

| A_, EN to LE Rise Setup Time          | t <sub>DS</sub>     | Figure 6                                      | C, E  | 200 |     |      | ns    |

| A_, EN to LE Rise Hold Time           | t <sub>DH</sub>     | Figure 6                                      | C, E  | 0   |     |      | ns    |

| LE Low Pulse Width                    | tL                  | Figure 6                                      | C, E  | 200 |     |      | ns    |

| RS Low Pulse Width                    | t <sub>RS</sub>     | Figure 6                                      | C, E  | 200 |     |      | ns    |

| SERIAL-INTERFACE TIMING               | •                   |                                               |       |     |     |      |       |

| Operating Frequency                   | fCLK                | Figure 7                                      | C, E  |     |     | 2.1  | MHz   |

| SCLK Pulse Width High                 | tcH                 | Figure 7                                      | C, E  | 200 |     |      | ns    |

| SCLK Pulse Width Low                  | t <sub>CL</sub>     | Figure 7                                      | C, E  | 200 |     |      | ns    |

| DIN to SCLK Rise Setup Time           | t <sub>DS</sub>     | Figure 7                                      | C, E  | 100 |     |      | ns    |

| DIN to SCLK Rise Hold Time            | t <sub>DH</sub>     | Figure 7                                      | C, E  | 0   |     |      | ns    |

| RS Low Pulse Width                    | t <sub>RS</sub>     | Figure 6                                      | C, E  | 200 |     |      | ns    |

### **ELECTRICAL CHARACTERISTICS—Single +3V Supply (continued)**

$(V_+ = V_L = +2.7V \text{ to } +3.6V, V_- = 0, V_{INH} = +2V, V_{INL} = +0.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$ ,  $V_+ = V_L = +3.0V$ .)

| PARAMETER                          | SYMBOL            | CONDITIONS                                 | TA    | MIN | TYP | MAX | UNITS |

|------------------------------------|-------------------|--------------------------------------------|-------|-----|-----|-----|-------|

| CS Fall to SCLK Rise Setup Time    | t <sub>CSS0</sub> | Figure 7                                   | C, E  | 100 |     |     | ns    |

| CS Rise to SCLK Rise Hold Time     | tCSH1             | Figure 7                                   | C, E  | 0   |     |     | ns    |

| CS Rise to SCLK Rise Setup<br>Time | t <sub>CSS1</sub> | Figure 7                                   | C, E  | 200 |     |     | ns    |

| CS Fall to SCLK Rise Hold Time     | tcss1             | Figure 7                                   | C, E  | 200 |     |     | ns    |

| SCLK Rise to DOUT Valid            | t <sub>DO</sub>   | C <sub>L</sub> = 50pF, Figure 7            | C, E  |     |     | 250 | ns    |

| POWER SUPPLY                       |                   |                                            |       |     |     |     |       |

| V+ Supply Current                  | 1+                | $V + = 3.6V, V_{IN} = 0 \text{ or } V_{I}$ | +25°C | -1  |     | 1   | μA    |

| v+ Supply Current                  | 1+                | V + - 3.0 V , V     V   - 0 0   V          | C, E  | -10 |     | 10  | μΑ    |

| V <sub>L</sub> Supply Current      | ΙL                | $V_L = 3.6V$ , all $V_{IN} = 0$ or $V_L$   | C, E  | -10 | 1   | 10  | μΑ    |

Note 2: The algebraic convention is used in this data sheet; the most negative value is shown in the minimum column.

Note 3: Guaranteed by design.

**Note 4:**  $\Delta R_{ON} = \Delta R_{ON(MAX)} - \Delta R_{ON(MIN)}$ .

**Note 5:** Resistance flatness is defined as the difference between the maximum and the minimum value of on-resistance as measured over the specified analog-signal range.

Note 6: Leakage parameters are 100% tested at maximum rated hot temperature and guaranteed by correlation at TA = +25°C.

Note 7: Off isolation =  $20log_{10}$  [ $V_{COM_{-}}$  / ( $V_{NC_{-}}$  or  $V_{NO_{-}}$ )],  $V_{COM_{-}}$  = output,  $V_{NC_{-}}$  or  $V_{NO_{-}}$  = input to off switch.

Note 8: Between any two switches.

**Note 9:** Leakage testing for single-supply operation is guaranteed by testing with dual supplies.

## Typical Operating Characteristics

$(V + = V_L = +5V, V - = -5V, T_A = +25^{\circ}C, unless otherwise noted.)$

## Typical Operating Characteristics (continued)

$(V + = V_L = +5V, V - = -5V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

#### INSERTION LOSS, OFF-ISOLATION, AND CROSSTALK vs. FREQUENCY (DUAL SUPPLIES)

## INSERTION LOSS, OFF-ISOLATION, AND CROSSTALK vs. FREQUENCY

## **Pin Description**

| PIN                          | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                       |

|------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 5, 7,<br>9, 21,<br>23, 25 | GND     | Ground. Connect all ground pins to a ground plane. See <i>Grounding</i> section.                                                                                                                                                                                                                               |

| 2                            | COM1    | Analog Switch Common Terminal. See <i>Truth Table</i> .                                                                                                                                                                                                                                                        |

| 3                            | V+      | Analog Positive Supply Voltage Input                                                                                                                                                                                                                                                                           |

| 4                            | NO1     | Normally Open Analog Input Terminal. See <i>Truth Tables</i> .                                                                                                                                                                                                                                                 |

| 6                            | NO2     | Normally Open Analog Input Terminal. See <i>Truth Tables</i> .                                                                                                                                                                                                                                                 |

| 8                            | NO3     | Normally Open Analog Input Terminal. See <i>Truth Tables</i> .                                                                                                                                                                                                                                                 |

| 10                           | NO4     | Normally Open Analog Input Terminal. See Truth Tables.                                                                                                                                                                                                                                                         |

| 11                           | 4/8     | Multiplexer Configuration Control. Connect to $V_L$ to select dual 2-channel mode. Connect to GND for single 4-channel multiplexer operation. See <i>Truth Tables</i> .                                                                                                                                        |

| 12                           | RS      | Active-Low Reset Input. In serial mode, drive $\overline{\rm RS}$ low to force the latches and shift registers to the power-on reset state and force all switches open. In parallel mode, drive RS low to force the latches to the power-on reset state and force all switches open. See <i>Truth Tables</i> . |

| 13                           | LE/CS   | In parallel mode, this pin is the transparent Latch Enable. In the serial mode, this pin is the Chip-Select Input. See <i>Truth Tables</i> .                                                                                                                                                                   |

| 14                           | A2/SCLK | Most Significant Address Bit in parallel mode with $4/8$ low. If $4/8$ pin is high, this pin is ignored. In the serial mode, this is the Serial Shift Clock Input. Data is loaded on the rising edge of SCLK. See <i>Truth Tables</i> .                                                                        |

| 15                           | A1/DIN  | Address Input in the parallel mode. Serial Data Input in serial mode. In serial mode, data is loaded on SCLK's rising edge.                                                                                                                                                                                    |

| 16                           | A0/DOUT | Least Significant Address Input in the parallel mode. In the serial mode this is an output from the internal 4-bit shift register. DOUT is intended for daisy-chain cascading. DOUT is not three-stated by $\overline{\text{CS}}$ . See <i>Serial Operation</i> .                                              |

| 17                           | EN      | Switch Enable. Drive EN low to force all channels off. Drive high to allow normal multiplexer operation. Operates asynchronously in serial mode. In parallel mode, EN is latched when $\overline{\text{LE}}$ signal is high.                                                                                   |

| 18                           | SER/PAR | Interface Select Input. Drive low for parallel data interface operation. Drive high for serial data interface operation and to enable the DOUT driver.                                                                                                                                                         |

| 19                           | VL      | Logic Supply Input. Powers the DOUT driver and other digital circuitry. $V_L$ sets both the digital input and output logic levels.                                                                                                                                                                             |

| 20                           | NO8     | Normally Open Analog Input Terminal. See <i>Truth Tables</i> .                                                                                                                                                                                                                                                 |

| 22                           | NO7     | Normally Open Analog Input Terminal. See <i>Truth Tables</i> .                                                                                                                                                                                                                                                 |

| 24                           | NO6     | Normally Open Analog Input Terminal. See Truth Tables.                                                                                                                                                                                                                                                         |

| 26                           | NO5     | Normally Open Analog Input Terminal. See Truth Tables.                                                                                                                                                                                                                                                         |

| 27                           | V-      | Analog Negative Supply Voltage Input. Connect to ground plane for single-supply operation.                                                                                                                                                                                                                     |

| 28                           | COM2    | Analog Switch Common Terminal. See <i>Truth Tables</i> .                                                                                                                                                                                                                                                       |

Figure 1. Turn-On/Turn-Off Time

Figure 2. Break-Before-Make Time Delay

Figure 3. Charge Injection

Figure 4. NO\_, COM\_ Capacitance

Figure 5. Off-Isolation, Crosstalk, and Bandwidth

Figure 6. Parallel Timing Diagram

Figure 7. Serial Timing Diagram

### **Detailed Description**

#### **Logic-Level Translators**

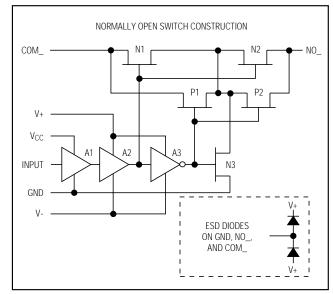

The MAX4588 is constructed of high-frequency "T" switches, as shown in Figure 8. The logic-level inputs are translated by amplifier A1 into a V+ to V- logic signal that drives amplifier A2. Amplifier A2 drives the gates of N-channel MOSFETs N1 and N2 from V+ to V-, turning them fully on or off. The same signal drives inverter A3 (which drives the P-channel MOSFETs P1 and P2, turning them fully on or off) from V+ to V-, and turns the N-channel MOSFET N3 on and off. The logic-level threshold is determined by VL and GND.

#### **Switch On Condition**

When the switch is on, MOSFETs N1, N2, P1, and P2 are on and MOSFET N3 is off (Figure 8). The signal path is COM\_ to NO\_, and because both N-channel and P-channel MOSFETs act as pure resistances, it is symmetrical (i.e., signals may pass in either direction). The off MOSFET, N3, has no DC conduction, but has a small amount of capacitance to GND. The four on MOSFETs also have capacitance to ground that, together with the series resistance, forms a lowpass filter. All of these capacitances are distributed evenly along the series resistance, so they act as a transmission line rather than a simple R-C filter. The MAX4588's construction allows an exceptional 180MHz bandwidth when the switches are on.

Figure 8. T-Switch Construction

Typical attenuation in  $75\Omega$  systems is 2.5dB and is reasonably flat up to 50MHz. Higher-impedance circuits show even lower attenuation (and vice versa), but slightly lower bandwidth due to the increased effect of the internal and external capacitance and the switch's internal resistance.

The MAX4588 is optimized for ±5V operation. Using lower supply voltages or a single supply increases switching time, on-resistance (and therefore on-state attenuation), and nonlinearity.

#### **Switch Off Condition**

When the switch is off, MOSFETs N1, N2, P1, and P2 are off and MOSFET N3 is on (Figure 8). The signal path is through the parasitic off-capacitances of the series MOSFETs, but it is shunted to ground by N3. This forms a highpass filter whose exact characteristics are dependent on the source and load impedances. In  $75\Omega$  systems, and below 10MHz, the attenuation can exceed 80dB. This value decreases with increasing frequency and increasing circuit impedances. External capacitance and board layout have a major role in determining overall performance.

# Applications Information Power-Supply Considerations

#### Overview

The MAX4588 construction is typical of many CMOS analog switches. It has four supply pins: V+, V-, V<sub>L</sub>, and GND. V+ and V- are used to drive the internal CMOS switches and set the limits of the analog voltage on any switch. Reverse ESD-protection diodes are internally connected between each analog signal pin and both V+ and V-. If the voltage on any pin exceeds V+ or V-, one of these diodes will conduct. During normal operation these reverse-biased ESD diodes leak, forming the only current drawn from V- and V+.

Virtually all the analog leakage current is through the ESD diodes. Although the ESD diodes on a given signal pin are identical, and therefore fairly well balanced, they are reverse-biased differently. Each is biased by either V+ or V- and the analog signal. This means their leakages vary as the signal varies. The difference in the two diode leakages from the signal path to the V+ and V- pins constitutes the analog signal-path leakage current. All analog leakage current flows to the supply terminals, not to the other switch terminal. This explains how both sides of a given switch can show leakage currents of either the same or opposite polarity.

There is no connection between the analog signal paths and GND. The analog signal paths consist of an N-channel and P-channel MOSFET with their sources and drains paralleled and their gates driven out of phase with V+ and V- by the logic-level translators.

$V_L$  and GND power the internal logic and logic-level translators, and set the input logic thresholds. The logic-level translators convert the logic levels to switched  $V_+$  and  $V_-$  signals to drive the gates of the

analog switches. This drive signal is the only connection between the logic supplies and the analog supplies.

#### **Bipolar-Supply Operation**

The MAX4588 operates with bipolar supplies between  $\pm 2.7V$  and  $\pm 6V$ . The V+ and V- supplies are not required to be symmetrical, but their sum cannot exceed the absolute maximum rating of 13.0V. Do not connect the MAX4588 V+ pin to +3V and connect the logic-level input pins to +5V logic-level signals. This level exceeds the absolute maximum ratings, and may cause damage to the part and/or external circuits.

CAUTION: The absolute maximum V+ to V- differential voltage is 13.0V. Typical "±6-Volt" or "12-Volt" supplies with ±10% tolerances can be as high as 13.2V. This voltage can damage the MAX4588. Even ±5% tolerance supplies may have overshoot or noise spikes that exceed 13.0V.

#### Single-Supply Operation

The MAX4588 operates from a single supply between +2.7V and +12V when V- is connected to GND. Observe all of the precautions listed in the *Bipolar-Supply Operation* section. Note, however, that these parts are optimized for ±5V operation, and AC and DC characteristics are degraded significantly when operating at less than ±5V. As the overall supply voltage (V+ to V-) is reduced, switching speed, on-resistance, offisolation, and distortion are degraded (see *Typical Operating Characteristics*).

Single-supply operation also limits signal levels and interferes with grounded signals. When V-=0, AC signals are limited to -0.3V. Voltages below -0.3V can be clipped by the internal ESD-protection diodes, and the parts can be damaged if excessive current flows.

#### Power Off

When power to the MAX4588 is off (i.e., V+=0 and V=0), the *Absolute Maximum Ratings* still apply. This means that none of the MAX4588 pins can exceed  $\pm 0.3V$ . Voltages beyond  $\pm 0.3V$  cause the internal ESD-protection diodes to conduct, with potentially catastrophic consequences.

#### Power-Supply Sequencing

When applying power to the MAX4588, follow this sequence: V+, V- (if biased to potential other than ground), V<sub>L</sub>, then logic inputs. Apply signals on the analog NO\_ and COM\_ pins any time after V+, V-, and GND voltages are set. Turning on all pins simultaneously is acceptable only if the circuit design guarantees concurrent power-up.

The power-down sequence is the opposite of the power-up sequence. That is, the  $V_L$  and logic inputs must go to zero potential before (or simultaneously with) the V- then V+ supplies. The *Absolute Maximum Ratings* must always be observed in order to ensure proper operation.

#### Grounding

#### DC Ground Considerations

Satisfactory high-frequency operation requires that careful consideration be given to grounding. For most applications, a ground plane is strongly recommended, and all GND pins must connect to it with solid copper. While the V+ and V- power-supply pins are common to all switches in a given package, each input is separated with ground pins that are not internally connected to each other. This contributes to the overall high-frequency performance by reducing channel-to-channel crosstalk. All the GND pins have ESD diodes to V+ and V-.

In systems that have separate digital and analog (signal) grounds, connect all GND pins to analog signal ground. Preserving a good signal ground is much more important than preserving a digital ground. Ground current is only a few nanoamperes.

The digital inputs have voltage thresholds determined by  $V_L$  and GND (V- does not influence the logic-level threshold). With +5V applied to  $V_L$ , the threshold is about 1.6V, ensuring compatibility with TTL- and CMOS-logic drivers.

#### AC Ground and Bypassing

A ground plane is mandatory for satisfactory high-frequency operation. Prototyping using hand wiring or wire-wrap boards is not recommended. Connect all GND pins to the ground plane with solid copper. (The GND pins extend the high-frequency ground through the package wire-frame, into the silicon itself, thus improving isolation.) Make the ground plane solid metal underneath the device, without interruptions. There should be no traces under the device itself. For DIP packages, this applies to both sides of a two-sided board. Failure to observe this has a minimal effect on the "on" characteristics of the switch at high frequencies, but will degrade the off-isolation and crosstalk.

When using the MAX4588's SO package on PC boards with a buried ground plane, connect each GND pin to the ground plane with a separate via. Do not share this via with any other ground path. Providing a ground via on both sides of the SMT land further enhances the off-isolation by lowering the parasitic inductance. The DIP package can have the through-holes directly tied to the buried plane, or thermally relieved as required to meet manufac-

turability requirements. Again, do not use the throughhole pads as the current path for any other components.

Bypass all V+ and V- pins to the ground plane with surface-mount  $0.01\mu F$  capacitors. Locate these capacitors as close as possible to the pins on the same side of the board as the device. Do not use feedthroughs or vias for bypass capacitors. If board layout dictates that the bypass capacitors are mounted on the opposite side of the PC board, use short feedthroughs or vias, directly under the V+ and V- pins. Use multiple vias if possible. If V- is 0, connect it directly to the ground plane with solid copper. Keep all traces short.

#### Signal Routing

Keep all signal leads as short as possible. Separate all signal leads from each other, and keep them away from any other traces that could induce interference. Separating the signal traces with generously sized ground wires also helps minimize interference. Routing signals via coaxial cable, terminated as close to the MAX4588 as possible, provides the highest isolation.

#### **Board Layout**

IC sockets degrade high-frequency performance and should not be used if signal bandwidth exceeds 5MHz. Surface-mount parts, having shorter internal lead frames, provide the best high-frequency performance. Keep all bypass capacitors close to the device, and separate all signal leads with ground planes. Such grounds tend to be wedge-shaped as they get closer to the device. Use vias to connect the ground planes on each side of the board, and place the vias in the apex of the wedge-shaped grounds that separate signal leads. Logic-level signal lead placement is not critical.

### Impedance Matching

The MAX4588 is intended for use in  $75\Omega$  systems, where the inputs are terminated external to the IC and the COM terminals see an impedance of  $600\Omega$  or higher. The MAX4588 can operate in  $50\Omega$  and  $75\Omega$  systems with terminations through the IC. However, variations in RON and RON flatness cause nonlinearities.

#### Crosstalk and Off-Isolation

The graphs shown in *Typical Operating Characteristics* for crosstalk and off-isolation are taken on adjacent channels. The adjacent channel is the worst-case condition. For example, NO1 has the worst off-isolation to COM1 due to their proximity. Furthermore, NO1 has the most crosstalk to NO2, and the least crosstalk to NO4. Choosing channels wisely necessitates separating the most sensitive channels from the most offensive. Conversely, the above information also applies to the NO5–NO8 inputs to the COM2 pin.

#### Power-On Reset (POR)

The MAX4588 has internal circuitry to guarantee a known state on power-up. In the default state, A0 = A1 = A2 = 0, disable = 1, and all switches are off. This state is equivalent to asserting  $\overline{\text{RS}}$  during normal operation.

#### Serial Operation

The serial mode is activated by driving the SER/PAR input pin to a logic high. The data is then entered using a normal SPI/MICROWIRE write operation. Refer to Figure 7 for a detailed diagram of the serial-interface logic. There are four flip-flops in the shift register, with the output of the fourth shift register being output on the DOUT pin. **Note: DOUT changes on the rising edge of SCLK.**

This allows cascading of multiple MAX4588s using only one chip-select line. For example, one 16-bit write could load the shift registers of four cascaded MAX4588s. The data from the shift register is moved to the internal control latches only upon the rising edge of  $\overline{\text{CS}}$ , so all four MAX4588s change state simultaneously.

### Parallel Operation

The parallel mode is activated by driving SER $\overline{PAR}$  to a logic low. The MAX4588 is programmed by a latched parallel bus scheme. Refer to Figure 6 for a detailed diagram of the parallel-interface logic. Note that  $4/\overline{8}$  is not latched. It is best to hard-wire  $4/\overline{8}$  to a known state for the desired mode of operation, or to use a dedicated microcontroller port pin.

#### **Truth Tables**

## **Parallel Operation**

| SER/PAR | A2 | A1 | A0 | EN | ĪĒ. | RS | 4/8 | SWITCH STATES                                       |

|---------|----|----|----|----|-----|----|-----|-----------------------------------------------------|

| 0       | х  | Х  | х  | Х  | 1   | 1  | Х   | Maintain previous state.                            |

| Х       | Х  | Х  | Х  | Х  | Х   | 0  | Х   | All switches off, latches are cleared.              |

| 1       | х  | Х  | х  | х  | х   | 1  | х   | Serial Mode. Refer to Serial Operation Truth Table. |

| 0       | Х  | Х  | Х  | 0  | 0   | 1  | Х   | All switches off.                                   |

| 0       | 0  | 0  | 0  | 1  | 0   | 1  | 0   | Connects NO1 to COM1                                |

| 0       | 0  | 0  | 1  | 1  | 0   | 1  | 0   | Connects NO2 to COM1                                |

| 0       | 0  | 1  | 0  | 1  | 0   | 1  | 0   | Connects NO3 to COM1                                |

| 0       | 0  | 1  | 1  | 1  | 0   | 1  | 0   | Connects NO4 to COM1                                |

| 0       | 1  | 0  | 0  | 1  | 0   | 1  | 0   | Connects NO5 to COM2                                |

| 0       | 1  | 0  | 1  | 1  | 0   | 1  | 0   | Connects NO6 to COM2                                |

| 0       | 1  | 1  | 0  | 1  | 0   | 1  | 0   | Connects NO7 to COM2                                |

| 0       | 1  | 1  | 1  | 1  | 0   | 1  | 0   | Connects NO8 to COM2                                |

| 0       | Х  | 0  | 0  | 1  | 0   | 1  | 1   | Connect NO1 to COM1 and NO5 to COM2                 |

| 0       | Х  | 0  | 1  | 1  | 0   | 1  | 1   | Connect NO2 to COM1 and NO6 to COM2                 |

| 0       | Х  | 1  | 0  | 1  | 0   | 1  | 1   | Connect NO3 to COM1 and NO7 to COM2                 |

| 0       | Х  | 1  | 1  | 1  | 0   | 1  | 1   | Connect NO4 to COM1 and NO8 to COM2                 |

x = Don't Care

**Note:** 4/8 is not latched when LE is high. When LE is low, all latches are transparent. A2, A1, A0, and EN are latched. Connect COM1 to COM2 externally for 1-of-8 single-ended operation.

MIXIM

Truth Tables (continued)

## **Serial Operation**

| SER/PAR | cs | SCLK | DIN | EN | RS | DOUT   | ON SWITCHES/STATES                                                                                |

|---------|----|------|-----|----|----|--------|---------------------------------------------------------------------------------------------------|

| 1       | Х  | Х    | Х   | Х  | 0  | 0      | All switches off. Latches and shift register are cleared. This is the power-on reset (POR) state. |

| 0       | Х  | х    | х   | х  | х  | High-Z | Parallel Mode. Refer to <i>Parallel Operation Truth Table</i> .                                   |

| 1       | Х  | Х    | Х   | 0  | 1  | *      | All switches off.                                                                                 |

| 1       | 1  | Х    | Х   | 1  | 1  | *      | Chip unselected.                                                                                  |

| 1       | 0  |      | 0   | 1  | 1  | *      | Input shift register loads one bit from DIN. DOUT updates on SCLK's rising edge.                  |

| 1       | 0  |      | 1   | 1  | 1  | *      | Input shift register loads one bit from DIN. DOUT updates on SCLK's rising edge.                  |

| 1       |    | х    | х   | 1  | 1  | *      | Contents of shift register transferred to control latches.                                        |

x = Don't Care

## Control Bit and 4/8 Logic

| DISABLE<br>BIT | A2<br>BIT | A1<br>BIT | A0<br>BIT | 4/8<br>PIN | ON SWITCHES/STATES                  |

|----------------|-----------|-----------|-----------|------------|-------------------------------------|

| 1              | Х         | Х         | Х         | Х          | All switches off.                   |

| 0              | 0         | 0         | 0         | 0          | Connect NO1 to COM1                 |

| 0              | 0         | 0         | 1         | 0          | Connect NO2 to COM1                 |

| 0              | 0         | 1         | 0         | 0          | Connect NO3 to COM1                 |

| 0              | 0         | 1         | 1         | 0          | Connect NO4 to COM1                 |

| 0              | 1         | 0         | 0         | 0          | Connect NO5 to COM2                 |

| 0              | 1         | 0         | 1         | 0          | Connect NO6 to COM2                 |

| 0              | 1         | 1         | 0         | 0          | Connect NO7 to COM2                 |

| 0              | 1         | 1         | 1         | 0          | Connect NO8 to COM2                 |

| 0              | Х         | 0         | 0         | 1          | Connect NO1 to COM1 and NO5 to COM2 |

| 0              | Х         | 0         | 1         | 1          | Connect NO2 to COM1 and NO6 to COM2 |

| 0              | Х         | 1         | 0         | 1          | Connect NO3 to COM2 and NO7 to COM2 |

| 0              | Х         | 1         | 1         | 1          | Connect NO4 to COM2 and NO8 to COM2 |

x = Don't Care

**Note:** DISABLE, A2, A1, and A0 are the 4 bits latched into the MAX4588 with a MICROWIRE/SPI write. A0 is the LSB (first bit in time). DISABLE is the MSB (last bit in time).

<sup>\*</sup>DOUT is delayed by 4 clock cycles from DIN.

\_\_\_\_\_Chip Information

**TRANSISTOR COUNT: 1033**

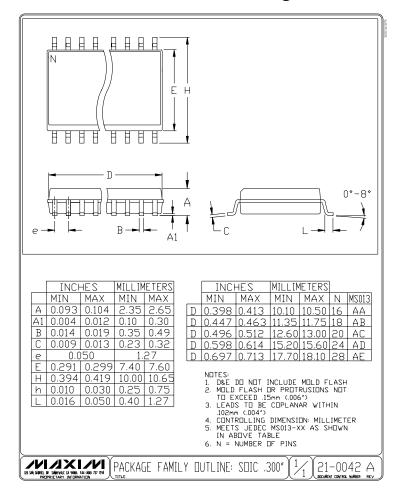

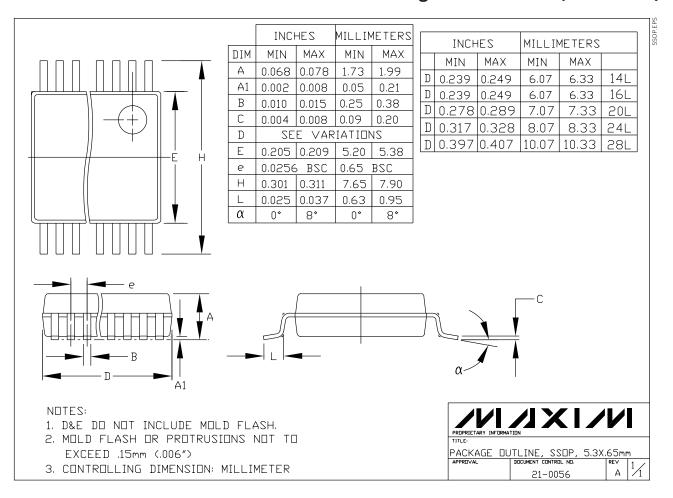

# Package Information

Package Information (continued)

## Package Information (continued)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Analog Devices Inc.:

MAX4588CAI+T MAX4588CAI+ MAX4588CWI+ MAX4588CWI+T MAX4588EAI+ MAX4588EAI+T