Click here to ask an associate for production status of specific part numbers. **MAX31889**

# ±0.25°C Accurate I<sup>2</sup>C Temperature Sensor

# **General Description**

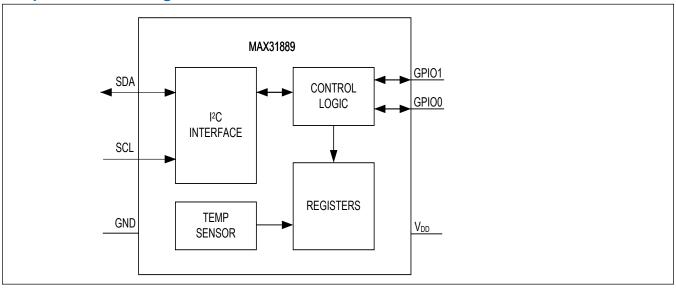

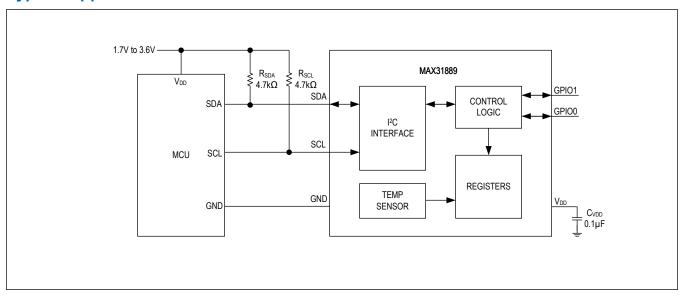

The MAX31889 operates from a 1.7V to 3.6V supply voltage, and is a low power, high-accuracy digital temperature sensor with ±0.25°C accuracy from -20°C to +105°C and ±0.65°C accuracy from -40°C to +125°C. The MAX31889 has 16-bit resolution (0.005°C).

The device uses a standard I<sup>2</sup>C serial interface to communicate with a host controller. Two GPIO pins are available. GPIO1 can be configured to trigger a temperature conversion, while GPIO0 can be configured to generate an interrupt for selectable status bits.

The MAX31889 includes a 32-word FIFO for the temperature data and also includes high and low threshold digital temperature alarms. The device is available in a 2mm x 2mm x 0.8mm, 6-pin µDFN package.

#### **Applications**

- Precision Temperature Monitoring

- RTD Replacement

- Internet of Things (IoT) Sensors

#### **Benefits and Features**

- High Accuracy and Precision

- ±0.25°C Accuracy from -20°C to +105°C

- ±0.65°C Accuracy from -40°C to +125°C

- Long Battery Life

- 1.7V to 3.6V Operating Voltage

- 68µA Operating Current During Measurement

- 0.55µA Standby Current

- Small Size

- 2mm x 2mm x 0.8mm, 6-Pin µDFN

- Safety and Compliance

- · High and Low Temperature Alarms

- I<sup>2</sup>C Digital Interface

- · Configurable Convert Temperature Input Pin

- Configurable Interrupt Output Pin

- 32-Word FIFO for Temperature Data

- 4 I<sup>2</sup>C Addresses Available—More Addresses Available by Request

- Unique ROM IDs Allow Device to Be NIST Traceable

## Simplified Block Diagram

## **Absolute Maximum Ratings**

| GPIOx to GND0.3V to +6V                                                        | Junction Temperature+150°C              |

|--------------------------------------------------------------------------------|-----------------------------------------|

| SDA,SCL to GND0.3V to +6V                                                      | Storage Temperature Range65°C to +150°C |

| Continuous Power Dissipation (Multilayer Board $\mu$ DFN, T <sub>A</sub> = +70 | Lead Temperature (soldering, 10s)+300°C |

| °C, derate 5.47mW/°C above 70°C )437.25mW/°C                                   | Soldering Temperature (reflow)+260°C    |

| Operating Temperature Range40°C to 125°C                                       | - · · · · · · ·                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### **µDFN**

| Package Code                           | L622+2           |

|----------------------------------------|------------------|

| Outline Number                         | <u>21-100397</u> |

| Land Pattern Number                    | <u>90-100138</u> |

| Thermal Resistance, Four-Layer Board:  |                  |

| Junction to Ambient (θ <sub>JA</sub> ) | 182.96°C/W       |

| Junction to Case (θ <sub>JC</sub> )    | 50.75°C/W        |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## **Electrical Characteristics**

$(V_{DD}$  = 1.8V,  $T_A$  = +25°C, minimum and maximum limits are from  $T_A$  = -40°C to +125°C, unless otherwise noted. (Note 1))

| PARAMETER                           | SYMBOL                | COND                                                 | ITIONS                      | MIN   | TYP   | MAX   | UNITS          |  |

|-------------------------------------|-----------------------|------------------------------------------------------|-----------------------------|-------|-------|-------|----------------|--|

| TEMPERATURE SENSO                   | R                     |                                                      |                             | •     |       |       |                |  |

|                                     |                       |                                                      | -20°C to +105°C,<br>3-sigma | -0.25 |       | +0.25 |                |  |

| Temperature                         |                       | V <sub>DD</sub> = 1.7V to 3.6V                       | -20°C to +105°C,<br>6-sigma | -0.45 |       | +0.45 | °C             |  |

| Measurement Error                   |                       | VDD = 1.7 V to 3.6 V                                 | -40°C to +125°C,<br>3-sigma | -0.65 |       | +0.65 |                |  |

|                                     |                       |                                                      | -40°C to +125°C,<br>6-sigma | -0.9  |       | +0.9  |                |  |

| Resolution                          |                       | 16-Bit                                               |                             |       | 0.005 |       | °C             |  |

| Repeatability                       |                       | VDD=1.8V, 1sps,120                                   | ) samples                   |       | 0.008 |       | °C rms         |  |

| Conversion Time                     | t <sub>CONV</sub>     | 16-bit                                               |                             |       | 16.5  | 17.85 | ms             |  |

| Long-Term Stability                 |                       | T <sub>A</sub> = +70°C, 0% RH                        |                             |       | 0.015 |       | °C/<br>1000hrs |  |

| Operating Supply Voltage            | V <sub>DD</sub>       | Guaranteed by PSR                                    | R                           | 1.7   |       | 3.6   | V              |  |

| DC Power Supply<br>Rejection Ratio  | PSRR                  | T <sub>A</sub> = +25°C                               |                             |       | 0.006 |       | °C/V           |  |

|                                     |                       |                                                      | T <sub>A</sub> = +25°C      |       | 68    | 105   | μΑ             |  |

| Operating Current                   |                       | During Conversion,<br>V <sub>DD</sub> = 1.7V to 3.6V | T <sub>A</sub> = +85°C      |       | 71    | 110   |                |  |

|                                     |                       | VDD = 1.7 V to 3.0 V                                 | T <sub>A</sub> = +125°C     |       | 87    | 140   | μA             |  |

|                                     |                       |                                                      | T <sub>A</sub> = +25°C      |       | 0.55  | 3     |                |  |

| Standby Current                     |                       | V <sub>DD</sub> = 3.6V                               | T <sub>A</sub> = +85°C      |       | 3.7   | 10    | μA             |  |

|                                     |                       |                                                      | T <sub>A</sub> = +125°C     |       | 15    | 38    |                |  |

| GPIO PINS                           |                       |                                                      |                             |       |       |       |                |  |

| Input Voltage Low                   | V <sub>IL_GPIO</sub>  |                                                      |                             |       |       | 0.4   | V              |  |

| Input Voltage High                  | V <sub>IH_GPIO</sub>  |                                                      |                             | 1.4   |       |       | V              |  |

| Input Hysteresis                    | V <sub>HYS_GPIO</sub> |                                                      |                             |       | 320   |       | mV             |  |

| Input Leakage Current               | I <sub>IN_GPIO</sub>  | $V_{IN} = 0V, T_A = +25^{\circ}$                     | 0                           |       | 0.01  | 1     | μA             |  |

| Input Capacitance                   | C <sub>IN_GPIO</sub>  |                                                      |                             |       | 10    |       | pF             |  |

| Input Low Pulse Width               |                       |                                                      |                             | 5     |       |       | μs             |  |

| Output Low Voltage                  | V <sub>OL_GPIO</sub>  | I <sub>SINK</sub> = 2mA                              |                             |       |       | 0.4   | V              |  |

| I <sup>2</sup> C INTERFACE / DIGITA | L I/O CHARAC          | TERISTICS                                            |                             |       |       |       | •              |  |

| Input Voltage Low                   | V <sub>IL</sub>       |                                                      |                             |       |       | 0.4   | V              |  |

| Input Voltage High                  | V <sub>IH</sub>       |                                                      |                             | 1.4   |       |       | V              |  |

| Input Hysteresis                    | V <sub>HYS</sub>      |                                                      |                             |       | 200   |       | mV             |  |

| Input Capacitance                   | C <sub>IN</sub>       |                                                      |                             |       | 10    |       | pF             |  |

| Open Drain Output Low<br>Voltage    | V <sub>OL_OD</sub>    | I <sub>SINK</sub> = 6mA, SDA P                       | in Only                     |       |       | 0.4   | V              |  |

| I <sup>2</sup> C INTERFACE / TIMINO | CHARACTERI            | STICS (Note 2)                                       |                             |       |       |       |                |  |

| I <sup>2</sup> C Write Address      |                       | GPIO1 = GPIO0 = 0                                    | V. See Table 3              |       | A0    |       | Hex            |  |

| I <sup>2</sup> C Read Address       |                       | GPIO1 = GPIO0 = 0                                    | V. See Table 3              |       | A1    |       | Hex            |  |

# **Electrical Characteristics (continued)**

$(V_{DD} = 1.8V, T_A = +25^{\circ}C, \text{ minimum and maximum limits are from } T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. (Note 1))}$

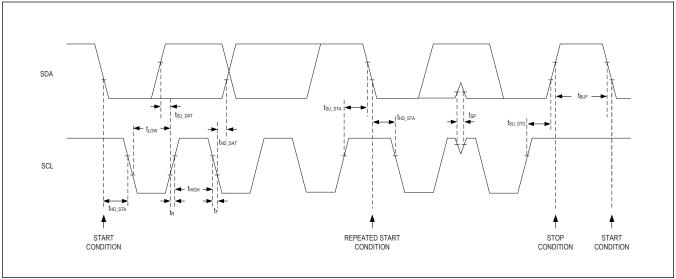

| PARAMETER                                             | SYMBOL              | CONDITIONS | MIN                       | TYP | MAX | UNITS |

|-------------------------------------------------------|---------------------|------------|---------------------------|-----|-----|-------|

| Serial Clock Frequency                                | f <sub>SCL</sub>    |            | 0                         |     | 400 | kHz   |

| Bus Free Time Between<br>STOP and START<br>Conditions | t <sub>BUF</sub>    |            | 1.3                       |     |     | μs    |

| Hold Time START and<br>Repeat START<br>Condition      | <sup>t</sup> HD_STA |            | 0.6                       |     |     | μs    |

| SCL Pulse-Width Low                                   | $t_{LOW}$           |            | 1.3                       |     |     | μs    |

| SCL Pulse-Width High                                  | <sup>t</sup> HIGH   |            | 0.6                       |     |     | μs    |

| Setup Time for a<br>Repeated START<br>Condition       | <sup>t</sup> SU_STA |            | 0.6                       |     |     | μs    |

| Data Hold Time                                        | t <sub>HD_DAT</sub> |            | 0                         |     | 900 | ns    |

| Data Setup Time                                       | t <sub>SU_DAT</sub> |            | 100                       |     |     | ns    |

| Setup Time for STOP<br>Condition                      | tsu_sto             |            | 0.6                       |     |     | μs    |

| Pulse Width of<br>Suppressed Spike                    | t <sub>SP</sub>     |            |                           |     | 50  | ns    |

| Bus Capacitance                                       | C <sub>B</sub>      |            |                           |     | 400 | pF    |

| SDA and SCL Receiving<br>Rise Time                    | t <sub>R</sub>      |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA and SCL Receiving Fall Time                       | t <sub>F</sub>      |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA Transmitting Fall<br>Time                         | t <sub>TF</sub>     |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

**Note 1:** All devices are 100% production tested at T<sub>A</sub> = +25°C. Specifications over temperature limits are guaranteed by design and characterization.

Note 2: For design guidance only. Not production tested.

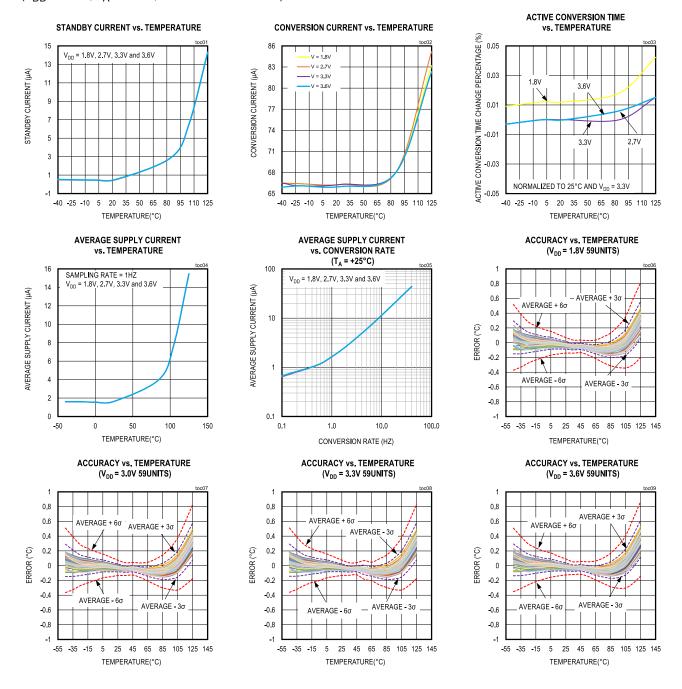

## **Typical Operating Characteristics**

$(V_{DD} = +1.8V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# **Typical Operating Characteristics (continued)**

$(V_{DD} = +1.8V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

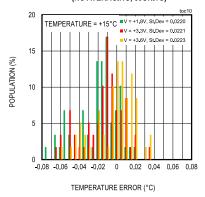

# TEMPERATURE ERROR OVER SUPPLY VOLTAGE (NO AVERAGING, 59UNITS)

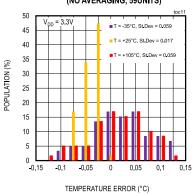

# TEMPERATURE ERROR OVER TEMPERATURE (NO AVERAGING, 59UNITS)

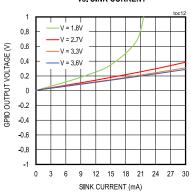

# GPIO OUTPUT VOLTAGE vs. SINK CURRENT

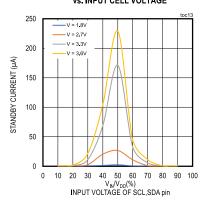

# STANDBY CURRENT vs. INPUT CELL VOLTAGE

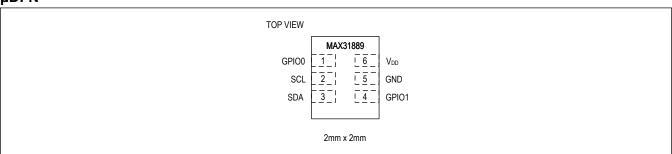

# **Pin Configuration**

## μDFN

# **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                    |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GPIO0           | General Purpose Input/Output 0. Programmable digital input or output. State at each I <sup>2</sup> C start condition can be used to configure I <sup>2</sup> C addresses. See <u>Table 1</u> and <u>Table 2</u> . Can be configured as an interrupt output. |

| 2   | SCL             | SCL Input. I <sup>2</sup> C Clock.                                                                                                                                                                                                                          |

| 3   | SDA             | SDA Input/Output. I <sup>2</sup> C Data I/O.                                                                                                                                                                                                                |

| 4   | GPIO1           | General Purpose Input/Output 1. State at each I <sup>2</sup> C start condition can be used to configure I <sup>2</sup> C addresses (see <u>Table 1</u> and <u>Table 2</u> ). Can be configured to act as an external temperature convert input.             |

| 5   | GND             | Ground.                                                                                                                                                                                                                                                     |

| 6   | V <sub>DD</sub> | Power Supply Input. A 100nF capacitor connected between V <sub>DD</sub> and GND is recommended.                                                                                                                                                             |

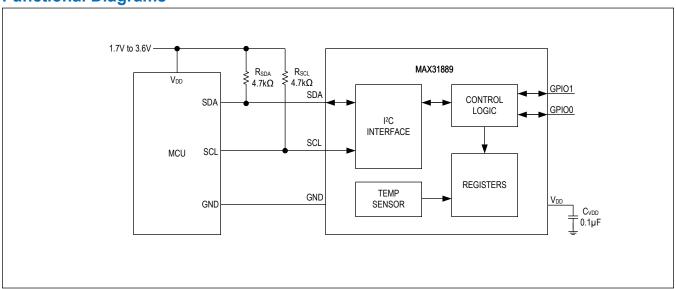

# **Functional Diagrams**

#### **Detailed Description**

The MAX31889 temperature sensor provides 16-bit Celsius temperature measurements with ±0.25°C accuracy over a -20°C to +105°C temperature range and ±0.65°C accuracy over a -40°C to +125°C temperature range.

A host can communicate with the sensor over an I<sup>2</sup>C/SMBus-compatible 2-wire interface with serial data (SDA) and serial clock (SCL) lines to read the FIFO, which contains up to 32, 2-byte temperature readings.

In addition to the FIFO, the interface provides access to the 2-byte high alarm trigger and 2-byte low alarm trigger registers (AH and AL) and a temperature sensor setup register. The Alarm High, Alarm Low, and Setup registers are volatile, so they don't retain data when the device is powered down.

The MAX31889 offers two programmable GPIO pins. The default state of the GPIO pins at power-up determines the 2 LSBs in the I<sup>2</sup>C address of the device. GPIO1 allows for an optional external convert temperature trigger while GPIO0 can be configured as an interrupt for selectable status bits.

#### Operation

#### **Measuring Temperature**

The device's core functionality is its direct-to-digital temperature sensor. The device powers up in a low-power standby state. There are two ways to initiate a temperature measurement; the master can write a "1" to the CONVERT\_T bit in the TEMP\_SENSOR\_SETUP [0x14] register or set GPIO1 as an active low convert trigger to allow temperature conversions to be triggered by an external signal. Following the conversion, the resulting temperature sensor data is stored in the FIFO memory as a 2-byte temperature word and the device returns to the standby state.

The output temperature data is calibrated in degrees Celsius. The temperature data is stored as a left-justified, 16-bit sign-extended two's complement number in the FIFO Data register (see <u>Figure 1</u>). The data is two's complement where the MSB indicates the sign of the temperature, with an MSB of 1 indicating a negative temperature and an MSB of 0 indicating a positive temperature.

To calculate the temperature from the measurement data, convert the two's complement value to the decimal value and use the following equation for 16-bit resolution.

T = Decimal Value x 0.005

For example, if the result is 0x1CE8, convert to decimal to get 7400, then T = 7400 x 0.005, or  $37^{\circ}C$ . Table 1 gives examples of digital output data and the corresponding temperature reading.

|     | TEMPERATURE D | ATA REGISTER FOR | RMAT  |       |       |       |      |      |

|-----|---------------|------------------|-------|-------|-------|-------|------|------|

|     | Bit15         | Bit14            | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 |

| MSB | T15           | T14              | T13   | T12   | T11   | T10   | Т9   | Т8   |

|     | D#7           | Direc            | Diff  | D:44  | D#0   | D:40  | DitA | D:40 |

|     | Bit7          | Bit6             | Bit5  | Bit4  | Bit3  | Bit2  | Bit1 | Bit0 |

| LSB | Т7            | Т6               | Т5    | T4    | Т3    | T2    | T1   | то   |

Figure 1. Temperature Data Register Format

**Table 1. 16-bit Temperature Data Format**

| TEMPERATURE (°C) | DIGITAL OUTPUT (BINARY) | DIGITAL<br>OUTPUT (HEX) | DIGITAL OUTPUT (DEC) |

|------------------|-------------------------|-------------------------|----------------------|

| +125             | 0110 0001 1010 1000     | 61A8                    | 25000                |

| +100             | 0100 1110 0010 0000     | 4E20                    | 20000                |

| +85              | 0100 0010 0110 1000     | 4268                    | 17000                |

| +70              | 0011 0110 1011 0000     | 36B0                    | 14,000               |

| +50              | 0010 0111 0001 0000     | 2710                    | 10,000               |

| +41              | 0010 0000 0000 1000     | 2008                    | 8,200                |

| +37              | 0001 1100 1110 1000     | 1CE8                    | 7,400                |

| +35.8            | 0001 1011 1111 1000     | 1BF8                    | 7,160                |

| +25              | 0001 0011 1000 1000     | 1388                    | 5,000                |

| +15              | 0000 1011 1011 1000     | 0BB8                    | 3,000                |

| +0.04            | 0000 0000 0000 1000     | 8000                    | 8                    |

| +0.02            | 0000 0000 0000 0100     | 0004                    | 4                    |

| +0.01            | 0000 0000 0000 0010     | 0002                    | 2                    |

| +0.005           | 0000 0000 0000 0001     | 0001                    | 1                    |

| 0                | 0000 0000 0000 0000     | 0000                    | 0                    |

| -0.005           | 1111 1111 1111 1111     | FFFF                    | -1                   |

| -0.01            | 1111 1111 1111 1110     | FFFE                    | -2                   |

| -0.02            | 1111 1111 1111 1100     | FFFC                    | -4                   |

| -0.04            | 1111 1111 1111 1000     | FFF8                    | -8                   |

| -20              | 1111 0000 0110 0000     | F060                    | -4000                |

| -40              | 1110 0000 1100 0000     | E0C0                    | -8000                |

#### **Alarm Signaling**

After the device performs a temperature conversion, the temperature value is compared with the user-defined two's complement alarm trigger values stored in the 2-byte Alarm High and 2-byte Alarm Low registers (see <u>Figure 2</u>). The default value for AH is 0x7FFF (+163.835°C) and the default value for AL is 0x8000 (-163.840°C). The MSB indicates if the value is positive or negative; for positive numbers the MSB is 0 and for negative numbers the MSB is 1. The Alarm High threshold (AH) is programmed in registers ALARM\_HI\_MSB [0x10] and ALARM\_HI\_LSB [0x11]. The alarm low threshold (AL) is programmed in registers ALARM LO MSB [0x12] and ALARM LO LSB [0x13].

If the measured temperature is lower than AL or higher than AH, an alarm condition exists and the corresponding status bit (TEMP\_LO or TEMP\_HI) is set in the STATUS [0x00] regsiter. When the alarm condition is detected and the corresponding interrupt enable bit (TEMP\_LO\_EN or TEMP\_HI\_EN) is set in the INTERRUPT\_ENABLE [0x01] register and if GPIO0\_MODE in the GPIO\_SETUP [0x20] register is set to 0x3, then a hardware interrupt asserts on the GPIO0 pin. The status bits, the alarm flag and the hardware interrupt stay asserted until the STATUS [0x00] register is read through the serial interface. The alarm flag only clears when STATUS is read. If the alarm flag is set and the next result does not trip the flag, then the flag remains set.

If the resolution or alarm settings change while the device is under an alarm condition, the alarm status must be cleared and another temperature conversion executed to update the alarm condition.

|         |                               | O REGISTER FORMA                 |            | B::40         | D::44         | D::40         | D::0        | D://0 |

|---------|-------------------------------|----------------------------------|------------|---------------|---------------|---------------|-------------|-------|

| Г       | Bit15                         | Bit14                            | Bit13      | Bit12         | Bit11         | Bit10         | Bit9        | Bit8  |

| MSB     | AH15                          | AH14                             | AH13       | AH12          | AH11          | AH10          | AH9         | AH8   |

|         | Bit7                          | Bit6                             | Bit5       | Bit4          | Bit3          | Bit2          | Bit1        | Bit0  |

| LSB     | AH7                           | AH6                              | AH5        | AH4           | AH3           | AH2           | AH1         | AH0   |

|         |                               |                                  |            | Alf           | Allo          | ATIZ          | AIII        | Ailu  |

|         |                               | REGISTER FORMAT                  |            | Bit12         | Bit11         | Bit10         | Bit9        | Bit8  |

|         | .OW THRESHOLD                 | REGISTER FORMAT                  |            |               |               |               |             |       |

| ALARM L | OW THRESHOLD<br>Bit15<br>AL15 | REGISTER FORMAT<br>Bit14<br>AL14 | Bit13      | Bit12<br>AL12 | Bit11<br>AL11 | Bit10<br>AL10 | Bit9<br>AL9 | Bit8  |

| ALARM L | .OW THRESHOLD<br>Bit15        | REGISTER FORMAT Bit14            | -<br>Bit13 | Bit12         | Bit11         | Bit10         | Bit9        | Bit8  |

Figure 2. Alarm Threshold Register Format

#### **GPIO**

The MAX31889 provides access to two GPIO pins which can be used to provide additional functionality as shown in <u>Table 2</u>. GPIO0 can be configured to output an interrupt while GPIO1 can be configured as an input for a temperature converison. The interrupt on GPIO0 is triggered based on selectable status bits in the INTERRUPT\_ENABLE[0X01] register. By writing to one of the available bits in the INTERRUPT\_ENABLE register, the flag for an interrupt is raised if GPIO0\_MODE[1:0] in the GPIO\_SETUP[0x20] register is set to 11. When GPIO1\_MODE[7:0] in the GPIO\_SETUP register is set to 11, driving the line low initiates an external temperature converison. <u>Table 1</u> shows a complete list of the functions of the two GPIO Pins.

The state of GPIO pins and the setting of the GPIO\_SETUP[0x20] register are used to determine the last two bits of the I<sup>2</sup>C address at each I<sup>2</sup>C start condition. This use of the GPIO pins is further detailed in the I<sup>2</sup>C Slave Address section.

**Table 2. GPIO Mode Functions**

| GPIOX_MODE[1:0] (X = 0,1) | GPIO0                       | GPIO1                       |

|---------------------------|-----------------------------|-----------------------------|

| 00                        | HiZ Input                   | HiZ Input                   |

| 01                        | Output                      | Output                      |

| 10 (default)              | 1MΩ Internal Pulldown Input | 1MΩ Internal Pulldown Input |

| 11                        | INTB                        | CONV                        |

#### I<sup>2</sup>C

#### I<sup>2</sup>C Slave Address

The I<sup>2</sup>C address is determined by a combination of the GPIO Mode and the state of the GPIO pins. I<sup>2</sup>C Slave Address is shown in Table 3, the LSB of I<sup>2</sup>C address is 0 for write option and 1 for read option. At power-up, GPIOx\_MODE[1:0] bits in the GPIO\_SETUP register(0x20) are set to mode 10 as shown in Table 3. GPIO Mode bits 10 configures GPIO0 and GPIO1 pins as input with a 1M $\Omega$  internal pulldown. With nothing connected, GPIO0 and GPIO1 pins are considered low, I<sup>2</sup>C address will be detected as 0xA0 for write option and 0xA1 for read option. If drive GPIO0 and GPIO1 pins to high at power-up, I<sup>2</sup>C address will be detected as 0xA6 for write option and 0xA7 for read option.

If the state of the GPIO mode bits for a given GPIO input are set to 01 or 11 (see <u>Table 2</u>), then corresponding address state of that bit is 0 for the purposes of determing the I<sup>2</sup>C address, the actual pin state of GPIO 1 and GPIO 0 are not measured. For example, when set GPIO Mode bits of GPIO0 and GPIO1 to 01 or 11, the I<sup>2</sup>C address is always 0xA0 for write option and 0xA1 for read option, regardless the voltage level of GPIO0 and GPIO1 pins. If the GPIO Mode bits for either of the GPIO pins are set as input and driven high, change of GPIO Mode bits to 01 or 11 will change I<sup>2</sup>C address. For example, when GPIO Mode bits of both GPIO0 and GPIO1 are set as 00( HiZ Input) and driven high, the I<sup>2</sup>C address is 0xA6 for write option and 0xA7 for read option. As soon as we set GPIO Mode bits of GPIO 0 and GPIO1 to 11(GPIO0 as INTB,GPIO1 as CONV), the I<sup>2</sup>C address is changed to 0xA0 for write option and 0xA1 for read option.

Table 3. I<sup>2</sup>C Slave Address

|   |   |   | I <sup>2</sup> C | AD | DRESS |       | W/R | GPIO S          | STATES          | CONDITION                            |

|---|---|---|------------------|----|-------|-------|-----|-----------------|-----------------|--------------------------------------|

| 7 | 6 | 5 | 4                | 3  | 2     | 1     | 0   | GPIO1_MODE[1:0] | GPIO0_MODE[1:0] |                                      |

| 1 | 0 | 1 | 0                | 0  | GPIO1 | GPIO0 | 0/1 | 10              | 10              | Default state at powerup             |

| 1 | 0 | 1 | 0                | 0  | GPIO1 | GPIO0 | 0/1 | 00              | 00              | Both GPIO1 and GPIO0 are inputs      |

| 1 | 0 | 1 | 0                | 0  | GPIO1 | GPIO0 | 0/1 | 10              | 00              | Both GPIO1 and GPIO0 are inputs      |

| 1 | 0 | 1 | 0                | 0  | GPIO1 | GPIO0 | 0/1 | 00              | 10              | Both GPIO1 and GPIO0 are inputs      |

| 1 | 0 | 1 | 0                | 0  | GPIO1 | 0     | 0/1 | 00              | 01              | GPIO1 is an input,GPIO0 is an output |

| 1 | 0 | 1 | 0                | 0  | GPIO1 | 0     | 0/1 | 00              | 11              | GPIO1 is an input,GPIO0 is an output |

| 1 | 0 | 1 | 0                | 0  | GPIO1 | 0     | 0/1 | 10              | 01              | GPIO1 is an input,GPIO0 is an output |

| 1 | 0 | 1 | 0                | 0  | GPIO1 | 0     | 0/1 | 10              | 11              | GPIO1 is an input,GPIO0 is an output |

| 1 | 0 | 1 | 0                | 0  | 0     | GPIO0 | 0/1 | 01              | 00              | GPIO1 is an output,GPIO0 is an input |

| 1 | 0 | 1 | 0                | 0  | 0     | GPIO0 | 0/1 | 01              | 10              | GPIO1 is an output,GPIO0 is an input |

| 1 | 0 | 1 | 0                | 0  | 0     | GPIO0 | 0/1 | 11              | 00              | GPIO1 is an input,GPIO0 is an input  |

| 1 | 0 | 1 | 0                | 0  | 0     | GPIO0 | 0/1 | 11              | 10              | GPIO1 is an input,GPIO0 is an input  |

| 1 | 0 | 1 | 0                | 0  | 0     | 0     | 0/1 | 01              | 01              | GPIO1 and GPIO0 are outputs          |

| 1 | 0 | 1 | 0                | 0  | 0     | 0     | 0/1 | 01              | 11              | GPIO1 and GPIO0 are outputs          |

| 1 | 0 | 1 | 0                | 0  | 0     | 0     | 0/1 | 11              | 01              | GPIO1 is an input,GPIO0 is an output |

| 1 | 0 | 1 | 0                | 0  | 0     | 0     | 0/1 | 11              | 11              | GPIO1 is an input,GPIO0 is an output |

#### I<sup>2</sup>C/SMBus Compatible Serial Interface

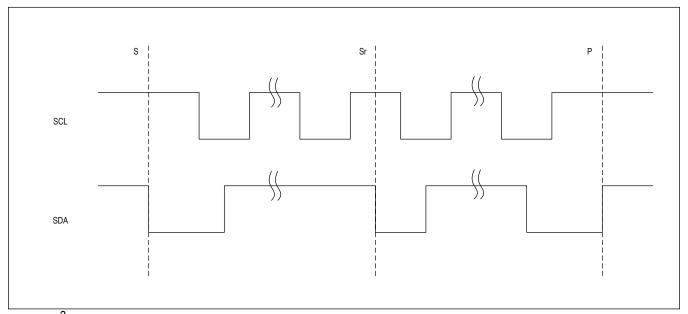

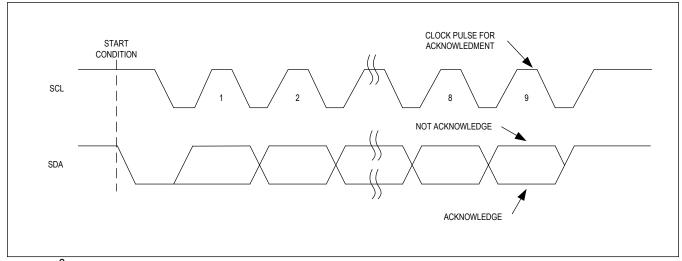

The MAX31889 features an I<sup>2</sup>C/SMBus™ compatible, 2-wire serial interface consisting of a serial data line (SDA) and a serial clock line (SCL). SDA and SCL facilitate communication between the MAX31889 and the master at clock rates up to 400kHz. Figure 3 shows the 2-wire interface timing diagram. The master generates SCL and initiates data transfer on the bus. The master device writes data to the MAX31889 by transmitting the proper slave address followed by the register address and then the data word. Each transmit sequence is framed by a START (S) or REPEATED START (Sr) condition and a STOP (P) condition. Each word transmitted to the MAX31889 is 8 bits long and is followed by an acknowledge clock pulse. A master reading data from the MAX31889 transmits the proper slave address followed by a series of nine SCL pulses. The MAX31889 transmits data on SDA in sync with the master-generated SCL pulses. The master acknowledges receipt of each byte of data. Each read sequence is framed by a START (S) or REPEATED START (Sr) condition, a Not Acknowledge (NACK), and a STOP (P) condition. SDA operates as both an input and an open-drain output. A pullup resistor is required on SDA. SCL operates only as an input. A pullup resistor is required on SCL if there are multiple masters on the bus, or if the single master has an open-drain SCL output. Series resistors in line with SDA and SCL are optional. Series resistors can protect the digital inputs of the MAX31889 from high-voltage spikes on the bus lines, and minimize crosstalk and undershoot of the bus signals.

#### Detailed I<sup>2</sup>C Timing Diagram

The detailed timing diagram of various electrical characteristics is shown in Figure 3.

Figure 3. Detailed I<sup>2</sup>C Timing Diagram

#### Bit Transfer

One data bit is transferred during each SCL cycle. The data on SDA must remain stable during the high period of the SCL pulse. Changes in SDA while SCL is high are control signals (see the <u>START and STOP Conditions</u> section).

#### **START and STOP Conditions**

SDA and SCL idle high when the bus is not in use. A master initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 4). A START condition from the master signals the beginning of a transmission to the MAX31889. The master terminates transmission, and frees the bus, by issuing a STOP condition. The bus remains active if a REPEATED START condition is generated instead of a STOP condition.

#### **Early STOP Conditions**

The MAX31889 recognizes a STOP condition at any point during data transmission except if the STOP condition occurs in the same high pulse as a START condition. For proper operation, do not send a STOP condition during the same SCL

high pulse as the START condition.

#### **Acknowledge Bit**

The acknowledge bit (ACK) is a clocked 9th bit that the MAX31889 uses to handshake receipt each byte of data when in write mode (Figure 5). The MAX31889 pulls down SDA during the entire master-generated 9th clock pulse if the previous byte is successfully received. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master will retry communication. The master pulls down SDA during the 9th clock cycle to acknowledge receipt of data when the MAX31889 is in read mode. An acknowledge is sent by the master after each read byte to allow data transfer to continue. A not-acknowledge is sent when the master reads the final byte of data from the MAX31889, followed by a STOP condition.

Figure 4. I<sup>2</sup>C START, STOP, and REPEATED START Conditions

Figure 5. I<sup>2</sup>C Acknowledge Bit

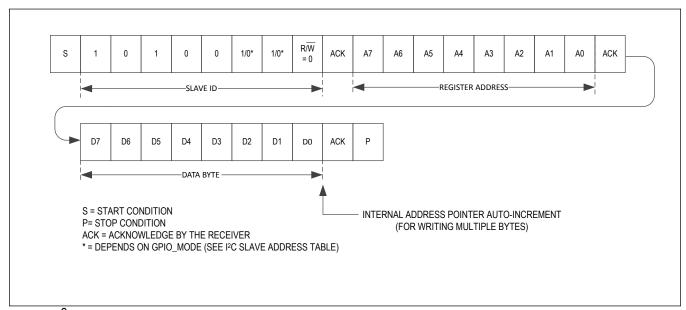

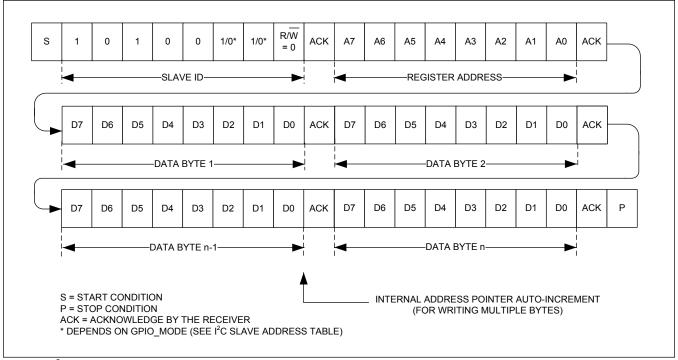

#### I<sup>2</sup>C Write Data Format

A write to the MAX31889 includes transmission of a START condition, the slave address with the R/W bit set to 0, one byte of data to configure the internal register address pointer, one or more bytes of data, and a STOP condition. Figure 6 illustrates the proper frame format for writing one byte of data to the MAX31889. Figure 7 illustrates the frame format for writing n-bytes of data to the MAX31889.

The master first sends the slave address with the R/W bit set to 0. This indicates that the master intends to write data to the MAX31889. The MAX31889 acknowledges receipt of the address byte during the master-generated 9th SCL pulse.

The second byte transmitted from the master configures the MAX31889's internal register address pointer. The pointer tells the MAX31889 where to write the next byte of data. An acknowledge pulse is sent by the MAX31889 upon receipt of the address pointer data.

The third byte sent to the MAX31889 contains the data that will be written to the chosen register. An acknowledge pulse from the MAX31889 signals receipt of the data byte. The address pointer auto increments to the next register address after each received data byte. This auto-increment feature allows a master to write to sequential registers within one continuous frame. The master signals the end of transmission by issuing a STOP condition. The auto\_increment feature is disabled when there is an attempt to write to the FIFO\_DATA (0x08) register.

Figure 6. I<sup>2</sup>C Single Byte Write Transaction

Figure 7. I<sup>2</sup>C Multi-Byte Write Transaction

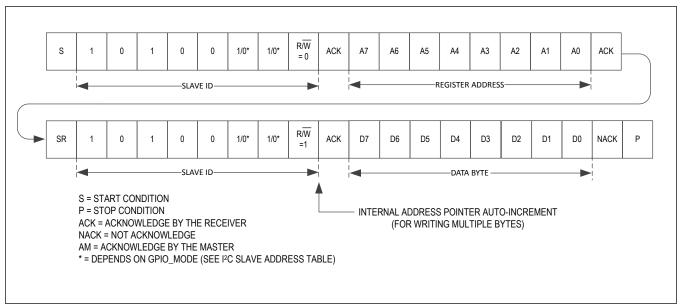

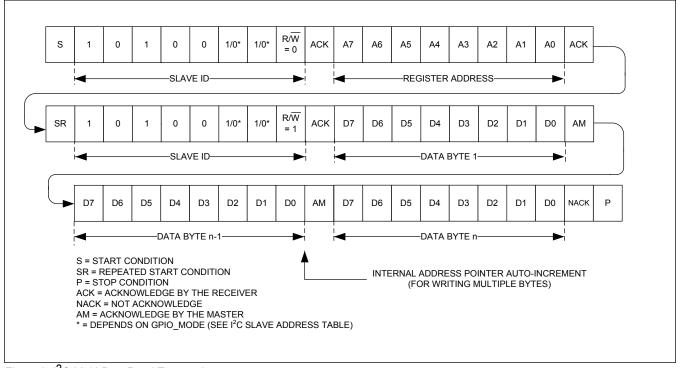

#### I<sup>2</sup>C Read Data Format

The master sends the slave address with the  $R/\overline{W}$  bit set to 1 to initiate a read operation. The MAX31889 acknowledges receipt of its slave address by pulling SDA low during the 9th SCL clock pulse. A START command followed by a read command resets the address pointer to register 0x00.

The first byte transmitted from the MAX31889 will be the contents of register 0x00. Transmitted data is valid on the rising edge of SCL. The address pointer auto-increments after each read data byte. This auto-increment feature allows all registers to be read sequentially within one continuous frame. The auto\_increment feature is disabled when there is an attempt to read from the FIFO\_DATA register, this allows for burst reading of the FIFO\_DATA register. A STOP condition can be issued after any number of read data bytes. If a STOP condition is issued followed by another read operation, the first data byte to be read will be from register 0x00.

The address pointer can be preset to a specific register before a read command is issued. The master presets the address pointer by first sending the MAX31889 slave address with the R/W bit set to 0 followed by the register address. A REPEATED START condition is then sent followed by the slave address with the R/W bit set to 1. The MAX31889 then transmits the content of the specified register. The address pointer auto-increments after transmitting the first byte.

The master acknowledges receipt of each read byte during the acknowledge clock pulse. The master must acknowledge all correctly received bytes except the last byte. The final byte must be followed by a not acknowledge from the master and then a STOP condition. <u>Figure 8</u> illustrates the frame format for reading one byte from the MAX31889. <u>Figure 9</u> illustrates the frame format for reading multiple bytes from the MAX31889.

Figure 8. I<sup>2</sup>C Single Byte Read Transaction

Figure 9. I<sup>2</sup>C Multi-Byte Read Transaction

## **FIFO Description**

The FIFO is 32 samples long and is designed for 16-bit wide temperature data. The master does a burst read of two

bytes starting at register 0x08 to read one 16-bit temperature sample, referred to as a word, from the FIFO. The master reads 2N bytes from the FIFO to get N samples.

There are seven registers that control how the FIFO is configured and read out. These registers are described in <u>Table</u> 4.

## Table 4. FIFO Register Map

| ADDRESS | REGISTER NAME         | В7 | В6               | B5                 | B4               | В3             | B2          | B1      | В0 |  |  |  |

|---------|-----------------------|----|------------------|--------------------|------------------|----------------|-------------|---------|----|--|--|--|

| 0x04    | FIFO Write Pointer    | -  | -                | -                  | FIFO_WR_PTR[4:0] |                |             |         |    |  |  |  |

| 0x05    | FIFO Read Pointer     | -  | -                | - FIFO_RD_PTR[4:0] |                  |                |             |         |    |  |  |  |

| 0x06    | FIFO Overflow Counter | -  | OVF_COUNTER[4:0] |                    |                  |                |             |         |    |  |  |  |

| 0x07    | FIFO Data Counter     | -  | -                |                    |                  | FIFO_DATA_CC   | DUNT[5:0]   |         |    |  |  |  |

| 0x08    | FIFO Data Register    |    |                  |                    |                  | FIFO_DATA[7:0] |             |         |    |  |  |  |

| 0x09    | FIFO Configuration 1  | -  | -                | -                  | FIFO_A_FULL[4:0] |                |             |         |    |  |  |  |

| 0x0A    | FIFO Configuration 2  | -  | -                | -                  | FLUSH_FIFO       | FIFO_STAT_CLR  | A_FULL_TYPE | FIFO_RO | -  |  |  |  |

#### FIFO\_WR\_PTR (address 0x04), Write Pointer

FIFO\_WR\_PTR[4:0] points to the FIFO location where the next word is to be written. This pointer advances for each word pushed on to the FIFO by the internal conversion process. The write pointer is updated from 5 bit counter and wraps around to count 0x00 from count 0x1F.

#### FIFO\_RD\_PTR (address 0x05), Read Pointer

FIFO\_RD\_PTR[4:0] points to the location from where the next word from the FIFO is to be read through the serial interface. This advances each time a word is read from the FIFO. The read pointer can be both read and written to. This allows a word to be reread from the FIFO if it has not already been overwritten. The read pointer is updated from a 5 bit counter and wraps around to count 0x00 from count 0x1F.

#### OVF\_COUNTER (address 0x06), Overflow Counter

OVF\_COUNTER[4:0] logs the number of words lost if new words are written after the FIFO is full. This counter saturates at count value 0x1F. Each time a complete word is popped from the FIFO (when the read pointer advances), the OVF\_COUNTER is reset to zero. This counter is essentially a debug tool. It should be read immediately before reading the FIFO in order to check if an overflow condition has occurred.

#### FIFO\_DATA\_COUNT (address 0x07), FIFO Data Counter

FIFO\_DATA\_COUNT[5:0] is a read-only register which holds the number of words available in the FIFO for the master to read. This increments when a new word is pushed to the FIFO, and decrements when the master reads a word from the FIFO.

#### FIFO\_DATA (address 0x08), FIFO Data

FIFO\_DATA[7:0] is a read-only register used to retrieve data from the FIFO. It is important to burst read the data from the FIFO. Each word is two bytes. So burst reading two bytes at FIFO\_DATA register through the serial interface advances the FIFO\_RD\_PTR by one. This configuration is best illustrated by the examples below.

Table 5 shows the Temperature Data format in the FIFO.

#### **Table 5. Temperature FIFO Data Format**

|       | FIFO DATA FORMAT (FIFO_DATA[15:0])                                                    |     |     |     |     |    |    |    |    |    |    |      |    |    |    |

|-------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|----|----|----|----|----|----|------|----|----|----|

| Bit15 | Bit15 Bit14 Bit13 Bit12 Bit11 Bit10 Bit9 Bit8 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 |     |     |     |     |    |    |    |    |    |    | Bit0 |    |    |    |

| T15   | T14                                                                                   | T13 | T12 | T11 | T10 | Т9 | T8 | T7 | T6 | T5 | T4 | T3   | T2 | T1 | T0 |

#### **FIFO DATA Read Example**

Number of samples available in the FIFO after the last read can be obtained by reading the OVF\_COUNTER[4:0] and FIFO\_DATA\_COUNT[5:0] registers using the following pseudo-code:

read the OVF\_COUNTER register

read the FIFO\_DATA\_COUNT register

if OVF\_COUNTER == 0 //no overflow occurred

NUM\_AVAILABLE\_SAMPLES = FIFO\_DATA\_COUNT

else

NUM AVAILABLE SAMPLES = 32 // overflow occurred and data has been lost

FIFO\_WR\_PTR[4:0] and FIFO\_RD\_PTR[4:0] are available for debug. They may also be used to calculate the number of available samples using the following pseudo-code:

If OVF\_COUNTER is zero,

NUM\_AVAILABLE\_WORDS = FIFO\_WR\_PTR - FIFO\_RD\_PTR

(Note: pointer wrap around should be taken into account)

else

NUM AVAILABLE WORDS = 32

<u>Table 6</u> shows the order in which the two bytes of the Temperature Data are read through the serial interface.

**Table 6. FIFO Data Read Format**

| SAMPLE NUMBER | BYTE NUMBER |      |      | FIFO | DATA R | EAD FOR | RMAT |      |      |

|---------------|-------------|------|------|------|--------|---------|------|------|------|

|               |             | Bit7 | Bit6 | Bit5 | Bit4   | Bit3    | Bit2 | Bit1 | Bit0 |

| Sample N      | 1           | T15  | T14  | T13  | T12    | T11     | T10  | Т9   | Т8   |

|               | 2           | T7   | T6   | T5   | T4     | Т3      | T2   | T1   | T0   |

| Sample N+1    | 1           | T15  | T14  | T13  | T12    | T11     | T10  | Т9   | Т8   |

|               | 2           | T7   | T6   | T5   | T4     | Т3      | T2   | T1   | T0   |

| Sample N+2    | 1           | T15  | T14  | T13  | T12    | T11     | T10  | Т9   | Т8   |

|               | 2           | T7   | T6   | T5   | T4     | T3      | T2   | T1   | T0   |

|               |             |      |      |      |        |         |      |      |      |

| Sample N+31   | 1           | T15  | T14  | T13  | T12    | T11     | T10  | Т9   | Т8   |

|               | 2           | T7   | T6   | T5   | T4     | Т3      | T2   | T1   | T0   |

#### FIFO A FULL (address 0x09), FIFO Almost Full

The FIFO\_A\_FULL[4:0] field in the FIFO Configuration 1 (0x09) register sets the application custom threshold for the FIFO and determines when the A\_FULL bit in the STATUS (0x00) register is asserted. The A\_FULL bit is set when the FIFO contains 32 minus FIFO\_A\_FULL[4:0] words. For example, when FIFO\_A\_FULL is set to 2, the flag is set when the 30<sup>th</sup> word is written to the FIFO. When the FIFO almost full condition is met, the A\_FULL bit is asserted in the STATUS register. If the A\_FULL\_EN bit in the INTERRUPT\_ENABLE (0x01) register is set and GPIO0\_MODE = 0x3 in the GPIO\_SETUP (0x20) register, then the interrupt is asserted on the GPIO0 pin. This condition should prompt the applications processor to read samples from the FIFO before it fills.

Before reading the data out of the FIFO, the application processor has to determine the number of available temperature samples. This can be accomplished by reading the OVF\_COUNTER and FIFO\_DATA\_COUNT registers.

#### FIFO\_RO (address 0x0A), FIFO Rollover

The FIFO\_RO bit in the FIFO Configuration 2 (0x0A) register determines whether samples get pushed on to the FIFO or discarded when it is full. If FIFO\_RO is enabled when FIFO is full, old samples are overwritten. If FIFO\_RO is not set, the new sample is discarded and the FIFO is not updated.

#### A\_FULL\_TYPE (address 0x0A), Almost Full Type

The A\_FLL\_TYPE bit defines the behavior of the A\_FULL interrupt. If the A\_FIFO\_TYPE bit is set low, the A\_FULL interrupt gets asserted when the A\_FULL condition is detected and cleared by a STATUS register read, then reasserts for every sample if the A\_FULL condition persists. If the A\_FIFO\_TYPE bit is set high, the A\_FULL status bit is asserted only when a new A\_FULL condition is detected. The status bit is cleared by a STATUS register read and does not reassert

for every sample until a new A FULL condition is detected.

#### FIFO\_STAT\_CLR (address 0x0A), FIFO Status Clear

The FIFO\_STAT\_CLR bit defines whether the A\_FULL status bit should clear by a FIFO\_DATA register read. If FIFO\_STAT\_CLR is set low, A\_FULL and TEMP\_RDY status bits are not get cleared by FIFO\_DATA register read but are cleared by STATUS register read. If FIFO\_STAT\_CLR is set high, A\_FULL and TEMP\_RDY status bits are cleared by a FIFO\_DATA register read or a STATUS register read.

## FLUSH\_FIFO (address 0x0A)

The FLUSH\_FIFO bit is used for flushing the FIFO. The FIFO becomes empty and the FIFO\_WR\_PTR[4:0], FIFO\_RD\_PTR[4:0], FIFO\_DATA\_COUNT[5:0] and OVF\_COUNTER[4:0] are reset to zero. FLUSH\_FIFO is a self-clearing bit.

# **Register Map**

# **Register Map**

| ADDRESS    | NAME                            | MSB           |                |   |                  |                   |                 |                | LSB             |

|------------|---------------------------------|---------------|----------------|---|------------------|-------------------|-----------------|----------------|-----------------|

| INTERRUP   | T AND STATUS                    |               |                |   |                  |                   |                 |                |                 |

| 0x00       | STATUS[7:0]                     | A_FULL        | _              | _ | _                | _                 | TEMP_L<br>O     | TEMP_H         | TEMP_R<br>DY    |

| 0x01       | INTERRUPT<br>ENABLE[7:0]        | A_FULL<br>_EN | _              | _ | -                | _                 | TEMP_L<br>O_EN  | TEMP_H<br>I_EN | TEMP_R<br>DY_EN |

| FIFO       |                                 |               |                |   |                  |                   |                 | •              |                 |

| 0x04       | FIFO WRITE<br>POINTER[7:0]      | _             | _              | _ |                  | FIFO              | D_WR_PTR        | [4:0]          |                 |

| 0x05       | FIFO READ<br>POINTER[7:0]       | _             | _              | _ |                  | FIF               | D_RD_PTR        | [4:0]          |                 |

| 0x06       | FIFO OVERFLOW COUNTER[7:0]      | _             | _              | _ |                  | OVF               | _COUNTER        | R[4:0]         |                 |

| 0x07       | FIFO DATA<br>COUNTER[7:0]       | _             | _              |   | F                | IFO_DATA          | _COUNT[5:       | 0]             |                 |

| 0x08       | FIFO DATA[7:0]                  |               | FIFO_DATA[7:0] |   |                  |                   |                 |                |                 |

| 0x09       | FIFO<br>CONFIGURATION<br>1[7:0] | _             | _              | _ | FIFO_A_FULL[4:0] |                   |                 |                |                 |

| 0x0A       | FIFO<br>CONFIGURATION<br>2[7:0] | _             | _              | _ | FLUSH_<br>FIFO   | FIFO_ST<br>AT_CLR | A_FULL<br>_TYPE | FIFO_R<br>O    | -               |

| SYSTEM     |                                 |               |                | • | •                |                   |                 |                |                 |

| 0x0C       | SYSTEM<br>CONTROL[7:0]          | _             | _              | _ | _                | _                 | _               | _              | RESET           |

| TEMPERAT   | URE                             |               |                |   |                  |                   |                 |                |                 |

| 0x10       | ALARM HIGH MSB[7:0]             |               |                |   | ALARM_H          | I_MSB[7:0]        |                 |                |                 |

| 0x11       | ALARM HIGH LSB[7:0]             |               |                |   | ALARM_H          | I_LSB[7:0]        |                 |                |                 |

| 0x12       | ALARM LOW MSB[7:0]              |               |                |   | ALARM_LO         | D_MSB[7:0]        |                 |                |                 |

| 0x13       | ALARM LOW LSB[7:0]              |               |                |   | ALARM_L          | O_LSB[7:0]        |                 |                |                 |

| 0x14       | TEMP SENSOR<br>SETUP[7:0]       | RFU           | [1:0]          | _ | _                | _                 | _               | _              | CONVE<br>RT_T   |

| GPIO       |                                 |               |                |   |                  |                   |                 |                |                 |

| 0x20       | GPIO SETUP[7:0]                 | GPIO1_M       | 1ODE[1:0]      | _ | _                | _                 | _               | GPIO0_N        | IODE[1:0]       |

| 0x21       | GPIO CONTROL[7:0]               | _             | _              | _ | _                | GPIO1_L<br>L      | _               | _              | GPIO0_L<br>L    |

| IDENTIFIER | RS                              |               |                |   |                  |                   |                 |                |                 |

| 0x31       | ROM ID 1[7:0]                   | ROM_ID1[7:0]  |                |   |                  |                   |                 |                |                 |

| 0x32       | ROM ID 2[7:0]                   | ROM_ID2[7:0]  |                |   |                  |                   |                 |                |                 |

| 0x33       | ROM ID 3[7:0]                   | ROM_ID3[7:0]  |                |   |                  |                   |                 |                |                 |

| 0x34       | ROM ID 4[7:0]                   |               | ROM_ID4[7:0]   |   |                  |                   |                 |                |                 |

| 0x35       | ROM ID 5[7:0]                   |               | ROM_ID5[7:0]   |   |                  |                   |                 |                |                 |

| 0x36       | ROM ID 6[7:0]                   |               |                |   | ROM_I            | D6[7:0]           |                 |                |                 |

# MAX31889

| ADDRESS | NAME                 | MSB |  |       |         |  | LSB |

|---------|----------------------|-----|--|-------|---------|--|-----|

| 0xFF    | PART IDENTIFIER[7:0] |     |  | PART_ | ID[7:0] |  |     |

# **Register Details**

# STATUS (0x0)

| BIT            | 7         | 6 | 5 | 4 | 3 | 2         | 1         | 0         |

|----------------|-----------|---|---|---|---|-----------|-----------|-----------|

| Field          | A_FULL    | - | _ | _ | - | TEMP_LO   | TEMP_HI   | TEMP_RDY  |

| Reset          | 0b0       | _ | _ | _ | _ | 0b0       | 0b0       | 0b0       |

| Access<br>Type | Read Only | - | _ | - | - | Read Only | Read Only | Read Only |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A_FULL   | 7    | This is a read-only bit. This bit is cleared when the STATUS register is read. It is also cleared when FIFO_DATA register is read, if FIFO_STAT_CLR = 1.                                                                                                                                                                                                                                                                                                                                                                                                      |

| TEMP_LO  | 2    | Temperature Sensor Alarm Low status bit:  This bit is asserted when the latest temperature sensor measurement is less than what is programmed in the Temperature Sensor Alarm Low register. When this bit is asserted and if the TEMP_LO_EN bit is set to 1, it then asserts the interrupt on the GPIO0 pin when programmed as an interrupt output. The master needs to read the status register to determine if the interrupt was asserted by the TEMP_LO status. This bit is cleared after the STATUS register is read.                                     |

| TEMP_HI  | 1    | Temperature Sensor Alarm High status bit:  This bit is asserted when the latest temperature sensor measurement is greater than what is programmed in the Temperature Sensor Alarm High register. When this bit is asserted and if the TEMP_HI_EN bit is set to 1, it then asserts the interrupt on the GPIO0 pin when programmed as interrupt output. The master needs to read the status register to determine if the interrupt was asserted by the TEMP_HI status. This bit is cleared after the STATUS register is read.                                   |

| TEMP_RDY | 0    | Temperature Sensor Conversion Complete status bit:  This bit is asserted when a temperature sensor measurement has completed and new data is available to be read by the master. When this bit is asserted and if TEMP_RDY_EN bit is set to 1, it then asserts the interrupt on the GPIO0 pin when programmed as an interrupt output. The master needs to read the status register to determine if the interrupt was asserted by the TEMP_RDY status. This bit is cleared after the STATUS register is read or after the Temperature Data registers are read. |

## **INTERRUPT ENABLE (0x1)**

| BIT            | 7             | 6 | 5 | 4 | 3 | 2              | 1              | 0               |

|----------------|---------------|---|---|---|---|----------------|----------------|-----------------|

| Field          | A_FULL_E<br>N | - | _ | - | _ | TEMP_LO_<br>EN | TEMP_HI_<br>EN | TEMP_RDY<br>_EN |

| Reset          | 0b0           | _ | _ | _ | _ | 0b0            | 0b0            | 0b0             |

| Access<br>Type | Write, Read   | - | _ | - | _ | Write, Read    | Write, Read    | Write, Read     |

| BITFIELD    | BITS | DESCRIPTION                                                                                                                                                                                                                          |

|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A_FULL_EN   | 7    | Set A_FULL_EN to 1 to enable the A_FULL interrupt on GPIO0 when programmed as an interrupt output. Set A_FULL_EN to 0 to disable the A_FULL interrupt.                                                                               |

| TEMP_LO_EN  | 2    | Temperature Sensor Alarm Low Interrupt Enable :  Set TEMP_LO_EN to 1 to enable the TEMP_LO interrupt on the GPIO0 pin when programmed as an interrupt output. Set TEMP_LO_EN to 0 to disable the TEMP_LO interrupt.                  |

| TEMP_HI_EN  | 1    | Temperature Sensor Alarm High Interrupt Enable:  Set TEMP_HI_EN to 1 to enable the TEMP_HI interrupt on the GPIO0 pin when programmed as an interrupt output. Set TEMP_HI_EN to 0 to disable the TEMP_HI interrupt.                  |

| TEMP_RDY_EN | 0    | Temperature Sensor Conversion Complete Interrupt Enable bit:  Set TEMP_RDY_EN to 1 to enable the TEMP_RDY interrupt on the GPIO0 pin when programmed as an interrupt output. Set TEMP_RDY_EN to 0 to disable the TEMP_RDY interrupt. |

## **FIFO WRITE POINTER (0x04)**

| BIT            | 7  | 6    | 5 | 4                | 3    | 2 | 1 | 0        |  |  |

|----------------|----|------|---|------------------|------|---|---|----------|--|--|

| Field          | _  | _    | _ | FIFO_WR_PTR[4:0] |      |   |   |          |  |  |

| Reset          | _  | _    | _ |                  | 0x00 |   |   |          |  |  |

| Access<br>Type | -  | _    | _ | Read Only        |      |   |   |          |  |  |

| BITFIE         | LD | BITS |   | DESCRIPTION      |      |   |   | <u> </u> |  |  |

| BITFIELD    | BITS | DESCRIPTION                                   |

|-------------|------|-----------------------------------------------|

| FIFO_WR_PTR | 4:0  | See the FIFO Description section for details. |

## **FIFO READ POINTER (0x05)**

| BIT            | 7  | 6    | 5 | 4           | 3                | 2 | 1 | 0 |  |  |

|----------------|----|------|---|-------------|------------------|---|---|---|--|--|

| Field          | _  | _    | _ |             | FIFO_RD_PTR[4:0] |   |   |   |  |  |

| Reset          | _  | _    | _ |             | 0x00             |   |   |   |  |  |

| Access<br>Type | _  | _    | _ |             | Write, Read, Ext |   |   |   |  |  |

| BITFIE         | LD | BITS |   | DESCRIPTION |                  |   |   |   |  |  |

| BITFIELD    | BITS | DESCRIPTION                                   |

|-------------|------|-----------------------------------------------|

| FIFO_RD_PTR | 4:0  | See the FIFO Description section for details. |

## **FIFO OVERFLOW COUNTER (0x06)**

| BIT            | 7 | 6 | 5 | 4         | 3                | 2 | 1 | 0 |  |  |

|----------------|---|---|---|-----------|------------------|---|---|---|--|--|

| Field          | _ | _ | _ |           | OVF_COUNTER[4:0] |   |   |   |  |  |

| Reset          | _ | _ | _ | 0x00      |                  |   |   |   |  |  |

| Access<br>Type | _ | _ | _ | Read Only |                  |   |   |   |  |  |

# MAX31889

| BITFIELD    | BITS | DESCRIPTION                                   |

|-------------|------|-----------------------------------------------|

| OVF_COUNTER | 4:0  | See the FIFO Description section for details. |

## **FIFO DATA COUNTER (0x07)**

| BIT            | 7 | 6 | 5                    | 4         | 3 | 2 | 1 | 0 |  |  |

|----------------|---|---|----------------------|-----------|---|---|---|---|--|--|

| Field          | _ | _ | FIFO_DATA_COUNT[5:0] |           |   |   |   |   |  |  |

| Reset          | _ | _ |                      | 0x00      |   |   |   |   |  |  |

| Access<br>Type | _ | _ |                      | Read Only |   |   |   |   |  |  |

| BITFIELD        | BITS | DESCRIPTION                                   |

|-----------------|------|-----------------------------------------------|

| FIFO_DATA_COUNT | 5:0  | See the FIFO Description section for details. |

## FIFO DATA (0x08)

| BIT            | 7              | 6    | 5 | 4    | 3    | 2 | 1 | 0 |  |

|----------------|----------------|------|---|------|------|---|---|---|--|

| Field          | FIFO_DATA[7:0] |      |   |      |      |   |   |   |  |

| Reset          |                | 0x00 |   |      |      |   |   |   |  |

| Access<br>Type |                |      |   | Read | Only |   |   |   |  |

| BITFIELD  | BITS | DESCRIPTION                                   |

|-----------|------|-----------------------------------------------|

| FIFO_DATA | 7:0  | See the FIFO Description section for details. |

## FIFO CONFIGURATION 1 (0x09)

| Reset<br>Access | _ | _ | _ | 0x0F        |  |  |  |  |

|-----------------|---|---|---|-------------|--|--|--|--|

| Access<br>Type  | _ | _ | _ | Write, Read |  |  |  |  |

| BITFIELD    | BITS | DESCRIPTION                                   |

|-------------|------|-----------------------------------------------|

| FIFO_A_FULL | 4:0  | See the FIFO Description section for details. |

## **FIFO CONFIGURATION 2 (0x0A)**

| BIT            | 7 | 6 | 5 | 4              | 3                 | 2               | 1           | 0 |

|----------------|---|---|---|----------------|-------------------|-----------------|-------------|---|

| Field          | _ | _ | _ | FLUSH_FIF<br>O | FIFO_STAT<br>_CLR | A_FULL_TY<br>PE | FIFO_RO     | 1 |

| Reset          | _ | _ | _ | 0b0            | 0b0               | 0b0             | 0b0         | 1 |

| Access<br>Type | _ | _ | _ | Write, Read    | Write, Read       | Write, Read     | Write, Read | 1 |

| BITFIELD      | BITS | DESCRIPTION                                   |

|---------------|------|-----------------------------------------------|

| FLUSH_FIFO    | 4    | See the FIFO Description section for details. |

| FIFO_STAT_CLR | 3    | See the FIFO Description section for details. |

| A_FULL_TYPE   | 2    | See the FIFO Description section for details. |

| FIFO_RO       | 1    | See the FIFO Description section for details. |

## **SYSTEM CONTROL (0x0C)**

| BIT            | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0          |

|----------------|---|---|---|---|---|---|---|------------|

| Field          | _ | _ | _ | _ | _ | _ | _ | RESET      |

| Reset          | _ | _ | _ | _ | _ | _ | _ | 0b0        |

| Access<br>Type | _ | _ | _ | _ | _ | _ | _ | Write Only |

| BITFIELD | BITS | DESCRIPTION                                                                                        |

|----------|------|----------------------------------------------------------------------------------------------------|

| RESET    | 0    | Setting this bit to 1 resets all register settings to default values. This is a self-clearing bit. |

## **ALARM HIGH MSB (0x10)**

This is the most significant byte of the alarm high threshold.

| BIT            | 7 6 5 4 3 2 1 0 |                   |  |        |      |  |  |  |  |  |

|----------------|-----------------|-------------------|--|--------|------|--|--|--|--|--|

| Field          |                 | ALARM_HI_MSB[7:0] |  |        |      |  |  |  |  |  |

| Reset          |                 | 0x7F              |  |        |      |  |  |  |  |  |

| Access<br>Type |                 |                   |  | Write, | Read |  |  |  |  |  |

| BITFIELD     | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |

|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |      | Alarm High Threshold Most Significant Byte:                                                                                                                                                                                                                                                                                                         |

| ALARM_HI_MSB | 7:0  | The ALARM_HI_MSB[7:0] bits are the most significant byte of the 16-bit temperature sensor alarm high bits. The ALARM_HI_MSB[7:0] and the ALARM_HI_LSB[7:0] bits form the full 16-bit temperature sensor alarm high threshold. The default for Alarm High Threshold is 0x7FFF, which is the highest temperature setting and also disables the alarm. |

## **ALARM HIGH LSB (0x11)**

| BIT            | 7 | 6                 | 5 | 4      | 3    | 2 | 1 | 0 |  |  |  |

|----------------|---|-------------------|---|--------|------|---|---|---|--|--|--|

| Field          |   | ALARM_HI_LSB[7:0] |   |        |      |   |   |   |  |  |  |

| Reset          |   | 0xFF              |   |        |      |   |   |   |  |  |  |

| Access<br>Type |   |                   |   | Write, | Read |   |   |   |  |  |  |

| BITFIELD     | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |

|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |      | Alarm High Threshold Least Significant Byte:                                                                                                                                                                                                                                                                                                         |

| ALARM_HI_LSB | 7:0  | The ALARM_HI_LSB[7:0] bits are the least significant byte of the 16-bit temperature sensor alarm high bits. The ALARM_HI_MSB[7:0] and the ALARM_HI_LSB[7:0] bits form the full 16-bit temperature sensor alarm high threshold. The default for Alarm High Threshold is 0x7FFF, which is the highest temperature setting and also disables the alarm. |

## **ALARM LOW MSB (0x12)**

| BIT            | 7 | 6                 | 5 | 4      | 3    | 2 | 1 | 0 |  |  |  |

|----------------|---|-------------------|---|--------|------|---|---|---|--|--|--|

| Field          |   | ALARM_LO_MSB[7:0] |   |        |      |   |   |   |  |  |  |

| Reset          |   | 0x80              |   |        |      |   |   |   |  |  |  |

| Access<br>Type |   |                   |   | Write, | Read |   |   |   |  |  |  |

| BITFIELD     | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALARM_LO_MSB | 7:0  | Alarm High Threshold Most Significant Byte:  The ALARM_LO_MSB[7:0] bits are the most significant byte of the 16-bit temperature sensor alarm low bits. The ALARM_LO_MSB[7:0] and the ALARM_LO_LSB[7:0] bits form the full 16-bit temperature sensor Alarm Low Threshold. The default for Alarm Low Threshold is 0x8000, which is the lowest temperature setting and also disables the alarm. |

## **ALARM LOW LSB (0x13)**

| BIT            | 7 | 6                 | 5 | 4      | 3    | 2 | 1 | 0 |  |  |  |

|----------------|---|-------------------|---|--------|------|---|---|---|--|--|--|

| Field          |   | ALARM_LO_LSB[7:0] |   |        |      |   |   |   |  |  |  |

| Reset          |   | 0x00              |   |        |      |   |   |   |  |  |  |

| Access<br>Type |   |                   |   | Write, | Read |   |   |   |  |  |  |

| BITFIELD     | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |

|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |      | Alarm Low Threshold Least Significant Byte:                                                                                                                                                                                                                                                                                                        |

| ALARM_LO_LSB | 7:0  | The ALARM_LO_LSB[7:0] bits are the least significant byte of the 16-bit temperature sensor alarm high bits. The ALARM_LO_MSB[7:0] and the ALARM_LO_LSB[7:0] bits form the full 16-bit temperature sensor Alarm High Threshold. The default for Alarm Low Threshold is 0x8000, which is the lowest temperature setting and also disables the alarm. |

## **TEMP SENSOR SETUP (0x14)**

| BIT            | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0             |

|----------------|-----------|---|---|---|---|---|---|---------------|

| Field          | RFU[1:0]  |   | _ | - | _ | _ | _ | CONVERT_<br>T |

| Reset          | 0b11      |   | - | - | - | - | - | 0b0           |

| Access<br>Type | Read Only |   | _ | _ | _ | _ | _ | Write, Read   |

| BITFIELD  | BITS | DESCRIPTION                                                                                                                                                                                     |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFU       | 7:6  | These bits are reserved for future use. When writing to this register, these bits must always be set to 1.                                                                                      |

| CONVERT_T | 0    | Start Temperature measturement  Writing '1' to this field starts temperature measurement. This is a self clearing bit, and automatically reset to 0 when the temperature measurement completes. |

## **GPIO SETUP (0x20)**

| BIT            | 7               | 6    | 5 | 4 | 3 | 2 | 1               | 0    |

|----------------|-----------------|------|---|---|---|---|-----------------|------|

| Field          | GPIO1_MODE[1:0] |      | _ | _ | _ | _ | GPIO0_MODE[1:0] |      |

| Reset          | 0b10            |      | _ | _ | _ | _ | 0b              | 10   |

| Access<br>Type | Write,          | Read | _ | _ | _ | _ | Write,          | Read |

| BITFIELD   | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                        |

|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO1_MODE | 7:6  | 00 = Digital input (HiZ). GPIO1 logic level read from the GPIO1_LL bit in the GPIO_CONTROL register. 01 = Digital output (open-drain). Set GPIO1 logic level by writing to the GPIO1_LL bit in the GPIO_CONTROL register. 10 = Digital Input with $1M\Omega$ pulldown. 11 = Convert Temperature Input (active low) |

| GPIO0_MODE | 1:0  | 00 = Digital input (HiZ). GPIO0 logic level read from the GPIO0_LL bit in the GPIO_CONTROL register. 01 = Digital output (open-drain). Set GPIO0 logic level by writing to the GPIO0_LL bit in the GPIO_CONTROL register. 10 = Digital Input with $1M\Omega$ pulldown. 11 = INTB (open-drain, active low)          |

## **GPIO CONTROL (0x21)**

| BIT            | 7 | 6 | 5 | 4 | 3           | 2 | 1 | 0           |

|----------------|---|---|---|---|-------------|---|---|-------------|

| Field          | _ | _ | _ | _ | GPIO1_LL    | _ | _ | GPIO0_LL    |

| Reset          | _ | _ | _ | _ | 0b0         | _ | _ | 0b0         |

| Access<br>Type | - | _ | _ | _ | Write, Read | _ | - | Write, Read |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                            |