**Features**

## SPI/MICROWIRE-Compatible UART with Integrated True Fail-Safe RS-485/RS-422 Transceivers

### **General Description**

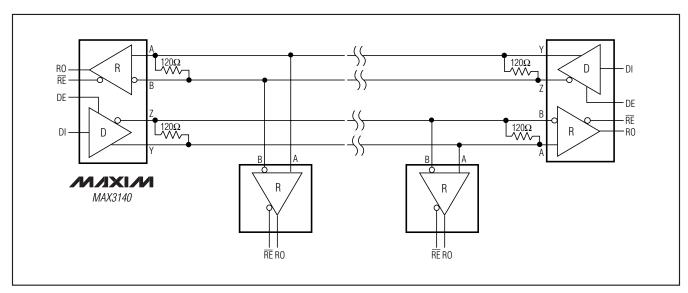

The MAX3140 is a complete universal asynchronous receiver-transmitter (UART) and a true fail-safe RS-485/RS-422 transceiver combined in a single 28-pin QSOP package for space-, cost-, and power-constrained applications. The MAX3140 saves additional board space as well as microcontroller (µC) I/O pins by featuring an SPI™/QSPI™/MICROWIRE™-compatible serial interface. It is pin-programmable for configuration in all RS-485/RS-422 networks.

The MAX3140 includes a single RS-485/RS-422 driver and receiver featuring true fail-safe circuitry, which guarantees a logic-high receiver output when the receiver inputs are open or shorted. This feature provides immunity to faults without requiring complex termination. The MAX3140 provides software-selectable control of half- or full-duplex operation, data rate, slew rate, and transmitter and receiver phase. The RS-485 driver slew rate is programmable to minimize EMI and results in maximum data rates of 115kbps, 500kbps, and 10Mbps. Independent transmitter/receiver phase control enables software correction of twisted-pair polarity reversal. A 1/8-unit-load receiver input impedance allows up to 256 transceivers on the bus.

The MAX3140's UART includes an oscillator circuit derived from an external crystal, and a baud-rate generator with software-programmable divider ratios for all common baud rates from 300 baud to 230k baud. The UART features an 8-word-deep receive FIFO that minimizes processor overhead and provides a flexible interrupt with four maskable sources, including address recognition on 9-bit networks. Two control lines are included for hardware handshaking—one input and one output.

The MAX3140 operates from a single +5V supply and typically consumes only 645µA with the receiver active. Hardware-invoked shutdown reduces supply current to only 20µA. The UART and RS-485/RS-422 functions can be used together or independently since the two functions share only supply and ground connections (the MAX3140 is hardware- and software-compatible with the MAX3100 and MAX3089).

### **Applications**

Industrial-Control Transceivers for EMI-Local Area Networks Sensitive Applications **HVAC** and Building Control **Embedded Systems** Point-of-Sale Devices Intelligent Instrumentation

SPI/QSPI are trademarks of Motorola. Inc. MICROWIRE is a trademark of National Semiconductor Corp.

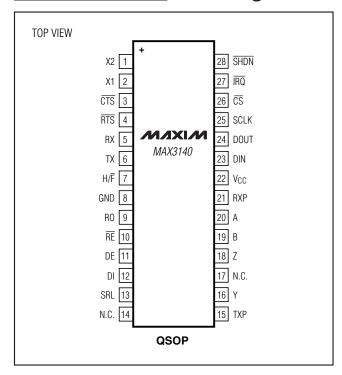

Pin Configuration appears at end of data sheet.

### ♦ Integrated UART and RS-485/RS-422 Transceiver in a Single 28-Pin QSOP

- ♦ SPI/MICROWIRE-Compatible Interface Saves µC I/O Pins

- **♦ True Fail-Safe Receiver Output Eliminates Complex Network Termination**

- ♦ Pin-Programmable RS-485/RS-422 Features Half/Full-Duplex Operation Slew-Rate Limiting for Reduced EMI 115kbps/500kbps/10Mbps Data Rates Receiver/Transmitter Phase for Twisted-Pair **Polarity Reversal**

- **♦ Full-Featured UART**

- Programmable Up to 230k baud with a 3.6864MHz Crystal

- 8-Word Receive FIFO Minimizes Processor Overhead

- 9-Bit Address-Recognition Interrupt

- ♦ Allows Up to 256 Transceivers on the Bus

- ♦ Low 20µA Hardware Shutdown Mode

- **♦** Hardware/Software-Compatible with MAX3100 and MAX3089

### **Ordering Information**

| PART        | TEMP. RANGE    | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX3140CEI+ | 0°C to +70°C   | 28 QSOP     |

| MAX3140EEI+ | -40°C to +85°C | 28 QSOP     |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

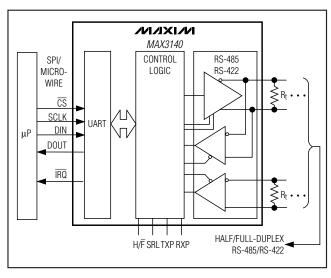

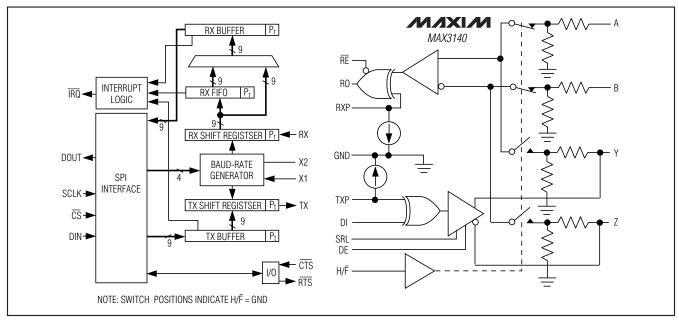

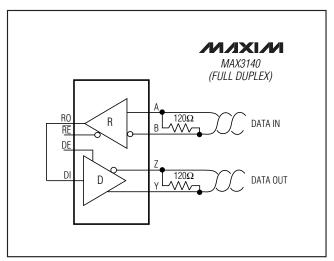

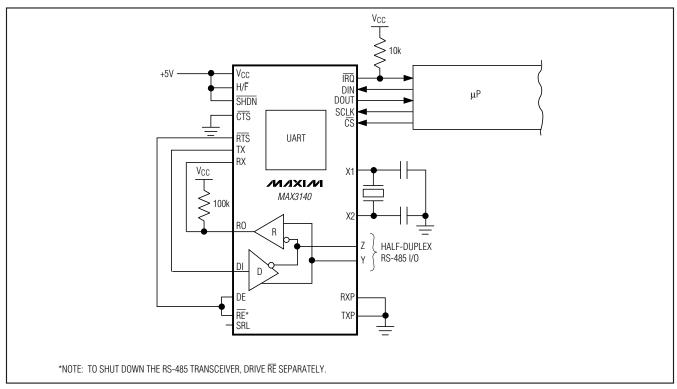

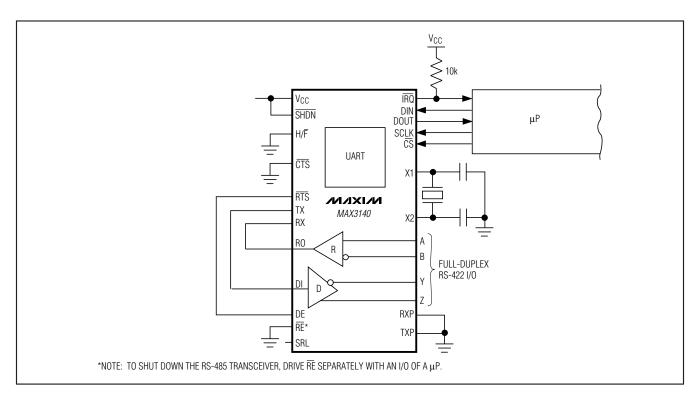

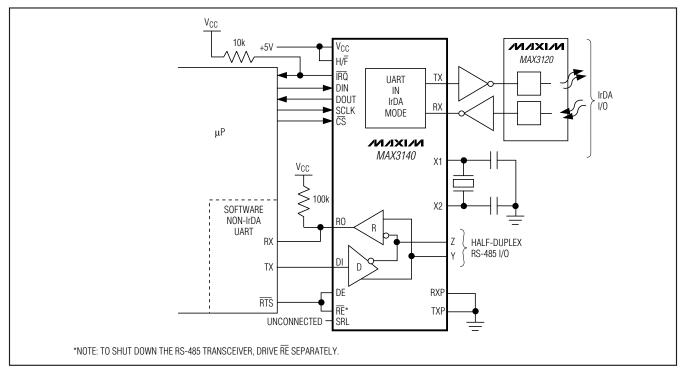

### **Typical Application Circuit**

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND+6V<br>Input Voltage to GND ( <del>CS</del> , <del>SHDN</del> , X1, <del>CTS</del> , RX, DIN, SCLK, <del>RE</del> , DE, H/ <del>F</del> , SRL, TXP, RXP, DI)0.3V to (V <sub>CC</sub> + 0.3V) |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Output Voltage to GND                                                                                                                                                                                              |   |

| DOUT, RTS, TX, X2, RO0.3V to (VCC + 0.3V)                                                                                                                                                                          | ) |

| ĪRQ0.3V to +6V                                                                                                                                                                                                     |   |

| Driver Output Voltage (Y, Z)±13V                                                                                                                                                                                   | ! |

| Receiver Input Voltage, Half Duplex (Y, Z) ±13V                                                                                                                                                                    |   |

| Receiver Input Voltage, Full Duplex (A, B)±25V                                                                                                                                                                     |   |

| TX, RTS Output Current100mA                                                                                                                                                                                        |   |

|                                                                                                                                                                                                                    |   |

| X2, DOUT, $\overline{\text{IRQ}}$ Short-Circuit Duration (to V <sub>CC</sub> or GND)Continuous Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28-pin QSOP (derate 10.8mW/°C above +70°C)860mW                                                                                                      |

| Operating Temperature Ranges                                                                                                                         |

| MAX3140CEI0°C to +70°C                                                                                                                               |

| MAX3140EEI40°C to +85°C                                                                                                                              |

| Storage Temperature Range65°C to +150°C                                                                                                              |

| Lead Temperature (soldering, 10sec)+300°C                                                                                                            |

| Soldering Temperature (reflow)+260°C                                                                                                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5V \pm 5\%, DE = V_{CC}, \overline{RE} = GND, \overline{SHDN} = V_{CC}, f_{XTL} = 1.8432MHz, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are measured with  $V_{CC} = +5V$ , UART configured for 9600 baud,  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                                            | SYMBOL              | CONDITIONS                                         |               |            | MIN                   | TYP                    | MAX  | UNITS              |    |  |

|----------------------------------------------------------------------|---------------------|----------------------------------------------------|---------------|------------|-----------------------|------------------------|------|--------------------|----|--|

| POWER SUPPLY                                                         |                     | I                                                  |               |            |                       |                        |      |                    |    |  |

| Supply Voltage                                                       | Vcc                 |                                                    |               |            |                       | 4.75                   |      | 5.25               | V  |  |

|                                                                      |                     |                                                    | CDI           | \/         | DE = V <sub>C</sub> C |                        | 0.7  | 1.9                |    |  |

| Cumply Cumpet                                                        | la a                | SHDN = Vcc;                                        | SHL           | - = ACC    | DE = GND              |                        | 0.64 | 1.6                | Л  |  |

| Supply Current                                                       | Icc                 | SHDNi bit = 0,<br>no load                          | SRL           | _ = GND    | DE = V <sub>CC</sub>  |                        | 0.74 | 2                  | mA |  |

|                                                                      |                     |                                                    | or o          | pen        | DE = GND              |                        | 0.69 | 1.8                |    |  |

| Supply Current with Only UART Shut Down                              | ICC SHDN<br>UART    | SHDN = GND or                                      | SHDN          | Ni bit = 1 |                       |                        | 0.47 | 1                  | mA |  |

| Supply Current with Both<br>RS-485 Transceiver and UART<br>Shut Down | ICC SHDN<br>(FULL)  | SHDN = GND or SHDNi bit = 1;<br>DE = GND; RE = Vcc |               |            |                       |                        | 20   | μΑ                 |    |  |

| UART OSCILLATOR INPUT (X                                             | 1)                  |                                                    |               |            |                       |                        |      |                    |    |  |

| Input High Voltage                                                   | V <sub>IH1</sub>    |                                                    |               |            |                       | 0.7V <sub>CC</sub>     |      |                    | V  |  |

| Input Low Voltage                                                    | V <sub>IL1</sub>    |                                                    |               |            |                       |                        |      | 0.2V <sub>CC</sub> | V  |  |

| Input Current                                                        | linua               | V <sub>X1</sub> = 0 or V <sub>CC</sub>             | SHDNi bit = 0 |            |                       |                        | 25   |                    |    |  |

| input Current                                                        | I <sub>IN1</sub>    | VX1 = 0 01 VCC                                     |               | SHDNi b    | it = 1                |                        |      | 2                  | μA |  |

| Input Capacitance                                                    | C <sub>IN1</sub>    |                                                    |               |            |                       |                        | 5    |                    | рF |  |

| UART LOGIC INPUTS (DIN, SC                                           | CLK, CS, SHI        | DN, CTS, RX)                                       |               |            |                       |                        |      |                    |    |  |

| Input High Voltage                                                   | V <sub>IH2</sub>    |                                                    |               |            |                       | 0.7V <sub>CC</sub>     |      |                    | V  |  |

| Input Low Voltage                                                    | V <sub>IL2</sub>    |                                                    |               |            |                       |                        |      | 0.3V <sub>CC</sub> | V  |  |

| Input Hysteresis                                                     | V <sub>H</sub> YST2 |                                                    |               |            |                       |                        | 250  |                    | mV |  |

| Input Leakage Current                                                | I <sub>LKG1</sub>   |                                                    |               |            |                       |                        |      | ±1                 | μΑ |  |

| Input Capacitance                                                    | C <sub>IN2</sub>    |                                                    |               |            |                       |                        | 5    |                    | рF |  |

| UART OUTPUTS (DOUT, TX, $\overline{F}$                               | RTS)                |                                                    |               |            |                       |                        |      |                    |    |  |

| Output High Voltage                                                  | VOH1                | ISOURCE = 5mA;                                     | DOUT          | Γ, RTS     |                       | Vcc - 0.5              |      |                    | V  |  |

| Output Flight Voltage                                                | VOHI                | ISOURCE = 10mA                                     |               | -          |                       | V <sub>C</sub> C - 0.5 |      |                    | V  |  |

| Output Low Voltage                                                   | V <sub>OL1</sub>    | Isink = 4mA; DO                                    |               | TS         |                       |                        |      | 0.4                | V  |  |

|                                                                      |                     | Isink = 25mA; TX                                   |               |            |                       |                        |      | 0.9                |    |  |

| Output Leakage                                                       | I <sub>LKG2</sub>   | CS = V <sub>CC</sub> ; D <sub>OUT</sub>            | only          |            |                       |                        |      | ±1                 | μΑ |  |

| Output Capacitance                                                   | Cout1               |                                                    |               |            |                       |                        | 5    |                    | рF |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +5V \pm 5\%, DE = V_{CC}, \overline{RE} = GND, \overline{SHDN} = V_{CC}, f_{XTL} = 1.8432MHz, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are measured with <math>V_{CC} = +5V$ , UART configured for 9600 baud,  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                             | SYMBOL            | COND                                          | ITIONS                                            | MIN                                   | TYP  | MAX       | UNITS |

|-------------------------------------------------------|-------------------|-----------------------------------------------|---------------------------------------------------|---------------------------------------|------|-----------|-------|

| UART IRQ OUTPUT (Open Dra                             | ıin)              |                                               |                                                   |                                       |      |           |       |

| Output Low Voltage                                    | V <sub>OL2</sub>  | I <sub>SINK</sub> = 4mA                       |                                                   |                                       |      | 0.4       | V     |

| Output Leakage                                        | I <sub>LKG3</sub> | VIRQ = VCC                                    |                                                   |                                       |      | ±1        | μΑ    |

| Output Capacitance                                    | Cout2             |                                               |                                                   |                                       | 5    |           | рF    |

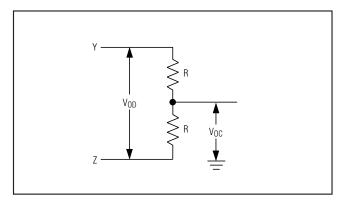

| RS-485 DRIVER                                         |                   | 1                                             |                                                   |                                       |      |           |       |

|                                                       | V <sub>OD1</sub>  | No load, Figure 1                             |                                                   |                                       |      | 5         |       |

| Differential Output Voltage                           | Vone              | $R = 50\Omega$ (RS-422), Fig                  | ure 1                                             | 2.0                                   |      |           | V     |

|                                                       | V <sub>OD2</sub>  | $R = 27\Omega$ (RS-422), Fig                  | ure 1                                             | 1.5                                   |      |           |       |

| Change in Magnitude of<br>Differential Output Voltage | ΔV <sub>OD</sub>  | $R = 50\Omega$ or $R = 27\Omega$ , F          | igure 1 (Note 2)                                  |                                       |      | 0.2       | V     |

| Common-Mode Output<br>Voltage                         | Voc               | $R = 50\Omega$ or $R = 27\Omega$ , F          | igure 1                                           |                                       |      | 3         | V     |

| Change In Magnitude of<br>Common-Mode Voltage         | ΔV <sub>OC</sub>  | $R = 50\Omega$ or $R = 27\Omega$ , F          | igure 1 (Note 2)                                  |                                       |      | 0.2       | V     |

| Input High Voltage                                    | VIH1              | DE, DI, RE                                    |                                                   | 2.0                                   |      |           | V     |

| Input High Voltage                                    | VIH1              | H/F, TXP, RXP                                 |                                                   | 2.4                                   |      |           | V     |

| Input Low Voltage                                     | V <sub>IL1</sub>  | DE, DI, RE, H/F, TXP, F                       | RXP                                               |                                       |      | 0.8       | V     |

| DI Input Hysteresis                                   | VHYS              | SRL = V <sub>CC</sub> or unconne              | ected                                             |                                       | 100  |           | mV    |

| Input Current                                         | l <sub>IN1</sub>  | DE, DI, RE  H/F, TXP, RXP, internal pull-down |                                                   |                                       |      | ±2        | μA    |

| input Guirent                                         | I <sub>IN2</sub>  |                                               |                                                   | 10                                    |      | 40        | μΑ    |

| SRL Input High Voltage                                | V <sub>IH2</sub>  |                                               |                                                   | V <sub>C</sub> C - 0.8                |      |           | V     |

| SRL Input Middle Voltage                              | V <sub>IM2</sub>  | (Note 3)                                      |                                                   | 0.4 • VCC                             |      | 0.6 • VCC | V     |

| SRL Input Low Voltage                                 | V <sub>IL2</sub>  |                                               |                                                   |                                       |      | 0.8       | V     |

| SRL Input Current                                     | I <sub>IN3</sub>  | SRL = V <sub>CC</sub>                         |                                                   |                                       |      | 75        | μA    |

| one input ourient                                     | UINO              | SRL = GND (Note 3)                            |                                                   | -75                                   |      |           | μΑ    |

| Full-Duplex Input Current                             | I <sub>IN4</sub>  | DE = GND                                      | V <sub>IN</sub> = 12V                             |                                       |      | 125       | μA    |

| (A and B)                                             | 11114             | $V_{CC} = GND \text{ or } 5.25V$              | $V_{IN} = -7V$                                    |                                       |      | -75       | μ/ (  |

| Full-Duplex Output Leakage                            | Io                | DE = GND                                      | V <sub>IN</sub> = 12V                             |                                       |      | 125       | μA    |

| (Y and Z)                                             |                   | V <sub>CC</sub> = GND or 5.25V                | V <sub>IN</sub> = -7V                             | -100                                  |      |           | P** * |

|                                                       |                   |                                               | -7V ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub>          | -250                                  |      |           |       |

| Short-Circuit Output Current                          | losp              | (Note 4)                                      | 0 ≤ V <sub>OUT</sub> ≤ 12V                        |                                       |      | 250       | mA    |

|                                                       |                   |                                               | 0 ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub>            | ±25                                   |      |           |       |

| RS-485 RECEIVER                                       | T ,,              | I = 1/ . 1/                                   |                                                   |                                       |      | ==        |       |

| Differential Threshold Voltage                        | VTH               | -7V ≤ V <sub>CM</sub> ≤ +12V                  |                                                   | -200                                  | -125 | -50       | mV    |

| Input Hysteresis                                      | ΔVTH              | 1 4 4 3 7                                     | 50. \/                                            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | 25   |           | mV    |

| Output High Voltage                                   | Voн               | ISOURCE = 4mA, V <sub>ID</sub> = -50mV        |                                                   | V <sub>CC</sub> - 1.5                 |      | 6 .       | V     |

| Output Low Voltage                                    | VoL               |                                               | I <sub>SINK</sub> = 4mA, V <sub>ID</sub> = -200mV |                                       |      | 0.4       | V     |

| Three-State Output Current                            | lozr              | $0.4V \le V_0 \le 2.4V$                       |                                                   |                                       |      | ±1        | μΑ    |

| Input Resistance                                      | RIN               | -7V ≤ V <sub>CM</sub> ≤ 12V                   |                                                   | 96<br>±7                              |      |           | kΩ    |

| Output Short-Circuit Current                          | Iosr              | U ≤ VRO ≤ VCC                                 | $0 \le V_{RO} \le V_{CC}$                         |                                       |      | ±95       | mA    |

### **UART SWITCHING CHARACTERISTICS**

$(V_{CC} = +5V \pm 5\%, f_{XTL} = 1.8432 MHz, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are measured with  $V_{CC} = +5V$ , UART configured for 9600 baud,  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                      | SYMBOL          | CONDITIONS                                        | MIN | TYP | MAX | UNITS |

|--------------------------------|-----------------|---------------------------------------------------|-----|-----|-----|-------|

| UART AC TIMING (Figure 1)      |                 |                                                   |     |     |     |       |

| CS Low to DOUT Valid           | t <sub>DV</sub> | C <sub>LOAD</sub> = 100pF                         |     |     | 100 | ns    |

| CS High to DOUT Tri-State      | t <sub>TR</sub> | $C_{LOAD} = 100pF, R_{\overline{CS}} = 10k\Omega$ |     |     | 100 | ns    |

| CS to SCLK Setup Time          | tcss            |                                                   | 100 |     |     | ns    |

| CS to SCLK Hold Time           | tcsh            |                                                   | 0   |     |     | ns    |

| SCLK Fall to DOUT Valid        | t <sub>DO</sub> | C <sub>LOAD</sub> = 100pF                         |     |     | 100 | ns    |

| DIN to SCLK Setup Time         | tDS             |                                                   | 100 |     |     | ns    |

| DIN to SCLK Hold Time          | tDH             |                                                   | 0   |     |     | ns    |

| SCLK Period                    | tcp             |                                                   | 238 |     |     | ns    |

| SCLK High Time                 | tcH             |                                                   | 100 |     |     | ns    |

| SCLK Low Time                  | tcl             |                                                   | 100 |     |     | ns    |

| SCLK Rising Edge to CS Falling | tCS0            |                                                   | 100 |     |     | ns    |

| CS Rising Edge to SCLK Rising  | tCS1            |                                                   | 200 |     |     | ns    |

| CS High Pulse Width            | tcsw            |                                                   | 200 |     |     | ns    |

| Output Rise Time               | tr              | TX, RTS, DOUT; CLOAD = 100pF                      |     | 10  |     | ns    |

| Output Fall Time               | tf              | TX, RTS, DOUT, RQ; CLOAD = 100pF                  |     | 10  |     | ns    |

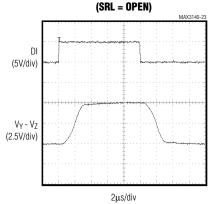

### **SWITCHING CHARACTERISTICS—SRL = Unconnected**

$(V_{CC} = +5V \pm 5\%, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V \text{ and } T_A = +25^{\circ}C.)$

| PARAMETER                                    | SYMBOL                                   | CONDITIONS                                                                      | MIN | TYP  | MAX  | UNITS |

|----------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------|-----|------|------|-------|

| Driver Input to Output                       | tdplh                                    | Figures 3 and 5, $R_{DIFF} = 54\Omega$ ,                                        | 500 | 2030 | 2600 | ns    |

| Driver input to Output                       | t <sub>DPHL</sub>                        | $C_{L1} = C_{L2} = 100pF$                                                       | 500 | 2030 | 2600 | 115   |

| Driver Output Skew   tDPLH - tDPHL           | tdskew                                   | Figures 3 and 5, $R_{DIFF}$ = $54\Omega$ , $C_{L1}$ = $C_{L2}$ = $100pF$        |     | -3   | ±200 | ns    |

| Driver Rise or Fall Time                     | t <sub>DR</sub> , t <sub>DF</sub>        | Figures 3 and 5, $R_{DIFF}$ = $54\Omega$ , $C_{L1}$ = $C_{L2}$ = $100pF$        | 667 | 1320 | 2500 | ns    |

| Maximum Data Rate                            | f <sub>MAX</sub>                         |                                                                                 | 115 |      |      | kbps  |

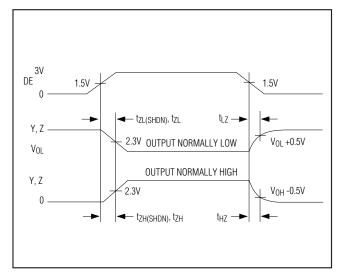

| Driver Enable to Output High                 | tDZH                                     | Figures 4 and 6, C <sub>L</sub> = 100pF, S2 closed                              |     |      | 3500 | ns    |

| Driver Enable to Output Low                  | tDZL                                     | Figures 4 and 6, C <sub>L</sub> = 100pF, S1 closed                              |     |      | 3500 | ns    |

| Driver Disable Time from Low                 | t <sub>DLZ</sub>                         | Figures 4 and 6, C <sub>L</sub> = 15pF, S1 closed                               |     |      | 100  | ns    |

| Driver Disable Time from High                | tDHZ                                     | Figures 4 and 6, C <sub>L</sub> = 15pF, S2 closed                               |     |      | 100  | ns    |

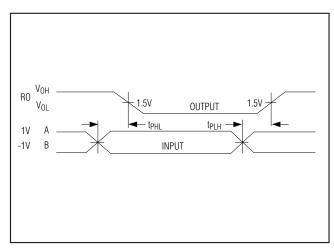

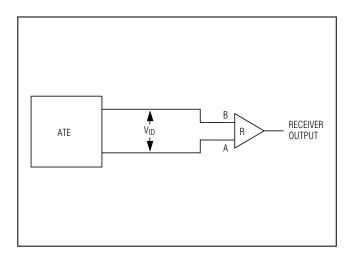

| Receiver Input to Output                     | t <sub>RPLH</sub> ,<br>t <sub>RPHL</sub> | Figures 7 and 9, $ V_{ID}  \ge 2.0V$ , rise and fall time of $V_{ID} \le 15$ ns |     | 127  | 200  | ns    |

| trplh - trphl   Differential   Receiver Skew | trskd                                    | Figures 7 and 9, $ V_{ID}  \ge 2.0V$ , rise and fall time of $V_{ID} \le 15$ ns |     | 3    | ±30  | ns    |

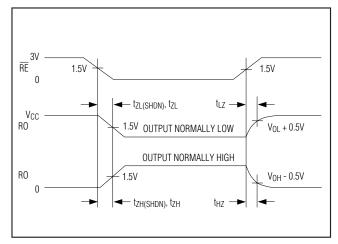

| Receiver Enable to Output Low                | t <sub>RZL</sub>                         | Figures 2 and 8, C <sub>L</sub> = 100pF, S1 closed                              |     | 20   | 50   | ns    |

| Receiver Enable to Output High               | t <sub>RZH</sub>                         | Figures 2 and 8, C <sub>L</sub> = 100pF, S2 closed                              |     | 20   | 50   | ns    |

| Receiver Disable Time from Low               | t <sub>RLZ</sub>                         | Figures 2 and 8, C <sub>L</sub> = 100pF, S1 closed                              |     | 20   | 50   | ns    |

| Receiver Disable Time from High              | <sup>†</sup> RHZ                         | Figures 2 and 8, C <sub>L</sub> = 100pF, S2 closed                              |     | 20   | 50   | ns    |

| Time to Shutdown                             | tshdn                                    | (Note 5)                                                                        | 50  | 200  | 600  | ns    |

| Driver Enable from Shutdown to Output High   | tDZH(SHDN)                               | Figures 4 and 6, C <sub>L</sub> = 15pF, S2 closed                               |     |      | 6000 | ns    |

| Driver Enable from Shutdown to<br>Output Low | tDZL(SHDN)                               | Figures 4 and 6, C <sub>L</sub> = 15pF, S1 closed                               |     |      | 6000 | ns    |

| Receiver Enable from Shutdown to Output High | <sup>†</sup> RZH(SHDN)                   | Figures 2 and 8, C <sub>L</sub> = 100pF, S2 closed                              |     |      | 3500 | ns    |

| Receiver Enable from Shutdown to Output Low  | <sup>t</sup> RZL(SHDN)                   | Figures 2 and 8, C <sub>L</sub> = 100pF, S1 closed                              |     |      | 3500 | ns    |

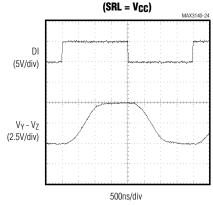

### SWITCHING CHARACTERISTICS—SRL = VCC

$(V_{CC} = +5V \pm 5\%, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V \text{ and } T_A = +25^{\circ}C.)$

| PARAMETER                                       | SYMBOL                                   | CONDITIONS                                                                      | MIN | TYP | MAX  | UNITS |

|-------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------|-----|-----|------|-------|

| Driver Input to Output                          | tDPLH                                    | Figures 3 and 5, $R_{DIFF} = 54\Omega$ ,                                        | 250 | 720 | 1000 | ns    |

| Driver input to Output                          | tDPHL                                    | $C_{L1} = C_{L2} = 100pF$                                                       | 250 | 720 | 1000 | 115   |

| Driver Output Skew   tDPLH - tDPHL              | tdskew                                   | Figures 3 and 5, $R_{DIFF}$ = 54 $\Omega$ , $C_{L1}$ = $C_{L2}$ = 100pF         |     | -3  | ±100 | ns    |

| Driver Rise or Fall Time                        | t <sub>DR</sub> , t <sub>DF</sub>        | Figures 3 and 5, $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100pF$              | 200 | 530 | 950  | ns    |

| Maximum Data Rate                               | f <sub>MAX</sub>                         |                                                                                 | 500 |     |      | kbps  |

| Driver Enable to Output High                    | t <sub>DZH</sub>                         | Figures 4 and 6, C <sub>L</sub> = 100pF, S2 closed                              |     |     | 2500 | ns    |

| Driver Enable to Output Low                     | tDZL                                     | Figures 4 and 6, C <sub>L</sub> = 100pF, S1 closed                              |     |     | 2500 | ns    |

| Driver Disable Time from Low                    | tDLZ                                     | Figures 4 and 6, C <sub>L</sub> = 15pF, S1 closed                               |     |     | 100  | ns    |

| Driver Disable Time from High                   | t <sub>DHZ</sub>                         | Figures 4 and 6, C <sub>L</sub> = 15pF, S2 closed                               |     |     | 100  | ns    |

| Receiver Input to Output                        | t <sub>RPLH</sub> ,<br>t <sub>RPHL</sub> | Figures 7 and 9, $ V_{ID}  \ge 2.0V$ , rise and fall time of $V_{ID} \le 15$ ns |     | 127 | 200  | ns    |

| trplh - trphl   Differential<br>  Receiver Skew | trskd                                    | Figures 7 and 9, $ V_{ID}  \ge 2.0V$ , rise and fall time of $V_{ID} \le 15$ ns |     | 3   | ±30  | ns    |

| Receiver Enable to Output Low                   | t <sub>RZL</sub>                         | Figures 2 and 8, C <sub>L</sub> = 100pF, S1 closed                              |     | 20  | 50   | ns    |

| Receiver Enable to Output High                  | trzh                                     | Figures 2 and 8, C <sub>L</sub> = 100pF, S2 closed                              |     | 20  | 50   | ns    |

| Receiver Disable Time from Low                  | t <sub>RLZ</sub>                         | Figures 2 and 8, C <sub>L</sub> = 100pF, S1 closed                              |     | 20  | 50   | ns    |

| Receiver Disable Time from High                 | t <sub>RHZ</sub>                         | Figures 2 and 8, C <sub>L</sub> = 100pF, S2 closed                              |     | 20  | 50   | ns    |

| Time to Shutdown                                | tshdn                                    | (Note 5)                                                                        | 50  | 200 | 600  | ns    |

| Driver Enable from Shutdown to Output High      | <sup>†</sup> DZH(SHDN)                   | Figures 4 and 6, C <sub>L</sub> = 15pF, S2 closed                               |     |     | 4500 | ns    |

| Driver Enable from Shutdown to<br>Output Low    | tDZL(SHDN)                               | Figures 4 and 6, C <sub>L</sub> = 15pF, S1 closed                               |     |     | 4500 | ns    |

| Receiver Enable from Shutdown to Output High    | tRZH(SHDN)                               | Figures 2 and 8, C <sub>L</sub> = 100pF, S2 closed                              |     |     | 3500 | ns    |

| Receiver Enable from Shutdown to Output Low     | <sup>†</sup> RZL(SHDN)                   | Figures 2 and 8, C <sub>L</sub> = 100pF, S1 closed                              |     |     | 3500 | ns    |

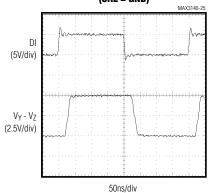

#### SWITCHING CHARACTERISTICS—SRL = GND

$(V_{CC} = +5V \pm 5\%, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V$  and  $T_A = +25^{\circ}C.)$

| PARAMETER                                                               | SYMBOL                            | CONDITIONS                                                                      | MIN | TYP  | MAX  | UNITS |

|-------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------|-----|------|------|-------|

| Driver Input to Output                                                  | tDPLH                             | Figures 3 and 5, $R_{DIFF} = 54\Omega$ ,                                        |     | 34   | 60   | 200   |

| Driver input to Output                                                  | tDPHL                             | $C_{L1} = C_{L2} = 100pF$                                                       |     | 34   | 60   | ns    |

| Driver Output Skew                                                      | tpoven                            | Figures 3 and 5, $R_{DIFF} = 54\Omega$ ,                                        |     | -2.5 | ±10  | ns    |

| toplh - tophl                                                           | tdskew                            | $C_{L1} = C_{L2} = 100pF$                                                       |     | -2.0 | ±10  | 115   |

| Driver Rise or Fall Time                                                | t <sub>DR</sub> , t <sub>DF</sub> | Figures 3 and 5, $R_{DIFF}$ = $54\Omega$ , $C_{L1}$ = $C_{L2}$ = $100pF$        |     | 14   | 25   | ns    |

| Maximum Data Rate                                                       | f <sub>MAX</sub>                  |                                                                                 | 10  |      |      | Mbps  |

| Driver Enable to Output High                                            | tDZH                              | Figures 4 and 6, C <sub>L</sub> = 100pF, S2 closed                              |     |      | 150  | ns    |

| Driver Enable to Output Low                                             | tDZL                              | Figures 4 and 6, C <sub>L</sub> = 100pF, S1 closed                              |     |      | 150  | ns    |

| Driver Disable Time from Low                                            | tDLZ                              | Figures 4 and 6, C <sub>L</sub> = 15pF, S1 closed                               |     |      | 100  | ns    |

| Driver Disable Time from High                                           | tDHZ                              | Figures 4 and 6, C <sub>L</sub> = 15pF, S2 closed                               |     |      | 100  | ns    |

| Receiver Input to Output                                                | trplh,<br>trphl                   | Figures 7 and 9, $ V_{ID}  \ge 2.0V$ , rise and fall time of $V_{ID} \le 15$ ns |     | 106  | 150  | ns    |

| t <sub>RPLH</sub> - t <sub>RPHL</sub>   Differential<br>  Receiver Skew | trskd                             | Figures 7 and 9, $ V_{ID}  \ge 2.0V$ , rise and fall time of $V_{ID} \le 15$ ns |     | 0    | ±10  | ns    |

| Receiver Enable to Output Low                                           | trzl                              | Figures 2 and 8, C <sub>L</sub> = 100pF, S1 closed                              |     | 20   | 50   | ns    |

| Receiver Enable to Output High                                          | t <sub>RZH</sub>                  | Figures 2 and 8, C <sub>L</sub> = 100pF, S2 closed                              |     | 20   | 50   | ns    |

| Receiver Disable Time from Low                                          | t <sub>RLZ</sub>                  | Figures 2 and 8, C <sub>L</sub> = 100pF, S1 closed                              |     | 20   | 50   | ns    |

| Receiver Disable Time from High                                         | tRHZ                              | Figures 2 and 8, C <sub>L</sub> = 100pF, S2 closed                              |     | 20   | 50   | ns    |

| Time to Shutdown                                                        | tshdn                             | (Note 5)                                                                        | 50  | 200  | 600  | ns    |

| Driver Enable from Shutdown to Output High                              | <sup>t</sup> DZH(SHDN)            | Figures 4 and 6, C <sub>L</sub> = 15pF, S2 closed                               |     |      | 250  | ns    |

| Driver Enable from Shutdown to<br>Output Low                            | <sup>†</sup> DZL(SHDN)            | Figures 4 and 6, C <sub>L</sub> = 15pF, S1 closed                               |     |      | 250  | ns    |

| Receiver Enable from Shutdown to Output High                            | <sup>†</sup> RZH(SHDN)            | Figures 2 and 8, C <sub>L</sub> = 100pF, S2 closed                              |     |      | 3500 | ns    |

| Receiver Enable from Shutdown to Output Low                             | <sup>†</sup> RZL(SHDN)            | Figures 2 and 8, C <sub>L</sub> = 100pF, S1 closed                              |     |      | 3500 | ns    |

- **Note 1:** All currents into the device are positive; all currents out of the device are negative. All voltages are referred to device ground unless otherwise noted.

- Note 2:  $\Delta V_{OD}$  and  $\Delta V_{OC}$  are the changes in  $V_{OD}$  and  $V_{OC}$ , respectively, when the DI input changes state.

- **Note 3:** The SRL pin is internally biased to  $V_{CC}/2$  by a  $100k\Omega/100k\Omega$  resistor-divider. It is guaranteed to be  $V_{CC}/2$  if left unconnected.

- Note 4: Maximum current level applies to peak current just prior to foldback-current limiting; minimum current level applies during current limiting.

- Note 5: The device is put into shutdown by bringing RE high and DE low. If the enable inputs are in this state for less than 50ns, the device is guaranteed not to enter shutdown. If the enable inputs are in this state for at least 600ns, the device is guaranteed to have entered shutdown.

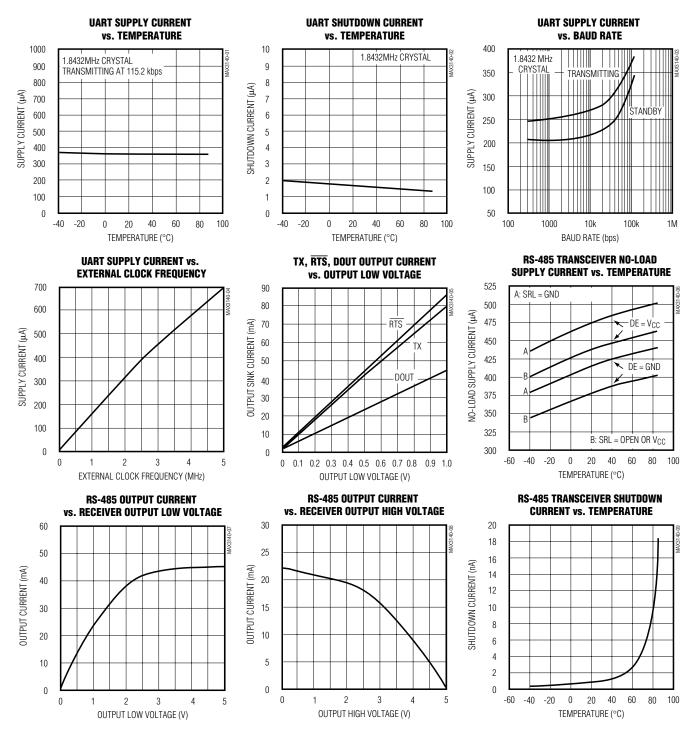

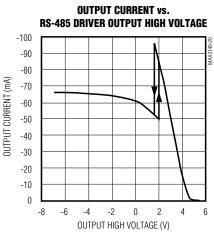

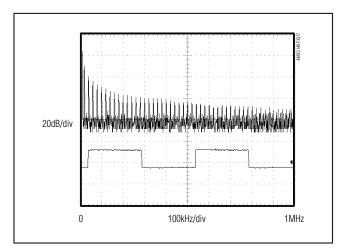

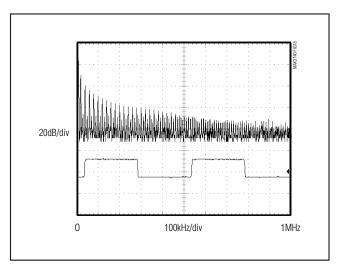

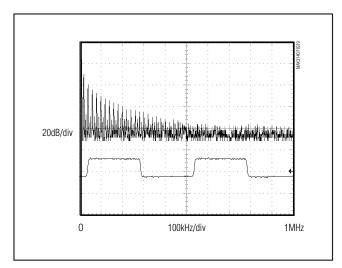

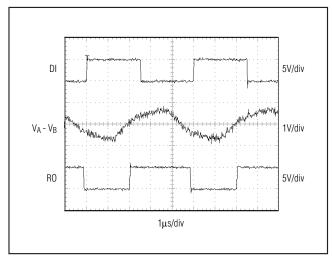

Typical Operating Characteristics

( $V_{CC} = +5V$ ,  $T_A = +25$ °C, unless otherwise noted.)

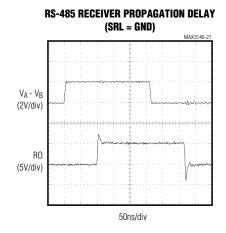

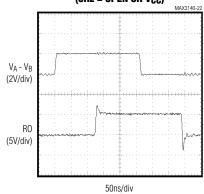

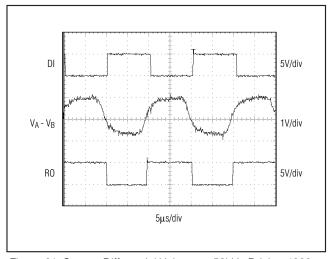

### Typical Operating Characteristics (continued)

$(V_{CC} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

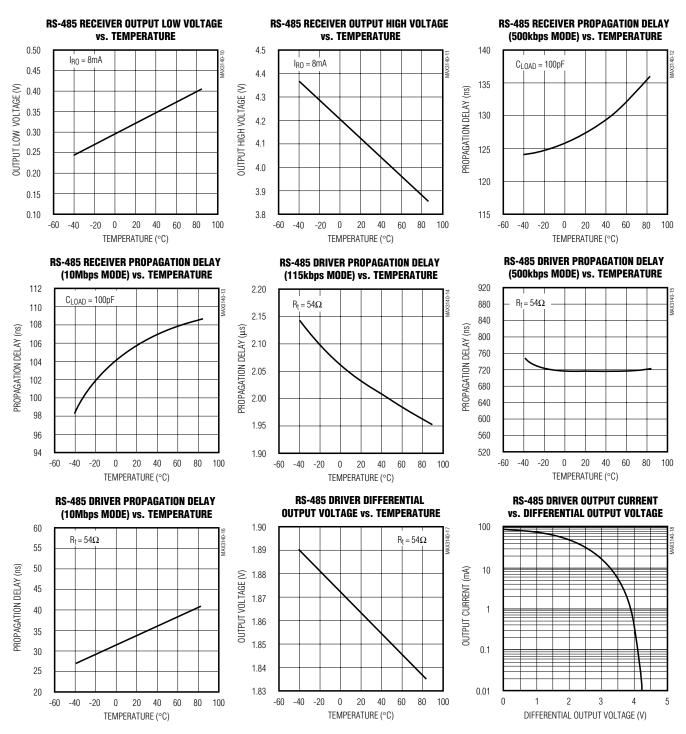

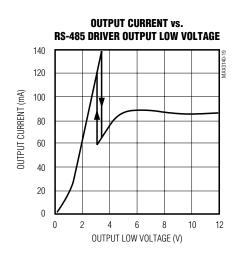

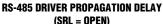

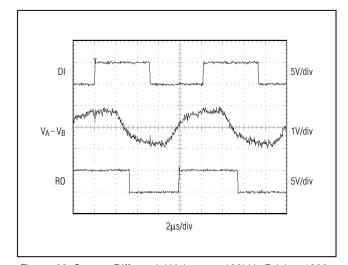

### Typical Operating Characteristics (continued)

$(V_{CC} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

RS-485 RECEIVER PROPAGATION DELAY (SRL = OPEN OR VCC)

RS-485 DRIVER PROPAGATION DELAY

## RS-485 DRIVER PROPAGATION DELAY (SRL = GND)

## Pin Description

| PIN            |                |      |                                                                                                                                                                                                                        |

|----------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FULL<br>DUPLEX | HALF<br>DUPLEX | NAME | FUNCTION                                                                                                                                                                                                               |

| 1              | 1              | X2   | UART Crystal Connection. Leave X2 unconnected for external clock. See the <i>Crystals</i> , <i>Oscillators</i> , <i>and Ceramic Resonators</i> section.                                                                |

| 2              | 2              | X1   | UART Crystal Connection. X1 also serves as an external clock input. See the <i>Crystals</i> , <i>Oscillators</i> , <i>and Ceramic Resonators</i> section.                                                              |

| 3              | 3              | CTS  | UART Clear-to-Send Active-Low Input. Read via the CTS bit.                                                                                                                                                             |

| 4              | 4              | RTS  | UART Request-to-Send Active-Low Output. Controlled by the RTS bit. Use to control the driver enable in RS-485 networks.                                                                                                |

| 5              | 5              | RX   | UART Asynchronous Serial-Data (receiver) Input. The serial information received from the modem or RS-232/RS-485 receiver. A transition on RX while in shutdown generates an interrupt (Table 1).                       |

| 6              | 6              | TX   | UART Asynchronous Serial-Data (transmitter) Output                                                                                                                                                                     |

| 7              | 7              | H/F  | RS-485 Half/Full-Duplex Selector Pin. Connect H/F to V <sub>CC</sub> for half-duplex mode; connect H/F to GND or leave it unconnected for full-duplex mode.                                                            |

| 8              | 8              | GND  | Ground                                                                                                                                                                                                                 |

| 9              | 9              | RO   | RS-485 Receiver Output. When RE is low and if A - B ≥ -50mV, RO will be high; if A - B ≤ -200mV, RO will be low.                                                                                                       |

| 10             | 10             | RE   | RS-485 Receiver Output Enable. Drive $\overline{\text{RE}}$ low to enable RO; RO is high impedance when $\overline{\text{RE}}$ is high. Drive $\overline{\text{RE}}$ high and DE low to enter low-power shutdown mode. |

| 11             | 11             | DE   | RS-485 Driver Output Enable. Drive DE high to enable driver outputs. These outputs are high impedance when DE is low. Drive RE high and DE low to enter low-power shutdown mode.                                       |

| 12             | 12             | DI   | RS-485 Driver Input. With DE high, a low on DI forces noninverting output low and inverting output high. Similarly, a high on DI forces noninverting output high and inverting output low.                             |

| 13             | 13             | SRL  | RS-485 Transceiver Slew-Rate-Limit Selector Pin. Connect SRL to GND for a 10Mbps communication rate, connect SRL to V <sub>CC</sub> for a 500kbps rate, or leave SRL unconnected for a 115kbps rate.                   |

| 14             | 14             | N.C. | No Connection. Not internally connected.                                                                                                                                                                               |

| 15             | 15             | TXP  | RS-485 Transmitter Phase. Connect TXP to GND or leave it unconnected for normal transmitter phase/polarity. Connect TXP to V <sub>CC</sub> to invert the transmitter phase/polarity.                                   |

| 16             | _              | Y    | RS-485 Noninverting Driver Output                                                                                                                                                                                      |

| _              | 16             | Y    | RS-485 Noninverting Receiver Input and RS-485 Noninverting Driver Output*                                                                                                                                              |

| 17             | 17             | N.C. | No Connection. Not internally connected.                                                                                                                                                                               |

| 18             |                | Z    | RS-485 Inverting Driver Output                                                                                                                                                                                         |

| _              | 18             | Z    | RS-485 Inverting Receiver Input and RS-485 Inverting Driver Output*                                                                                                                                                    |

| 19             | _              | В    | RS-485 Inverting Receiver Input                                                                                                                                                                                        |

| _              | 19             | В    | RS-485 Receiver Input Resistors*                                                                                                                                                                                       |

| 20             | _              | Α    | RS-485 Noninverting Receiver Input                                                                                                                                                                                     |

|                | 20             | А    | RS-485 Receiver Input Resistors*                                                                                                                                                                                       |

### **Pin Description (continued)**

| P              | PIN            |      |                                                                                                                                                                                                               |

|----------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FULL<br>DUPLEX | HALF<br>DUPLEX | NAME | FUNCTION                                                                                                                                                                                                      |

| 21             | 21             | RXP  | RS-485 Receiver Phase. Connect RXP to GND or leave it unconnected for normal receiver phase/polarity. Connect RXP to VCC to invert the receiver phase/polarity.                                               |

| 22             | 22             | Vcc  | Positive Supply (4.75V to 5.25V)                                                                                                                                                                              |

| 23             | 23             | DIN  | UART SPI/MICROWIRE Serial-Data Input. Schmitt-trigger input.                                                                                                                                                  |

| 24             | 24             | DOUT | UART SPI/MICROWIRE Serial-Data Output. High impedance when $\overline{\text{CS}}$ is high.                                                                                                                    |

| 25             | 25             | SCLK | UART SPI/MICROWIRE Serial-Clock Input. Schmitt-trigger input.                                                                                                                                                 |

| 26             | 26             | CS   | UART Active-Low Chip-Select Input. DOUT goes high impedance when $\overline{\text{CS}}$ is high. $\overline{\text{IRQ}}$ , TX, and $\overline{\text{RTS}}$ are always active. Schmitt-trigger input.          |

| 27             | 27             | ĪRQ  | UART Active-Low Interrupt Output. Open-drain interrupt output to microprocessor.                                                                                                                              |

| 28             | 28             | SHDN | UART Hardware Shutdown Input. When shut down (SHDN = 0), the UART oscillator turns off immediately without waiting for the current transmission to end, reducing the supply current to just leakage currents. |

<sup>\*</sup>In half-duplex mode, the driver outputs serve as receiver inputs. The full-duplex receiver inputs ( A and B) still have a 1/8-unit load, but do not affect the receiver output.

## Transceiver Function Tables

| TRANSMITTING |     |         |    |                   |        |  |  |  |

|--------------|-----|---------|----|-------------------|--------|--|--|--|

|              | INP | OUTPUTS |    |                   |        |  |  |  |

| TXP          | RE  | DE      | DI | Z                 | Y      |  |  |  |

| 0            | Х   | 1       | 1  | 0                 | 1      |  |  |  |

| 0            | Х   | 1       | 0  | 1                 | 0      |  |  |  |

| 1            | Х   | 1       | 1  | 1                 | 0      |  |  |  |

| 1            | Х   | 1       | 0  | 0                 | 1      |  |  |  |

| Х            | 0   | 0       | Х  | High-Z            | High-Z |  |  |  |

| X            | 1   | 0       | Х  | Shutdown (High-Z) |        |  |  |  |

| RECEIVING |     |    |      |                  |                  |                      |  |  |  |  |  |

|-----------|-----|----|------|------------------|------------------|----------------------|--|--|--|--|--|

|           |     | ı  | NPUT | 3                |                  | OUTPUTS              |  |  |  |  |  |

| H/F       | RXP | RE | DE   | A-B              | Y-Z              | RO                   |  |  |  |  |  |

| 0         | 0   | 0  | Х    | ≥ -0.05V         | Х                | 1                    |  |  |  |  |  |

| 0         | 0   | 0  | Х    | ≤ -0.2V          | Х                | 0                    |  |  |  |  |  |

| 0         | 1   | 0  | Χ    | ≥ -0.05V         | Х                | 0                    |  |  |  |  |  |

| 0         | 1   | 0  | Χ    | ≤ -0.2V          | Х                | 1                    |  |  |  |  |  |

| 1         | 0   | 0  | Χ    | X                | ≥ -0.05V         | 1                    |  |  |  |  |  |

| 1         | 0   | 0  | Χ    | Х                | ≤ -0.2V          | 0                    |  |  |  |  |  |

| 1         | 1   | 0  | Х    | Х                | ≥ -0.05V         | 0                    |  |  |  |  |  |

| 1         | 1   | 0  | Χ    | Х                | ≤ -0.2V          | 1                    |  |  |  |  |  |

| 0         | 0   | 0  | X    | Open/<br>Shorted | Х                | 1                    |  |  |  |  |  |

| 1         | 0   | 0  | X    | Х                | Open/<br>Shorted | 1                    |  |  |  |  |  |

| 0         | 1   | 0  | Х    | Open/<br>Shorted | Х                | 0                    |  |  |  |  |  |

| 1         | 1   | 0  | Х    | Х                | Open/<br>Shorted | 0                    |  |  |  |  |  |

| Х         | Χ   | 1  | 1    | Х                | Х                | High-Z               |  |  |  |  |  |

| Х         | X 1 |    | 0    | Х                | Х                | Shutdown<br>(High-Z) |  |  |  |  |  |

Figure 1. Driver DC Test Load

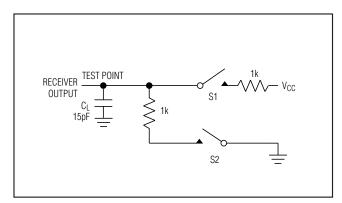

Figure 2. Receiver Enable/Disable Timing Test Load

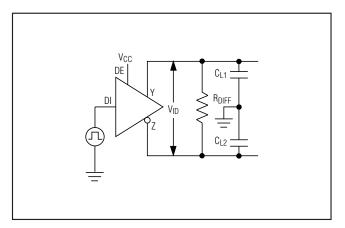

Figure 3. Driver Timing Test Circuit

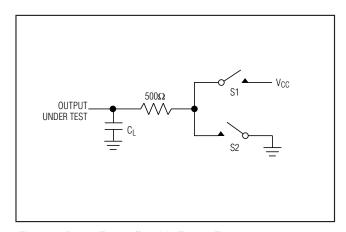

Figure 4. Driver Enable/Disable Timing Test Load

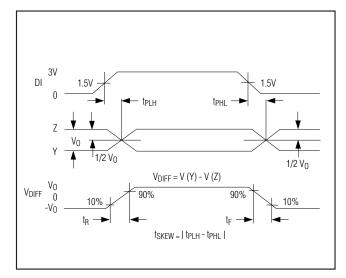

Figure 5. Driver Propagation Delays

Figure 6. Driver Enable and Disable Times

Figure 7. Receiver Propagation Delays

Figure 8. Receiver Enable and Disable Times

Figure 9. Receiver Propagation Delay Test Circuit

### **Detailed Description**

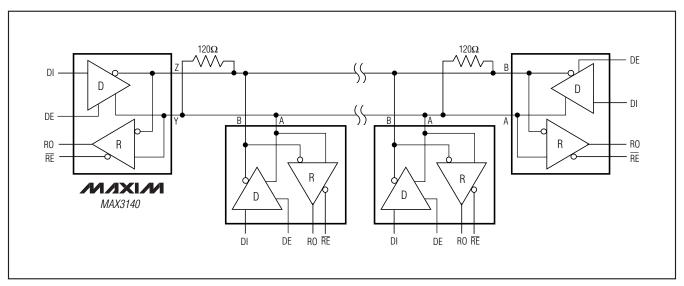

The MAX3140 combines an SPI/QSPI/MICROWIRE-compatible UART (MAX3100) and an RS-485/RS-422 transceiver (MAX3089) in one package. The UART supports data rates up to 230k baud for both standard UART bit streams as well as IrDA, and includes an 8-word receive FIFO. Also included is a parity-bit interrupt useful in 9-bit address recognition.

The RS-485/RS-422 transceiver has a true fail-safe receiver and allows up to 256 transceivers on the bus. Other features include pin-selectable full/half-duplex operation and a phase control to correct for twisted-

pair reversal. The slew rate of the RS-485/RS-422 transceiver is selectable, limiting the maximum data rate to 115kbps, 500kbps, or 10Mbps. The RS-485/RS-422 drivers are output short-circuit current limited, and thermal shutdown circuitry protects the RS-485/RS-422 drivers against excessive power dissipation.

The UART and RS-485/RS422 functions can be used together or independently since the two functions only share supply and ground connections. This part operates from a single +5V supply.

#### **UART**

The universal asynchronous receiver transmitter (UART) interfaces the SPI/MICROWIRE-compatible synchronous serial data from a microprocessor (µP) to asynchronous, serial-data communication ports (RS-485, IrDA). Figure 10 shows the MAX3140 functional diagram. Included in the UART function is an SPI/MICROWIRE interface, a baud-rate generator, and an interrupt generator.

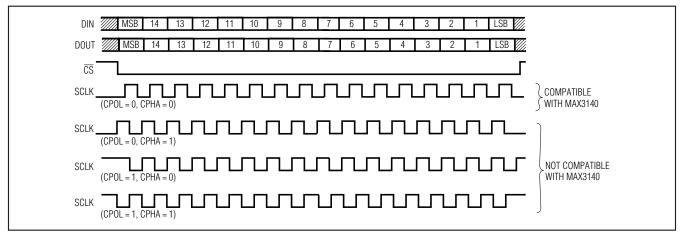

#### SPI Interface

The MAX3140 is compatible with SPI, QSPI (CPOL = 0, CPHA = 0), and MICROWIRE serial-interface standards (Figure 11). The MAX3140 has a unique full-duplex architecture that expects a 16-bit word for DIN and simultaneously produces a 16-bit word for DOUT regardless of which read/write register used. The DIN stream is monitored for its first two bits to tell the UART the type of data transfer being executed (see the WRITE CONFIGURATION register, READ CONFIGURATION register, WRITE DATA register, and READ DATA register sections). DIN (MOSI) is latched on

Figure 10. Functional Diagram

Figure 11. Compatible CPOL and CPHA Modes

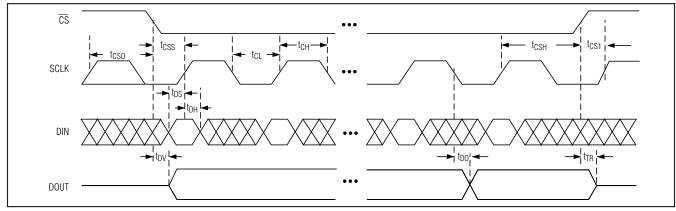

SCLK's rising edge. DOUT (MISO) is read into the  $\mu P$  on SCLK's rising edge. The first bit (bit 15) of DOUT transitions on  $\overline{\text{CS}}$ 's falling edge, and bits 14–0 transition on SCLK's falling edge. Figure 12 shows the detailed serial timing specifications for the synchronous SPI port.

Only 16-bit words are expected. If  $\overline{CS}$  goes high in the middle of a transmission (any time before the 16th bit), the sequence is aborted (i.e., data does not get written to individual registers). Most operations, such as the

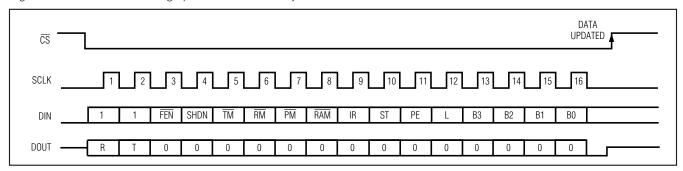

clearing of internal registers, are executed only on  $\overline{CS}$ 's rising edge. Every time  $\overline{CS}$  goes low, a new 16-bit stream is expected. Figure 13 shows an example of using the WRITE CONFIGURATION register.

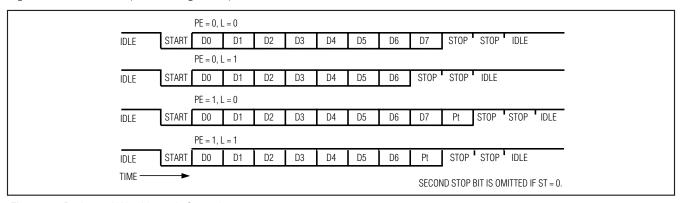

Table 1 describes the bits located in the WRITE CONFIGURATION, READ CONFIGURATION, WRITE DATA, and READ DATA registers. This table also describes whether the bit is a read or write bit and what the power-on reset states (POR) of the bits are. Figure 14 shows an example of parity and word length control.

Figure 12. Detailed Serial Timing Specifications for the Synchronous Port

Figure 13. SPI Interface (Write Configuration)

Figure 14. Parity and Word Length Control

**Table 1. Bit Descriptions**

| BIT<br>NAME | BIT<br>TYPE | POR<br>STATE | DESCRIPTION                                                                                                                                                                                                                                                                                                   |

|-------------|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B0-B3       | write       | 0000         | Baud-Rate Divisor Select Bits. Sets the baud clock's value (Table 6).                                                                                                                                                                                                                                         |

| B0-B3       | read        | 0000         | Baud-Rate Divisor Select Bits. Reads the 4-bit baud clock value assigned to these registers.                                                                                                                                                                                                                  |

| CTS         | read        | No<br>change | Clear-to-Send-Input. Records the state of the $\overline{CTS}$ pin (CTS bit = 0 implies $\overline{CTS}$ pin = logic high).                                                                                                                                                                                   |

| D0t-D7t     | write       | XXXXXXXX     | Transmit-Buffer Register. Eight data bits written into the transmit-buffer register. D7t is ignored when $L=1$ .                                                                                                                                                                                              |

| D0r–D7r     | read        | 00000000     | Eight data bits read from the receive FIFO or the receive-buffer register. When $L=1$ , D7r is always 0.                                                                                                                                                                                                      |

| FEN         | write       | 0            | FIFO Enable. Enables the receive FIFO when $\overline{\text{FEN}} = 0$ . When $\overline{\text{FEN}} = 1$ , FIFO is disabled.                                                                                                                                                                                 |

| FEN         | read        | 0            | FIFO-Enable Readback. FEN's state is read.                                                                                                                                                                                                                                                                    |

| IR          | write       | 0            | Enables the IrDA timing mode when IR = 1.                                                                                                                                                                                                                                                                     |

| IR          | read        | 0            | Reads the value of the IR bit.                                                                                                                                                                                                                                                                                |

| L           | write       | 0            | Bit to set the word length of the transmitted or received data. $L=0$ results in 8-bit words (9-bit words if $PE=1$ ) (see Figure 5). $L=1$ results in 7-bit words (8-bit words if $PE=1$ ).                                                                                                                  |

| L           | read        | 0            | Reads the value of the L bit.                                                                                                                                                                                                                                                                                 |

| Pt          | write       | Х            | Transmit-Parity Bit. This bit is treated as an extra bit that is transmitted if PE = 1. In 9-bit networks, the MAX3140 does not calculate parity. If PE = 0, then this bit (Pt) is ignored in transmit mode (see the <i>9-Bit Networks</i> section).                                                          |

| Pr          | read        | X            | Receive-Parity Bit. This bit is the extra bit received if $PE = 1$ . Therefore, $PE = 1$ results in 9-bit transmissions (L = 0). If $PE = 0$ , then $Pr$ is set to 0. $Pr$ is stored in the FIFO with the receive data (see the <i>9-Bit Networks</i> section).                                               |

| PE          | write       | 0            | Parity-Enable Bit. Appends the Pt bit to the transmitted data when PE = 1, and sends the Pt bit as written. No parity bit is transmitted when PE = 0. With PE = 1, an extra bit is expected to be received. This data is put into the Pr register. Pr = 0 when PE = 0. The MAX3140 does not calculate parity. |

| PE          | read        | 0            | Reads the value of the Parity-Enable bit.                                                                                                                                                                                                                                                                     |

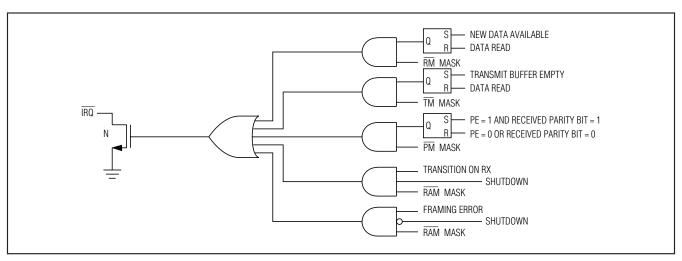

| PM          | write       | 0            | Mask for Pr bit. $\overline{IRQ}$ is asserted if $\overline{PM} = 1$ and Pr = 1 (Table 7).                                                                                                                                                                                                                    |

| PM          | read        | 0            | Reads the value of the $\overline{PM}$ bit (Table 7).                                                                                                                                                                                                                                                         |

| R           | read        | 0            | Receive Bit or FIFO Not Empty Flag. R = 1 means new data is available to be read or is being read from the receive register or FIFO. If performing a READ DATA or WRITE DATA operation, the R bit will clear on the falling edge of SCLK's 16th pulse if no new data is available.                            |

| RM          | write       | 0            | Mask for R bit. $\overline{IRQ}$ is asserted if $\overline{RM}$ = 1 and R = 1 (Table 7).                                                                                                                                                                                                                      |

| RM          | read        | 0            | Reads the value of the $\overline{\rm RM}$ bit (Table 7).                                                                                                                                                                                                                                                     |

| RAM         | write       | 0            | Mask for RA/FE bit. $\overline{\text{IRQ}}$ is asserted if $\overline{\text{RAM}} = 1$ and RA/FE = 1 (Table 7).                                                                                                                                                                                               |

| RAM         | read        | 0            | Reads the value of the RAM bit (Table 7).                                                                                                                                                                                                                                                                     |

| RTS         | write       | 0            | Request-to-Send Bit. Controls the state of the $\overline{\text{RTS}}$ output. This bit is reset on power-up (RTS bit = 0 sets the $\overline{\text{RTS}}$ pin = logic high).                                                                                                                                 |

### Table 1. Bit Descriptions (continued)

| BIT<br>NAME | BIT<br>TYPE | POR<br>STATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA/FE       | read        | 0            | Receiver-Activity/Framing-Error Bit. In shutdown mode, this is the RA bit. In normal operation, this is the FE bit. In shutdown mode, a transition on RX sets RA = 1. In normal mode, a framing error sets FE = 1. A framing error occurs if a zero is received when the first stop bit is expected. FE is set when a framing error occurs, and cleared upon receipt of the next properly framed character independent of the FIFO being enabled. When the device wakes up, it is likely that a framing error will occur. This error is cleared with a WRITE CONFIGURATION. The FE bit is not cleared on a READ DATA operation. When an FE is encountered, the UART resets itself to the state where it is looking for a start bit. |

| SHDNi       | write       | 0            | Software-Shutdown Bit. Enter software shutdown with a WRITE CONFIGURATION where SHDNi = 1. Software shutdown takes effect after $\overline{\text{CS}}$ goes high, and causes the oscillator to stop as soon as the transmitter becomes idle. Software shutdown also clears R, T, RA/FE, D0r–D7r, D0t–D7t, Pr, Pt, and all data in the receive FIFO. RTS and CTS can be read and updated while in shutdown. Exit software shutdown with a WRITE CONFIGURATION where SHDNi = 0. The oscillator restarts typically within 50ms of $\overline{\text{CS}}$ going high. RTS and CTS are unaffected. Refer to the <i>Pin Description</i> for hardware shutdown $\overline{\text{(SHDN)}}$ input).                                          |

| SHDNo       | read        | 0            | Shutdown Read-Back Bit. The READ CONFIGURATION register outputs SHDNo = 1 when the UART is in shutdown. Note that this bit is not sent until the current byte in the transmitter is sent (T = 1). This tells the processor when it may shut down the RS-485/RS-422 driver. This bit is also set immediately when the device is shut down through the $\overline{\text{SHDN}}$ pin.                                                                                                                                                                                                                                                                                                                                                  |

| ST          | write       | 0            | Transmit-Stop Bit. One stop bit will be transmitted when $ST = 0$ . Two stop bits will be transmitted when $ST = 1$ . The receiver only requires one stop bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ST          | read        | 0            | Reads the value of the ST bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Т           | read        | 1            | Transmit-Buffer-Empty Flag. T = 1 means that the transmit buffer is empty and ready to accept another data word.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TE          | write       | 0            | Transmit-Enable Bit. If $\overline{\text{TE}} = 1$ , then only the $\overline{\text{RTS}}$ pin is updated on $\overline{\text{CS}}$ 's rising edge. The contents of $\overline{\text{RTS}}$ , Pt, and D0t-D7t transmit on $\overline{\text{CS}}$ 's rising edge when $\overline{\text{TE}} = 0$ .                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TM          | write       | 0            | Mask for T Bit. $\overline{IRQ}$ is asserted if $\overline{TM} = 1$ and T = 1 (Table 7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TM          | read        | 0            | Reads the value of the $\overline{\text{TM}}$ bit (Table 7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### Notice to High-Level Programmers