# MAX24001

# 2.5Gbps Tx Burst-Mode Laser Transceiver

## **General Description**

The MAX24001 is a complete burst-mode laser driver transmitter and limiting amplifier receiver for use within fiber optic modules for FTTx applications. A fully compliant GPON/GEPON module with digital diagnostics can be realized when used with a 2KB EEPROM and suitable optics. Alternatively, a microcontroller can be used in conjunction with the MAX24001; however, this is not a necessity in order to achieve SFF-8472 compliance.

The 2.5Gbps limiting receive path features programmable output swing control, rate selection, and OMA-based loss-of-signal detection. Functions are also provided which facilitate the implementation of APD biasing without the need for an external DC-DC converter.

The burst-mode laser driver has temperature compensated modulation control using a lookup table. Closed-loop control of laser power incorporates tracking error compensation and has multiple options for rapidly settling the laser power thus enabling fast registration and shutdown on the network. Diagnostics are enhanced with the inclusion of programmable transmit signal detection during bursts, and rogue ONU detection between bursts. This is linked to a laser safety system which allows the modulation and bias currents to be shut off in response to a range of different fault conditions detected on-chip.

The transmit and receive systems are independently powered and can respond separately to the SLEEP pin. The MAX24001 is highly configurable from either EEPROM or low-cost MCU using a two-wire interface.

# **Applications**

GPON, GEPON, Gigabit Ethernet

19-6460; Rev 2; 2/14

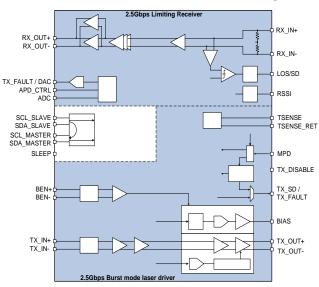

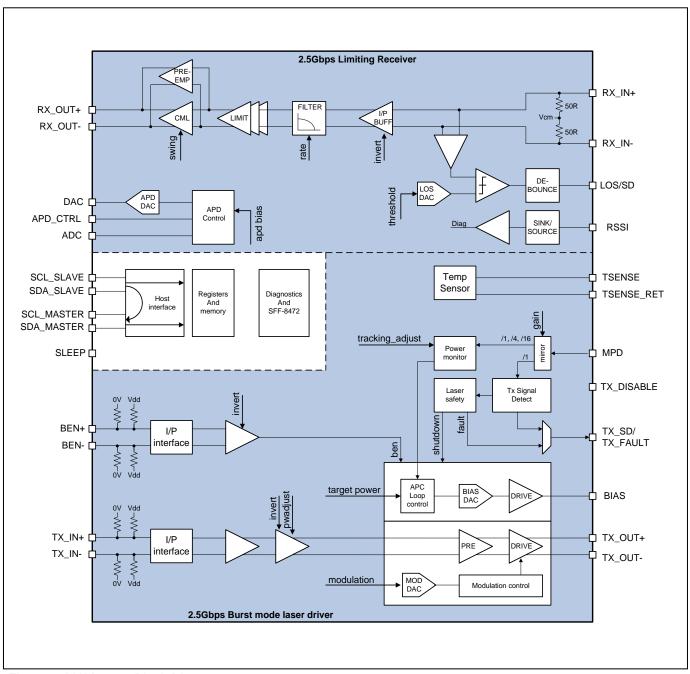

# Functional Diagram

#### Features

- 2.5Gbps Limiting Receiver

- Integrated APD Bias Loop With Overvoltage And Overcurrent Protection

- " OMA-Based LOS Detection

- " 1.25Gbps to 2.5Gbps Laser Driver

- " CML, LVPECL, HSTL, SSTL-Compatible Inputs

- Open and Closed-Loop Bias Control

- " Temperature-Compensated I<sub>MOD</sub> Control

- Highly Configurable Laser Safety System

- " Transmit TX\_SD and Rogue ONU Detection

- " SFP MSA and SFF-8472 Digital Diagnostics

- Integrated Temperature Sensor

- Power-Saving SLEEP Modes

- External DAC, ADC, and PWM Interfaces

# Ordering Information

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX24001TL+ | -40°C to +95°C | 40 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

Maxim Integrated 1

Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: <a href="www.maximintegrated.com/errata">www.maximintegrated.com/errata</a>. For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at <a href="www.maximintegrated.com">www.maximintegrated.com</a>.

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on V <sub>DD TX</sub> , V <sub>DD TXO</sub> , V <sub>DD RX</sub> , V <sub>DD RXO</sub> | 0.3V to +3.65V |

|------------------------------------------------------------------------------------------------------|----------------|

| Voltage Range on Any Pin Not Otherwise Specified (with respect to V <sub>SS</sub> *)                 |                |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                                | ` - ,          |

| TQFN (derate 35.7mW/°C above +70°C)                                                                  | 2857.1mW       |

| Operating Temperature Range                                                                          | 40°C to +95°C  |

| Junction Temperature                                                                                 | +150°C         |

| Storage Temperature                                                                                  | 70°C to +150°C |

| Lead Temperature (soldering, 10s)                                                                    | +300°C         |

| Soldering Temperature (reflow)                                                                       | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

| PARAMETER                | SYMBOL              | CONDITIONS                     | MIN  | TYP | MAX                       | UNITS |

|--------------------------|---------------------|--------------------------------|------|-----|---------------------------|-------|

| Operating Supply Voltage | $V_{DD}$            |                                | 3.0  | 3.3 | 3.6                       | V     |

| RSSI Pin Compliance      | RSSI Pin Compliance | ROSA sourcing to RSSI pin      |      |     | V <sub>DD</sub> -<br>0.75 | V     |

| •                        |                     | ROSA sinking from RSSI pin     | 0.75 |     |                           | V     |

| BIAS Pin Compliance      |                     |                                | 0.8  |     |                           | V     |

| TX_OUT Pin Compliance    |                     |                                | 0.8  |     |                           | V     |

| MPD Input Current        |                     | For correct APC loop operation | 40   |     | 2000                      | μA    |

| MPD Input Capacitance    |                     | For correct APC loop operation | 4    |     | 20                        | pF    |

| Junction Temperature     |                     |                                | -40  |     | +120                      | °C    |

| Case Temperature         |                     |                                | -40  |     | +95                       | °C    |

Device not guaranteed to meet parametric specifications when operated beyond these conditions. Permanent damage may be incurred by operating beyond these limits.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 2.97V \text{ to } 3.63V, T_A = -40^{\circ}\text{C to } +95^{\circ}\text{C.}) \text{ (Note 1)}$

Note 1: Electrical specifications are production tested at  $T_A = +25^{\circ}C$ . Specifications over the entire operating temperature range are guaranteed by design and characterization. Typical specifications are at  $T_A = +25^{\circ}C$ , 3.3V.

#### **CONTINUOUS RATINGS**

| PARAMETER      | SYMBOL          | CONDITIONS                                                                                                         | MIN | TYP | MAX | UNITS |

|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Supply Current | I <sub>DD</sub> | Excluding laser bias and modulation currents, 20mA bias and modulation current, Rx CML output 400mV <sub>P-P</sub> |     | 136 |     | mA    |

# **RECEIVER CHARACTERISTICS**

| PARAMETER                    | SYMBOL | CONDITIONS                                                                                            | MIN | TYP  | MAX | UNITS             |

|------------------------------|--------|-------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| Differential Input Impedance |        |                                                                                                       | 80  | 100  | 120 | Ω                 |

| Maximum Input Data Rate      |        |                                                                                                       |     | 2.5  |     | Gbps              |

| Minimum Input Data Rate      |        |                                                                                                       |     | 1.25 |     | Gbps              |

| Input Sensitivity            |        | Differential, BER = 1E-10, 2.5Gbps, PRBS 2 <sup>23</sup> -1 pattern                                   |     | 6.5  | 13  | mV <sub>P-P</sub> |

| Deterministic Jitter         |        | 2.5Gbps, $V_{OUT}$ = 800m $V_{P-P}$ , $V_{IN}$ between 25m $V_{P-P}$ differential and 1000m $V_{P-P}$ |     | 40   |     | ps <sub>P-P</sub> |

| Random Jitter                |        | 2.5Gbps, $V_{OUT}$ = 800m $V_{P-P}$ , $V_{IN}$ between 25m $V_{P-P}$ differential and 1000m $V_{P-P}$ |     | 2.7  |     | ps <sub>RMS</sub> |

| Output Rise/Fall Times       |        | 2.5Gbps, $V_{OUT}$ = 800m $V_{P-P}$ , $V_{IN}$ = 25m $V_{P-P}$ differential and 1000m $V_{P-P}$       |     | 60   |     | ps                |

| Low-Frequency Cutoff         |        |                                                                                                       |     | 30   |     | kHz               |

| Output Impedance             |        | 1MHz differential                                                                                     | 80  | 100  | 120 | Ω                 |

| Minimum Output Swing         |        | Differential, 4-bit programmable (Note 2)                                                             |     | 200  | 240 | $mV_{P-P}$        |

| Maximum Output Swing         |        | Differential, 4-bit programmable (Note 2)                                                             | 800 | 880  |     | $mV_{P-P}$        |

Note 2: Measured with 1111111100000000 pattern.

## LOSS OF SIGNAL AND RSSI CHARACTERISTICS

| PARAMETER                     | SYMBOL | CONDITIONS                    | MIN | TYP  | MAX | UNITS             |

|-------------------------------|--------|-------------------------------|-----|------|-----|-------------------|

| Maximum OMA LOS Assert Time   |        |                               |     | 11   |     | μs                |

| Maximum OMA LOS Deassert Time |        |                               |     | 11   |     | μs                |

| Maximum LOS Threshold Setting |        |                               |     | 400  |     | mV <sub>P-P</sub> |

| LOC Assemble and              |        | LOS DAC = 50 (Note 3)         |     | 67   |     | mV <sub>P-P</sub> |

| LOS Assert/Deassert Level     |        | LOS DAC = 105 (Note 3)        |     | 143  |     | mV <sub>P-P</sub> |

| Maximum RSSI Current Level    |        | Sourced or sunk from RSSI pin |     | 1200 |     | μA                |

Note 3: LOS assert and deassert levels can be set independently to define hysteresis.

# TRANSMITTER CHARACTERISTICS

| PARAMETER                                      | SYMBOL | CONDITIONS                                                                                                            | MIN | TYP   | MAX | UNITS              |

|------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------|-----|-------|-----|--------------------|

| Maximum Input Data Rate                        |        | PRBS23                                                                                                                |     | 2.488 |     | Gbps               |

| Minimum Input Data Rate                        |        | PRBS23                                                                                                                |     | 1.25  |     | Gbps               |

| Maximum Modulation Current                     |        |                                                                                                                       | 80  |       |     | mA <sub>P-P</sub>  |

| Minimum Modulation Current                     |        |                                                                                                                       |     | 8     |     | mA <sub>P-P</sub>  |

| Maximum Electrical Rise/Fall Time (20% to 80%) |        | Measured using $15\Omega$ effective termination, $I_{MOD} = 8mA_{P-P}$ to $80mA_{P-P}$                                |     | 96    |     | ps                 |

| Total Jitter                                   |        | PRBS15, 2.488Gbps, I <sub>MOD</sub> = 8mA <sub>P-P</sub> to 80mA <sub>P-P</sub> , differential electrical measurement |     | 65    | 175 | mUI <sub>P-P</sub> |

| Deterministic Jitter                           |        | PRBS15, 2.488Gbps, I <sub>MOD</sub> = 8mA <sub>P-P</sub> to 80mA <sub>P-P</sub> , differential electrical measurement |     | 45    |     | mUI <sub>P-P</sub> |

| Random Jitter                                  |        | PRBS15, 2.488Gbps, I <sub>MOD</sub> = 8mA <sub>P-P</sub> to 80mA <sub>P-P</sub> , differential electrical measurement |     | 1.11  |     | mUI <sub>RMS</sub> |

| Maximum Bias Current                           |        |                                                                                                                       |     | 90    |     | mA                 |

### **BURST TIMINGS**

| PARAMETER                                                      | SYMBOL | CONDITIONS                                                                                                                                        | MIN | TYP | MAX | UNITS |

|----------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

|                                                                |        | Disable: Bias current reduced to 20% of its maximum value.                                                                                        |     |     |     |       |

| Burst Enable/Disable Time<br>(Electrical)                      |        | Enable: Bias current increased to 90% of desired bias plus modulation current                                                                     |     | 7   | 12  | ns    |

|                                                                |        | Target bias current > 3mA                                                                                                                         |     |     |     |       |

| Minimum Burst Length to Update APC Loop                        |        | During closed-loop operation                                                                                                                      |     | 90  |     | ns    |

| Minimum Burst Gap                                              |        | During closed-loop operation                                                                                                                      |     | 75  |     | ns    |

| Maximum Initial Mean Power<br>Control Settling Time (APC Loop) |        | From power-on, negation of TX_DISABLE, or negation of SLEEP to 90% of desired optical power.  Fast settling algorithm enabled, no fast start LUT. |     | 1.2 |     | ms    |

|                                                                |        | Bias current overshoot < 10%                                                                                                                      |     |     |     |       |

|                                                                |        | Bias current > 4mA                                                                                                                                |     |     |     |       |

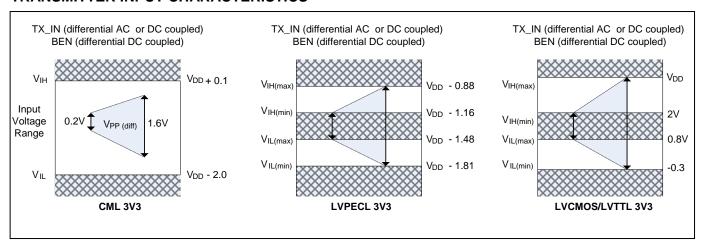

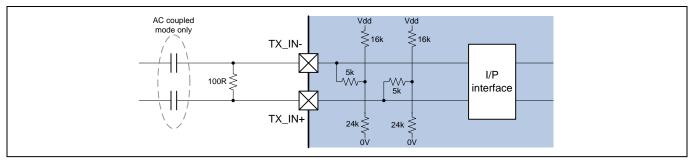

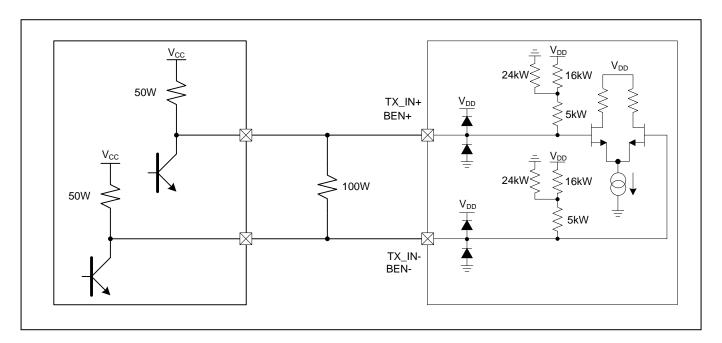

### TRANSMITTER INPUT CHARACTERISTICS

Typical I/O ranges for TX\_IN and BEN are shown. TX\_IN and BEN inputs are also compatible with HSTL and SSTL for low-voltage operation.

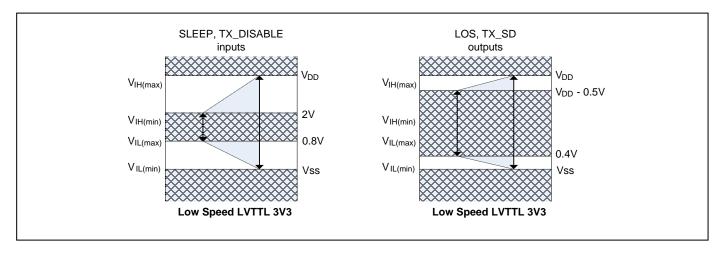

#### **DIGITAL I/O CHARACTERISTICS**

| PARAMETER                                  | SYMBOL | CONDITIONS                                          | MIN | TYP   | MAX | UNITS |

|--------------------------------------------|--------|-----------------------------------------------------|-----|-------|-----|-------|

| Time To Initialise                         |        | From power-up or hot plug                           |     | 71    |     | ms    |

| TX_DISABLE Assert                          |        | TX_DISABLE assert to optical disable                |     | 0.3   |     | μs    |

| TX_DISABLE Negate                          |        | TX_DISABLE negate to optical enable                 |     | 0.5   |     | ms    |

| TX_DISABLE to Reset                        |        | Time TX_DISABLE must be held high to reset TX_FAULT |     | 0.155 |     | μs    |

| Maximum Delay BEN Change to TX_SD Response |        | Rising or falling edge                              |     | 100   |     | ns    |

| Light During Gap to Laser<br>Shutdown      |        | Rogue ONU                                           |     | 100   |     | μs    |

Typical I/O Ranges for SLEEP, TX\_DISABLE, LOS and TX\_SD

# **PERIPHERAL FUNCTIONS**

| PARAMETER                    | SYMBOL | CONDITIONS                                                       | MIN | TYP | MAX | UNITS |

|------------------------------|--------|------------------------------------------------------------------|-----|-----|-----|-------|

| Power-On-Reset (POR) Voltage |        | Module 3V3 supply voltage above which reset will not be asserted |     |     | 2.5 | V     |

| Fower-On-Reset (FOR) Voltage |        | Module 3V3 supply voltage below which reset is guaranteed        | 2.2 |     |     | V     |

# **APD Control**

| PARAMETER                   | SYMBOL | CONDITIONS                           | MIN  | TYP  | MAX  | UNITS |

|-----------------------------|--------|--------------------------------------|------|------|------|-------|

| ADC Pin Minimum Voltage     |        |                                      |      |      | 1.30 | V     |

| ADC Pin Maximum Voltage     |        |                                      | 2.25 |      |      | V     |

| DAC Pin Minimum Current     |        |                                      |      | 0    |      | mA    |

| DAC Pin Maximum Current     |        |                                      |      | 0.45 |      | mA    |

| DAC Pin Compliance          |        |                                      |      | 1.5  |      | V     |

| DIAMA Francisco             |        | Minimum PWM frequency                |      | 250  |      | kHz   |

| PWM Frequency               |        | Maximum PWM frequency                |      | 2    |      | MHz   |

| Step Response Settling Time |        | Load current change from 20µA to 1mA |      | 2    |      | ms    |

# **SLEEP**

| PARAMETER             | SYMBOL | CONDITIONS                                                                 | MIN | TYP | MAX | UNITS |

|-----------------------|--------|----------------------------------------------------------------------------|-----|-----|-----|-------|

| Sleep Assert/Deassert |        | Time to allow first operation or enter sleep from deassertion of sleep pin |     | 100 |     | ns    |

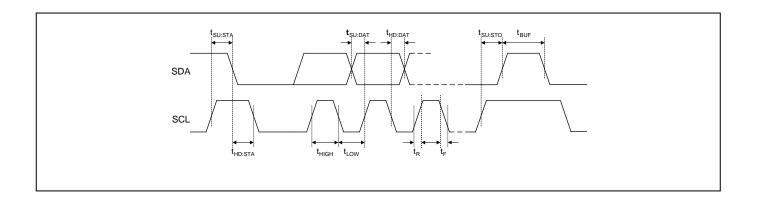

# TWO-WIRE INTERFACE CHARACTERISTICS

| PARAMETER                                                | SYMBOL                          | CONDITIONS                                                     | MIN TYP | MAX | UNITS |

|----------------------------------------------------------|---------------------------------|----------------------------------------------------------------|---------|-----|-------|

| Maximum SCL Clock Frequency                              |                                 |                                                                | 400     |     | kHz   |

| Minimum SCL Clock LOW Period                             | t <sub>LOW</sub>                |                                                                | 1200    |     | ns    |

| Minimum SCL Clock HIGH Period                            | t <sub>HIGH</sub>               |                                                                | 600     |     | ns    |

| Minimum Setup Time For A<br>Repeated START Condition     | t <sub>SU:STA</sub>             |                                                                | 600     |     | ns    |

| Minimum Hold Time (Repeated)<br>START Condition          | t <sub>HD:STA</sub>             |                                                                | 600     |     | ns    |

| Minimum Data Hold Time                                   | t <sub>HD:DAT</sub>             |                                                                | 0       |     | ns    |

| Minimum Data Setup Time                                  | t <sub>SU:DAT</sub>             |                                                                | 100     |     | ns    |

| Minimum Setup Time for STOP Condition                    | t <sub>su:sto</sub>             |                                                                | 600     |     | ns    |

| Minimum Bus Free Time Between a STOP and START Condition | t <sub>BUF</sub>                |                                                                | 1200    |     | ns    |

| Maximum Rise and Fall Times of Both SDA and SCL Signals  | t <sub>R</sub> , t <sub>F</sub> |                                                                | 300     |     | ns    |

| Minimum Rise and Fall Times of Both SDA and SCL Signals  | t <sub>R,</sub> t <sub>F</sub>  | $C_b$ = capacitance of a single bus line $C_x$ = 20 + 0.1 x Cb | Сх      |     | ns    |

| Maximum Capacitance for Each I/O Pin                     |                                 |                                                                | 10      |     | pF    |

# **DIGITAL DIAGNOSTICS**

| PARAMETER                         | SYMBOL      | CONDITIONS                                     | MIN TYP | MAX | UNITS  |

|-----------------------------------|-------------|------------------------------------------------|---------|-----|--------|

| TEMPERATURE                       | remperature |                                                |         |     |        |

| Reporting Resolution              |             | -40°C to +95°C range                           | 0.85    |     | °C/LSB |

| Maximum Inaccuracy                |             | Single-point calibration, external mode        | ±2      |     | °C     |

| POWER SUPPLY                      | •           |                                                |         |     | 1      |

| Reporting Resolution              |             | 3.0V to 3.6V range                             | 10      |     | mV/LSB |

| Maximum Inaccuracy                |             | Calibrated, within the supply reporting range  | ±3      |     | %      |

| TX BIAS                           | •           |                                                |         |     |        |

| Reporting Resolution              |             | 5mA to 90mA range                              | 0.392   |     | mA/LSB |

| Maximum Inaccuracy                |             | Calibrated, within the Tx bias reporting range | ±10     |     | %      |

| TX POWER                          |             |                                                |         |     | 1      |

|                                   |             | <b>mpd_range</b> = 00, 40μA to 200μA           | 0.78    |     | μA/LSB |

| MPD Current Reporting Resolution  |             | <b>mpd_range</b> = 01, 100μA to 800μA          | 3.125   |     | μA/LSB |

|                                   |             | mpd_range = 10, 400μA to 2000μA                | 12.5    |     | μA/LSB |

| Maximum Inaccuracy                |             | Calibrated, within the MPD operating range     | ±20     |     | %      |

| RX POWER                          | •           |                                                |         |     | 1      |

|                                   |             | 0 to 16μA (Note 4)                             | 0.5     |     | μA/LSB |

| RSSI Current Reporting Resolution |             | 16μA to 206μA (Note 4)                         | 2.0     |     | μA/LSB |

|                                   |             | 206μA to 1000μA (Note 4)                       | 8.0     |     | μA/LSB |

|                                   |             | 3μA to 25μA, calibrated (Note 4)               | ±25     |     | %      |

| Maximum Inaccuracy                |             | 25μA to 1000μA, calibrated (Note 4)            | ±10     |     | %      |

Note 4: rx\_rssi\_scale = 00 (x1 gain) range and resolution settings can be changed to improve accuracy.

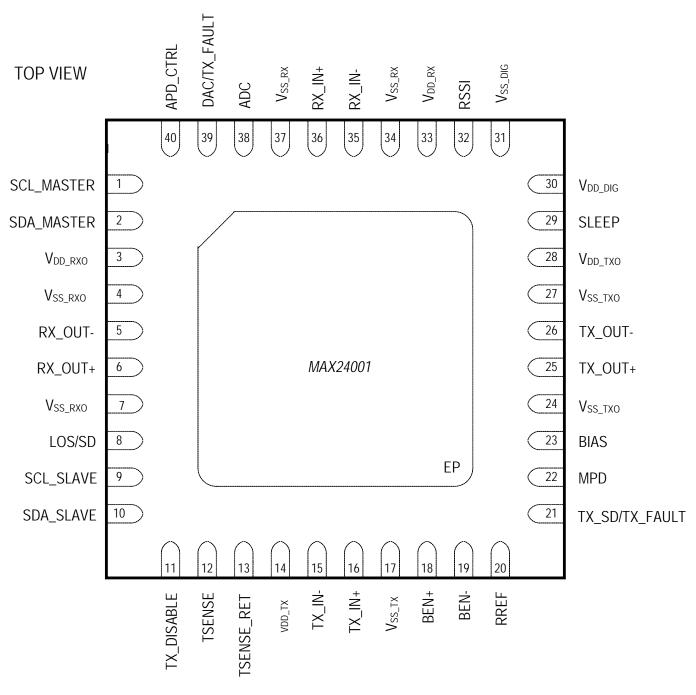

# Pin Configuration

TQFN (5mm x 5mm)

# Pin Description

| PIN | NAME                | DIR    | TYPE       | FUNCTION                                                                                                                                                         |

|-----|---------------------|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SCL_MASTER          | O/P    | LVTTL      | Two-Wire Interface Clock Connection To EEPROM, with Internal 10kΩ Pullup Resistor                                                                                |

| 2   | SDA_MASTER          | I/O    | LVTTL      | Two-Wire Interface Data Connection To EEPROM, with Internal 10kΩ Pullup Resistor                                                                                 |

| 3   | $V_{DD\_RXO}$       | Analog | +3.3V      | Receiver Output Power Supply                                                                                                                                     |

| 4   | V <sub>SS_RXO</sub> | Analog | GND        | Receiver Output Ground Connection                                                                                                                                |

| 5   | RX_OUT-             | O/P    | High Speed | Limiting Receiver Inverted Output. 100Ω differential to RX_OUT+.                                                                                                 |

| 6   | RX_OUT+             | O/P    | High Speed | Limiting Receiver Noninverted Output. 100Ω differential to RX_OUT                                                                                                |

| 7   | V <sub>SS_RXO</sub> | Analog | GND        | Receiver Output Ground Connection                                                                                                                                |

| 8   | LOS/SD              | O/P    | LVTTL      | Loss-Of-Signal Indication. Open drain with external 4.7k $\Omega$ to 10k $\Omega$ resistor.                                                                      |

| 9   | SCL_SLAVE           | I/P    | LVTTL      | Two-Wire Interface Clock Connection To Host. with external 10kΩ pullup resistor                                                                                  |

| 10  | SDA_SLAVE           | I/O    | LVTTL      | Two-Wire Interface Data Connection To Host. with external 10kΩ pullup resistor                                                                                   |

| 11  | TX_DISABLE          | I/P    | LVTTL      | Internally pulled high to V <sub>DD_DIG</sub> with a 7.5kΩ resistor                                                                                              |

| 12  | TSENSE              | Analog | Analog     | Temperature Sensor Current Force                                                                                                                                 |

| 13  | TSENSE_RET          | Analog | Analog     | Temperature Sensor Current Return                                                                                                                                |

| 14  | $V_{DD\_TX}$        | Analog | +3.3V      | Transmitter Power Supply                                                                                                                                         |

| 15  | TX_IN-              | I/P    | High Speed | Transmitter Input Signal Inverted                                                                                                                                |

| 16  | TX_IN+              | I/P    | High Speed | Transmitter Input Signal Noninverted                                                                                                                             |

| 17  | V <sub>SS_TX</sub>  | Analog | GND        | Transmitter Ground Connection                                                                                                                                    |

| 18  | BEN+                | I/P    | High Speed | Burst-Enable Noninverted                                                                                                                                         |

| 19  | BEN-                | I/P    | High Speed | Burst-Enable Inverted                                                                                                                                            |

| 20  | RREF                | Analog | Analog     | Connects to External Precision Resistor                                                                                                                          |

| 21  | TX_SD/<br>TX_FAULT  | O/P    | LVTTL      | Push-Pull Signal Detect Indication. Can be configured as open-drain TX_FAULT output, pulled high externally using a 4.7k $\Omega$ to 10k $\Omega$ resistor.      |

| 22  | MPD                 | I/P    | Analog     | Monitor Photodiode Input                                                                                                                                         |

| 23  | BIAS                | Analog | Analog     | Bias Current Sink                                                                                                                                                |

| 24  | $V_{SS\_TXO}$       | Analog | GND        | Transmitter Output Ground Connection                                                                                                                             |

| 25  | TX_OUT+             | O/P    | High Speed | Laser Data Differential Drive Output                                                                                                                             |

| 26  | TX_OUT-             | O/P    | High Speed | Laser Data Differential Drive Output                                                                                                                             |

| 27  | V <sub>SS_TXO</sub> | Analog | GND        | Transmitter Output Ground Connection                                                                                                                             |

| 28  | $V_{DD\_TXO}$       | Analog | +3.3V      | Transmitter Output Power Supply                                                                                                                                  |

| 29  | SLEEP               | I/P    | LVTTL      | Sleep Mode Select                                                                                                                                                |

| 30  | $V_{DD\_DIG}$       | Analog | +3.3V      | Digital Power Supply                                                                                                                                             |

| 31  | $V_{SS\_DIG}$       | Analog | GND        | Digital Ground Connection                                                                                                                                        |

| 32  | RSSI                | I/P    | Analog     | Rx Photodiode Monitor (RSSI)                                                                                                                                     |

| 33  | $V_{DD\_RX}$        | Analog | +3.3V      | Receiver Power Supply                                                                                                                                            |

| 34  | V <sub>SS_RX</sub>  | Analog | GND        | Receiver Ground Connection                                                                                                                                       |

| 35  | RX_IN-              | I/P    | CML        | Receiver Input Signal. Differential 100Ω with RX_IN+.                                                                                                            |

| 36  | RX_IN+              | I/P    | CML        | Receiver Input Signal. Differential 100Ω with RX_IN                                                                                                              |

| 37  | V <sub>SS_RX</sub>  | Analog | GND        | Receiver Ground Connection                                                                                                                                       |

| 38  | ADC                 | I/P    | Analog     | Voltage Input to On-Chip ADC                                                                                                                                     |

| 39  | DAC/TX_FAULT        | O/P    | Analog     | Current Output For APD Loop Control. Can be configured as open-drain TX_FAULT output, pulled high externally using a 4.7k $\Omega$ to 10k $\Omega$ resistor.     |

| 40  | APD_CTRL            | O/P    | LVTTL      | 3V3 Push-Pull APD Bias PWM Output. Can be configured as open-drain APD bias shutdown pin, pulled high externally using a 4.7k $\Omega$ to 10k $\Omega$ resistor. |

|     | EP                  | Analog | GND        | Exposed Pad. Solder to board to provide effective thermal connection to circuit board                                                                            |

# **Detailed Description**

Figure 1. MAX24001 Block Diagram

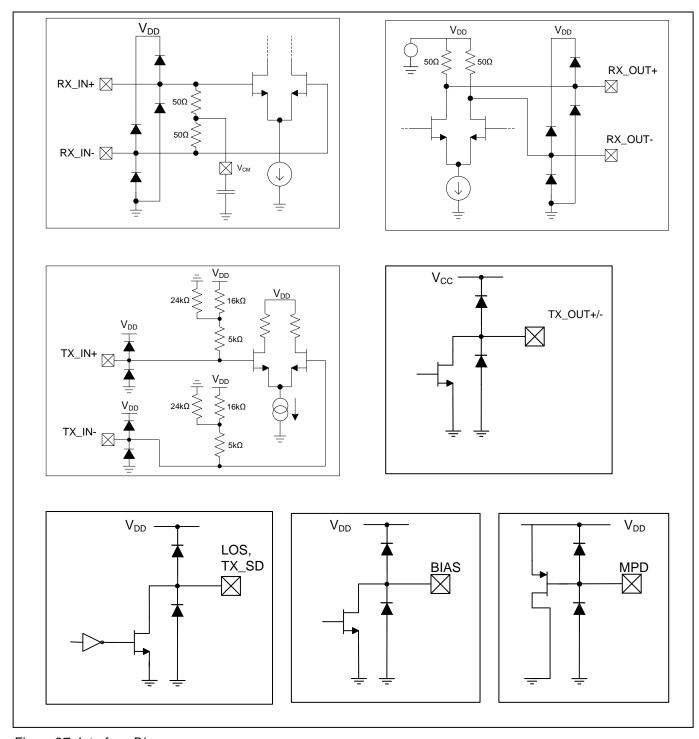

### Receiver Signal Path

[Control Register Address Range A4h: 90h to 93h]

The signal arriving at RX\_IN is terminated with a  $100\Omega$  load to minimise return loss. An input buffer adds peaking to compensate for up to 10mm of FR4. The level of peaking is controlled by the **rx\_input\_peak** register. The signal can also be inverted using **rx\_invert**.

| rx_ratesel0 or rx_ratesel1 | BANDWIDTH<br>(GHz) | BIT RATE<br>(Gbps) |

|----------------------------|--------------------|--------------------|

| 00                         | 1                  | 1.25               |

| 01                         | 1.8                | 2.488              |

The received signal is then band limited to one of two rates selected by the **soft\_rate\_select** bit of the **system\_control** register (A2h: 7Bh). If **soft\_rate\_select** = '0' then select **rx\_ratesel0** else select **rx\_ratesel1**. Filter bandwidths are nominally designed to be 0.7x the available data rates.

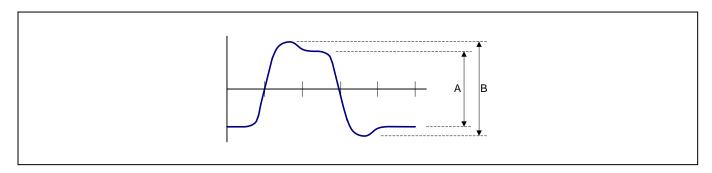

The CML output stage is a high-current driver that delivers a 200mV to 880mV signal from a low-impedance  $50\Omega$  output. The **rx\_output\_swing** register is used to control the signal at RX\_OUT with 45mV resolution. Preemphasis may also be applied to the output signal using **rx\_preemphasis**. The pre-emphasis (defined as ((B-A)/B) x 100) can be set to 0%, 2%, 6% or 10%. The pre-emphasis ratio remains relatively constant when A is adjusted.

Figure 2. Rx Pre-Emphasis Control

The CML, pre-emphasis and limiting stages may be automatically powered down under loss-of-signal conditions (LOS = '1') by setting the **los\_squelch** register. This feature uses the debounced LOS signal prior to any inversion caused by setting **los\_invert**. Alternatively, the CML, pre-emphasis and limiting stages may be directly powered down by setting the **squelch** register.

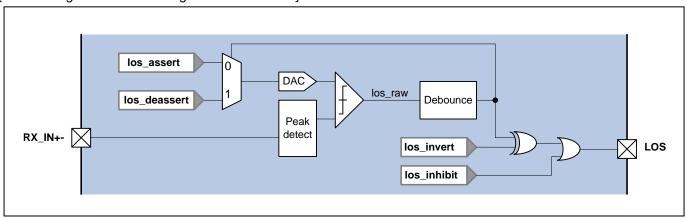

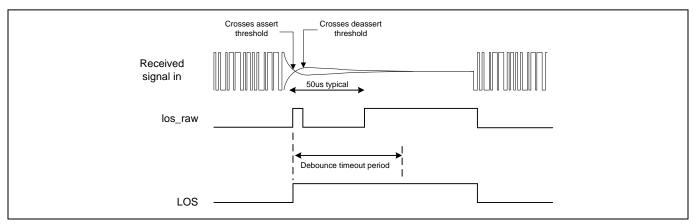

#### Receiver Loss of Signal (LOS)

[Control Register Address Range A4h: 9Bh to 9Dh]

When the peak signal amplitude detected at RX\_IN drops below the threshold level set by **los\_assert** then a loss-of-signal condition is reported on the LOS pin and the **los\_deassert** threshold is selected. The signal amplitude must then rise back above the threshold set by **los\_deassert** before the loss-of-signal condition is removed and the **los\_assert** threshold is re-selected. The two thresholds can be used to introduce a wide range of hysteresis into LOS detection. The deassert threshold level should be higher than the assert threshold for correct operation.

When the comparator output (los\_raw) changes, the los debounce circuit holds the new value at its output for a programmable period of time controlled by **los\_debounce**. Longer debounce timeout periods may be required to accommodate the much longer timeframe pulses caused by the response of the TIA AGC when the signal is suddenly interrupted. The decay of the differential signal is characterized by an unwanted signal crossover as shown in the diagram below. The unwanted pulse on los\_raw is rejected by setting the debounce period to > 50µs.

Figure 4. LOS Debounce Operation

The **los\_invert** register is used to configure the pin for Signal Detect (SD) instead of LOS. An output mask (**los\_inhibit**) holds the output to the LOS pin high after power-on reset until the configuration register load from EEPROM or microcontroller is complete. This avoids multiple transitions on the LOS pin during initialization, which can cause fault conditions to occur at the system level.

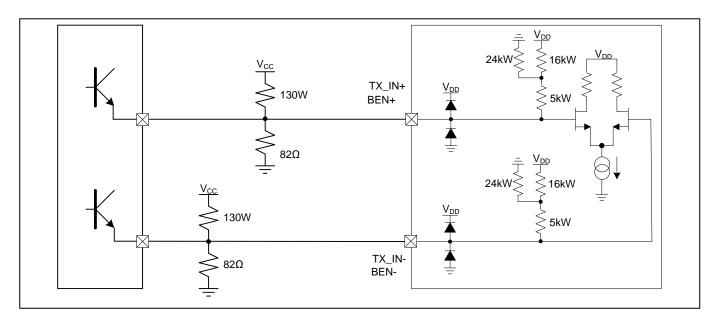

#### Transmitter Signal Path

[Control Register Address Range A4h: 9Eh to A1h]

The input to the transmitter signal path supports CML, LVPECL, HSTL, and SSTL electrical signalling schemes with a minimum of external components. The input may be either DC or AC coupled. An external  $100\Omega$  resistor provides differential termination. The internal potential dividers set the common mode level at 2.0V when the input is AC-coupled.

Figure 5. TX IN and BEN Input Termination and Signal Conditioning

The laser modulation current is controlled by the **tx\_moddac** register with a resolution of 375µA per LSB (nominally). This register may be set by the host, or alternatively set the **modlut\_en** bit to cause the **tx\_moddac** register to be automatically refreshed from the modulation lookup table (LUT) every 10ms. The modulation LUT is stored in external EEPROM at TWI slave address A6h, register address range 80h to FFh. It is indexed using the upper 7 bits of **temperature uncal**.

If the **modramp\_en** register is set then the value in **tx\_moddac** ramps progressively from the old value to the new value by 1 LSB every cycle of the internal 64MHz clock. This prevents glitches from occurring in the DAC. If ramping is disabled then updates to **tx\_moddac** are effective immediately. The modulation current is switched off between bursts and when the laser safety system asserts a shutdown. **burst\_invert** is used to invert the differential signal on BEN±. **tx\_invert** is used to invert the polarity of the transmit signal path.

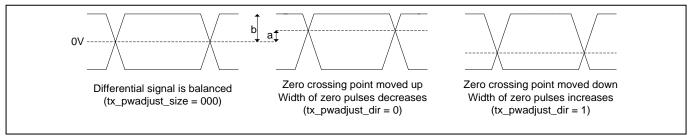

### Eye Optimization

The pulse width of the transmitted signal is adjusted by moving the crossing point of the eye up or down using **tx\_pwadjust\_dir**. Use the **tx\_pwadjust\_size** to control the amount of adjustment, in the direction set by **tx\_pwadjust\_dir**. At maximum adjustment, the zero crossing point (a) is moved by 40% of the 0-pk eye opening (b). The **tx\_pwadjust\_hires** register can be used to halve the adjustment step size and thus increase resolution (at the expense of halving the range).

Figure 6. Crossing Point Adjustment

The tx\_snubber register is used to snub out overshoot or undershoot in the output eye.

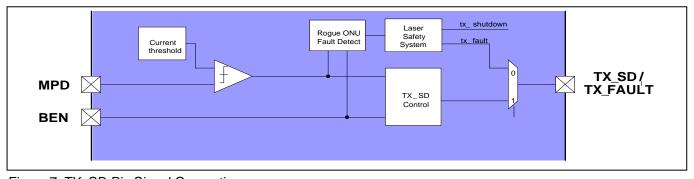

#### Tx Signal Detect

[Control Register Address Range A4h: ADh to AEh, BEh to BFh]

The Tx Signal Detect feature comprises two related areas of functionality:

For external signal and rogue ONU fault detect by the host, the MAX24001 controls the TX\_SD pin as follows:  $TX_SD = '1'$  when there is light;  $TX_SD = '0'$  when there is no light from the laser.

For on-chip "Rogue ONU fault detect", the MAX24001 detects the presence of light during the burst gap. This fault condition is input to the laser safety system which can then optionally shut down the laser within 100µs of light being detected.

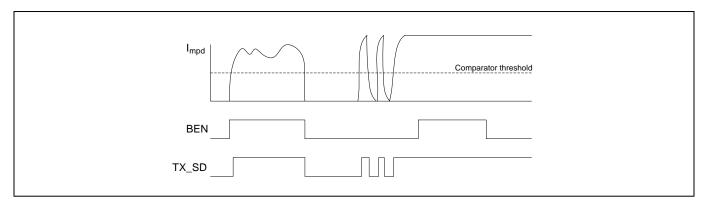

Figure 7. TX\_SD Pin Signal Generation

The MPD current is compared with a threshold current set by the **txsd\_threshold** register. This determines the MPD current level at which both TX\_SD and rogue ONU are detected.

When BEN = '0' the TX\_SD logic transfers the comparator output directly through to tx\_sd. In addition, the Rogue ONU Fault Detect logic transfers the comparator output through to the laser safety system. The **txsd\_rogueonu\_delay** register specifies the delay (in cycles of the internal 64MHz clock) between the falling edge of BEN and testing for rogue ONU. The rogue onu fault condition is not generated during this time.

When BEN = '1' the TX\_SD logic output goes high when the input from the comparator goes high. This state is latched. The  $tx\_sd$  signal will then remain high until either the end of the burst, or until the comparator output remains low for a period of time exceeding the time defined by the  $txsd\_deglitch\_period$  register. This prevents  $tx\_sd$  from toggling during a burst due to the pattern sensitivity of the MPD current. (During bias loop fast-start,  $tx\_sd$  is held at '1')

Selection between TX\_SD and TX\_FAULT functionality is governed by the **txsd\_select** register. The **txsd\_allow** register holds the pin high until the configuration register load from EEPROM (or microcontroller) is complete. This avoids multiple transitions on the TX\_SD pin during initialization.

### Rogue ONU Behavior

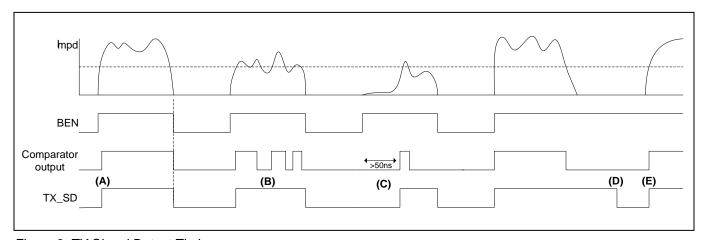

Figure 8. Rogue ONU Timing

#### TX\_SD Behavior

Figure 9. TX Signal Detect Timing

During the gaps the TX\_SD logic is transparent and the comparator output is routed directly through to the TX\_SD pin.

#### During the bursts:

- (A) The TX\_SD pin is asserted high when the MPD current first exceeds the threshold.

- (B) The TX\_SD pin will not toggle in response to short term fluctuations of the MPD current above and below the threshold (due to the pattern sensitivity of the MPD current).

- **(C)** There is a requirement that the TX\_SD pin responds within 50ns of the assertion of BEN. The MPD current is settled and the TX\_SD circuitry can respond well within 50ns of the start of a burst. However, the MAX24001 will assert TX\_SD high whenever a signal is detected during a long burst—even if the signal does not appear until well after the initial 50ns.

- **(D)** If the laser stops outputting light during a burst, then there is a delay before TX\_SD goes low. This is necessary in order to distinguish between the MPD current dipping below threshold due to a run of zeros, and the MPD current dropping below threshold due to a legitimate loss of signal. The delay is programmable using **txsd deglitch period**.

- (E) If the signal is restored during a burst then TX\_SD is asserted high again.

#### Laser Biasing

[Control Register Address Range A4h: A2h to A9h]

The bias current is controlled by the **tx\_biasdac** register in one of six operating modes:

| OPERATING<br>MODE              | DESCRIPTION                                                                                                                                                                                                                                                                          | tx_biasmode<br><2:0> |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Open loop, static              | tx_biasdac only changes when it is written by the host                                                                                                                                                                                                                               | 000                  |

| Open loop, LUT                 | tx_biasdac is constantly refreshed from values read from a temperature indexed lookup table (the bias LUT)                                                                                                                                                                           | 001                  |

| Closed loop,<br>natural start  | An automatic power control (APC) loop constantly adjusts tx_biasdac in order to maintain a target laser output power level. tx_biasdac defaults to near-zero after power-up and then converges naturally on the target level over a duration of time dictated by the loop bandwidth. | 100                  |

| Closed loop,<br>LUT start      | The APC loop controls tx_biasdac, and tx_biasdac is preloaded from the bias LUT at power-up.                                                                                                                                                                                         | 101                  |

| Closed loop,<br>fast start     | The APC loop controls tx_biasdac, and a fast-start algorithm is invoked at power-up to rapidly converge the loop on the target power level.                                                                                                                                          | 110                  |

| Closed loop,<br>LUT fast start | The APC loop controls tx_biasdac. tx_biasdac is preloaded from the bias LUT at power up, and then a fast-start algorithm is invoked to rapidly converge the loop on the target power level.                                                                                          | 111                  |

#### Operational Overview

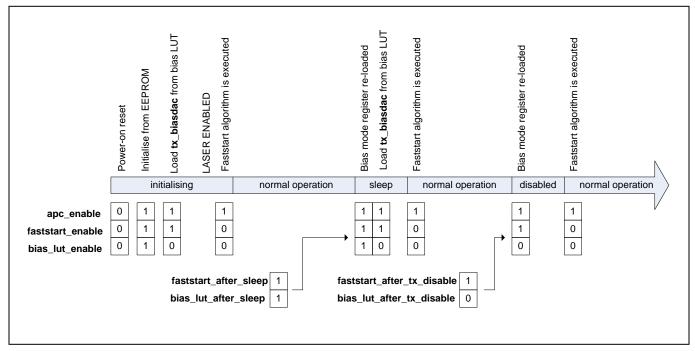

The tx biasmode<2:0> register is a grouping of three individual controls registers:

tx\_biasmode<0>: bias\_lut\_enable tx\_biasmode<1>: faststart\_enable tx\_biasmode<2>: apc\_enable

#### Open-Loop Operation

Clear the apc\_enable register for open-loop operation.

The laser bias current is controlled by the **tx\_biasdac** register with a resolution of 92.5µA per LSB (nominal). This register may be set by the host, or alternatively set the **bias\_lut\_enable** bit to cause the **tx\_biasdac** register to be automatically refreshed from the bias lookup table (LUT) every 10ms. The bias LUT is stored in external EEPROM at TWI slave address A6h, register address range 00h to 7Fh. It is indexed using the upper 7 bits of **temperature\_uncal**.

If the **biasramp\_en** register is set then the value in **tx\_biasdac** ramps progressively from the old value to the new by 1 LSB every cycle of the internal 64MHz clock. This prevents glitches from occurring in the DAC. If ramping is disabled then updates to **tx\_biasdac** are effective immediately.

#### Closed-Loop Operation

Set the **apc\_enable** register for closed-loop operation.

The automatic power control (APC) loop compares a value of laser output power produced by the power monitoring circuits with a target level set by **tx\_apc\_target**. This proportional error value is scaled using the **apc\_loop\_gain** and is then used to adjust the value of **tx\_biasdac** (which has a number of internal precision extension bits). The **apc\_loop\_gain** register thus controls the bandwidth of the APC loop.

Since the bandwidth of the loop is not very high, it is desirable to set the **tx\_biasdac** register to a point as close as possible to the target laser power level before the APC loop takes over. This is achieved by preloading the **tx\_biasdac** register with a value from the bias LUT and/or running a search algorithm (referred to as fast-start). These actions are both triggered by the **bias\_lut\_enable** and **faststart\_enable** bits. When these bits are set, then a table lookup or fast-start will occur at the next available opportunity. Once the lookup or fast-start has occurred then these bits are cleared. The host may therefore re-trigger fast/lut start by resetting **bias\_lut\_enable** and **faststart enable** at any time. The bits are also set automatically as follows:

On power-up: tx\_biasmode is configured from EEPROM

During SLEEP: The value in **faststart\_after\_sleep** is transferred to **faststart\_enable**

The value in bias lut after sleep is transferred to bias lut enable

During TX\_DISABLE: The value in faststart\_after\_txdisable is transferred to faststart\_enable

The value in bias\_lut\_after\_txdisable is transferred to bias\_lut\_enable

Thus, the required loop behavior when the laser is enabled can be independently configured for reset, sleep mode and tx disable. This is further illustrated in the figure below:

Figure 10. Behavior of the tx\_biasmode Register in Closed-Loop Mode

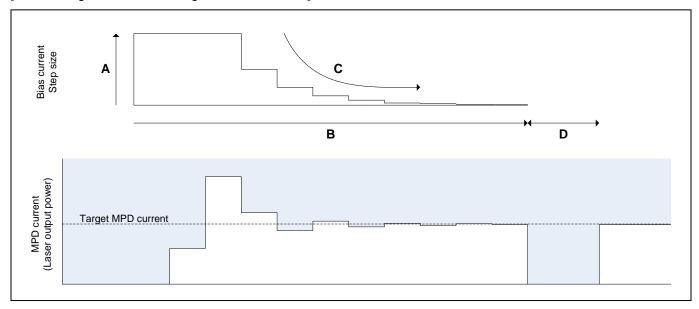

#### Fast-Start Algorithm

[Control Register Address Range A4h: AAh to Ach]

Figure 11. Fast-Start Algorithm Timing

During fast-start, the MAX24001 is temporarily reconfigured. The modulation driver sinks a constant current of  $I_{MOD}/2$  on TX\_OUT to represent the contribution made by the signal current to the average power. The power monitoring circuit is reconfigured to supply a direct comparison between the received MPD current and the target MPD current. The process of making a change to bias current and then a subsequent comparison of MPD current and target current is referred to as iteration. An iteration has a fixed duration (nominally 62ns).

Initially, the bias current is stepped up on every iteration until the MPD current exceeds the threshold. The initial bias current step size A is ideally  $\frac{1}{2}$  the modulation current, the rationale being that this is the largest step which can be taken whilst ensuring that the P1 power level is not exceeded. More generally, the initial step size is defined as A = (tx\_fstart\_initial/256) x I<sub>MOD</sub>.

When the target level is exceeded the step size then decays (C). Halving the step size every iteration amounts to a binary search. In practice, incomplete settling of the loop can result in a small overshoot of the target current level. It is therefore recommended that each step is slightly more than 0.5x the previous step. This is configurable using the **fstart\_decay** register. The **fstart\_decay** register determines the multiplication factor applied to the step size on each subsequent iteration of the fast-start algorithm.

| f <sub>start_decay</sub> | STEP DECAY<br>MULTIPLIER |

|--------------------------|--------------------------|

| 100000                   | 32/64 = 0.5              |

| 100001                   | 33/64 = 0.516            |

| 100010                   | 34/64 = 0.531            |

| 100011                   | 35/64 = 0.547            |

| 100100                   | 36/64 = 0.563            |

| 100101                   | 37/64 = 0.5785           |

| **                       |                          |

| 101110                   | 46/64 = 0.719            |

| 101111                   | 47/64 = 0.734            |

The direction of each current step depends on whether the measured MPD current is above or below the target level. The number of iterations B is controlled by the **fstart\_duration** register. The maximum number of iterations which can be guaranteed to complete within 3 x 400ns bursts is 15.

At the end of the fast-start algorithm, the laser output stage switches from sinking DC  $I_{MON}/2$  on TX\_OUT to full amplitude signal. This may result in a brief current spike. A facility is provided to optionally shut down the modulation current through the laser during this transition period (D). Use the **fstart\_recovery\_en** and **fstart\_recovery\_time** registers to shut down the modulation current for 0, 1, or 2 iterations.

#### APC Loop Bandwidth

The **apc\_loop\_gain** register adjusts the gain of the APC control loop. Loop bandwidth (Hz) is calculated as a function of **apc\_loop\_gain**:

$$\begin{split} Bandwidth\,(Hz) = \frac{2^{apc\_loop\_gain - 15} \ \ k_{elec} \ \ \ k_{mpd} \ \ \ (biasdac\_lsb \ \ \ 4) \ \ f_{CLOCK}}{2 \ \ p \ \ 16 \ \ mondac\_lsb} \\ = 2^{apc\_loop\_gain - 15} \ \ \ k_{elec} \ \ \ k_{mpd} \ \ \ 3.02 \ \ \ 10^8 \end{split}$$

Where: mondac\_lsb =  $0.78\mu A$ biasdac\_lsb =  $92.5\mu A$

$f_{CLOCK}$  = 64MHz (typical)

kmpd = 0.0625 when **mpd\_range** = 10

0.25 when mpd\_range = 01 1 when mpd\_range = 00

$k_{elec}$  = (MPD current)/(laser current)

| apc_loop_gain                                     | GAIN                                                                                                 |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 0000<br>0001<br>0010<br>:<br>1100<br>1101<br>1110 | 2 <sup>-15</sup> 2 <sup>-14</sup> 2 <sup>-13</sup> : 2 <sup>-3</sup> 2 <sup>-2</sup> 2 <sup>-1</sup> |

| 1111                                              | 1                                                                                                    |

#### **Power Monitoring**

A power monitoring circuit generates a digital measure of MPD current (laser power) based on time-averaged samples taken during bursts when the laser is enabled. It has three settings in order to accommodate the wide range of monitor photodiode currents. The range setting (**mpd\_range**) is chosen at the time that the module is calibrated, and does not change during normal operation of the APC loop. The unfiltered, 8-bit digital measure of MPD current is used internally by the APC loop.

| mpd_range | PD MIRROR<br>GAIN | I <sub>MON</sub> OPERATING<br>RANGE (µA) |

|-----------|-------------------|------------------------------------------|

| 00        | 1                 | 40 to 200                                |

| 01        | 1/4               | 100 to 800                               |

| 10        | 1/16              | 400 to 2000                              |

Tracking error in the TOSA means that the MPD current may vary over temperature in a nonlinear way for a given laser optical power. If the temperature-indexed tracking error lookup table (LUT) is enabled then the digital measure of MPD current is multiplied by the values read from the LUT. Each entry in the LUT represents a number in the range 0.5 (00h) to 1.5 (FFh), and 80h represents unity gain.

Set the **trackinglut\_en** bit to enable this feature. A correction factor is retrieved from the tracking error LUT every 10ms. This LUT is stored in external EEPROM at TWI slave address A8h, register address range 80h to FFh. It is indexed using the upper 7 bits of **temperature uncal**.

The digital measure of MPD current (including tracking error compensation) is used by the APC loop to control bias current.

#### **Power Reporting**

For power reporting purposes, the power monitor output is low-pass filtered to suppress the pattern sensitivity of the MPD current. This filter bandwidth is programmable using the mon\_bandwidth register. Bandwidth =  $64/(2\pi \times 2^{(15-n)})$  where n is the 4-bit integer mon\_bandwidth value up to a maximum of 14. The filtered measure of laser power can be read from the txpower uncal register.

| mon_bandwidth    | BANDWIDTH at f <sub>CLOCK</sub> = 64MHz |

|------------------|-----------------------------------------|

| 0000<br>0001     | 311Hz<br>622Hz                          |

| 1000             | <br>80kHz                               |

| <br>1110<br>1111 | 5.1MHz<br>No filtering                  |

The *mpd\_range* should be set at a level which accommodates the expected range of MPD current. The MAX24001 is not designed to automatically range switch during normal APC loop operation. However, if the APC loop fails and the power monitor saturates then the *mpd\_range* will temporarily switch so that power reporting can cover the full 0 to 2mA range of photodiode current. The range then recovers back to the original setting if the power monitor value drops back below 64.

### **Power Leveling**

The power\_levelling register implements GPON power levelling. Set to 00, 01, or 1x to reduce the modulation amplitude set by tx\_moddac by x1, x0.5 and x0.25, respectively. This register will also reduce the power level by having the same effect on the output of the tx\_apc\_target register. Power levelling does not affect the bias current in open-loop mode.

#### Laser Safety

[Control Register Address Range A4h: AFh to B3h]

The laser safety system generates two signals, tx\_fault\_int and tx\_shutdown\_int. Tx\_fault\_int is pure status. It reports via both register and TX\_FAULT pin whether one or more enabled fault conditions have occurred. The TX\_FAULT pin can be configured to appear at pin 21 or 39 using pin\_config0. Tx\_shutdown\_int is a control signal. It disables the bias and modulation currents to the laser when one or more enabled fault conditions have occurred.

#### **Fault Conditions**

The fault conditions which affect tx fault int and tx shutdown int are:

Bias Fault This occurs when the BIAS pin is shorted to ground.

APC Fault This occurs when the MPD pin is shorted to ground.

VREF Fault This occurs when the RREF pin is shorted to ground.

VDD Fault This occurs when brownouts are detected on TX or TXO.

Tx Disable Fault Is given by: (TX\_DISABLE XOR tx\_disable\_invert) OR soft\_tx\_disable where

TX\_DISABLE is the pin value and **soft\_tx\_disable** is in SFF-8472 **status control**.

Soft Tx Fault This occurs when the **soft\_tx\_fault** bit in **software\_faults** register is set.

RogueOnu Fault If the laser is on during a gap between bursts then this fault condition is generated.

Alarm Fault This occurs when one or more of the SFF-8472 DDM alarm flags are set to '1'. The flags

which contribute to Alarm Fault are programmable via Is\_alarmflag\_en.

When the laser is in shutdown then the bias fault condition is ignored by the laser safety system. When tx\_shutdown is deasserted there is a 250µs delay before the bias fault condition is used. This allows the circuit which detect a ground short on the bias pin time to settle before the bias fault condition is seen by the laser safety system.

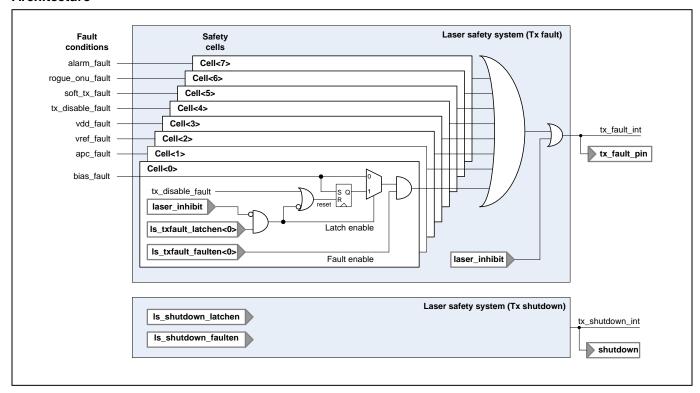

#### Architecture

Figure 12. Laser Safety System

The laser safety system (Tx fault) generates the  $tx_fault_int$  signal. The status of this signal can be accessed in the SFF-8472 **status\_control** register. The signal is also multiplexed onto the TX\_FAULT/TX\_SD pin.

Every safety cell has its own pair of latch enable and fault enable control register bits. The fault condition can only propagate through to the output when \_faulten = '1'. When \_latchen = '1' a latched version of the fault condition is used. The latch is held in reset when latching is disabled or when the tx\_disable\_fault signal is asserted. Note that tx disable fault is also a fault condition signal.

When it is asserted, the laser\_inhibit signal holds all latches in reset and forces the tx\_fault\_int signal to '1'. Note that after the power-on reset, laser\_inhibit is enabled. During initialization pin\_config is the last configuration register to be loaded from EEPROM and therefore has the effect of clearing laser\_inhibit and thus enabling the laser.

**Is\_fault\_status** reports the status of the fault conditions at the inputs to the safety cells.

The laser safety system is fully replicated for controlling laser shutdown. The system uses the **Is\_shutdown\_faulten** and **Is\_shutdown\_latchen** registers and produces the tx\_shutdown\_int signal for disabling the modulation and bias currents. The internal architecture is otherwise the same as the system for Tx Fault. The **shutdown** register can be found in **hardware\_status**.

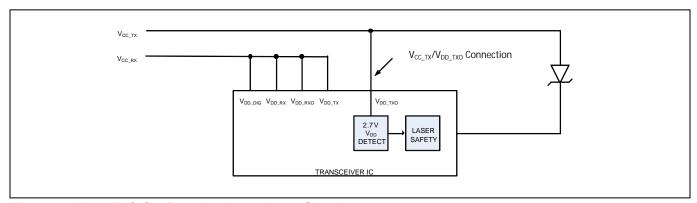

The module Tx supply  $(V_{CC\_TX})$  can be used in some applications to shut down the laser. This is supported in MAX24001 by detecting the removal of  $V_{CC\_TX}$  on the  $V_{DD\_TXO}$  pin.  $V_{CC\_TX}$  is connected to  $V_{DD\_TXO}$  as shown in Figure 13. A shutdown is then asserted if the voltage falls below 2.7V. If the connection between  $V_{CC\_TX}$  and  $V_{DD\_TXO}$  is not used,  $V_{DD\_TXO}$  must be connected to another supply.

Figure 13. VDD\_TXO Configured to Assert Laser Shutdown

#### Temperature Sensor

[Control Register Address Range A4h: B6h, B9h, C1h]

The MAX24001 includes an integrated temperature sensor that reports the module temperature at the sensor transistor. The **temp\_ext\_sensor** register selects between an internal transistor or an external PNP transistor connected to the TSENSE and TSENSE\_RET pins. If an external transistor is used then the PCB tracks connecting an external PNP transistor to the chip each have resistance <<  $1\Omega$ . i.e. the tracks must be kept as short as possible. The temperature sensor reports a value in **temperature\_uncal** once every 65ms. Resolution is approximately 0.8C per LSB of **temperature\_uncal**. Part-to-part accuracy is optimized by adjusting **temp\_calibrate** until each part reports the same value of **temperature\_uncal** at a common temperature.

Setting **leave\_pu** and **tempsense\_pu** enables the temperature sensor to be in a power-saving mode by powering down between reads.

#### APD Controller

[Control register address range A4h: 94h]

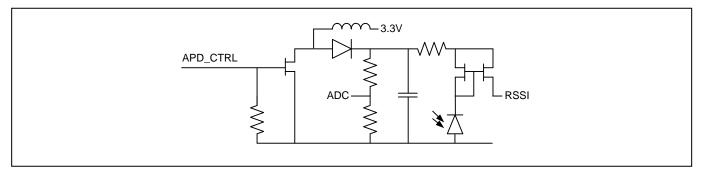

Figure 14. APD Biasing Application

Figure 14 shows a simplified arrangement for controlling the APD bias voltage, whereby the FET is switched by a pulse width modulated signal. The duty cycle can be used to control the voltage across the capacitor. This voltage can be sampled at the tap point of the potential divider. The MAX24001 provides functions which support this approach.

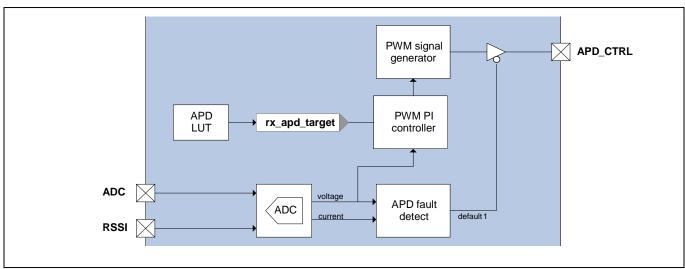

Figure 15. APD Biasing Control Loop Components

The PWM frequency can be configured to be 250kHz, 500kHz, 1MHz or 2MHz by **pwm\_frequency**. The 8-bit value of **rx\_apdpwm** adjusts the duty cycle from 0/256 to 255/256.

The APD controller adjusts the value of **rx\_apdpwm** according to the proportional and integral gain setting of the loop in registers **k\_proportional** and **k\_integral** such that the voltage level sampled on the ADC pin converges on the target value **rx\_apd\_target**. The target value apdlut\_en may be fixed, or it may be actively refreshed from the temperature indexed APD lookup table (LUT) when **target\_lut\_enable** is set. This LUT is stored in EEPROM at two-wire slave address A8h, register address range 00h to 7Fh. The LUT is indexed by **temperature\_uncal**.

When the APD controller is active, a limit may be imposed on the maximum PWM duty using max duty.

#### APD Controller—Additional features

APD safety features are also implemented. If the sampled value of RSSI current exceeds **rx\_apd\_i\_threshold**, or the sampled voltage on the ADC pin exceeds **rx\_apd\_v\_threshold** then the APC\_CTRL pin driver is disabled (Hi-Z). Set the thresholds to FFh to disable this feature.

The APD controller is disabled when **k\_proportional** and **k\_integral** are both zero. The value in **rx\_apdpwm** can be written directly, or will be periodically refreshed from the APD LUT if **pwm\_lut\_enable** is set. The polarity of the output on APD CTRL can be inverted by setting **pwm invert** to '1'.

If an external control loop is used (for example, using an external DC-DC converter) then this loop could be controlled by the DAC pin. The DAC is controlled from the **rx\_apddac** register. This will be periodically refreshed from the APD LUT if **dac\_lut\_enable** is set. In this arrangement, the APD\_CTRL pin can be used to control the shutdown input pin of the DC-DC converter.

#### **Digital Diagnostics**

#### Data Generation

[Control Register Address Range A4h: B4h to B5h, E6h to EAh]

Temperature, supply voltage, laser bias current, transmit power, and received power are all periodically sampled.

#### **Temperature**

The uncalibrated temperature can be read from the temperature\_uncal register.

#### Supply Voltage

Select between Tx and Rx supply voltages using **adc\_supplysel**, and adjust the sampling rate using **supply\_bandwidth**. The uncalibrated supply voltage can be read from the **supply\_uncal** register.

#### Tx Bias Current

The bias current measured during a burst will continue to be reported between bursts, irrespective of the length of the gap. If the laser is deliberately shutdown by the laser safety system or by asserting TX\_DISABLE then Bias Current reports zero and the low alarm/warning flags are set. The uncalibrated bias current is read from the **bias\_uncal** register.

#### Tx Power

The Tx Power measured during a burst will continue to be reported between bursts, irrespective of the length of the gap. If the laser is deliberately shutdown by the laser safety system or by asserting TX\_DISABLE then Tx Power reports zero and the low alarm/warning flags are set. The uncalibrated Tx Power is read from the **txpower\_uncal** register.

#### Rx Power

The RSSI pin can both source and sink a current (**rx\_rssi\_sink**) which is proportional to the optical power incident on the receiver. Resolution can be enhanced by applying additional gain (x1, x1.5 or x2) to the current at the RSSI pin using the **rx\_rssi\_scale** register (see **los\_rssi\_config**).

For Rx power measurement, the ADC is used in nonlinear "3-slope" mode. This provides both wide dynamic range and high resolution at low powers. The uncalibrated, 3-slope encoded value of Rx Power is read from the **rxpower\_uncal** register.

| RSSI CU     | rxpower_uncal |            |                |

|-------------|---------------|------------|----------------|

| GAIN x1     | GAIN x1.5     | GAIN x2    | ixpowei_uiicai |

| 0 to 16     | 0 to 11       | 0 to 8     | 0 to 32        |

| 16 to 208   | 11 to 139     | 8 to 104   | 32 to 128      |

| 208 to 1232 | 139 to 821    | 104 to 616 | 128 to 255     |

Adjust the Rx Power sampling bandwidth using **rxpower bandwidth**.

### **Digital Diagnostic Monitors**

The raw digital measures of: temperature, supply voltage, bias current, Tx Power, and Rx power are converted into calibrated SFF-8472 Digital Diagnostic Monitor (DDM) values once every 10ms when sff\_en is set and the main loop is active (mainloop\_en is set). These registers are located in main\_config. The following calibration constants are used:

| METRIC          | REFERENCE | SLOPE<br>(SLA: A4h) | OFFSET<br>(SLA: A4h) | DDM<br>(SLA: A2h) |

|-----------------|-----------|---------------------|----------------------|-------------------|

| Temperature     | temp      | 00h-01h             | 02h-03h              | 60h-61h           |

| Supply Voltage  | vcc       | 04h-05h             | 06h–07h              | 62h-63h           |

| Tx Bias Current | bias      | 08h-09h             | 0Ah-0Bh              | 64h-65h           |

| Tx Power        | txpower   | 0Ch-0Dh             | 0Eh-0Fh              | 66h-67h           |

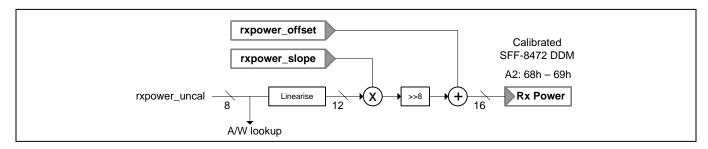

| Rx Power        | rxpower   | 10h-11h (slope 0)   | 12h-13h (offset 0)   | 68h-69h           |

|                 |           | 14h-15h (slope 1)   | 16h-17h (offset 1)   |                   |

All slope values (including Rx power) are stored as 16-bit fixed point (unsigned) as per SFF-8472 external calibration constants. The slope is calculated as DDM LSB's per ADC increment, e.g. for supply voltage the slope unit (bit 8) represents units of 100µA per ADC increment (hence the >>8 operation after multiplication).

All offset values (including Rx power) are stored as 16-bit fixed point (signed two's complement) as per SFF-8472 external calibration constants. In all cases, the upper byte of the 16-bit word is stored at the lower address.

Rx power has an additional pair of constants to support a rough piecewise linear approximation of the nonlinear characteristic of received optical power vs. RSSI current. This occurs when a series resistor is used between the APD and the APD bias voltage generation circuit. It provides a form of compression, protecting the APD by reducing avalanche gain if current gets too high.

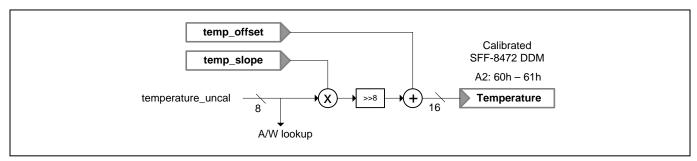

#### **Temperature**

Figure 16. Calculating the Temperature DDM

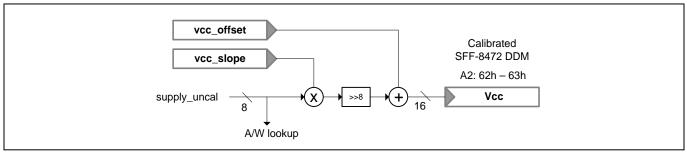

#### Supply Voltage

Figure 17. Calculating the Supply Voltage DDM

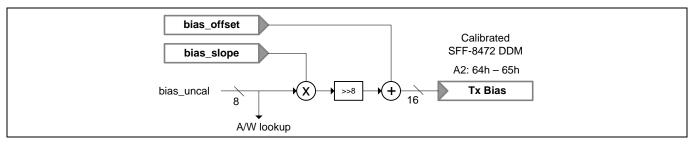

#### Tx Bias Current

Figure 18. Calculating the Bias Current DDM

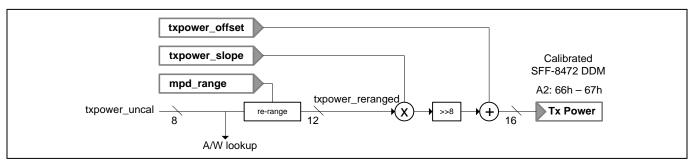

#### Tx Power

Figure 19. Calculating the Tx Power DDM

The power monitor generates an 8-bit measure of MPD current after a gain of 1, 1/4, or 1/16 has been applied. Reranging increases the Tx Power value when gains < 1 have been applied to the MPD current.

#### Rx Power

Figure 20. Calculating the Rx Power DDM

The following formulae are used to convert the 3-slope **rxpower\_uncal** value into a linear pseudo 12-bit (0 to 2448) value:

The selected pair of slope and offset values depend on the value of **linearized\_rx\_power**. If **linearized\_rx\_power** is greater than **rxpower\_threshold**, then use the slope and offset pair from the address range 14h to 17h. Otherwise use the slope and offset pair from address range 10h to 13h. This coarsely accommodates the nonlinearity of the curve of received optical power vs. RSSI current.

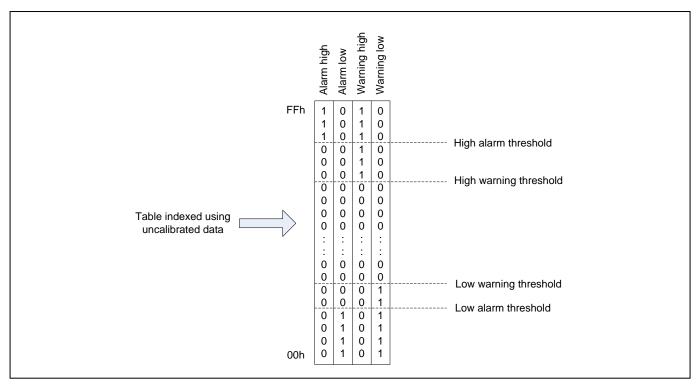

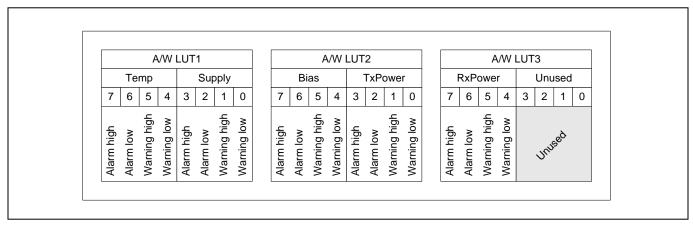

#### Alarm and Warning Flags

Figure 21. Using 8-Bit Calibrated Data to Look Up Alarm and Warning Flags

Figure 22. Alarm and Warning LUT Mapping

The uncalibrated 8-bit diagnostic data values are used to index the alarm and warning LUTs. Construct a LUT by identifying the required threshold levels in absolute units (V, C, mA,  $\mu$ W) and then reverse the calculations shown by the figures in the previous section to yield corresponding uncalibrated threshold levels. For Tx and Rx power, these should incorporate the range and 3-slope encoding, respectively.

The **Is\_alarmflag\_en** register controls which of the DDM alarm flags contribute to the laser safety alarm\_fault fault condition.

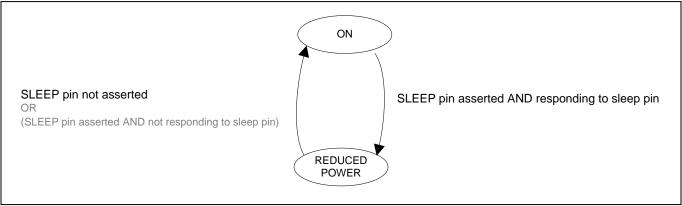

## Power-Up and Sleep Mode

[Control Register Address Range A4h:8Ch, B8h]

The MAX24001 can be put into a low-power mode of operation when the SLEEP pin is asserted. This is achieved by combining the sleep function with the chip-power sequencing, SLEEP can be configured to independently affect the Rx and Tx signal paths.

Rx Signal path: The response to the SLEEP pin is controlled by the rx\_respond\_to\_sleeppin register.

Tx Signal path: The response to the SLEEP pin is controlled by the tx\_respond\_to\_sleeppin register.

Figure 23. Conditions for Moving In and Out of Sleep Mode

The device will only move between these states when power sequencing is enabled (tx\_powerup\_en and rx\_powerup\_en are set).

The host can alternatively put the MAX24001 to sleep using the tx force sleep and rx force sleep registers.

#### Initialization and Control

#### Overview

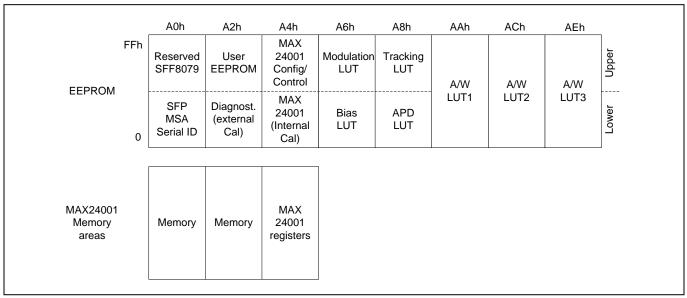

The MAX24001 is normally used in conjunction with a 2k byte EEPROM.

Figure 24. Address Map

### **Normal Operation**

During initialization, data is transferred from EEPROM areas with TWI slave addresses A0h and A2h into shadow areas of memory on the MAX24001. Device configuration data is transferred from area A4h into MAX24001 registers.

During normal operation, the MAX24001 has exclusive access to the lookup tables held in EEPROM using the TWI master interface. The MAX24001 TWI slave interface only decodes slave addresses A0h and A2h, and when the host accesses these areas it is accessing the shadowed memory on the MAX24001. The diagnostic data in the memory is regularly refreshed.

#### Using a Microcontroller

If the initialization fails, then the MAX24001 defaults to a state whereby the Tx and Rx paths are not enabled, the main loop is off, and all memory areas are accessible. A microcontroller may then upload data to registers and control the operation of the MAX24001.

#### Module Setup

To access EEPROM (cf initialisation status and system control registers)

- " Clear mainloop en. This stops the main loop.

- Wait until eeprom dma idle is set. Accesses to EEPROM have then ceased.

- " Set external\_access to direct accesses via the TWI slave interface to EEPROM.

All regions of the EEPROM may then be accessed as long as the chip is in security level 2.

#### Access Control

[Control register address range A2h: 7Ch to 7Fh, and A4h: 82h to 8Bh]

Three levels of security are defined. The security level determines which areas of EEPROM and register space may be accessed via the two-wire interface. The security level is selected by the **password\_entry** register and can be read from the **security\_level** register in **system\_status**.

**Level2** – (password\_entry value matches password2). The host has full read and write access to all address spaces. (password2 has priority over password1).

**Level1** – (password\_entry value matches password1). The host has read and write access to A0h and A2h only, as defined by the upper nibbles of the password\_configA0 and password\_configA2 registers.

**Level0** – (password\_entry value matches neither password1 nor password2). The host has read and write access to A0h and A2h only, as defined by the lower nibbles of the password\_configA0 and password\_configA2 registers.

**Password1** and **password2** can only be written in level2. The security level will not change when writing a new value to **password2**. Typically access in level 0 is more restrictive than access in level1. Read and write access to A2h:78h to 7Fh is always permitted. If access is denied then the transaction is discarded in the case of a write, and returns FFh in the case of a read. During burst-mode accesses, access permission and destination are tested on a byte-by-byte basis.

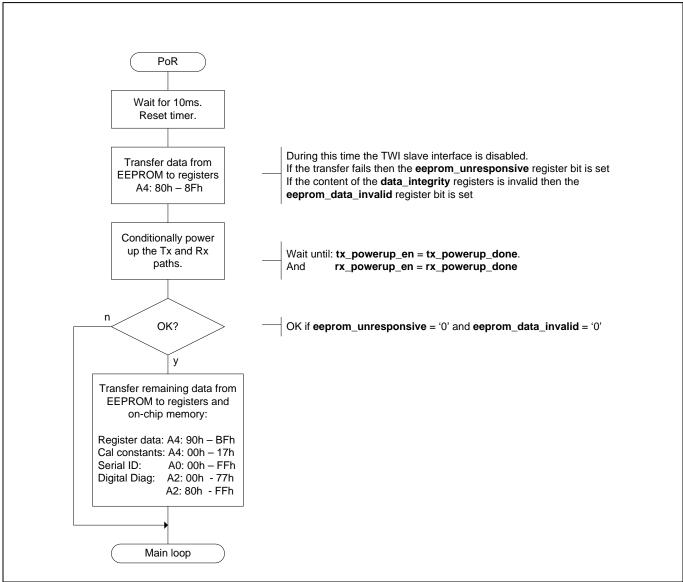

#### Initialization Sequence

[Control register addresses A4h: 80h, 81h, 8Ch, E0h]

Figure 25. Initialization Sequence

The data integrity bytes are the first two bytes to be read from EEPROM (addresses A4: 80h to 81h). If **data\_integrity0** = C3h and **data\_integrity1** = 5Ah then it is inferred that the EEPROM is correctly programmed and initialization continues.

If the read access fails (no EEPROM) then **eeprom\_unresponsive** is set. If the read access succeeds but the data integrity values are incorrect then **eeprom\_data\_invalid** is set. In both cases the transfer from EEPROM is aborted to prevent MAX24001 defaults from being overwritten with random data. The Tx and Rx paths will not power up and the MAX24001 will remain in the wait state at the start of the main loop.

The data integrity values only exist in EEPROM. They have no corresponding registers.

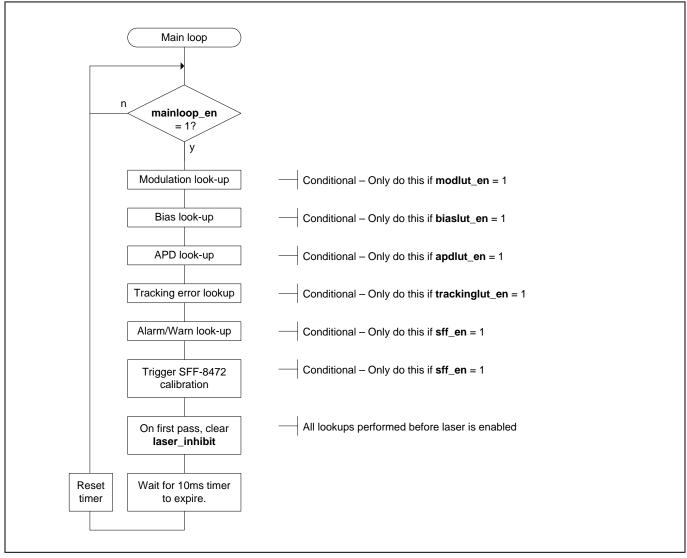

### Main Operating Loop

[Control register address A4h: B7h]

Figure 26. Main Operating Loop

The modulation, bias, APD, and tracking error LUTs are all 128 bytes and indexed by the upper 7 bits of the uncalibrated temperature sensor output (**temperature\_uncal**). Typically, LUT entry 14h corresponds with a temperature of -40°C. LUT resolution is then 1.6°C between consecutive table entries. These values are approximate and may vary slightly from batch to batch.

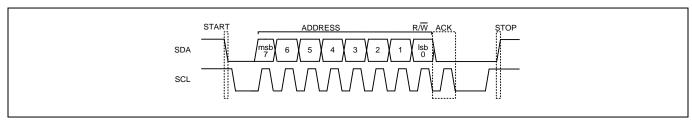

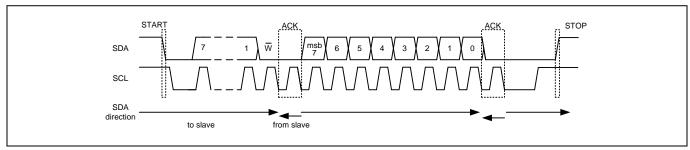

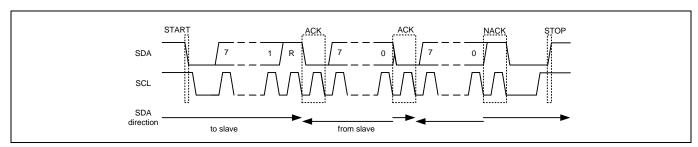

#### Two-Wire Interface (TWI) Protocol

The SDA\_SLAVE and SCL\_SLAVE pins are referred to as the slave two-wire interface (slave TWI). The slave TWI provides external access to both registers within the MAX24001 and to any device connected to the SCL\_MASTER and SDA\_MASTER pins (the master TWI). Typically, an EEPROM is connected to the master TWI.

#### Framing and Data Transfer

The two-wire interface comprises a clock line (SCL) and a data line (SDA).

An individual transaction is framed by a START condition and a STOP condition. A START condition occurs when a bus master pulls SDA low while SCL is high. A STOP condition occurs when the bus master allows SDA to transition low-to-high when SCL is high. Within the frame the master has exclusive control of the bus. The MAX24001 supports Repeated START conditions whereby the master may simultaneously end one frame and start another without releasing the bus by replacing the STOP condition with a START condition.

Within a frame the state of SDA only changes when SCL is low. A data bit is transferred on a low-to-high transition of SCL. Data is arranged in packets of 9 bits. The first 8 bits represent data to be transferred (most significant bit first). The last bit is an acknowledge bit. The recipient of the data holds SDA low during the ninth clock cycle of a data packet to acknowledge (ACK) the byte. Leaving SDA to be pulled high on the ninth bit signals a not-acknowledged (NACK) condition. The interpretation of the acknowledge bit by the sender depends on the type of transaction and the nature of the byte being received. SDA is bidirectional so that the master may send data bytes during write transactions and the slave may send data bytes during reads.

#### **Device Addressing**