MAX20481

Click here to ask an associate for production status of specific part numbers.

# Four- to Seven-Input Automotive Power-System Monitor Family

#### **General Description**

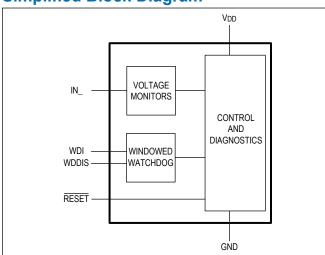

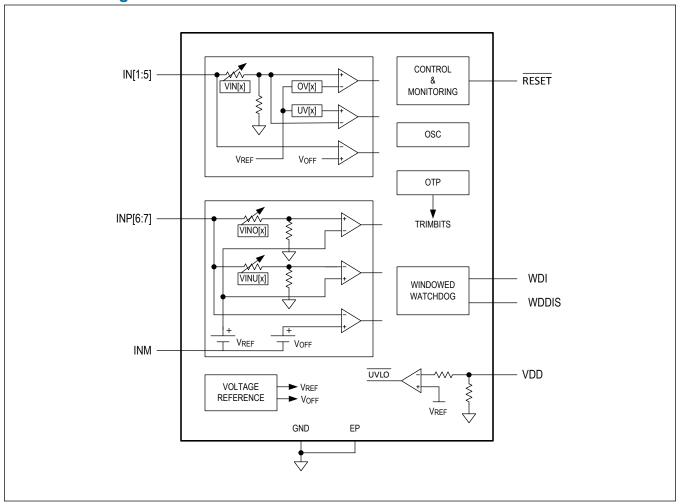

The MAX20481 is a complete ASIL-compliant SoC power system monitor with up to seven voltage-monitor inputs. Each input has factory OTP programmable OV/UV thresholds of between 2.5% and 10% with  $\pm 1\%$  accuracy. Two of the inputs have a separate remote ground-sense input for use with high-current SoC supplies.

The MAX20481 contains a factory-programmable windowed watchdog with digital input pins for both refreshing and disabling the watchdog. The RESET pin of the device can be set at the factory to assert under a variety of conditions.

The MAX20481 significantly reduces system size and component count while improving reliability compared to separate ICs or discrete components. The MAX20481 meets ASIL B reliability levels in a standalone application. The device is designed to operate from -40°C to +125°C ambient temperature.

#### **Applications**

- ADAS

- Autonomous Driving Processing Systems

- Remote Sensor Modules

- Power System Supervision and MCU/SoC Montioring

#### **Benefits and Features**

- Small Solution

- 2.35V to 5.50V Operating Supply Voltage

- · No External Components Needed

- 150µA Operating Current

- High Precision

- Selectable 102.5% to 110% OV Monitors

- Selectable 97.5% to 90% UV Monitors

- ±1% Accuracy

- 0.5% Step Size

- ASIL B Compliance

- Highly Integrated

- · Five Fixed-Voltage Monitoring Inputs

- Two Differential-Voltage Monitoring Inputs with Remote GND Sense

- Windowed Watchdog with Disable Pin for SoC Programming

- · Error-Correcting Code (ECC) on Internal OTP

- Factory-Programmable RESET Pin

- 16-Pin, Side-Wettable TQFN with Exposed Pad (3mm x 3mm)

- AEC-Q100 Qualified

- -40°C to +125°C Operating Temperature

## **Simplified Block Diagram**

## **TABLE OF CONTENTS**

| General Description                       |     |

|-------------------------------------------|-----|

| Applications                              |     |

| Benefits and Features                     |     |

| Simplified Block Diagram                  |     |

| Absolute Maximum Ratings                  | 4   |

| Package Information                       | 4   |

| 16-TQFN-EP                                | 4   |

| Electrical Characteristics                | 4   |

| Typical Operating Characteristics         | 7   |

| Pin Configurations                        |     |

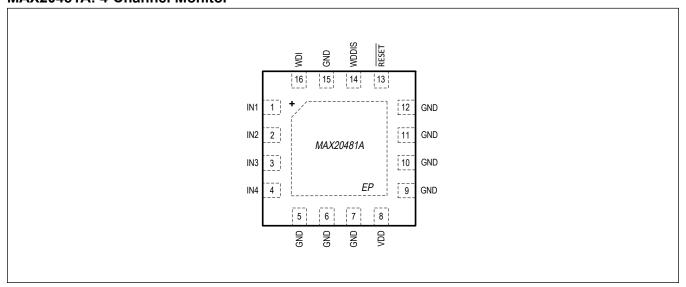

| MAX20481A: 4-Channel Monitor              | 8   |

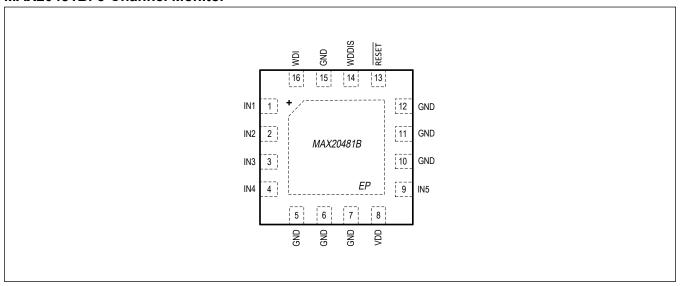

| MAX20481B: 5-Channel Monitor              | 8   |

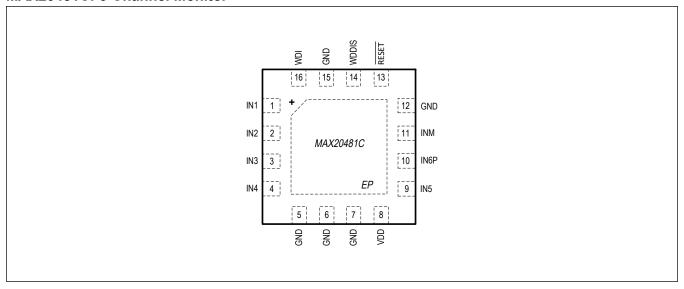

| MAX20481C: 6-Channel Monitor              | g   |

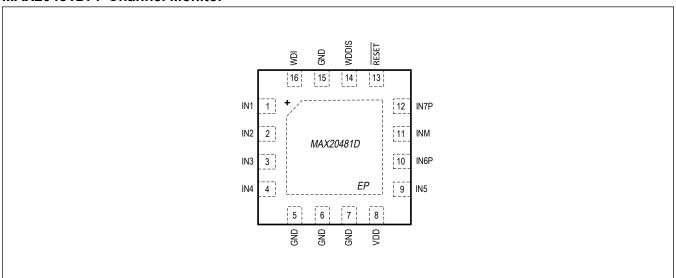

| MAX20481D: 7-Channel Monitor              | 9   |

| Pin Description                           | g   |

| Functional Diagrams                       | 11  |

| Detailed Description                      | 12  |

| Voltage Monitor                           |     |

| Windowed Watchdog and Reset Control       | 12  |

| Watchdog Window Settings                  |     |

| RESET Output                              |     |

| Register Map                              |     |

| Top Level                                 |     |

| Register Details                          |     |

| Applications Information                  | 21  |

| Diagnostics                               | 21  |

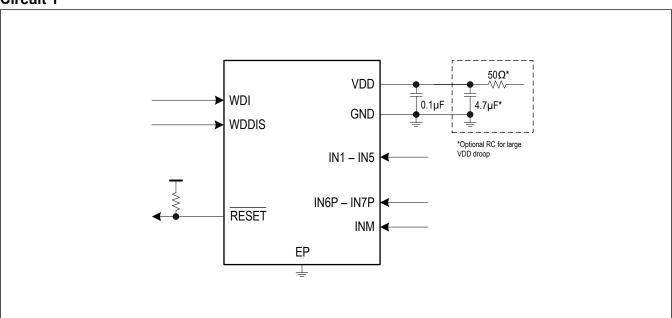

| Typical Application Circuits              | 21  |

| Circuit 1                                 | 21  |

| Ordering Information                      | 22  |

| D. C. | 0.0 |

|          | LIST OF TABLES          |                                          |

|----------|-------------------------|------------------------------------------|

|          |                         | - Ivioritor i arriiry                    |

| MAX20481 | Four- to Seven-Input Au | itomotive Power-System<br>Monitor Family |

# Four- to Seven-Input Automotive Power-System Monitor Family

#### **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND | 0.3V to +6V            | Continuous Power Dissipation ( $T_A = +70$ | D°C)           |

|------------------------|------------------------|--------------------------------------------|----------------|

| IN1-IN5 to GND         | 0.3V to +6V            | 16-TQFN (derate 22.5mW/°C > 70°C)          | 1797.8mW       |

| INP6-INP7 to GND       | 0.3V to +6V            | Operating Temperature                      | 40°C to +125°C |

| INM to GND             |                        | Junction Temperature                       | +150°C         |

| RESET to GND           | 0.3V to +6V            | Storage Temperature Range                  | 65°C to +150°C |

| WDI to GND             | 0.3V to +6V            | Lead Temperature Range                     |                |

| WDDIS to GND           | -0.3\/ to \/DD + 0.3\/ | ,                                          |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### 16-TQFN-EP

| Package Code                           | T1633Y+5         |  |  |  |  |  |  |

|----------------------------------------|------------------|--|--|--|--|--|--|

| Outline Number                         | <u>21-100150</u> |  |  |  |  |  |  |

| Land Pattern Number                    | <u>90-100064</u> |  |  |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |                  |  |  |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> ) | 44.5°C/W         |  |  |  |  |  |  |

| Junction to Case $(\theta_{JC})$       | 5.9°C/W          |  |  |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{DD} = 3.3V, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted, Typical values are at  $T_A = 25^{\circ}C$  under normal conditions, unless otherwise noted. (Note 1)

| PARAMETER                     | SYMBOL            | CONDITIONS                      | MIN  | TYP  | MAX    | UNITS |  |

|-------------------------------|-------------------|---------------------------------|------|------|--------|-------|--|

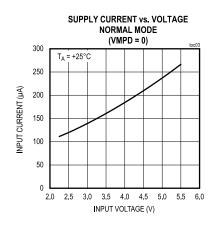

| Supply Voltage Dange          | \/                | Fully operational               | 2.35 |      | 5.5    | V     |  |

| Supply Voltage Range          | V <sub>DD</sub>   | RESET output guaranteed low     | 1.2  |      |        | V     |  |

| UVLO                          | V                 | V <sub>DD</sub> Voltage Rising  | 1.85 | 2.05 | 2.25   | V     |  |

| UVLO                          | V <sub>UVLO</sub> | V <sub>DD</sub> Voltage Falling | 1.75 | 1.95 | 2.15   | V     |  |

| Internal Oscillator           | fosc              |                                 | 1.15 | 1.28 | 1.40   | MHz   |  |

| IN1-IN4                       |                   |                                 |      |      |        |       |  |

| Input Current                 | I <sub>IN</sub> _ | V <sub>IN</sub> _ ≤ 3.3V        |      | 1    | 1.5    | μA    |  |

| Set-Point Range               |                   |                                 | 0.5  |      | 3.6875 | V     |  |

| Set-Point Resolution          |                   | 12.5mV/step                     |      | 8    |        | Bits  |  |

| OV/UV Threshold<br>Range      |                   |                                 | 2.5  |      | 10     | %     |  |

| OV/UV Threshold<br>Resolution |                   | 0.5%/step                       |      | 4    |        | Bits  |  |

# **Electrical Characteristics (continued)**

$(V_{DD} = 3.3V, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted, Typical values are at  $T_A = 25^{\circ}C$  under normal conditions, unless otherwise noted. (Note 1)

| PARAMETER                     | SYMBOL            | CONDITIONS                                              | MIN  | TYP  | MAX   | UNITS |

|-------------------------------|-------------------|---------------------------------------------------------|------|------|-------|-------|

| OV/UV Threshold               |                   | (IN1 through IN4) ≥ 1.0V. Factory-trimmed thresholds.   | -1   |      | 1     | %     |

| Accuracy                      |                   | (IN1 through IN4) < 1.0V. Factory-trimmed thresholds.   | -10  |      | 10    | mV    |

| OFF Threehold                 |                   | (IN1 through IN4) voltage falling                       | 0.23 | 0.25 | 0.27  | V     |

| OFF Threshold                 | V <sub>OFF</sub>  | (IN1 through IN4) voltage rising                        | 0.28 | 0.3  | 0.32  | ]     |

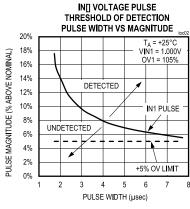

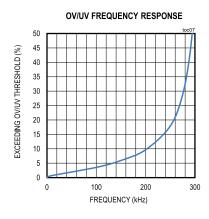

| UV Comparator Filter<br>Time  | t <sub>UV</sub>   | 2% below threshold                                      |      | 5    |       | μs    |

| OV Comparator Filter Time     | t <sub>OV</sub>   | 2% above threshold                                      |      | 5    |       | μs    |

| IN5                           |                   |                                                         |      |      |       |       |

| Input Current                 | I <sub>IN5</sub>  | V <sub>IN5</sub> ≤ 5V                                   |      | 1.5  | 2.3   | μA    |

| Set-Point Range               |                   |                                                         | 0.5  |      | 5.5   | V     |

| Set-Point Resolution          |                   | 20mV/step                                               |      | 8    |       | Bits  |

| OV/UV Threshold<br>Resolution |                   | 0.5%/step                                               |      | 4    |       | Bits  |

| OV/UV Threshold               |                   | IN5 ≥ 1.0V. Factory-trimmed thresholds.                 | -1   |      | 1     | %     |

| Accuracy                      |                   | IN5 < 1.0V. Factory-trimmed thresholds.                 | -10  |      | 10    | mV    |

| OFF Threshold                 | V <sub>OFF</sub>  | IN5 voltage falling                                     | 0.23 | 0.25 | 0.27  | V     |

|                               |                   | IN5 voltage rising                                      | 0.28 |      |       |       |

| UV Comparator Filter<br>Time  | t <sub>UV</sub>   | 2% below threshold                                      |      | 5    |       | μs    |

| OV Comparator Filter<br>Time  | t <sub>OV</sub>   | 2% above threshold                                      |      | 5    |       | μs    |

| OV/UV Threshold<br>Range      |                   |                                                         | 2.5  |      | 10    | %     |

| IN6P-IN7P, INM                | •                 |                                                         |      |      |       |       |

| INM Range                     | V <sub>INM</sub>  |                                                         | -0.1 |      | 0.1   | V     |

| Input Current                 | I <sub>IN</sub> _ | V <sub>IN</sub> _ ≤ 1.8V                                |      | 1.4  | 2.2   | μA    |

| Set-Point Range               |                   | Relative to INM                                         | 0.5  |      | 1.775 | V     |

| Set-Point Resolution          |                   | 5mV/step                                                |      | 8    |       | Bits  |

| Cat Daint Assurance           |                   | (IN6P, IN7P) ≥ 1.0V                                     | -1   |      | 1     | %     |

| Set-Point Accuracy            |                   | (IN6P, IN7P) < 1.0V                                     | -10  |      | 10    | mV    |

| OFF Threshold                 |                   | (IN6P, IN7P) voltage falling, relative to INM 0.23 0.25 |      | 0.27 |       |       |

|                               | V <sub>OFF</sub>  | (IN6P, IN7P) voltage rising, relative to INM            | 0.28 | 0.3  | 0.32  | V     |

| UV Comparator Filter<br>Time  | t <sub>UV</sub>   | 2% below threshold                                      |      | 5    |       | μs    |

| OV Comparator Filter<br>Time  | t <sub>OV</sub>   | 2% above threshold                                      |      | 5    |       | μs    |

## **Electrical Characteristics (continued)**

$(V_{DD} = 3.3V, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted, Typical values are at  $T_A = 25^{\circ}C$  under normal conditions, unless otherwise noted. (Note 1)

| PARAMETER                | SYMBOL              | CONDITIONS                                       | MIN  | TYP | MAX  | UNITS |

|--------------------------|---------------------|--------------------------------------------------|------|-----|------|-------|

| WDI, WDDIS INPUTS        |                     |                                                  |      |     |      |       |

| Input High Level         | V <sub>IH</sub>     | Input Voltage Rising                             | 1.3  |     |      | V     |

| Input Low Level          | V <sub>IL</sub>     | Input Voltage Falling                            |      |     | 0.4  | V     |

| Hysteresis               |                     |                                                  |      | 0.1 |      | V     |

| DIGITAL OUTPUT (RESE     | T)                  |                                                  |      |     |      | •     |

| Digital Output Low Level | V <sub>RL</sub>     | V <sub>DD</sub> = 2.35V, I <sub>SINK</sub> = 2mA |      |     | 0.2  | V     |

| Digital Output Leakage   | I <sub>R-LKG</sub>  | RESET = 5.0V                                     |      |     | 1    | μA    |

|                          |                     | RHLD[1:0] = 00                                   |      | 6   |      | μs    |

| Active Timeout Period    | d t <sub>HOLD</sub> | RHLD[1:0] = 01                                   | 7.2  | 8   | 8.8  |       |

|                          |                     | RHLD[1:0] = 10                                   | 14.4 | 16  | 17.6 | ms    |

|                          |                     | RHLD[1:0] = 11                                   | 28.8 | 32  | 35.2 |       |

Note 1: Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

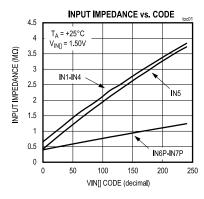

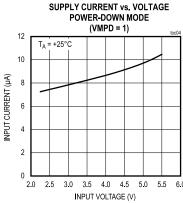

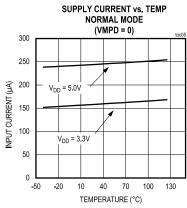

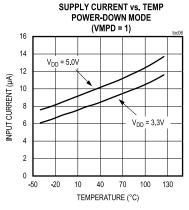

## **Typical Operating Characteristics**

$(V_{DD} = 3.3V, T_A = +25^{\circ}C)$

# **Pin Configurations**

#### MAX20481A: 4-Channel Monitor

#### MAX20481B: 5-Channel Monitor

#### MAX20481C: 6-Channel Monitor

#### MAX20481D: 7-Channel Monitor

## **Pin Description**

|           | •         |           |           |        |                                                 |

|-----------|-----------|-----------|-----------|--------|-------------------------------------------------|

|           | Р         | IN        |           | NAME   | FUNCTION                                        |

| MAX20481A | MAX20481B | MAX20481C | MAX20481D | NAIVIE | FUNCTION                                        |

| MAX20481  |           |           |           |        |                                                 |

| 1         | 1         | 1         | 1         | IN1    | Input Voltage Monitor 1                         |

| 2         | 2         | 2         | 2         | IN2    | Input Voltage Monitor 2                         |

| 3         | 3         | 3         | 3         | IN3    | Input Voltage Monitor 3                         |

| 4         | 4         | 4         | 4         | IN4    | Input Voltage Monitor 4                         |

| 5, 6, 7   | 5, 6, 7   | 5, 6, 7   | 5, 6, 7   | GND    | Ground. Connect all grounds together at the EP. |

# **Pin Description (continued)**

|           | PIN       |           |           |       | FUNCTION                                                                                                                                                                                                                   |

|-----------|-----------|-----------|-----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX20481A | MAX20481B | MAX20481C | MAX20481D | NAME  | FUNCTION                                                                                                                                                                                                                   |

| 8         | 8         | 8         | 8         | VDD   | Input Supply Voltage. Connect a 0.1µF capacitor between V <sub>DD</sub> and GND and place close to the IC.                                                                                                                 |

| 9         | -         | -         | -         | GND   | Ground. Connect all grounds together at the EP.                                                                                                                                                                            |

| -         | 9         | 9         | 9         | IN5   | Input Voltage Monitor 5                                                                                                                                                                                                    |

| 10        | 10        | -         | -         | GND   | Ground. Connect all grounds together at the EP.                                                                                                                                                                            |

| _         | _         | 10        | 10        | IN6P  | Differential Input Voltage Monitor 6                                                                                                                                                                                       |

| 11        | 11        | _         | _         | GND   | Ground. Connect all grounds together at the EP.                                                                                                                                                                            |

| _         | _         | 11        | 11        | INM   | Common Negative Input for Voltage Monitors 6 and 7.                                                                                                                                                                        |

| 12        | 12        | 12        | -         | GND   | Ground. Connect all grounds together at the EP.                                                                                                                                                                            |

| _         | _         | -         | 12        | IN7P  | Differential Input Voltage Monitor 7                                                                                                                                                                                       |

| 13        | 13        | 13        | 13        | RESET | RESET Output. Open-drain output that signals a status change. Can be mapped to any combination of input monitors to indicate that they are within nominal operating range. Connect to logic supply with a pullup resistor. |

| 14        | 14        | 14        | 14        | WDDIS | Watchdog Disable. Connect to GND to enable windowed watchdog. Connect to V <sub>DD</sub> to disable watchdog.                                                                                                              |

| 15        | 15        | 15        | 15        | GND   | Ground. Connect all grounds together at the EP.                                                                                                                                                                            |

| 16        | 16        | 16        | 16        | WDI   | Watchdog Input. A low-to-high transition will refresh the watchdog. This pin is only available on the MAX20481 version.                                                                                                    |

| -         | -         | -         | -         | EP    | Exposed Pad. Connect to ground. Does not serve as a substitute for a proper GND pin connection.                                                                                                                            |

# **Functional Diagrams**

#### **Detailed Description**

The MAX20481 is an ASIL B-compliant SoC power-system monitor. It has up to 7 channels voltage monitors to supervise system power rails, and a windowed watchdog for SoC/MCU monitoring. The system features numerous checks and redundancies to maintain a high performance level and meet ASIL B reliability specifications.

#### **Voltage Monitor**

The MAX20481 IC has up to seven voltage-monitor channels available for system power rails. Five of the monitors have single-ended inputs. For these channels, a nominal voltage is set first and OV/UV thresholds (as a percentage of that nominal voltage setting) are set second. The remaining two monitors have differential inputs and share a remote ground-sense pin (INM). Unlike the other monitors, which have a nominal voltage + %OV/UV configuration, the two differential inputs have completely independent OV and UV comparators. Each comparator can be configured with a separate reference voltage.

Monitor channels IN1 through IN5 have the single-ended configuration, with OV/UV thresholds independently configurable from  $\pm 2.5\%$  to  $\pm 10\%$  in 0.5% steps. IN1 through IN4 have a nominal voltage set-point range of 0.50V to 3.6875V, while IN5 has an extended range of 0.50V to 5.50V. IN6P and IN7P have the differential configuration. Their OV and UV set points can range from 0.50V to 1.775V; these measurements are with respect to the voltage difference between the INxP supply and INM remote ground-sense pins. Every monitor channel also has an OFF comparator that asserts when the monitor input voltage falls below 0.25V (typ).

Modern SoCs and processors can require a large amount of supply current, which may cause small offsets in ground voltages (even when using multiple large ground planes). To account for this when using the differential channels, route the INM pin separately from ground and connect to a point near where the IN6P and IN7P lines are connected. If this feature is not necessary, the INM pin can be grounded directly at the IC. The comparators on the voltage monitors are designed to respond quickly for applications that require rapid response to voltage fluctuations. If a slower response is desired, an RC filter can be added between the IC pin and the monitored voltage rail. If an RC filter is implemented, the value of the resistor should be kept low to avoid artificial voltage shift at the IC pins. Because each IN\_ pin draws a few microamperes of current, the filter resistor value should be  $1k\Omega$  or less.

#### **Windowed Watchdog and Reset Control**

The IC also contains a windowed watchdog for external SoC monitoring. The closed and open windows are independently configurable, as well as the main watchdog clock (which can range from 200µs/tick to 12.8ms/tick). Because the watchdog is meant to supervise a processor system, it features an extended first-update window: when the IC RESET pin deasserts, the watchdog window is immediately opened and extended to provide extra time for an SoC to finish any boot sequences before being required to update the watchdog. (The specific length of the extended first-update window is configurable as well.) The watchdog is refreshed through a dedicated pin on the IC (the WDI pin). A low-to-high transition triggers a refresh of the watchdog. For system programming at the factory, there is also an active-high watchdog disable pin (WDDIS). Pulling the pin high disables the watchdog functionality while leaving the voltage monitors fully active. The watchdog will trigger an error signal on both too-early or too-late update faults. It can be configured to assert RESET on every update violation, or only after encountering two consecutive violations. The watchdog is inactive while the RESET pin is asserted low (for any fault condition).

#### **Watchdog Window Settings**

A regular watchdog window consists of two parts: an initial (closed) window during which updates are not allowed, and a second (open) window during which updates are accepted. For a given watchdog clock rate two clock (set according to the WDCDIV register), the two window lengths are as follows:

$t_{\text{CLO}} = t_{\text{WDCLK}} \times 8 \times \text{WDCFG1.CLO}[3:0]$  $t_{\text{OPN}} = t_{\text{WDCLK}} \times 8 \times \text{WDCFG1.OPN}[3:0]$

If a refresh is sent to the IC during the closed window, the IC asserts a fault and restarts the watchdog once RESET deasserts. When the IC receives a valid refresh, it will immediately transition to a new closed window. It will not finish the existing open window. The first cycle encountered once the watchdog starts (either on power-on reset or once RESET deasserts) is different from the typical closed/open cycle. It has no closed window, and is longer than a normal cycle.

#### MAX20481

# Four- to Seven-Input Automotive Power-System Monitor Family

This is to allow for an SoC or MCU to run through a boot sequence that may take longer than the usual watchdog cycle. The length of the first update window is an odd multiple of the sum of the normal closed and open windows:  $t_{1UD} = (t_{OPN} + t_{CLO}) \times (1 + 2 \times WDCFG2.1UD[2 : 0])$

#### **RESET** Output

The device features an open-drain interrupt/reset output that asserts low when any mapped fault conditions occur. RESET remains asserted for a fixed timeout period after all triggering fault conditions are removed. The fixed timeout period can be set to 6μs, 8ms, 16ms, or 32ms. The RESET pin works as an open-drain output. To obtain a logic signal, place a pullup resistor between the RESET pin and system I/O voltage (10kΩ to 100kΩ recommended for reduced current consumption). Mapping of this pin to selected fault sources is fully programmable.

# **Register Map**

#### Top Level

| ADDRESS               | NAME              | MSB  |                   |       |     |      |          |       | LSB    |

|-----------------------|-------------------|------|-------------------|-------|-----|------|----------|-------|--------|

| General Configuration |                   |      |                   |       |     |      |          |       |        |

| 0x01                  | CONFIG1[7:0]      | _    | -                 | -     | _   | _    | _        | MBST  | _      |

| Voltage Mo            | nitor System      | ·    |                   |       |     |      |          |       |        |

| 0x04                  | RSTMAP[7:0]       | PARM | IN7               | IN6   | IN5 | IN4  | IN3      | IN2   | IN1    |

| 0x08                  | <u>VIN1[7:0]</u>  |      |                   |       | D[7 | 7:0] |          |       |        |

| 0x09                  | <u>VIN2[7:0]</u>  |      |                   |       | D[7 | 7:0] |          |       |        |

| 0x0A                  | <u>VIN3[7:0]</u>  |      |                   |       | D[7 | 7:0] |          |       |        |

| 0x0B                  | <u>VIN4[7:0]</u>  |      |                   |       | D[7 | 7:0] |          |       |        |

| 0x0C                  | <u>VIN5[7:0]</u>  |      |                   |       | D[7 | 7:0] |          |       |        |

| 0x0D                  | <u>VINO6[7:0]</u> |      |                   |       | D[7 | 7:0] |          |       |        |

| 0x0E                  | <u>VINU6[7:0]</u> |      | D[7:0]            |       |     |      |          |       |        |

| 0x0F                  | <u>VINO7[7:0]</u> |      |                   |       | D[7 | 7:0] |          |       |        |

| 0x10                  | <u>VINU7[7:0]</u> |      |                   |       | D[7 | 7:0] |          |       |        |

| 0x11                  | OVUV1[7:0]        |      | OV                | [3:0] |     |      | UV       | [3:0] |        |

| 0x12                  | OVUV2[7:0]        |      | OV                | [3:0] |     |      | UV       | [3:0] |        |

| 0x13                  | OVUV3[7:0]        |      | OV                | [3:0] |     |      | UV       | [3:0] |        |

| 0x14                  | <u>OVUV4[7:0]</u> |      | OV[3:0] UV[3:0]   |       |     |      |          |       |        |

| 0x15                  | <u>OVUV5[7:0]</u> |      | OV[3:0] UV[3:0]   |       |     |      |          |       |        |

| Watchdog a            | and RESET Control |      |                   |       |     |      |          |       |        |

| 0x27                  | WDCDIV[7:0]       | _    | -                 |       |     | WDI  | V[5:0]   |       |        |

| 0x28                  | WDCFG1[7:0]       |      | CLO[3:0] OPN[3:0] |       |     |      | N[3:0]   |       |        |

| 0x29                  | WDCFG2[7:0]       | _    | _                 |       |     |      | 1UD[2:0] |       |        |

| 0x2C                  | RSTCTRL[7:0]      | _    | _                 | _     | _   | _    | MR1      | RHLI  | D[1:0] |

# **Register Details**

#### CONFIG1 (0x01)

Configuration Register 1

| oormigaration register r |   |   |   |   |   |   |             |   |

|--------------------------|---|---|---|---|---|---|-------------|---|

| BIT                      | 7 | 6 | 5 | 4 | 3 | 2 | 1           | 0 |

| Field                    | _ | _ | _ | _ | _ | - | MBST        | - |

| Reset                    | _ | _ | _ | _ | _ | _ | OTP         | _ |

| Access<br>Type           | _ | _ | _ | _ | _ | _ | Write, Read | _ |

| BITFIELD | BITS | DESCRIPTION                                                                                                   | DECODE                                                                                                          |

|----------|------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| MBST     | 1    | Built-In Self-Test Mapping. When set, any comparator that fails BIST will cause the RESET pin to be asserted. | 0: BIST for OV/UV/OFF comparators not mapped to RESET pin 1: BIST for OV/UV/OFF comparators mapped to RESET pin |

#### RSTMAP (0x4)

Interrupt Mapping

| BIT            | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|----------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Field          | PARM        | IN7         | IN6         | IN5         | IN4         | IN3         | IN2         | IN1         |

| Reset          | OTP         |

| Access<br>Type | Write, Read |

| BITFIELD | BITS | DESCRIPTION                                                                                    | DECODE                                                                                                          |

|----------|------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| PARM     | 7    | Parity RESET Mapping. Defines whether or not a parity check failure will assert the RESET pin. | 0: Parity faults are not mapped to the RESET pin.  1: Any parity fault will cause the RESET pin to be asserted. |

| IN7      | 6    | RESET Mapping. Defines whether or not OV/UV assertions will cause the RESET pin to trigger.    | 0: OV/UV faults are not mapped to the RESET pin.  1: OV/UV faults are mapped to the RESET pin.                  |

| IN6      | 5    | RESET Mapping. Defines whether or not OV/UV assertions will cause the RESET pin to trigger.    | 0: OV/UV faults are not mapped to the RESET pin.  1: OV/UV faults are mapped to the RESET pin.                  |

| IN5      | 4    | RESET Mapping. Defines whether or not OV/UV assertions will cause the RESET pin to trigger.    | 0: OV/UV faults are not mapped to the RESET pin.  1: OV/UV faults are mapped to the RESET pin.                  |

| IN4      | 3    | RESET Mapping. Defines whether or not OV/UV assertions will cause the RESET pin to trigger.    | 0: OV/UV faults are not mapped to the RESET pin. 1: OV/UV faults are mapped to the RESET pin.                   |

| IN3      | 2    | RESET Mapping. Defines whether or not OV/UV assertions will cause the RESET pin to trigger.    | 0: OV/UV faults are not mapped to the RESET pin.  1: OV/UV faults are mapped to the RESET pin.                  |

| IN2      | 1    | RESET Mapping. Defines whether or not OV/UV assertions will cause the RESET pin to trigger.    | 0: OV/UV faults are not mapped to the RESET pin.  1: OV/UV faults are mapped to the RESET pin.                  |

| IN1      | 0    | RESET Mapping. Defines whether or not OV/UV assertions will cause the RESET pin to trigger.    | 0: OV/UV faults are not mapped to the RESET pin.  1: OV/UV faults are mapped to the RESET pin.                  |

#### VIN1 (0x8)

IN1 Nominal Voltage Set Point

| BIT            | 7           | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |

|----------------|-------------|-----------------|--|--|--|--|--|--|--|

| Field          |             | D[7:0]          |  |  |  |  |  |  |  |

| Reset          | OTP         |                 |  |  |  |  |  |  |  |

| Access<br>Type | Write, Read |                 |  |  |  |  |  |  |  |

| BITFIELD | BITS | DESCRIPTION          | DECODE                                                       |

|----------|------|----------------------|--------------------------------------------------------------|

| D        | 7:0  | Nominal Rail Voltage | V <sub>NOM</sub> = 500mV + 12.5mV x D[7:0] (0.5V to 3.6875V) |

#### VIN2 (0x9)

IN2 Nominal Voltage Set Point

| BIT            | 7           | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|-------------|--------|---|---|---|---|---|---|

| Field          |             | D[7:0] |   |   |   |   |   |   |

| Reset          |             | OTP    |   |   |   |   |   |   |

| Access<br>Type | Write, Read |        |   |   |   |   |   |   |

| BITFIELD | BITS | DESCRIPTION          | DECODE                                                       |

|----------|------|----------------------|--------------------------------------------------------------|

| D        | 7:0  | Nominal Rail Voltage | V <sub>NOM</sub> = 500mV + 12.5mV x D[7:0] (0.5V to 3.6875V) |

#### **VIN3 (0xA)**

IN3 Nominal Voltage Set Point

| II TO I TOITIII TOI | Voltage Set Form |        |   |   |   |   |   |   |

|---------------------|------------------|--------|---|---|---|---|---|---|

| BIT                 | 7                | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

| Field               |                  | D[7:0] |   |   |   |   |   |   |

| Reset               | OTP              |        |   |   |   |   |   |   |

| Access<br>Type      | Write, Read      |        |   |   |   |   |   |   |

| BITFIELD | BITS | DESCRIPTION          | DECODE                                                       |

|----------|------|----------------------|--------------------------------------------------------------|

| D        | 7:0  | Nominal Rail Voltage | V <sub>NOM</sub> = 500mV + 12.5mV x D[7:0] (0.5V to 3.6875V) |

#### **VIN4 (0xB)**

IN4 Nominal Voltage Set Point

| BIT            | 7           | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |

|----------------|-------------|-----------------|--|--|--|--|--|--|--|

| Field          |             | D[7:0]          |  |  |  |  |  |  |  |

| Reset          |             | OTP             |  |  |  |  |  |  |  |

| Access<br>Type | Write, Read |                 |  |  |  |  |  |  |  |

| BITFIELD | BITS | DESCRIPTION          | DECODE                                                       |

|----------|------|----------------------|--------------------------------------------------------------|

| D        | 7:0  | Nominal Rail Voltage | V <sub>NOM</sub> = 500mV + 12.5mV x D[7:0] (0.5V to 3.6875V) |

#### **VIN5 (0xC)**

IN5 Nominal Voltage Set Point

| BIT            | 7           | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |

|----------------|-------------|-----------------|--|--|--|--|--|--|--|

| Field          |             | D[7:0]          |  |  |  |  |  |  |  |

| Reset          | OTP         |                 |  |  |  |  |  |  |  |

| Access<br>Type | Write, Read |                 |  |  |  |  |  |  |  |

| BITFIELD | BITS | DESCRIPTION          | DECODE                                                  |

|----------|------|----------------------|---------------------------------------------------------|

| D        | 7:0  | Nominal Rail Voltage | V <sub>NOM</sub> = 500mV + 20mV x D[7:0] (0.5V to 5.6V) |

#### VINO6 (0xD)

IN6 Overvoltage Threshold Set Point

# Four- to Seven-Input Automotive Power-System Monitor Family

| BIT            | 7           | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----------------|-------------|--------|---|---|---|---|---|---|--|

| Field          |             | D[7:0] |   |   |   |   |   |   |  |

| Reset          |             | OTP    |   |   |   |   |   |   |  |

| Access<br>Type | Write, Read |        |   |   |   |   |   |   |  |

| BITFIELD | BITS | DESCRIPTION  | DECODE                                                                                  |

|----------|------|--------------|-----------------------------------------------------------------------------------------|

| D        | 7:0  | OV Threshold | $V_{OV6} = 500 \text{mV} + 5 \text{mV} \times D[7:0] (0.5 \text{V to } 1.775 \text{V})$ |

## VINU6 (0xE)

IN6 Undervoltage Threshold Set Point

| BIT            | 7 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |

|----------------|---|-----------------|--|--|--|--|--|--|

| Field          |   | D[7:0]          |  |  |  |  |  |  |

| Reset          |   | OTP             |  |  |  |  |  |  |

| Access<br>Type |   | Write, Read     |  |  |  |  |  |  |

| BITFIELD | BITS | DESCRIPTION  | DECODE                                                   |

|----------|------|--------------|----------------------------------------------------------|

| D        | 7:0  | UV Threshold | V <sub>UV6</sub> = 500mV + 5mV x D[7:0] (0.5V to 1.775V) |

#### VINO7 (0xF)

IN7 Overvoltage Threshold Set Point

| BIT            | 7 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |

|----------------|---|-----------------|--|--|--|--|--|--|

| Field          |   | D[7:0]          |  |  |  |  |  |  |

| Reset          |   | ОТР             |  |  |  |  |  |  |

| Access<br>Type |   | Write, Read     |  |  |  |  |  |  |

| BITFIELD | BITS | DESCRIPTION  | DECODE                                                                                  |

|----------|------|--------------|-----------------------------------------------------------------------------------------|

| D        | 7:0  | OV Threshold | $V_{OV7} = 500 \text{mV} + 5 \text{mV} \times D[7:0] (0.5 \text{V to } 1.775 \text{V})$ |

#### **VINU7 (0x10)**

IN7 Undervoltage Threshold Set Point

| BIT            | 7           | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |

|----------------|-------------|-----------------|--|--|--|--|--|--|

| Field          |             | D[7:0]          |  |  |  |  |  |  |

| Reset          |             | OTP             |  |  |  |  |  |  |

| Access<br>Type | Write, Read |                 |  |  |  |  |  |  |

| BITFIELD | BITS | DESCRIPTION  | DECODE                                                                                  |

|----------|------|--------------|-----------------------------------------------------------------------------------------|

| D        | 7:0  | UV Threshold | $V_{UV7} = 500 \text{mV} + 5 \text{mV} \times D[7:0] (0.5 \text{V to } 1.775 \text{V})$ |

#### **OVUV1 (0x11)**

IN1 Overvoltage and Undervoltage Thresholds

| BIT            | 7 | 6      | 5    | 4 | 3       | 2      | 1    | 0 |  |

|----------------|---|--------|------|---|---------|--------|------|---|--|

| Field          |   | OV[    | 3:0] |   | UV[3:0] |        |      |   |  |

| Reset          |   | 0      | ГР   |   | OTP     |        |      |   |  |

| Access<br>Type |   | Write, | Read |   |         | Write, | Read |   |  |

| BITFIELD | BITS | DESCRIPTION                | DECODE                           |

|----------|------|----------------------------|----------------------------------|

| OV       | 7:4  | IN1 Overvoltage Threshold  | OV (%) = 102.5% + 0.5% x OV[3:0] |

| UV       | 3:0  | IN1 Undervoltage Threshold | UV (%) = 97.5% - 0.5% x UV[3:0]  |

#### **OVUV2 (0x12)**

IN2 Overvoltage and Undervoltage Thresholds

|                | o and one of the government of |        |       |   |         |        |      |   |  |

|----------------|--------------------------------|--------|-------|---|---------|--------|------|---|--|

| BIT            | 7                              | 6      | 5     | 4 | 3       | 2      | 1    | 0 |  |

| Field          |                                | OV     | [3:0] |   | UV[3:0] |        |      |   |  |

| Reset          |                                | 0      | TP    |   | OTP     |        |      |   |  |

| Access<br>Type |                                | Write, | Read  |   |         | Write, | Read |   |  |

| BITFIELD | BITS | DESCRIPTION                | DECODE                           |  |  |

|----------|------|----------------------------|----------------------------------|--|--|

| OV       | 7:4  | IN2 Overvoltage Threshold  | OV (%) = 102.5% + 0.5% x OV[3:0] |  |  |

| UV       | 3:0  | IN2 Undervoltage Threshold | UV (%) = 97.5% - 0.5% x UV[3:0]  |  |  |

#### OVUV3 (0x13)

IN3 Overvoltage and Undervoltage Thresholds

| BIT            | 7 | 6      | 5     | 4 | 3 2 1 0 |        |      |  |

|----------------|---|--------|-------|---|---------|--------|------|--|

| Field          |   | OV     | [3:0] |   | UV[3:0] |        |      |  |

| Reset          |   | 0      | TP    |   | OTP     |        |      |  |

| Access<br>Type |   | Write, | Read  |   |         | Write, | Read |  |

|                |   |        |       |   |         |        |      |  |

| BITFIELD | BITS | DESCRIPTION                | DECODE                           |

|----------|------|----------------------------|----------------------------------|

| OV       | 7:4  | IN3 Overvoltage Threshold  | OV (%) = 102.5% + 0.5% x OV[3:0] |

| UV       | 3:0  | IN3 Undervoltage Threshold | UV (%) = 97.5% - 0.5% x UV[3:0]  |

#### OVUV4 (0x14)

IN4 Overvoltage and Undervoltage Thresholds

| IIII OVOIVOILA | 90 0 0 |       |        |   |         |       |        |   |  |

|----------------|--------|-------|--------|---|---------|-------|--------|---|--|

| BIT            | 7      | 6     | 5      | 4 | 3       | 2     | 1      | 0 |  |

| Field          |        | OV    | [3:0]  |   | UV[3:0] |       |        |   |  |

| Reset          |        | 0     | TP     |   | OTP     |       |        |   |  |

| Access<br>Type |        | Write | , Read |   |         | Write | , Read |   |  |

| BITFIELD | BITS | DESCRIPTION                | DECODE                           |  |  |

|----------|------|----------------------------|----------------------------------|--|--|

| OV       | 7:4  | IN4 Overvoltage Threshold  | OV (%) = 102.5% + 0.5% x OV[3:0] |  |  |

| UV       | 3:0  | IN4 Undervoltage Threshold | UV (%) = 97.5% - 0.5% x UV[3:0]  |  |  |

#### **OVUV5 (0x15)**

IN5 Overvoltage and Undervoltage Thresholds

| BIT            | 7 | 6      | 5    | 4 | 3       | 2      | 1    | 0 |  |

|----------------|---|--------|------|---|---------|--------|------|---|--|

| Field          |   | OV     | 3:0] |   | UV[3:0] |        |      |   |  |

| Reset          |   | 0      | ГР   |   | OTP     |        |      |   |  |

| Access<br>Type |   | Write, | Read |   |         | Write, | Read |   |  |

| BITFIELD | BITS | DESCRIPTION                | DECODE                           |  |  |

|----------|------|----------------------------|----------------------------------|--|--|

| OV       | 7:4  | IN5 Overvoltage Threshold  | OV (%) = 102.5% + 0.5% x OV[3:0] |  |  |

| UV       | 3:0  | IN5 Undervoltage Threshold | UV (%) = 97.5% - 0.5% x UV[3:0]  |  |  |

#### WDCDIV (0x27)

Watchdog Mode and Clock Divider

| BIT            | 7 | 6 | 5         | 4 | 3      | 2    | 1 | 0 |

|----------------|---|---|-----------|---|--------|------|---|---|

| Field          | _ | _ | WDIV[5:0] |   |        |      |   |   |

| Reset          | _ | _ | OTP       |   |        |      |   |   |

| Access<br>Type | _ | _ |           |   | Write, | Read |   |   |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                             | DECODE                                          |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| WDIV     | 5:0  | Watchdog Clock Divider. The main oscillator is divided by 32 and supplied to the watchdog subsystem. This field controls further dividing of the clock. | t <sub>WDCLK</sub> = (WDIV[5:0] + 1) x 25μs x 8 |

#### **WDCFG1 (0x28)**

Watchdog Configuration Register 1

|                |   | 9.0.0  |       |   |          |        |      |   |  |

|----------------|---|--------|-------|---|----------|--------|------|---|--|

| BIT            | 7 | 6      | 5     | 4 | 3        | 2      | 1    | 0 |  |

| Field          |   | CLC    | [3:0] |   | OPN[3:0] |        |      |   |  |

| Reset          |   | 0      | TP    |   | OTP      |        |      |   |  |

| Access<br>Type |   | Write, | Read  |   |          | Write, | Read |   |  |

| BITFIELD | BITS | DESCRIPTION                                                                                                    | DECODE                                                     |  |  |

|----------|------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|

| CLO      | 7:4  | Watchdog Closed Window. Sets the length of the first portion of a watchdog period, where updates are rejected. | t <sub>CLO</sub> = (CLO[3:0] + 1) x 8 x t <sub>WDCLK</sub> |  |  |

| OPN      | 3:0  | Watchdog Open Window. Sets the length of the second portion of a watchdog period, where updates are accepted.  | t <sub>OPN</sub> = (OPN[3:0] + 1) x 8 x t <sub>WDCLK</sub> |  |  |

#### **WDCFG2 (0x29)**

Watchdog Configuration Register 2

# Four- to Seven-Input Automotive Power-System Monitor Family

| BIT            | 7 | 6 | 5 | 4 | 3         | 2           | 1 | 0 |

|----------------|---|---|---|---|-----------|-------------|---|---|

| Field          | _ | _ | _ | _ | WDEN      | 1UD[2:0]    |   |   |

| Reset          | _ | _ | _ | _ | OTP       | OTP         |   |   |

| Access<br>Type | _ | _ | _ | _ | Read Only | Write, Read |   |   |

| BITFIELD | BITS | DESCRIPTION                                                                               | DECODE                                                                          |

|----------|------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| WDEN     | 3    |                                                                                           |                                                                                 |

| 1UD      | 2:0  | First Update Extension. Sets the length of the first open window after RESET deassertion. | t <sub>1OPN</sub> = (t <sub>CLO</sub> + t <sub>OPN</sub> ) x (1UD[2:0] x 2 + 1) |

#### RSTCTRL (0x2C)

#### RESET Control

| TEOL! CONTO    |   |   |   |   |   |             |             |   |

|----------------|---|---|---|---|---|-------------|-------------|---|

| BIT            | 7 | 6 | 5 | 4 | 3 | 2           | 1           | 0 |

| Field          | _ | _ | _ | _ | _ | MR1         | RHLD[1:0]   |   |

| Reset          | _ | _ | _ | _ | - | OTP         | OTP         |   |

| Access<br>Type | _ | _ | _ | _ | _ | Write, Read | Write, Read |   |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                            | DECODE                                                                                                                                                                                             |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MR1      | 2    | Watchdog Violation Count for RESET Assertion. This determines whether the RESET pin is asserted on any single watchdog violation, or after two consecutive violations. | RESET will assert after any watchdog violation.     RESET will assert only after two consecutive violations. Valid updates will reset the violation counter if one violation has been encountered. |

| RHLD     | 1:0  | RESET Hold/Active Timeout Time. This is the amount of time that the RESET pin remains low after the removal of any event that would cause the RESET pin to assert low. | 00: 0ms (6µs typ, used for interrupt-style functionality) 01: 8ms 10: 16ms 11: 32ms                                                                                                                |

## **Applications Information**

#### **Diagnostics**

The MAX20481 is ASIL B-compliant in a standalone monitor role. In addition to out-of-bounds voltage rails and watchdog faults, the IC can also use the RESET pin to communicate various internal faults, including register parity-check failures, oscillator faults, and comparator BIST results. Internal OTP configuration information is protected by an automatic single-error-correcting coding scheme. For full safety-related information, contact Maxim Integrated.

## **Table 1. Diagnostics**

| 140.0 11 2.49.1004.00                      |                                                                                                                                            |  |  |  |  |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| FAULT                                      | DIAGNOSTIC COVERAGE                                                                                                                        |  |  |  |  |  |

| Short to GND/V <sub>DD</sub> on IN[x] pins | OV/UV comparators assert depending on voltage                                                                                              |  |  |  |  |  |

| Open on IN[x] pins                         | UV/OFF comparators assert                                                                                                                  |  |  |  |  |  |

| IN[x] comparator fault                     | Built-in self-test operates at power-on and can communicate faults through RESET pin                                                       |  |  |  |  |  |

| Short to GND on V <sub>DD</sub> pin        | RESET is pulled low (if connected to same supply as IC)                                                                                    |  |  |  |  |  |

| Open on V <sub>DD</sub> pin                | Can be detected through host-induced test                                                                                                  |  |  |  |  |  |

| Open GND pin                               | RESET can still assert down to one body diode above system ground. Persistent UV conditions will occur if monitored rails are operational. |  |  |  |  |  |

| Short to V <sub>DD</sub> on RESET          | Can be detected through host-induced test                                                                                                  |  |  |  |  |  |

| Open on RESET pin                          | Can be detected through host-induced test                                                                                                  |  |  |  |  |  |

| Internal watchdog block failure            | Can be detected through host-induced test                                                                                                  |  |  |  |  |  |

# **Typical Application Circuits**

#### Circuit 1

# Four- to Seven-Input Automotive Power-System Monitor Family

# **Ordering Information**

| PART               | Ch1<br>(V) | Ch2<br>(V) | Ch3<br>(V) | Ch4<br>(V) | CH5<br>(V) | Ch6 OV<br>(V) | Ch6 UV<br>(V) | Ch7 OV<br>(V) | Ch7 UV<br>(V) |

|--------------------|------------|------------|------------|------------|------------|---------------|---------------|---------------|---------------|

| MAX20481AATEB/VY+* | 1.8000     | 2.8000     | 0.5000     | 0.5000     | _          | _             | _             |               |               |

| MAX20481AATEC/VY+  | 3.3000     | 1.8000     | 1.1500     | 0.5000     | _          | _             | _             | _             | _             |

| MAX20481BATEA/VY+  | 1.0250     | 1.8000     | 1.3500     | 3.3000     | 1.2000     | _             | _             |               |               |

| MAX20481CATEA/VY+  | 3.300      | 1.8000     | 2.5000     | 0.5000     | 1.1000     | 1.0050        | 0.8350        | _             | _             |

Y denotes a side-wettable package.

For variants with different options, contact the factory.

Devices are also available in tape-and-reel packaging. Specify tape and reel by adding "T" to the part number when ordering.

<sup>/</sup>V+ denotes an automotive-qualified part.

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

<sup>\*</sup>Future product—contact factory for availability.

# Four- to Seven-Input Automotive Power-System Monitor Family

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                                                     | PAGES<br>CHANGED |

|--------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 8/19          | Initial release                                                                                                                 | _                |

| 1                  | 8/19          | Added <u>Typical Operating Characteristics</u>                                                                                  | 7                |

| 2                  | 1/20          | Updated <u>General Description</u> , <u>Benefits and Features</u> , <u>Pin Configurations</u> , and <u>Detailed Description</u> | 1, 8, 9, 13      |

| 3                  | 9/20          | Updated Electrical Characteristics and Functional Diagrams                                                                      | 6, 11            |

| 4                  | 5/21          | Updated <u>Package Information</u>                                                                                              | 3                |

| 5                  | 6/21          | Updated <u>Ordering Information</u> table                                                                                       | 13               |

| 6                  | 12/21         | Added Register Map, <u>ASIL Diagnostics</u> section, and MAX20481BATEA/VY+ to <u>Ordering Information</u> table                 | 14–20, 21,<br>22 |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Analog Devices Inc.:

MAX20481BATEA/VY+ MAX20481CATEA/VY+ MAX20481AATEC/VY+ MAX20481BATEA/VY+T MAX20481CATEA/VY+T