# 0.7% Accuracy, Single Window Voltage Monitor with BIST

**MAX16138**

#### **General Description**

The MAX16138 is a low-voltage, ±0.7% accurate supervisory circuit that monitors a single system supply voltage for undervoltage and overvoltage faults within a factory set threshold window. When the monitored supply voltage drops below the undervoltage threshold or goes above the overvoltage threshold, the reset output asserts low. The reset output deasserts after the reset timeout period when the supply voltage returns within the undervoltage and overvoltage threshold window.

The reset output is active low available in either the push-pull or open-drain options. The MAX16138 offers factory-trimmed nominal input voltage options from 0.51V to 5.01V in approximately 20mV increment. A variety of factory-trimmed undervoltage/overvoltage thresholds from  $\pm 2\%$  to  $\pm 9\%$  are available to accommodate different supply voltages and tolerances.

The MAX16138 features a unique Built-In-Self-Test (BIST) diagnostic capability that monitors the health of the internal reset circuit during power-up. If the built-in-self-test fails, the MAX16138 asserts BIST low. During normal operation, the MAX16138 performs an on-demand BIST when the CLR/BIST is pulled low for more than 150µs. See the <u>Built-In Self-Test</u> section for more details.

The MAX16138 is available in a small, 2mm x 2mm, 8-pin TDFN side-wettable package and operates over the automotive temperature range of -40°C to +125°C.

## **Applications**

- Advanced Driver-Assistance Systems (ADAS)

- Multivoltage ASICs

- Servers

- Storage Equipment

#### **Benefits and Features**

- ±0.7% Allow Precision Supply Monitoring

- BIST Enhances System Safety

- Enables ASIL Compliance at System Level

- Factory-Set Threshold 0.51V to 5.01V with 20mV Increment

- Factory-Set Input Tolerance ±2% to ±9% UV/OV Threshold Window

- · Factory-Set Reset Timeout

- · Latched Overvoltage Fault Output

- 5µs Overvoltage Fault Response

- Open-Drain/Push-Pull Reset Output

- 2mm x 2mm TDFN-8 Side-Wettable Package

- -40°C to +125°C Temperature Range

- AEC-Q100 Qualified

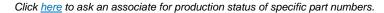

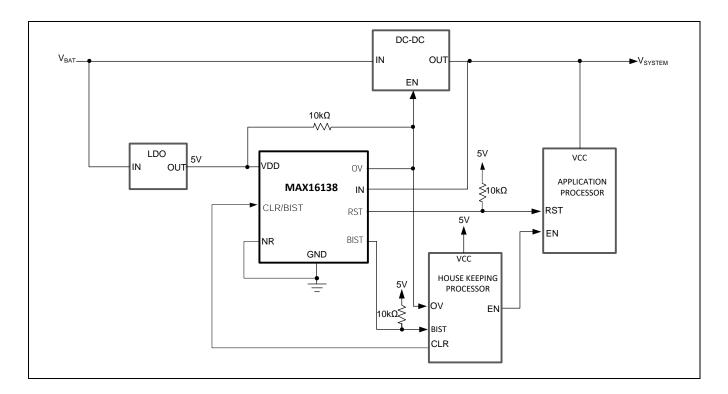

### **Typical Application Circuit**

Ordering Information appears at end of data sheet.

# 0.7% Accuracy, Single Window Voltage Monitor with BIST

# **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND0.3V to 6V                                                                | Operating Temperature Range40°C to +125°C |

|-------------------------------------------------------------------------------------------------|-------------------------------------------|

| IN, RST Open-Drain Output, CLR/BISTB, OV, BIST, NR to                                           | Junction Temperature+150°C                |

| GND0.3V to 6V                                                                                   | Soldering Temperature (Reflow)+26C°C      |

| RST Push-Pull Output to GND0.3V to (V <sub>DD</sub> +0.3)V                                      | Storage Temperature Range65°C to +150°C   |

| Input/Output Continuous Current, RST, CLR/BISTB, OV, BIST, NR20mA                               | Lead Temperature (Soldering, 10s) 300°C   |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C, TDFN-8, derate 6.2mW/°C above +70°C)496mW |                                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

| Package Code                                           | T822CY+2C        |  |  |

|--------------------------------------------------------|------------------|--|--|

| Outline Number                                         | <u>21-100341</u> |  |  |

| Land Pattern Number                                    | <u>90-100117</u> |  |  |

| Thermal Resistance, Four Layer Board:                  |                  |  |  |

| Junction-to-Ambient (θ <sub>J</sub> A)                 | 162(°C/W)        |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 20(°C/W)         |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$((V_{DD} = 1.71 \text{V to } 5.50 \text{V}. T_A = T_J = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25 ^{\circ}\text{C}$  under normal conditions, unless otherwise noted.) TYP is at 3.3V.  $10 \text{k}\Omega$  pullup resistor for all the open drain outputs.)

| PARAMETER                                                             | SYMBOL                 | κΩ pullup resistor for all the open drain outpu CONDITIONS                                                             | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Operating Voltage                                                     | V <sub>DD</sub>        | Comparators Functional                                                                                                 | 1.71 |      | 5.5  | V     |

| Range Minimum Supply Voltage                                          |                        | RST is guaranteed to be at a known logic                                                                               | 1.1  |      |      | V     |

| Supply Current                                                        | I <sub>DD</sub>        | RST, OV, BIST not asserted                                                                                             |      | 12   | 25.5 | μA    |

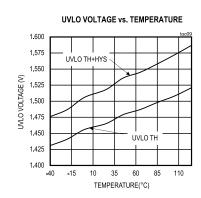

| Undervoltage Lockout                                                  |                        |                                                                                                                        |      | 12   | 20.0 | μΛ    |

| Threshold                                                             | V <sub>UVLO</sub>      | V <sub>DD</sub> Rising                                                                                                 | 1.3  | 1.5  | 1.68 | V     |

| Undervoltage Lockout<br>Threshold Hysteresis                          |                        | V <sub>DD</sub> falling                                                                                                |      | 47   |      | mV    |

| Input Threshold Voltage Programming Range                             | $V_{IN\_TH}$           |                                                                                                                        | 0.51 |      | 5.01 | V     |

| Input Voltage<br>Programming Step                                     |                        |                                                                                                                        |      | 20   |      | mV    |

| Undervoltage/<br>Overvoltage Window<br>Threshold Programming<br>Range | TOL                    | Reset occurs when V <sub>IN</sub> falls outside of V <sub>IN_TH</sub> (1 ±TOL)                                         | ±2   |      | ±9   | %     |

| Window Threshold<br>Programming<br>Resolution                         | TOL <sub>RES</sub>     |                                                                                                                        |      | 1    |      | %     |

| INPUT THRESHOLD ACC                                                   | CURACY                 |                                                                                                                        |      |      |      |       |

| Undervoltage Threshold<br>Accuracy                                    | Vu∨th_a                | All V <sub>IN_TH</sub> setting, V <sub>IN</sub> falling, V <sub>UVTH</sub> = V <sub>IN_TH</sub> (1 - TOL%)             | -0.7 |      | +0.7 | %     |

| Overvoltage Threshold Accuracy                                        | V <sub>OVTH_A</sub>    | All V <sub>IN_TH</sub> settling, V <sub>IN</sub> rising,<br>V <sub>OVTH</sub> =V <sub>IN_TH</sub> (1 + TOL%)           | -0.7 |      | +0.7 | %     |

| Undervoltage/Overvolta                                                |                        | Option A                                                                                                               |      | 0.25 |      |       |

| ge Hysteresis                                                         | V <sub>HYS</sub>       | Option B                                                                                                               |      | 0.50 |      | %VT   |

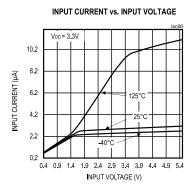

| Input Current                                                         | I <sub>IN</sub>        |                                                                                                                        |      | 1.3  | 5    | μA    |

| Overvoltage Fault-to-OV Assert Delay                                  | t <sub>OV DLY</sub>    | (V <sub>OVTH</sub> - 1%) to (V <sub>OVTH</sub> + 1%)                                                                   |      | 5    |      | μs    |

| OV Fault Glitch                                                       | V <sub>OVTH</sub> + 5% |                                                                                                                        |      | 0.2  |      | μs    |

| CLEAR/BUILT-IN SELF-                                                  | TEST INPUT (CL         | RB/BIST)                                                                                                               |      |      |      |       |

| CLRB/BIST Input Glitch                                                |                        |                                                                                                                        | 50   |      |      | ns    |

| Immunity CLRB/BIST Input Pulse Width to Clear OV Latch                | t <sub>CLR</sub>       | From falling edge of CLRB/BIST to OV rising edge                                                                       | 0.4  |      |      | μs    |

| CLRB/BIST Pulse Width to Initiate BIST                                | t <sub>BIST</sub>      | From falling edge of CLRB/BIST to start of BIST (Note 2)                                                               | 150  |      |      | μs    |

| CLRB/BIST Internal Pull Up Resistance                                 |                        | ()                                                                                                                     |      | 50   |      | kΩ    |

| On-Demand CLRB/BIST to BIST Assert Delay                              |                        | From the falling edge of CLRB/BIST to BIST asserting                                                                   |      |      | 380  | μs    |

| RESET OUTPUT(RST)                                                     |                        | DIOT asserting                                                                                                         |      |      |      |       |

| KLSEI OUIFUI(KSI)                                                     |                        | From the time when \(\text{\cdots}\) ontors                                                                            |      |      |      | 1     |

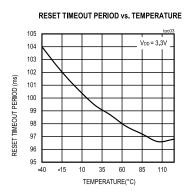

| Reset Timeout Period<br>Accuracy                                      | t <sub>RP</sub>        | From the time when $V_{IN}$ enters overvoltage/undervoltage thresholdwindow to the time RST goes high, $V_{DD}$ = 3.3V | -20  |      | +20  | %     |

# 0.7% Accuracy, Single Window Voltage Monitor with BIST

$((V_{DD} = 1.71V \text{ to } 5.50V. T_A = T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C} \text{ under normal conditions,}$

unless otherwise noted.) TYP is at 3.3V.  $10k\Omega$  pullup resistor for all the open drain outputs.)

| PARAMETER                                       | SYMBOL           | CONDITIONS                                                      | MIN                   | TYP  | MAX          | UNITS |  |

|-------------------------------------------------|------------------|-----------------------------------------------------------------|-----------------------|------|--------------|-------|--|

| IN-to-RST Propagation                           | t <sub>DOV</sub> | (V <sub>OVTH</sub> - 1%) to (V <sub>OVTH</sub> + 1%)            |                       | 5    |              |       |  |

| Delay                                           | t <sub>DUV</sub> | (V <sub>UVTH</sub> + 1%) to (V <sub>UVTH</sub> - 1%)            |                       | 12   |              | μs    |  |

| RST Leakage Current                             |                  | V <sub>RST</sub> = V <sub>OV</sub> = 5.5V                       |                       | 0.01 | 1            | μΑ    |  |

| INPUT VOLTAGE (CLR/E                            | BIST, NR)        |                                                                 |                       |      |              |       |  |

| Input Voltage Low                               | V <sub>IL</sub>  |                                                                 |                       |      | 0.3 x<br>VDD | V     |  |

| Input Voltage High                              | $V_{IH}$         |                                                                 | 0.7 x<br>VDD          |      |              | V     |  |

| Leakage Current                                 |                  | $V_{CLRB/BIST} = V_{NR} = V_{DD},$                              | -0.1                  |      | +0.1         | μΑ    |  |

| OUTPUT VOLTAGE (RS                              | T, OV, BIST)     |                                                                 | •                     |      |              | •     |  |

|                                                 |                  | RST, OV, BIST, V <sub>DD</sub> = 5V, I <sub>SINK</sub> = 3mA    |                       | 0.1  | 0.3          |       |  |

| Output Voltage Low                              | $V_{OL}$         | RST, OV, BIST, V <sub>DD</sub> = 1.71V, I <sub>SINK</sub> = 3mA |                       | 0.1  | 0.3          | V     |  |

|                                                 |                  | RST, V <sub>DD</sub> = 1.71V, I <sub>SINK</sub> = 8µA           |                       | 0.1  | 0.3          |       |  |

| Reset Output Voltage<br>High (Push-Pull Option) | V <sub>OH</sub>  | V <sub>DD</sub> = 1.71V, I <sub>SOURCE</sub> = 200μA            | 0.8 x V <sub>DD</sub> |      |              | V     |  |

| Reset Output Voltage<br>High (Push-Pull Option  | V <sub>OH</sub>  | V <sub>DD</sub> = 4.5V, I <sub>SOURCE</sub> = 800μA             | 0.8 x V <sub>DD</sub> |      |              | V     |  |

**Note 1:** Outputs are guaranteed to be in correct state down to  $V_{DD} = 1.1V$ .

**Note 2:** Minimum pulse required to clear OV latch state. No overvoltage fault present and RST = high.

Note 3: Use <100k $\Omega$  pullup resistor for RST pin, otherwise BIST error is reported.

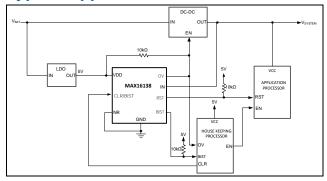

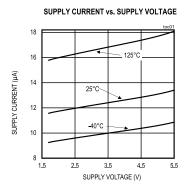

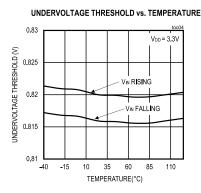

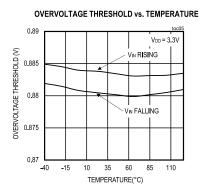

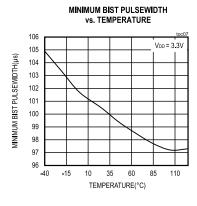

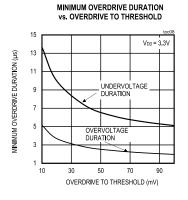

## **Typical Operating Characteristics**

$(V_{DD} = 1.71 \text{V to } 5.50 \text{V}, T_A = -40 ^{\circ} \text{C} \text{ to } 125 ^{\circ} \text{C}. \text{ Typical values are at } V_{DD} = 3.3 \text{V}, \text{ unless otherwise specified.})$

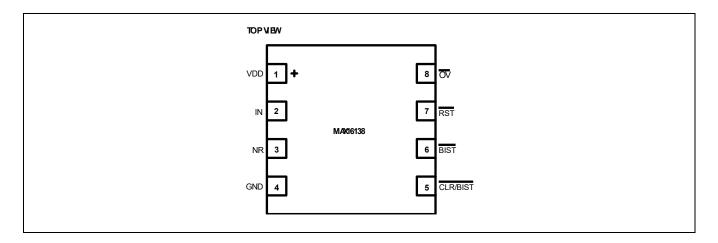

# **Pin Configuration**

# **Pin Description**

| PIN | NAME     | FUNCTION                                                                                                                                                                                                                                                                                            |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDD      | Supply Input. Bypass V <sub>DD</sub> to ground with a 0.1µF capacitor.                                                                                                                                                                                                                              |

|     |          | Monitoring Input IN (Factory-Set Threshold Monitoring Input). When V <sub>IN</sub> falls outside the factory selected                                                                                                                                                                               |

| 2   | IN       | undervoltage/overvoltage threshold window, RST asserts and stays asserted for a selected reset timeout period after $V_{\text{IN}}$ falls within the undervoltage/overvoltage threshold window. When $V_{\text{IN}}$ exceeds the                                                                    |

|     |          | overvoltage threshold, OV asserts and indicates an overvoltage fault.                                                                                                                                                                                                                               |

| 3   | NR       | No Reset BIST Logic Input. Setting NR to a logic low and driving CLRB/BIST low for more than 150µs initiates BIST and asserts the reset output and BIST if BIST fails. Setting NR to a logic high and driving CLRB/BIST low for more than 150µs initiates BIST and asserts BIST only if BIST fails. |

| 4   | GND      | Ground                                                                                                                                                                                                                                                                                              |

| 5   | CLR/BIST | Overvoltage Clear/Built-In-Self-Test Input. CLRB/BIST is a multiplexed function input. A falling edge on CLRB/BIST clears OV latch. Drving CLRB/BIST for more than 150µs initiates BIST.                                                                                                            |

| 6   | BIST     | Active-Low, Open-Drain Output. BIST asserts low if BIST fails. Pull BIST to V <sub>DD</sub> with a pullup resistor.                                                                                                                                                                                 |

| 7   | RST      | Open-Drain Reset Output. RST asserts low when V <sub>IN</sub> falls outside of the undervoltage/overvoltage threshold window. The reset output deasserts after the reset timeout period when V <sub>IN</sub> enters the undervoltage/overvoltage threshold window                                   |

| 8   | OV       | Open-Drain, Active-Low Overvoltage Latched Fault Output. OV latches low when the voltage at IN exceeds the overvoltage threshold setting. OV latch is cleared on the falling edge of CLRB/BIST.                                                                                                     |

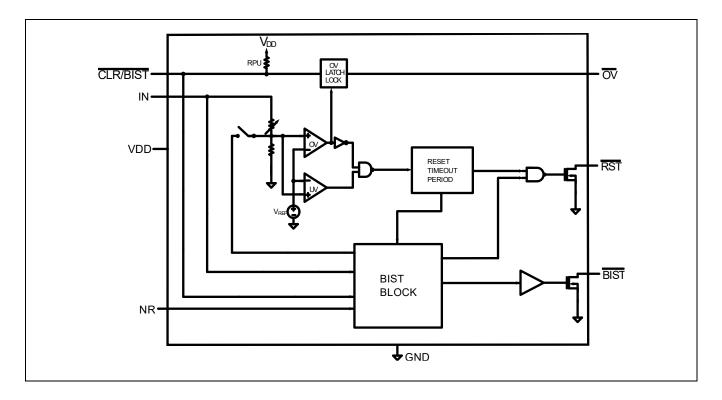

# **Functional Diagram**

### **Detailed Description**

The MAX16138 is a high-accuracy single-channel supervisory reset circuit that monitors the system supply for undervoltage and overvoltage faults within factory-programmable window thresholds. The MAX16138's Built-In Self-Test (BIST) diagnostic capability and overvoltage fault output optimizes system safety in ADAS applications. A reset output (RST) asserts when the input voltage falls outside of the threshold window. The reset output deasserts after the reset timeout period when the supply voltage returns to its nominal voltage level.

#### Input Voltage Threshold

The MAX16138 offers a wide range of nominal input voltages from 0.51V to 5.01V, in approximately 20mV increments. Each selected nominal input voltage is factory-trimmed halfway between the undervoltage and overvoltage threshold window. See the <u>Undervoltage/Overvoltage Thresholds</u> section for more details. Contact Analog Devices for options not listed in the <u>Ordering Information</u> table.

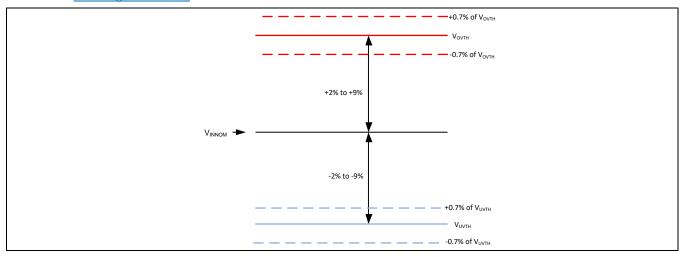

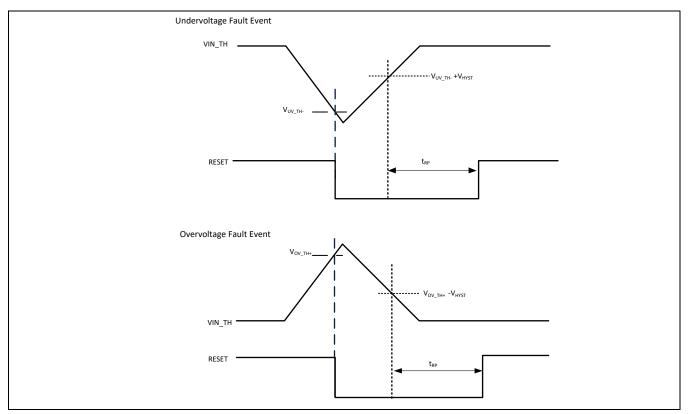

Figure 1. Undervoltage/Overvoltage Threshold Tolerance and Accuracy

#### **Undervoltage/Overvoltage Threshold**

The MAX16138 monitors supply voltage for undervoltage/overvoltage faults with respect to the nominal input voltage within  $\pm 0.7\%$  accuracy over the operating temperature and supply ranges. The undervoltage and overvoltage thresholds are factory-trimmed from  $\pm 2\%$  to  $\pm 9\%$ , in  $\pm 1\%$  increments. Contact Analog Devices for a threshold not listed in the *Ordering Information* table.

#### **Undervoltage/Overvoltage Threshold Hysteresis**

The monitoring input (IN) features undervoltage/overvoltage threshold hysteresis that provides immunity to short input transients. The input hysteresis is factory-set to either 0.25% or 0.5% and is applicable to both the undervoltage and overvoltage thresholds. Contact Analog Devices for a hysteresis option not listed in the *Ordering Information* table.

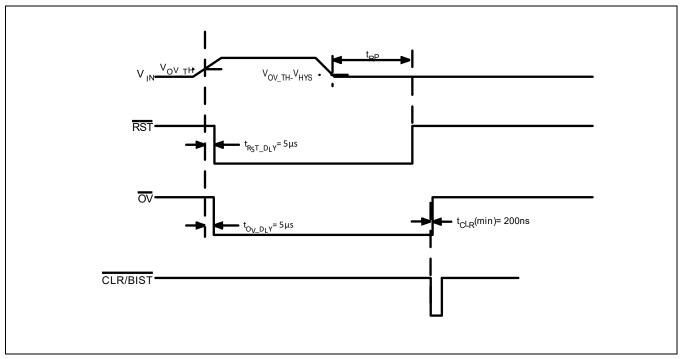

#### **Overvoltage Fault Output**

OV is an open-drain, active-low latched output that latches low  $5\mu s$  after  $V_{IN}$  exceeds the overvoltage threshold level. OV latch is cleared on the falling edge of CLR/BIST after the overvoltage fault is removed. See the <u>Electrical Characteristics</u> table and <u>Figure 2</u> for more details.

Figure 2. Clear Input Timing Diagram

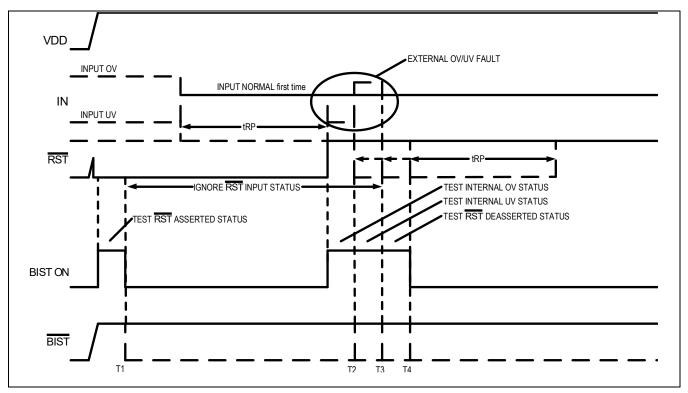

#### **Built-In Self-Test**

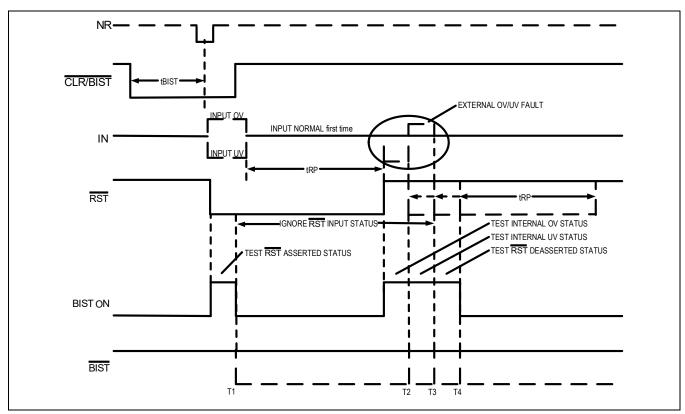

Built-in Self-Test (BIST) is a diagnostic feature that monitors the health of the MAX16138. BIST is initiated during power-up and completes after the expiration of the reset timeout period. During power-up, the MAX16138 monitors the state of the reset output. A high-logic reset output status during power-up indicates a fault either inside or outside the MAX16138, and BIST is pulled low. See the following *Figure 3* at T1. After the expiration of the reset timeout period, the MAX16138 generates internally fictitious undervoltage and overvoltage fault scenarios, and RST deasserts. If the MAX16138 internal circuit does not respond properly to the internally generated undervoltage and overvoltage faults, BIST and RST are pulled low. See the *Figure 3* at T2 and T3. Then the MAX16138 monitors the state of the reset output again. A low-logic reset output status indicates a fault either inside or outside the MAX16138 and BIST is pulled low. See T4 in *Figure 3*.

Figure 3. MAX16138 BIST Timing Relationship

#### **On-Demand BIST**

On-demand BIST allows the MAX16138 to initiate BIST during normal operation. On-demand BIST is initiated when CLR/BIST is pulled low for more than t<sub>BIST</sub>. See the <u>Electrical Characteristics</u> table for more details. If CLR/BIST is pulled low for less than t<sub>BIST</sub> or if the input is overvoltage or undervoltage before the expiration of t<sub>BIST</sub>, on-demand BIST is ignored.

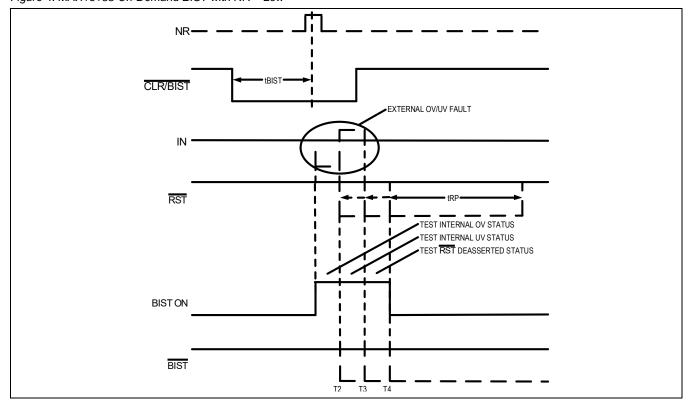

With NR at logic low and CLR/BIST pulled low for more than t<sub>BIST</sub>, the on-demand BIST operation is similar to that of power-up; the MAX16138 pulls the reset output low during the internal OV and UV testing while keeping the system in reset (*Figure 4*). When NR is at logic high and CLR/BIST is pulled low for more than t<sub>BIST</sub>, the on-demand BIST operation is carried out without pulling the reset output low. See *Figure 5* for more details.

Figure 4. MAX16138 On-Demand BIST with NR = Low

Figure 5. MAX16138 On-Demand BIST with NR = High

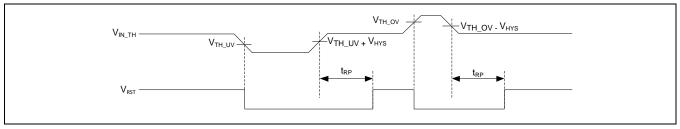

#### **Reset Timeout Period**

The active-low, open-drain reset output (RST) asserts low when the input voltage falls outside the set undervoltage and overvoltage window threshold. The reset output deasserts after the reset timeout period when the input voltage falls within the set window threshold. At power-up, the resets stay asserted for the reset timeout period once  $V_{DD}$  is above the UVLO. The reset output requires a pullup resistor to  $V_{DD}$ . The MAX16138 offers 16 factory-set reset timeout periods. The MAX16138 is also available in push-pull option. Contact Analog Devices for availability. See <u>Table 1</u> for available options and <u>Figure 6</u> for more details.

**Table 1. Reset Timeout Options**

| Table 1. Reset Timeout Options |  |

|--------------------------------|--|

| MIN RESET TIMEOUT PERIOD       |  |

| 1ms                            |  |

| 5ms                            |  |

| 10ms                           |  |

| 15ms                           |  |

| 20ms                           |  |

| 50ms                           |  |

| 100ms                          |  |

| 150ms                          |  |

| 200ms                          |  |

| 250ms                          |  |

| 300ms                          |  |

| 500ms                          |  |

| 750ms                          |  |

| 1000ms                         |  |

| 15000ms                        |  |

Figure 6. Reset Output Timing Diagram

### **Applications Information**

#### **Setting Input Thresholds Tolerance and Hysteresis**

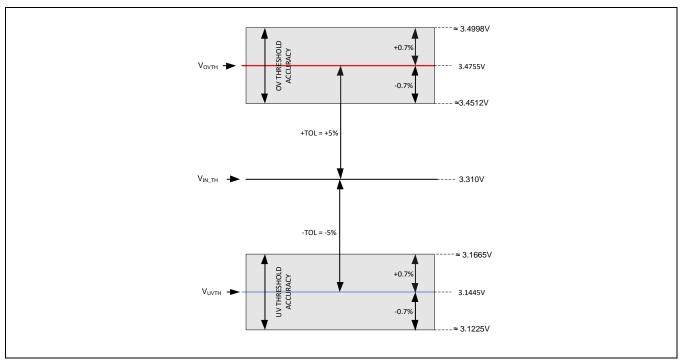

The MAX16138 monitors a system supply voltage for undervoltage/overvoltage window threshold. Depending on the system supply tolerance requirement, the undervoltage/overvoltage thresholds can be factory-trimmed from  $\pm 2\%$  to  $\pm 9\%$ . The tolerance setting is symmetrical with respect to the selected nominal input threshold voltage ( $V_{IN\_NOM}$ ). A detailed calculation of how to determine the undervoltage/overvoltage threshold levels with  $\pm 0.7\%$  threshold accuracy for 3.31V  $\pm 5\%$  supply voltage is as follows:

$V_{IN\_NOM} = 3.31V$   $TOL = \pm 5\%$   $V_{UVTH} = V_{IN\_NOM} (1 - 5\%) = 3.31V (1 - 0.05) = 3.1445V$   $V_{OVTH} = V_{IN\_NOM} (1 + 5\%) = 3.31V (1 + 0.05) = 3.4755V$

#### where:

V<sub>IN NOM</sub> is the selected nominal input threshold voltage

TOL is the input tolerance

V<sub>UVTH</sub> is undervoltage threshold voltage

V<sub>OVTH</sub> is the overvoltage threshold voltage

The MAX16138 monitors the supply voltage with  $\pm 0.7\%$  accuracy over the operating temperature and supply range. The accuracy range for the 3.3V  $\pm 5\%$  is as follows:

$V_{UVTH\_A} = V_{UVTH} (1 \pm 0.7\%) = 3.1445V (1 \pm 0.007) = 3.1445V \pm 0.0220115V$  $V_{OVTH\_A} = V_{OVTH} (1 \pm 0.7\%) = 3.4775V (1 \pm 0.007) = 3.4775V \pm 0.0243425V$

where  $V_{UVTH\_A}$  is the undervoltage threshold accuracy range and  $V_{OVTH\_A}$  is the overvoltage threshold accuracy range. See *Figure 7* for details.

Figure 7. Undervoltage/Overvoltage Threshold Accuracy

Hysteresis adds noise immunity to the voltage monitors and prevents oscillation due to repeated triggering when the monitored voltage is near the threshold trip voltage.

A detailed calculation to get the threshold hysteresis is as follows:

$V_{IN\_TH} = 3.31V$

Hysteresis = 0.5%

$V_{HYST} = 3.31V \times 0.5\% = 0.01655V$

Figure 8. Undervoltage/Overvoltage Threshold Hysteresis

#### **Power-Supply Bypassing/Noise Immunity**

The MAX16138 operates from a 1.71V to 5.50V supply. Bypass  $V_{DD}$  to ground with a 0.1 $\mu$ F capacitor as close to the device as possible. An additional capacitor improves transient immunity.

#### **Selector Guide Table**

| PART NUMBER       | THRESHOLD<br>VOLTAGE | TOLERANCE | HYSTERESIS | RESET TIMEOUT |

|-------------------|----------------------|-----------|------------|---------------|

| MAX16138ATA01/VY+ | 0.85V                | ±4%       | ±0.5%      | 100ms         |

# **Typical Application Circuit**

# **Ordering Information**

| PART NUMBER       | TEMP RANGE     | PIN-PACKAGE |  |

|-------------------|----------------|-------------|--|

| MAX16138ATA01/VY+ | -40°C to 125°C | 8-TDFN      |  |

N denotes an automotive qualified part.

Y = Side-wettable package.

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

\*Future product—contact factory for availability.

## **Revision History**

| REVISION | REVISION | DESCRIPTION              | PAGES   |

|----------|----------|--------------------------|---------|

| NUMBER   | DATE     | DESCRIPTION              | CHANGED |

| 0        | 4/22     | Release for Market Intro | _       |

www.analog.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

MAX16138ATA01/VY+ MAX16138ATA01/VY+T