#### Click here to ask an associate for production status of specific part numbers.

### Quad-Channel Industrial Digital Output/Digital Input

### **General Description**

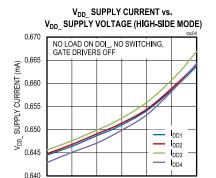

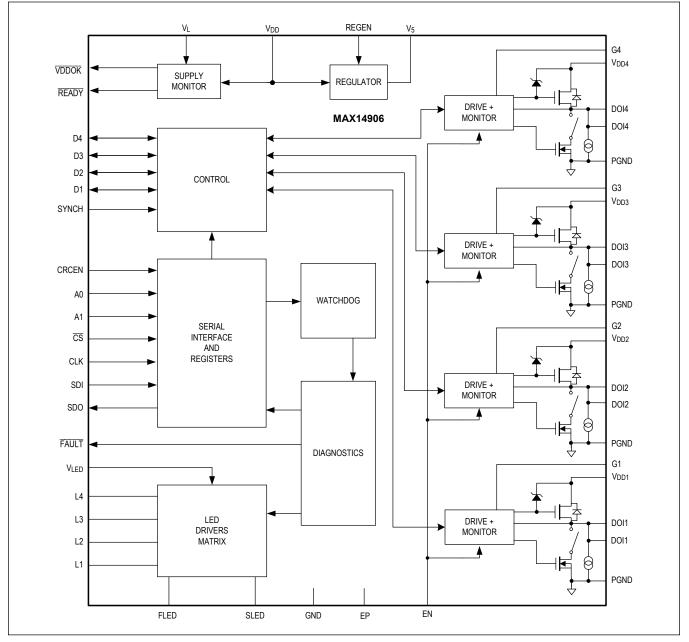

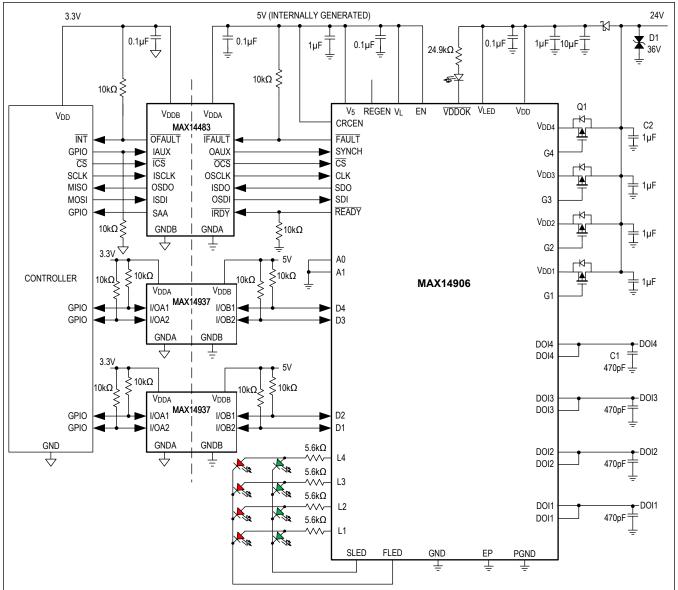

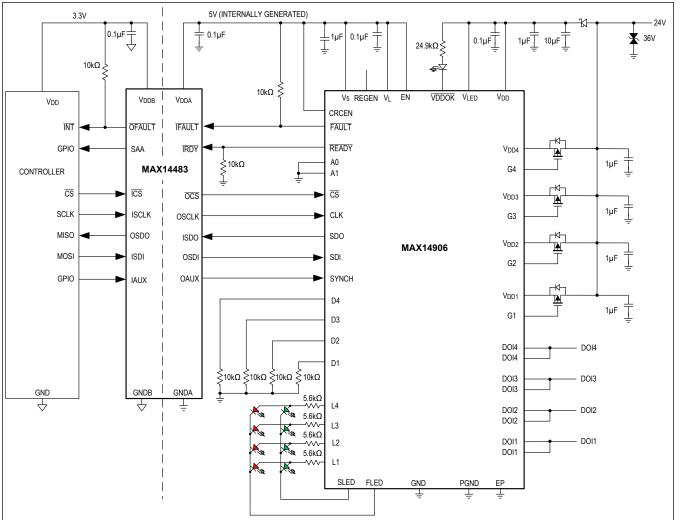

The MAX14906 is an IEC 61131-2 compliant, high-speed, four-channel industrial digital output, digital input device that can be configured on a per-channel basis as a high-side (HS) switch, push-pull (PP) driver, or a Type 1 and 3, or Type 2 digital input. The MAX14906 is specified for operation with a supply voltage up to 40V and is tolerant to 65V.

The high-side switch current limiting is settable from 130mA to 1.2A with the option of 2x load inrush current. The high-side driver on-resistance is  $120m\Omega$  (typ) at 25°C ambient temperature. Optional push-pull operation allows high speed driving of cables and fast discharge of load capacitance. For digital input operation, current sinks for 2.3mA (Type 1 and 3) or 7mA (Type 2) are provided.

The SPI interface has a built-in chip addressing decoder, allowing communication with multiple MAX14906 devices utilizing a shared SPI with a common chip select (CS). The SPI interface provides flexibility for global and per-channel configuration and diagnostics, including supply overvoltage and undervoltage detection, wire-break or openwire detection, thermal overload and current limit reporting, and more. For high-speed operation, the digital input and output states can be monitored and changed directly using pins for increased system speed and throughput.

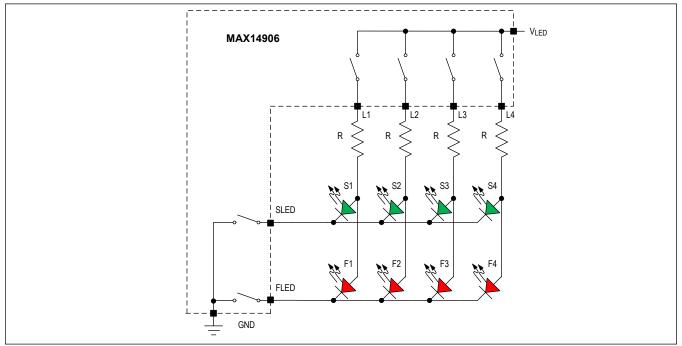

Open-wire detection monitors open-wire/open-load conditions with switches in the off state. LED drivers provide indication of per-channel fault, status, and supply undervoltage conditions. Internal active clamps allow for fast turnoff of inductive loads. Integrated line-to-ground and lineto-line surge protection only requires a TVS on V<sub>DD</sub>.

The MAX14906 is available in a compact 48-pin 7mm x 7mm QFN package.

### **Applications**

- Industrial Digital Output and Input Module

- Configurable Digital Input/Output

- Motor Control

- PLC Systems

- Distributed Control Systems (DCS)

### **Benefits and Features**

- Per-Channel Configurability Enables Wide Range of Applications

- Digital Output: High-Side (HS) Switch or Push-Pull (PP) Driver

- Digital Input: Software Selectable Type 1 and 3, or Type 2

- Current Limit Settable from 130mA to 1.2A

- Serial (SPI) or Direct Operation Using Pins

- Independent Channel Powering

- Fault Tolerant with Built-In Diagnostics

- Per-Channel Diagnostics

- Integrated Voltage Supply Monitoring and Short-to-V<sub>DD</sub> Detection

- Open-Wire/Open-Load Detection

- Thermal Shutdown Protection

- Watchdog Timer

- 5-Bit CRC Code Generation and Checking for SPI Error Detection

- High Integration Reduces BOM Count and PCB Space

- Integrated LDO Compatible with 5V Logic Devices

- Internal Active Clamps for Fast Inductive Load

Turn-Off

- 0.6µs (typ) DO and 1µs (typ) DI Propagation Delays

- Addressable SPI

- 7mm x 7mm TQFN Package

- Reduced Power and Heat Dissipation

- Low R<sub>DSON</sub> for High-Side Switches, 120mΩ (typ)

- Accurate Output Current Limiting

- Accurate Input Current Sinks, Type 1 and 3, or Type 2

- Robust Design

- 10V to 40V Operating Supply Range, 65V Tolerant

- SafeDemag<sup>TM</sup> Allows Fast Turn-Off of Unlimited Inductance

- ±16kV Air-Gap ESD and ±8kV Contact ESD

- ±1kV Surge Tolerant Using TVS Protection on V<sub>DD</sub> to GND

- -40°C to +125°C Operating Temperature

SafeDemag is a trademark of Maxim Integrated Products, Inc.

Ordering Information appears at end of datasheet.

19-100736; Rev 4; 4/22

© 2022 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

One Analog Way, Wilmington, MA 01887 U.S.A. | Tel: 781.329.4700 | © 2022 Analog Devices, Inc. All rights reserved.

# Quad-Channel Industrial Digital Output/Digital Input

### **Quad Industrial Digital Output, Digital Input**

## Quad-Channel Industrial Digital Output/Digital Input

### **Absolute Maximum Ratings**

| V <sub>DD</sub> , V <sub>DD1</sub> , V <sub>DD2</sub> , V <sub>DD3</sub> , V <sub>DD4</sub> , V <sub>LED</sub> 0.3V to +65V | Continuous Current                                                   |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| DOI1, DOI2, DOI3, DOI4                                                                                                      | DOI_Load CurrentInternally Limited                                   |

| $V_{DD} < V_{DD}_{OVTH}$ ( $V_{DD} - 49V$ ) to ( $V_{DD} + 0.3V$ )                                                          | All Pins other than DOI100mA to +100mA                               |

| $V_{DD} > V_{DD} OVTH$                                                                                                      | Inductive Demagnetization Energy (I <sub>DOI</sub> < 0.6A) Unlimited |

| V <sub>5</sub> , V <sub>L</sub> 0.3V to +6V                                                                                 | Continuous Power Dissipation (T <sub>A</sub> = +70°C)                |

| SDI, CLK, CS, EN, A0, A1, SYNCH, REGEN0.3V to +6V                                                                           | TQFN 48 (derate 40mW/°C above 70°C)                                  |

| FAULT0.3V to +6V                                                                                                            | Junction TemperatureInternally Limited                               |

| D1, D2, D3, D4, SDO, READY0.3V to (V <sub>L</sub> + 0.3V)                                                                   | Storage Temperature Range65°C to +150°C                              |

| SLED, FLED, L1, L2, L3, L4, VDDOK0.3V to (V <sub>LED</sub> + 0.3V)                                                          | Lead Temperature (soldering, 10s)+300°C                              |

| G1, G2, G3, G40.3V to min(40V, V <sub>DD</sub> + 0.3V)                                                                      | Soldering Temperature (reflow)+260°C                                 |

| Note 1: All voltages relative to GND.                                                                                       |                                                                      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **48 TQFN**

| Package Code                          | T4877+6C                              |  |  |  |

|---------------------------------------|---------------------------------------|--|--|--|

| Outline Number                        | <u>21-0144</u>                        |  |  |  |

| Land Pattern Number                   | <u>90-0130</u>                        |  |  |  |

| Thermal Resistance, Four-Layer Board: | Thermal Resistance, Four-Layer Board: |  |  |  |

| Junction to Ambient ( $\theta_{JA}$ ) | 25°C/W                                |  |  |  |

| Junction to Case ( $\theta_{JC}$ )    | 1°C/W                                 |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

## Quad-Channel Industrial Digital Output/Digital Input

### **Electrical Characteristics**

| PARAMETER                                                                 | SYMBOL                  | CONDITIONS                                                                                                                                 | MIN                      | TYP  | MAX  | UNITS |

|---------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|------|-------|

| V <sub>DD</sub> AND V <sub>DD</sub> SUPPLY                                | VOLTAGES                |                                                                                                                                            |                          |      |      |       |

| Supply Voltage V and                                                      |                         | Normal Operating Conditions                                                                                                                | 10                       |      | 40   |       |

| Supply Voltage V <sub>DD</sub> and V <sub>DD</sub> _                      | V <sub>DD</sub>         | Overvoltage Lockout Tolerance                                                                                                              | V <sub>DD_OV</sub><br>TH |      | 65   | V     |

|                                                                           |                         | All channels in HS mode, $V_{DD}$ = 40V,<br>REGEN = GND, DOI_ not loaded, no<br>load on V <sub>5</sub> , gate drivers off                  |                          | 2.5  | 4.5  |       |

| Sum of V <sub>DD</sub> and V <sub>DD</sub> _<br>Supply Currents           | IDD_ON                  | All channels in PP mode, $V_{DD}$ = 40V,<br>REGEN = GND, 10kHz switching, no load<br>on DOI_, no load on V <sub>5</sub> , gate drivers off |                          | 4    | 7    | mA    |

|                                                                           |                         | All channels in DI mode, REGEN = GND                                                                                                       |                          | 2.5  | 4.5  |       |

| V <sub>DD</sub> _Supply Current                                           | IDD_ON_IN               | All G_turned on                                                                                                                            |                          | 0.5  | 1.4  | mA    |

| V <sub>DD</sub> _Overvoltage<br>Lockout Threshold                         | V <sub>DD_OVTH</sub>    | V <sub>DD_</sub> rising                                                                                                                    | 41.5                     | 43.5 | 45   | V     |

| V <sub>DD</sub> _Overvoltage<br>Lockout Hysteresis                        | V <sub>DD_OVHYST</sub>  |                                                                                                                                            |                          | 1    |      | V     |

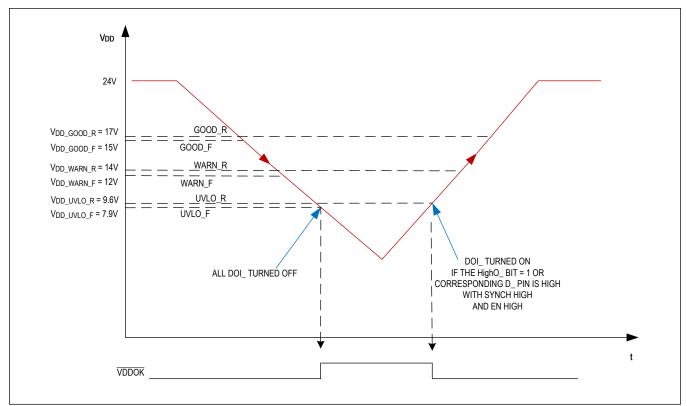

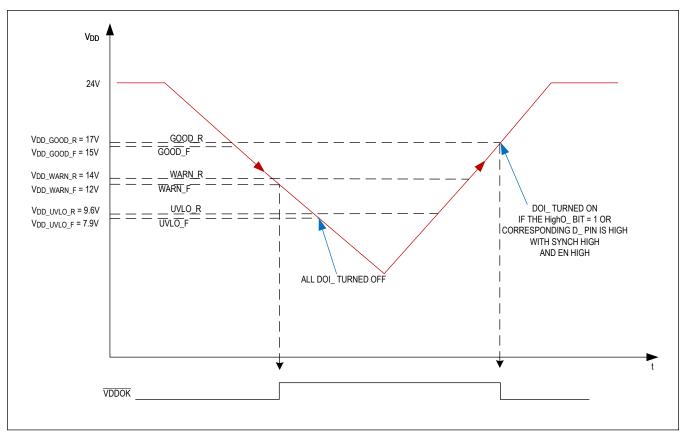

| $V_{DD}$ and $V_{DD}$                                                     | V <sub>DD_UVLO_</sub> R | $V_{DD}$ , $V_{DD}$ _rising                                                                                                                |                          |      | 9.6  | V     |

| Undervoltage Lockout<br>Threshold                                         | V <sub>DD_UVLO_F</sub>  | V <sub>DD</sub> , V <sub>DD</sub> _falling                                                                                                 | 7.9                      |      |      |       |

| V <sub>DD</sub> and V <sub>DD</sub><br>Undervoltage Lockout<br>Hysteresis | V <sub>DD_UVHYST</sub>  |                                                                                                                                            |                          | 1    |      | v     |

| V <sub>DD</sub> Undervoltage                                              | V <sub>DD_WARN_R</sub>  | V <sub>DD</sub> rising                                                                                                                     |                          |      | 14   | v     |

| Warning Threshold                                                         | V <sub>DD_WARN_F</sub>  | V <sub>DD</sub> falling                                                                                                                    | 12                       |      |      | V     |

| V <sub>DD</sub> Undervoltage<br>Warning Hysteresis                        | V <sub>DD_WARN_H</sub>  |                                                                                                                                            |                          | 1    |      | v     |

| V <sub>DD</sub> Undervoltage Good                                         | V <sub>DD_GOOD_R</sub>  | V <sub>DD</sub> rising                                                                                                                     |                          |      | 17   | v     |

| Threshold                                                                 | V <sub>DD_GOOD_F</sub>  | V <sub>DD</sub> falling                                                                                                                    | 15                       |      |      | v     |

| V <sub>DD</sub> Undervoltage Good<br>Hysteresis                           | V <sub>DD_GOOD_H</sub>  |                                                                                                                                            |                          | 1    |      | V     |

| LOGIC INTERFACE SUP                                                       | PLY (V <sub>L</sub> )   |                                                                                                                                            |                          |      |      |       |

| V <sub>L</sub> Supply Voltage                                             | VL                      |                                                                                                                                            | 2.5                      |      | 5.5  | V     |

| V <sub>L</sub> Supply Current                                             | I <sub>VL</sub>         | All logic inputs high or low, logic outputs unloaded                                                                                       |                          | 18   | 40   | μA    |

| V <sub>L</sub> POR Threshold                                              | V <sub>L_POR</sub>      | V <sub>L</sub> voltage falling                                                                                                             | 1                        | 1.27 | 1.55 | V     |

| 5V SUPPLY (V <sub>5</sub> )                                               |                         |                                                                                                                                            |                          |      |      |       |

| V <sub>5</sub> Supply Voltage                                             | V <sub>5</sub>          | REGEN = GND                                                                                                                                | 4.75                     | 5.0  | 5.25 | V     |

| V <sub>5</sub> Supply Current in HS<br>Mode                               | IV5_ON_HS               | All channels in HS mode, REGEN =<br>GND, all DOI_ switches ON and<br>unloaded                                                              |                          | 1    | 1.8  | mA    |

## Quad-Channel Industrial Digital Output/Digital Input

### **Electrical Characteristics (continued)**

| PARAMETER                                             | SYMBOL                     | CONDITIONS                                                                                          | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>5</sub> Supply Current in Active-Clamp PP Mode | IV5_ON_PP_AC               | All channels in active clamp PP mode,<br>REGEN = GND, all DOI_ switches ON<br>and unloaded          |      | 1.1  | 2    | mA    |

| V <sub>5</sub> Supply Current in Simple PP Mode       | IV5_ON_PP                  | All channels in simple PP mode, REGEN<br>= GND, all DOI_switches ON and<br>unloaded                 |      | 1.1  | 2    | mA    |

| V <sub>5</sub> Supply Current in DI<br>Mode           | IV5_ON_DI                  | All channels in DI mode, REGEN = GND,<br>all DOI_ at 30V                                            |      | 1.1  | 2    | mA    |

| V <sub>5</sub> Undervoltage<br>Lockout Threshold      | V <sub>5_UVLO</sub>        | V <sub>5</sub> rising                                                                               | 3.8  |      | 4.4  | V     |

| V <sub>5</sub> Undervoltage<br>Lockout Hysteresis     | V <sub>5UVLO_HYS</sub>     |                                                                                                     |      | 0.3  |      | V     |

| <b>5V LINEAR REGULATO</b>                             | R (V <sub>5</sub> , REGEN) |                                                                                                     |      |      |      |       |

| V <sub>5</sub> Regulator Output<br>Voltage            | V <sub>5</sub>             | REGEN = open, 0mA to 20mA external<br>load current                                                  | 4.75 | 5.0  | 5.25 | V     |

| V <sub>5</sub> Regulator Current<br>Limit             | I <sub>CL_V5</sub>         | REGEN = open                                                                                        | 25   |      |      | mA    |

| REGEN Pullup Current                                  | IPU_REGEN                  | REGEN = GND                                                                                         | 5    |      | 30   | μA    |

| REGEN Threshold                                       | V <sub>TH_REGEN</sub>      | REGEN rising                                                                                        | 1    | 1.6  | 2.5  | V     |

| DRIVER OUTPUTS (DOI                                   | _)                         |                                                                                                     |      |      |      |       |

| High-Side On-<br>Resistance                           | R <sub>ON_HS</sub>         | HS or PP modes, I <sub>DOI</sub> _ = 500mA                                                          |      | 120  | 240  | mΩ    |

| Low-Side On-<br>Resistance                            | R <sub>ON_LS</sub>         | DoMode_ = 11 (Simple PP mode), I <sub>DOI_</sub><br>= 100mA                                         |      | 1    | 3    | Ω     |

| Low-Side Output Low                                   | Maxim                      | Active clamp PP mode, I <sub>DOI</sub> = 100mA                                                      |      |      | 1.2  | v     |

| Voltage                                               | V <sub>OL_LS</sub>         | Simple PP mode, I <sub>DOI</sub> = 100mA                                                            |      |      | 0.4  |       |

| DOI_ Clamp Voltage                                    |                            | Relative to V <sub>DD</sub> _, I <sub>DOI</sub> _ = 10mA, V <sub>DD</sub> _ < V <sub>DD</sub> _OVTH | -63  | -55  | -49  | v     |

|                                                       | V <sub>CL</sub>            | Relative to GND, I <sub>DOI</sub> = 10mA,<br>V <sub>DD_OVTH</sub> < V <sub>DD</sub> _< 60V          | -6   | -4.5 | -3   | v     |

|                                                       | ILK40_DOI                  | V <sub>DD</sub> = 40V, HS mode, DOI_ = off, 0V <<br>DOI_ < V <sub>DD</sub> _                        | -60  |      | +60  | μA    |

| DOI_ Leakage                                          | ILKDOI_ANA                 | V <sub>DD</sub> _= 40V, low-leakage high-<br>impedance mode, 0V < DOI_ < V <sub>DD</sub> _          | -2.4 |      | +2.4 | μA    |

## Quad-Channel Industrial Digital Output/Digital Input

### **Electrical Characteristics (continued)**

| PARAMETER                                | SYMBOL                 | CONDITIONS                                                                                                                        | MIN | TYP | MAX  | UNITS     |  |  |

|------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-----------|--|--|

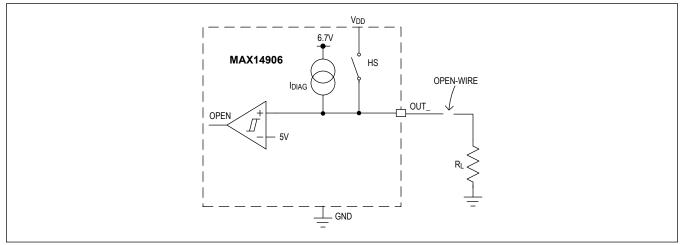

| OFF STATE DIAGNOSTICS (DOI_)             |                        |                                                                                                                                   |     |     |      |           |  |  |

|                                          | IDIAG1                 | OWOffEn_ = 1, V <sub>DOI</sub> _ < 5V or V <sub>DOI</sub> _ ><br>9V, OWOffCs = 00, Both Open-Wire and<br>Short-to-V <sub>DD</sub> | 20  | 60  | 120  |           |  |  |

| Diagnostic Test Current                  | IDIAG2                 | OWOffEn_ = 1, V <sub>DOI</sub> < 5V or V <sub>DOI</sub> ><br>9V, OWOffCs = 01, Both Open-Wire and<br>Short-to-V <sub>DD</sub>     | 60  | 100 | 180  |           |  |  |

| Diagnostic Test Current                  | I <sub>DIAG3</sub>     | OWOffEn_ = 1, V <sub>DOI</sub> < 5V or V <sub>DOI</sub> ><br>9V, OWOffCs = 10, Both Open-Wire and<br>Short-to-V <sub>DD</sub>     | 200 | 300 | 440  | - μΑ<br>- |  |  |

|                                          | I <sub>DIAG4</sub>     | OWOffEn_ = 1, V <sub>DOI</sub> < 5V or V <sub>DOI</sub> > 9V, OWOffCs = 11, Both Open-Wire and Short-to-V <sub>DD</sub>           | 460 | 600 | 760  |           |  |  |

| DOI_ Open Voltage,<br>OWOff_             | V <sub>OUT_OFF</sub>   | OWOffEn_ = 1, I <sub>DOI</sub> _ = 0mA                                                                                            | 5.8 | 6.7 | 7.6  | V         |  |  |

| Open-Wire Detection<br>Threshold, OWOff_ | V <sub>TH_OWOFF</sub>  | OWOffEn_ = 1                                                                                                                      | 5   |     | 5.8  | V         |  |  |

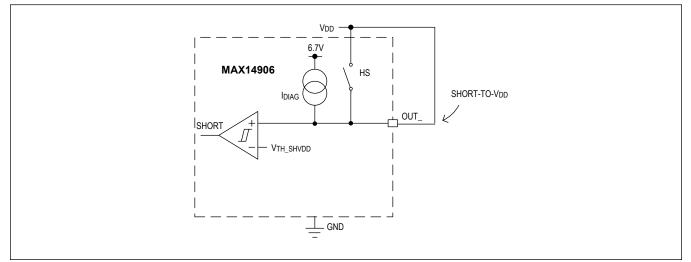

|                                          | VTH_SHVDD1             | ShVddEn_ = 1, ShtVddThr = 00                                                                                                      | 8.2 | 9   | 10   |           |  |  |

| Short-to-V <sub>DD</sub> Detection       | VTH_SHVDD2             | ShVddEn_ = 1, ShtVddThr = 01                                                                                                      | 9.1 | 10  | 10.9 | v         |  |  |

| Threshold                                | VTH_SHVDD3             | ShVddEn_ = 1, ShtVddThr = 10                                                                                                      | 11  | 12  | 13   |           |  |  |

|                                          | V <sub>TH_SHVDD4</sub> | ShVddEn_ = 1, ShtVddThr = 11                                                                                                      | 13  | 14  | 15   |           |  |  |

## Quad-Channel Industrial Digital Output/Digital Input

### **Electrical Characteristics (continued)**

| PARAMETER                     | SYMBOL                  | COND                                                          | MIN                                                                                                                                                  | TYP              | MAX                           | UNITS                                                                                                          |     |     |     |   |

|-------------------------------|-------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------|-----|-----|-----|---|

| CURRENT LIMITING (DO          | ,<br>                   |                                                               |                                                                                                                                                      |                  |                               |                                                                                                                |     |     |     |   |

|                               |                         | CL_[1:0] = 01, see<br>Table 2                                 | $\begin{array}{l} DoMode_[1:0] = 01\\ and t > t_{INRUSH}, or\\ DoMode_[1:0] = \\ 00, 10 \text{ or } 11 \text{ and } t\\ is don't care \end{array}$   | 130              | 175                           | 220                                                                                                            |     |     |     |   |

|                               |                         |                                                               | DoMode_[1:0] = 01<br>and t $\leq$ t <sub>INRUSH</sub>                                                                                                | 300              | 350                           | 400                                                                                                            |     |     |     |   |

|                               |                         | CL_[1:0] = 10, see<br>Table 2                                 | $\begin{array}{l} DoMode\_[1:0] = 01\\ and t > t_{INRUSH}, or\\ DoMode\_[1:0] = \\ 00, 10 \text{ or } 11 \text{ and } t\\ is don't care \end{array}$ | 300              | 350                           | 400                                                                                                            | mA  |     |     |   |

|                               |                         |                                                               | DoMode_[1:0] = 01<br>and t $\leq$ t <sub>INRUSH</sub>                                                                                                | 600              | 700                           | 800                                                                                                            |     |     |     |   |

| HS Current Limit              | CL_[                    | CL_[1:0] = 00, see<br><u>Table 2</u>                          | $\begin{array}{l} DoMode_[1:0] = 01\\ and t > t_{INRUSH}, or\\ DoMode_[1:0] = \\ 00, 10 \text{ or } 11 \text{ and } t\\ is don't care \end{array}$   | 600              | 700                           | 800                                                                                                            |     |     |     |   |

|                               |                         |                                                               | DoMode_[1:0] = 01<br>and t $\leq$ t <sub>INRUSH</sub>                                                                                                | 1.2              | 1.4                           | 1.6                                                                                                            |     |     |     |   |

|                               |                         |                                                               |                                                                                                                                                      |                  | CL_[1:0] = 11, see<br>Table 2 | DoMode_[1:0] = 01<br>and t > t <sub>INRUSH</sub> , or<br>DoMode_[1:0] =<br>00, 10 or 11 and t<br>is don't care | 1.2 | 1.4 | 1.6 | A |

|                               |                         |                                                               | DoMode_[1:0] = 01<br>and t $\leq$ t <sub>INRUSH</sub>                                                                                                | 2.4              | 2.8                           | 3.2                                                                                                            |     |     |     |   |

| LS Current Limit              | I <sub>CLIM_LS</sub>    | DO PP modes                                                   |                                                                                                                                                      | 150              | 200                           | 280                                                                                                            | mA  |     |     |   |

| DIGITAL INPUT (DOI_)          | . –                     | •                                                             |                                                                                                                                                      |                  |                               |                                                                                                                |     |     |     |   |

| Threshold Voltage             | V <sub>TH_DOI_DI</sub>  | DI mode, DOI_ rising                                          | 9                                                                                                                                                    | 6.7              |                               | 8.0                                                                                                            | V   |     |     |   |

| Hysteresis Voltage            | V <sub>HYS_DOI_DI</sub> | DI mode                                                       |                                                                                                                                                      |                  | 1.2                           |                                                                                                                | V   |     |     |   |

|                               | IDOI_DI_L               | DI mode, Typ2Di = 0                                           |                                                                                                                                                      | 0                |                               | 2.6                                                                                                            |     |     |     |   |

| Current Sink                  | IDOI_DI_H               | DI mode, Typ2Di = 0<br>V <sub>DOI</sub> _< V <sub>DD</sub> _  | ), 8V < V <sub>DOI</sub> _ < 40V,                                                                                                                    | 2.0              | 2.3                           | 2.6                                                                                                            | mA  |     |     |   |

|                               | IDOI_DI_L               | DI mode, Typ2Di = 1                                           | , 0V < V <sub>DOI</sub> _ < 5V                                                                                                                       | 0                |                               | 7.5                                                                                                            | ШA  |     |     |   |

|                               | IDOI_DI_H               | DI mode, Typ2Di = 1<br>V <sub>DOI</sub> _ < V <sub>DD</sub> _ | I, 8V < V <sub>DOI</sub> _ < 40V,                                                                                                                    | 6.0              | 7.0                           | 7.7                                                                                                            | 1   |     |     |   |

| LOGIC INTERFACE I/O           | 1                       | 1                                                             |                                                                                                                                                      |                  |                               |                                                                                                                |     |     |     |   |

| Input Voltage High            | VIH                     |                                                               |                                                                                                                                                      | $0.7 \times V_L$ |                               |                                                                                                                | V   |     |     |   |

| Input Voltage Low             | VIL                     |                                                               |                                                                                                                                                      |                  |                               | $0.3 	ext{ x V}_{L}$                                                                                           | V   |     |     |   |

| Input Threshold<br>Hysteresis | VIHYS                   |                                                               |                                                                                                                                                      |                  | 0.11 x<br>V <sub>L</sub>      |                                                                                                                | V   |     |     |   |

## Quad-Channel Industrial Digital Output/Digital Input

### **Electrical Characteristics (continued)**

| PARAMETER                                   | SYMBOL               | CONDITIONS                                                      | MIN                        | TYP | MAX                      | UNITS |

|---------------------------------------------|----------------------|-----------------------------------------------------------------|----------------------------|-----|--------------------------|-------|

| Input Pull-Down<br>Resistor                 | R <sub>IN_PD</sub>   | EN pin                                                          | 110                        | 200 | 260                      | kΩ    |

| Input Leakage                               | ILEAK                | $GND < V_{IN} < V_{L}$                                          | -1                         |     | +1                       | μA    |

| Output Logic High                           | V <sub>OH</sub>      | I <sub>LOAD</sub> = -5mA                                        | V <sub>L</sub> - 0.33      |     |                          | V     |

| Output Logic Low                            | V <sub>OL</sub>      | I <sub>LOAD</sub> = +5mA                                        |                            |     | 0.33                     | V     |

| Output Leakage D_                           | ILEAK_DOI            | DO modes                                                        | -1                         |     | +1                       | μA    |

| Output Leakage SDO                          | ILEAK_SDO            | CS is high                                                      | -1                         |     | +1                       | μA    |

| GATE DRIVER (G_)                            |                      |                                                                 |                            |     |                          |       |

| V <sub>DD</sub> Threshold for G_<br>Turn-on | V <sub>DDTH_G</sub>  | G_ driver clamp voltage to GND                                  | 43                         | 48  | 59                       | V     |

| G_ On Voltage                               | V <sub>ON_G</sub>    | DO modes, DOI_ $\leq$ V <sub>DD</sub> _                         | V <sub>DD_</sub> -<br>14   |     | V <sub>DD_</sub> -<br>10 | V     |

| G_ Off Switch<br>Resistance                 | R <sub>ON_G</sub>    | DI modes                                                        |                            | 50  |                          | Ω     |

| <b>OPEN-DRAIN OUTPUTS</b>                   | (FAULT, VDDO         | K, READY)                                                       |                            |     |                          |       |

| Output Logic Low<br>(FAULT, VDDOK)          | V <sub>ODL</sub>     | I <sub>LOAD</sub> = +5mA                                        |                            |     | 0.33                     | V     |

| Output Logic High<br>(READY)                | V <sub>ODH</sub>     | I <sub>LOAD</sub> = -5mA                                        | V <sub>L</sub> - 0.33      |     |                          | V     |

| Leakage (FAULT)                             | I <sub>ODL</sub>     | Open-drain output off, V <sub>OD</sub> = 5.5V                   | -1                         |     | +1                       | μA    |

| Leakage (VDDOK)                             | I <sub>ODL</sub>     | Open-drain output off, V <sub>OD</sub> = 40V                    | -5                         |     | +5                       | μA    |

| Leakage (READY)                             | I <sub>ODL</sub>     | Open-drain output off, V <sub>OD</sub> = GND                    | -1                         |     | +1                       | μA    |

| LED DRIVERS (L_, FLED                       | ), SLED)             |                                                                 |                            |     |                          |       |

| LED Supply Voltage                          | V <sub>LED</sub>     |                                                                 | 3.0                        |     | V <sub>DD</sub>          | V     |

| LED Supply Current                          | I <sub>LED</sub>     | $V_{LED}$ = 40V, SLED = Off, FLED = Off                         |                            |     | 1                        | μA    |

| L_ Voltage High                             | V <sub>OH_L</sub>    | L_ = On, I <sub>L</sub> _ = 5mA                                 | V <sub>LED</sub> -<br>0.33 |     |                          | v     |

| L_ Off Leakage Current                      | ILEAK_L              | $L_= Off, V_{L_} = 0V$                                          |                            |     | 5                        | μA    |

| SLED Output Voltage<br>Low                  | V <sub>OL_SLED</sub> | SLED = On, I <sub>SLED</sub> = 5mA                              |                            |     | 0.33                     | V     |

| SLED Off Leakage<br>Current                 | ILEAK_SLED           | SLED = Off, V <sub>SLED</sub> = V <sub>LED</sub>                |                            |     | 5                        | μA    |

| FLED Output Voltage<br>Low                  | VOL_FLED             | FLED = On, I <sub>FLED</sub> = 5mA                              |                            |     | 0.33                     | V     |

| FLED Off Leakage<br>Current                 | ILEAK_FLED           | FLED = Off, V <sub>FLED</sub> = V <sub>LED</sub>                |                            |     | 5                        | μA    |

| DO MODES PROPAGAT                           | ION DELAY (D_        | or SYNCH to DOI_)                                               |                            |     |                          |       |

| DOI Output Propagation<br>Delay Low-to-High | tPD_LH               | Delay from D_ (or SYNCH) to DOI_ rising by 0.5V, HS or PP modes |                            | 0.4 | 1.5                      | μs    |

## Quad-Channel Industrial Digital Output/Digital Input

### **Electrical Characteristics (continued)**

| PARAMETER                                   | SYMBOL                  | CONDITIONS                                                                                                                                 | MIN | TYP  | MAX | UNITS |

|---------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| DOI Output Propagation<br>Delay High-to-Low | <sup>t</sup> PD_HL      | Delay between D_ switching low (or SYNCH high) to DOI_falling by 0.5V, $V_{DD} = 24V$ , $R_L = 10k\Omega$ , $C_L = 0.1nF$ , HS or PP modes |     | 0.6  | 1.5 | μs    |

| DOI Output Rise Time                        | t <sub>R</sub>          | HS or PP modes, 20% to 80% $V_{DD}$ , $V_{DD\_}$ = 24V, $R_L$ = 10k $\Omega,~C_L$ = 0.1nF                                                  |     | 0.6  | 1.5 | μs    |

|                                             |                         | HS modes, 80% to 20% V <sub>DD</sub> , V <sub>DD</sub> = 24V, R <sub>L</sub> = 10k $\Omega$ , C <sub>L</sub> = 0.1nF                       |     | 1    |     |       |

| DOI Output Fall Time                        | t <sub>F</sub>          | PP modes, 80% to 20% V <sub>DD</sub> , V <sub>DD</sub> = 24V, R <sub>L</sub> = 10k $\Omega$ , C <sub>L</sub> = 0.1nF                       |     | 0.9  | 2   | μs    |

| DI MODES PROPAGATI                          | ON DELAY (DOI           | _ to D_)                                                                                                                                   |     |      |     | •     |

| Propagation Delay High-<br>to-Low           | <sup>t</sup> PD_HL_DI   | DI modes, SYNCH = high, delay from<br>DOI_ falling to 5V to D_ low                                                                         |     | 0.9  | 1.8 | μs    |

| Propagation Delay Low-<br>to-High           | <sup>t</sup> PD_LH_DI   | DI modes, SYNCH = high, delay from<br>DOI_ rising to 8V to D_ high                                                                         |     | 1.1  | 2   | μs    |

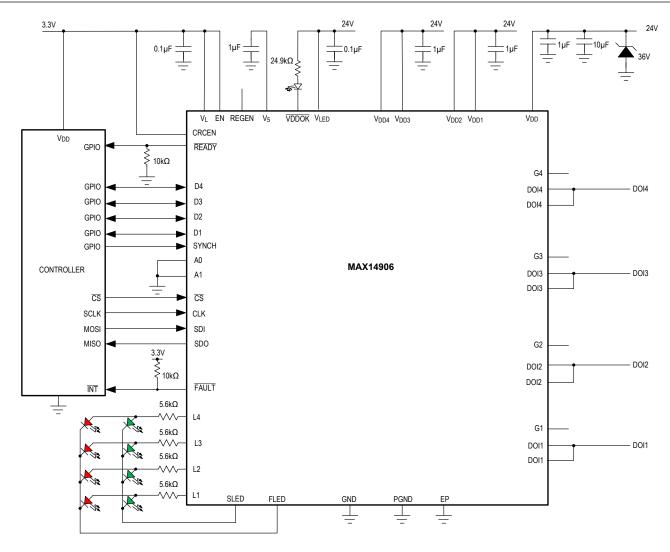

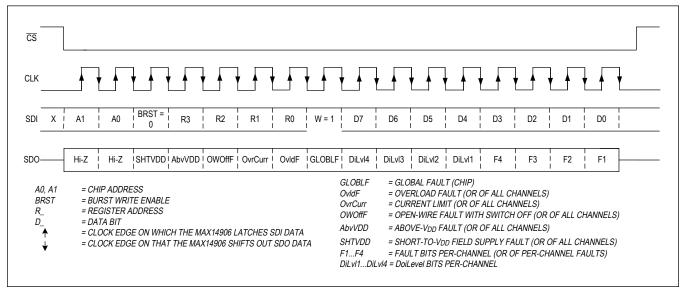

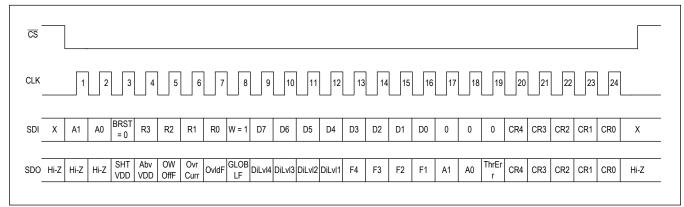

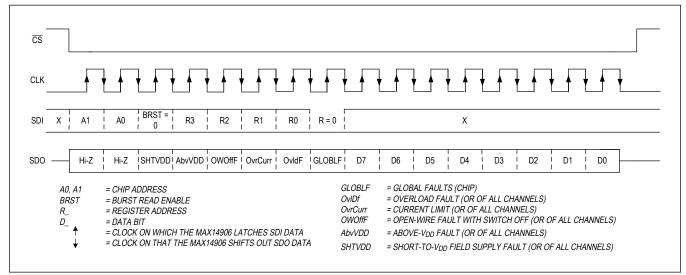

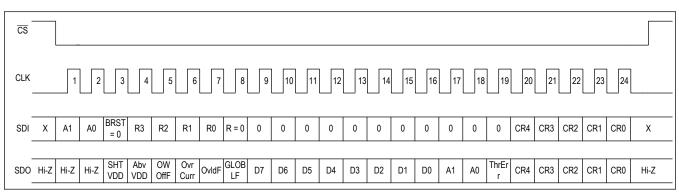

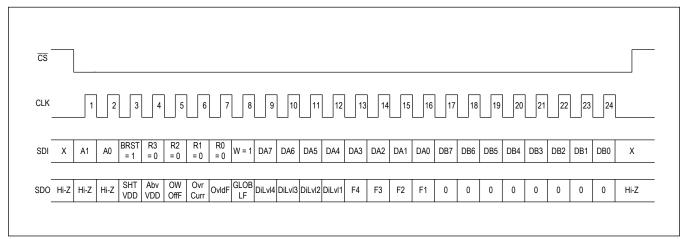

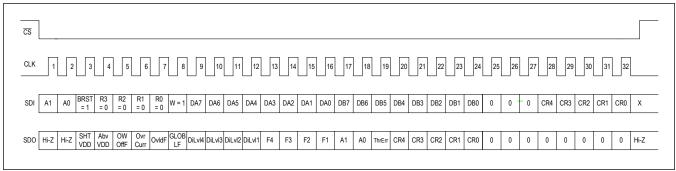

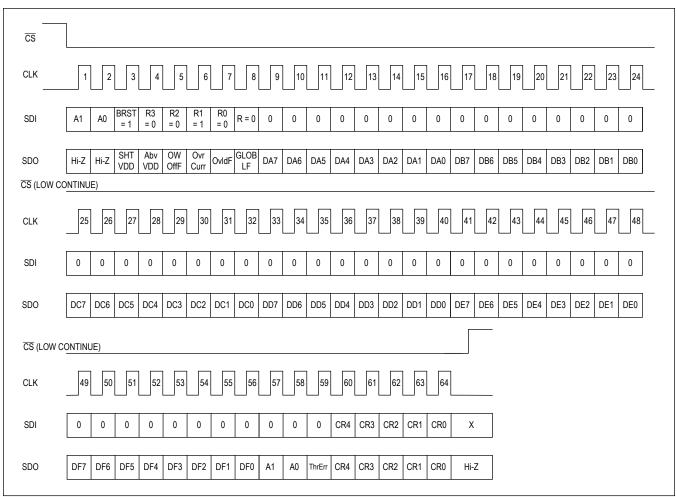

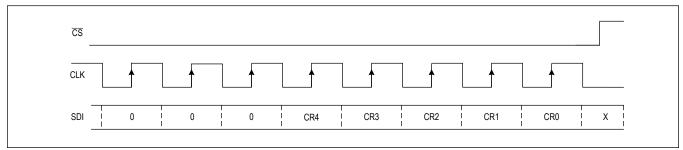

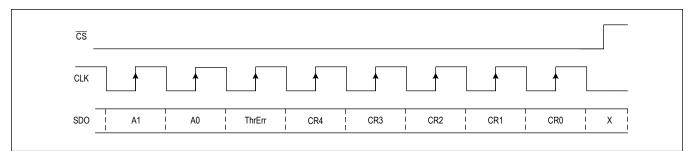

| SPI TIMING CHARACTE                         | RISTICS (Figure         | <u>1</u> )                                                                                                                                 |     |      |     |       |

| CLK Clock Period                            | t <sub>CLK</sub>        |                                                                                                                                            | 100 |      |     | ns    |

| CLK Pulse Width High                        | t <sub>CH</sub>         |                                                                                                                                            | 40  |      |     | ns    |

| CLK Pulse Width Low                         | t <sub>CL</sub>         |                                                                                                                                            | 40  |      |     | ns    |

| CS Fall to CLK Rise<br>Time                 | tcss                    |                                                                                                                                            | 40  |      |     | ns    |

| SDI Hold Time                               | t <sub>DH</sub>         |                                                                                                                                            | 10  |      |     | ns    |

| SDI Setup Time                              | t <sub>DS</sub>         |                                                                                                                                            | 10  |      |     | ns    |

| SDO Propagation Delay                       | tDO                     | C <sub>L</sub> = 10pF, CLK falling edge to SDO stable                                                                                      |     |      | 30  | ns    |

| SDO Rise and Fall<br>Times                  | t <sub>FT</sub>         | C <sub>L</sub> = 10pF                                                                                                                      |     | 1    |     | ns    |

| CS Hold Time                                | tCSH                    |                                                                                                                                            | 40  |      |     | ns    |

| CS Pulse Width High                         | t <sub>CSPW</sub>       |                                                                                                                                            | 40  |      |     | ns    |

| WATCHDOG TIMING CH                          | IARACTERISTIC           | S                                                                                                                                          |     |      |     |       |

|                                             |                         | WDTo = 01                                                                                                                                  |     | 200  |     |       |

| Watchdog Timeout                            | t <sub>WD</sub>         | WDTo = 10                                                                                                                                  |     | 600  |     | ms    |

|                                             |                         | WDTo = 11                                                                                                                                  |     | 1200 |     |       |

| Watchdog Timeout<br>Accuracy                | twd_acc                 | SynchWDEn = 1, see <u>Config2</u> register for watchdog timeout                                                                            | -30 |      | +30 | %     |

| LED MATRIX TIMING CH                        | HARACTERISTIC           | S                                                                                                                                          |     |      |     |       |

| LED Driver Scan Rate                        | fLED                    | Update rate for each LED                                                                                                                   |     | 1    |     | kHz   |

| THERMAL PROTECTION                          | N                       |                                                                                                                                            |     |      |     |       |

| Driver Thermal<br>Shutdown Temperature      | T <sub>JSHDN</sub>      | Junction temperature rising                                                                                                                |     | 170  |     | °C    |

| Driver Thermal<br>Shutdown Hysteresis       | T <sub>JSHDN_HYST</sub> |                                                                                                                                            |     | 15   |     | °C    |

## Quad-Channel Industrial Digital Output/Digital Input

### **Electrical Characteristics (continued)**

$(V_{DD} = V_{DD1} = V_{DD2} = V_{DD3} = V_{DD4} = +10V$  to +40V,  $V_{LED} = +3.0V$  to +40V,  $V_5 = +4.5V$  to +5.5V,  $V_L = +2.5V$  to +5.5V,  $T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ ,  $V_{DD} = V_{DD_-} = V_{LED} = +24V$ ,  $V_L = 3.3V$ , REGEN = Open, and  $V_5 = 5V$ .) (Note 2)

| PARAMETER                           | SYMBOL                      | CONDITIONS                                                                                           | MIN | TYP | MAX | UNITS |  |

|-------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|--|

| Chip Thermal Shutdown               | T <sub>CSHDN</sub>          | Temperature rising                                                                                   |     | 150 |     | °C    |  |

| Chip Thermal Shutdown<br>Hysteresis | T <sub>CSHDN_HYS</sub><br>T |                                                                                                      |     | 10  |     | °C    |  |

| LDO Thermal Shutdown                | T <sub>LDSHDN</sub>         |                                                                                                      |     | 165 |     | °C    |  |

| EMC PROTECTION                      |                             |                                                                                                      |     |     |     |       |  |

| ESD                                 |                             | DOI_ pin, IEC 61000-4-2, Contact<br>Discharge, add a 470pF capacitor on<br>each DOI_ to GND (Note 3) |     | ±8  |     |       |  |

|                                     | VESD                        | DOI_ pin, IEC 61000-4-2 Air-Gap<br>Discharge (Note 3)                                                |     | ±16 |     | kV    |  |

|                                     |                             | All pins, Human Body Model                                                                           |     | ±2  |     |       |  |

| Surge                               | V <sub>SURGE</sub>          | DOI_to PGND or Earth GND, IEC<br>61000-4-5 (42Ω/0.5μF) (Note 4)                                      |     | ±1  |     | kV    |  |

Note 2: All units are production tested at T<sub>A</sub> = +25°C. Specifications over temperature are guaranteed by design.

**Note 3:** Bypass  $V_{DD}$  and  $V_{DD}$  pins to GND with 1µF capacitor as close as possible to the device for high ESD protection. If an external transistor is used on  $\nabla_{DD}$ , place the FET as close to  $V_{DD}$  as possible with 1µF capacitor on the other side of the FET to PGND.

**Note 4:** At typical application value of  $V_{DD}$  = 24V with a TVS protection on  $V_{DD}$  to GND.

Figure 1. SPI Timing Diagram

# Quad-Channel Industrial Digital Output/Digital Input

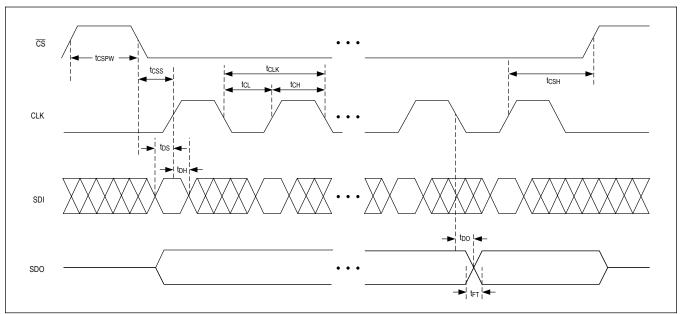

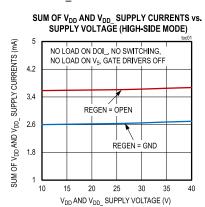

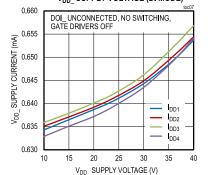

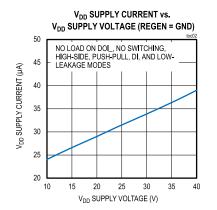

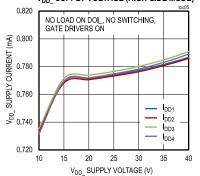

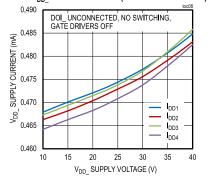

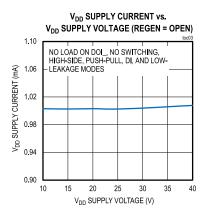

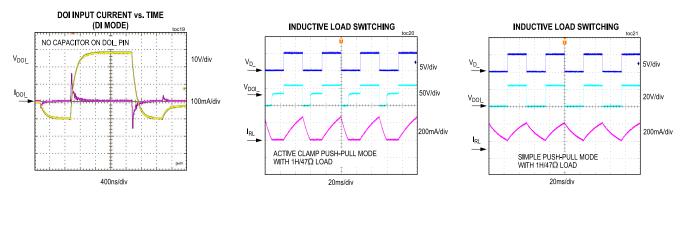

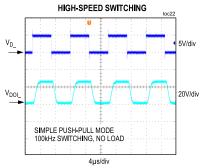

### **Typical Operating Characteristics**

$(V_{DD} = V_{DD_{-}} = V_{LED} = +24V, V_{L} = +5V, REGEN = GND, V_{5} = +5V, no load on V_{5}, T_{A} = +25^{\circ}C, unless otherwise noted.)$

20 25 30 35 40

10

15

V<sub>DD</sub>\_SUPPLY CURRENT vs. V<sub>DD</sub>\_SUPPLY VOLTAGE (DI MODE)

V<sub>DD</sub>\_SUPPLY VOLTAGE (V)

V<sub>DD</sub>\_SUPPLY CURRENT vs. V<sub>DD</sub>\_SUPPLY VOLTAGE (HIGH-SIDE MODE)

V<sub>DD</sub>\_SUPPLY CURRENT vs. V<sub>DD</sub>\_SUPPLY VOLTAGE (LOW-LEAKAGE MODE)

V<sub>DD</sub>\_SUPPLY CURRENT vs. V<sub>DD</sub>\_SUPPLY VOLTAGE (PUSH-PULL MODE)

$V_{DD}$ ,  $V_{DD}$  AND  $V_5$  SUPPLY CURRENTS vs. TEMPERATURE (HIGH-SIDE MODE)

# Quad-Channel Industrial Digital Output/Digital Input

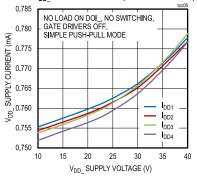

**Typical Operating Characteristics (continued)**

$(V_{DD} = V_{DD} = V_{LED} = +24V, V_L = +5V, REGEN = GND, V_5 = +5V, no load on V_5, T_A = +25^{\circ}C, unless otherwise noted.)$

# Quad-Channel Industrial Digital Output/Digital Input

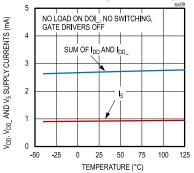

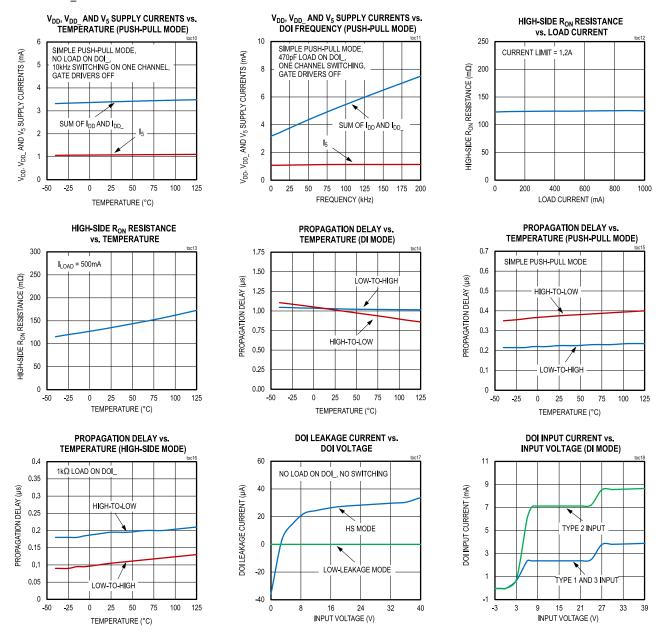

### **Typical Operating Characteristics (continued)**

$(V_{DD} = V_{DD} = V_{LED} = +24V, V_L = +5V, REGEN = GND, V_5 = +5V, no load on V_5, T_A = +25^{\circ}C, unless otherwise noted.)$

# Quad-Channel Industrial Digital Output/Digital Input

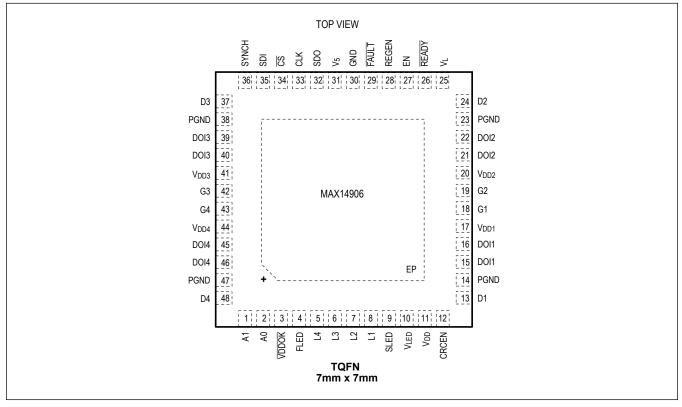

### **Pin Configuration**

#### MAX14906

# Quad-Channel Industrial Digital Output/Digital Input

# **Pin Description**

| PIN                                                        | NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPP                                                 | LY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11, 17, 20,<br>41, 44<br>VDD, VDD1,<br>VDD2, VDD3,<br>VDD4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply Voltage (Nominally 24V). If using a common $V_{DD}$ supply for all channels, connect all $V_{DD}$ together. $V_{DD}$ can also be independently supplied. Bypass $V_{DD}$ to GND using a 1µF capacitor. Bypass the $V_{DD}$ supplies on the same package side to GND using a shared 1µF capacitor. In order to allow DOI_ to go higher than $V_{DD}$ , an optional pMOS transistor can be used on $V_{DD}$ supply be the same package is a desired result. |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | supply. In this case connect a 1µF capacitor between its drain and PGND.                                                                                                                                                                                                                                                                                                                                                                                         |

| 30                                                         | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Logic/Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14, 23, 38, 47                                             | PGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power Ground. Connect all PGND pins together to GND                                                                                                                                                                                                                                                                                                                                                                                                              |

| 31                                                         | $V_5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Analog Supply Voltage/LDO Output. When REGEN is unconnected, the LDO is enabled and V <sub>5</sub> is a 5V supply output. If REGEN = GND, an external 5V supply has to be connected to V <sub>5</sub> . Bypass V <sub>5</sub> to GND using a 1 $\mu$ F ceramic capacitor.                                                                                                                                                                                        |

| 28                                                         | REGEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $V_5$ Regulator Enable Input. Leave REGEN unconnected for enabling/using the internal 5V regulator. Connect REGEN to GND to disable the internal regulator for powering $V_5$ from an external regulator.                                                                                                                                                                                                                                                        |

| 25                                                         | VL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Logic Reference Input. V <sub>L</sub> defines the levels on all I/O logic interface pins. Bypass V <sub>L</sub> to GND using a 0.1 $\mu$ F ceramic capacitor.                                                                                                                                                                                                                                                                                                    |

| —                                                          | EP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Exposed Pad. Connect the exposed pad to GND.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24V DIGITAL C                                              | OUTPUT/INPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15, 16                                                     | DOI1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Channel 1: High-Side/Push-Pull Output or Digital Input                                                                                                                                                                                                                                                                                                                                                                                                           |

| 21, 22                                                     | DOI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Channel 2: High-Side/Push-Pull Output or Digital Input                                                                                                                                                                                                                                                                                                                                                                                                           |

| 39, 40                                                     | DOI3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Channel 3: High-Side/Push-Pull Output or Digital Input                                                                                                                                                                                                                                                                                                                                                                                                           |

| 45, 46                                                     | DOI4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Channel 4: High-Side/Push-Pull Output or Digital Input                                                                                                                                                                                                                                                                                                                                                                                                           |

| LOGIC INTER                                                | ACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13                                                         | D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Logic I/O Pin. When channel 1 is in digital output mode, the D1 input switches the DOI1 output when SYNCH is high. When channel 1 is in digital input mode, the D1 output represents the logic state of the DOI1 input when SYNCH is high.                                                                                                                                                                                                                       |

| 24                                                         | D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Logic I/O Pin. When channel 2 is in digital output mode, the D2 input switches the DOI2 output when SYNCH is high. When channel 2 is in digital input mode, the D2 output represents the logic state of the DOI2 input when SYNCH is high.                                                                                                                                                                                                                       |

| 37                                                         | D3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Logic I/O Pin. When channel 3 is in digital output mode, the D3 input switches the DOI3 output when SYNCH is high. When channel 3 is in digital input mode, the D3 output represents the logic state of the DOI3 input when SYNCH is high.                                                                                                                                                                                                                       |

| 48                                                         | D4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Logic I/O Pin. When channel 4 is in digital output mode, the D4 input switches the DOI4 output when SYNCH is high. When channel 4 is in digital input mode, the D4 output represents the logic state of the DOI4 input when SYNCH is high.                                                                                                                                                                                                                       |

| 36                                                         | 36       SYNCH       SYNCH Control Input. When DOI_ are configured as digital outputs, they are updated simultaneously on the rising SYNCH edge, as determined by the contents of the SetOUT or the D_ input pins. The DOI_ output states do not change when SYNCH is held low. Wh SYNCH is high, the DOI_ output states change immediately when a new value is written is SetOUT register or the associated D_ input pin.         All DOI_ logic levels (both in DO and DI modes) are read and latched on the falling SYNCH is here suits are stored in the DoiLevel register and the D_ output pins if the DOI_ channel |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 27                                                         | EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | configured in DI mode.         DOI Enable Pin. Drive the EN pin high to enable the DOI_ outputs. Drive EN low to disable/three-state all DOI_ outputs.                                                                                                                                                                                                                                                                                                           |

# Quad-Channel Industrial Digital Output/Digital Input