#### **MAX14813**

# Ultra-Compact Octal 3L/Quad 5L Pulser with T/R Switches and Beamforming Capability

#### **General Description**

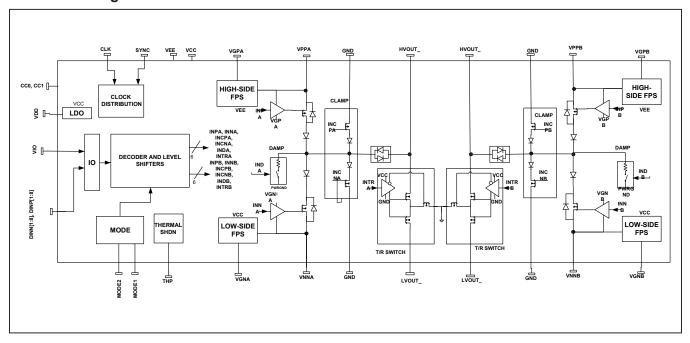

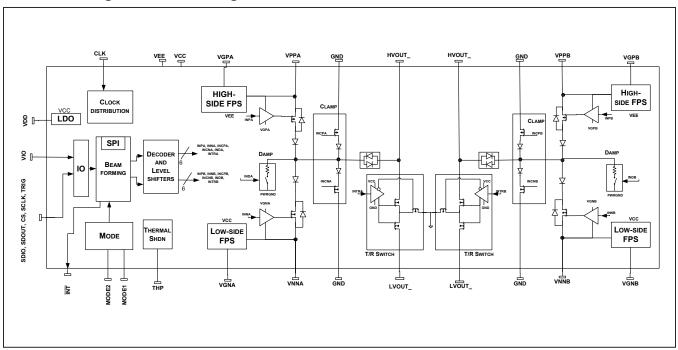

The MAX14813 is a very high density, high-voltage ultrasound transmitter (pulser) in a wafer-level package (WLP). It is particularly aimed to address ultrasound imaging applications in which PCB space is a concern.

It features eight 3-level channels operating from two independent pairs of HV supplies. Each channel can transmit up to  $170V_{P-P}$  with up to 2.1A current capability. The current capability can be programmed down to 0.35A with 4 steps of programmability. It also features an integrated 1A active clamp (Return to Zero).

The MAX14813 can also be configured as a quad 5-levels (2.1A) pulser plus quad active T/R switches.

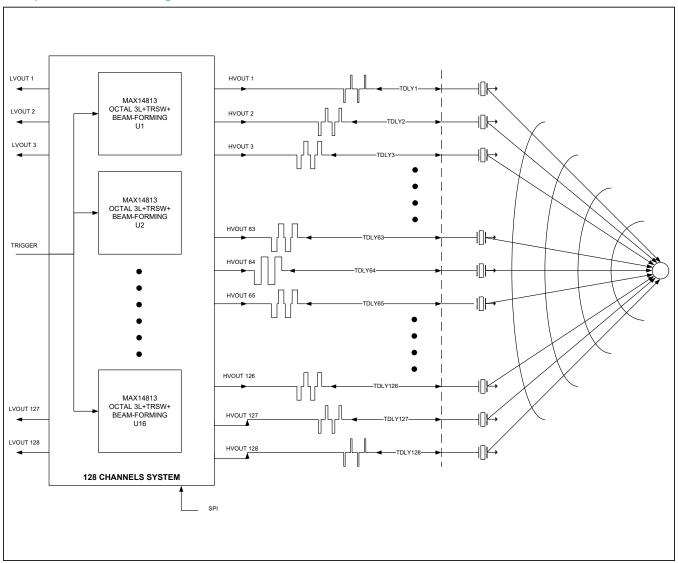

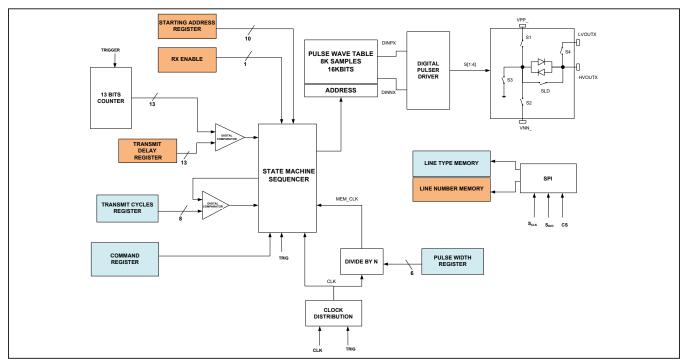

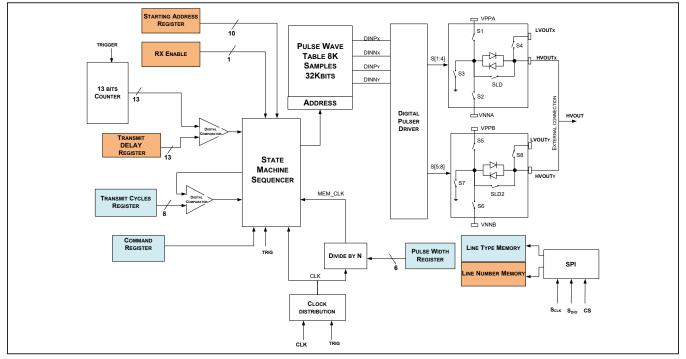

The MAX14813 features embedded digital resources (SRAM and state machine) that can be used to support transmit beamforming resulting in a dramatic saving of the number of interconnects and FPGA I/Os. The embedded digital resources are programmed through an high speed serial interface and supports sophisticated transmit techniques likewise pulse width modulation for burst-shaping and apodization for beam shaping.

Alternatively, the device can be controlled in a conventional manner by an external digital source (FPGA or similar) through dedicated CMOS logic inputs.

The MAX14813 features independent active T/R switches. The T/R switches can possibly be externally configured to support Receive Multiplexing in which a fewer number of receive than transmit channels are used.

The MAX14813 is packaged into a 6.33mm x 6.65mm WLP, with a  $12 \times 13$  ball grid array.

### **Applications**

- Ultrasound Medical Imaging

- Ultrasound Industrial Applications (NDT)

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Optimized for Compact and Portable Applications

- High Density Eight Channels 3 Levels Pulser in a 6.33mm x 6.65mm WLP

- Integrated Low-Power, Low-Noise, Active T/R Switches

- Direct-Drive Architecture Eliminates External Floating Power Supply (FPS) and HV Signal Capacitors

- Embedded Beamforming Eliminates Transmit FPGA, Simplifies PCB Layout, and Eases Synchronization

- Flexibility

- · Support Receive Multiplexing

- Can Use Internal/External Beamforming Resources

- Can Operate as Octal 3 Levels or Quad 5 Levels

- Embedded Digital Resources for Beamforming

- 8K Samples (Per Channel) Pulse Wave Table SRAM Stores Up to 1024 Unique Patterns

- Line Number Memory Stores Beamforming Line Information For Up To 1.5K Lines (3 Levels) or 3K Lines (5 Levels)

- 128 Line Type Registers Stores Setting Information for All the Channels

- State Machine for Delay Beamforming with 5ns Time Resolution

- Programmable Number of Cycles and Pattern Time Base (Pulse Width)

- High Performance (Designed to Enhance Image Quality)

- Excellent Second Harmonic distortion and Pulse Inversion Performances

- Low Propagation Delay 12ns (typ) Ensures Excellent Phase Noise for Doppler Modes and Excellent Part-to-Part Matching

- Fast Rising Falling Edges Enables Fine Resolution PWM or Acoustic Power Control

- Low Power

- Low Quiescent Power Dissipation (4.1mW/Channel in Octal Mode)

- Programmable Current Capability Down to 0.35A for CWD and Low-Voltage Modes

- Robustness

- Thermal Warning at 110°C

- Thermal Shutdown at 150°C

# **Simplified Block Diagram**

### **Absolute Maximum Ratings**

| V <sub>IO</sub> to GND0.3V to +5.6V                                       | THP to GND0.3V to +5.6V                  |

|---------------------------------------------------------------------------|------------------------------------------|

| V <sub>DD</sub> to GND0.3V to +2V                                         | DINNx to GND (x = 18)0.3V to +5.6V       |

| V <sub>CC</sub> to GND0.3V to +5.6V                                       | DINPx to GND (x = 18)0.3V to +5.6V       |

| V <sub>EE</sub> to GND5.6V to +0.3V                                       | MODE2 to GND0.3V to +5.6V                |

| V <sub>PPA</sub> to GND0.3V to +110V                                      | MODE1 to GND0.3V to +5.6V                |

| V <sub>NNA</sub> to GND110V to +0.3V                                      | CLK to GND0.3V to +5.6V                  |

| V <sub>NNB</sub> to GNDV <sub>NNA</sub> - 0.3V to +0.3V                   | SYNC/INT to GND0.3V to +5.6V             |

| V <sub>PPB</sub> to GND0.3V to V <sub>PPA</sub> + 0.3V                    | CC0 to GND0.3V to V <sub>IO</sub> + 0.3V |

| V <sub>GNB</sub> to GNDV <sub>NNB</sub> - 0.3V to V <sub>NNB</sub> + 5.6V | CC1 to GND0.3V to V <sub>IO</sub> + 0.3V |

| V <sub>GPA</sub> to GNDV <sub>PPA</sub> - 5.6V to V <sub>PPA</sub> + 0.3V | Operating Temperature Range0°C to +85°C  |

| V <sub>GNA</sub> to GNDV <sub>NNA</sub> - 0.3V to V <sub>NNA</sub> + 5.6V | Storage Temperature Range65°C to +150°C  |

| V <sub>GPB</sub> to GNDV <sub>PPB</sub> - 5.6V to V <sub>PPB</sub> + 0.3V | Soldering Temperature (Reflow)+260°C     |

| HVOUTx to GND (x = 18) $V_{NNA}$ - 0.6V to $V_{PPA}$ + 0.6V               |                                          |

| LVOUTx to GND (x = 18) –                                                  |                                          |

| Current Limited at ±100mA1V to +1V                                        |                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### WLP156 6.65mm x 6.33mm

| PACKAGE CODE                           | W1566A6+1                 |

|----------------------------------------|---------------------------|

| Outline Number                         | <u>21-100007</u>          |

| Land Pattern Number                    | See Application Note 1891 |

| Thermal Resistance, Four-Layer Board:  |                           |

| Junction to Ambient (θ <sub>JA</sub> ) | 19                        |

| Junction to Case (θ <sub>JC</sub> )    | NA                        |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

(V<sub>CC</sub> = 5V±5%, V<sub>EE</sub> = -5V ±5%, V<sub>PPA</sub> = +85V, V<sub>NNA</sub> = -85V, V<sub>PPB</sub> = +85V, V<sub>NNB</sub> = -85V, VIO = +1.7V to +3.3V, Direct Mode,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted, Typical values are VIO = +2.5V,  $T_{CC}$  = - $T_{CC}$  = 5V,  $T_{CC}$  = - $T_{CC}$  = 5V,  $T_{CC}$  = -V<sub>EE</sub> = 5V,  $T_{CC}$  = 0V,  $T_{CC}$  =

| PARAMETER                                                                              | SYMBOL            | CONDITIONS                                                                                          | MIN                    | TYP  | MAX                    | UNITS |

|----------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------|------------------------|------|------------------------|-------|

| OPERATING VOLTAGE RA                                                                   | TING              |                                                                                                     |                        |      |                        |       |

| I/O Logic Supply Voltage                                                               | V <sub>IO</sub>   |                                                                                                     | 1.7                    |      | 3.3                    | V     |

| Positive Drive Supply Voltage                                                          | V <sub>CC</sub>   | 4.75 5 5.25                                                                                         |                        | 5.25 | V                      |       |

| Negative Drive Supply<br>Voltage                                                       | V <sub>EE</sub>   |                                                                                                     | -5.25                  | -5   | -4.75                  | V     |

| High-side Supply Voltage                                                               | $V_{PPA}$         |                                                                                                     | 0                      |      | 85                     | V     |

| nigh-side Supply Voltage                                                               | $V_{PPB}$         |                                                                                                     | 0                      |      | V <sub>PPA</sub>       | V     |

| Low-side Supply Voltage                                                                | $V_{NNA}$         |                                                                                                     | -85                    |      | 0                      | V     |

| Low-side Supply Voltage                                                                | V <sub>NNB</sub>  |                                                                                                     | V <sub>NNA</sub>       |      | 0                      | V     |

| LOGIC I/O PINS SPECIFICA                                                               | ATIONS            |                                                                                                     |                        |      |                        |       |

| Low-level Input                                                                        | $V_{IL}$          |                                                                                                     |                        |      | 0.33 x V <sub>IO</sub> | V     |

| High-level Input                                                                       | $V_{IH}$          |                                                                                                     | 0.66 x V <sub>IO</sub> |      |                        | V     |

| Logic Input Pulldown<br>Resistor                                                       | R <sub>IN</sub>   | Pins: MODE_, CC_, CLK                                                                               | 70                     | 100  | 130                    | ΚΩ    |

| Logic Input Pulldown<br>Resistor                                                       | R <sub>IN</sub>   | Pin SYNC                                                                                            | 40                     | 60   | 80                     | ΚΩ    |

| Logic Input Differential<br>Resistor                                                   | R <sub>DIFF</sub> | PINS: INNx, INPx                                                                                    | 70                     | 100  | 130                    | kΩ    |

| Input Leakage on Logic Inputs Pins                                                     | I <sub>LEAK</sub> | All logic input pins aside MODE_, SYNC, CLK, CC_<br>Logic Input connected to V <sub>IO</sub> or GND | -1                     |      | 1                      | μA    |

| Low Level Output Voltage<br>pins THP (All Modes) and<br>INT (Beamforming Mode<br>Only) | V <sub>OL</sub>   | R <sub>PULLUP</sub> = 1kΩ                                                                           |                        |      | 0.1 x V <sub>IO</sub>  | V     |

| Logic Input Capacitance                                                                | C <sub>IN</sub>   |                                                                                                     |                        | 4    |                        | pF    |

| CURRENT CONSUMPTION                                                                    | I SHUTDOWN I      | MODE                                                                                                |                        |      |                        |       |

| VIO Supply Current                                                                     | I <sub>IO</sub>   | All Inputs connected to GND or V <sub>IO</sub> .                                                    |                        | 5    | 12                     | μΑ    |

| V <sub>EE</sub> Supply Current                                                         | I <sub>EE</sub>   | All Inputs connected to GND or V <sub>IO</sub> .                                                    |                        | 10   | 20                     | μΑ    |

| V <sub>CC</sub> Supply Current                                                         | Icc               | All Inputs connected to GND or V <sub>IO</sub> .                                                    |                        | 70   | 120                    | μΑ    |

| V <sub>NN</sub> Supply Current                                                         | I <sub>NN</sub> _ | All Inputs connected to GND or V <sub>IO</sub> .                                                    |                        | 0    | 5                      | μA    |

| V <sub>PP</sub> Supply Current                                                         | I <sub>PP</sub> _ | All Inputs connected to GND or V <sub>IO</sub> .                                                    |                        | 0    | 5                      | μA    |

| Total Power Dissipation in Shutdown                                                    |                   | Shutdown Mode. Total power dissipation (8 channels)                                                 |                        | 0.4  |                        | mW    |

### **Electrical Characteristics (continued)**

$(V_{CC}=5V\pm5\%,~V_{EE}=-5V~\pm5\%,~V_{PPA}=+85V,~V_{NNA}=-85V,~V_{PPB}=+85V,~V_{NNB}=-85V,~V_{IO}=+1.7V~to~+3.3V,~Direct~Mode,~T_A=T_{MIN}~to~T_{MAX},~unless~otherwise~noted,~Typical~values~are~VIO=+2.5V,~V_{CC}=-V_{EE}=5V,~V_{PP}=V_{NN}=+85V,~T_A=+25^{\circ}C,~Limits~are~100\%~tested~at~T_A=+85^{\circ}C~and~guaranteed~by~design~in~the~entire~temperature~range,~CC0=0V,~CC1=0V,~SYNC=0V,~HVOUT~Load=1K\Omega//220pF~)$

| PARAMETER                                                                                | PARAMETER SYMBOL CONDITIONS       |                                           | MIN         | TYP        | MAX | UNITS |

|------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------|-------------|------------|-----|-------|

| OPERATING CURRENT CO                                                                     | NSUMPTION/                        | QUIESCENT-Direct-Mode Octal 3 Levels      |             |            |     |       |

| V <sub>IO</sub> Supply Current - Quiescent I <sub>IOQ</sub> All channels in receive mode |                                   |                                           |             | 5          | 12  | μA    |

| V <sub>EE</sub> Supply Current -<br>Quiescent                                            | I <sub>EEQ</sub>                  | All channels in receive mode              |             | 210        | 350 | μA    |

| V <sub>CC</sub> Supply Current - Quiescent                                               | I <sub>CCQ</sub>                  | All channels in receive mode              |             | 350        | 540 | μA    |

| V <sub>NN</sub> Total Supply Current -<br>Quiescent                                      | I <sub>NNQ</sub>                  | All channels in receive mode              |             | 150        | 250 | μA    |

| V <sub>PP</sub> Total Supply Current -<br>Quiescent                                      | I <sub>PPQ</sub>                  | All channels in receive mode              |             | 150        | 250 | μA    |

| Total Quiescent Power Dissipation per Channel                                            | P <sub>DIS1</sub>                 | Receive mode. Quiescent power per channel |             | 4.1        |     | mW    |

| OPERATING CURRENT CO                                                                     | NSUMPTION/                        | CWD MODE-Normal Drop-Direct Mode Oc       | tal 3 Level | s (Note 2) |     | -     |

| V <sub>IO</sub> Supply Current                                                           | I <sub>IO1</sub>                  | 8 chs running CW mode                     |             | 60         | 100 | μA    |

| V <sub>EE</sub> Supply Current                                                           | I <sub>EE1</sub>                  | 8 chs running CW mode                     |             | 8.8        | 13  | mA    |

| V <sub>CC</sub> Supply Current                                                           | I <sub>CC1</sub>                  | 8 chs running CW mode                     |             | 7.9        | 11  | mA    |

| V <sub>NN</sub> Supply Current                                                           | I <sub>NN1</sub>                  | 8 chs running CW mode                     |             | 90         | 130 | mA    |

| V <sub>PP</sub> Supply Current                                                           | I <sub>PP1</sub>                  | 8 chs running CW mode                     |             | 90         | 130 | mA    |

| Total CWD Power Dissipation per Channel                                                  | $P_{dCW}$                         | CWD Normal power per channel              |             | 122        |     | mW    |

| OPERATING CURRENT CO                                                                     | NSUMPTION/                        | CWD MODE-Low Drop-Beamforming Mod         | e (Note 3)  |            |     |       |

| VIO Supply Current                                                                       | I <sub>IO2</sub>                  | 8 chs running CW mode                     |             | 6          | 12  | μA    |

| V <sub>EE</sub> Supply Current                                                           | I <sub>EE2</sub>                  | 8 chs running CW mode                     |             | 8.8        | 13  | mA    |

| V <sub>CC</sub> Supply Current                                                           | I <sub>CC2</sub>                  | 8 chs running CW mode                     |             | 10.4       | 14  | mA    |

| V <sub>NN</sub> Supply Current                                                           | I <sub>NN2</sub>                  | 8 chs running CW mode                     |             | 83         | 120 | mA    |

| V <sub>PP</sub> Supply Current                                                           | I <sub>PP2</sub>                  | 8 chs running CW mode                     |             | 83         | 120 | mA    |

| Total CWD Power<br>Dissipation per channel                                               | $P_{dCW}$                         | CWD Low drop power per channel            |             | 95         |     | mW    |

| OPERATING CURRENT CO                                                                     | NSUMPTION A                       | B MODE-Direct Mode Octal 3 Levels (Not    | e 4)        |            |     |       |

| V <sub>IO</sub> Supply Current                                                           | I <sub>IO3</sub>                  | 8 chs running B-mode                      |             | 6          | 12  | μA    |

| V <sub>EE</sub> Supply Current                                                           | I <sub>EE3</sub>                  | 8 chs running B-mode                      |             | 0.25       | 0.6 | mA    |

| V <sub>CC</sub> Supply Current                                                           | I <sub>CC3</sub>                  | 8 chs running B-mode                      |             | 0.4        | 0.9 | mA    |

| V <sub>NN</sub> Supply Current                                                           | I <sub>NN3</sub>                  | 8 chs running B-mode                      |             | 2.9        | 4.6 | mA    |

| V <sub>PP</sub> Supply Current                                                           | I <sub>PP3</sub>                  | 8 chs running B-mode                      |             | 2          | 3   | mA    |

| Total B Mode Power<br>Dissipation per Channel                                            | r PdB B-mode power per channel 62 |                                           |             |            |     | mW    |

### **Electrical Characteristics (continued)**

$(V_{CC}=5V\pm5\%,~V_{EE}=-5V~\pm5\%,~V_{PPA}=+85V,~V_{NNA}=-85V,~V_{PPB}=+85V,~V_{NNB}=-85V,~V_{IO}=+1.7V~to~+3.3V,~Direct~Mode,~T_A=T_{MIN}~to~T_{MAX},~unless~otherwise~noted,~Typical~values~are~VIO=+2.5V,~V_{CC}=-V_{EE}=5V,~V_{PP}=V_{NN}=+85V,~T_A=+25^{\circ}C,~Limits~are~100\%~tested~at~T_A=+85^{\circ}C~and~guaranteed~by~design~in~the~entire~temperature~range,~CC0=0V,~CC1=0V,~SYNC=0V,~HVOUT~Load=1K\Omega//220pF~)$

| PARAMETER                                                              | PARAMETER SYMBOL CONDITIONS |                                                          | MIN  | TYP | MAX  | UNITS |

|------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------|------|-----|------|-------|

| HVOUT - LVOUT PIN CHAP                                                 | RACTERISTIC                 |                                                          |      |     |      |       |

| Small-Signal Total Parasitic Capacitor on HVOUT                        | CHVOUTSS                    | Vs = 100mV <sub>P-P</sub> . T/R switch ON                |      | 30  |      | pF    |

| Equivalent Large-Signal<br>Parasitic Capacitor on<br>HVOUT             | CHVOUTLS                    | Vs = 200V <sub>P-P</sub> (Note 5)                        |      | 55  |      | pF    |

| Bleed Resistor on HVOUT                                                | R <sub>BLEED</sub>          | T/R switch OFF                                           | 15   | 27  | 38   | ΚΩ    |

| Bleed Resistor on LVOUT                                                | R <sub>BLEED</sub>          | Small signal. T/R switch off.                            | 33   | 55  | 67   | ΚΩ    |

| THERMAL PROTECTION S                                                   | PECIFICATION                | IS                                                       |      |     |      |       |

| Thermal warning Threshold                                              | THP                         |                                                          |      | 110 |      | °C    |

| Thermal Warning<br>Hysteresis                                          | T <sub>HYS</sub>            |                                                          |      | 5   |      | °C    |

| Thermal Shutdown<br>Threshold                                          | T <sub>SHD</sub>            |                                                          |      | 150 |      | °C    |

| Thermal Shutdown<br>Hysteresis                                         | T <sub>HYS</sub>            |                                                          |      | 20  |      | °C    |

| 1.8V LDO                                                               |                             |                                                          |      |     |      |       |

| LDO Output Voltage                                                     | V <sub>DD</sub>             | Quiescent                                                | 1.72 | 1.8 | 1.87 | V     |

| LDO Dropout                                                            | Drop                        | I = 20mA                                                 |      | 2.5 |      | mV    |

| FUNCTIONAL TIMINGS (N                                                  | ote 7)                      |                                                          |      |     |      |       |

| Output Enable Time From<br>Shutdown Mode to Any<br>Other Mode          | T <sub>EN</sub>             |                                                          |      |     | 0.5  | ms    |

| Output Disable Time From<br>Any Other Mode to<br>Shutdown Mode         | TDI                         |                                                          | 0.5  |     | 3    | μs    |

| Time From One Operating<br>Mode to Any Other Mode<br>(Except Shutdown) | T <sub>MODE</sub>           | From MODE [2:1] change to entering in new operating mode | 0.5  |     | 3    | μs    |

| Transmit Setup Time<br>(Direct Mode)                                   | T <sub>SETTX</sub>          | From T/R switch off to start of transmission (Note 6)    | 0.8  |     |      | μs    |

| FUNCTIONAL TIMINGS (N                                                  | ote 7)/Beamfori             | ming Mode Timings                                        |      |     |      |       |

| Master Clock Frequency                                                 | Fmax                        |                                                          |      |     | 200  | MHz   |

| Master Clock Input Duty<br>Cycle                                       | Ckduty                      |                                                          | 40   |     | 60   | %     |

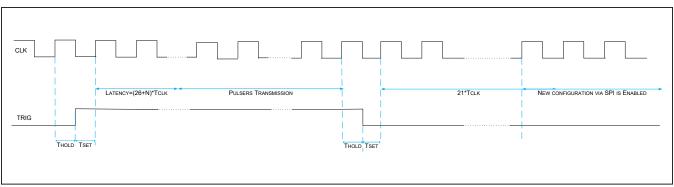

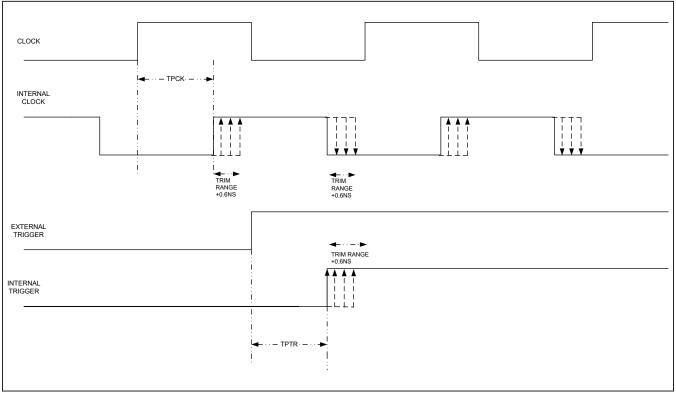

| TRIG to CLK Setup Time                                                 | Tset                        | Beamforming mode only.                                   | 1.25 |     |      | ns    |

| TRIG to CLK Hold Time                                                  | Thold                       | Beamforming mode only.                                   | 1.25 |     |      | ns    |

### **Electrical Characteristics (continued)**

$(V_{CC}=5V\pm5\%,~V_{EE}=-5V~\pm5\%,~V_{PPA}=+85V,~V_{NNA}=-85V,~V_{PPB}=+85V,~V_{NNB}=-85V,~V_{IO}=+1.7V~to~+3.3V,~Direct~Mode,~T_A=T_{MIN}~to~T_{MAX},~unless~otherwise~noted,~Typical~values~are~VIO=+2.5V,~V_{CC}=-V_{EE}=5V,~V_{PP}=V_{NN}=+85V,~T_A=+25^{\circ}C,~Limits~are~100\%~tested~at~T_A=+85^{\circ}C~and~guaranteed~by~design~in~the~entire~temperature~range,~CC0=0V,~CC1=0V,~SYNC=0V,~HVOUT~Load=1K\Omega//220pF~)$

| PARAMETER                                                  | SYMBOL             | CONDITIONS                                                         | MIN  | TYP | MAX | UNITS |  |  |  |

|------------------------------------------------------------|--------------------|--------------------------------------------------------------------|------|-----|-----|-------|--|--|--|

| FUNCTIONAL TIMINGS (Note 7)/Direct Mode Functional Timings |                    |                                                                    |      |     |     |       |  |  |  |

| Master Clock Frequency                                     | F <sub>MAX</sub>   |                                                                    |      |     | 200 | MHz   |  |  |  |

| Master Clock Input Duty<br>Cycle                           | CK <sub>DUTY</sub> |                                                                    | 40   |     | 60  | %     |  |  |  |

| Data to CLK Setup Time                                     | T <sub>SET</sub>   |                                                                    | 1.25 |     |     | ns    |  |  |  |

| Data to CLK Hold Time                                      | T <sub>HOLD</sub>  |                                                                    | 1.25 |     |     | ns    |  |  |  |

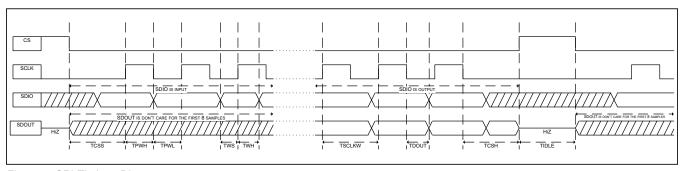

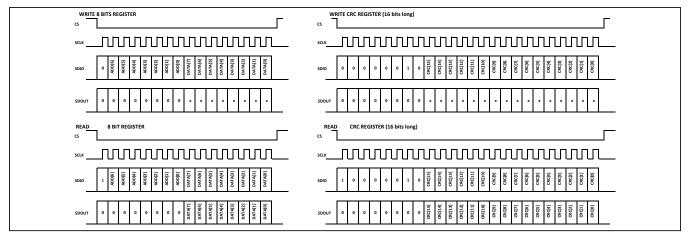

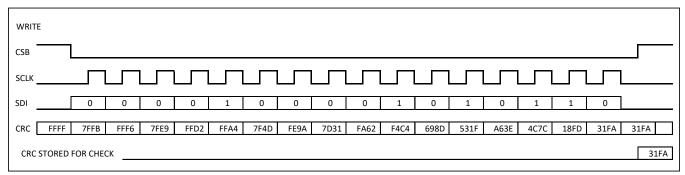

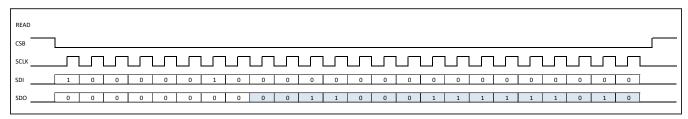

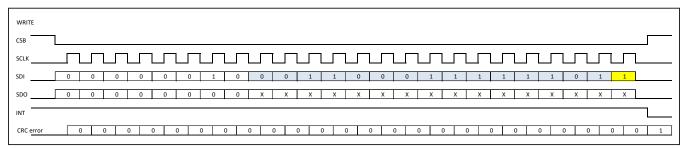

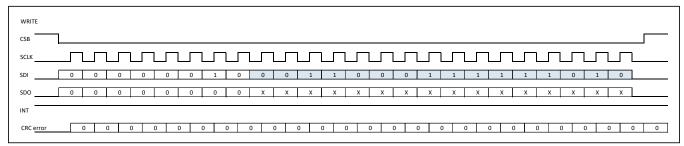

| SPI-(Beamforming Mode C                                    | Only)              |                                                                    |      |     |     |       |  |  |  |

| SCLK Write Period                                          | T <sub>SCLKW</sub> | Beamforming mode only. Serial Data Write.                          | 20   |     |     | ns    |  |  |  |

| SDIO to SCLK Setup Time                                    | t <sub>WS</sub>    | Beamforming mode only. Serial Data Write.                          | 5    |     |     | ns    |  |  |  |

| SDIO to SCLK Hold Time                                     | t <sub>WH</sub>    | Beamforming mode only. Serial Data Write                           | 5    |     |     | ns    |  |  |  |

| SCLK to CS Setup Time                                      | T <sub>CSS</sub>   | Beamforming mode only                                              | 5    |     |     | ns    |  |  |  |

| SCLK to CS Hold Time                                       | T <sub>CSH</sub>   | Beamforming mode only                                              | 5    |     |     | ns    |  |  |  |

| SCLK to SDIO Output<br>Data Delay at 2.5V                  | SDIOdly            | Beamforming mode only. Serial Data Read. C <sub>LOAD</sub> = 15pF. | 7    | 14  | 22  | ns    |  |  |  |

| SCLK to SDO Output Data<br>Delay at 2.5V                   | SDOdly             | Beamforming Mode only. Serial Data Read. C <sub>LOAD</sub> = 15pF. | 7    | 14  | 22  | ns    |  |  |  |

| CS Min High Level Interval                                 | T <sub>IDLE</sub>  | From CS rising edge to CS falling edge                             | 5    |     |     | ns    |  |  |  |

| SCLK Pulse-Width High                                      | T <sub>PWH</sub>   |                                                                    | 9    |     |     | ns    |  |  |  |

| SCLK pulse width low                                       | $T_{PWL}$          |                                                                    | 9    |     |     | ns    |  |  |  |

- **Note 1:** All devices are 100% production tested at T<sub>A</sub> = +85C. Limits over the operating temperature range are guaranteed by design.

- Note 2: CWD Mode 1: Continuous Wave Doppler, f = 5MHz,  $V_{IO}$  = +2.5V, Direct mode, CC0 = CC1 = 1,  $V_{PPB}$  = - $V_{NNB}$  = +5V. Load:  $1K\Omega//220pF$ . Normal Drop mode.

- Note 3: CWD Mode 2: Continuous Wave Doppler, f = 5MHz,  $V_{IO}$  = +2.5V, Beamforming–Low Drop Mode, CC0 = CC1 =1 ,  $V_{PPB}$  = - $V_{NNB}$  = +4V. Load:1K $\Omega$ //220pF.

- Note 4: B mode: Direct mode, CC0 = CC1 = 0, f = 5MHz, PRF = 5KHz, 1 period,  $V_{IO}$  = +2.5V,  $V_{PP}$  = - $V_{NN}$  = +85V. Load: 1K $\Omega$ //220pF.

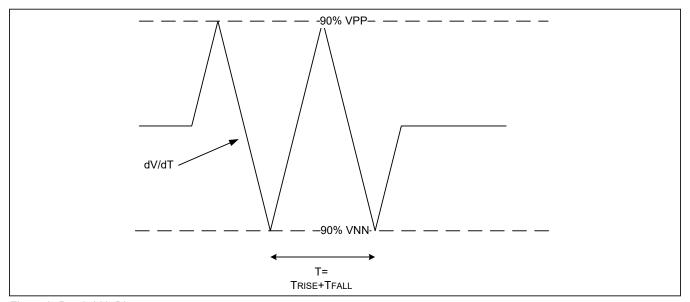

- Note 5: The equivalent high signal output capacitance (CHS) is calculated as the ratio between the pulser output current (I<sub>OLS</sub> and I<sub>OHS</sub>) and the output slew rate at 0V when the pulser is not loaded.

- C = IO/(dV/dt) at 0V

- **Note 6:** Both the T/R switch and Damp are designed to be self-protected against the HV transmission. The part is not damaged even if the Transmit setup time is not respected.

- Note 7: Setup/hold timings as well as the maximum frequency specifications, assume input rise/fall edges (from 20% to 80%) faster than 0.6ns.

#### **Electrical Characteristics—Pulser**

(V<sub>CC</sub> = 5V±5%, V<sub>EE</sub> = -5V ±5%, V<sub>PPA</sub> = +85V, V<sub>NNA</sub> = -85V, V<sub>PPB</sub> = +85V, V<sub>NNB</sub> = -85V, VIO = +1.7V to +3.3V, Direct Mode, CC0 = 0V, CC1 = 0V, SYNC = 0V, HVOUT Load = 1K $\Omega$ //220pF, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted, Typical values are VIO = +2.5V, V<sub>CC</sub> = -V<sub>EE</sub> = 5V, V<sub>PP</sub> = V<sub>NN</sub> = +85V, T<sub>A</sub> = +25°C, Limits are 100% tested at T<sub>A</sub> = +85°C and guaranteed by design in the entire temperature range )

| PARAMETER SYMBOL              |                   | CONDITIONS                         | MIN | TYP  | MAX | UNITS |  |

|-------------------------------|-------------------|------------------------------------|-----|------|-----|-------|--|

| PULSER DC SPECIFICAT          | IONS CC0 = 0 C    | C1 = 0                             |     |      |     |       |  |

| Low-Side Output<br>Impedance  | R <sub>OLS</sub>  | I <sub>OUT</sub> = 50mA            |     | 13   | 29  | Ω     |  |

| High-Side Output<br>Impedance | R <sub>OHS</sub>  | I <sub>OUT</sub> = -50mA           |     | 13   | 29  | Ω     |  |

| Low-Side Output Current       | I <sub>OLS</sub>  | V <sub>DS</sub> = +85V             |     | 2.1  |     | Α     |  |

| High-Side Output Current      | I <sub>OHS</sub>  | V <sub>DS</sub> = +85V             |     | 2.1  |     | Α     |  |

| PULSER DC SPECIFICAT          | IONS CC0 = 1 C    | C1 = 0                             |     |      |     |       |  |

| Low-Side Output<br>Impedance  | R <sub>OLS</sub>  | I <sub>OUT</sub> = 50mA            |     | 16   | 33  | Ω     |  |

| High-Side Output<br>Impedance | R <sub>OHS</sub>  | I <sub>OUT</sub> = -50mA           |     | 16   | 33  | Ω     |  |

| Low-Side Output Current       | I <sub>OLS</sub>  | V <sub>DS</sub> = +85V             |     | 1.75 |     | Α     |  |

| High-Side Output Current      | I <sub>OHS</sub>  | V <sub>DS</sub> = +85V             |     | 1.75 |     | Α     |  |

| PULSER DC SPECIFICAT          | IONS CC0 = 0 C    | C1 = 1                             |     |      |     |       |  |

| Low-Side Output<br>Impedance  | R <sub>OLS</sub>  | I <sub>OUT</sub> = 50mA            |     | 30   | 55  | Ω     |  |

| High-Side Output<br>Impedance | R <sub>OHS</sub>  | I <sub>OUT</sub> = -50mA           |     | 40   | 76  | Ω     |  |

| Low-Side Output Current       | I <sub>OLS</sub>  | V <sub>DS</sub> = +85V             |     | 0.7  |     | Α     |  |

| High-Side Output Current      | I <sub>OHS</sub>  | V <sub>DS</sub> = +85V             |     | 0.7  |     | Α     |  |

| PULSER DC SPECIFICAT          | IONS CC0 = 1 C    | C1 = 1                             |     |      |     |       |  |

| Low-Side Output<br>Impedance  | R <sub>OLS</sub>  | I <sub>OUT</sub> = 50mA            |     | 61.5 | 130 | Ω     |  |

| High-Side Output Impedance    | R <sub>OHS</sub>  | I <sub>OUT</sub> = -50mA           |     | 81   | 155 | Ω     |  |

| Low-Side Output Current       | I <sub>OLS</sub>  | V <sub>DS</sub> = +85V             |     | 0.35 |     | Α     |  |

| High-Side Output Current      | I <sub>OHS</sub>  | V <sub>DS</sub> = +85V             |     | 0.35 |     | Α     |  |

| CLAMP E DAMP DC SPEC          | CIFICATIONS       |                                    |     |      |     |       |  |

| CLAMP nFET Output             | В                 | I <sub>OUT</sub> = 50mA, 5 levels  |     | 8    |     |       |  |

| Impedance                     | R <sub>ONG</sub>  | I <sub>OUT</sub> = 50mA, 3 levels  |     | 16   | 33  | Ω     |  |

| CLAMP pFET Output             | Б                 | I <sub>OUT</sub> = -50mA, 5 levels |     | 8    |     |       |  |

| Impedance                     | R <sub>OPG</sub>  | I <sub>OUT</sub> = -50mA, 3 levels |     | 16   | 33  | Ω     |  |

| CLAMP nFET Output             |                   | V <sub>DS</sub> = +85V, 5 levels   |     | 2    |     |       |  |

| Current                       | long              | V <sub>DS</sub> = +85V, 3 levels   |     | 1    |     | A     |  |

| CLAMP pFET Output             |                   | V <sub>DS</sub> = +85V, 5 levels   |     | 2    |     |       |  |

| Current                       | l <sub>OPG</sub>  | V <sub>DS</sub> = +85V, 3 levels   |     | 1    |     | A     |  |

| DAMP Output Impedance         | R <sub>DAMP</sub> |                                    |     | 130  | 240 | Ω     |  |

### **Electrical Characteristics—Pulser (continued)**

$(V_{CC}=5V\pm5\%,\,V_{EE}=-5V\pm5\%,\,V_{PPA}=+85V,\,V_{NNA}=-85V,\,V_{PPB}=+85V,\,V_{NNB}=-85V,\,V_{IO}=+1.7V\,\,to\,\,+3.3V,\,Direct\,\,Mode,\,CC0=0V,\,CC1=0V,\,SYNC=0V,\,HVOUT\,\,Load=1K\Omega//220pF,\,T_A=T_{MIN}\,\,to\,\,T_{MAX},\,unless\,\,otherwise\,\,noted,\,Typical\,\,values\,\,are\,\,VIO=+2.5V,\,V_{CC}=-V_{EE}=5V,\,V_{PP}=V_{NN}=+85V,\,T_A=+25^{\circ}C,\,Limits\,\,are\,\,100\%\,\,tested\,\,at\,\,T_A=+85^{\circ}C\,\,and\,\,guaranteed\,\,by\,\,design\,\,in\,\,the\,\,entire\,\,temperature\,\,range\,\,)$

| PARAMETER                                                  | SYMBOL           | CONDITIONS                                                                                                                                                                                | MIN | TYP  | MAX | UNITS |

|------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| PULSER AC SPECIFICATI                                      | ONS 3 Levels N   | lode                                                                                                                                                                                      |     |      |     |       |

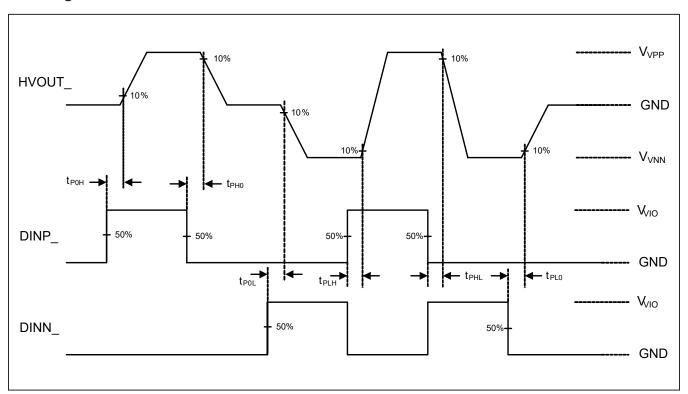

| Logic Input to Output<br>Low-to-High Propagation<br>Delay  | T <sub>PLH</sub> | Trasparent mode: from I <sub>NP</sub> /I <sub>NN</sub> at 50% to output at 10% of the transition swing Clocked mode: from CLK rising edge at 50% to output at 10% of the transition swing |     | 12   | 18  | ns    |

| Logic Input to Output<br>High-to-Low Propagation<br>Delay  | T <sub>PHL</sub> | Trasparent mode: from I <sub>NP</sub> /I <sub>NN</sub> at 50% to output at 10% of the transition swing Clocked mode: From CLK rising edge at 50% to output at 10% of the transition swing |     | 12   | 18  | ns    |

| Logic Input to Output<br>Low-to-GND Propagation<br>Delay   | T <sub>PL0</sub> | Trasparent mode: from I <sub>NP</sub> /I <sub>NN</sub> at 50% to output at 10% of the transition swing Clocked mode: from CLK rising edge at 50% to output at 10% of the transition swing |     | 11.5 | 18  | ns    |

| Logic Input-to-Output<br>High to GND Propagation<br>Delay  | T <sub>PH0</sub> | Trasparent mode: from I <sub>NP</sub> /I <sub>NN</sub> at 50% to output at 10% of the transition swing Clocked mode: from CLK rising edge at 50% to output at 10% of the transition swing |     | 11.5 | 18  | ns    |

| Logic Input-to-Output<br>GND to High Propagation<br>Delay  | T <sub>P0H</sub> | Trasparent mode: from I <sub>NP</sub> /I <sub>NN</sub> at 50% to output at 10% of the transition swing Clocked mode: From CLK rising edge at 50% to output at 10% of the transition swing |     | 12.7 | 18  | ns    |

| Logic Input to Output<br>GND to Low Propagation<br>Delay   | T <sub>P0L</sub> | Trasparent mode: from I <sub>NP</sub> /I <sub>NN</sub> at 50% to output at 10% of the transition swing Clocked mode: From CLK rising edge at 50% to output at 10% of the transition swing |     | 12.7 | 18  | ns    |

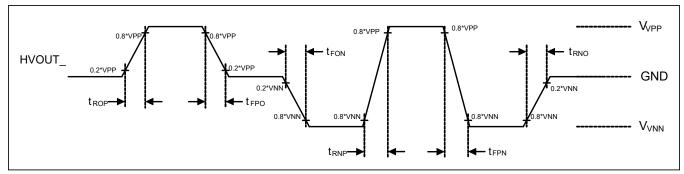

| OUT_ Fall Time<br>(V <sub>PP</sub> _ to V <sub>NN</sub> _) | T <sub>FPN</sub> | From 0.8 x V <sub>PP</sub> _ to 0.8 x V <sub>NN</sub> _,<br>V <sub>PP</sub> = -V <sub>NN</sub> = 80V                                                                                      |     | 18.7 |     | ns    |

| OUT_ Rise Time<br>(V <sub>NN</sub> _ to V <sub>PP</sub> _) | T <sub>RNP</sub> | From 0.8xVNN_ to 0.8 x V <sub>PP_</sub> ,<br>V <sub>PP</sub> = -V <sub>NN</sub> = 80V                                                                                                     |     | 18.7 |     | ns    |

| OUT_ Rise Time<br>(GND to V <sub>PP</sub> _)               | T <sub>R0P</sub> | From 0.2 x V <sub>PP</sub> to 0.8 x V <sub>PP</sub> , V <sub>PP</sub> = 80V                                                                                                               |     | 8.5  |     | ns    |

### **Electrical Characteristics—Pulser (continued)**

(V<sub>CC</sub> = 5V±5%, V<sub>EE</sub> = -5V ±5%, V<sub>PPA</sub> = +85V, V<sub>NNA</sub> = -85V, V<sub>PPB</sub> = +85V, V<sub>NNB</sub> = -85V, VIO = +1.7V to +3.3V, Direct Mode, CC0 = 0V, CC1 = 0V, SYNC = 0V, HVOUT Load = 1K $\Omega$ //220pF, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted, Typical values are VIO = +2.5V, V<sub>CC</sub> = -V<sub>EE</sub> = 5V, V<sub>PP</sub> = V<sub>NN</sub> = +85V, T<sub>A</sub> = +25°C, Limits are 100% tested at T<sub>A</sub> = +85°C and guaranteed by design in the entire temperature range )

| PARAMETER                                                     | SYMBOL            | CONDITIONS                                                                                                                                            | MIN | TYP | MAX | UNITS |  |

|---------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|--|

| OUT_ Fall Time<br>(GND to V <sub>NN</sub> _)                  | T <sub>F0N</sub>  | From 0.2 x V <sub>NN</sub> to 0.8 x V <sub>NN</sub> ,<br>V <sub>NN</sub> = -80V                                                                       |     |     |     |       |  |

| OUT_ Rise Time<br>(V <sub>NN</sub> _ to GND)                  | T <sub>RN0</sub>  | From 0.8 x V <sub>NN</sub> to 0.2 x V <sub>NN</sub> ,<br>V <sub>NN</sub> = -80V                                                                       |     | 17  |     | ns    |  |

| OUT_ Fall Time<br>(V <sub>PP</sub> _ to GND)                  | T <sub>FP0</sub>  | From 0.8 x V <sub>PP</sub> _ to 0.2 x V <sub>PP</sub> _, V <sub>PP</sub> = 80V                                                                        |     | 17  |     | ns    |  |

| Slew Rate 220pF                                               | SR1               | $C_L = 220 pF V_{PP} = -V_{NN} = 60 V$                                                                                                                |     | 6.5 |     | V/ns  |  |

| Slew Rate 70pF//100Ω                                          | SR2               | $C_L = 70 \text{pF}, R_L = 100 \Omega V_{PP} = -V_{NN} = 60 V$                                                                                        |     | 20  |     | V/ns  |  |

| 2nd Harmonic Distortion                                       | THD2              | f <sub>OUT</sub> = 5MHz, V <sub>PP</sub> =-V <sub>NN</sub> = 80V, square wave (20 cycles)                                                             |     | -40 |     | dBc   |  |

| Pulse Cancellation 1<br>Fundamental                           | PC1               | f <sub>OUT</sub> = 1MHz - 5MHz, V <sub>PP</sub> =-V <sub>NN</sub> = 80V, 2 cycles.                                                                    |     | -40 |     | dBc   |  |

| Pulse Cancellation 2<br>Second Harmonic                       | PC2               | f <sub>OUT</sub> _ = 1MHz - 5MHz,<br>V <sub>PP</sub> _ = -V <sub>NN</sub> _ = 80V, 2 cycles.                                                          |     | -40 |     | dBc   |  |

| Pulser Bandwidth                                              | BW                | V <sub>PP</sub> = -V <sub>NN</sub> = +60V. Defined as the maximum frequency at which the pulser is capable of driving at least 90% of the transition. |     | 25  |     | MHz   |  |

| PULSER AC SPECIFICAT                                          | IONS              |                                                                                                                                                       |     |     |     |       |  |

| CWD Voltage Drop                                              | V <sub>DROP</sub> | Drop between supply voltage and output voltage levels CWD, I <sub>OUT</sub> = ±10mA, f = 5MHz, V <sub>PP</sub> = -V <sub>NN</sub> = 5V                | 2.1 |     |     | V     |  |

| CWD Voltage Drop–Low Drop Mode (Beamforming Mode Only)  VDROP |                   | Drop between supply voltage and output voltage levels CWD, I <sub>OUT</sub> = ±10mA, f = 5MHz, V <sub>PP</sub> = -V <sub>NN</sub> = 5V                |     | 1.4 |     | V     |  |

| Propagation Delay Part-<br>to-Part Matching (Skew)            | ΔΤρ               | 3 std: between different parts. Same temperature same voltage supplies.                                                                               | ± 2 |     |     | ns    |  |

### **Electrical Characteristics—T/R Switch**

( $V_{CC}$  = 5V ±5%,  $V_{EE}$  = -5V ±5%, VIO = +1.7V to +3.3V, Direct Mode,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted, Typical values are VIO = +2.5V,  $V_{CC}$  = - $V_{EE}$  = 5V,  $T_A$  = +25°C, Limits are 100% tested at  $T_A$  = +85°C and guaranteed by design in the entire temperature range )

| PARAMETER                                                     | SYMBOL               | CONDITIONS                                                                                                                                                                      | MIN | TYP   | MAX | UNITS             |

|---------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------------------|

| T/R SWITCH DC SPECIFIC                                        | CATIONS              |                                                                                                                                                                                 |     |       |     |                   |

| T/R Switch Power<br>Consumption per Channel                   | T <sub>RPOW</sub>    |                                                                                                                                                                                 |     | <0.1  |     | mW                |

| LVOUT_ Output Voltage<br>Linear Range                         | LVRANGE              | Sinusoidal tone on HVOUT. f = 1MHz to 20MHz. Load on LVOUT = $100\Omega$ , THD < 1%                                                                                             |     | ±0.53 |     | V                 |

| Equivalent Small-Signal<br>Shunt Capacitance on<br>Pin LVOUT_ | COFFLV               | 0.1V <sub>P-P</sub> , f = 5MHz sinusoidal tone signal T/R switch off                                                                                                            |     | 4.5   |     | pF                |

| T <sub>RSW</sub> On Impedance                                 | RTRON                | f = 1MHz to 15MHz. Measured between HVOUT_ and LVOUT_                                                                                                                           |     | 12    | 22  | Ω                 |

| T <sub>RSW</sub> On DC Output<br>Voltage                      | LVOFFON              | No load on HVOUT and LVOUT                                                                                                                                                      | -4  | 0     | +4  | mV                |

| T <sub>RSW</sub> Off DC Output<br>Voltage                     | LVOFFOFF             | No load on HVOUT and LVOUT                                                                                                                                                      | -4  | 0     | +4  | mV                |

| T/R SWITCH AC SPECIFIC                                        | CATIONS              |                                                                                                                                                                                 |     |       |     | ,                 |

| T <sub>RSW</sub> Turn-On time                                 | T <sub>ONTRSW</sub>  |                                                                                                                                                                                 |     | 0.5   | 1   | μs                |

| T <sub>RSW</sub> Turn-Off time                                | T <sub>OFFTRSW</sub> |                                                                                                                                                                                 |     |       | 0.2 | μs                |

| T <sub>RSW</sub> Harmonic<br>Distortion THD                   | T <sub>HDTRSW</sub>  | $R_{LOAD}$ = 200 $\Omega$ , $V_{SIGN}$ = 100m $V_{PP}$ , $f$ = 1MHz to 20MHz                                                                                                    |     | -60   |     | dB                |

| T <sub>RSW</sub> Turn On Voltage<br>Spike on HVOUT            | V <sub>PKHVON</sub>  | 20pF//200Ω load on HVOUT, 20pF//200Ω load on LVOUT Low-pass filtered at 20MHz                                                                                                   |     | 55    |     | mV <sub>P-P</sub> |

| T <sub>RSW</sub> Turn OFF Voltage<br>Spike on HVOUT           | V <sub>PKHVOFF</sub> | 20pF//200Ω load on HVOUT, 20pF//200Ω load on LVOUT Low-Pass Filtered at 20MHz                                                                                                   |     | 6     |     | mV <sub>P-P</sub> |

| T <sub>RSW</sub> Off Isolation                                | OFFISO               | f = 5MHz. Measured between HVOUT and LVOUT                                                                                                                                      |     | -64   |     | dB                |

| Power Supply Modulation<br>Ratio on V <sub>CC</sub>           | PSMR                 | T <sub>RSW</sub> on. Sinusoidal tone (1KHz, 500mVRMS) superimposed onto VCC DC level. Sinusoidal tone on HVOUT (5MHz, 200mVRMS). LVOUT: terminated with 50Ω                     |     | -58   |     | dB                |

| Power Supply Modulation<br>Ratio on V <sub>EE</sub>           | PSMR                 | TRSW on. Sinusoidal tone (1KHz, 500mV <sub>RMS</sub> ) superimposed onto V <sub>EE</sub> DC level. Sinusoidal tone on HVOUT (5MHz, 200mVRMS). LVOUT: terminated with $50\Omega$ |     | -80   |     | dB                |

# **Pin Configuration**

|   |                                                 |                  |                |        |        |       | TOP VIEW<br>P SIDE DOV | VN)    |       |         |         |         |         |

|---|-------------------------------------------------|------------------|----------------|--------|--------|-------|------------------------|--------|-------|---------|---------|---------|---------|

| • | 1                                               | 2                | 3              | 4      | 5      | 6     | 7                      | 8      | 9     | 10      | 11      | 12      | 13      |

| ı | (N.C.)                                          | (N.C.)           | (vcc)          | (VGPB) | (VPPB) | (VEE) | (VGNB)                 | (VNNB) | (vcc) | (LVOUT) | (HVOUT) | (N.C.)  | (N.C.)  |

| ; | (N.C.)                                          | (DINP)<br>8      | (THP)          | (VGPB) | (VPPB) | (GND) | (VGNB)                 | (VNNB) | (GND) | (N.C.)  | (LVOUT) | (HVOUT) | (N.C.)  |

|   | (DINN 7                                         | (DINP7)          | (MODE2)        | (GND)  | (VPPB) | (GND) | (GND)                  | (VNNB) | (GND) | (GND)   | (GND)   | (GND)   | (HVOUT) |

| , | (DINN 6                                         | (DINP6)          | (DINN8)        | (GND)  | (VPPB) | (GND) | (GND)                  | (VNNB) | (GND) | (GND)   | (GND)   | (GND)   | (LVOUT) |

|   | (DINN5/<br>CS)                                  | (DINP5/)<br>SCLK | (GND)          | (GND)  | (VPPB) | (GND) | (GND)                  | (VNNB) | (GND) | (GND)   | (GND)   | (GND)   | (HVOUT  |

| : | (VDD)                                           | (CC1/<br>SDOUT)  | (GND)          | (GND)  | (GND)  | (GND) | (GND)                  | (GND)  | (GND) | (GND)   | (GND)   | (GND)   | (LVOUT  |

| i | (VIO)                                           | (CLK)            | (CCO/<br>SDIO) | (GND)  | (GND)  | (GND) | (GND)                  | (GND)  | (GND) | (GND)   | (GND)   | (GND)   | (LVOUT  |

|   | (DINN 4                                         | (DINP4/)<br>TRIG | (GND)          | (GND)  | (VPPA) | (GND) | (GND)                  | (VNNA) | (GND) | (GND)   | (GND)   | (GND)   | (HVOUT4 |

|   | $\begin{pmatrix} DINN \\ 3 \end{pmatrix}$       | (DINP3)          | (DINN1)        | (GND)  | (VPPA) | (GND) | (GND)                  | (VNNA) | (GND) | (GND)   | (GND)   | (GND)   | (LVOUT) |

| ı | (DINN2)                                         | (DINP2)          | (MODE1)        | (GND)  | (VPPA) | (GND) | (GND)                  | (VNNA) | (GND) | (GND)   | (GND)   | (GND)   | (HVOUT  |

|   | $\left(\begin{array}{c} N.C \end{array}\right)$ | (DINP1)          | (SYNC/)<br>INT | (VGPA) | (VPPA) | (GND) | (VGNA)                 | (VNNA) | (GND) | (N.C.)  | (LVOUT) | (HVOUT) | (N.C.)  |

|   | (N.C.)                                          | (N.C.)           | (vcc)          | (VGPA) | (VPPA) | (VEE) | (VGNA)                 | (VNNA) | (vcc) | (LVOUT) | (HVOUT) | (N.C.)  | (N.C.)  |

|   |                                                 |                  |                |        |        |       | WLP<br>n x 6.33m       | ım     |       |         |         |         |         |

### **Pin Description**

| PIN                                                                                                                                                                                                                                                                                                                                          | NAME | FUNCTION                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER                                                                                                                                                                                                                                                                                                                                        |      |                                                                                                                                                                                                                               |

| H5, J5, K5, L5, M5                                                                                                                                                                                                                                                                                                                           | VPPA | HV Positive Power Supply Input. Connect HV bypass capacitor between $V_{PPA}$ and GND as close as possible to the device. Capacitor value depends on the application and typically varies in a range from 100nF to 1 $\mu$ F. |

| A5, B5, C5, D5, E5                                                                                                                                                                                                                                                                                                                           | VPPB | HV Positive Power Supply Input. Connect HV bypass capacitor between $V_{PPB}$ and GND as close as possible to the device. Capacitor value depends on the application and typically varies in a range from 100nF to 1 $\mu$ F. |

| M8, L8, K8, J8, H8                                                                                                                                                                                                                                                                                                                           | VNNA | HV Negative Power Supply Input. Connect HV bypass capacitor between $V_{NNA}$ and GND as close as possible to the device. Capacitor value depends on the application and typically varies in a range from 100nF to 1 $\mu$ F. |

| A8, B8, C8, D8, E8                                                                                                                                                                                                                                                                                                                           | VNNB | HV Negative Power Supply Input. Connect HV bypass capacitor between $V_{NNB}$ and GND as close as possible to the device. Capacitor value depends on the application and typically varies in a range from 100nF to 1 $\mu$ F. |

| M3, A3, M9, A9                                                                                                                                                                                                                                                                                                                               | VCC  | $V_{CC}$ Positive Analog Supply Voltage Input. Connect 220nF or greater bypass capacitors to GND, one per side, as close as possible to the device.                                                                           |

| M6, A6                                                                                                                                                                                                                                                                                                                                       | VEE  | V <sub>EE</sub> Negative Analog Supply Voltage Input. Connect 220nF or greater bypass capacitors to GND, one per side, as close as possible to the device                                                                     |

| F1                                                                                                                                                                                                                                                                                                                                           | VDD  | LDO Output. 1.8V typ. Connect $1\mu F$ bypass capacitor between $V_{DD}$ and GND as close as possible to the device.                                                                                                          |

| G1                                                                                                                                                                                                                                                                                                                                           | VIO  | Logic I/O Voltage Supply. Connect > 0.1µF bypass capacitor between VIO and GND as close as possible to the device.                                                                                                            |

| M4, L4                                                                                                                                                                                                                                                                                                                                       | VGPA | High-Side Driver Floating Power Supply Output. Connect $1\mu F$ bypass capacitor between $V_{GPA}$ and $V_{PPA}$ as close as possible to the device.                                                                          |

| A4, B4                                                                                                                                                                                                                                                                                                                                       | VGPB | High-Side Driver Floating Power Supply Output. Connect $1\mu F$ bypass capacitor between $V_{GPB}$ and $V_{PPB}$ as close as possible to the device.                                                                          |

| M7, L7                                                                                                                                                                                                                                                                                                                                       | VGNA | Low-Side Driver Floating Power Supply Output. Connect $1\mu F$ bypass capacitor between $V_{GNA}$ and $V_{NNA}$ as close as possible to the device.                                                                           |

| A7, B7                                                                                                                                                                                                                                                                                                                                       | VGNB | Low-Side Driver Floating Power Supply Output. Connect $1\mu F$ bypass capacitor between $V_{\mbox{GNB}}$ and $V_{\mbox{NNB}}$ as close as possible to the device.                                                             |

| E3, F3, H3, C4, D4,<br>E4, F4, G4, H4, J4,<br>K4, F5, G5, B6, C6,<br>D6, E6, F6, G6, H6,<br>J6, K6, L6, C7, D7,<br>E7, F7, G7, H7, J7,<br>K7, F8, G8, B9, C9,<br>D9, E9, F9, G9, H9,<br>J9, K9, L9, C10,<br>D10, E10, F10,<br>G10, H10, J10, K10,<br>C11, D11, E11, F11,<br>G11, H11, J11, K11,<br>C12, D12, E12, F12,<br>G12, H12, J12, K12 | GND  | Ground                                                                                                                                                                                                                        |

# **Pin Description (continued)**

| PIN                 | NAME           | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|---------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pulser HV Outputs   | '              |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| M11                 | HVOUT1         | HV Output Channel 1                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| L12                 | HVOUT2         | HV Output Channel 2                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| K13                 | HVOUT3         | HV Output Channel 3                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| H13                 | HVOUT4         | HV Output Channel 4                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| E13                 | HVOUT5         | HV Output Channel 5                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| C13                 | HVOUT6         | HV Output Channel 6                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| B12                 | HVOUT7         | HV Output Channel 7                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| A11                 | HVOUT8         | HV Output Channel 8                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| T/R Switch LV Outp  | uts            |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| M10                 | LVOUT1         | LV Output (T/R Switch Output) Channel 1                                                                                                                                                                                                                                                                                                                                                                                |  |

| L11                 | LVOUT2         | LV Output (T/R Switch Output) Channel 2                                                                                                                                                                                                                                                                                                                                                                                |  |

| J13                 | LVOUT3         | LV Output (T/R Switch Output) Channel 3                                                                                                                                                                                                                                                                                                                                                                                |  |

| G13                 | LVOUT4         | LV Output (T/R Switch Output) Channel 4                                                                                                                                                                                                                                                                                                                                                                                |  |

| F13                 | LVOUT5         | LV Output (T/R Switch Output) Channel 5                                                                                                                                                                                                                                                                                                                                                                                |  |

| D13                 | LVOUT6         | LV Output (T/R Switch Output) Channel 6                                                                                                                                                                                                                                                                                                                                                                                |  |

| B11                 | LVOUT7         | LV Output (T/R Switch Output) Channel 7                                                                                                                                                                                                                                                                                                                                                                                |  |

| A10                 | LVOUT8         | LV Output (T/R Switch Output) Channel 8                                                                                                                                                                                                                                                                                                                                                                                |  |

| Control Logic Digit | al Inputs/Oเ   | ıtputs                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| K3                  | MODE1          | CMOS Logic Input                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| C3                  | MODE2          | CMOS Logic Input                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| В3                  | THP            | Open Drain Output. Thermal warning.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| L3                  | SYNC/<br>INT   | CMOS Logic Input in Direct Mode, Interrupt Open-Drain Output in Beamforming Mode. When in Direct mode, connect SYNC/INT logic-high to operate in Clocked mode whereas connect SYNC/INT logic-low to operate in Transparent mode. When in Beamforming mode, SYNC/INT is an open-drain output which carries interrupt signals (refer to the beamforming description). Connect $1K\Omega$ external resistor to $V_{IO}$ . |  |

| G3                  | CC0/<br>SDIO   | CMOS Logic Current Control Input in Direct Mode (CC0) SPI Data Input-Output in Beamforming Mode (SDIO)                                                                                                                                                                                                                                                                                                                 |  |

| F2                  | CC1/SD-<br>OUT | CMOS Logic Current Control Input in Direct Mode (CC1) SPI Data Output in Beamforming Mode (SDOUT)                                                                                                                                                                                                                                                                                                                      |  |

# **Pin Description (continued)**

| PIN                                                                     | NAME           | FUNCTION                                                                                                             |  |

|-------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------|--|

| Logic Input Signal P                                                    |                | TONOTION                                                                                                             |  |

|                                                                         | 1              | T                                                                                                                    |  |

| L2                                                                      | DINP1          | CMOS Positive Logic Input for Channel 1                                                                              |  |

| K2                                                                      | DINP2          | CMOS Positive Logic Input for Channel 2                                                                              |  |

| J2                                                                      | DINP3          | CMOS Positive Logic Input for Channel 3                                                                              |  |

| H2                                                                      | DINP4/<br>TRIG | CMOS Positive Logic Input for Channel 4 in Direct Mode (DINP4) CMOS Trigger Login Input in Beam Forming Mode (TRIG)  |  |

|                                                                         | DINP5/         | CMOS Positive Logic Input for Channel 5 in Direct Mode (DINP5)                                                       |  |

| E2                                                                      | SCLK           | SPI Clock Input in Beamforming Mode (SCLK)                                                                           |  |

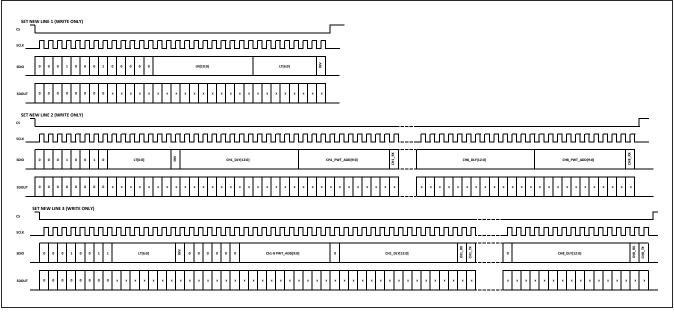

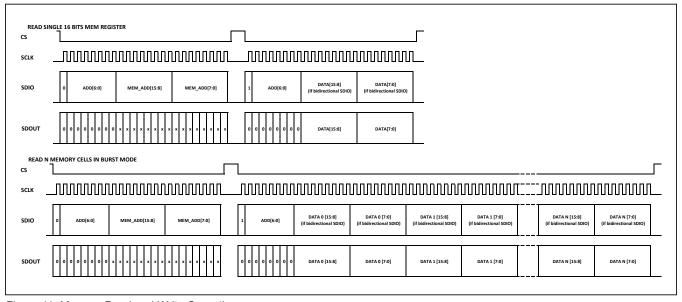

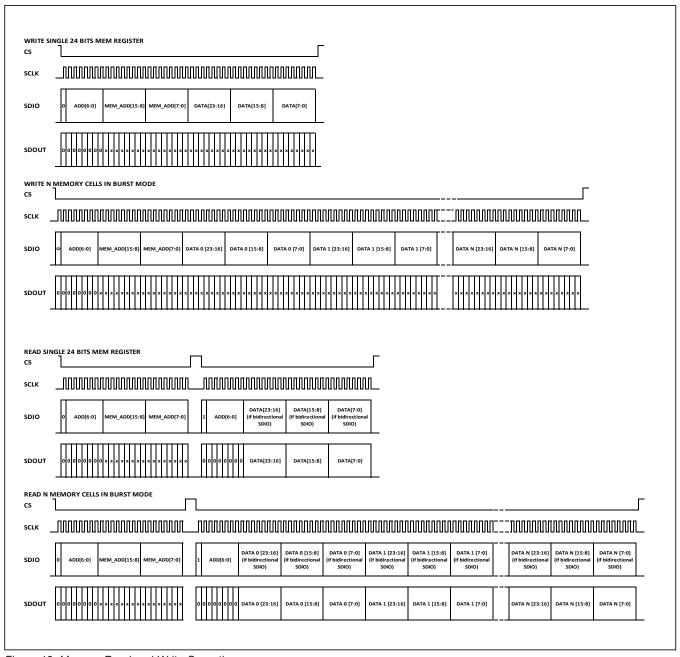

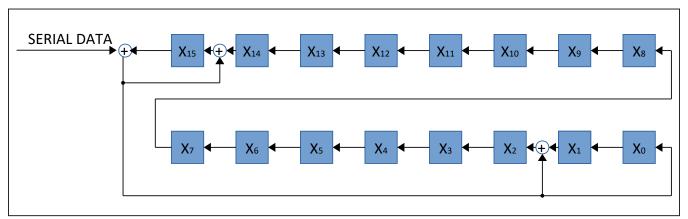

| D2                                                                      | DINP6          | CMOS Positive Logic Input for Channel 6                                                                              |  |