# Microprocessor-Compatible 12-Bit D/A Converter

**AD567**

## 1.1 Scope.

This specification covers the requirements for a high speed 12-bit resolution bipolar current output D/A converter with double buffered latch and high stability buried Zener reference.

### 1.2 Part Number.

The complete part number per Table 1 of this specification is as follows:

Device

Part Number

-1

AD567SD/883B

## 1.2.3 Case Outline.

See Appendix 1 of General Specification ADI-M-1000: package outline: D-28.

## 1.3 Absolute Maximum Ratings. (T<sub>A</sub> = +25°C unless otherwise noted)

| V <sub>CC</sub> to Power Ground                    |

|----------------------------------------------------|

|                                                    |

| V <sub>EE</sub> to Power Ground                    |

| Voltage on DAC Output (Pin 2)                      |

| Digital Inputs (Pins 10-15, 17-28) to Power Ground |

| Ref In to Reference Ground                         |

| Bipolar Offset to Reference Ground                 |

| 10V Span R to Reference Ground                     |

| 20V Span R to Reference Ground                     |

| Ref Out                                            |

| Momentary Short to $V_{CC}$                        |

| Power Dissipation                                  |

| Storage Temperature Range                          |

| Lead Temperature (Soldering 10sec)                 |

## 1.5 Thermal Characteristics.

Thermal Resistance  $\theta_{JC} = 25^{\circ}\text{C/W}$

$\theta_{JA} = 60^{\circ}\text{C/W}$

## AD567—SPECIFICATIONS

Table 1.

| Test                                       | Symbol             | Device     | Design<br>Limit<br>@+25°C | Sub<br>Group<br>1 | Sub<br>Group<br>2,3 | Test Condition <sup>1</sup>                                            | Units                |

|--------------------------------------------|--------------------|------------|---------------------------|-------------------|---------------------|------------------------------------------------------------------------|----------------------|

| Relative Accuracy                          | RA                 | -1         | 1/2                       | 1/2               | 3/4                 | All Bits with Positive Errors On.<br>All Bits with Negative Errors On. | ± LSB max            |

| Differential Nonlinearity                  | DNL                | - 1        | 3/4                       | 3/4               | 1                   | Major Carry Errors                                                     | ± LSB max            |

| Gain Error <sup>2</sup>                    | A <sub>E</sub>     | -1         | 0.25                      | 0.25              |                     | All Bits On                                                            | ±% FSR max           |

| Gain Temperature<br>Coefficient            | TCA <sub>E</sub>   | - 1        | 30                        |                   | 30                  | All Bits On                                                            | ± ppm/°C max         |

| Unipolar Offset Error                      | Vos                | -1         | 0.05                      | 0.05              |                     | All Bits Off                                                           | ±% FSR max           |

| Temperature Coefficient<br>Unipolar Offset | TCV <sub>OS</sub>  | -1         | 2                         |                   | 2                   | All Bits Off                                                           | ± ppm/°C max         |

| Bipolar Zero Error <sup>3</sup>            | B <sub>PZE</sub>   | - 1        | 0.15                      | 0.15              |                     | MSB On, All Other Bits Off<br>Bipolar                                  | ±% FSR max           |

| B/P Zero Temperature<br>Coefficient        | TCB <sub>BZE</sub> | <b>– 1</b> | 10                        |                   | 10                  | MSB On, All Other Bits Off<br>Bipolar                                  | ± ppm/°C max         |

| Reference Input Resistance                 | R <sub>IN</sub>    | -1         | 15                        |                   |                     |                                                                        | kΩ min               |

|                                            |                    |            | 25                        |                   |                     |                                                                        | kΩ max               |

| Output Resistance                          | R <sub>OUT</sub>   | - 1        | 6                         |                   |                     | Exclusive of Span Resistor                                             | kΩ min               |

|                                            |                    |            | 10                        |                   |                     |                                                                        | kΩ min               |

| Reference Output Voltage                   | V <sub>REF</sub>   | - 1        | 9.9                       | 9.9               | 9.9                 | Bipolar, 0.1mA External Load                                           | V min                |

|                                            |                    |            | 10.10                     | 10.10             | 10.10               | $V_{CC} = +12V, V_{EE} = -12V^4$                                       | V max                |

| Compliance Voltage                         | V <sub>CPL</sub>   | -1         | 1.5                       |                   |                     |                                                                        | – V min              |

|                                            |                    |            | 10.0                      |                   |                     |                                                                        | V max                |

| Output Current Settling<br>Time            | t <sub>SL</sub>    | 1          | 500                       |                   |                     | See Figure 1                                                           | ns max               |

| Output Current                             | Iour               | -1         | 1.6                       | 1.6               |                     | Unipolar All Bits On                                                   | – mA min             |

|                                            |                    |            | 2.4                       | 2.4               |                     | V <sub>IH</sub> + 5.0V                                                 | – mA max             |

|                                            |                    |            | 0.8                       | 0.8               |                     | Bipolar All Bits On                                                    | – mA min             |

|                                            |                    |            | 1.2                       | 1.2               |                     | $V_{IH} + 5.0V$                                                        | - mA max             |

| Power Supply Rejection Ratio               | PSRR               | -1         | 10                        | 10                |                     | $+11.4V \le V_{CC} \le +16.5V$                                         | ppm of FSR/<br>% max |

|                                            |                    |            | 25                        | 25                |                     | $-16.5V \le V_{EE} \le -11.4V$                                         |                      |

| Power Supply Current                       | I <sub>CC</sub>    | -1         | 5                         | 5                 |                     | $V_{CC} = +16.5V, V_{EE} = -16.5V$                                     | mA max               |

|                                            | I <sub>EE</sub>    | -1         | 25                        | 25                |                     | All Bits Low                                                           | – mA max             |

| Power Dissipation                          | P <sub>D</sub>     | -1         | 495                       | 495               |                     | $V_{CC} = +16.5V, V_{EE} = -16.5V$<br>All Bits Low                     | mW max               |

| Digital Input High Voltage                 | V <sub>IH</sub>    | -1         | 2.0                       | 2.0               |                     |                                                                        | V min                |

|                                            |                    |            | 5.5                       |                   |                     |                                                                        | V max                |

| Digital Input Low Voltage                  | $V_{1L}$           | -1         | 0.8                       | 0.8               |                     |                                                                        | V max                |

| Digital Input High Current                 | I <sub>IH</sub>    | -1         | 300                       | 300               |                     | $V_{IH} = 5.5V$                                                        | μ.A max              |

| Digital Input Low Current                  | I <sub>IL</sub>    | -1         | 100                       | 100               |                     | $V_{IL} = 0.0V$                                                        | μA max               |

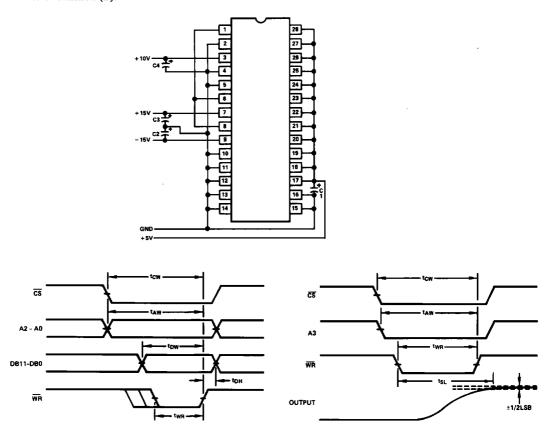

| Write Pulse Width                          | twR                | -1         | 100                       |                   |                     | See Note 5                                                             | ns min               |

| Data Setup Time                            | tow                | -1         | 50                        |                   |                     | See Note 5                                                             | ns min               |

| Data Hold Time                             | t <sub>DH</sub>    | -1         | 10                        |                   |                     | See Note 5                                                             | ns min               |

| CS Valid to End of WR                      | t <sub>CW</sub>    | -1         | 100                       |                   |                     | See Note 5                                                             | ns min               |

| Address Valid End of WR                    | t <sub>AW</sub>    | -1         | 100                       |                   |                     | See Note 5                                                             | ns min               |

| Latch Functionality                        | A <sub>EΔ</sub>    | -1         | 1                         | 1                 | 1                   | See Notes 6 and 7                                                      | ± LSB max            |

| Latch Functionality                        | Vosa               | - i        | 1                         | 1                 | 1                   | See Note 6                                                             | ± LSB max            |

- $V_{CC} = +15V$ ,  $V_{EE} = -15V$ ,  $50\Omega$  resistor pin 6 to pin 8,  $A_0A_1A_2A_3\overline{CS}$ ,  $\overline{WR} = Logic "0"$ ,  $V_{IH} = 2.0V$ ,  $V_{IL} = 0.8V$ , Unipolar configuration unless otherwise specified.  $V_{IH} = +2.0V$ ,  $V_{IL} = +0.7V$  guaranteed design limits at  $-55^{\circ}C$  and  $+125^{\circ}C$ .

- Unipolar pin 3 connected to amplifier output to utilize 10 volt span.

- Bipolar pin 4 connected to amplifier output to utilize 20 volt span, 50Ω resistor pin 1 to pin 6.

- <sup>2</sup>Gain adjustment range  $\pm 0.25\%$  min.

- <sup>3</sup>Bipolar zero adjustment range ± 0.15% min.

- <sup>4</sup>In subgroup 1, the reference output is loaded with 0.5mA nominal reference current, 1.0mA bipolar offset current

- and 0.1mA additional current. In subgroups 2 and 3, only the 0.5mA reference input current is applied. The reference must be

- buffered to supply external loads at elevated temperatures.

- <sup>5</sup>See Figure 1 and Table 2.

- <sup>6</sup>All bits low, A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub>, A<sub>3</sub> = Logic "0"; A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub>, A<sub>3</sub> initialized to Logic "1", each 4-bit register set to Logic "1",

- and Ao, A1, A2 set sequentially to Logic "0" and back to Logic "1" to latch data into first rank.

- <sup>7</sup>A<sub>3</sub> set to Logic "0" and back to Logic "1" to latch full scale output into second rank.

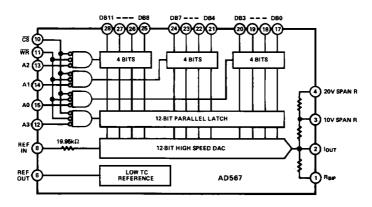

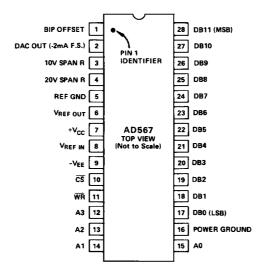

## 3.2.1 Functional Block Diagram and Terminal Assignments.

### 3.2.4 Microcircuit Technology Group.

This microcircuit is covered by technology group (56).

## 4.2.1 Life Test/Burn-In Circuit.

Steady state life test is per MIL-STD-883 Method 1005. Burn-in is per MIL-STD-883 Method 1015 test condition (B).

Figure 1.

Table 2. Truth Table

| <u>cs</u> | WR | A3 | A2 | A1 | A0 | Operation                          |

|-----------|----|----|----|----|----|------------------------------------|

| 1         | Х  | х  | х  | Х  | Х  | No Operation                       |

| x         | 1  | Х  | Х  | Х  | Х  | No Operation                       |

| 0         | 0  | 1  | 1  | 1  | 0  | Enable 4 LSBs of First Rank        |

| 0         | 0  | 1  | 1  | 0  | 1  | Enable 4 Middle Bits of First Rank |

| 0         | 0  | 1  | 0  | 1  | 1  | Enable 4 MSBs of First Rank        |

| 0         | 0  | 0  | 1  | 1  | 1  | Loads Second Rank from First Rank  |

| 0         | 0  | 0  | 0  | 0  | 0  | All Latches Transparent            |

<sup>&</sup>quot;X" = Don't Care

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.: 5962-8780101XA