LTC6416

## FEATURES

- 2GHz –3dB Small Signal Bandwidth

- **300MHz ±0.1dB Bandwidth**

- 1.8nV/√Hz Output Noise

- 46.25dBm Equivalent OIP3 at 140MHz

- 40.25dBm Equivalent OIP3 Up to 300MHz

- -81dBc/-72dBc HD2/HD3 at 140MHz, 2V<sub>P-P</sub> Out

- -84.5dBc IM3 at 140MHz, 2V<sub>P-P</sub> Out Composite

- -74dBc/-67.5dBc HD2/HD3 at 300MHz, 2V<sub>P-P</sub> Out

- -72.5dBc IM3 at 300MHz, 2V<sub>P-P</sub> Out Composite

- Programmable High Speed, Fast Recovery Output Clamping

- DC-Coupled Signal Path

- Operates on Single 2.7V to 3.9V Supply

- Low Power: 150mW on 3.6V

- 2mm × 3mm 10-Pin DFN Package

## **APPLICATIONS**

- Differential ADC Driver

- IF Sampling Receivers

- Impedance Transformer

- SAW Filter Interface

- CCD Buffer

## 2 GHz Low Noise Differential 16-Bit ADC Buffer

## DESCRIPTION

The LTC<sup>®</sup>6416 is a differential unity gain buffer designed to drive 16-bit ADCs with extremely low output noise and excellent linearity beyond 300MHz. Differential input impedance is  $12k\Omega$ , allowing 1:4 and 1:8 transformers to be used at the input to achieve additional system gain.

With no external biasing or gain setting components and a flow-through pinout, the LTC6416 is very easy to use. It can be DC-coupled and has a common mode output offset of -40mV. If the input signals are AC-coupled, the LTC6416 input pins are internally biased to provide an output common mode voltage that is set by the voltage on the V<sub>CM</sub> pin.

In addition the LTC6416 has high speed, fast recovery clamping circuitry to limit output signal swing. Both the high and low clamp voltages are internally biased to allow maximum output swing but are also user programmable via the CLLO and CLHI pins.

Supply current is nominally 42mA and the LTC6416 operates on supply voltages ranging from 2.7V to 3.9V.

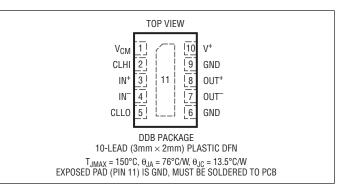

The LTC6416 is packaged in a 10-lead  $3mm \times 2mm$  DFN package. Pinout is optimized for placement directly adjacent to Linear's high speed 12-, 14- and 16-bit ADCs.

Ω, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

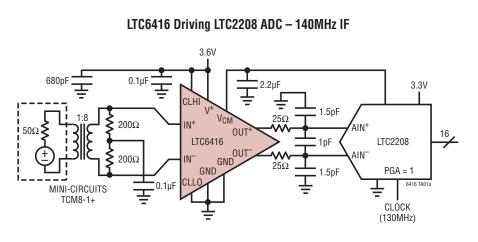

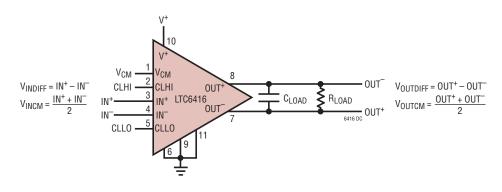

# TYPICAL APPLICATION

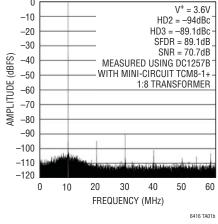

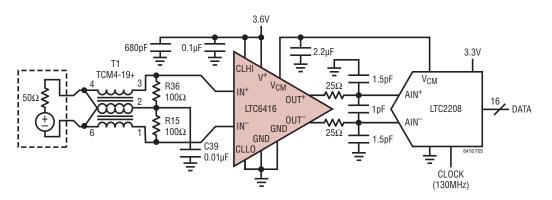

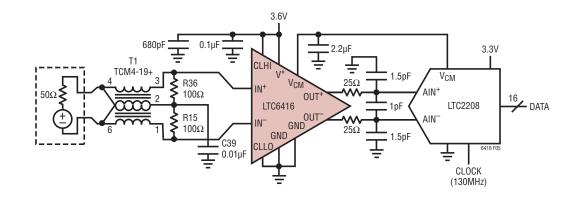

## LTC6416 Driving LTC2208 ADC with 1:8 Transformer $f_{IN}$ =140MHz, $f_S$ = 130MHz, -1dBFS, PGA = 1

6416f

4

# ABSOLUTE MAXIMUM RATINGS

(Note 1)

| Total Supply Voltage (V <sup>+</sup> to GND)4V                                        |

|---------------------------------------------------------------------------------------|

| Input Current (CLLO, CLHI, V <sub>CM</sub> , IN <sup>+</sup> , IN <sup>-</sup> )±10mA |

| Output Current (OUT <sup>+</sup> , OUT <sup>-</sup> )±22.5mA                          |

| Operating Temperature Range (Note 2)–40°C to 85°C                                     |

| Specified Temperature Range (Note 3) – 40°C to 85°C                                   |

| Storage Temperature Range65°C to 150°C                                                |

| Junction Temperature 150°C                                                            |

# PIN CONFIGURATION

# ORDER INFORMATION

#### Lead Free Finish

| TAPE AND REEL (MINI) | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|----------------------|-------------------|---------------|---------------------------------|-------------------|

| LTC6416CDDB#TRMPBF   | LTC6416CDDB#TRPBF | LDDY          | 10-Lead (3mm × 2mm) Plastic DFN | 0°C to 70°C       |

| LTC6416IDDB#TRMPBF   | LTC6416IDDB#TRPBF | LDDY          | 10-Lead (3mm × 2mm) Plastic DFN | -40°C to 85°C     |

$\mathsf{TRM} = 500 \mathsf{ pieces. *Temperature grades are identified by a label on the shipping container.$

Consult LTC Marketing for parts specified with wider operating temperature ranges.

Consult LTC Marketing for information on lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# 3.6V ELECTRICAL CHARACTERISTICS The • denotes the specifications which apply over the full

operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . V<sup>+</sup> = 3.6V, GND = 0V, No  $R_{LOAD}$ ,  $C_{LOAD} = 6pF$ .  $V_{CM} = 1.25V$ , CLHI = V<sup>+</sup>, CLLO = 0V unless otherwise noted.  $V_{INCM}$  is defined as (IN<sup>+</sup> + IN<sup>-</sup>)/2.  $V_{OUTCM}$  is defined as (OUT<sup>+</sup> + OUT<sup>-</sup>)/2.  $V_{INDIFF}$  is defined as (OUT<sup>+</sup> - OUT<sup>-</sup>). See DC test circuit schematic.

| SYMBOL                | PARAMETER                                   | CONDITIONS                                                            |   | MIN          | ТҮР      | MAX         | UNITS                                |

|-----------------------|---------------------------------------------|-----------------------------------------------------------------------|---|--------------|----------|-------------|--------------------------------------|

| Input/Output Cha      | racteristics                                |                                                                       |   |              |          |             |                                      |

| G <sub>DIFF</sub>     | Differential Gain                           | $V_{INDIFF} = \pm 1.2V$ Differential                                  | • | -0.3<br>-0.4 | -0.15    | 0<br>0      | dB<br>dB                             |

| TCG <sub>DIFF</sub>   | Differential Gain Temperature Coefficient   |                                                                       | • |              | -0.00033 |             | dB/°C                                |

| VSWINGDIFF            | Differential Output Voltage Swing           | V <sub>OUTDIFF</sub> V <sub>INDIFF</sub> = ±2.3V                      | • | 3.7<br>3.3   | 4.2      |             | V <sub>P-P</sub><br>V <sub>P-P</sub> |

| V <sub>SWINGMIN</sub> | Output Voltage Swing Low                    | Single-Ended Measurement of OUT+, $OUT^{-}$ . $V_{INDIFF} = \pm 2.3V$ | • |              | 0.2      | 0.3<br>0.35 | V<br>V                               |

| V <sub>SWINGMAX</sub> | Output Voltage Swing High                   | Single-Ended Measurement of OUT+, $OUT^{-}$ . $V_{INDIFF} = \pm 2.3V$ | • | 2.15<br>2    | 2.3      |             | V<br>V                               |

| I <sub>OUT</sub>      | Output Current Drive                        | Single-Ended Measurement of OUT+, OUT <sup>-</sup>                    | • | ±20          |          |             | mA                                   |

| V <sub>0S</sub>       | Differential Input Offset Voltage           | $IN^+ = IN^- = 1.25V$ , $V_{OS} = V_{OUTDIFF}/G_{DIFF}$               | • | 5<br>10      | -0.5     | 5<br>10     | mV<br>mV                             |

| TCV <sub>OS</sub>     | Differential Input Offset Voltage Drift     |                                                                       |   |              | 1        |             | µV/°C                                |

| VIOCM                 | Common Mode Offset Voltage, Input to Output | V <sub>OUTCM</sub> – V <sub>INCM</sub>                                | • | -65<br>-75   | -47      | -15<br>-5   | mV<br>mV                             |

**3.6V ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . V<sup>+</sup> = 3.6V, GND = 0V, No R<sub>LOAD</sub>, C<sub>LOAD</sub> = 6pF. V<sub>CM</sub> = 1.25V, CLHI = V<sup>+</sup>, CLLO = 0V unless otherwise noted. V<sub>INCM</sub> is defined as (IN<sup>+</sup> + IN<sup>-</sup>)/2. V<sub>OUTCM</sub> is defined as (OUT<sup>+</sup> + OUT<sup>-</sup>)/2. V<sub>INDIFF</sub> is defined as (IN<sup>+</sup> - IN<sup>-</sup>). V<sub>OUTDIFF</sub> is defined as (OUT<sup>+</sup> - OUT<sup>-</sup>). See DC test circuit schematic.

| SYMBOL                                                  | PARAMETER                                                                          | CONDITIONS                                                                                         |   | MIN          | ТҮР   | MAX         | UNITS    |

|---------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---|--------------|-------|-------------|----------|

| IVR <sub>MIN</sub>                                      | Input Voltage Range, IN <sup>+</sup> , IN <sup>-</sup><br>(Minimum) (Single-Ended) | Defined by Output Voltage Swing Test                                                               | • |              |       | 0.1         | V        |

| IVR <sub>MAX</sub>                                      | Input Voltage Range IN <sup>+</sup> , IN <sup>-</sup><br>(Maximum) (Single-Ended)  | Defined by Output Voltage Swing Test                                                               | • | 2.4          |       |             | V        |

| IB                                                      | Input Bias Current, IN+, IN <sup>-</sup>                                           | $IN^{+} = IN^{-} = 1.25V$                                                                          |   | -15          | -5    | 15          | μA       |

| R <sub>INDIFF</sub>                                     | Differential Input Resistance                                                      | $V_{INDIFF} = \pm 1.2V$                                                                            |   | 9            | 12    | 15          | kΩ       |

| C <sub>INDIFF</sub>                                     | Differential Input Capacitance                                                     |                                                                                                    |   |              | 1     |             | pF       |

| R <sub>INCM</sub>                                       | Input Common Mode Resistance                                                       | $IN^+ = IN^- = 0.65V$ to 1.85V                                                                     |   |              | 6     |             | kΩ       |

| CMRR                                                    | Common Mode Rejection Ratio                                                        | $IN^+ = IN^- = 0.65V \text{ to } 1.85V,$<br>CMRR = (V <sub>OUTDIFF</sub> /G <sub>DIFF</sub> /1.2V) | • | 63.5<br>59.6 | 83    |             | dB<br>dB |

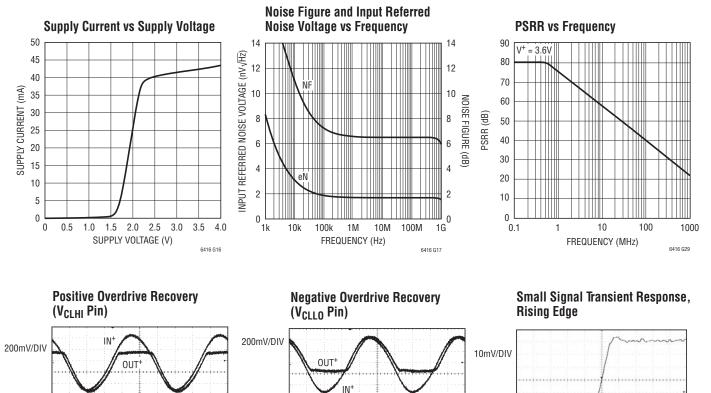

| e <sub>N</sub>                                          | Input Noise Voltage Density                                                        | f = 100kHz                                                                                         |   |              | 1.8   |             | nV/√Hz   |

| i <sub>N</sub>                                          | Input Noise Current Density                                                        | f = 100kHz                                                                                         |   |              | 6.5   |             | pA/√Hz   |

| Output Common Mode                                      | e Voltage Control                                                                  |                                                                                                    |   |              |       |             |          |

| G <sub>CM</sub>                                         | V <sub>CM</sub> Pin Common Mode Gain                                               | V <sub>CM</sub> = 0.65V to 1.85V                                                                   |   | 0.9          | 0.96  | 1.05        | V/V      |

| VINCMDEFAULT                                            | Default Input Common Mode Voltage                                                  | V <sub>INCM</sub> . IN <sup>+</sup> , IN <sup>-</sup> , V <sub>CM</sub> Pin Floating               |   | 1.3          | 1.38  | 1.45        | V        |

| $V_{OS} (V_{CM} - V_{INCM})$                            | Offset Voltage, $V_{CM}$ to $V_{INCM}$                                             | $V_{CM} - V_{INCM}, V_{CM} = 1.25V$                                                                |   | -70          | -28   | 70          | mV       |

| VOUTCMDEFAULT                                           | Default Output Common Mode Voltage                                                 | Inputs Floating, V <sub>CM</sub> Pin Floating                                                      |   | 1.25         | 1.34  | 1.45        | V        |

| V <sub>OS</sub> (V <sub>CM</sub> – V <sub>OUTCM</sub> ) | Offset Voltage, $V_{CM}$ to $V_{OUTCM}$                                            | $V_{CM} - V_{OUTCM}, V_{CM} = 1.25V$                                                               |   | -60          | 15    | 60          | mV       |

| Voutcmmin                                               | Output Common Mode Voltage Range<br>(Minimum)                                      | V <sub>CM</sub> = 0.1V                                                                             | • |              | 0.37  | 0.5<br>0.55 | V<br>V   |

| Voutcmmax                                               | Output Common Mode Voltage Range<br>(Maximum)                                      | V <sub>CM</sub> = 2.7V                                                                             | • | 2.3<br>2.25  | 2.46  |             | V<br>V   |

| V <sub>CMDEFAULT</sub>                                  | V <sub>CM</sub> Pin Default Voltage                                                |                                                                                                    |   | 1.325        | 1.36  | 1.425       | V        |

| R <sub>VCM</sub>                                        | V <sub>CM</sub> Pin Input Resistance                                               |                                                                                                    |   | 2.5          | 3.8   | 5.1         | kΩ       |

| CVCM                                                    | V <sub>CM</sub> Pin Input Capacitance                                              |                                                                                                    |   |              | 1     |             | pF       |

| BVCM                                                    | V <sub>CM</sub> Pin Bias Current                                                   | V <sub>CM</sub> = 1.25V                                                                            | • | -50          | -32   | 50          | μA       |

| DC Clamping Charact                                     | eristics                                                                           |                                                                                                    |   |              |       |             |          |

| VCLHIDEFAULT                                            | Default Output Clamp Voltage, High                                                 |                                                                                                    |   | 2.3          | 2.45  | 2.6         | V        |

| V <sub>OS</sub> (CLHI – V <sub>OUTCM</sub> )            | Offset Voltage, CLHI to V <sub>OUTCM</sub>                                         |                                                                                                    | • | -55          | 13    | 55          | mV       |

| VCLLODEFAULT                                            | Default Output Clamp Voltage, Low                                                  |                                                                                                    | • | 0.125        | 0.265 | 0.425       | V        |

| $V_{OS}$ (CLLO – $V_{OUTCM}$ )                          | Offset Voltage, CLLO to V <sub>OUTCM</sub>                                         |                                                                                                    | • | -120         | -70   | 0           | mV       |

| R <sub>CLHI</sub>                                       | CLHI Pin Input Resistance                                                          | V <sub>CLHI</sub> = 2.45V                                                                          |   | 3            | 4.1   | 5           | kΩ       |

| IB <sub>CLHI</sub>                                      | CLHI Pin Bias Current                                                              | V <sub>CLHI</sub> = 2.45V                                                                          |   | -25          | -1    | 25          | μA       |

| R <sub>CLLO</sub>                                       | CLLO Pin Input Resistance                                                          | V <sub>CLL0</sub> = 0.275V                                                                         | • | 1.5          | 2.3   | 3.2         | kΩ       |

| IBCLLO                                                  | CLLO Pin Bias Current                                                              | V <sub>CLL0</sub> = 0.275V                                                                         |   | -25          | 4.5   | 25          | μA       |

| Power Supply                                            |                                                                                    |                                                                                                    |   |              |       |             |          |

| VS                                                      | Supply Voltage Range                                                               |                                                                                                    |   | 2.7          |       | 3.9         | V        |

| I <sub>S</sub>                                          | Supply Current                                                                     |                                                                                                    | • | 33           | 42    | 51<br>54    | mA<br>mA |

| PSRR                                                    | Power Supply Rejection Ratio                                                       | V <sub>S</sub> = 2.7V to 3.6V                                                                      |   | 57.5         | 80    |             | dB       |

|                                                         |                                                                                    |                                                                                                    |   |              |       |             |          |

**3.3V ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . V<sup>+</sup> = 3.3V, GND = 0V, No  $R_{LOAD}$ ,  $C_{LOAD} = 6pE$ .  $V_{CM} = 1.25V$ , CLHI = V<sup>+</sup>, CLLO = 0V unless otherwise noted.  $V_{INCM}$  is defined as  $(IN^+ + IN^-)/2$ .  $V_{OUTCM}$  is defined as  $(OUT^+ + OUT^-)/2$ .  $V_{INDIFF}$  is defined as  $(OUT^+ - IN^-)$ .  $V_{OUTDIFF}$  is defined as  $(OUT^+ - OUT^-)$ . See DC test circuit schematic.

| SYMBOL                        | PARAMETER                                                             | CONDITIONS                                                                                                                                     |   | MIN          | ТҮР      | MAX         | UNITS                                |

|-------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|----------|-------------|--------------------------------------|

| Input/Output Characte         | ristics                                                               | 1                                                                                                                                              |   |              |          |             | 1                                    |

| G <sub>DIFF</sub>             | Differential Gain                                                     | $V_{INDIFF} = \pm 1.2V$                                                                                                                        | • | -0.3<br>-0.4 | -0.15    | 0<br>0      | dB<br>dB                             |

| TCG <sub>DIFF</sub>           | Differential Gain Temperature Coefficient                             |                                                                                                                                                |   |              | -0.00033 |             | dB/°C                                |

| V <sub>OUTDIFF</sub>          | Differential Output Voltage Swing                                     | $V_{INDIFF} = \pm 2.3V$                                                                                                                        | • | 3.5<br>3.2   | 4        |             | V <sub>P-P</sub><br>V <sub>P-P</sub> |

| V <sub>OUTMIN</sub>           | Output Voltage Swing Low                                              | Single-Ended Measurement of OUT <sup>+</sup> , OUT <sup>-</sup> . $V_{INDIFF} = \pm 2.3V$                                                      | • |              | 0.2      | 0.3<br>0.35 | V<br>V                               |

| V <sub>OUTMAX</sub>           | Output Voltage Swing High                                             | Single-Ended Measurement of OUT <sup>+</sup> , OUT <sup>-</sup> . $V_{INDIFF} = \pm 2.3V$                                                      | • | 2.05<br>1.95 | 2.2      |             | V<br>V                               |

| I <sub>OUT</sub>              | Output Current Drive (Note 4)                                         | Single-Ended Measurement of OUT <sup>+</sup> , OUT <sup>-</sup>                                                                                | • | ±20          |          |             | mA                                   |

| V <sub>0S</sub>               | Differential Input Offset Voltage                                     | $IN^+ = IN^- = 1.25V$ , $V_{OS} = V_{OUTDIFF}/G_{DIFF}$                                                                                        | • | 5<br>10      | -0.1     | 5<br>10     | mV<br>mV                             |

| TCV <sub>OS</sub>             | Differential Input Offset Voltage Drift                               |                                                                                                                                                | • |              | 1        |             | μV/°C                                |

| V <sub>IOCM</sub>             | Common Mode Offset Voltage, Input to Output                           | V <sub>OUTCM</sub> – V <sub>INCM</sub>                                                                                                         | • | -65<br>-75   | -40      | -15<br>-5   | mV<br>mV                             |

| IVR <sub>MIN</sub>            | Input Voltage Range, IN+, IN <sup>-</sup><br>(Minimum) (Single-Ended) | Defined by Output Voltage Swing Test                                                                                                           | • |              |          | 0.1         | V                                    |

| IVR <sub>MAX</sub>            | Input Voltage Range, IN+, IN <sup>-</sup><br>(Maximum) (Single-Ended) | Defined by Output Voltage Swing Test                                                                                                           | • | 2.4          |          |             | V                                    |

| I <sub>B</sub>                | Input Bias Current, IN+, IN-                                          | $IN^{+} = IN^{-} = 1.25V$                                                                                                                      |   | -15          | -4       | 15          | μA                                   |

| R <sub>INDIFF</sub>           | Differential Input Resistance                                         | $V_{INDIFF} = \pm 1.2V$                                                                                                                        |   | 9            | 12       | 15          | kΩ                                   |

| CINDIFF                       | Differential Input Capacitance                                        |                                                                                                                                                |   |              | 1        |             | pF                                   |

| RINCM                         | Input Common Mode Resistance                                          | $IN^+ = IN^- = 0.65V \text{ to } 1.85V$                                                                                                        |   |              | 6        |             | kΩ                                   |

| CMRR                          | Common Mode Rejection Ratio                                           | $ \begin{array}{l} IN^{+} = IN^{-} = 0.65V \text{ to } 1.85V = \Delta V_{INCM}, \\ CMRR = (V_{OUTDIFF}/G_{DIFF}/\Delta V_{INCM}) \end{array} $ | • | 63.5<br>59.6 | 83       |             | dB<br>dB                             |

| e <sub>N</sub>                | Input Noise Voltage Density                                           | f = 100kHz                                                                                                                                     |   |              | 1.8      |             | nV/√Hz                               |

| i <sub>N</sub>                | Input Noise Current Density                                           | f = 100kHz                                                                                                                                     |   |              | 6.5      |             | pA/√Hz                               |

| Output Common Mode            | e Voltage Control                                                     | 1                                                                                                                                              |   |              |          |             |                                      |

| G <sub>CM</sub>               | V <sub>CM</sub> Pin Common Mode Gain                                  | V <sub>CM</sub> = 0.65V to 1.85V                                                                                                               | ٠ | 0.9          | 0.96     | 1.05        | V/V                                  |

| VINCMDEFAULT                  | Default Input Common Mode Voltage                                     | V <sub>INCM</sub> . IN <sup>+</sup> , IN <sup>-</sup> , V <sub>CM</sub> Pin Floating                                                           | ٠ | 1.2          | 1.28     | 1.35        | V                                    |

| $V_{OS} (V_{CM} - V_{INCM})$  | Offset Voltage, V <sub>CM</sub> to V <sub>INCM</sub>                  | $V_{CM} - V_{INCM}, V_{CM} = 1.25V$                                                                                                            | ٠ | -70          | -26      | 70          | mV                                   |

| VOUTCMDEFAULT                 | Default Output Common Mode Voltage                                    | Inputs Floating, V <sub>CM</sub> Pin Floating                                                                                                  | • | 1.15         | 1.24     | 1.35        | V                                    |

| $V_{OS} (V_{CM} - V_{OUTCM})$ | Offset Voltage, V <sub>CM</sub> to V <sub>OUTCM</sub>                 | $V_{CM} - V_{OUTCM}, V_{CM} = 1.25V$                                                                                                           | ٠ | -60          | 14       | 60          | mV                                   |

| Voutcmmin                     | Output Common Mode Voltage<br>(Minimum)                               | V <sub>CM</sub> = 0.1V                                                                                                                         | • |              | 0.34     | 0.5<br>0.55 | V<br>V                               |

| V <sub>OUTCMMAX</sub>         | Output Common Mode Voltage<br>(Maximum)                               | V <sub>CM</sub> = 2.4V                                                                                                                         | • | 2.05<br>2    | 2.16     |             | V<br>V                               |

| V <sub>CMDEFAULT</sub>        | V <sub>CM</sub> Pin Default Voltage                                   |                                                                                                                                                | ٠ | 1.2          | 1.25     | 1.3         | V                                    |

| R <sub>VCM</sub>              | V <sub>CM</sub> Pin Input Resistance                                  |                                                                                                                                                |   | 2.5          | 3.8      | 5.1         | kΩ                                   |

| C <sub>VCM</sub>              | V <sub>CM</sub> Pin Input Capacitance                                 |                                                                                                                                                |   |              | 1        |             | pF                                   |

| BVCM                          | V <sub>CM</sub> Pin Bias Current                                      | V <sub>CM</sub> = 1.25V                                                                                                                        |   | -10          | 0.2      | 10          | μA                                   |

**3.3V ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . V<sup>+</sup> = 3.3V, GND = 0V, No  $R_{LOAD}$ ,  $C_{LOAD} = 6pF$ .  $V_{CM} = 1.25V$ , CLHI = V<sup>+</sup>, CLLO = 0V unless otherwise noted.  $V_{INCM}$  is defined as  $(IN^+ + IN^-)/2$ .  $V_{OUTCM}$  is defined as  $(OUT^+ + OUT^-)/2$ .  $V_{INDIFF}$  is defined as  $(IN^+ - IN^-)$ .  $V_{OUTDIFF}$  is defined as  $(OUT^+ - OUT^-)$ . See DC test circuit schematic.

| SYMBOL                                       | PARAMETER                                  | CONDITIONS                 |       | MIN  | ТҮР  | MAX | UNITS    |

|----------------------------------------------|--------------------------------------------|----------------------------|-------|------|------|-----|----------|

| DC Clamping Characte                         | ristics                                    |                            |       |      |      |     | <u> </u> |

| V <sub>CLHIDEFAULT</sub>                     | Default Output Clamp Voltage, High         |                            | •     | 2.1  | 2.23 | 2.4 | V        |

| V <sub>OS</sub> (CLHI – V <sub>OUTCM</sub> ) | Offset Voltage, CLHI to V <sub>OUTCM</sub> |                            | •     | -55  | 4    | 55  | mV       |

| VCLLODEFAULT                                 | Default Output Clamp Voltage, Low          |                            | •     | 0.1  | 0.25 | 0.4 | V        |

| V <sub>OS</sub> (CLLO – V <sub>OUTCM</sub> ) | Offset Voltage, CLLO to V <sub>OUTCM</sub> |                            | •     | -120 | -72  | 0   | mV       |

| R <sub>CLHI</sub>                            | CLHI Pin Input Resistance                  | V <sub>CLHI</sub> = 2.25V  | •     | 3    | 4.1  | 5   | kΩ       |

| IB <sub>CLHI</sub>                           | CLHI Pin Bias Current                      | V <sub>CLHI</sub> = 2.25V  | •     | -25  | -1   | 25  | μA       |

| R <sub>CLLO</sub>                            | CLLO Pin Input Resistance                  | V <sub>CLL0</sub> = 0.25V  | •     | 1.5  | 2.3  | 3.2 | kΩ       |

| IBCLLO                                       | CLLO Pin Bias Current                      | V <sub>CLL0</sub> = 0.25V  | •     | -25  | 3    | 25  | μA       |

| Power Supply                                 |                                            |                            | · · · |      |      |     | <u> </u> |

| V <sub>S</sub>                               | Supply Voltage Range                       |                            | •     | 2.7  |      | 3.9 | V        |

| Is                                           | Supply Current                             |                            |       | 33   | 42   | 51  | mA       |

|                                              |                                            |                            | •     |      |      | 54  | mA       |

| PSRR                                         | Power Supply Rejection Ratio               | $V_{\rm S}$ = 2.7V to 3.6V | •     | 57.5 | 80   |     | dB       |

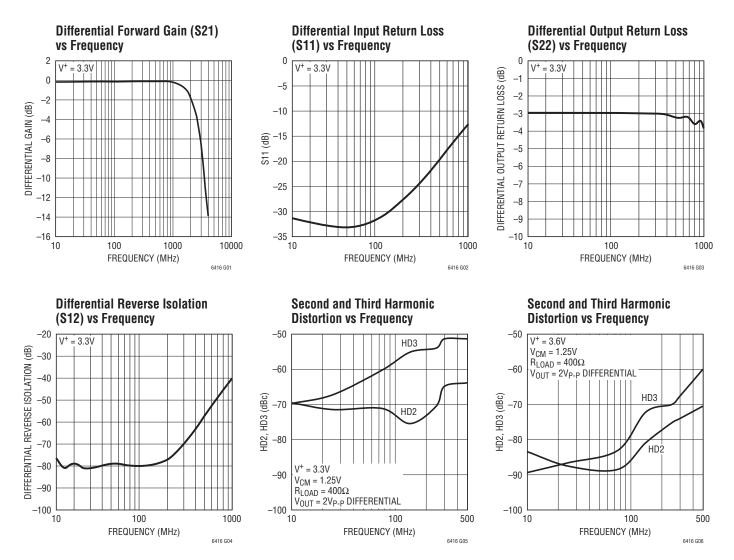

## AC ELECTRICAL CHARACTERISTICS The • denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . V<sup>+</sup> = 3.3V and 3.6V unless otherwise noted, GND = 0V, No R<sub>LOAD</sub>, C<sub>LOAD</sub> = 6pF. V<sub>CM</sub> = 1.25V, CLHI = V<sub>CC</sub>, CLLO = 0V unless otherwise noted. V<sub>INCM</sub> is defined as (IN<sup>+</sup> + IN<sup>-</sup>)/2. V<sub>OUTCM</sub> is defined as (OUT<sup>+</sup> + OUT<sup>-</sup>)/2. V<sub>INDIFF</sub> is defined as (IN<sup>+</sup> - IN<sup>-</sup>). V<sub>OUTDIFF</sub> is defined as (OUT<sup>+</sup> - OUT<sup>-</sup>). See DC test circuit schematic.

| SYMBOL                | PARAMETER                                  | CONDITIONS                                                                                                                                                                                                                            | MIN | ТҮР                            | MAX | UNITS                                        |

|-----------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------|-----|----------------------------------------------|

| Differential A        | C Characteristics                          | ,                                                                                                                                                                                                                                     |     |                                |     | <u>.                                    </u> |

| –3dBBW                | –3dB Bandwidth                             | 200mV <sub>P-P,OUT</sub> Differential                                                                                                                                                                                                 |     | 2                              |     | GHz                                          |

| 0.1dBBW               | ±0.1dB Bandwidth                           | 200mV <sub>P-P,OUT</sub> Differential                                                                                                                                                                                                 |     | 0.3                            |     | GHz                                          |

| 0.5dBBW               | ±0.5dB Bandwidth                           | 200mV <sub>P-P,OUT</sub> Differential                                                                                                                                                                                                 |     | 1.4                            |     | GHz                                          |

| 1/f                   | 1/f Noise Corner                           |                                                                                                                                                                                                                                       |     | 25                             |     | kHz                                          |

| SR                    | Slew Rate                                  | Differential                                                                                                                                                                                                                          |     | 3.4                            |     | V/ns                                         |

| t <sub>S1%</sub>      | 1% Settling Time                           | 2V <sub>P-P,OUT</sub>                                                                                                                                                                                                                 |     | 1.8                            |     | ns                                           |

| Common Mod            | e AC Characteristics (V <sub>CM</sub> Pin) |                                                                                                                                                                                                                                       | ,   |                                |     |                                              |

| -3dBBW <sub>VCM</sub> | V <sub>CM</sub> Pin Small Signal –3dB BW   | V <sub>CM</sub> = 0.1V <sub>P-P</sub> , Measured Single-Ended<br>at Output                                                                                                                                                            |     | 9                              |     | MHz                                          |

| SR <sub>CM</sub>      | Common Mode Slew Rate                      | Measured Single-Ended at Output                                                                                                                                                                                                       |     | 40                             |     | V/µs                                         |

| AC Clamping           | Characteristics                            |                                                                                                                                                                                                                                       |     |                                |     |                                              |

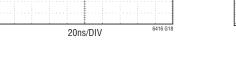

| t <sub>OVDR</sub>     | Overdrive Recovery Time                    | 1.9V <sub>P-P,OUT</sub>                                                                                                                                                                                                               |     | 5                              |     | ns                                           |

| AC Linearity          | ·                                          |                                                                                                                                                                                                                                       |     |                                |     | <u>.</u>                                     |

| 70MHz Signa           |                                            |                                                                                                                                                                                                                                       |     |                                |     |                                              |

| HD2                   | Second Harmonic Distortion                 | $ \begin{array}{l} V^{+}=3.3V, V_{CM}=1.05V, V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.3V, V_{CM}=1.25V, V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.6V, V_{CM}=1.05V, V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.6V, V_{CM}=1.25V, V_{OUTDIFF}=2V_{P-P} \end{array} $ |     | -83.5<br>-71<br>-78.5<br>-88.5 |     | dBc<br>dBc<br>dBc<br>dBc<br>dBc              |

**AC ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . V<sup>+</sup> = 3.3V and 3.6V unless otherwise noted, GND = 0V, No R<sub>LOAD</sub>, C<sub>LOAD</sub> = 6pF. V<sub>CM</sub> = 1.25V, CLHI = V<sub>CC</sub>, CLLO = 0V unless otherwise noted. V<sub>INCM</sub> is defined as (IN<sup>+</sup> + IN<sup>-</sup>)/2. V<sub>OUTCM</sub> is defined as (OUT<sup>+</sup> + OUT<sup>-</sup>)/2. V<sub>INDIFF</sub> is defined as (IN<sup>+</sup> - IN<sup>-</sup>). V<sub>OUTDIFF</sub> is defined as (OUT<sup>+</sup> - OUT<sup>-</sup>). See DC test circuit schematic.

| SYMBOL     | PARAMETER                                             | CONDITIONS                                                                                                                                                                                                                                                     | MIN | ТҮР                          | MAX | UNITS                           |

|------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------|-----|---------------------------------|

| HD3        | Third Harmonic Distortion                             | $ \begin{array}{l} V^{+}=3.3V, \ V_{CM}=1.05V, \ V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.3V, \ V_{CM}=1.25V, \ V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.6V, \ V_{CM}=1.05V, \ V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.6V, \ V_{CM}=1.25V, \ V_{OUTDIFF}=2V_{P-P} \\ \end{array} $       |     | -73<br>-60<br>-94.5<br>-83   |     | dBc<br>dBc<br>dBc<br>dBc<br>dBc |

| IM3        | Output Third Order Intermodulation<br>Distortion      |                                                                                                                                                                                                                                                                |     | -76.5<br>-86                 |     | dBc<br>dBc                      |

| OIP3       | Output Third Order Intercept (Equivalent)<br>(Note 5) |                                                                                                                                                                                                                                                                |     | 42.25<br>47                  |     | dBm<br>dBm                      |

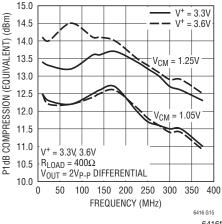

| P1dB       | Output 1dB Compression Point (Equivalent)<br>(Note 5) | V <sup>+</sup> = 3.6V, V <sub>CM</sub> = 1.25V                                                                                                                                                                                                                 |     | 14.1                         |     | dBm                             |

| 140MHz Sig | nal                                                   |                                                                                                                                                                                                                                                                |     |                              |     |                                 |

| HD2        | Second Harmonic Distortion                            | $ \begin{array}{l} V^{+}=3.3V, V_{CM}=1.05V, V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.3V, V_{CM}=1.25V, V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.6V, V_{CM}=1.05V, V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.6V, V_{CM}=1.25V, V_{OUTDIFF}=2V_{P-P} \end{array} $                          |     | -79.5<br>-75.5<br>-73<br>-81 |     | dBc<br>dBc<br>dBc<br>dBc<br>dBc |

| HD3        | Third Harmonic Distortion                             | $ \begin{array}{l} V^{+}=3.3V, \ V_{CM}=1.05V, \ V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.3V, \ V_{CM}=1.25V, \ V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.6V, \ V_{CM}=1.05V, \ V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.6V, \ V_{CM}=1.25V, \ V_{OUTDIFF}=2V_{P-P} \\ \end{array} $       |     | 64<br>55<br>70<br>72         |     | dBc<br>dBc<br>dBc<br>dBc<br>dBc |

| IM3        | Output Third Order Intermodulation<br>Distortion      |                                                                                                                                                                                                                                                                |     | -75<br>-84.5                 |     | dBc<br>dBc                      |

| OIP3       | Output Third Order Intercept (Equivalent)<br>(Note 5) | $V^+ = 3.3V$ , $V_{CM} = 1.05V$ , $V_{OUTDIFF} = 2V_{P-P}$<br>$V^+ = 3.6V$ , $V_{CM} = 1.25V$ , $V_{OUTDIFF} = 2V_{P-P}$                                                                                                                                       |     | 41.5<br>46.25                |     | dBm<br>dBm                      |

| P1dB       | Output 1dB Compression Point (Equivalent)<br>(Note 5) | V+ = 3.6V, V <sub>CM</sub> = 1.25V                                                                                                                                                                                                                             |     | 14.1                         |     | dBm                             |

| 300MHz Sig | nal                                                   |                                                                                                                                                                                                                                                                |     |                              |     |                                 |

| HD2        | Second Harmonic Distortion                            | $ \begin{array}{l} V^{+}=3.3V, V_{CM}=1.05V, V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.3V, V_{CM}=1.25V, V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.6V, V_{CM}=1.05V, V_{OUTDIFF}=2V_{P-P} \\ V^{+}=3.6V, V_{CM}=1.25V, V_{OUTDIFF}=2V_{P-P} \end{array} $                          |     | 75<br>65<br>69.5<br>74       |     | dBc<br>dBc<br>dBc<br>dBc<br>dBc |

| HD3        | Third Harmonic Distortion                             | $\begin{array}{l} V^{+}=3.3V, V_{CM}=1.05V, V_{OUTDIFF}=2V_{P-P}\\ V^{+}=3.3V, V_{CM}=1.25V, V_{OUTDIFF}=2V_{P-P}\\ V^{+}=3.6V, V_{CM}=1.05V, V_{OUTDIFF}=2V_{P-P}\\ V^{+}=3.6V, V_{CM}=1.25V, V_{OUTDIFF}=2V_{P-P} \end{array}$                               |     | 59<br>51.5<br>63<br>67.5     |     | dBc<br>dBc<br>dBc<br>dBc<br>dBc |

| IM3        | Output Third Order Intermodulation<br>Distortion      | $ \begin{array}{l} V^{+}=3.3 \text{V}, \text{V}_{\text{CM}}=1.05 \text{V}, \text{V}_{\text{OUTDIFF}}=2 \text{V}_{\text{P-P}} \\ \text{V}^{+}=3.6 \text{V}, \text{V}_{\text{CM}}=1.25 \text{V}, \text{V}_{\text{OUTDIFF}}=2 \text{V}_{\text{P-P}} \end{array} $ |     | -68.5<br>-72.5               | -64 | dBc<br>dBc                      |

| OIP3       | Output Third Order Intercept (Equivalent)<br>(Note 5) | $ \begin{array}{l} V^{+}=3.3 \text{V}, \text{V}_{\text{CM}}=1.05 \text{V}, \text{V}_{\text{OUTDIFF}}=2 \text{V}_{\text{P-P}} \\ \text{V}^{+}=3.6 \text{V}, \text{V}_{\text{CM}}=1.25 \text{V}, \text{V}_{\text{OUTDIFF}}=2 \text{V}_{\text{P-P}} \end{array} $ | 36  | 38.25<br>40.25               |     | dBm<br>dBm                      |

| P1dB       | Output 1dB Compression Point (Equivalent)<br>(Note 5) | V <sup>+</sup> = 3.6V, V <sub>CM</sub> = 1.25V                                                                                                                                                                                                                 |     | 12.9                         |     | dBm                             |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC6416C/LTC6416I is guaranteed functional over the operating temperature range of -40°C to 85°C.

Note 3: The LTC6416C is guaranteed to meet specified performance from 0°C to 70°C. It is designed, characterized and expected to meet specified performance from -40°C and 85°C but is not tested or QA sampled

at these temperatures. The LT6416I is guaranteed to meet specified performance from -40°C to 85°C.

Note 4: This parameter is pulse tested.

Note 5: Since the LTC6416 is a voltage-output buffer, a resistive load is not required when driving an AD converter. Therefore, typical output power is very small. In order to compare the LTC6416 with amplifiers that require a  $50\Omega$ output load, the LTC6416 output voltage swing driving a given R<sub>1</sub> is converted to OIP3 and P1dB as if it were driving a 50 $\Omega$  load. Using this modified convention, 2V<sub>P-P</sub> is by definition equal to 10dBm, regardless of actual R<sub>I</sub>.

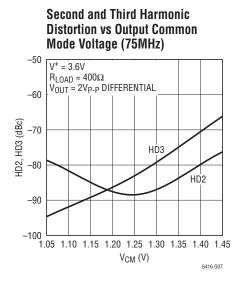

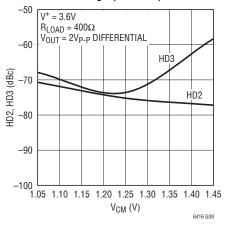

Second and Third Harmonic Distortion vs Output Common Mode Voltage (300MHz)

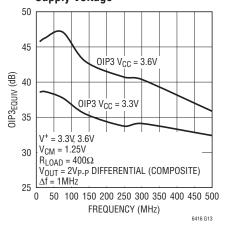

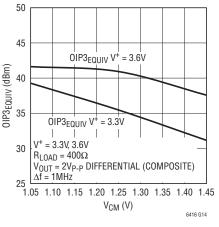

Output Third Order Intercept (OIP3<sub>EQUIV</sub>) vs Frequency and Supply Voltage

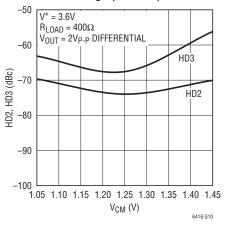

Second and Third Harmonic Distortion vs Output Common Mode Voltage (140MHz)

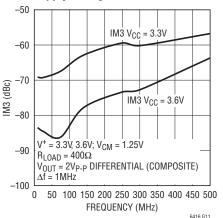

Third Order Intermodulation Distortion (IM3) vs Frequency and Supply Voltage

Output Third Order Intercept (OIP3<sub>EQUIV</sub>) vs Output Common Mode Voltage and Supply Voltage (140MHz)

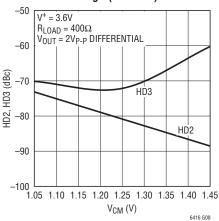

Second and Third Harmonic Distortion vs Output Common Mode Voltage (250MHz)

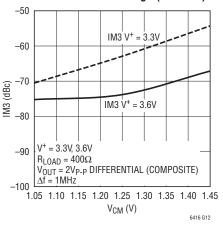

#### Third Order Intermodulation Distortion (IM3) vs Output Common Mode Voltage (140MHz)

Output 1dB Compression (Equivalent) vs Frequency, V<sub>CM</sub> and Supply Voltage

500ps/DIV

20ns/DIV

6416 G19

#### Small Signal Transient Response, Falling Edge

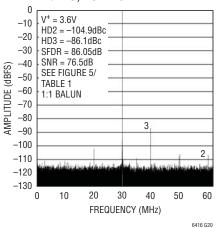

#### LTC6416 Driving LTC2208 16-Bit ADC, 64K Point FFT, f<sub>IN</sub> = 30MHz, -1dBFS, PGA = 1

9

## PIN FUNCTIONS

**V<sub>CM</sub> (Pin 1):** This pin sets the output common mode voltage seen at OUT<sup>+</sup> and OUT<sup>-</sup> by driving IN<sup>+</sup> and IN<sup>-</sup> through an internal buffer with a high output resistance of 6k. The V<sub>CM</sub> pin has a Thevenin equivalent resistance of approximately 3.8k and can be overdriven by an external voltage. If no voltage is applied to V<sub>CM</sub>, it will float to a default voltage of approximately 1.25V on a 3.3V supply or 1.36V on a 3.6V supply. The V<sub>CM</sub> pin should be bypassed with a high-quality ceramic bypass capacitor of at least 0.1µF.

**CLHI (Pin 2):** High Side Clamp Voltage. The voltage applied to the CLHI pin defines the upper voltage limit of the OUT<sup>+</sup> and OUT<sup>-</sup> pins. This voltage should be set at least 300mV above the upper voltage range of the driven ADC. On a 3.3V supply, the CLHI pin will float to a 2.23V default voltage. On a 3.6V supply, the CLHI pin will float to a 2.45V default voltage. CLHI has a Thevenin equivalent of approximately 4.1k $\Omega$  and can be overdriven by an external voltage. The CLHI pin should be bypassed with a high-quality ceramic bypass capacitor of at least 0.1µE.

**IN<sup>+</sup>,IN<sup>-</sup> (Pins 3, 4):** Non-inverting and inverting input pins of the buffer, respectively. These pins are high impedance, approximately  $6k\Omega$ . If AC-coupled, these pins will self bias to the voltage present at the V<sub>CM</sub> pin.

**CLLO (Pin 5):** Low Side Clamp Voltage. The voltage applied to the CLLO pin defines the lower voltage limit of the OUT<sup>+</sup> and OUT<sup>-</sup> pins. This voltage should be set at least 300mV below the lower voltage range of the driven

ADC. On a 3.3V supply, the CLLO pin will float to a 0.25V default voltage. On a 3.6V supply, the CLLO pin will float to a 0.265V default voltage. CLLO has a Thevenin equivalent resistance of approximately 2.3k and can be overdriven by an external voltage. The CLLO pin should be bypassed with a high quality ceramic bypass capacitor of at least 0.1µF.

**GND (Pins 6, 9, 11):** Negative power supply, normally tied to ground. Both pins and the exposed paddle must be tied to the same voltage. GND may be tied to a voltage other than ground as long as the voltage between V<sup>+</sup> and GND is 2.7V to 4V. If the GND pins are not tied to ground, bypass them with 680pF and 0.1µF capacitors as close to the package as possible.

**OUT<sup>-</sup>, OUT<sup>+</sup> (Pins 7, 8):** Outputs. The LTC6416 outputs are low impedance. Each output has an output impedance of approximately  $9\Omega$  at DC.

**V**<sup>+</sup> (**Pin 10**): Positive Power Supply. Typically 3.3V to 3.6V. Split supplies are possible as long as the voltage between V<sup>+</sup> and GND is 2.7V to 4V. Bypass capacitors of 680pF and 0.1 $\mu$ F as close to the part as possible should be used between the supplies.

**Exposed Pad (Pin 11):** Ground. The exposed pad must be soldered to the printed circuit board ground plane for good heat transfer. If GND is a voltage other than ground, the Exposed Pad must be connected to a plane with the same potential as the GND pins – Not to the system ground plane.

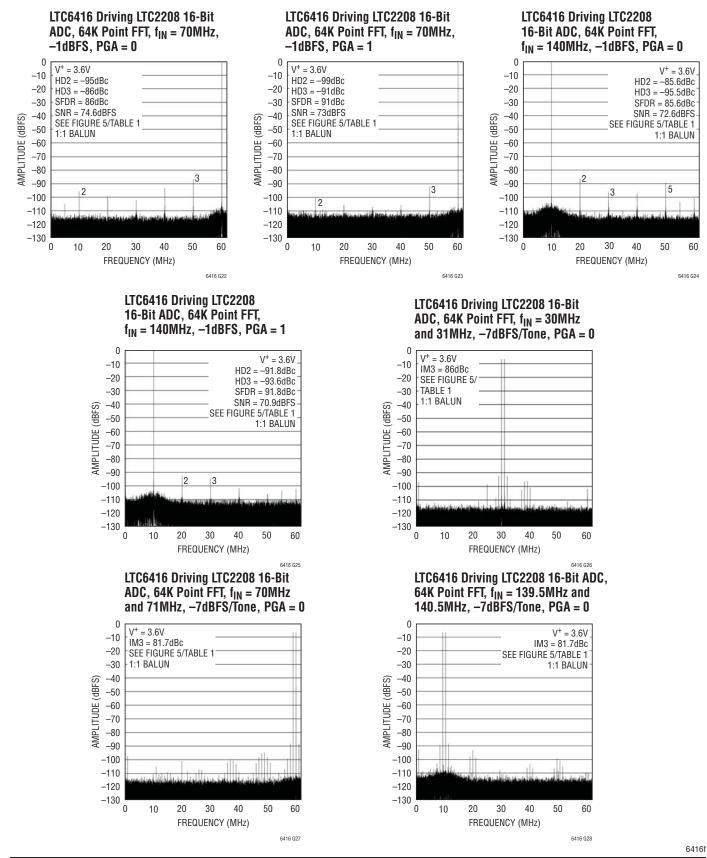

## DC TEST CIRCUIT SCHEMATIC

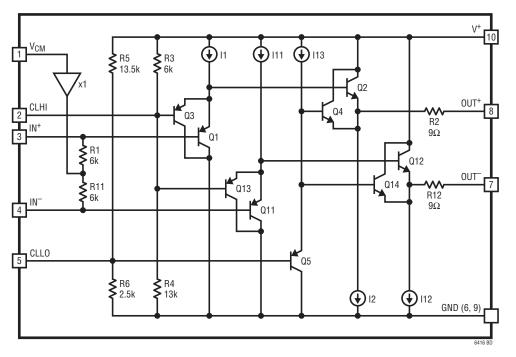

# **BLOCK DIAGRAM**

LTC6416 Simplified Schematic

### **Circuit Operation**

The LTC6416 is a low noise and low distortion fully differential unity-gain ADC driver with operation from DC to 2GHz (-3dB bandwidth), a differential input impedance of  $12k\Omega$ , and a differential output impedance of  $18\Omega$ . The LTC6416 is composed of a fully differential buffer with output common mode voltage control circuitry and high speed voltage-limiting clamps at the output. Small output resistors of  $9\Omega$  improve the circuit stability over various load conditions. They also simplify possible external filtering options, which are often desirable when the load is an ADC. Lowpass or bandpass filters are easily implemented with just a few external components. The LTC6416 is very flexible in terms of I/O coupling. It can be AC- or DCcoupled at the inputs, the outputs or both. When using the LTC6416 with DC-coupled inputs, best performance is obtained with an input common mode voltage between 1V and 1.5V. For AC-coupled operation, the LTC6416 will take the voltage applied to the  $V_{CM}$  pin and use it to bias the inputs so that the output common mode voltage equals  $V_{CM}$ , thus no external circuitry is needed. The  $V_{CM}$  pin has been designed to directly interface with the V<sub>CM</sub> pin found on Linear Technology's 16-, 14- and 12-bit high speed ADC families.

### Input Impedance and Matching

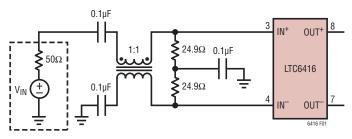

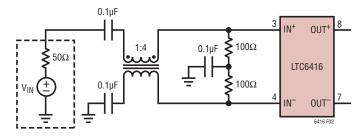

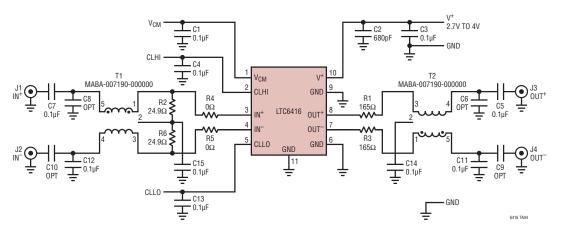

The LTC6416 has a high differential input impedance of  $12k\Omega$ . The differential inputs may need to be terminated to a lower value impedance, e.g.  $50\Omega$ , in order to provide an impedance match for the source. Figure 1 shows input

matching using a 1:1 balun, while Figure 2 shows matching using a 1:4 balun. These circuits provide a wideband impedance match. The balun and matching resistors must be placed close to the input pins in order to minimize the rejection due to input mismatch. In Figure 1, the capacitor center-tapping the two  $24.9\Omega$  resistors improves high frequency common mode rejection. As an alternative to this wideband approach, a narrowband impedance match can be used at the inputs of the LTC6416 for frequency selection and/or noise reduction.

The noise performance of the LTC6416 also depends upon the source impedance and termination. For example, the input 1:4 balun in Figure 2 improves SNR by adding 6dB of voltage gain at the inputs. A trade-off between gain and noise is obvious when constant noise figure circle and constant gain circle are plotted within the same input Smith Chart. This technique can be used to determine the optimal source impedance for a given gain and noise requirement.

### **Output Match and Filter**

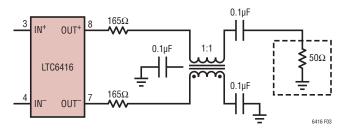

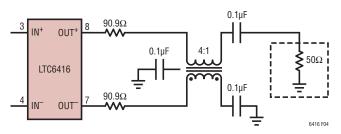

The LTC6416 provides a source resistance of  $9\Omega$  at each output. For testing purposes, Figure 3 and Figure 4 show the LTC6416 driving a differential 400 $\Omega$  load impedance using a 1:1 or 1:4 balun, respectively.

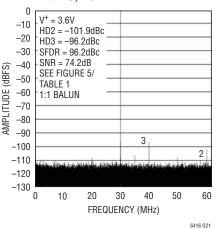

The LTC6416 can drive an ADC directly without external output impedance matching, but improved performance can usually be obtained with the addition of a few external components. Figure 5 shows a typical topology used for driving the LTC2208 16-bit ADC.

Figure 1. Input Termination for Differential 50 $\Omega$  Input Impedance Using a 1:1 Balun

6416

Figure 2. Input Termination for Differential 50 $\Omega$  Input Impedance Using a 1:4 Balun

Figure 3. Output Termination for Differential 400  $\Omega$  Load Impedance Using a 1:1 Balun

Figure 4. Output Termination for Differential 400  $\Omega$  Load Impedance Using a 4:1 Balun

Figure 5. DC1257B Simplified Schematic with Suggested Output Termination for Driving an LTC2208 16-Bit ADC at 140MHz

As seen in Table 1, suggested component values for the filter will change for differing IF frequencies.

| lable 1.           |                             |                         |

|--------------------|-----------------------------|-------------------------|

| INPUT<br>Frequency | LTC6416 OUTPUT<br>RESISTORS | FILTERING<br>Capacitors |

| 30MHz              | 50Ω                         | 5.6pF/6.8pF/5.6pF       |

| 70MHz              | 25Ω                         | 5.6pF/6.8pF/5.6pF       |

| 140MHz             | 25Ω                         | 1.5pF/1pF/1.5pF         |

| 250MHz             | 5Ω                          | -/-/-                   |

Table 1.

### **Output Common Mode Adjustment**

The output common mode voltage is set by the V<sub>CM</sub> pin. Because the input common mode voltage is approximately the same as the output common mode voltage, both are approximately equal to V<sub>CM</sub>. The V<sub>CM</sub> pin has a Thevenin equivalent resistance of 3.8k and can be overdriven by an external voltage. The V<sub>CM</sub> pin floats to a default voltage of 1.25V on a 3.3V supply and 1.36V on a 3.6V supply. The output common mode voltage is capable of tracking V<sub>CM</sub> in a range from 0.34V to 2.16V on a 3.3V supply. The V<sub>CM</sub> pin can be floated, but it should always be bypassed close to the LTC6416 with a 0.1µF bypass capacitor to ground. When interfacing with A/D converters such as the LTC22xx families, the V<sub>CM</sub> pin can be connected to the V<sub>CM</sub> output pin of the ADC, as shown in Figure 5.

### **CLLO and CLHI Pins**

The CLLO and CLHI pins are used to set the clamping voltage for high speed internal circuitry. This circuitry limits the single-ended minimum and maximum voltage excursion seen at each of the outputs. This feature is extremely important in applications with input signals having very large peak-to-average ratios such as cellular basestation receivers. If a very large peak signal arrives at the LTC6416, the voltages applied to the CLLO and CLHI pins will determine the minimum and maximum output swing respectively. Once the input signal returns to the normal operating range, the LTC6416 returns to linear operation within 5ns. Both CLLO and CLHI are high impedance inputs. CLLO has an input impedance of 2.3k, while CLHI has an input impedance of 4.1k. On a 3.3V supply, CLLO self-biases to 0.25V while CLHI self-biases

to 2.23V. On a 3.6V supply, CLLO self-biases to 0.265V while CLHI self-biases to 2.45V. Both CLLO and CLHI pins should be bypassed with a 0.1 $\mu$ F capacitor as close to the LTC6416 as possible.

### Interfacing the LTC6416 to A/D Converters

The LTC6416 has been specifically designed to interface directly with high speed A/D converters. It is possible to drive the ADC directly from the LTC6416. In practice, however, better performance may be obtained by adding a few external components at the output of the LTC6416. Figure 5 shows the LTC6416 being driven by a 1:8 transformer which provides 9dB of voltage gain while also performing a single-ended to differential conversion. The differential outputs of the LTC6416 are lowpass filtered, then drive the differential inputs of the LTC2208 ADC. In many applications, an anti-alias filter like this is desirable to limit the wideband noise of the amplifier. This is especially true in high performance 16-bit designs. The minimum recommended network between the LTC6416 and the ADC is simply two  $5\Omega$  series resistors, which are used to help eliminate resonances associated with the stray capacitance of PCB traces and the stray inductance of the internal bond wires at the ADC input, and the driver output pins.

## **Single-Ended Signals**

The LTC6416 has not been designed to convert singleended signals to differential signals. A single-ended input signal can be converted to a differential signal via a balun connected to the inputs of the LTC6416.

## **Power Supply Considerations**

For best linearity, the LTC6416 should have a positive supply of V<sup>+</sup> = 3.6V. The LTC6416 has an internal edge-triggered supply voltage clamp. The timing mechanism of the clamp enables the LTC6416 to withstand ESD events. This internal clamp is also activated by voltage overshoot and rapid slew rate on the positive supply V<sup>+</sup> pin. The LTC6416 should not be hot-plugged into a powered socket. Bypass capacitors of 680pF and 0.1µF should be placed to the V<sup>+</sup> pin, as close as possible to the LTC6416.

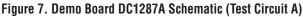

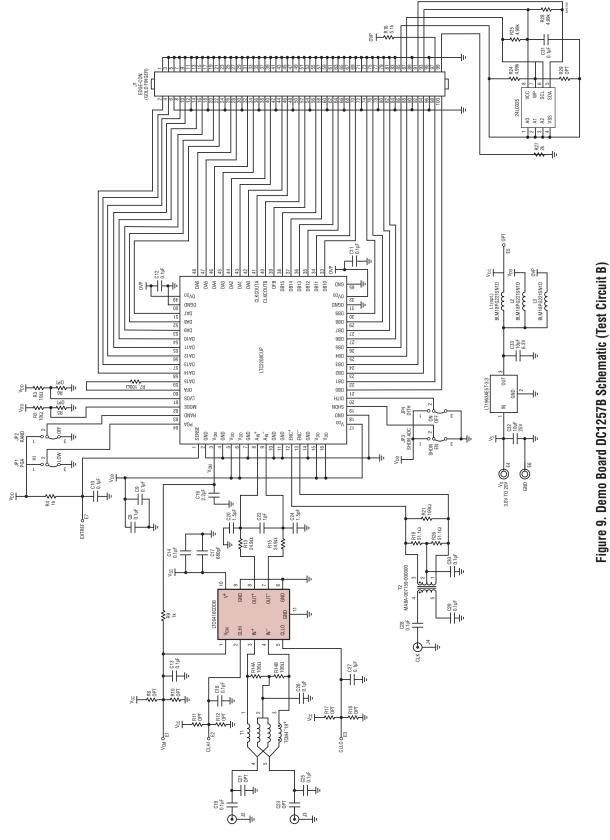

## Test Circuits

Due to the fully differential design of the LTC6416 and its usefulness in applications both with and without ADCs, two test circuits are used to generate the information in this data sheet. Test circuit A is Demo Board DC1287A, a two-port demonstration circuit for the LTC6416. The board layout and the schematic are shown in Figures 6 and 7. This circuit includes input and output 1:1 baluns for single-ended-to-differential conversion, allowing direct analysis using a 2-port network analyzer. In this circuit implementation, there are series resistors at the output to present the LTC6416 with a  $382\Omega$  differential load, thereby optimizing distortion performance. Including the 1:1 input and output baluns, the -3dB bandwidth is approximately 2GHz.

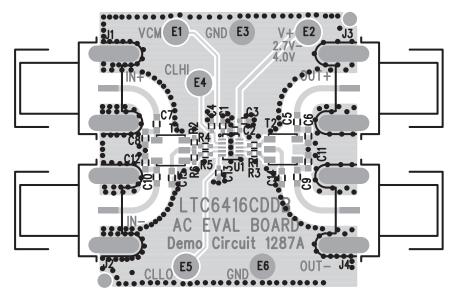

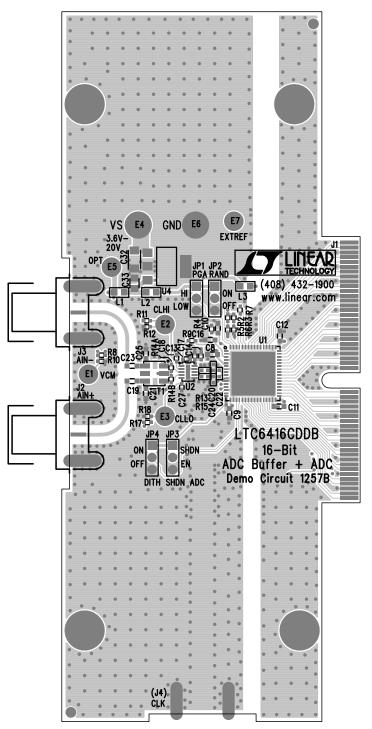

Test circuit B is Demo Circuit DC1257B. It consists of an LTC6416 driving an LTC2208 ADC. It is intended for use in conjunction with demo circuit DC890B (computer interface board) and proprietary Linear Technology evaluation software to evaluate the performance of both parts together. Both the DC1257B board layout and the schematic can be seen in Figures 8 and 9.

Figure 6. Demo Board DC1287A Layout

Figure 8. Demo Board DC1257B Layout

LINEAR TECHNOLOGY

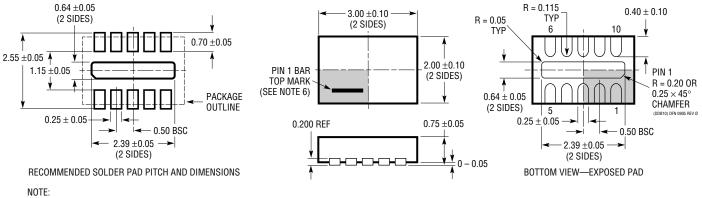

## PACKAGE DESCRIPTION

#### DDB Package 10-Lead Plastic DFN (3mm × 2mm)

(Reference LTC DWG # 05-08-1722 Rev Ø)

1. DRAWING CONFORMS TO VERSION (WECD-1) IN JEDEC PACKAGE OUTLINE M0-229

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# **TYPICAL APPLICATION**

DC1257B Simplified Schematic with Suggested Output Termination for Driving an LTC2208 16-Bit ADC at 140MHz

# **RELATED PARTS**

| PART NUMBER                                    | DESCRIPTION                                                                 | COMMENTS                                                                                                                                        |

|------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Fixed Gain IF Amplifiers/                      | ADC Drivers                                                                 |                                                                                                                                                 |

| LT1993-2/LT1993-4/<br>LT1993-10                | 800MHz Differential Amplifier/ADC Drivers                                   | -72dBc IM3 at 70MHz $2V_{P-P}$ Composite, $A_V = 2V/V$ , $4V/V$ , $10V/V$                                                                       |

| LTC6400-8/LTC6400-14/<br>LTC6400-20/LTC6400-26 | 1.8GHz Low Noise, Low Distortion Differential<br>ADC Drivers                | -71dBc IM3 at 240MHz 2V <sub>P-P</sub> Composite, I <sub>S</sub> = 90mA, AV = 8dB, 14dB, 20dB, 26dB                                             |

| LTC6401-8/LTC6401-14/<br>LTC6401-20/LTC6401-26 | 1.3GHz Low Noise, Low Distortion Differential<br>ADC Drivers                | -74dBc IM3 at 140MHz $2V_{P-P}$ Composite, I <sub>S</sub> = 50mA, AV = 8dB, 14dB, 20dB, 26dB                                                    |

| LT6402-6/LT6402-12/<br>LT6402-20               | 300MHz Differential Amplifier/ADC Drivers                                   | -71dBc IM3 at 20MHz 2V <sub>P-P</sub> Composite, A <sub>V</sub> = 6dB, 12dB, 20dB                                                               |

| LTC6420-XX                                     | Dual 1.8GHz Low Noise, Low Distortion Differential ADC Drivers              | Dual Version of the LTC6400-XX, $A_V = 8dB$ , 14dB, 20dB, 26dB                                                                                  |

| LTC6421-XX                                     | Dual 1.3GHz Low Noise, Low Distortion Differential ADC Drivers              | Dual Version of the LTC6401-XX, $A_V = 8dB$ , 14dB, 20dB, 26dB                                                                                  |

| IF Amplifiers/ADC Drivers                      | s with Digitally Controlled Gain                                            |                                                                                                                                                 |

| LT5514                                         | Ultra-Low Distortion IF Amplifier/ADC Driver with Digitally Controlled Gain | OIP3 = 47dBm at 100MHz, Gain Range 10.5dB to 33dB 1.5dB steps                                                                                   |

| LT5524                                         | Low Distortion IF Amplifier/ADC Driver with Digitally Controlled Gain       | OIP3 = 40dBm at 100MHz, Gain Range 4.5dB to 37dB 1.5dB steps                                                                                    |

| LT5554                                         | High Dynamic Range 7-bit Digitally Controlled IF<br>VGA/ADC Driver          | OIP3 = 46dBm at 200MHz, Gain Range 1.725 to 17.6dB 0.125dB steps                                                                                |

| Baseband Differential An                       | plifiers                                                                    | ·                                                                                                                                               |

| LT1994                                         | Low Noise, Low Distortion Differential Amplifier/<br>ADC Driver             | 16-Bit SNR and SFDR at 1MHz, Rail-to-Rail Outputs                                                                                               |

| LTC6403-1                                      | Low Noise Rail-to-Rail Output Differential Amplifier/<br>ADC Driver         | 16-Bit SNR and SFDR at 3MHz, Rail-to-Rail Outputs, $e_N = 2.8 \text{ nV}/\sqrt{\text{Hz}}$                                                      |

| LTC6404-1/LTC6404-2                            | Low Noise Rail-to-Rail Output Differential Amplifier/<br>ADC Driver         | 16-Bit SNR and SFDR at 10MHz, Rail-to-Rail Outputs, $e_N = 1.5$ nV/ $\sqrt{Hz}$ , LTC6404-1 is unity-gain stable, LTC6404-2 is Gain-of-2 Stable |

| LTC6406                                        | 3GHz Rail-to-Rail Input Differential Amplifier/<br>ADC Driver               | -65dBc IM3 at 50MHz $2V_{P-P}$ Composite, Rail-to-Rail Inputs, $e_N = 1.6nV/\sqrt{Hz}$ , 18mA                                                   |

| LT6411                                         | Low Power Differential ADC Driver/Dual Selectable<br>Gain Amplifier         | -83dBc IM3 at 70MHz $2V_{P-P}$ Composite, $A_V = 1, -1$ or 2, 16mA, Excellent for Single-Ended to Differential Conversion                       |

6416f LT 1108 • PRINTED IN USA

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

LTC6416CDDB#TRPBF LTC6416IDDB#TRMPBF LTC6416IDDB#TRPBF LTC6416CDDB#TRMPBF DC1287A