## 16-/14-/11-Bit 2.7Gsps DACs

## **FEATURES**

- 80dBc SFDR at 50MHz f<sub>OUT</sub>

- >68dBc SFDR from DC to 1080MHz f<sub>OUT</sub>

- 40mA Nominal Full-Scale, ±1V Output Compliant

- 10mA to 60mA Adjustable Full-Scale Current Range

- Single or Dual Port DDR LVDS and DHSTL Interface

- Low Latency (7.5 Cycles for Single Port, 11 Cycles for Dual Port)

- >78dBc 2-Tone IMD from DC to 1000MHz f<sub>OUT</sub>

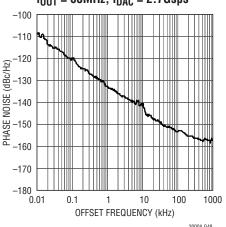

- -156dBc/Hz Additive Phase Noise at 1MHz Offset for 65MHz f<sub>OUT</sub>

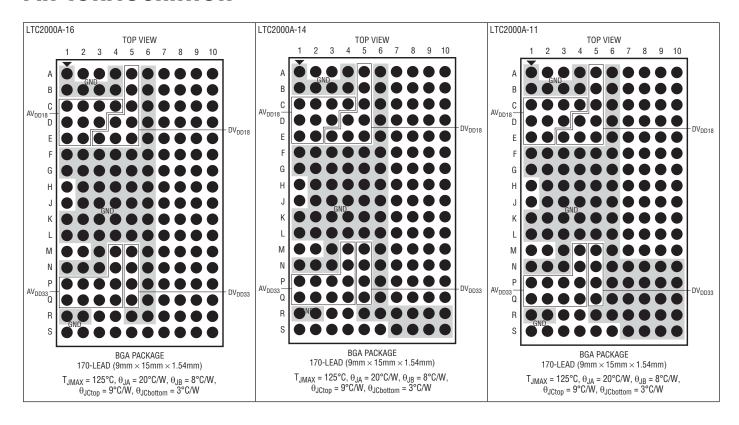

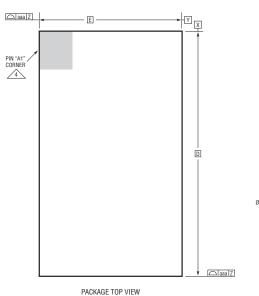

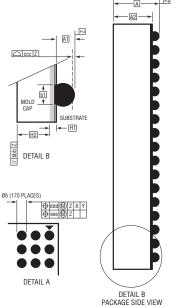

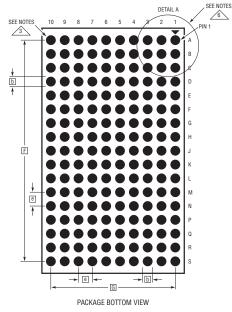

- 170-Lead (9mm × 15mm) BGA Package

## **APPLICATIONS**

- Broadband Communication Systems

- DOCSIS CMTS

- Direct RF Synthesis

- Radar

- Instrumentation

- Automatic Test Equipment

## DESCRIPTION

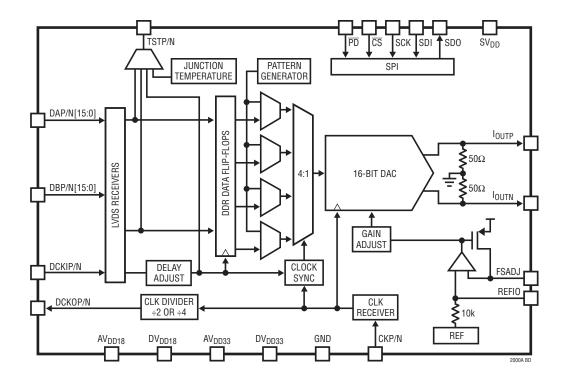

The LTC®2000A is a family of 16-/14-/11-bit 2.7Gsps current steering DACs with exceptional spectral purity.

The single (1.35Gsps mode) or dual (2.7Gsps mode) port source synchronous LVDS interface supports data rates of up to 1.35Gbps using a 675MHz DDR data clock, which can be either in quadrature or in phase with the data. An internal synchronizer automatically aligns the data with the DAC sample clock.

Additional features such as pattern generation, LVDS loopout and junction temperature sensing simplify system development and testing.

A serial peripheral interface (SPI) port allows configuration and read back of internal registers. Operating from 1.86V and 3.3V supplies, the LTC2000A consumes 2.41W at 2.7Gsps and 1.43W at 1.35Gsps.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. Patents, including 8330633.

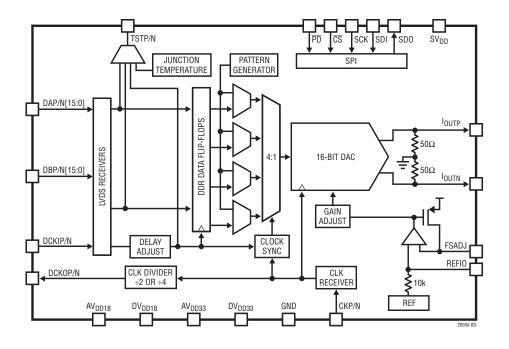

## **BLOCK DIAGRAM**

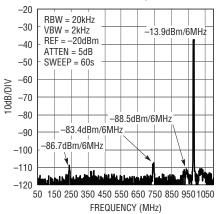

SFDR vs f<sub>OUT</sub>, f<sub>DAC</sub> = 2.7Gsps

100

DIGITAL AMPLITUDE = 0dBFS

loutes = 40mA

90

60

50

200

400

600

800

1000

1200

f<sub>OUT</sub> (MHz)

2000afb

## LTC2000A

## TABLE OF CONTENTS

| Features                              |    |

|---------------------------------------|----|

| Applications                          | 1  |

| Block Diagram                         | 1  |

| Description                           | 1  |

| Absolute Maximum Ratings              | 3  |

| Pin Configuration                     |    |

| Order Information                     |    |

| Electrical Characteristics            | 5  |

| Timing Characteristics                |    |

| Typical Performance Characteristics   |    |

| Pin Functions                         |    |

| Block Diagram                         |    |

| Timing Diagrams                       |    |

| Operation                             |    |

| Introduction                          |    |

| Dual-Port Mode                        |    |

| Single-Port Mode                      |    |

| Serial Peripheral Interface (SPI)     |    |

| Power-On Reset                        |    |

| Power Down                            |    |

| Reference Operation                   |    |

| Setting the Full-Scale Current        |    |

| DAC Transfer Function                 |    |

| Analog Outputs (I <sub>OUTP/N</sub> ) |    |

| DAC Sample Clock (CKP/N)              | 25 |

| Divided Clock Output (DCKOP/N)        |    |

| LVDS Data Clock Input (DCKIP/N)       |    |

| LVDS Data input Ports (DAP/N, DBP/N)                      | .26 |

|-----------------------------------------------------------|-----|

| Clock Synchronizer                                        | .27 |

| Minimizing Harmonic Distortion                            |     |

| Measuring LVDS Input Timing Skew                          |     |

| Measuring Internal Junction Temperature (T <sub>J</sub> ) | .32 |

| Pattern Generator                                         | .32 |

| SPI Register Summary                                      | 33  |

| Applications Information                                  |     |

| Sample Start-Up Sequence                                  | .34 |

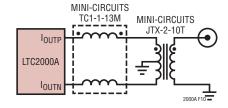

| Output Configurations                                     | .35 |

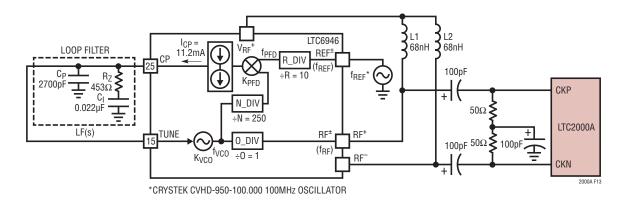

| Generating the DAC Sample Clock                           | .35 |

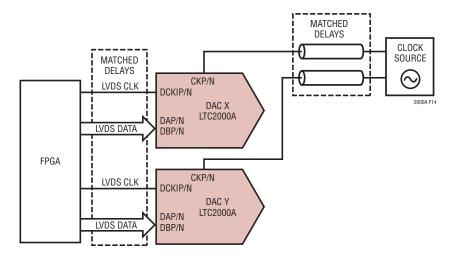

| Synchronizing Multiple LTC2000As in Dual-Port             |     |

| Mode                                                      | .36 |

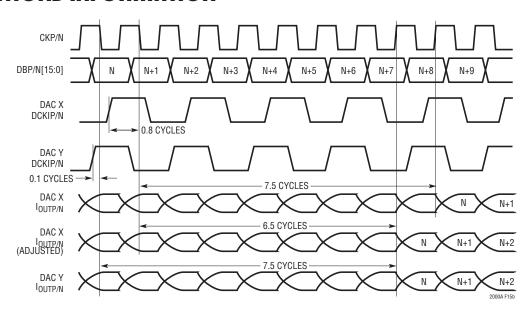

| Synchronizing Multiple LTC2000As in Single-Port           |     |

| Mode                                                      | .38 |

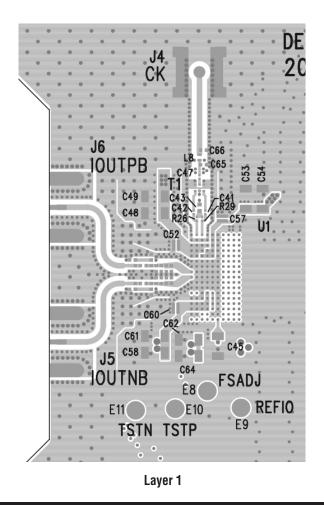

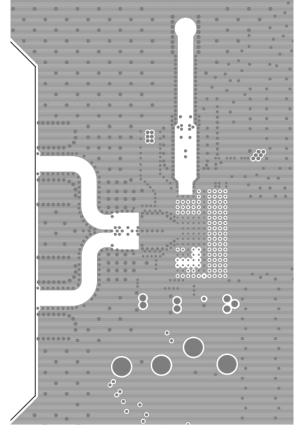

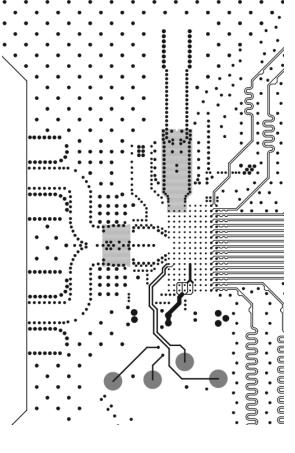

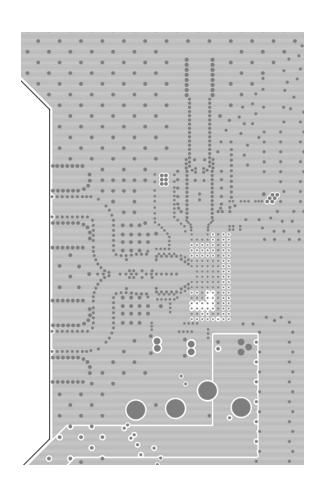

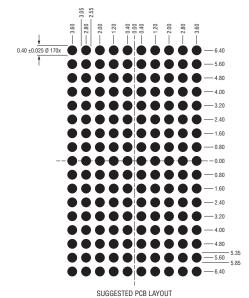

| PCB Layout Considerations                                 | .40 |

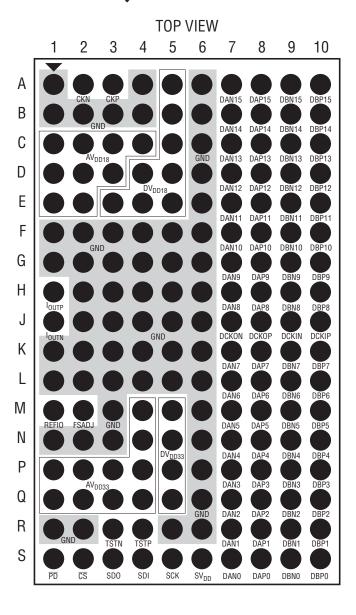

| Pin Locations (LTC2000A-16)                               | 45  |

| Pin Locations (LTC2000A-14)                               | 47  |

| Pin Locations (LTC2000A-11)                               |     |

| Package Description                                       |     |

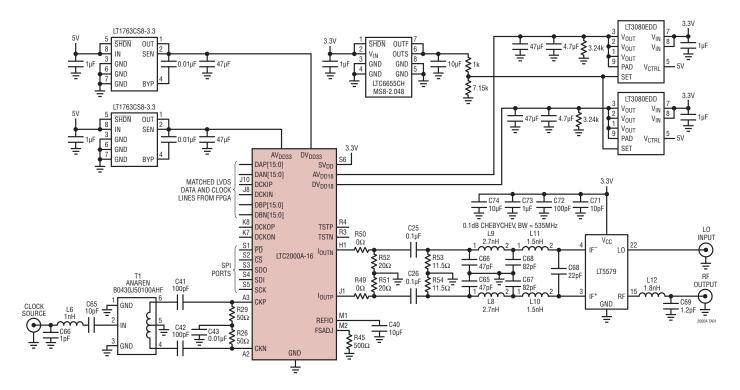

| Typical Application                                       |     |

| Related Parts                                             |     |

## **ABSOLUTE MAXIMUM RATINGS** (Notes 1, 2)

| AV <sub>DD33</sub> , DV <sub>DD33</sub> , SV <sub>DD</sub> 0 | .3V to 4V |

|--------------------------------------------------------------|-----------|

| AV <sub>DD18</sub> , DV <sub>DD18</sub> 0                    |           |

| $I_{OUTP}$ , $I_{OUTN}$ 1.2V to Min (AV <sub>DD33</sub> +    | 0.3V, 4V) |

| FSADJ, REFIO0.3V to Min (AV <sub>DD33</sub> +                |           |

| DCKIP, DCKIN0.3V to Min (DV <sub>DD33</sub> +                | 0.3V, 4V) |

| DCKOP, DCKON0.3V to Min (DV <sub>DD33</sub> +                | 0.3V, 4V) |

| DAP/N, DBP/N $-0.3V$ to Min (DV <sub>DD33</sub> +            | 0.3V, 4V) |

| TSTP, TSTN $-0.3V$ to Min (AV <sub>DD33</sub> +              |           |

| CKP, CKN –0.3V to M               | in (AV <sub>DD18</sub> + 0.3V, 2V) |

|-----------------------------------|------------------------------------|

| CS, PD, SCK, SDI, SD00.3V to      | Min $(SV_{DD} + 0.3V, 4V)$         |

| Operating Temperature Range       |                                    |

| LTC2000AC                         | 0°C to 70°C                        |

| LTC2000AI                         | 40°C to 85°C                       |

| Maximum Junction Temperature      | 125°C                              |

| Storage Temperature Range         | 55°C to 125°C                      |

| Lead Temperature (Soldering, 10 s | sec)260°C                          |

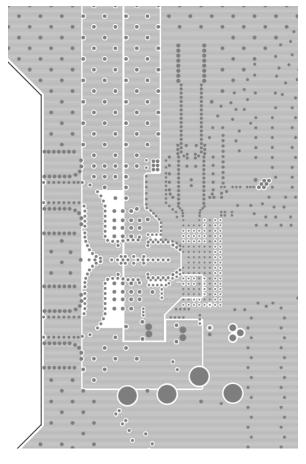

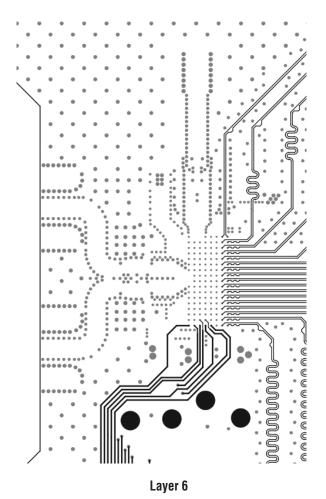

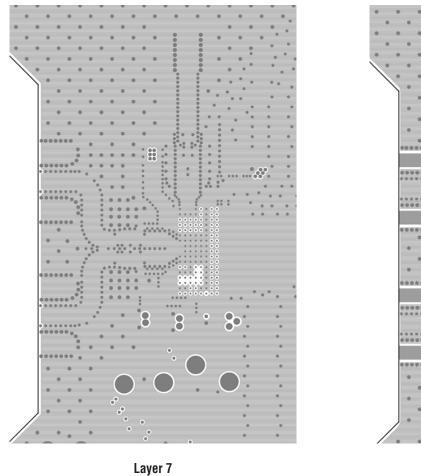

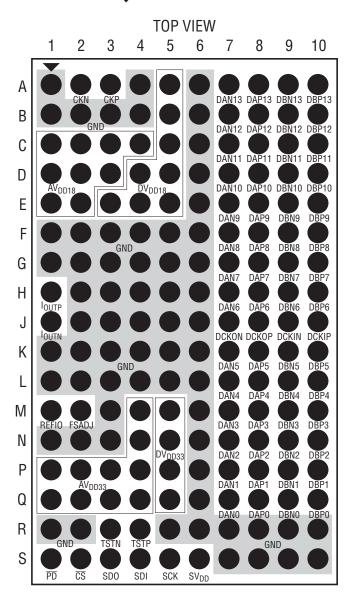

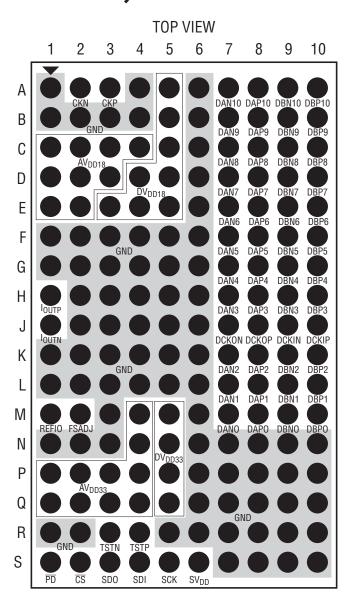

## PIN CONFIGURATION

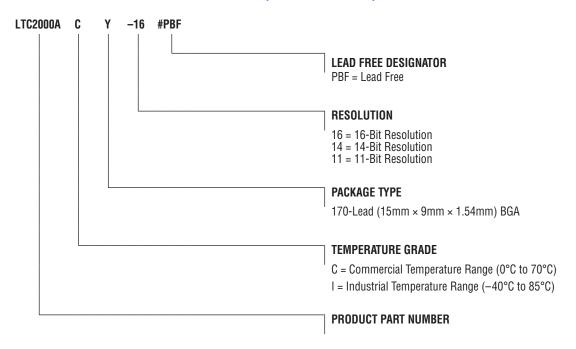

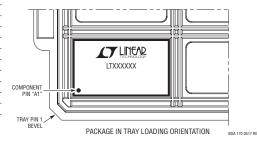

## ORDER INFORMATION http://www.linear.com/product/LTC2000A#orderinfo

| PART NUMBER       | BALL FINISH   | PART MARKING* | PACKAGE TYPE | MSL RATING | TEMPERATURE RANGE |

|-------------------|---------------|---------------|--------------|------------|-------------------|

| LTC2000ACY-16#PBF | SAC305 (RoHS) | LTC2000Y-16   | BGA          | 3          | 0°C to 70°C       |

| LTC2000ACY-14#PBF | SAC305 (RoHS) | LTC2000Y-14   | BGA          | 3          | 0°C to 70°C       |

| LTC2000ACY-11#PBF | SAC305 (RoHS) | LTC2000Y-11   | BGA          | 3          | 0°C to 70°C       |

| LTC2000AIY-16#PBF | SAC305 (RoHS) | LTC2000Y-16   | BGA          | 3          | -40°C to 85°C     |

| LTC2000AIY-14#PBF | SAC305 (RoHS) | LTC2000Y-14   | BGA          | 3          | -40°C to 85°C     |

| LTC2000AIY-11#PBF | SAC305 (RoHS) | LTC2000Y-11   | BGA          | 3          | -40°C to 85°C     |

| LTC2000AIY-16     | Sn/Pb         | LTC2000Y-16   | BGA          | 3          | -40°C to 85°C     |

Consult ADI Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

This product is only offered in trays. For more information go to: http://www.linear.com/packaging/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . AV<sub>DD18</sub>, DV<sub>DD18</sub> = 1.8V to 1.92V, AV<sub>DD33</sub>, DV<sub>DD33</sub> = 3.135V to 3.465V, SV<sub>DD</sub> = 1.71V to 3.465V, R<sub>FSADJ</sub> =  $500\Omega$ ,  $12.5\Omega$  load from  $I_{OUTP/N}$  to GND including internal  $50\Omega$  termination, unless otherwise specified.

| SYMBOL     | PARAMETER                          | CONDITIONS                                                                                                    |   | MIN  | TYP      | MAX   | UNITS      |

|------------|------------------------------------|---------------------------------------------------------------------------------------------------------------|---|------|----------|-------|------------|

| DC Perfori | mance                              |                                                                                                               |   |      |          |       |            |

|            | Resolution                         | LTC2000A-16                                                                                                   | • | 16   |          |       | Bits       |

|            |                                    | LTC2000A-14                                                                                                   | • | 14   |          |       | Bits       |

|            |                                    | LTC2000A-11                                                                                                   | • | 11   |          |       | Bits       |

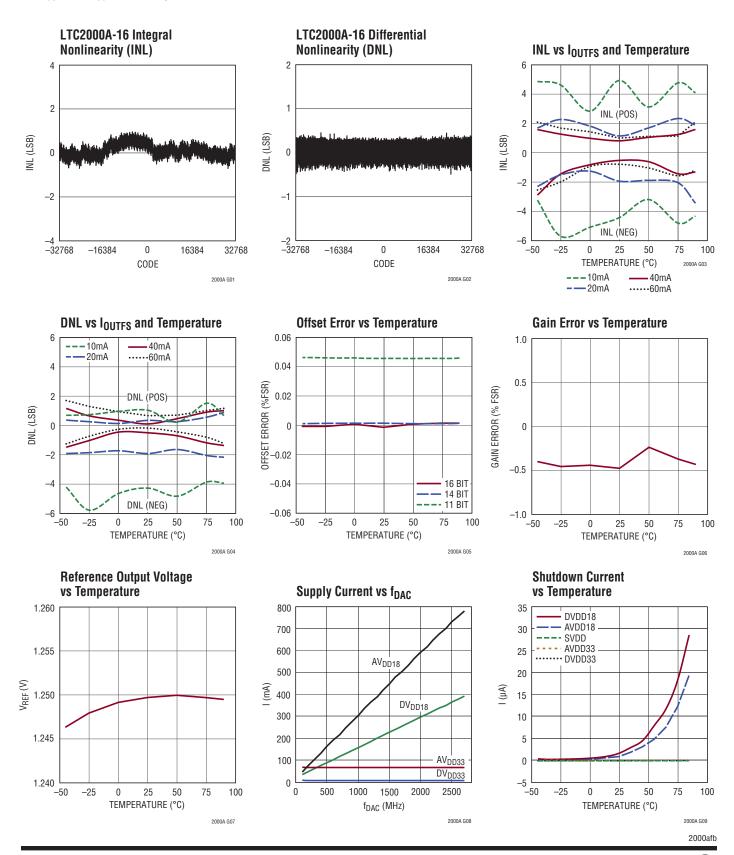

| DNL        | Differential Nonlinearity          | LTC2000A-16                                                                                                   | • |      | ±0.5     | ±2.7  | LSB        |

|            |                                    | LTC2000A-14                                                                                                   | • |      | ±0.2     | ±1    | LSB        |

|            |                                    | LTC2000A-11                                                                                                   | • |      | ±0.1     | ±0.5  | LSB        |

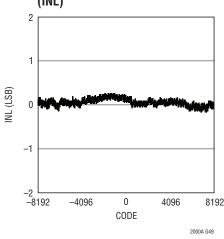

| INL        | Integral Nonlinearity              | LTC2000A-16                                                                                                   | • |      | ±1       | ±4    | LSB        |

|            |                                    | LTC2000A-14                                                                                                   | • |      | ±0.5     | ±2    | LSB        |

|            |                                    | LTC2000A-11                                                                                                   | • |      | ±0.2     | ±1    | LSB        |

|            | Offset Error                       | LTC2000A-16                                                                                                   | • |      |          | ±0.05 | % FSR      |

|            |                                    | LTC2000A-14                                                                                                   | • |      |          | ±0.06 | % FSR      |

|            |                                    | LTC2000A-11                                                                                                   | • |      |          | ±0.09 | % FSR      |

| -          | Offset Error Drift                 |                                                                                                               |   |      | 1        |       | ppm/°C     |

|            | Gain Error                         |                                                                                                               |   |      | ±0.5     |       | % FSR      |

|            | Gain Error Drift                   |                                                                                                               |   |      | 5        |       | ppm/°C     |

|            | Power Supply Rejection Ratio       | Full-Scale; AV <sub>DD33</sub> = 3.135V to 3.465V                                                             |   |      | 69       |       | dB         |

| Analog Ou  | itput                              | . 5500                                                                                                        |   |      |          |       |            |

|            | Full-Scale Output Current          | $R_{FSADJ} = 500\Omega$                                                                                       |   |      | 40       |       | mA         |

|            | Output Compliance Range            | 10/100                                                                                                        | • | -1   |          | 1     | V          |

|            | Output Resistance                  | I <sub>OUTP/N</sub> to GND                                                                                    | • | 42   | 50       | 58    | Ω          |

|            | Output Capacitance                 | 3011/10                                                                                                       |   |      | 6        |       | pF         |

| -          | Output Bandwidth                   | $R_{IOUTP/N} = 12.5\Omega$ , $-3dB$ Excluding $\sin(x)/x$                                                     |   |      | 2.1      |       | GHz        |

| AC Perfori |                                    | 10011710                                                                                                      |   |      |          |       |            |

|            | Maximum Update Rate                | Dual-Port Mode                                                                                                | • | 2.7  |          |       | Gsps       |

|            | ·                                  | Single-Port Mode                                                                                              | • | 1.35 |          |       | Gsps       |

| SFDR       | Spurious Free Dynamic Range        | f <sub>OUT</sub> = 50MHz, LIN_DIS = 0, LIN_GN = 75%                                                           |   |      | 82       |       | dBc        |

|            | $f_{DAC} = 1.25Gsps, 0dBFS$        | f <sub>OUT</sub> = 100MHz, LIN_DIS = 0, LIN_GN = 75%<br>f <sub>OUT</sub> = 250MHz, LIN_DIS = 0, LIN_GN = 75%  |   |      | 82<br>74 |       | dBc<br>dBc |

|            |                                    | f <sub>OUT</sub> = 230MHz, LIN_DIS = 0, LIN_GN = 75%                                                          |   |      | 74<br>74 |       | dBc        |

|            | Spurious Free Dynamic Range        | f <sub>OUT</sub> = 100MHz, LIN DIS = 0, LIN GN = 75%                                                          |   |      | 75       |       | dBc        |

|            | f <sub>DAC</sub> = 2.7Gsps, 0dBFS  | f <sub>OUT</sub> = 200MHz, LIN_DIS = 0, LIN_GN = 75%                                                          | • | 67   | 72       |       | dBc        |

|            |                                    | f <sub>OUT</sub> = 500MHz, LIN_DIS = 0, LIN_GN = 75%<br>f <sub>OUT</sub> = 1000MHz, LIN_DIS = 0, LIN_GN = 75% |   |      | 75<br>72 |       | dBc<br>dBc |

|            |                                    | f <sub>OUT</sub> = 500MHz, LIN_DIS = 0, LIN_GIN = 75%                                                         |   |      | 67       |       | dBc        |

|            |                                    | $f_{OUT} = 3000MHz$ , LIN_DIS = 1                                                                             |   |      | 61       |       | dBc        |

| IMD        | 2-Tone Intermodulation Distortion  | f <sub>OLIT</sub> = 50MHz, LIN_DIS = 0, LIN_GN = 75%                                                          |   |      | 103      |       | dBc        |

|            | $f_{OUT2} = f_{OUT1} + 1.25MHz$    | f <sub>OUT</sub> = 100MHz, LIN_DIS = 0, LIN_GN = 75%                                                          |   |      | 93       |       | dBc        |

|            | $f_{DAC} = 1.25Gsps, -6dBFS$       | f <sub>OUT</sub> = 250MHz, LIN_DIS = 0, LIN_GN = 75%                                                          |   |      | 97<br>84 |       | dBc<br>dBc |

|            | 2-Tone Intermodulation Distortion  | f <sub>OUT</sub> = 500MHz, LIN_DIS = 0, LIN_GN = 75%<br>f <sub>OUT</sub> = 100MHz, LIN_DIS = 1                |   |      | 87       |       | dBc        |

|            | $f_{OUT2} = f_{OUT1} + 1.25MHz$    | f <sub>OUT</sub> = 100MHz, LIN_DIS = 1                                                                        |   |      | 86       |       | dBc        |

|            | f <sub>DAC</sub> = 2.7Gsps, –6dBFS | $f_{OUT} = 500MHz$ , LIN_DIS = 1                                                                              |   |      | 82       |       | dBc        |

|            |                                    | f <sub>OUT</sub> = 1000MHz, LIN_DIS = 1                                                                       |   |      | 80       |       | dBc        |

|            |                                    | f <sub>OUT</sub> = 500MHz, LIN_DIS = 0, LIN_GN = 75%                                                          |   |      | 79       |       | dBc        |

|            |                                    | f <sub>OUT</sub> = 1000MHz, LIN_DIS = 0, LIN_GN = 75%                                                         |   |      | 68       |       | dBc        |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . AV<sub>DD18</sub>, DV<sub>DD18</sub> = 1.8V to 1.92V, AV<sub>DD33</sub>, DV<sub>DD33</sub> = 3.135V to 3.465V, SV<sub>DD</sub> = 1.71V to 3.465V, R<sub>FSADJ</sub> =  $500\Omega$ ,  $12.5\Omega$  load from  $I_{OUTP/N}$  to GND including internal  $50\Omega$  termination, unless otherwise specified.

| SYMBOL        | PARAMETER                                                                                                           | CONDITIONS                                                                                                                                   |   | MIN   | TYP                          | MAX   | UNITS                                |

|---------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---|-------|------------------------------|-------|--------------------------------------|

| NSD           | Noise Spectral Density<br>OdBFS Single Tone, f <sub>DAC</sub> = 2.7Gsps,<br>I <sub>OUTFS</sub> = 40mA               | LTC2000A-16, $f_{OUT} = 100 MHz$<br>LTC2000A-16, $f_{OUT} = 350 MHz$<br>LTC2000A-16, $f_{OUT} = 550 MHz$<br>LTC2000A-16, $f_{OUT} = 950 MHz$ |   |       | -164<br>-158<br>-155<br>-153 |       | dBm/Hz<br>dBm/Hz<br>dBm/Hz<br>dBm/Hz |

|               |                                                                                                                     | LTC2000A-14, $f_{OUT} = 100 MHz$<br>LTC2000A-14, $f_{OUT} = 350 MHz$<br>LTC2000A-14, $f_{OUT} = 550 MHz$<br>LTC2000A-14, $f_{OUT} = 950 MHz$ |   |       | -163<br>-158<br>-155<br>-153 |       | dBm/Hz<br>dBm/Hz<br>dBm/Hz<br>dBm/Hz |

|               |                                                                                                                     | LTC2000A-11, $f_{OUT} = 100MHz$<br>LTC2000A-11, $f_{OUT} = 350MHz$<br>LTC2000A-11, $f_{OUT} = 550MHz$<br>LTC2000A-11, $f_{OUT} = 950MHz$     |   |       | -156<br>-154<br>-153<br>-150 |       | dBm/Hz<br>dBm/Hz<br>dBm/Hz<br>dBm/Hz |

|               | Phase Noise<br>f <sub>DAC</sub> = 2.7Gsps, f <sub>OUT</sub> = 65MHz<br>0dBFS Single Tone, I <sub>OUTFS</sub> = 40mA | 10kHz Offset<br>1MHz Offset                                                                                                                  |   |       | -141<br>-156                 |       | dBc/Hz<br>dBc/Hz                     |

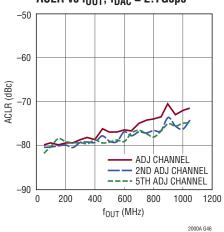

| WCDMA<br>ACLR | WCDMA ACLR (Single Carrier)<br>Adjacent/Alternate Adjacent Channel                                                  | $f_{DAC} = 2.7Gsps, f_{OUT} = 350MHz$<br>$f_{DAC} = 2.7Gsps, f_{OUT} = 950MHz$                                                               |   |       | 78/79<br>72/75               |       | dBc<br>dBc                           |

| Latency       |                                                                                                                     |                                                                                                                                              |   |       |                              |       |                                      |

|               | Latency (Note 5)                                                                                                    | Single-Port Mode<br>Dual-Port Mode, DAP/N Data<br>Dual-Port Mode, DBP/N Data                                                                 |   |       | 7.5<br>10<br>11              |       | Cycles<br>Cycles<br>Cycles           |

|               | Aperture Delay                                                                                                      | CKP/N Rising to I <sub>OUTP/N</sub> Transition                                                                                               |   |       | 3                            |       | ns                                   |

|               | Settling Time                                                                                                       | ±0.1% FSR, Full-Scale Step                                                                                                                   |   |       | 2.2                          |       | ns                                   |

| Reference     |                                                                                                                     |                                                                                                                                              |   |       |                              |       |                                      |

|               | Output Voltage                                                                                                      |                                                                                                                                              | • | 1.225 | 1.25                         | 1.275 | V                                    |

|               | Input Voltage                                                                                                       |                                                                                                                                              | • | 1.1   |                              | 1.4   | V                                    |

|               | Reference Temperature Coefficient                                                                                   |                                                                                                                                              |   |       | ±25                          |       | ppm/°C                               |

|               | Output Impedance                                                                                                    |                                                                                                                                              |   |       | 10                           |       | kΩ                                   |

| DAC Clock     | Inputs (CKP, CKN)                                                                                                   |                                                                                                                                              |   |       |                              |       |                                      |

|               | Differential Input Voltage Range                                                                                    |                                                                                                                                              | • | ±0.3  |                              | ±1.8  | V                                    |

|               | Common-Mode Input Voltage                                                                                           | Set Internally                                                                                                                               |   |       | 1                            |       | V                                    |

| -             | Sampling Clock Frequency                                                                                            |                                                                                                                                              | • | 50    |                              | 2700  | MHz                                  |

| -             | Input Impedance                                                                                                     |                                                                                                                                              |   |       | 5                            |       | kΩ                                   |

| LVDS Input    | ts (DCKIP, DCKIN, DAP/N, DBP/N)                                                                                     |                                                                                                                                              |   |       |                              |       |                                      |

|               | Differential Input Voltage Range                                                                                    |                                                                                                                                              | • | ±0.2  |                              | ±0.6  | V                                    |

|               | Common-Mode Voltage Range                                                                                           |                                                                                                                                              | • | 0.4   |                              | 1.8   | V                                    |

|               | Differential Input Impedance                                                                                        |                                                                                                                                              | • | 95    | 120                          | 145   | Ω                                    |

|               | Maximum Data Rate                                                                                                   |                                                                                                                                              | • |       |                              | 1350  | Mbps                                 |

|               | LVDS Clock Frequency                                                                                                |                                                                                                                                              | • | 25    |                              | 675   | MHz                                  |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $AV_{DD18}$ ,  $DV_{DD18} = 1.8V$  to 1.92V,  $AV_{DD33}$ ,  $DV_{DD33} = 3.135V$  to 3.465V,  $SV_{DD} = 1.71V$  to 3.465V,  $R_{FSADJ} = 500\Omega$ ,  $12.5\Omega$  load from  $I_{OUTP/N}$  to GND including internal  $50\Omega$  termination, unless otherwise specified.

| SYMBOL              | PARAMETER                                                            | CONDITIONS                                                                                                                                                                                                 |   | MIN          | TYP                      | MAX                     | UNITS                |

|---------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|--------------------------|-------------------------|----------------------|

| LVDS Outp           | ut (DCKOP, DCKON)                                                    | ,                                                                                                                                                                                                          |   |              |                          |                         |                      |

|                     | Differential Output Voltage                                          | 100 $\Omega$ Differential Load, DCKO_ISEL = 0 50 $\Omega$ Differential Load, DCKO_ISEL = 1                                                                                                                 | • | 0.24<br>0.24 | 0.36<br>0.36             | 0.48<br>0.48            | V                    |

|                     | Common-Mode Output Voltage                                           |                                                                                                                                                                                                            | • | 1.075        | 1.2                      | 1.325                   | V                    |

|                     | Internal Termination Resistance                                      | DCKO_TRM = 1                                                                                                                                                                                               |   |              | 100                      |                         | Ω                    |

| CMOS Dig            | ital Inputs (CS, PD, SCK, SDI)                                       |                                                                                                                                                                                                            |   |              |                          |                         |                      |

| V <sub>IH</sub>     | Digital Input High Voltage                                           |                                                                                                                                                                                                            | • | 70           |                          |                         | %V <sub>SVDD</sub>   |

| $V_{IL}$            | Digital Input Low Voltage                                            |                                                                                                                                                                                                            | • |              |                          | 30                      | %V <sub>SVDD</sub>   |

| $I_{LK}$            | Digital Input Leakage                                                | $V_{IN} = GND \text{ or } SV_{DD}$                                                                                                                                                                         | • |              |                          | ±10                     | μA                   |

| CIN                 | Digital Input Capacitance                                            |                                                                                                                                                                                                            |   |              | 8                        |                         | pF                   |

| CMOS Dig            | ital Output (SDO)                                                    |                                                                                                                                                                                                            |   |              |                          |                         |                      |

| V <sub>OH</sub>     | Digital Output High Voltage                                          | I <sub>SOURCE</sub> = 0.2mA                                                                                                                                                                                | • | 85           |                          |                         | %V <sub>SVDD</sub>   |

| $V_{0L}$            | Digital Output Low Voltage                                           | I <sub>SINK</sub> = 1.6mA                                                                                                                                                                                  | • |              |                          | 15                      | %V <sub>SVDD</sub>   |

|                     | Hi-Z Output Leakage                                                  |                                                                                                                                                                                                            | • |              |                          | ±10                     | μA                   |

|                     | Hi-Z Output Capacitance                                              |                                                                                                                                                                                                            |   |              | 8                        |                         | pF                   |

| Power Sup           | ply                                                                  |                                                                                                                                                                                                            |   |              |                          |                         |                      |

| $V_{VDD33}$         | AV <sub>DD33</sub> , DV <sub>DD33</sub> Supply Voltage               |                                                                                                                                                                                                            | • | 3.135        | 3.3                      | 3.465                   | V                    |

| V <sub>VDD18</sub>  | AV <sub>DD18</sub> , D <sub>VDD18</sub> Supply Voltage               |                                                                                                                                                                                                            | • | 1.8          | 1.86                     | 1.92                    | V                    |

| $V_{SVDD}$          | SV <sub>DD</sub> SPI Supply Voltage                                  |                                                                                                                                                                                                            | • | 1.71         |                          | 3.465                   | V                    |

| I <sub>AVDD33</sub> | AV <sub>DD33</sub> Supply Current, AV <sub>DD33</sub> = 3.3V         | $\frac{\overline{PD}}{\overline{PD}} = SV_{DD}$ $\overline{PD} = GND$                                                                                                                                      | • |              | 68<br>0.1                | 78<br>10                | mA<br>μA             |

| I <sub>DVDD33</sub> | DV <sub>DD33</sub> Supply Current, DV <sub>DD33</sub> = 3.3V         | PD = SV <sub>DD</sub><br>PD = GND                                                                                                                                                                          | • |              | 8<br>0.1                 | 14<br>5                 | mA<br>μA             |

| I <sub>AVDD18</sub> | AV <sub>DD18</sub> Supply Current, AV <sub>DD18</sub> = 1.86V        | $ \begin{aligned} &f_{DAC} = 2700 \text{MHz} \\ &f_{DAC} = 1350 \text{MHz} \\ &f_{DAC} = 0 \text{Hz}, \overline{PD} = \text{SV}_{DD} \\ &f_{DAC} = 0 \text{Hz}, \overline{PD} = \text{GND} \end{aligned} $ | • |              | 780<br>425<br>23<br>3    | 870<br>480<br>27<br>180 | mA<br>mA<br>mA<br>μA |

| I <sub>DVDD18</sub> | DV <sub>DD18</sub> Supply Current, DV <sub>DD18</sub> = 1.86V        |                                                                                                                                                                                                            | • |              | 380<br>210<br>10<br>0.1  | 440<br>240<br>14<br>240 | mA<br>mA<br>mA<br>μA |

| I <sub>SVDD</sub>   | SV <sub>DD</sub> Supply Current (Note 4),<br>SV <sub>DD</sub> = 3.3V | f <sub>SCK</sub> = 0Hz                                                                                                                                                                                     | • |              | 0.1                      | 5                       | μА                   |

|                     | Total Power Dissipation                                              | $ \begin{aligned} &f_{DAC} = 2700 \text{MHz} \\ &f_{DAC} = 1350 \text{MHz} \\ &f_{DAC} = 0 \text{Hz}, \overline{PD} = \text{SV}_{DD} \\ &f_{DAC} = 0 \text{Hz}, \overline{PD} = \text{GND} \end{aligned} $ |   |              | 2408<br>1432<br>312<br>6 |                         | mW<br>mW<br>mW<br>μW |

**TIMING CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A=25^{\circ}C$ .  $AV_{DD18}$ ,  $DV_{DD18}=1.8V$  to 1.92V,  $AV_{DD33}$ ,  $DV_{DD33}=3.135V$  to 3.465V,  $SV_{DD}=1.71V$  to 3.465V,  $R_{FSADJ}=500\Omega$ , output load  $50\Omega$  double terminated, unless otherwise specified.

| SYMBOL          | PARAMETER                                     | CONDITIONS                                |   | MIN         | TYP | MAX | UNITS    |

|-----------------|-----------------------------------------------|-------------------------------------------|---|-------------|-----|-----|----------|

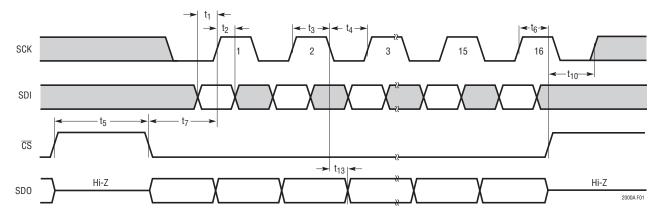

| t <sub>1</sub>  | SDI Valid to SCK Setup                        | (Note 3)                                  | • | 4           |     |     | ns       |

| t <sub>2</sub>  | SDI Valid to SCK Hold                         | (Note 3)                                  | • | 4           |     |     | ns       |

| t <sub>3</sub>  | SCK High Time                                 | (Note 3)                                  | • | 9           |     |     | ns       |

| t <sub>4</sub>  | SCK Low Time                                  | (Note 3)                                  | • | 9           |     |     | ns       |

| t <sub>5</sub>  | CS Pulse Width                                | (Note 3)                                  | • | 10          |     |     | ns       |

| t <sub>6</sub>  | SCK High to CS High                           | (Note 3)                                  | • | 7           |     |     | ns       |

| t <sub>7</sub>  | CS Low to SCK High                            | (Note 3)                                  | • | 7           |     |     | ns       |

| t <sub>10</sub> | CS High to SCK High                           | (Note 3)                                  | • | 7           |     |     | ns       |

| t <sub>13</sub> | SCK Low to SDO Valid                          | Unloaded (Note 3)                         | • | 10          |     |     | ns       |

|                 | SCK Frequency                                 | 50% Duty Cycle (Note 3)                   | • |             |     | 50  | MHz      |

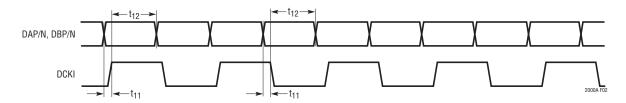

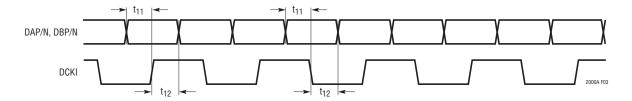

| t <sub>11</sub> | LVDS DAP/N, DBP/N to DCKI Setup Time (Note 3) | DCKI_Q = 1<br>DCKI_Q = 0, DCKI_TADJ = 000 | • | 200<br>570  |     |     | ps<br>ps |

| t <sub>12</sub> | LVDS DAP/N, DBP/N to DCKI Hold Time (Note 3)  | DCKI_Q = 1<br>DCKI_Q = 0, DCKI_TADJ = 000 | • | 200<br>–170 |     |     | ps<br>ps |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All voltages are with respect to GND.

Note 3: Guaranteed by design and not production tested.

Note 4: Digital inputs at 0V or SV<sub>DD</sub>.

**Note 5:** Latency is the delay from a transition on DCKIP/N until the CKP/N transition which causes the sample on DAP/N or DBP/N to appear at the DAC output I<sub>OUTP/N</sub>, as measured in DAC sample clock (CKP/N) cycles.

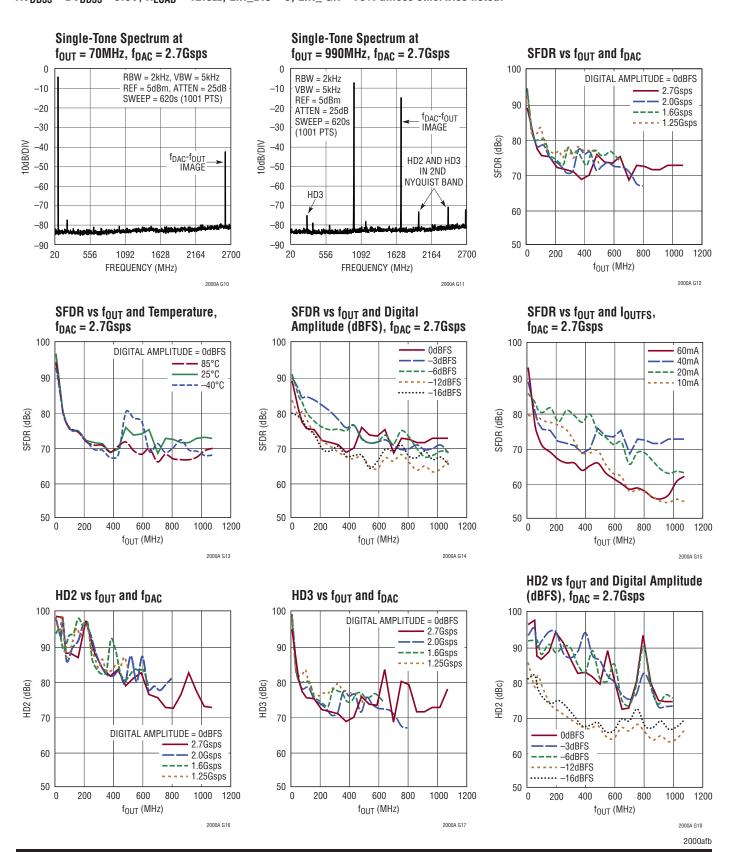

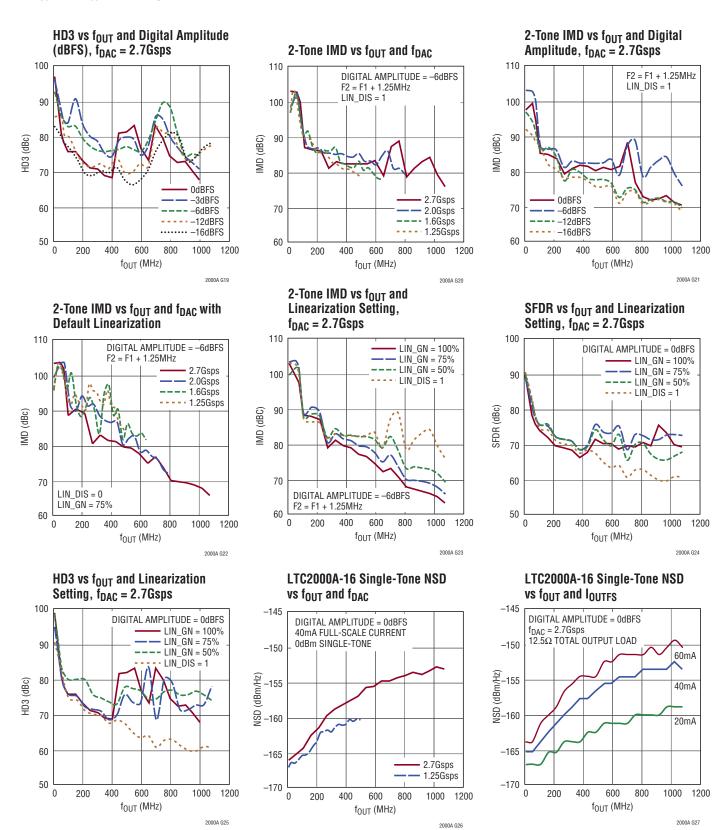

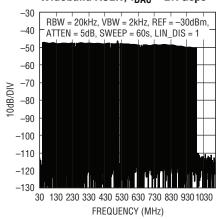

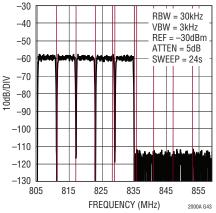

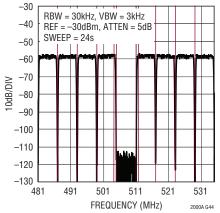

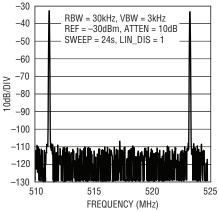

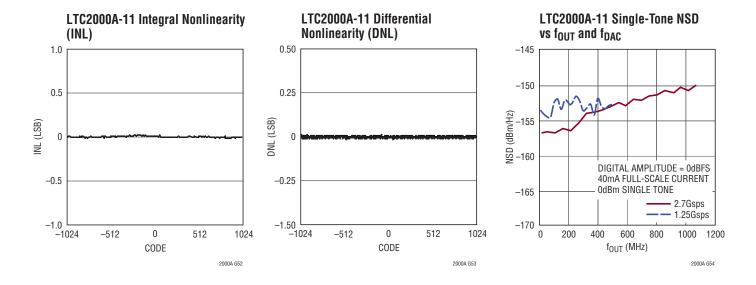

# TYPICAL PERFORMANCE CHARACTERISTICS $I_{OUTFS} = 40 \text{mA}, T_A = 25 ^{\circ}\text{C}, AV_{DD18} = DV_{DD18} = 1.86 \text{V}, AV_{DD33} = DV_{DD33} = 3.3 \text{V}, R_{L0AD} = 12.5 \Omega, unless otherwise noted.}$

## TYPICAL PERFORMANCE CHARACTERISTICS $I_{OUTFS} = 40 mA$ , $T_A = 25 ^{\circ}C$ , $AV_{DD18} = DV_{DD18} = 1.86 V$ , $AV_{DD33} = DV_{DD33} = 3.3 V$ , $R_{L0AD} = 12.5 \Omega$ , $LIN_DIS = 0$ , $LIN_GN = 75 \%$ unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS $I_{OUTFS} = 40 \text{mA}$ , $T_A = 25 ^{\circ}\text{C}$ , $AV_{DD18} = DV_{DD18} = 1.86 \text{V}$ , $AV_{DD33} = DV_{DD33} = 3.3 \text{V}$ , $R_{L0AD} = 12.5 \Omega$ , $LIN_DIS = 0$ , $LIN_B = 75 \%$ unless otherwise noted.

2000afh

## TYPICAL PERFORMANCE CHARACTERISTICS $I_{OUTFS} = 40 \text{mA}$ , $T_A = 25 ^{\circ}\text{C}$ , $AV_{DD18} = DV_{DD18} = 1.86 \text{V}$ , $AV_{DD33} = DV_{DD33} = 3.3 \text{V}$ , $R_{LOAD} = 12.5 \Omega$ , $LIN_DIS = 0$ , $LIN_GN = 75 \%$ unless otherwise noted.

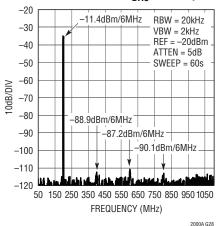

#### LTC2000A-16

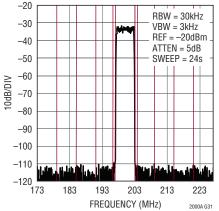

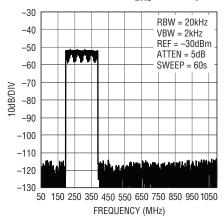

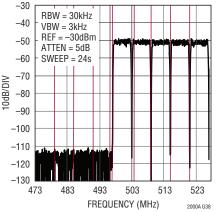

#### Single Carrier DOCSIS Low Band Wideband ACLR, $f_{DAC} = 2.7Gsps$

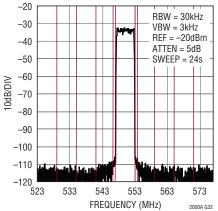

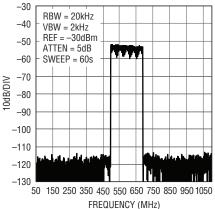

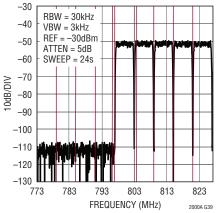

**Single Carrier DOCSIS Mid Band** Wideband ACLR,  $f_{DAC} = 2.7Gsps$

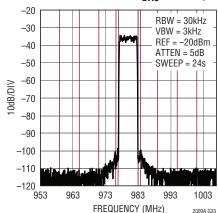

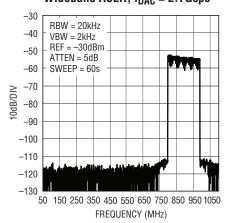

Single Carrier DOCSIS High Band Wideband ACLR, f<sub>DAC</sub> = 2.7Gsps

2000A G30

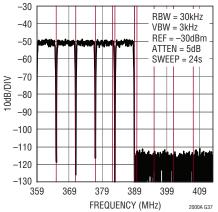

#### **Single Carrier DOCSIS Low Band** Narrowband ACLR, $f_{DAC} = 2.7Gsps$

CARRIER POWER = -11.40dBm, CENTER FREQ = 200MHz

| OFFSET FREQ | BW      | LOWER     | UPPER     |

|-------------|---------|-----------|-----------|

| 3.375MHz    | 750kHz  | -99.97dBm | -95.33dBm |

| 6.375MHz    | 5.25MHz | -95.69dBm | -95.18dBm |

| 12.00MHz    | 6MHz    | -96.89dBm | -95.80dBm |

| 18.00MHz    | 6MHz    | -96.68dBm | -96.60dBm |

| 24.00MHz    | 6MHz    | -96.19dBm | -95.94dBm |

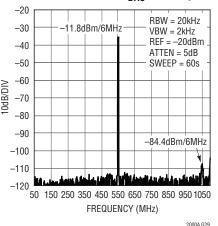

#### **Single Carrier DOCSIS Mid Band** Narrowband ACLR, $f_{DAC} = 2.7Gsps$

CARRIER POWER = -11.85dBm, CENTER FREQ = 550MHz

| OFFSET FREQ | BW      | LOWER     | UPPER     |

|-------------|---------|-----------|-----------|

| 3.375MHz    | 750kHz  | -95.92dBm | -92.58dBm |

| 6.375MHz    | 5.25MHz | -91.68dBm | -91.81dBm |

| 12.00MHz    | 6MHz    | -94.58dBm | -94.33dBm |

| 18.00MHz    | 6MHz    | -94.54dBm | -94.36dBm |

| 24.00MHz    | 6MHz    | -94.17dBm | -94.16dBm |

Single Carrier DOCSIS High Band Narrowband ACLR,  $f_{DAC} = 2.7Gsps$

CARRIER POWER = -13.95dBm, CENTER FREQ = 980MHz

| OFFSET FREQ | BW      | LOWER     | UPPER     |

|-------------|---------|-----------|-----------|

| 3.375MHz    | 750kHz  | -89.76dBm | -90.00dBm |

| 6.375MHz    | 5.25MHz | -87.24dBm | -86.24dBm |

| 12.00MHz    | 6MHz    | -92.87dBm | -92.16dBm |

| 18.00MHz    | 6MHz    | -93.36dBm | -92.29dBm |

| 24.00MHz    | 6MHz    | -92.65dBm | -91.52dBm |

2000A G34

TYPICAL PERFORMANCE CHARACTERISTICS  $I_{OUTFS} = 40 mA$ ,  $T_A = 25 ^{\circ}C$ ,  $AV_{DD18} = DV_{DD18} = 1.86V$ ,  $AV_{DD33} = DV_{DD33} = 3.3V$ ,  $R_{L0AD} = 12.5\Omega$ ,  $LIN_DIS = 0$ ,  $LIN_GN = 75\%$  unless otherwise noted.

#### LTC2000A-16

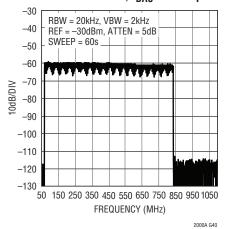

#### 32-Carrier DOCSIS Low Band Wideband ACLR, $f_{DAC} = 2.7Gsps$

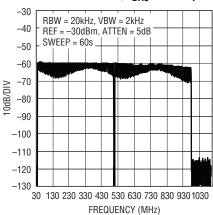

## Wideband ACLR, $f_{DAC} = 2.7Gsps$

32-Carrier DOCSIS Mid Band

### 32 Carrier DOCSIS High Band Wideband ACLR, $f_{DAC} = 2.7Gsps$

2000A G36

#### 32-Carrier DOCSIS Low Band Narrowband ACLR, $f_{DAC} = 2.7Gsps$

CARRIER POWER = -28.77dBm, CENTER FREQ = 386MHz

| OFFSET FREQ | BW      | LOWER     | UPPER      |

|-------------|---------|-----------|------------|

| 3.375MHz    | 750kHz  | -39.64dBm | -103.72dBm |

| 6.375MHz    | 5.25MHz | -29.39dBm | -94.79dBm  |

| 12.00MHz    | 6MHz    | -28.89dBm | -94.96dBm  |

| 18.00MHz    | 6MHz    | -28.83dBm | -95.34dBm  |

| 24.00MHz    | 6MHz    | -28.74dBm | -95.75dBm  |

#### 32 Carrier DOCSIS Mid Band Narrowband ACLR, $f_{DAC} = 2.7Gsps$

2000A G35

CARRIER POWER = -28.59dBm, CENTER FREQ = 500MHz

| OFFSET FREQ |          | BW      | LOWER      | UPPER     |

|-------------|----------|---------|------------|-----------|

|             | 3.375MHz | 750kHz  | -102.11dBm | -39.71dBm |

|             | 6.375MHz | 5.25MHz | -94.82dBm  | -28.18dBm |

|             | 12.00MHz | 6MHz    | -94.42dBm  | -28.96dBm |

|             | 18.00MHz | 6MHz    | -94.16dBm  | -29.11dBm |

|             | 24.00MHz | 6MHz    | -94.17dBm  | -29.04dBm |

### 32 Carrier DOCSIS High Band Narrowband ACLR, $f_{DAC} = 2.7Gsps$

CARRIER POWER = -29.43dBm, CENTER FREQ = 800MHz

| OFFSET FREQ | BW      | LOWER     | UPPER     |

|-------------|---------|-----------|-----------|

| 3.375MHz    | 750kHz  | -97.92dBm | -40.25dBm |

| 6.375MHz    | 5.25MHz | -89.60dBm | -29.56dBm |

| 12.00MHz    | 6MHz    | -89.45dBm | -29.23dBm |

| 18.00MHz    | 6MHz    | -89.52dBm | -29.40dBm |

| 24.00MHz    | 6MHz    | -89.38dBm | -29.56dBm |

## TYPICAL PERFORMANCE CHARACTERISTICS $I_{OUTFS} = 40 \text{mA}$ , $T_A = 25 ^{\circ}\text{C}$ , $AV_{DD18} = DV_{DD18} = 1.86 \text{V}$ , $AV_{DD33} = DV_{DD33} = 3.3 \text{V}$ , $R_{L0AD} = 12.5 \Omega$ , $LIN_DIS = 0$ , $LIN_GN = 75 \%$ unless otherwise noted.

#### LTC2000A-16

#### 128 Carrier DOCSIS Low Band Wideband ACLR, $f_{DAC} = 2.7Gsps$

### 157 Carrier DOCSIS Gap Channel Wideband ACLR, $f_{DAC} = 2.7Gsps$

#### 157 Carrier Tones with Gap Channel Wideband ACLR, $f_{DAC} = 2.7Gsps$

2000A G42

### 128 Carrier DOCSIS Low Band Narrowband ACLR, $f_{DAC} = 2.7Gsps$

|               |              | . ,    |        |        |

|---------------|--------------|--------|--------|--------|

| CARRIER POWER | = −37.77dBm, | CENTER | FREQ = | 832MHz |

|               |              |        |        |        |

| OFFSET FREQ | BW      | LOWER     | UPPER      |

|-------------|---------|-----------|------------|

| 3.375MHz    | 750kHz  | -47.75dBm | -104.61dBm |

| 6.375MHz    | 5.25MHz | -38.07dBm | -95.82dBm  |

| 12.00MHz    | 6MHz    | -37.57dBm | -95.53dBm  |

| 18.00MHz    | 6MHz    | -37.39dBm | -95.43dBm  |

| 24.00MHz    | 6MHz    | -37.27dBm | -95.18dBm  |

|             |         |           |            |

### **157 Carrier DOCSIS Gap Channel** Narrowband ACLR, $f_{DAC} = 2.7Gsps$

GAP CHANNEL POWER = -96.61dBm, CENTER FREQ = 508MHz

| OFFSET FREQ | BW      | LOWER     | UPPER     |

|-------------|---------|-----------|-----------|

| 3.375MHz    | 750kHz  | -47.17dBm | -48.00dBm |

| 6.375MHz    | 5.25MHz | -36.79dBm | -36.67dBm |

| 12.00MHz    | 6MHz    | -36.58dBm | -36.56dBm |

| 18.00MHz    | 6MHz    | -36.76dBm | -36.60dBm |

| 24.00MHz    | 6MHz    | -36.76dBm | -36.69dBm |

#### 157 Carrier Tones with Gap Channel Narrowband ACLR, f<sub>DAC</sub> = 2.7Gsps

$\begin{array}{l} \textbf{TYPICAL PERFORMANCE CHARACTERISTICS} & I_{OUTFS} = 40\text{mA}, \ T_A = 25^{\circ}\text{C}, \ AV_{DD18} = DV_{DD18} = 1.86\text{V}, \\ AV_{DD33} = DV_{DD33} = 3.3\text{V}, \ R_{L0AD} = 12.5\Omega, \ LIN\_DIS = 0, \ LIN\_GN = 75\% \ unless \ otherwise \ noted. \\ \end{array}$

LTC2000A-16 Single Carrier WCDMA ACLR vs f<sub>OUT</sub>, f<sub>DAC</sub> = 2.7Gsps

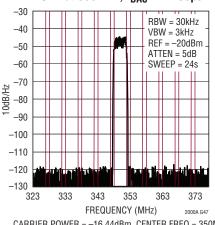

LTC2000A-16 Single Carrier WCDMA ACLR at 350MHz,  $f_{DAC} = 2.7Gsps$

CARRIER POWER = -16.44dBm, CENTER FREQ = 350MHz

| OFFSET FREQ | BW                                          | LOWER                                                                        | UPPER                                                                                                               |

|-------------|---------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 5.00MHz     | 3.84MHz                                     | -95.14dBm                                                                    | -94.76dBm                                                                                                           |

| 10.00MHz    | 3.84MHz                                     | -95.76dBm                                                                    | -96.22dBm                                                                                                           |

| 15.00MHz    | 3.84MHz                                     | -95.41dBm                                                                    | -95.10dBm                                                                                                           |

| 20.00MHz    | 3.84MHz                                     | -95.69dBm                                                                    | -96.41dBm                                                                                                           |

| 25.00MHz    | 3.84MHz                                     | -95.00dBm                                                                    | -96.69dBm                                                                                                           |

|             | 5.00MHz<br>10.00MHz<br>15.00MHz<br>20.00MHz | 5.00MHz<br>10.00MHz<br>3.84MHz<br>15.00MHz<br>20.00MHz<br>3.84MHz<br>3.84MHz | 5.00MHz 3.84MHz -95.14dBm<br>10.00MHz 3.84MHz -95.76dBm<br>15.00MHz 3.84MHz -95.41dBm<br>20.00MHz 3.84MHz -95.69dBm |

Additive Phase Noise,  $f_{OUT} = 65MHz$ ,  $f_{DAC} = 2.7Gsps$

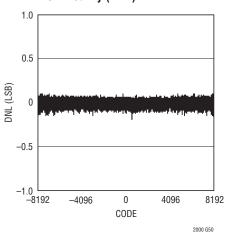

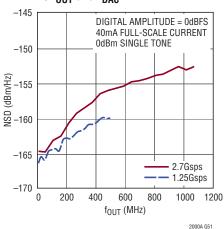

#### LTC2000A-14 Integral Nonlinearity (INL)

#### LTC2000A-14 Differential Nonlinearity (DNL)

LTC2000A-14 Single-Tone NSD vs four and fdac

#

## PIN FUNCTIONS

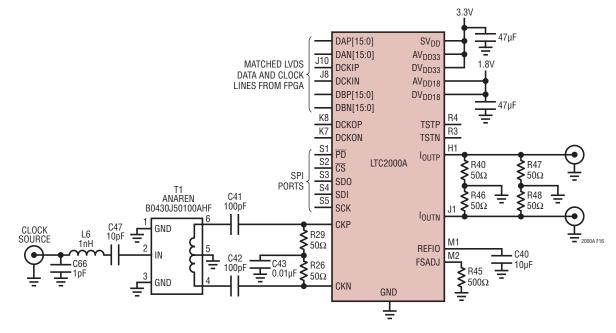

AV<sub>DD18</sub>: 1.8V Analog Supply Voltage Input. 1.8V to 1.92V.

**AV<sub>DD33</sub>:** 3.3V Analog Supply Voltage Input. 3.135V to 3.465V.

**CKP, CKN:** DAC Sample Clock Inputs. Maximum clock frequency ( $f_{DAC}$ ) is 2700MHz. Clock signal should be AC coupled.

$\overline{\text{CS}}$ : Serial Interface Chip Select Input. When  $\overline{\text{CS}}$  is low, SCK is enabled for shifting data on SDI into the register. When  $\overline{\text{CS}}$  is taken high, SCK is disabled and SDO is high impedance.

**DAP[15:0], DAN[15:0]:** Port A LVDS Data Inputs. Maximum data rate is 1.35Gbps. Port A is used only in dual-port mode. Connect to GND if not used. The data input format is two's complement.

**DBP[15:0], DBN[15:0]:** Port B LVDS Data Inputs. Maximum data rate is 1.35Gbps. In single-port mode, only Port B is used. In dual-port mode, the sample from Port B appears at I<sub>OUTP/N</sub> one cycle after the sample from Port A. The data input format is two's complement.

**DCKIP**, **DCKIN**: LVDS Data Clock Inputs. Maximum frequency ( $f_{DCKI}$ ) is 675MHz. In dual-port mode,  $f_{DCKI} = f_{DAC}/4$ . In single-port mode,  $f_{DCKI} = f_{DAC}/2$

**DCKOP, DCKON:** LVDS Data Clock Outputs. Maximum frequency is 675MHz. Select frequency ( $f_{DAC}/4$  or  $f_{DAC}/2$ ), output current (3.5mA or 7mA), and termination (none or 100 $\Omega$ ) using register 0x02.

**DV**<sub>DD18</sub>: 1.8V Digital Supply Voltage Input. 1.8V to 1.92V.

**DV**<sub>DD33</sub>: 3.3V Digital Supply Voltage Input. 3.135V to 3.465V.

**FSADJ**: Full-Scale Adjust Pin. The DAC full-scale current is  $16 \cdot (V_{REFIO}/R_{FSADJ})$ . Connect a  $500\Omega$  resistor from FSADJ to GND to set the full-scale current to 40mA.

GND: Ground.

**I**<sub>OUTP</sub>, **I**<sub>OUTN</sub>: DAC Analog Current Outputs. Differential output is nominally  $\pm 40$ mA. Maximum update rate is 2.7Gsps. The output current is evenly divided between I<sub>OUTP</sub> and I<sub>OUTN</sub> when the two's compliment DAC code is set to mid-scale (all zeros).

$\overline{PD}$  (Pin S1): Active Low Power-Down Input. When  $\overline{PD}$  is low, the LTC2000A supply current is less than 440 $\mu$ A. To exit power-down mode switch  $\overline{PD}$  high to SV<sub>DD</sub>.

**REFIO:** Reference Voltage Input or Output. The 1.25V internal reference is available at the pin through a 10k internal resistor. May be overdriven with an external reference voltage between 1.1V and 1.4V.

**SCK:** Serial Interface Clock Input. Maximum frequency is 50MHz.

**SDI:** Serial Interface Data Input. Data on SDI is clocked in on the rising edge of SCK.

**SD0:** Serial Interface Data Output. Data is clocked out onto SD0 by the falling edge of SCK. SD0 is high impedance when  $\overline{\text{CS}}$  is high.

**SV<sub>DD</sub>:** SPI Supply Voltage Input. 1.71V to 3.465V.

**TSTP**, **TSTN**: Test Output Pins. May be optionally used to measure internal temperature or timing of LVDS inputs. See Measuring Internal Junction Temperature and Measuring LVDS Input Timing Skew sections in Applications Information. Use SPI internal registers 0x18 and 0x19 to control TSTP/N. Connect to GND if not used.

**Note:** For pin locations, refer to the Pin Locations section of this data sheet.

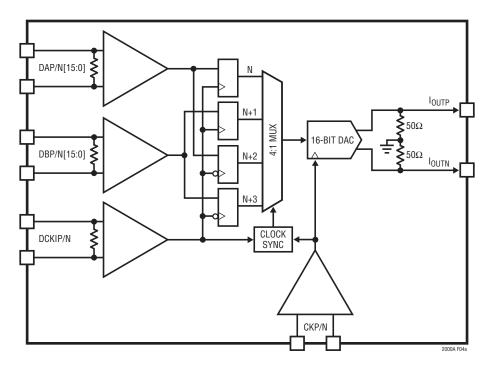

## **BLOCK DIAGRAM**

## TIMING DIAGRAMS

Figure 1. Serial Interface Timing

Figure 2. LVDS Interface Timing (DCKI\_Q = 0, DCK\_TADJ = 000)

Figure 3. LVDS Interface Timing (DCKI\_Q = 1)

## **OPERATION**

#### Introduction

The LTC2000A is a family of 2.7Gsps current steering DACs. Three resolutions (16-, 14-, 11-bit) are available in a 170-lead BGA package. The LTC2000A features high output bandwidth and output current, while maintaining a clean output spectrum with low spurs, making it ideal for generating high frequency or broadband signals. The LTC2000A output current is nominally 40mA and is a scaled (16x) replica of the current flowing out of the FSADJ pin (nominally 2.5mA). The high output current allows

flexibility in the output impedance, and the high FSADJ current and low scaling factor give excellent close-in phase noise performance.

The LTC2000A has two 16-, 14-, 11-bit wide LVDS or DHSTL-compatible parallel data input ports (DAP/N, DBP/N). Each data input port is capable of receiving two's complement data at up to 1.35Gbps using a double data rate (DDR) data input clock (DCKIP/N) at up to 675MHz. The DDR data input clock may be either in quadrature or in phase with the data arriving on the data input ports.

2000afb

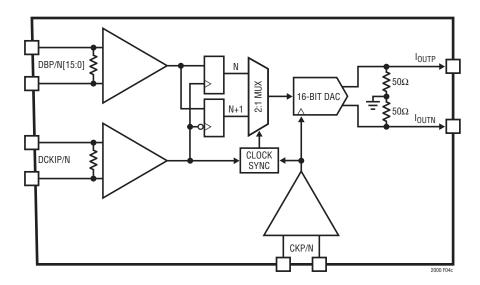

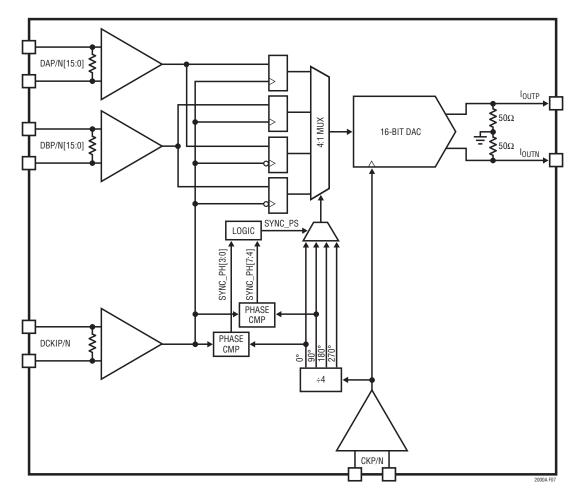

After incoming data is sampled by DCKIP/N, an internal multiplexer interleaves the data for resampling by the DAC sample clock (CKP/N). See Figures 4a and 4b. After a pipeline delay (latency) of up to 11 DAC sample clock cycles, the rising edges of CKP/N update the DAC code and a proportional differential output current is steered between the two outputs (I<sub>OUTP/N</sub>). Note it takes about 3ns (aperture delay) from the CKP/N rising edge that updates a DAC code to the actual I<sub>OUTP/N</sub> transition for that DAC code.

An internal clock synchronizer monitors the incoming phase of DCKIP/N and chooses the appropriate phase for the multiplexer control signals to ensure that the data is sampled correctly by CKP/N. The LTC2000A also generates an LVDS clock output (DCKOP/N) by dividing the sample clock frequency to simplify clocking of the host FPGA or ASIC. Additional features such as pattern generation, LVDS loopout, and junction temperature sensing simplify system development and testing.

The serial peripheral interface (SPI) port allows configuration and read back of the internal registers which control the above functions.

#### **Dual-Port Mode**

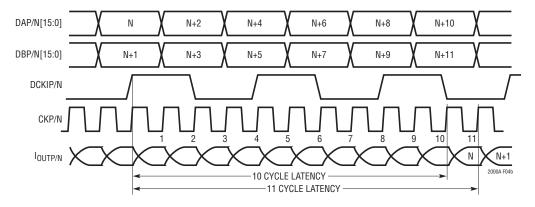

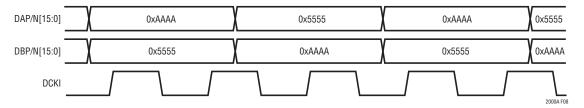

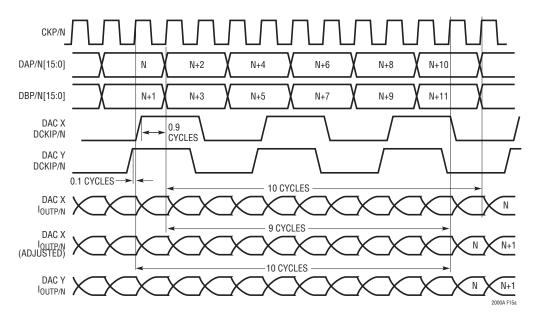

In dual-port mode, data is written to both ports A and B simultaneously and then subsequently interleaved inside the LTC2000A, allowing DAC output sampling rates of up to 2.7Gsps. Figures 4a and 4b show a simplified block diagram and sample waveforms for dual-port operation.

The LVDS data input ports A and B are sampled on both the falling and rising edges of the DDR data input clock (DCKIP/N) by four groups of flip-flops. The contents of these flip-flops are then interleaved by the 4:1 MUX and sampled by the DAC sample clock (CKP/N) at frequencies up to 2.7GHz, with data from port A (DAP/N) preceding data from port B (DBP/N) at the DAC output.

Note that the sample clock (CKP/N) frequency is always four times the DDR data input clock (DCKIP/N) frequency in dual-port mode. For example, to use the DAC at 2.7Gsps, apply a 2.7GHz clock to CKP/N and a 675MHz clock to DCKIP/N and send data into both ports A and B (DAP/N, DBP/N) at 1.35Gsps per port.

Latency is defined as the delay from the DCKIP/N transition that samples a DAC code to the CKP/N rising transition which causes that sample to appear at the DAC output  $I_{OUTP/N}$ . In dual-port mode the latency from DAP/N to  $I_{OUTP/N}$  is 10 sample clock cycles and the latency from DBP/N to  $I_{OUTP/N}$  is 11 cycles, starting from the CKP/N rising edge that immediately follows the DCKIP/N transition that sampled the DAC code (Figure 4b).

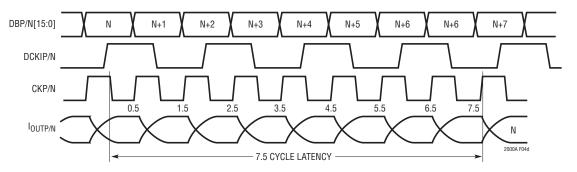

## Single-Port Mode

In single-port mode, data is written to port B (DBP/N) only, allowing DAC output sampling rates of up to 1.35Gsps. Figures 4c and 4d show a block diagram and sample waveforms representing single-port operation. Samples are written to port B (DBP/N) and sampled on both the falling and rising edges of the DDR data input clock (DCKIP/N) by two groups of flip-flops. The contents of these flip-flops are then interleaved into a single data stream by the 2:1 MUX and sampled by the DAC sample clock (CKP/N) at frequencies up to 1.35GHz.

Note that in single-port mode the sample clock (CKP/N) frequency is always twice the DDR data input clock (DCKIP/N) frequency. For example, to use the DAC at 1.35Gsps, apply a 1.35GHz clock to CKP/N and a 675MHz clock to DCKIP/N and send data into port B (DBP/N) at 1.35Gsps. In single-port mode, port A (DAP/N) should be grounded. Due to the design of the internal clock synchronizer in single port mode, there is a half cycle shift in the single port latency. The latency from DBP/N to  $I_{\rm OUTP/N}$  in single-port mode is 7.5 sample clock cycles, starting from the CKP/N falling edge that immediately follows the DCKIP/N transition that sampled the DAC code (Figure 4d).

Figure 4a. Simplified Block Diagram – Dual-Port Operation

Figure 4b. Sample Waveforms – Dual-Port Operation

Figure 4c. Simplified Block Diagram-Single-Port Operation

Figure 4d. Sample Waveforms - Single-Port Operation

### Serial Peripheral Interface (SPI)

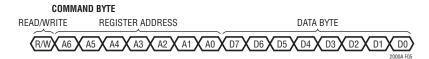

The LTC2000A uses an SPI/MICROWIRE-compatible 3-wire serial interface to configure and read back internal registers. The  $SV_{DD}$  pin is the power supply for the SPI interface (nominally 1.8V or 3.3V). The  $\overline{CS}$  input is level triggered. When this input is taken low, it acts as a chip-select signal, enabling the SDI and SCK buffers and the SPI input register. After the falling edge of  $\overline{CS}$ , the first data byte clocked into SDI by the rising edges of SCK is the command byte. The first bit of the command byte signifies a read (R/W = 1) or write (R/W = 0) operation. The next seven bits contain the register address, which completes the command byte.

The next byte transferred after the command byte is the data byte. For write operations, the data byte is written to the SPI register specified by the register address set in the command byte. During read operations, the data byte is ignored, and the contents of the selected SPI register are clocked out onto the SDO pin by the falling edges of SCK. During write operations, SDO will be low. When  $\overline{\text{CS}}$  goes high, SDO is high impedance. Figure 5 shows the SPI command and data input.

Users wishing to transfer multiple bytes of data at once may do so, with the address for each subsequent byte automatically incremented internally. The address will continue to increment until  $\overline{\text{CS}}$  goes high or until address bits A[4:0] reach 0x1F, after which subsequent bytes will continue to be written to the same address.

Reserved address and bit locations should not be written with any value other than zero. Table 11 contains a full description of all internal SPI registers and can be found in the SPI Register Summary section.

#### Power-On Reset

The internal power-on reset circuit will reset the LTC2000A upon power up and clear the output to mid-scale when power is first applied, making system initialization consistent and repeatable. All internal registers are reset to 0x00, with the exception of register address 0x08, which resets to 0x08. A software reset can also be applied by using the SPI interface to load 0x01 into register address 0x01, setting SW\_RST to 1 (see Table 1). Note that the SW\_RST bit is automatically cleared when  $\overline{\text{CS}}$  returns high. It is recommended that users perform a software reset once all power supplies are stable.

#### **Power Down**

Users wishing to save power when the DAC is not being used may reduce the supply current to less than  $440\mu A$  by pulling the  $\overline{PD}$  pin to GND or by writing to register 0x01 to set FULL\_PD = 1. Alternatively, users may power down unused portions of the chip individually using DAC\_PD, CK\_PD, DCKO\_DIS, DCKI\_EN, DA\_EN, and DB\_EN in registers 0x01, 0x02, 0x03, and 0x04 (see Table 1).

## **Reference Operation**

The LTC2000A has a 1.25V internal bandgap voltage reference that drives the REFIO pin through a 10k internal resistor, and should be buffered if driving any additional external load. For noise performance, a  $0.1\mu F$  capacitor to GND is recommended on the REFIO pin, but is not required for stability.

In the case where an external reference would be preferred, the external reference is simply applied to the REFIO pin and overdrives the internal reference. The acceptable external reference range is 1.1V to 1.4V.

Figure 5. SPI Command and Data Input

Table 1. Power-On Reset and Power-Down SPI Registers

| ADDRESS | BIT | NAME     | DESCRIPTION                                                                                                                                                                                                                             |

|---------|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01    | 0   | SW_RST   | Software Reset. Set SW_RST = 1 to restore all registers to their power-on reset state. SW_RST is automatically cleared when $\overline{\text{CS}}$ returns high. All registers reset to 0x00, except address 0x08 which resets to 0x08. |

|         | 1   | DAC_PD   | DAC Power Down. Set DAC_PD = 1 to power down the DAC and FSADJ bias circuits.                                                                                                                                                           |

|         | 2   | FULL_PD  | Full Power Down. Set FULL_PD = 1 to power down all active circuits on the chip and reduce the supply current to less than 100µA.                                                                                                        |

| 0x02    | 0   | CK_PD    | CKP/N Clock Receiver Power Down. CKP/N clock receiver is powered down when CK_PD = 1.                                                                                                                                                   |

|         | 4   | DCKO_DIS | DCKOP/N Output Disable. Set DCKO_DIS = 1 to power down the DCKO LVDS transmitter. For DCKO_DIS = 1, DCKOP/N are high impedance.                                                                                                         |

| 0x03    | 0   | DCKI_EN  | DCKIP/N Clock Receiver Enable. Set DCKI_EN = 1 to enable the DCKI clock receiver.                                                                                                                                                       |

| 0x04    | 0   | DA_EN    | DAC Data Port A LVDS Receiver Enable. Set DA_EN = 1 to enable port A (DAP/N) LVDS receivers. For DA_EN = 0, port A LVDS receivers are powered down and port A data will be zeroes.                                                      |

|         | 1   | DB_EN    | DAC Data Port B LVDS Receiver Enable. Set DB_EN = 1 to enable port B (DBP/N) LVDS receivers. For DB_EN = 0, port B LVDS receivers are powered down and port B data will be zeroes.                                                      |

Note: Registers 0x01 to 0x04 reset to 0x00 (default).

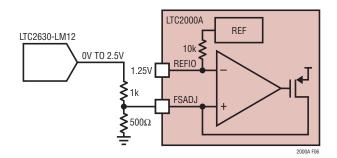

### **Setting the Full-Scale Current**

The full-scale DAC output current ( $I_{OUTFS}$ ) is nominally 40mA, but can be adjusted as low as 10mA or as high as 60mA. The full-scale current is set by placing an external resistor ( $R_{FSADJ}$ ) between the FSADJ pin and GND. An internal reference control loop amplifier sets the current flowing through  $R_{FSADJ}$  such that the voltage at FSADJ is equal to the voltage at REFIO, which is typically 1.25V.  $I_{OUTFS}$  is set as a scaled replica of the current flowing out of the FSADJ pin ( $I_{FSADJ}$ ):

$$I_{FSADJ} = \frac{V_{REFIO}}{R_{FSADJ}}$$

$$I_{OUTFS} = 16 \cdot I_{FSADJ} \cdot \frac{256}{256 + GAIN\_ADJ}$$

where GAIN\_ADJ is a 6-bit two's complement number from -32 to 31 (nominally 0) which can be programmed using SPI register 0x09 as shown in Table 2. For example, for  $R_{FSADJ} = 500\Omega$ ,  $V_{REFIO} = 1.25V$ , and GAIN\_ADJ = 0x00, the control loop will force 1.25V at the FSADJ pin, causing 2.5mA to flow through  $R_{FSADJ}$ .  $I_{OUTFS}$  will then be set to  $16 \cdot 2.5$ mA = 40mA.

Changing GAIN\_ADJ to 0x1F (+31) will decrease the current by 10.8% to 35.7mA. Changing GAIN\_ADJ to 0x20 (-32) will increase the current by 14.3% to 45.7mA.

Note that GAIN\_ADJ appears in the denominator of the equation for I<sub>OUTFS</sub>, so the adjustment resolution varies from 0.5% to 0.3% per step. The circuit shown in Figure 6 may be used to vary the full-scale output current beyond the range of the GAIN ADJ register.

DAC linearity and harmonic distortion may be degraded when using full-scale currents other than 40mA. The full-scale current must not exceed 60mA, and is recommended to be at least 10mA.

Figure 6. LTC2000A Full-Scale Adjust from 20mA to 60mA

Table 2. Full-Scale Gain Adjustment

| ADDRESS | BIT   | NAME     | DESCRIPTION    |                    |                 |                                                                 |

|---------|-------|----------|----------------|--------------------|-----------------|-----------------------------------------------------------------|

| 0x09    | [5:0] | GAIN_ADJ | GAIN_ADJ (HEX) | GAIN_ADJ (DECIMAL) | GAIN ADJUSTMENT | FULL-SCALE CURRENT $(R_{FSADJ} = 500\Omega, V_{REFIO} = 1.25V)$ |

|         |       |          | 0x1F           | +31                | 89.2%           | 35.68mA                                                         |

|         |       |          | 0x1E           | +30                | 89.5%           | 35.80mA                                                         |

|         |       |          | _              | _                  | _               | _                                                               |

|         |       |          | 0x01           | +1                 | 99.6%           | 39.84mA                                                         |

|         |       |          | 0x00           | 0                  | 100.0%          | 40.00mA                                                         |

|         |       |          | 0x3F           | -1                 | 100.4%          | 40.16mA                                                         |

|         |       |          | _              | _                  | _               | _                                                               |

|         |       |          | 0x21           | -31                | 113.8%          | 45.51mA                                                         |

|         |       |          | 0x20           | -32                | 114.3%          | 45.71mA                                                         |

Note: Register 0x09 resets to 0x00 (default).

#### **DAC Transfer Function**

The LTC2000A contains an array of current sources that are steered through differential switches to either  $I_{OUTP}$  or  $I_{OUTN}$ , depending on the DAC code programmed through the LVDS parallel interface. The LTC2000A uses a 16-/14-/11-bit two's complement DAC code. The complementary current outputs,  $I_{OUTP}$  and  $I_{OUTN}$ , source current from 0mA to  $I_{OUTFS}$ . For  $I_{OUTFS} = 40$ mA (nominal),  $I_{OUTP}$  swings from 0mA (for zero-scale DAC code) to 40mA (for full-scale DAC code).  $I_{OUTN}$  is complementary to  $I_{OUTP}$ . When the DAC code is set to mid-scale (all zeros),  $I_{OUTFS}$  is evenly divided between  $I_{OUTP}$  and  $I_{OUTN}$ .  $I_{OUTP}$  and  $I_{OUTN}$  are given by the following formulas:

#### LTC2000A-16:

$I_{OUTP} = I_{OUTFS} \bullet (CODE + 32768)/65536 + I_{OUTCM}$  $I_{OUTN} = I_{OUTFS} \bullet (32768 - CODE - 1)/65536 + I_{OUTCM}$

## LTC2000A-14:

$I_{OUTP} = I_{OUTFS} \bullet (CODE + 8192)/16384 + I_{OUTCM}$  $I_{OUTN} = I_{OUTFS} \bullet (8192 - CODE - 1/4)/16384 + I_{OUTCM}$

#### LTC2000A-11:

I<sub>OUTP</sub> = I<sub>OUTFS</sub> • (CODE + 1024)/2048 + I<sub>OUTCM</sub> I<sub>OUTN</sub> = I<sub>OUTFS</sub> • (1024 - CODE - 1/32)/2048 + I<sub>OUTCM</sub>

The DAC code ranges from  $-2^{N-1}$  to  $2^{N-1} - 1$ , with N being the DAC resolution (16/14/11). I<sub>OUTCM</sub> is a small, constant common-mode output current that is equal to approximately 0.2% full-scale, or 80µA for I<sub>OUTES</sub> = 40mA.

The LTC2000A differential output currents typically drive a resistive load either directly or drive an equivalent resistive load through a transformer (see the Output Configurations section). The voltage outputs generated by the  $I_{OUTP}$  and  $I_{OUTN}$  outputs currents are then:

$V_{OUTP} = I_{OUTP} \cdot R_{LOAD}$

$V_{OUTN} = I_{OUTN} \cdot R_{LOAD}$

$V_{DIFF} = V_{OUTP} - V_{OUTN} = (I_{OUTP} - I_{OUTN}) \cdot R_{LOAD}$

Substituting the values above gives:

#### LTC2000A-16:

$V_{DIFF} = V_{REFIO} \cdot (R_{LOAD}/R_{FSADJ}) \cdot (2 \cdot CODE + 1)/4096$

#### LTC2000A-14

$V_{DIFF} = V_{REFIO} \cdot (R_{LOAD}/R_{FSADJ}) \cdot (2 \cdot CODE + 1/4)/1024$

#### LTC2000A-11:

$V_{DIFF} = V_{REFIO} \cdot (R_{LOAD}/R_{FSADJ}) \cdot (2 \cdot CODE + 1/32)/128$

Note that the gain of the DAC depends on the ratio of  $R_{LOAD}$  to  $R_{FSADJ}$ , and the gain error tempco is affected by the temperature tracking of  $R_{LOAD}$  with  $R_{FSADJ}$ .

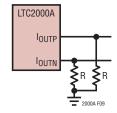

## Analog Outputs (I<sub>OUTP/N</sub>)

The two complementary analog outputs ( $I_{OUTP/N}$ ) have low output capacitance that, with appropriate  $R_{LOAD}$  values, can achieve high output bandwidths of 2.1GHz. The analog outputs also have an internal impedance of  $50\Omega$  to GND that will affect the calculation of  $R_{LOAD}$  and the output

voltage swing of the DAC. For example, loading both  $I_{OUTP}$  and  $I_{OUTN}$  with external  $50\Omega$  resistors to GND will cause  $R_{LOAD}$  to equal  $25\Omega$ . Assuming an  $I_{OUTFS}$  of 40mA,  $V_{DIFF}$  will swing between 1V and -1V.

The specified output compliance voltage range is ±1V. Above 1V, the differential current steering switches will start to approach the transition from saturation to linear region and degrade DAC linearity. Below –1V protection diodes will limit the swing of the DAC. Small voltage swings and low common-mode voltages typically result in the best distortion performance.

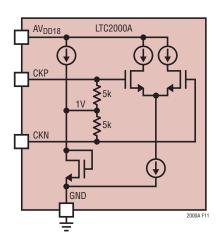

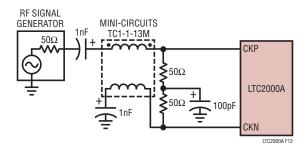

### DAC Sample Clock (CKP/N)

The DAC sample clock (CKP/N) is used to update the LTC2000A outputs at rates of up to 2.7Gsps. Provide a clean, low jitter differential clock at up to 2.7GHz on pins CKP/N (see Generating the DAC Sample Clock section). The DC bias point of CKP/N is set internally through a  $5k\Omega$  impedance. A 0dBm DAC sample clock should be sufficient to obtain the performance shown in the Typical Performance Characteristics section. For best jitter and phase noise, AC couple a differential clock onto CKP/N with balanced duty cycle and the highest possible amplitude and slew rate.

Use SPI register 0x02 to control the DAC sample clock receiver (Table 3). The LTC2000A contains a clock detector which sets  $CK_0K = 1$  if the DAC sample clock is present and  $f_{DAC} > 50MHz$ . When the sample clock is not present  $(CK_0K = 0)$ , the DAC output is forced to mid-scale and the internal data path is held at reset. Set  $CK_0K = 1$  to

power down the clock receiver and save power when the DAC is not being used. Note that at power-on reset, the DAC sample clock receiver is on by default.

### Divided Clock Output (DCKOP/N)

The LTC2000A contains a programmable clock divider and LVDS transmitter which provide a divided version (either  $f_{DAC}/4$  or  $f_{DAC}/2$ ) of the DAC sample clock for use by the host FPGA or ASIC. Use SPI register 0x02 to control DCKOP/N (Table 3). At power-on reset, the LVDS transmitter will provide a clock signal at  $f_{DAC}/4$  with a 3.5mA differential output current.

If desired, set DCKO\_DIV = 1 to change the divided clock output frequency to  $f_{DAC}/2$ . The output current can be increased to 7mA by setting DCKO\_ISEL = 1, and an internal  $100\Omega$  differential termination can be enabled by setting DCKO\_TRM = 1. Set DCKO\_DIS = 1 to disable the LVDS transmitter and save power when not in use.

### LVDS Data Clock Input (DCKIP/N)

The DAC code data written to the LTC2000A is captured on both the rising and falling edges of DCKIP/N. For single-port operation, provide a DDR clock at half the DAC sample clock frequency ( $f_{DCKI} = f_{DAC}/2$ ). To use a 1.35GHz sample clock in single-port mode, provide a 675MHz clock on DCKIP/N. For dual-port operation, provide a DDR clock at one quarter the DAC sample clock frequency ( $f_{DCKI} = f_{DAC}/4$ ). To use a 2.7GHz sample clock in dual-port mode, provide a 675MHz clock on DCKIP/N.

Table 3. DAC Sample Clock, and Divided Clock Output SPI Registers

| ADDRESS                                                     | BIT | NAME                                           | DESCRIPTION                                                                                                                                                                        |

|-------------------------------------------------------------|-----|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x02 0 CK_PD CKP/N Clock Receiver Power Down When CK_PD = 1 |     | CKP/N Clock Receiver Power Down When CK_PD = 1 |                                                                                                                                                                                    |

|                                                             | 1   | CK_OK                                          | CKP/N Clock Present Indicator. When CK_OK = 1, clock is present at CKP/N pins and f <sub>DAC</sub> > 50MHz. When CK_OK = 0, DAC output is forced to mid-scale. CK_OK is read only. |

|                                                             | 4   | DCKO_DIS                                       | DCKOP/N Output Disable. Set DCKO_DIS = 1 to power down the DCKO LVDS transmitter. For DCKO_DIS = 1, DCKOP/N are high impedance.                                                    |

|                                                             | 5   | DCKO_DIV                                       | DCKOP/N Divide Select. When DCKO_DIV = 0, $f_{DCKOP/N} = f_{DAC}/4$ . When DCKO_DIV = 1, $f_{DCKOP/N} = f_{DAC}/2$ .                                                               |