## **MAX77505**

#### **General Description**

The MAX77505 is a low-quiescent current (800nA typ), high-efficiency hysteretic buck converter operating from a 2.5V to 16V input voltage range. The device offers high efficiency over the entire load range. Hence, it is ideal for either a primary battery or four alkaline batterypowered applications, which require long standby/idling time with short working time, such as asset tracking and door-lock devices.

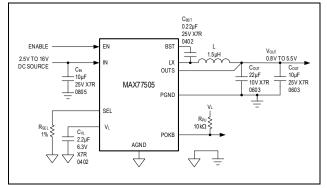

A resistor ( $R_{SEL}$ ) selects one of thirty preset output voltages between 0.8V and 5.5V. The device has input undervoltage lockout, cycle-by-cycle switch current limit, and thermal shutdown to protect the system and the device itself. The device is available in a 10-lead FC2QFN package (2.0mm x 2.0mm x 0.55mm).

## **Applications**

- 2-3 Cell Li+ Battery Applications

- 4-Cell Alkaline Battery Applications

- IoT, Wearable Devices

- Smart Meter, Door Locks, Asset Trackers, etc.

## **Benefits and Features**

- Input Voltage: 2.5V to 16V

- Output Voltage: 0.8V to 5.5V

- Long Battery Life

- 70nA Shutdown Current

- 800nA Ultra-Low Quiescent Current (IQ)

- 86% Efficiency at 100µA Load at 7.6V<sub>IN</sub>, 3.3V<sub>OUT</sub>

- 95% Peak Efficiency at 7.6V<sub>IN</sub>, 3.3V<sub>OUT</sub>

- POKB Output (Open-Drain)

- SEL Pin for Output Voltage Selection

- Protections Features

- Cycle-by-Cycle Inductor Peak Current Limit

- Short Circuit, Undervoltage Lockout (UVLO), and Thermal Protection

- FC2QFN-10 Package (2.0mm x 2.0mm x 0.55mm)

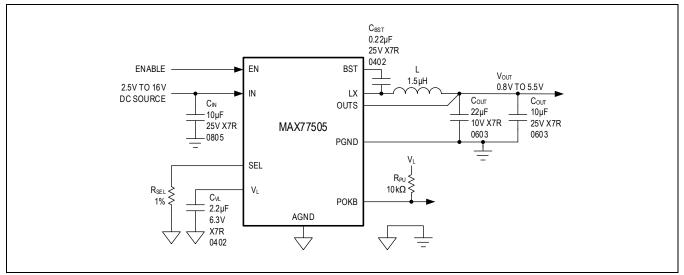

## **Simplified Application Diagram**

Ordering Information appears at end of data sheet.

nanoPower Technology is a trademark of Maxim Integrated Products, Inc.

## **Absolute Maximum Ratings**

| IN, LX to PGND0.3V to +17.6V                                           | PGND to AGND0.3V to +0.3V                                     |

|------------------------------------------------------------------------|---------------------------------------------------------------|

| LX to PGND (less than 10ns) (Note 1) (V <sub>IN</sub> – 22)V to +22.0V | Continuous Power Dissipation at T <sub>A</sub> = 70°C (Derate |

| BST to LX0.3V to +2.0V                                                 | 12.05mW/°C above +70°C) (Note 2)                              |

| V <sub>L</sub> , POKB, SEL to AGND0.3V to +2.0V                        | Maximum Junction Temperature+150°C                            |

| EN to AGND0.3V to +17.6V                                               | Storage Temperature Range65°C to +150°C                       |

| OUTS to AGND                                                           | Soldering Temperature (Reflow)+260°C                          |

- **Note 1:** LX has internal clamp diodes to its corresponding PGND and IN. Applications that forward bias these diodes should not exceed the ICs package power dissipation limits.

- Note 2: Package thermal measurements were obtained using the method described in JEDEC specification JESD51-7, using a FR-4, four-layer board. For detailed information on package thermal considerations, refer to https://www.analog.com/en/technical-articles/thermal-characterization-of-ic-packages.html

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Recommended Operating Conditions**

| PARAMETERS                 | SYMBOL           | CONDITIONS | TYPICAL RANGE   |

|----------------------------|------------------|------------|-----------------|

| Input Voltage Range        | V <sub>IN</sub>  |            | 2.5V to 16V     |

| Output Current Range       | I <sub>OUT</sub> |            | 0A to 3A        |

| Junction Temperature Range | ТJ               |            | -40°C to +125°C |

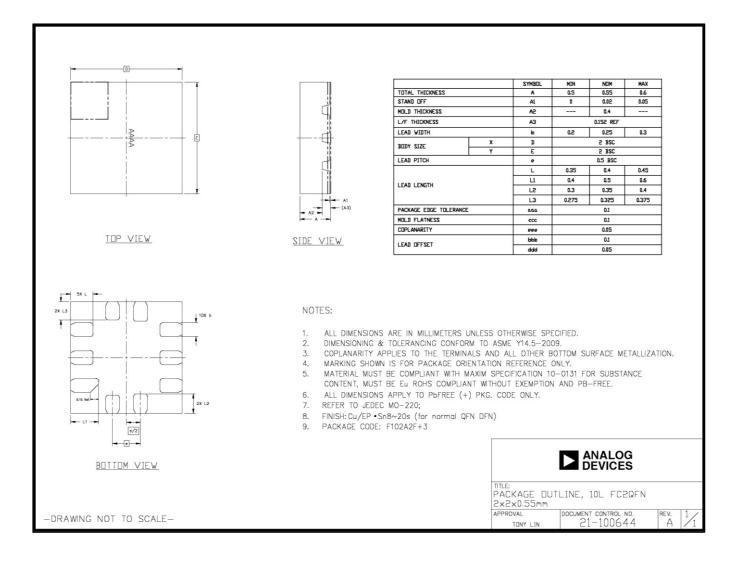

## Package Information

#### 10 FC2QFN

| Package Code                                              | F102A2F+3                      |  |  |  |

|-----------------------------------------------------------|--------------------------------|--|--|--|

| Outline Number                                            | <u>21-100644</u>               |  |  |  |

| Land Pattern Number                                       | Refer to Application Note 1891 |  |  |  |

| Thermal Resistance, Four Layer Board:                     |                                |  |  |  |

| Junction-to-Ambient ( $\theta_{JA}$ )                     | 83.01°C/W                      |  |  |  |

| Junction-to-Case (BOT) Thermal Resistance $(\theta_{JC})$ | 38.24°C/W                      |  |  |  |

## **Electrical Characteristics**

$(T_A \approx T_J, V_{IN} = 7.6V, V_{OUT} = 3.3V, Typicals are at T_A \approx T_J = +25^{\circ}C$ . Limits are 100% production tested at  $T_J = +25^{\circ}C$ . The MAX77505 is tested under pulsed load conditions such that  $T_A \approx T_J$ . Limits over the operating temperature range  $(T_J = -40^{\circ}C \text{ to } +125^{\circ}C)$  and relevant voltage range are guaranteed by design and characterization using statistical process control methods. (Note 3))

| PARAMETER                                     | SYMBOL                | CON                                                          | DITIONS                                                   | MIN   | TYP   | MAX   | UNITS |  |

|-----------------------------------------------|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------|-------|-------|-------|-------|--|

| INPUT SUPPLY                                  |                       |                                                              |                                                           | •     |       |       |       |  |

| Operating Voltage<br>Range                    | V <sub>IN</sub>       |                                                              |                                                           | 2.5   |       | 16    | V     |  |

| Undervoltage Lockout                          | V <sub>UVLO_R</sub>   | V <sub>IN</sub> rising                                       |                                                           | 2.400 | 2.450 | 2.500 |       |  |

| (UVLO)                                        | V <sub>UVLO_F</sub>   | V <sub>IN</sub> falling                                      |                                                           | 2.325 | 2.375 | 2.425 | V     |  |

| Shutdown Current                              | I <sub>SHDN</sub>     | EN = Low, V <sub>IN</sub> < 1                                | 3V, T <sub>J</sub> = +25°C                                |       | 70    | 300   | nA    |  |

| Quiescent Current                             | Ι <sub>Q</sub>        | EN = High, no load                                           | l, T <sub>J</sub> = +25°C                                 |       | 800   |       | nA    |  |

| OUTPUT VOLTAGE ACC                            | URACY                 |                                                              |                                                           |       |       |       |       |  |

| Output Voltage Range                          | V <sub>OUT</sub>      |                                                              |                                                           | 0.8   |       | 5.5   | V     |  |

| Output Voltage<br>Accuracy                    | V <sub>OUT_ACC</sub>  | V <sub>IN</sub> = 2 x V <sub>OUT</sub>                       | In CCM operation                                          | -2    |       | +2    | %     |  |

| Low-Power Mode Over-                          |                       | Measured as a percentage of                                  | 0.8V ≤ V <sub>OUT</sub> ≤<br>2.3V                         | +2.75 | +4.5  | +6    | %     |  |

| Regulation Hysteresis<br>(Skip Lower Limit)   | V <sub>OUT_HYS</sub>  | target output<br>voltage                                     | 2.5V ≤ V <sub>OUT</sub> ≤<br>5.5V                         | +1.2  | +2.75 | +4    | %     |  |

| OUTPUT VOLTAGE REG                            | ULATION               |                                                              |                                                           |       |       |       |       |  |

| Line Regulation                               | $\Delta V/V_{IN}$     | ( <u>Note 4</u> )                                            | V <sub>IN</sub> = 2.5V to 16V,<br>I <sub>OUT</sub> = 0.8A | -0.1  |       | +0.1  | %/V   |  |

| Load Regulation                               | $\Delta V/I_{OUT}$    | ( <u>Note 4</u> )                                            | In CCM operation                                          |       | 0.35  |       | %/A   |  |

| POWER STAGE                                   |                       |                                                              |                                                           |       |       |       |       |  |

| High-Side MOSFET<br>Peak Current Limit        | I <sub>LIM</sub>      |                                                              |                                                           | 4000  | 4600  | 5200  | mA    |  |

| High-Side MOSFET On-<br>Resistance            | R <sub>DSON_HS</sub>  | I <sub>LX</sub> = -300mA                                     |                                                           |       | 50    |       | mΩ    |  |

| Low-Side MOSFET On-<br>Resistance             | R <sub>DSON_LS</sub>  | I <sub>LX</sub> = 300mA                                      |                                                           |       | 45    |       | mΩ    |  |

| Switching Frequency                           | fsw                   | In CCM operation                                             |                                                           |       | 2.0   |       | MHz   |  |

| Output Voltage Active<br>Discharge Resistance | R <sub>ADIS</sub>     |                                                              |                                                           |       | 120   |       | Ω     |  |

| Minimum Effective                             | C <sub>EFF(MIN)</sub> | 0.8V ≤ V <sub>OUT</sub> < 1.5                                | V                                                         |       | 20    |       | μF    |  |

| Output Capacitance                            |                       | V <sub>OUT</sub> ≥ 1.5V                                      |                                                           | 10    |       |       | μΓ    |  |

| TIMING                                        |                       | -                                                            |                                                           |       |       |       |       |  |

| Turn-On Delay Time                            | <sup>t</sup> DLY_EN   | From EN = High to<br>10°C to +125°C                          | POKB = Low, T <sub>J</sub> = -                            |       | 3     | 32    | ms    |  |

| LOGIC THRESHOLD                               |                       |                                                              |                                                           |       |       |       |       |  |

| Input High Level                              | VIH                   |                                                              |                                                           | 1.2   |       |       | V     |  |

| Input Low Level                               | VIL                   |                                                              |                                                           |       |       | 0.4   | V     |  |

| Output Low Level                              | V <sub>OL</sub>       | I <sub>POKB</sub> = -1mA                                     |                                                           |       |       | 0.3   | V     |  |

| Inverted Power-OK                             | V <sub>POKB_F</sub>   | V <sub>OUT</sub> rising, expre<br>of target V <sub>OUT</sub> | ssed as a percentage                                      | 90    | 93    |       | ~     |  |

| (POKB) Threshold                              |                       | Vau falling over                                             | essed as a percentage                                     | İ     |       |       | - %   |  |

## 16V Input, 4.6A Switching Current Low IQ Buck Converter

$(T_A \approx T_J, V_{IN} = 7.6V, V_{OUT} = 3.3V, Typicals are at T_A \approx T_J = +25^{\circ}C$ . Limits are 100% production tested at  $T_J = +25^{\circ}C$ . The MAX77505 is tested under pulsed load conditions such that  $T_A \approx T_J$ . Limits over the operating temperature range  $(T_J = -40^{\circ}C \text{ to } +125^{\circ}C)$  and relevant voltage range are guaranteed by design and characterization using statistical process control methods. (Note 3))

| PARAMETER                      | SYMBOL                | CONDITIONS            | MIN | TYP | MAX | UNITS |

|--------------------------------|-----------------------|-----------------------|-----|-----|-----|-------|

| Thermal Shutdown<br>Threshold  | T <sub>SHDN</sub>     | T <sub>J</sub> rising |     | 150 |     | °C    |

| Thermal Shutdown<br>Hysteresis | T <sub>SHDN_HYS</sub> |                       |     | 20  |     | °C    |

**Note 3:** The maximum ambient temperature consistent with this specification is determined by specific operating conditions, board layout, rated package thermal impedance, and other environmental factors.

Note 4: Not production tested. Design guidance only.

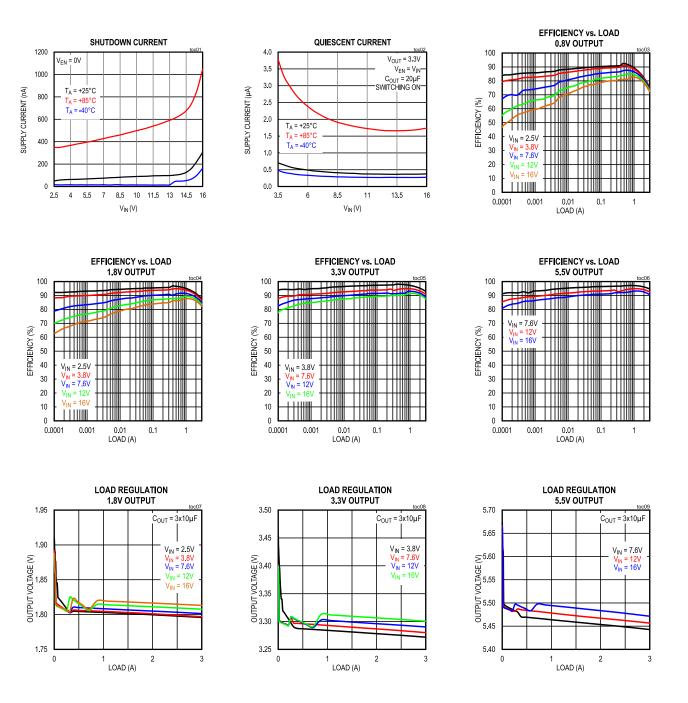

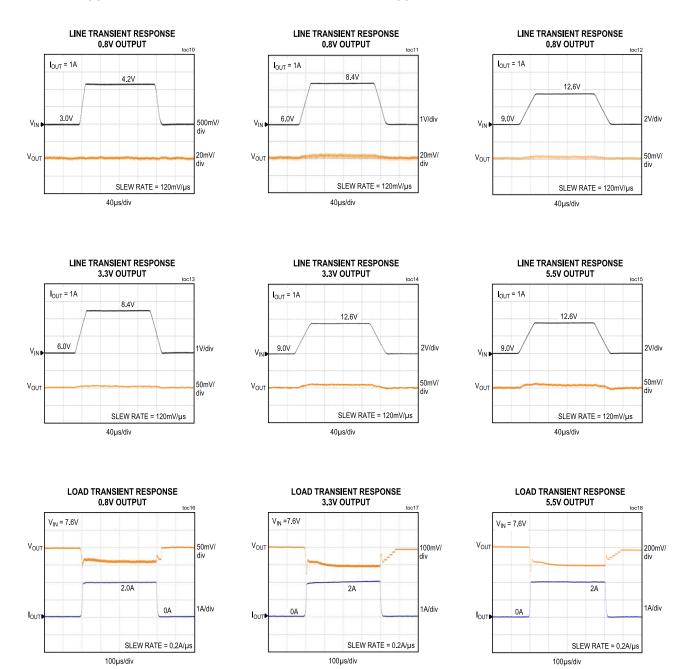

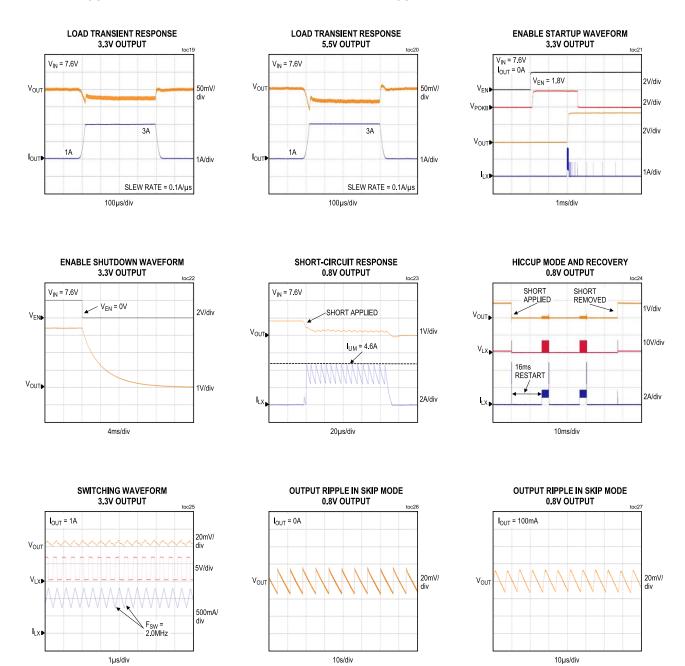

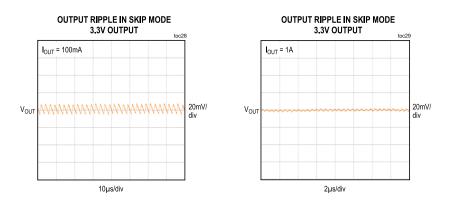

## **Typical Operating Characteristics**

(VIN = 7.6V, VOUT = 3.3V, L = 1.5µH (Sumida 0420CDMCCDS-1R5MC), COUT = 3x10µF, TA = +25°C, unless otherwise noted.)

(VIN = 7.6V, VOUT = 3.3V, L = 1.5µH (Sumida 0420CDMCCDS-1R5MC), COUT = 3x10µF, TA = +25°C, unless otherwise noted.)

(VIN = 7.6V, VOUT = 3.3V, L = 1.5µH (Sumida 0420CDMCCDS-1R5MC), COUT = 3x10µF, TA = +25°C, unless otherwise noted.)

## 16V Input, 4.6A Switching Current Low IQ Buck Converter

(VIN = 7.6V, V<sub>OUT</sub> = 3.3V, L = 1.5µH (Sumida 0420CDMCCDS-1R5MC), C<sub>OUT</sub> = 3x10µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

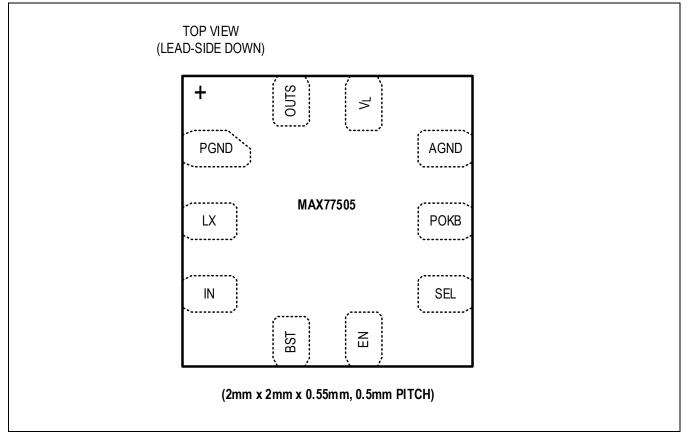

## **Pin Configurations**

## 10 FC2QFN

## **Pin Descriptions**

| PIN | NAME | FUNCTION                                                                                          | Туре              |

|-----|------|---------------------------------------------------------------------------------------------------|-------------------|

| 1   | PGND | Power Ground                                                                                      | Power<br>Ground   |

| 2   | LX   | Buck Converter Switch Node                                                                        | Power             |

| 3   | IN   | Buck Converter Power Input. Bypass to PGND with a 10µF X7R ceramic capacitor.                     | Power<br>Input    |

| 4   | BST  | Buck Converter Bootstrap Input. Connect a 0.22µF X7R ceramic capacitor between BST and LX.        | Power             |

| 5   | EN   | Buck Converter Enable Input                                                                       | Input             |

| 6   | SEL  | Output Voltage Selection Input. Connect a resistor between SEL and AGND to preset output voltage. | Analog            |

| 7   | POKB | Inverted Power-OK Output (Open-Drain).<br>A 10kΩ pullup resistor is required.                     | Digital<br>Output |

| 8   | AGND | Analog Ground                                                                                     | Analog<br>Ground  |

| 9   | VL   | Internal LDO Bypass Output. Bypass to AGND with a 2.2µF X7R ceramic capacitor.                    | Analog            |

| 10  | OUTS | Buck Output Voltage Sensing Input                                                                 | Analog<br>Input   |

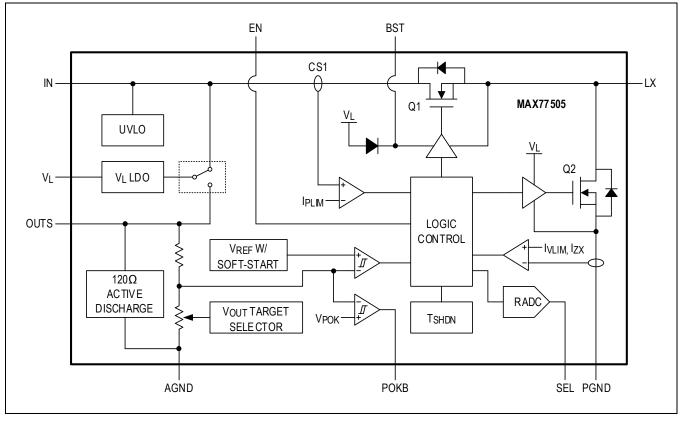

## **Block Diagram**

## **Detail Descriptions**

The MAX77505 is a small, high-efficiency nanoPower step-down (buck) DC-DC converter. The step-down converter uses synchronous rectification and internal current mode compensation. The buck operates on a supply voltage between 2.5V and 16V. The output voltage is configurable through a single resistor ( $R_{SEL}$ ) from the SEL pin to ground. The buck utilizes Analog Devices nanoPower Technology<sup>TM</sup> to achieve ultra-low sub-microampere quiescent current ( $I_Q$ ), which maintains high efficiency at light loads.

#### **Buck Regulator Control Scheme**

The MAX77505 buck converter uses a current-control hysteretic topology. The buck converter senses the inductor current to implement a pseudo-fixed inductor ripple current, which gives approximately 2MHz switching frequency in CCM operation under typical operating conditions ( $V_{IN}$  = 7.6V,  $V_{OUT}$  = 3.3V with a 1.5µH inductor). To accommodate the pseudo-fixed inductor current ripple, the switching frequency varies over operating conditions.

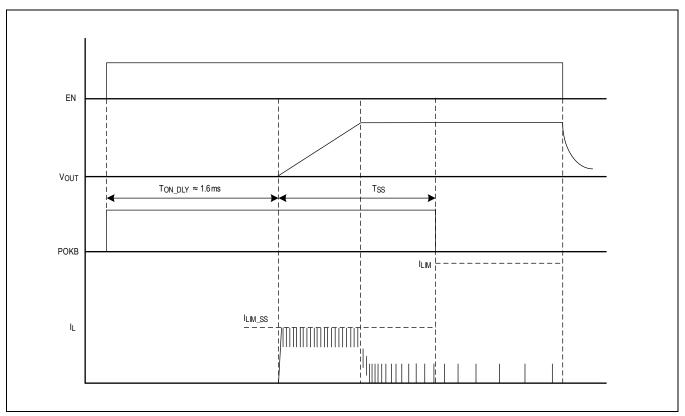

In DCM operation, the buck converter turns on the high side MOSFET (Q1) until the inductor current reaches  $I_{LIM}/6$ . The buck converter then turns on the low side MOSFET (Q2) to deliver the energy stored in the inductor until the inductor current falls below  $I_{ZX}$  (zero crossing). When zero crossing is no longer detected due to an increased load current, the buck controller increases the peak current limit from  $I_{LIM}/6$  to  $I_{LIM}/3$  and repeats the process. When zero crossing is no longer detected after  $I_{LIM} = I_{LIM}/3$ , the part transitions into CCM. See *Figure 1* and *Table 1* for more information.

Once the sensed output voltage at the OUTS pin reaches the low-power mode over-regulation hysteresis ( $V_{OUT_HYS}$ ), the buck converter goes into low-power mode by turning off control circuits whenever the inductor current zero-crossing is detected. In low-power mode, the controller wakes up every 20ms to check if the output voltage is still higher than  $V_{OUT_HYS}$ . If the output voltage hits  $V_{OUT_HYS}$  while the buck controller is awake, it initiates an LX switching. In case the output voltage drops below  $V_{OUT_HYS}$  by 10mV, the buck controller exits low-power mode immediately.

Figure 1. MAX77505 Startup Operation

#### Output Enable Control

The MAX77505 includes an EN pin that can be used to turn on the 16V input low quiescent current hysteretic buck converter. It can be connected to a separate supply as well as pulled up to IN. When the EN pin is pulled HIGH, the MAX77505 goes through the soft-start process to start the buck converter to the output voltage selected by the R<sub>SEL</sub> which can be seen in <u>Table 1</u>. See the <u>Startup</u> section and <u>Output Voltage Selection</u> section for more details.

When the EN pin goes low, the MAX77505 stops switching immediately and turns off the output voltage active discharge circuit which is described in the <u>Output Voltage Active Discharge</u> section.

#### Startup

When the EN pin goes logic high, the internal reference circuit and the bias circuits start up and then the resistance value at the SEL pin is latched. With about 1.6ms of startup delay time, the MAX77505 initiates the soft-start.

The soft-start function is to prevent the MAX77505 from drawing too much current from the input source (due to an inrush current to the output capacitors) by ramping up the internal reference voltage from zero to the target value with a controlled slew rate. During startup, the MAX77505 also reduces the switch current limit to 25% of its normal value until the POKB comparator triggers.

#### Power Down

When the EN pin is pulled logic low threshold, the MAX77505 stops switching and turns on the output voltage discharge resistor until the output is discharged.

#### **Output Voltage Selection with RSEL**

Whenever the MAX77505 is enabled, it reads the resistance ( $R_{SEL}$ ) between the SEL and AGND and programs the output voltage according to <u>*Table 1*</u>. Ensure that  $R_{SEL}$  resistors have 1% or better tolerances.

| R <sub>SEL</sub> (Ω) | V <sub>OUT</sub> (V) | R <sub>SEL</sub> (Ω) | V <sub>OUT</sub> (V) |

|----------------------|----------------------|----------------------|----------------------|

| ≤ 95.3               | 3.3                  | 3.74k                | 3.0                  |

| 200                  | 0.8                  | 8.06k                | 3.2                  |

| 309                  | 0.9                  | 12.4k                | 3.4                  |

| 422                  | 1.0                  | 16.9k                | 3.6                  |

| 536                  | 1.1                  | 21.5k                | 3.7                  |

| 649                  | 1.2                  | 26.1k                | 3.8                  |

| 768                  | 1.3                  | 30.9k                | 4.0                  |

| 909                  | 1.5                  | 36.5k                | 4.2                  |

| 1.05k                | 1.8                  | 42.2k                | 4.3                  |

| 1.21k                | 1.9                  | 48.7k                | 4.5                  |

| 1.40k                | 2.2                  | 56.2k                | 5.0                  |

| 1.62k                | 2.3                  | 64.9k                | 5.2                  |

| 1.87k                | 2.5                  | 75.0k                | 5.3                  |

| 2.15k                | 2.7                  | 86.6k                | 5.5                  |

| 2.49k                | 2.8                  | 100k                 | 3.1                  |

| 2.87k                | 2.9                  | ≥ 115k               | 4.8                  |

#### Table 1. R<sub>SEL</sub> Selection Table

#### Switch Current Limit

The MAX77505 provides a cycle-by-cycle switch current limit ( $I_{LIM}$ ) at the high-side MOSFET. When the peak current limit is triggered, the MAX77505 turns off the high-side MOSFET immediately and the low-side MOSFET starts to discharge the inductor current and the high-side MOSFET stays off until the inductor current reaches 50% of the  $I_{LIM}$ . In case the MAX77505 detects peak current limit events more than 16 times consecutively, the MAX77505 enters hiccup mode and keeps both high-side and low-side MOSFETs off for about 15ms before attempting startup again.

When the zero crossing is detected at the low-side MOSFET, both the high-side and the low-side MOSFETs are turned off (Hi-Z state of LX node) until the voltage at the OUTS pin falls below its target output voltage.

#### **Output Voltage Active Discharge**

When the MAX77505 is disabled by the EN pin or the UVLO fault event, the active discharge circuit is engaged to discharge the energy stored at the output capacitor. When the active discharge circuit is activated, a  $120\Omega$  (typ) resistor is connected between the OUTS pin and AGND.

#### Undervoltage Lockout

When the input voltage falls below the UVLO falling threshold ( $V_{UVLO_F}$ , 2.375V, typ) during the operation, the MAX77505 disables the buck output immediately. If the EN pin is kept high, the MAX77505 automatically reinitiates the startup procedure when the input voltage rises above the UVLO rising threshold ( $V_{UVLO_R}$ , 2.450V typ).

#### **Thermal Shutdown**

When the junction temperature exceeds 150°C (typ), the buck converter output is latched off and is not allowed to restart until the junction temperature drops below the thermal shutdown hysteresis level (130°C, typ). Once the junction temperature cools down, either power cycling of the input voltage or toggling the EN pin is required to restart the buck converter from the latch-off state.

## **Applications Information**

#### Inductor Selection

Choose an inductor with a saturation current that is greater than or equal to the maximum peak current limit setting ( $I_{LIM}$ ). Inductors with lower saturation current and higher DCR ratings tend to be physically small. Higher values of DCR reduce buck efficiency. Choose the RMS current rating of the inductor (the current at which temperature rises appreciably) based on the system's expected load current.

The chosen inductor value should ensure that the peak inductor ripple current ( $I_{PEAK}$ ) is below the high-side MOSFET peak current limit ( $I_{LIM}$ ) so that the buck can maintain voltage regulation overload. A 1.5µH value inductor is recommended through the operation range of the device.

#### **Input Capacitor selection**

Choose the input capacitor ( $C_{IN}$ ) to be a 10µF nominal capacitor that maintains 2µF effective capacitance at its working voltage. Larger values improve the decoupling of the buck converter but increase inrush current from the voltage supply when connected.  $C_{IN}$  reduces the current peaks drawn from the input power source during buck operation and filters the switching noise in the system.

#### **Output Capacitor Selection**

Sufficient output capacitance ( $C_{OUT}$ ) is required for stable operation of the buck. Choose the effective  $C_{OUT}$  to be 20µF minimum for output voltage ranges between 0.8V to 1.5V and 10µF for output ranges above 1.5V.

Effective  $C_{OUT}$  is the actual capacitance value seen by the buck output during operation. Choose effective  $C_{OUT}$  carefully by considering the capacitor's initial tolerance, variation with temperature, and derating with DC bias. Refer to <u>*Tutorial*</u> <u>5527</u> for more information.

Larger values of  $C_{OUT}$  (above the required effective minimum) improve load transient performance but increase the input surge currents during soft-start and output voltage changes. The output filter capacitor must have low enough ESR to meet output ripple and load transient requirements. The output capacitance must be high enough to absorb the inductor energy while transitioning from full-load to no-load conditions. When using high-capacitance, low-ESR capacitors, the filter capacitor's ESR dominates the output voltage ripple in continuous conduction mode.

Ceramic capacitors with X5R or X7R dielectric are highly recommended due to their small size, low ESR, and small temperature coefficients. All ceramic capacitors derate with DC bias voltage (effective capacitance goes down as DC bias goes up). Generally, small case size capacitors derate heavily compared to larger case sizes (0603 case size performs better than 0402). Consider the effective capacitance value carefully by consulting the manufacturer's data sheet.

#### **Bootstrap Capacitor**

Sufficient bootstrap capacitance is required to ensure that the internal gate drive for the switch MOSFETs is properly biased. Select a bootstrap capacitor  $C_{BST}$  value of 0.22µF. Ensure that the voltage rating of the bootstrap capacitor is a minimum of 2V.

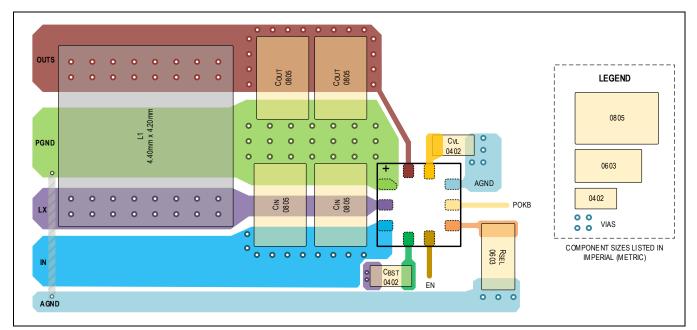

#### **PCB Layout Guidelines**

Careful circuit board layout is critical to achieve low switching power losses and clean, stable operation. <u>Figure 2</u> shows an example of a PCB top-metal layout for the device.

Follow these guidelines when designing the PCB:

- Place the input capacitors immediately next to the IN pin of the device. Since the device can operate up to 2.0MHz switching frequency, this placement is critical for the effective decoupling of high-frequency noise from the IN pin.

- Place the inductor and output capacitor close to the device and keep the loop area of the switching current small.

- Make the trace between LX and the inductor short and wide. Do not take up an excessive amount of area. The voltage

on this node switches quickly and additional area creates additional radiated emissions.

- Connect AGND and PGND on the PCB. Connect them through a low-impedance inner PCB ground layer close to the IC.

- Keep the power traces and load connections short and wide. Use both top and inner PCB copper planes to reduce the trace impedance. This practice is essential for high-efficiency performance.

- Place the V<sub>L</sub> capacitor close to the V<sub>L</sub> pin and next to the AGND pin.

Figure 2. PCB Layout Example (FC2QFN)

## **Typical Application Circuit**

## **Ordering Information**

| PART NUMBER    | I <sub>LIM</sub> (TYP) | PIN-PACKAGE |

|----------------|------------------------|-------------|

| MAX77505AEFB+  | 4.6A                   | 10-FC2QFN   |

| MAX77505AEFB+T | 4.6A                   | 10-FC2QFN   |

+Denotes a lead(Pb)-free/ROHS-compliant package.

T = Tape and reel.

Note: Contact Analog Devices for a list of future products.

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|------------------|-----------------|------------------|

| 0                  | 10/23            | Initial release |                  |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

MAX77505AEFB+T