# Low Noise, Low Power, Wide Bandwidth, 3-Axis MEMS Accelerometer

#### **FEATURES**

- ▶ Ultralow noise density: 20  $\mu g/\sqrt{Hz}$  (XY) and 27  $\mu g/\sqrt{Hz}$  (Z)

- ▶ Low power consumption

- High performance: 340 µA

- ▶ Ultra-low power: 33 µA

- Wide bandwidth: 4 kHz

- Relative flatness with equalization: <0.5 dB</p>

- ▶ Relative flatness without equalization: <2 dB

- ▶ Low latency: group delay <110 µs

- Digital features

- ▶ 16-bit ADC

- Multiprotocol serial interfaces: SPI or I<sup>2</sup>C

- ▶ Multiprotocol audio data output: I<sup>2</sup>S, TDM, and PDM

- ▶ Programmable LPF and HPF

- Data synchronous or asynchronous sampling

- Output FIFO: 320 word

- Built-in features for system-level power savings

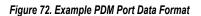

- Single tap, double tap, and triple tap detection

- Activity and inactivity detection

- Configurable interrupt modes

- Integrated temperature sensor

- Voltage range options

- V<sub>S</sub> with internal regulators: 2.25 V to 3.6 V (or V<sub>1P8</sub> at 1.8 V)

- ► V<sub>DDIO</sub>: 1.14 V to 3.6 V (1.62 V to 3.6 V for full temperature range)

- Electromechanical self test

- ▶ 10,000 g mechanical shock survival

- ▶ RoHS compliant

- ► Operating temperature range: -40°C to +85°C

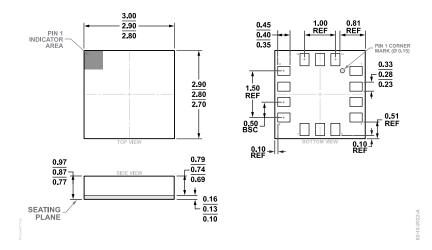

- ▶ 14-terminal, 2.9 mm × 2.8 mm × 0.87 mm, LGA package

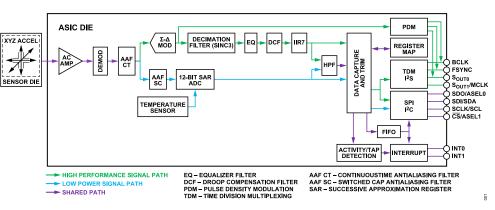

#### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The ADXL380 is a low noise density, low power, 3-axis accelerometer with selectable measurement ranges. The ADXL380 supports the  $\pm 4 g$ ,  $\pm 8 g$ , and  $\pm 16 g$  ranges.

The ADXL380 offers industry leading noise, enabling precision applications with minimal calibration. The low noise and low power ADXL380 enables accurate measurements of audio signals or heart sounds even in high vibration environments.

The ADXL380 multifunction pin names may be referenced only by their relevant function for either the serial peripheral interface (SPI) or inter-IC( $I^2C$ ) interface, or these pin names can be referenced by their audio function (pulse density modulation (PDM), inter-IC sound ( $I^2S$ ), or time division multiplexing (TDM)).

In addition to its low power consumption, the ADXL380 has many features to enable true system level performance. These features include a built-in micropower temperature sensor, singletap, double tap, and triple tap detection, and a state machine to prevent false triggering. In addition, the ADXL380 has provisions for external control of the sampling time and/or an external clock.

The ADXL380 operates on a wide, 2.25 V to 3.6 V supply range (or 1.8 V supply) and can interface, if necessary, to a host operating on a separate supply voltage. The ADXL380 is available in a 14-terminal, 2.9 mm × 2.8 mm × 0.87 mm, LGA package.

#### **APPLICATIONS**

- Audio and active noise cancellation (ANC)

- Robotics

- Wearables and low power motion detection

- Seismic imaging

- Condition-based monitoring

#### Figure 1. Functional Block Diagram

#### Rev. 0

DOCUMENT FEEDBACK

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| General Description                         | 1  |

| Applications                                | 1  |

| Functional Block Diagram                    | 1  |

| Specifications                              | 4  |

| Timing Specifications                       | 7  |

| Digital Timing Diagrams                     |    |

| Absolute Maximum Ratings                    |    |

| Thermal Resistance                          |    |

| Recommended Soldering Profile               |    |

| ESD Caution                                 |    |

| Pin Configuration and Function Descriptions |    |

| Typical Performance Characteristics         |    |

| Theory of Operation                         |    |

| Mechanical Device Operation                 |    |

| Operating Modes                             |    |

| Standby Mode                                |    |

| Measurement Mode                            |    |

| Selectable Measurement Ranges               |    |

| Digital Output                              |    |

| Temperature Sensor                          |    |

| Axes of Acceleration Sensitivity            |    |

| Power Sequencing                            |    |

| Power Supply Description                    |    |

|                                             |    |

| Overrange Protection<br>Self Test           |    |

|                                             |    |

| Filter                                      |    |

| Noise                                       |    |

| Power Savings Features                      |    |

| Operating Modes                             |    |

| Motion Detection.                           |    |

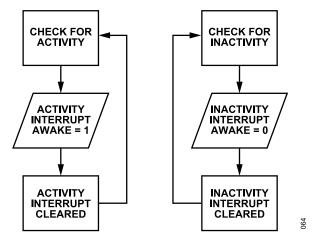

| Activity Detection                          |    |

| Inactivity Detection                        |    |

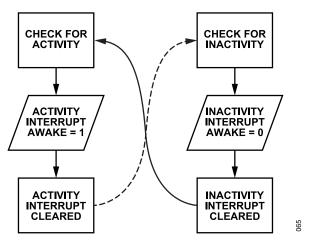

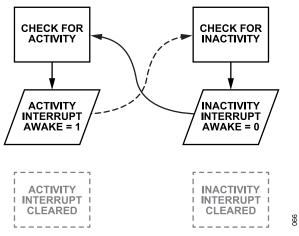

| Linking Activity and Inactivity Detection   |    |

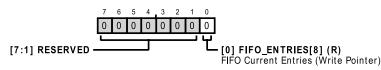

| FIFO                                        |    |

| System-Level Power Savings                  |    |

| Data Recording and Event Context            |    |

| FIFO Configuration                          |    |

| FIFO Modes                                  |    |

| FIFO Interrupts                             |    |

| FIFO Watermark                              |    |

| FIFO Ready                                  |    |

| FIFO Overrun                                |    |

| FIFO Full                                   |    |

| Communications                              |    |

| SPI Instructions                            |    |

| I <sup>2</sup> C Interface                  |    |

| I <sup>2</sup> S/TDM Interface              |    |

| PDM Interface                               | 38 |

| Additional Features40                       |

|---------------------------------------------|

| Free Fall Detection40                       |

| Tap Detection40                             |

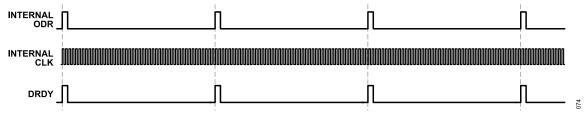

| External Clock41                            |

| External Trigger41                          |

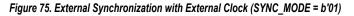

| External Synchronization41                  |

| Self Test45                                 |

| User Register Protection45                  |

| Concurrent Operating Modes45                |

| Interrupts45                                |

| Status Flags and Error Handling45           |

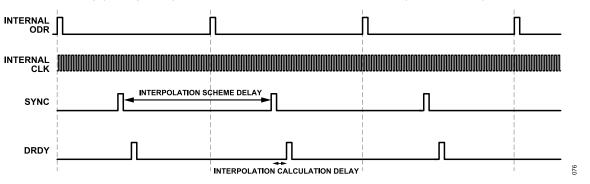

| Latency47                                   |

| Low Latency Mode47                          |

| Serial Communications49                     |

| SPI Bus Sharing49                           |

| Register Map50                              |

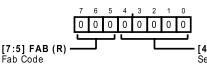

| Analog Devices Device ID Register 52        |

| Analog Devices MEMS Device ID Register53    |

| Part ID Register53                          |

| Part ID and Revision ID Register53          |

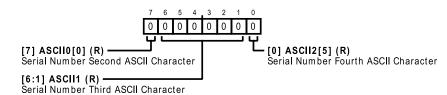

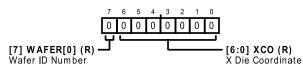

| Serial Number 0 Register53                  |

| Serial Number 1 Register54                  |

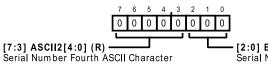

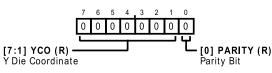

| Serial Number 2 Register54                  |

| Serial Number 3 Register54                  |

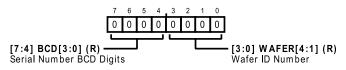

| Serial Number 4 Register55                  |

| Serial Number 5 Register55                  |

| Serial Number 6 Register55                  |

| Device Sensor Parameter Registers56         |

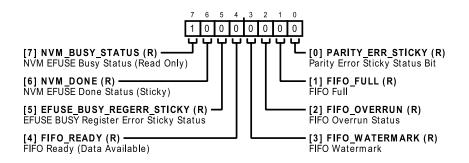

| Status 0 Register (Clear on Read)57         |

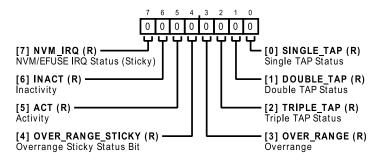

| Status 1 Register (Clear on Read)58         |

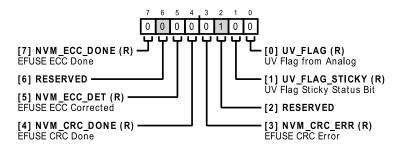

| Status 2 Register (Clear on Read)59         |

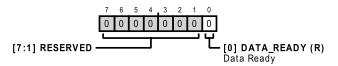

| Status 3 Register (Clear on Read)60         |

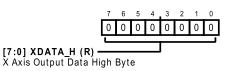

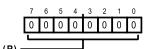

| X Axis Data Output Read (High Byte,         |

| Bits[15:8]) Register60                      |

| X Axis Data Output Read (Low Byte,          |

| Bits[7:0]) Register61                       |

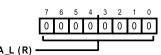

| Y Axis Data Output Read (High Byte,         |

| Bits[15:8]) Register61                      |

| Y Axis Data Output Read (Low Byte,          |

| Bits[7:0]) Register61                       |

| Z Axis Data Output Read (High Byte,         |

| Bits[15:8]) Register61                      |

| Z Axis Data Output Read (Low Byte,          |

| Bits[7:0]) Register62                       |

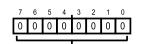

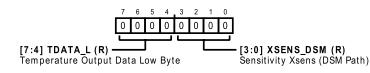

| Temperature Data Output Read (High Byte)    |

| Register                                    |

| Temperature Data Output Read (Low Byte)     |

| and Sensor DSM Register                     |

| FIFO Read Data (from FIFO Block) Register63 |

| FIFO Status Registers                               | 63 |

|-----------------------------------------------------|----|

| Miscellaneous 0 (Read Only) Register                | 63 |

| Miscellaneous 1 (Read Only) Register                | 64 |

| Sensor DSM Register                                 | 64 |

| Clock Control Register                              | 65 |

| OP MODE Register                                    | 65 |

| Digital Enable Register                             |    |

| Data Ready and I <sup>2</sup> C Communication Port  |    |

| Configuration Register                              | 67 |

| NVM (EFUSE) User Control Register                   | 68 |

| Register Reset                                      |    |

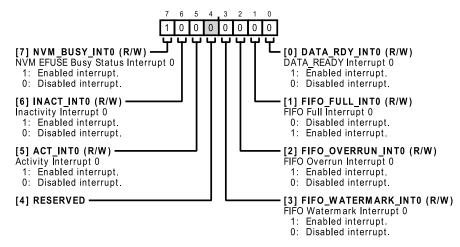

| Interrupt Pin 0 Enables MAP0 Register               | 69 |

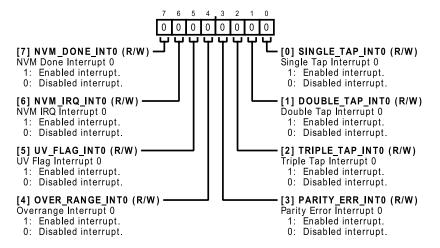

| Interrupt Pin 0 Enables MAP1 Register               | 70 |

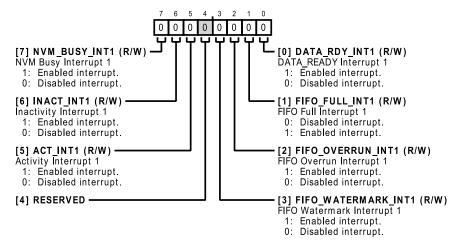

| Interrupt Pin 1 Enables MAP0 Register               | 71 |

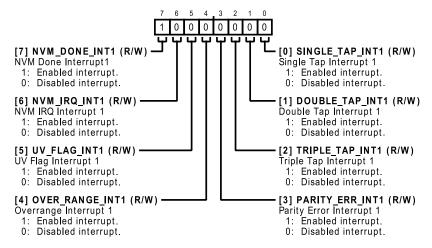

| Interrupt Pin 1 Enables MAP1 Register               | 72 |

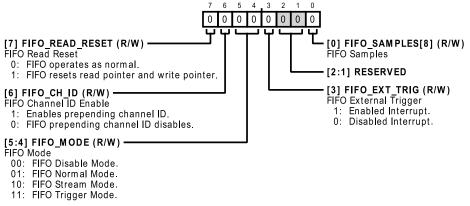

| FIFO Configuration 0 Register                       | 73 |

| FIFO Configuration 1 Register                       |    |

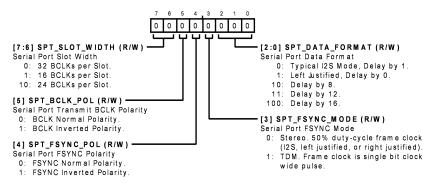

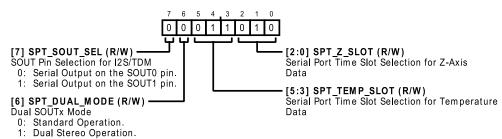

| Serial Port Configuration 0 Register                | 74 |

| Serial Port Configuration 1 Register                |    |

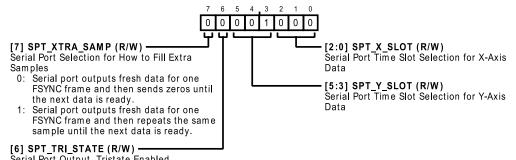

| Serial Port Configuration 2 Register                | 75 |

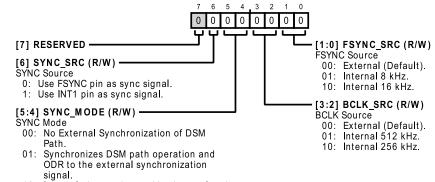

| SYNC and Serial Port Configuration Register         | 76 |

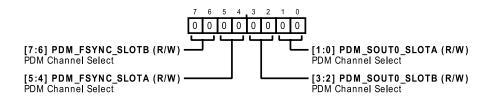

| PDM Configuration Register                          |    |

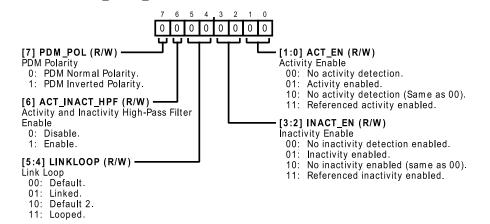

| Activity, Inactivity, and PDM Control Register      | 77 |

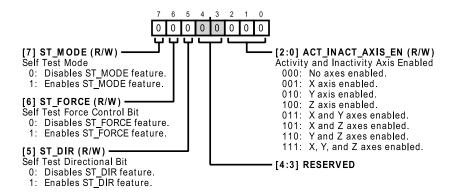

| Activity and Inactivity and Self-Test Control       |    |

| Register                                            |    |

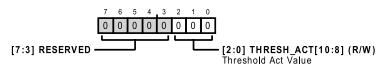

| Activity Threshold (High Byte) Register             |    |

| Activity Threshold (Low Byte) Register              | 79 |

| Timed Activity (High Byte, Bits[23:16])             |    |

| Register                                            |    |

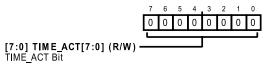

| Timed Activity (Mid Byte, Bits[15:7]) Register      |    |

| Timed Activity (Low Byte, Bits[7:0]) Register       |    |

| Inactivity Threshold (High Byte) Register           |    |

| Inactivity Threshold (Low Byte) Register            | 81 |

| Timed Inactivity (High Byte, Bits[23:16])           |    |

| Register<br>Timed Inactivity (Mid Byte, Bits[15:8]) | 81 |

| Timed Inactivity (Mid Byte, Bits[15:8])             |    |

| Register                                            | 82 |

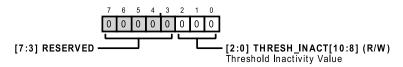

| Timed Inactivity (Low Byte, Bits[7:0])              |    |

| Register                                            | 82 |

## **REVISION HISTORY**

8/2024—Revision 0: Initial Version

| Tap Threshold Register82                     |  |

|----------------------------------------------|--|

| Tap Duration Register83                      |  |

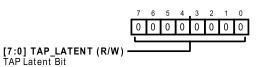

| Tap Latency Wait Time Register83             |  |

| Tap Window Register                          |  |

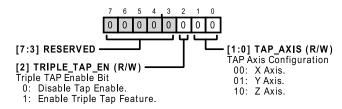

| Tap Configuration Register84                 |  |

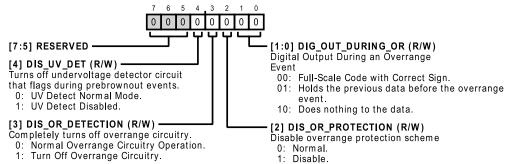

| Undervoltage and Overrange Configuration     |  |

| Register85                                   |  |

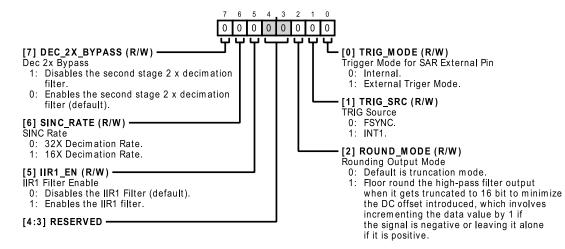

| SAR Trigger and Digital Filter Configuration |  |

| Register86                                   |  |

| X-Axis SAR User Offset Register87            |  |

| Y-Axis SAR User Offset Register              |  |

| Z-Axis SAR User Offset Register              |  |

| X-Axis DSM User Offset Register              |  |

| Y-Axis DSM User Offset Register88            |  |

| Z-Axis DSM User Offset Register88            |  |

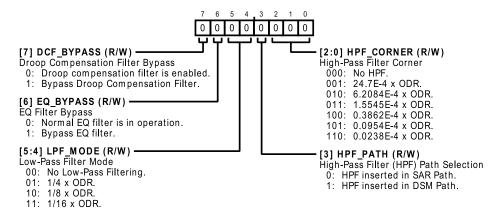

| Digital Filter Configuration Register        |  |

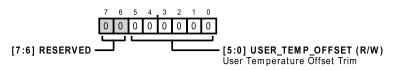

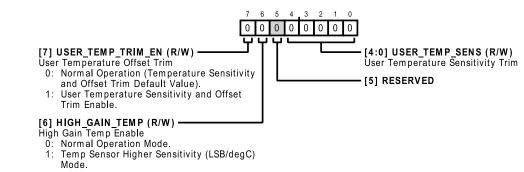

| User Temperature Sensor Control Registers 90 |  |

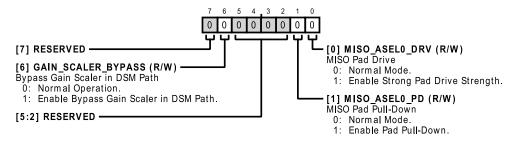

| MISO and Gain Scaler Configuration           |  |

| Register                                     |  |

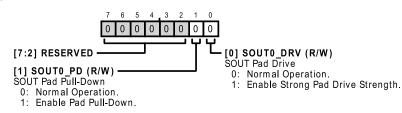

| S <sub>OUT0</sub> Pad Control Register       |  |

| Register91                                 |  |

|--------------------------------------------|--|

| S <sub>OUT0</sub> Pad Control Register91   |  |

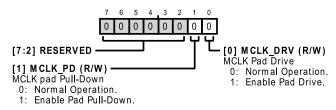

| MCLK Pad Register92                        |  |

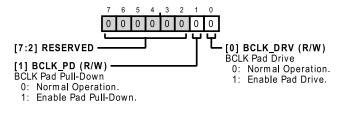

| BCLK Pad Register92                        |  |

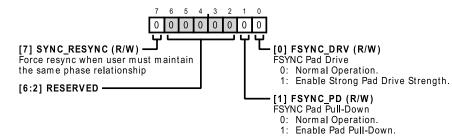

| FSYNC Pad and Resync Configuration         |  |

| Register93                                 |  |

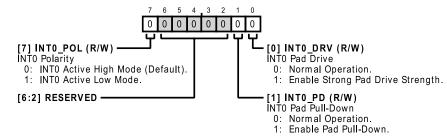

| INT0 Pad Control Register                  |  |

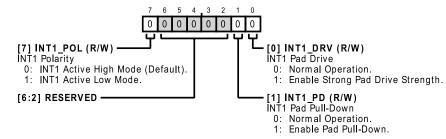

| INT1 Pad Control Register95                |  |

| Applications Information                   |  |

| Application Examples96                     |  |

| Device Configuration96                     |  |

| Power Supply Requirements100               |  |

| Interrupts101                              |  |

| Using an External Clock102                 |  |

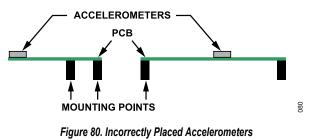

| Mechanical Considerations for Mounting 102 |  |

| PCB Footprint102                           |  |

| Outline Dimensions                         |  |

| Ordering Guide103                          |  |

| Models, Measurement Range, and             |  |

| Communications Interface103                |  |

| Evaluation Boards103                       |  |

$T_A = 25^{\circ}C$ , supply voltage (V<sub>S</sub>) = 3.3 V, x-axis and y-axis acceleration = 0 g, z-axis acceleration = 1 g, and full-scale range = ±4 g,, and high performance (HP) mode, unless otherwise noted.

#### Table 1. Specifications

| Parameter                                                                                        | Test Conditions/<br>Comments       | Min         | Тур      | Мах  | Unit            |

|--------------------------------------------------------------------------------------------------|------------------------------------|-------------|----------|------|-----------------|

| SENSOR INPUT                                                                                     | Each axis                          |             | <b>.</b> | -    |                 |

| Full-Scale Range (FSR)                                                                           | User selectable                    | ±4, ±8, ±16 |          |      | g               |

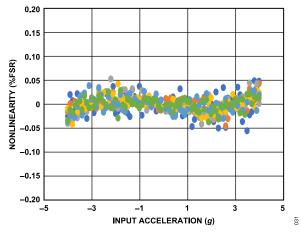

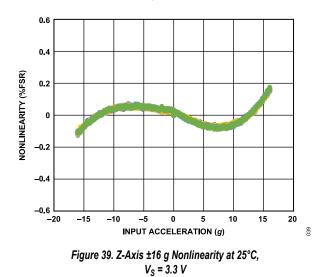

| Nonlinearity <sup>1, 2</sup>                                                                     | Percentage of full                 |             |          |      | 5               |

| -                                                                                                | scale range (FSR)                  |             |          |      |                 |

|                                                                                                  | ±4 g, ±8 g                         |             |          | ±0.1 | %FSR            |

|                                                                                                  | ±16 g                              |             |          | ±0.4 | %FSR            |

| Total Harmonic Distortion (THD)                                                                  | 3.57 g at 1 kHz                    |             | 0.1      |      | %FSR            |

| Cross-Axis Sensitivity <sup>3</sup>                                                              |                                    |             | ±2       | ±2.5 | %               |

| Sensor Resonant Frequency <sup>4</sup>                                                           | X-axis and Y-axis                  |             | 5.1      |      | kHz             |

|                                                                                                  | Z-axis                             |             | 3.8      |      | kHz             |

| Quality Factor <sup>4</sup>                                                                      | X-axis and Y-axis                  |             | 2.2      |      |                 |

|                                                                                                  | Z-axis                             |             | 1.2      |      |                 |

| SENSITIVITY                                                                                      | Each axis                          |             |          |      |                 |

| Sensitivity                                                                                      | ±4 g                               |             | 7500     |      | LSB/g           |

|                                                                                                  | ±8 g                               |             | 3750     |      | LSB/g           |

|                                                                                                  | ±16 g                              |             | 1875     |      | LSB/g           |

| Scale Factor                                                                                     | ±4 g                               |             | 133.3    |      | µg/LSB          |

|                                                                                                  | ±8 g                               |             | 266.7    |      | µg/LSB          |

|                                                                                                  | ±16 g                              |             | 533.3    |      | µg/LSB          |

| Sensitivity Error at 25°C                                                                        | X-axis and Y-axis                  |             | ±1.6     |      | %               |

|                                                                                                  | Z-axis                             |             | ±1.8     |      | %               |

| Sensitivity Change due to Temperature                                                            | T <sub>A</sub> = −40°C to +85°C    |             | ±0.02    |      | %/°C            |

| OUTPUT RESOLUTION                                                                                | Each axis                          |             |          |      |                 |

| All g Ranges                                                                                     | Σ-Δ modulator, DSM                 |             | 16       |      | Bits            |

|                                                                                                  | (high performance)                 |             |          |      |                 |

|                                                                                                  | SAR (low power) <sup>5</sup>       |             | 12       |      | Bits            |

| 0 g OFFSET                                                                                       | Each axis                          |             |          |      |                 |

| 0 <i>g</i> Output for X <sub>OUT</sub> , Y <sub>OUT</sub> , and Z <sub>OUT</sub> <sup>1, 6</sup> |                                    | -250        | ±60      | +250 | mg              |

| 0 g Offset vs. Temperature                                                                       | $T_A = -40^{\circ}C$ to +85°C      |             | 1.0      |      | mg/°C           |

| Bias Repeatability <sup>7</sup>                                                                  | X-axis and Y-axis                  |             | 100      |      | μg              |

|                                                                                                  | Z-axis                             |             | 120      |      | μg              |

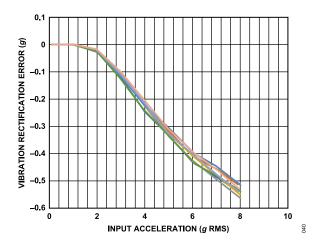

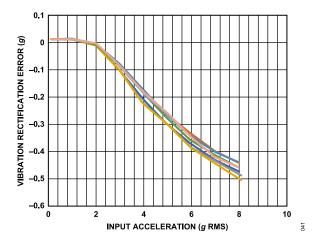

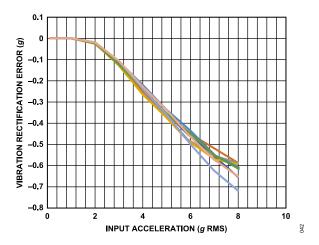

| Vibration Rectification Error (VRE)                                                              | Offset due to 2.5 g                |             | 28       |      | mg              |

|                                                                                                  | RMS vibration, in 1 <i>g</i> field |             |          |      |                 |

| NOISE PERFORMANCE                                                                                |                                    |             |          |      |                 |

| Noise Density                                                                                    |                                    |             |          |      |                 |

| High Performance (HP) Mode <sup>8</sup>                                                          | X-axis and Y-axis                  |             | 20       |      | µ <i>g</i> /√Hz |

|                                                                                                  | Z-axis                             |             | 20       |      | µg/√Hz          |

| Reduced Bandwidth (RBW) Mode                                                                     | X-axis and Y-axis                  |             | 23       |      | µg/√Hz          |

|                                                                                                  | Z-axis                             |             | 29       |      | µg/√Hz          |

| Low Power (LP) Mode                                                                              | X-axis and Y-axis                  |             | 39       |      | µg/√Hz          |

|                                                                                                  | Z-axis and T-axis                  |             | 49       |      | µg/√Hz          |

| Very Low Power (VLP) Mode                                                                        | X-axis and Y-axis                  |             | 49<br>94 |      | µg/√Hz          |

| vory Low Fower (VEF) Mode                                                                        | Z-axis and T-axis                  |             | 94<br>97 |      | µg/√Hz          |

|                                                                                                  | Z-axis                             |             | 9/       |      | µg/∿⊓∠          |

#### Table 1. Specifications (Continued)

| D                                                                   | Test Conditions/                                |      | <b>T</b>  |      | 1124                  |

|---------------------------------------------------------------------|-------------------------------------------------|------|-----------|------|-----------------------|

| Parameter                                                           | Comments                                        | Min  | Тур       | Мах  | Unit                  |

| Ultra-Low Power (ULP) Mode                                          | X-axis and Y-axis                               |      | 160       |      | µg/√Hz                |

|                                                                     | Z-axis                                          |      | 160       |      | µg/√Hz                |

| HS Mode                                                             | X-axis and Y-axis                               |      | 66        |      | µg/√Hz                |

|                                                                     | Z-axis                                          |      | 71        |      | µg/√Hz                |

| Output Noise <sup>9</sup>                                           |                                                 |      |           |      |                       |

| HP Mode                                                             | X-axis and Y-axis                               |      | 1.3       |      | mg RMS                |

|                                                                     | Z-axis                                          |      | 1.7       |      | mg RMS                |

| RBW Mode                                                            | X-axis and Y-axis                               |      | 1.0       |      | mg RMS                |

|                                                                     | Z-axis                                          |      | 1.3       |      | mg RMS                |

| LP Mode                                                             | X-axis and Y-axis                               |      | 1.2       |      | mg RMS                |

|                                                                     | Z-axis                                          |      | 1.5       |      | mg RMS                |

| VLP Mode                                                            | X-axis and Y-axis                               |      | 2.1       |      | mg RMS                |

|                                                                     | Z-axis                                          |      | 2.2       |      | mg RMS                |

| ULP Mode                                                            | X-axis and Y-axis                               |      | 1.2       |      | mg RMS                |

|                                                                     | Z-axis                                          |      | 1.2       |      | mg RMS                |

| Heart Sounds (HS) Mode                                              | X-axis and Y-axis                               |      | 1.5       |      | mg RMS                |

|                                                                     | Z-axis                                          |      | 1.6       |      | mg RMS                |

| Velocity Random Walk (VRW)                                          | X-axis and Y-axis                               |      | 10        |      | mg/twie<br>mm/sec/√hr |

|                                                                     | Z-axis                                          |      | 12        |      | mm/sec/√hr            |

| Bias Stability                                                      | All axes                                        |      | 6.5       |      |                       |

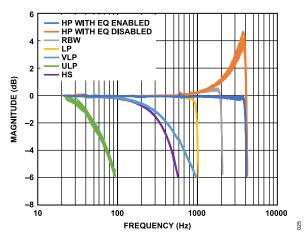

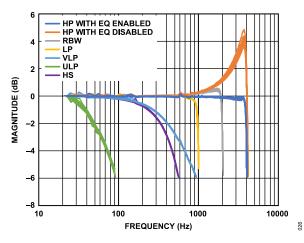

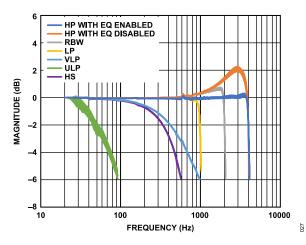

| BANDWIDTH                                                           | All configurable filters<br>set to default      |      | 0.0       |      | hâ                    |

| Bandwidth (−3 dB Corner)                                            |                                                 |      |           |      |                       |

| HP Mode                                                             |                                                 |      | 4000      |      | Hz                    |

| RBW Mode                                                            |                                                 |      | 2000      |      | Hz                    |

| LP Mode                                                             |                                                 |      | 1000      |      | Hz                    |

| VLP Mode                                                            |                                                 |      | 500       |      | Hz                    |

| ULP Mode                                                            |                                                 |      | 500<br>50 |      | Hz                    |

| HS Mode                                                             |                                                 |      | 400       |      | Hz                    |

| Relative Flatness                                                   |                                                 |      | 400       |      | 112                   |

| HP Mode                                                             |                                                 |      |           |      |                       |

|                                                                     | V avia and V avia                               |      | 0         |      |                       |

| Without Digital Correction (<2.5 kHz)                               | X-axis and Y-axis                               |      | 2         |      | dB                    |

|                                                                     | Z-axis                                          |      | 2         |      | dB                    |

| With Digital Correction (<3.8 kHz)                                  | X-axis and Y-axis                               |      | 0.5       |      | dB                    |

|                                                                     | Z-axis                                          |      | 0.5       |      | dB                    |

| RBW Mode                                                            |                                                 |      |           |      |                       |

| Without Digital Correction (<2 kHz)                                 | X-axis and Y-axis                               |      | 0.5       |      | dB                    |

|                                                                     | Z-axis                                          |      | 1         |      | dB                    |

| ELF TEST                                                            |                                                 |      |           |      |                       |

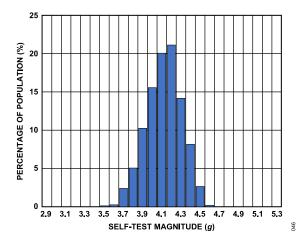

| Self-Test Delta (STΔ) <sup>10</sup>                                 | X-axis and Y-axis                               | 2.5  | 4.0       | 5.5  | g                     |

|                                                                     | Z-axis                                          | 2.0  | 3.0       | 3.8  | g                     |

| OWER SUPPLY                                                         |                                                 |      |           |      |                       |

| Operating Voltage Range (V <sub>S</sub> )                           |                                                 | 2.25 |           | 3.6  | V                     |

| Input and Output Voltage Range (V <sub>DDIO</sub> )                 | T <sub>A</sub> = −25°C to +85°C                 | 1.14 |           | 3.6  | V                     |

|                                                                     | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ | 1.62 |           | 3.6  | V                     |

| V <sub>1P8</sub> with Internal Low Dropout Regulator (LDO) Bypassed | V <sub>SUPPLY</sub> = 0 V                       | 1.62 | 1.8       | 1.98 | V                     |

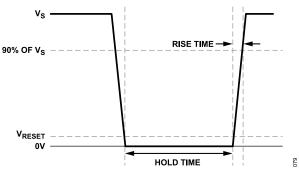

| Supply Reset Threshold (V <sub>RESET</sub> )                        |                                                 |      |           | 1.2  | V                     |

| Hold Time                                                           |                                                 | 1    |           |      | ms                    |

#### Table 1. Specifications (Continued)

| Parameter                           | Test Conditions/<br>Comments | Min     | Тур  | Max | Unit   |

|-------------------------------------|------------------------------|---------|------|-----|--------|

| Rise Time                           | 0 V to 90% of V <sub>S</sub> | NVIII I | קעי  | 4   | ms     |

| Supply Current <sup>11</sup>        | LDO enabled                  |         |      | 7   | 1115   |

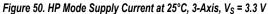

| HP Mode                             |                              |         | 340  |     |        |

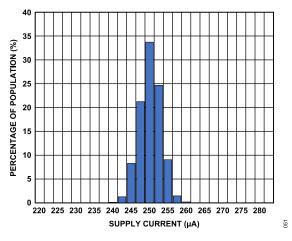

| RBW Mode                            |                              |         | 250  |     | μA     |

| LP Mode                             |                              |         |      |     | μA     |

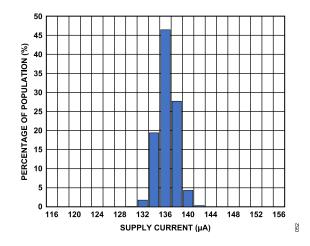

|                                     |                              |         | 140  |     | μA     |

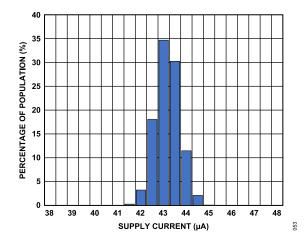

| VLP Mode                            |                              |         | 44   |     | μA     |

| ULP Mode                            |                              |         | 33   |     | μA     |

| HS Mode                             |                              |         | 32   |     | μA     |

| Standby                             |                              |         | 6.8  |     | μA     |

| Turn-On Time <sup>12</sup>          |                              |         |      |     |        |

| Standby to Valid Data Time          |                              |         |      | 2   | ms     |

| Power-Up to Standby                 |                              |         |      | 3   | ms     |

| CLOCK                               |                              |         |      |     |        |

| Internal Oscillator                 |                              |         | 512  |     | kHz    |

| DELAYS                              |                              |         |      |     |        |

| Group Delay                         |                              |         |      |     |        |

| Default Mode                        | X-axis and Y-axis            |         | 710  |     | μs     |

|                                     | Z-axis                       |         | 750  |     | μs     |

| Low Latency Mode <sup>13</sup>      | X-axis and Y-axis            |         | 95   |     | μs     |

|                                     | Z-axis                       |         | 110  |     | μs     |

| TEMPERATURE SENSOR <sup>1, 14</sup> |                              |         |      |     |        |

| Output at 25°C                      |                              |         | 550  |     | LSB    |

| Sensitivity                         |                              |         | 10.2 |     | LSB/°C |

| Sensitivity Error                   |                              |         | 0.06 |     | %      |

| ENVIRONMENTAL                       |                              |         |      |     |        |

| Operating Temperature Range         |                              | -40     |      | +85 | °C     |

<sup>1</sup> Typical value based on characterization, not tested in production.

<sup>2</sup> Nonlinearity is measured with a DC input stimulus.

<sup>3</sup> Cross-axis sensitivity is defined as coupling between any two axes. Typical value based on characterization, not tested in production.

<sup>4</sup> Typical value defined based on design and simulation. It is not tested in production.

- <sup>5</sup> Note that the lower 4 bits of the SAR are zeros, which is to match the 16-bit DSM.

- <sup>6</sup> Different supplies and measurement range settings can cause a shift in performance.

- <sup>7</sup> Repeatability provides an estimate for long-term drift in the bias, as observed during 500 hours of high-temperature operating life (HTOL) at 105°C and 1000 cycles of temperature cycle testing (TCT). Repeatability represents the root sum square (RSS) of the bias drift associated with HTOL and TCT.

- <sup>8</sup> Noise density values with equalization filter enabled.

- <sup>9</sup> RMS noise with default bandwidth setting used for each power mode.

- <sup>10</sup> Self-test change is defined as the positive self-test output (when the positive beam deflection is asserted) minus the negative self-test output (when the negative beam deflection is asserted). Different supplies and *g* ranges cause different self-test changes.

- <sup>11</sup> Supply current is measured with default configurations with XYZ channels enabled. Supply current may increase when additional features (temperature sensor, first in, first out (FIFO), or external analog-to-digital converter (ADC) for example) are enabled.

- <sup>12</sup> Refer to the Power Supply Requirements section for the minimum supply rise time requirement.

- <sup>13</sup> Low latency mode bypasses optional filters. See the Latency section for more information including configuration settings.

- <sup>14</sup> Nominal values for temperature sensor output with HIGH\_GAIN\_TEMP = 0.

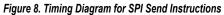

# TIMING SPECIFICATIONS

#### Table 2. I<sup>2</sup>C Input and Output Levels and Timing (T<sub>A</sub> = 25°C, V<sub>S</sub> = 3.3 V, and V<sub>DDIO</sub> = 3.3 V) <sup>1</sup>

|                                         |                    | Test Conditions/                                     |                               | I2C_HSM_EN = 0<br>(Fast Mode) |                         | HSM_EN = 1<br>Speed Mode) |      |

|-----------------------------------------|--------------------|------------------------------------------------------|-------------------------------|-------------------------------|-------------------------|---------------------------|------|

| Parameter                               | Symbol             | Comments                                             | Min                           | Мах                           | Min                     | Max                       | Unit |

| DC INPUT LEVELS                         |                    |                                                      |                               |                               |                         |                           |      |

| Input Voltage                           |                    |                                                      |                               |                               |                         |                           |      |

| Low Level                               | VIL                |                                                      |                               | $0.3 \times V_{DDIO}$         |                         | $0.3 \times V_{DDIO}$     | V    |

| High Level                              | VIH                |                                                      | 0.7 × V <sub>DDIO</sub>       |                               | 0.7 × V <sub>DDIO</sub> |                           | V    |

| Hysteresis of Schmitt Trigger<br>Inputs | V <sub>HYS</sub>   |                                                      | 0.05 × V <sub>DDIO</sub>      |                               | $0.1 \times V_{DDIO}$   |                           | V    |

| Input Current                           | I <sub>IL</sub>    | $0.1 \times V_{DDIO} < V_{IN} < 0.9 \times V_{DDIO}$ | -10                           | +10                           |                         |                           | μA   |

| DC OUTPUT LEVELS                        |                    |                                                      |                               |                               |                         |                           |      |

| Output Voltage                          | V <sub>OL</sub>    | Low level current<br>(I <sub>OL</sub> ) = 7 mA       |                               |                               |                         |                           |      |

| Low Level                               | V <sub>OL1</sub>   | V <sub>DDIO</sub> > 2 V                              |                               | 0.4                           |                         |                           | V    |

|                                         | V <sub>OL2</sub>   | V <sub>DDIO</sub> ≤ 2 V                              |                               | $0.2 \times V_{DDIO}$         |                         |                           | V    |

| Output Current                          | VIH                |                                                      | 0.7 × V <sub>DDIO</sub>       |                               | 0.7 × V <sub>DDIO</sub> |                           | V    |

| Low Level                               | I <sub>OL</sub>    | V <sub>OL</sub> = 0.4 V                              | 20                            |                               |                         |                           | mA   |

|                                         |                    | V <sub>OL</sub> = 0.6 V                              | 6                             |                               |                         |                           | mA   |

| AC INPUT LEVELS                         |                    |                                                      |                               |                               |                         |                           |      |

| SCL Frequency                           |                    |                                                      | 0.01                          | 1                             | 0.01                    | 3.4                       | MHz  |

| SCL High Time                           | t <sub>HIGH</sub>  |                                                      | 260                           |                               | 60                      |                           | ns   |

| SCL Low Time                            | t <sub>LOW</sub>   |                                                      | 500                           |                               | 160                     |                           | ns   |

| Start Setup Time                        | t <sub>SUSTA</sub> |                                                      | 260                           |                               | 160                     |                           | ns   |

| Start Hold Time                         | t <sub>HDSTA</sub> |                                                      | 260                           |                               | 160                     |                           | ns   |

| SDA Setup Time                          | t <sub>SUDAT</sub> |                                                      | 50                            |                               | 10                      |                           | ns   |

| SDA Hold Time                           | t <sub>HDDAT</sub> |                                                      | 0                             |                               | 0                       |                           | ns   |

| Stop Setup Time                         | t <sub>SUSTO</sub> |                                                      | 360                           |                               | 160                     |                           | ns   |

| Bus Free Time                           | t <sub>BUF</sub>   |                                                      | 500                           |                               |                         |                           | ns   |

| SCL Input Rise Time                     | t <sub>RCL</sub>   |                                                      |                               | 120                           |                         | 80                        | ns   |

| SCL Input Fall Time                     | t <sub>FCL</sub>   |                                                      |                               | 120                           |                         | 80                        | ns   |

| SDA Input Rise Time                     | t <sub>RDA</sub>   |                                                      |                               | 120                           |                         | 160                       | ns   |

| SDA Input Fall Time                     | t <sub>FDA</sub>   |                                                      |                               | 120                           |                         | 160                       | ns   |

| Width of Spike to Suppress              | t <sub>SP</sub>    | Not shown in Figure                                  |                               | 50                            |                         | 10                        | ns   |

| AC OUTPUT LEVELS                        |                    |                                                      |                               |                               |                         |                           |      |

| Propagation Delay                       |                    | Load capacitance<br>(C <sub>LOAD</sub> ) = 500 pF    |                               |                               |                         |                           |      |

| Data                                    | t <sub>VDDAT</sub> |                                                      | 97                            | 450                           | 27                      | 135                       | ns   |

| Acknowledge                             | t <sub>VDACK</sub> |                                                      |                               | 450                           |                         |                           | ns   |

| Output Fall Time                        | t <sub>F</sub>     | Not shown in Figure                                  | 20 × (V <sub>DDIO</sub> /5.5) | 120                           |                         |                           | ns   |

<sup>1</sup> Timing may be different with I2C\_SDA\_SLOW enabled.

#### Table 3. SPI Digital Input and Output ( $T_A = 25^{\circ}C$ , $V_S = 3.3 V$ , and $V_{DDIO} = 3.3 V$ )

|                           |                 |                                                      |                         | Limit <sup>1</sup>      |      |

|---------------------------|-----------------|------------------------------------------------------|-------------------------|-------------------------|------|

| Parameter                 | Symbol          | Test Conditions/Comments                             | Min                     | Max                     | Unit |

| DIGITAL INPUT             |                 |                                                      |                         |                         |      |

| Low Level Input Voltage   | VIL             |                                                      |                         | 0.3 × V <sub>DDIO</sub> | V    |

| High Level Input Voltage  | V <sub>IH</sub> |                                                      | 0.7 × V <sub>DDIO</sub> |                         | V    |

| Low Level Input Current   | IL.             | Input voltage (V <sub>IN</sub> ) = V <sub>DDIO</sub> |                         | -0.1                    | μA   |

| High Level Input Current  | I <sub>IH</sub> | V <sub>IN</sub> = 0 V                                | 0.1                     |                         | μA   |

| DIGITAL OUTPUT            |                 |                                                      |                         |                         |      |

| Low Level Output Voltage  | V <sub>OL</sub> | $I_{OL} = I_{OL, MIN}$                               |                         | 0.2 × V <sub>DDIO</sub> | V    |

| High Level Output Voltage | V <sub>OH</sub> | $I_{OH} = I_{OH, MAX}$                               | 0.8 × V <sub>DDIO</sub> |                         | V    |

| Low Level Output Current  | I <sub>OL</sub> | V <sub>OL</sub> = V <sub>OL, MAX</sub>               | 1                       |                         | mA   |

| High Level Output Current | I <sub>OH</sub> | V <sub>OH</sub> = V <sub>OH, MIN</sub>               |                         | -2                      | mA   |

<sup>1</sup> Limits based on characterization results, not production tested.

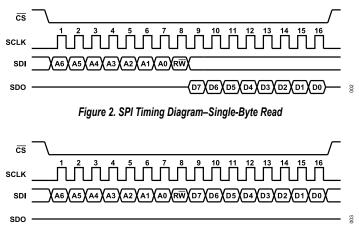

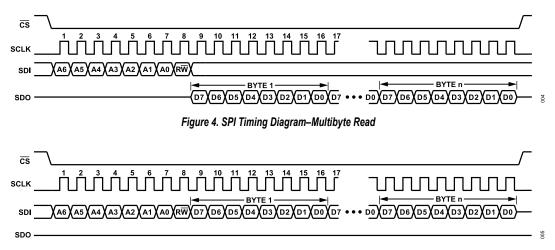

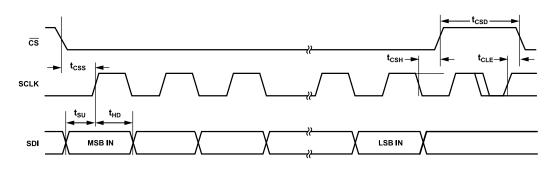

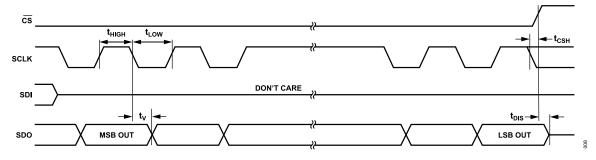

#### Table 4. SPI Timing ( $T_A = 25^{\circ}$ C, $V_S = 3.3$ V, and $V_{DDIO} = 3.3$ V)

|                   | Li   | mit <sup>1, 2, 3</sup> | _    |                                                            |

|-------------------|------|------------------------|------|------------------------------------------------------------|

| Parameter         | Min  | Max                    | Unit | Description                                                |

| f <sub>CLK</sub>  | 0.1  | 8                      | MHz  | Clock frequency                                            |

| t <sub>CSS</sub>  | 100  |                        | ns   | CS setup time                                              |

| t <sub>CSH</sub>  | 0.02 | 1000                   | μs   | CS hold time                                               |

| t <sub>CSD</sub>  | 20   |                        | ns   | CS disable time                                            |

| t <sub>SU</sub>   | 20   |                        | ns   | Data setup time                                            |

| t <sub>HD</sub>   | 20   |                        | ns   | Data hold time                                             |

| t <sub>HIGH</sub> | 50   |                        | ns   | Clock high time                                            |

| t <sub>LOW</sub>  | 50   |                        | ns   | Clock low time                                             |

| t <sub>CLE</sub>  | 25   |                        | ns   | Clock enable time                                          |

| t <sub>V</sub>    | 0    | 50                     | ns   | Output valid from clock low (not shown in timing diagrams) |

| t <sub>DIS</sub>  | 0    | 25                     | ns   | Output disable time (not shown in timing diagrams)         |

<sup>1</sup> Limits based on design targets; not production tested.

$^2$  The timing values are measured corresponding to the input thresholds (V<sub>IL</sub> and V<sub>IH</sub>) given in Table 3.

<sup>3</sup> Maximum loading should not exceed 12 pF.

Figure 3. SPI Timing Diagram-Single-Byte Write

Figure 5. SPI Timing Diagram–Multibyte Write

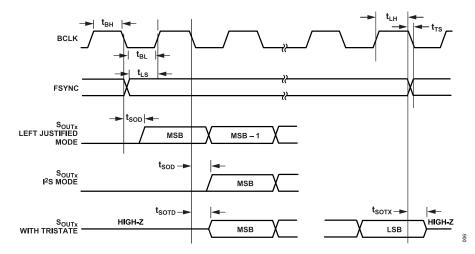

| Table 5. I <sup>2</sup> S, TDM, and PDM Timing ( $T_A$ = 25°C, $V_S$ = 3.3 V, and $V_{DDIO}$ = 3 | 3.3 V) |

|--------------------------------------------------------------------------------------------------|--------|

|--------------------------------------------------------------------------------------------------|--------|

| Parameter            | Min   | Max    | Unit | Description                                                                                                             |

|----------------------|-------|--------|------|-------------------------------------------------------------------------------------------------------------------------|

| SERIAL PORT          |       |        |      |                                                                                                                         |

| t <sub>BL</sub>      | 18    |        | ns   | BCLK low pulse width (controller and subordinate modes)                                                                 |

| t <sub>BH</sub>      | 18    |        | ns   | BCLK high pulse width (controller and subordinate modes)                                                                |

| f <sub>BCLK</sub>    | 0.512 | 12.288 | MHz  | BCLK frequency                                                                                                          |

| t <sub>LS</sub>      | 3     |        | ns   | FSYNC setup, time to BCLK rising (subordinate mode)                                                                     |

| t <sub>LH</sub>      | 5     |        | ns   | FSYNC hold, time from BCLK rising (subordinate mode)                                                                    |

| f <sub>SYNC</sub>    | 2     | 48     | kHz  | FSYNC frequency                                                                                                         |

| t <sub>TS</sub>      |       | 6      | ns   | BCLK falling to FSYNC timing skew (controller mode)                                                                     |

| tsod                 | 0     | 30     | ns   | $S_{\text{OUTx}}$ delay, time from BCLK falling (controller and subordinate modes), $V_{\text{DDIO}}$ at 1.62 V minimum |

|                      | 0     | 80     | ns   | $S_{OUTx}$ delay, time from BCLK falling (controller and subordinate modes), $V_{\text{DDIO}}$ at 1.14 V minimum        |

| t <sub>SOTD</sub>    | 0     | 15     | ns   | BCLK falling to S <sub>OUTx</sub> driven in tristate mode                                                               |

| t <sub>SOTX</sub>    | 0     | 15     | ns   | BCLK falling to S <sub>OUTx</sub> tristated in tristate mode                                                            |

| PDM OUTPUT           |       |        |      |                                                                                                                         |

| f <sub>PDM_CLK</sub> | 0.512 | 12.288 | MHz  | PDM clock frequency                                                                                                     |

| t <sub>HOLD</sub>    | 35    | 46     | ns   | PDM data hold time                                                                                                      |

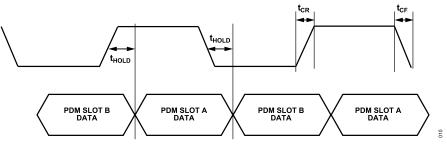

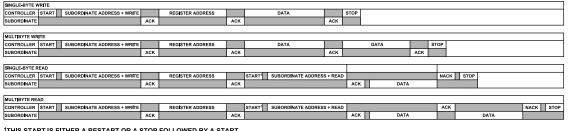

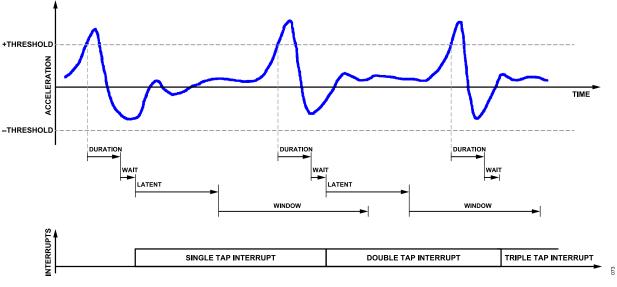

# DIGITAL TIMING DIAGRAMS

SDO

Figure 6. I<sup>2</sup>S/TDM Serial Output Port Timing Diagram

Figure 7. SPI Port Timing Diagram

Figure 9. I<sup>2</sup>C Port Timing Diagram

200

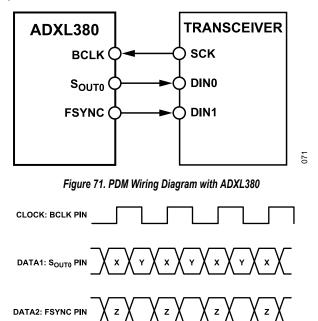

Figure 10. PDM Output Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 6. Absolute Maximum Ratings

| Parameter                                                                                                                                                | Rating                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Mechanical Shock (Any Axis, 0.2 ms)                                                                                                                      | 10,000 <i>g</i>                     |

| Vs                                                                                                                                                       | -0.3 V to +4.0 V                    |

| V <sub>DDIO</sub>                                                                                                                                        | -0.3 V to +4.0 V                    |

| V <sub>1P8</sub> Configured as Input                                                                                                                     | -0.3 V to +2.0 V                    |

| Digital Inputs (FSYNC, SCLK/SCL, SDI/SDA, SDO/ASEL0, $\overline{\text{CS}}/\text{ASEL1}$ , $S_{\text{OUT0}}$ , $S_{\text{OUT1}}/\text{MCLK}$ , and BCLK) | -0.3 V to V <sub>DDIO</sub> + 0.3 V |

| Temperature Range (Storage)                                                                                                                              | -55°C to +150°C                     |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

Thermal resistance values specified in Table 7 are simulated based on JEDEC specs (unless specified otherwise) and should be used in compliance with JESD51-12.

$\theta_{JA}$  is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure,  $\theta_{JC}$  is the junction-to-case thermal resistance,  $\Psi_{JT}$  is the junction-to-top of the package thermal resistance, and  $\Psi_{JB}$  is the junction-to-bottom of the package thermal resistance.

#### Table 7. Package Characteristics

| Package Type | $\theta_{JA}$ | θ <sub>JC</sub> | Ψ <sub>JT</sub> | Ψ <sub>JB</sub> | Unit |

|--------------|---------------|-----------------|-----------------|-----------------|------|

| CC-14-3      | 71.3          | 46.0            | 2.9             | 47.0            | °C/W |

#### **RECOMMENDED SOLDERING PROFILE**

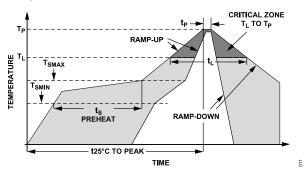

Figure 11 and Table 8 provide details about the recommended soldering profile.

Figure 11. Recommended Soldering Profile

Table 8. Recommended Soldering Profile

|                                                                 | Condition         |                   |  |  |  |

|-----------------------------------------------------------------|-------------------|-------------------|--|--|--|

| Profile Feature                                                 | Sn63/Pb37         | Pb-Free           |  |  |  |

| Average Ramp Rate $(T_L \text{ to } T_P)$                       | 3°C/sec maximum   | 3°C/sec maximum   |  |  |  |

| Preheat                                                         |                   |                   |  |  |  |

| Minimum Temperature (T <sub>SMIN</sub> )                        | 100°C             | 150°C             |  |  |  |

| Maximum Temperature (T <sub>SMAX</sub> )                        | 150°C             | 200°C             |  |  |  |

| Time (T <sub>SMIN</sub> to T <sub>SMAX</sub> )(t <sub>S</sub> ) | 60 sec to 120 sec | 60 sec to 180 sec |  |  |  |

| T <sub>SMAX</sub> to T <sub>L</sub> Ramp-Up Rate                | 3°C/sec maximum   | 3°C/sec maximum   |  |  |  |

| Time Maintained Above                                           |                   |                   |  |  |  |

| Liquidous (T <sub>L</sub> )                                     |                   |                   |  |  |  |

| Liquidous Temperature (T <sub>L</sub> )                         | 183°C             | 217°C             |  |  |  |

| Time (t <sub>L</sub> )                                          | 60 sec to 150 sec | 60 sec to 150 sec |  |  |  |

| Peak Temperature (T <sub>P</sub> )                              | 240 + 0/-5°C      | 260 + 0/-5°C      |  |  |  |

| Time Within 5°C of Actual Peak                                  | 10 sec to 30 sec  | 20 sec to 40 sec  |  |  |  |

| Temperature (t <sub>P</sub> )                                   |                   |                   |  |  |  |

| Ramp-Down Rate                                                  | 6°C/sec maximum   | 6°C/sec maximum   |  |  |  |

| Time 25°C to Peak Temperature                                   | 6 minutes maximum | 8 minutes max     |  |  |  |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

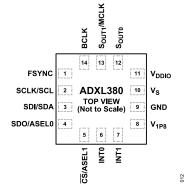

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

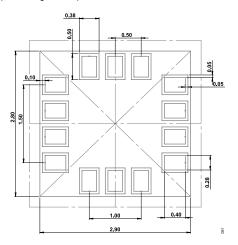

Figure 12. Pin Configuration (Top View)

#### Table 9. Pin Function Descriptions

|         |                          | Description                                                                      |                                                                            |                                                                                  |                                                                                  |  |  |  |

|---------|--------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

| Pin No. | Mnemonic                 | SPI                                                                              | I <sup>2</sup> S/TDM                                                       | l <sup>2</sup> C                                                                 | PDM                                                                              |  |  |  |

| 1       | FSYNC                    | Interrupt Input in FIFO Trigger<br>Mode (Optional)                               | Frame Sync (FSYNC)                                                         | Interrupt Input in FIFO Trigger<br>Mode (Optional)                               | SOUT1                                                                            |  |  |  |

| 2       | SCLK/SCL                 | SPI, Clock (SCLK)                                                                | Not Applicable                                                             | I <sup>2</sup> C, Serial Clock (SCL)                                             | Not Applicable                                                                   |  |  |  |

| 3       | SDI/SDA                  | SPI, Serial Data Input (SDI)                                                     | Not Applicable                                                             | I <sup>2</sup> C, Serial Data (SDA)                                              | Not Applicable                                                                   |  |  |  |

| 1       | SDO/ASEL0                | SPI, Serial Data Output (SDO)                                                    | Not Applicable                                                             | I <sup>2</sup> C, Address Select 0 (ASEL0)                                       | Not Applicable                                                                   |  |  |  |

| 5       | CS/ASEL1                 | SPI, Chip Select                                                                 | Not Applicable                                                             | I <sup>2</sup> C, Address Select 1 (ASEL1)                                       | Not Applicable                                                                   |  |  |  |

| 6       | INT0                     | Interrupt 0                                                                      | Interrupt 0                                                                | Interrupt 0                                                                      | Interrupt 0                                                                      |  |  |  |

| ,       | INT1                     | Interrupt 1                                                                      | Interrupt 1                                                                | Interrupt 1                                                                      | Interrupt 1                                                                      |  |  |  |

| }       | V <sub>1P8</sub>         | Internally Regulated Voltage<br>(External 1.8 V When V <sub>S</sub><br>Grounded) | Internally Regulated Voltage (External 1.8 V When V <sub>S</sub> Grounded) | Internally Regulated Voltage<br>(External 1.8 V When V <sub>S</sub><br>Grounded) | Internally Regulated Voltage<br>(External 1.8 V When V <sub>S</sub><br>Grounded) |  |  |  |

| )       | GND                      | Ground                                                                           | Ground                                                                     | Ground                                                                           | Ground                                                                           |  |  |  |

| 0       | Vs                       | Supply Voltage                                                                   | Supply Voltage                                                             | Supply Voltage                                                                   | Supply Voltage                                                                   |  |  |  |

| 1       | V <sub>DDIO</sub>        | Input and Output Supply                                                          | Input and Output Supply                                                    | Input and Output Supply                                                          | Input and Output Supply                                                          |  |  |  |

| 2       | S <sub>OUT0</sub>        | Not Applicable                                                                   | Data Channel 0 (S <sub>OUT0</sub> )                                        | Not Applicable                                                                   | Data Channel 0 (S <sub>OUT0</sub> )                                              |  |  |  |

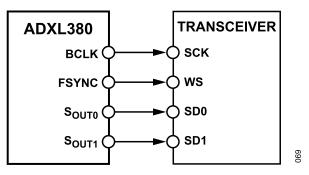

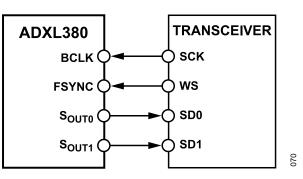

| 3       | S <sub>OUT1</sub> / MCLK | Not Applicable                                                                   | MCLK or Data Channel 1 (S <sub>OUT1</sub> )                                | Not Applicable                                                                   | Not Applicable                                                                   |  |  |  |

| 14      | BCLK                     | Not Applicable                                                                   | Bit Clock (BCLK)                                                           | Not Applicable                                                                   | Bit Clock (BCLK)                                                                 |  |  |  |

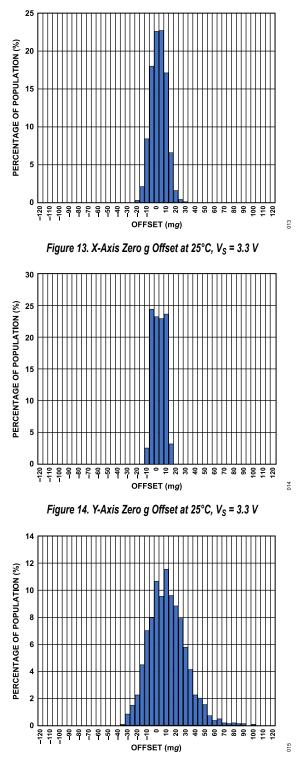

$T_A = 25^{\circ}$ C,  $V_S = 3.3$  V, x-axis and y-axis acceleration = 0 g, z-axis acceleration = 1 g, full-scale range = ±4 g, and default settings for other registers, unless otherwise noted.

Figure 15. Z-Axis Zero g Offset at 25°C,  $V_{\rm S}$  = 3.3 V

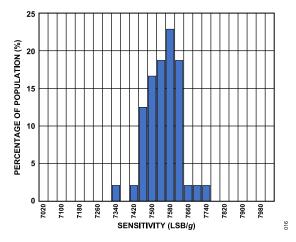

Figure 16. X-Axis Sensitivity at 25°C,  $V_S$  = 3.3 V, ±4 g Range

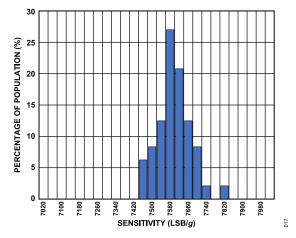

Figure 17. Y-Axis Sensitivity at 25°C, V<sub>S</sub> = 3.3 V, ±4g Range

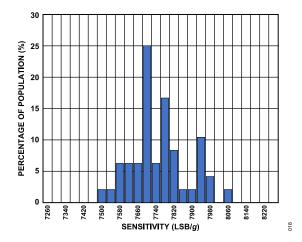

Figure 18. Z-Axis Sensitivity at 25°C, V<sub>S</sub> = 3.3 V, ±4 g Range

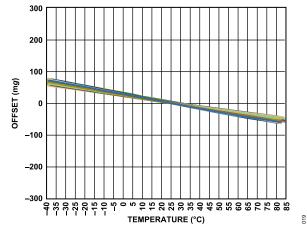

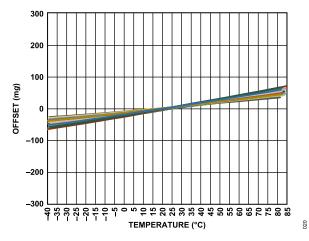

Figure 19. X-Axis Offset vs. Temperature at 25°C, V<sub>S</sub> = 3.3 V

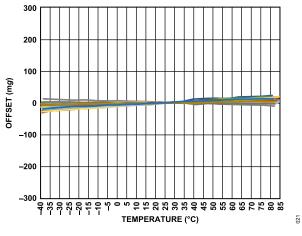

Figure 20. Y-Axis Offset vs. Temperature at 25°C, V<sub>S</sub> = 3.3 V

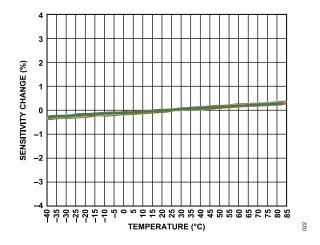

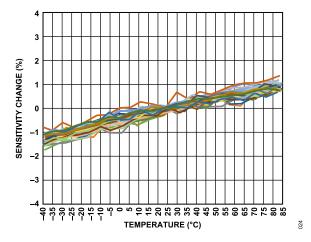

Figure 22. X-Axis Sensitivity Change vs. Temperature at 25°C, V<sub>S</sub> = 3.3 V

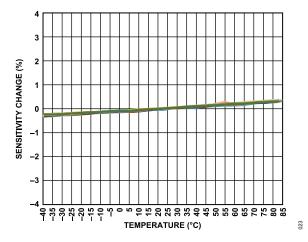

Figure 23. Y-Axis Sensitivity Change vs. Temperature at 25°C, V<sub>S</sub> = 3.3 V

Figure 24. Z-Axis Sensitivity Change vs. Temperature at 25°C, V<sub>S</sub> = 3.3 V

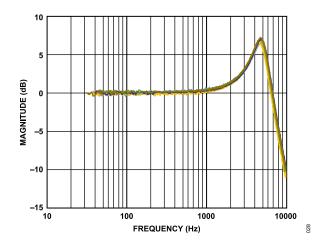

Figure 25. X-Axis Frequency Response at 25°C, V<sub>S</sub> = 3.3 V

Figure 26. Y-Axis Frequency Response at 25°C, V<sub>S</sub> = 3.3 V

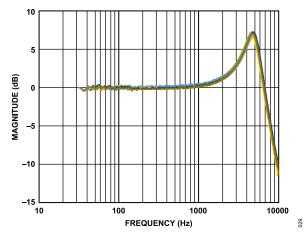

Figure 27. Z-Axis Frequency Response at 25°C, V<sub>S</sub> = 3.3 V

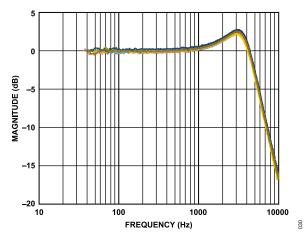

Figure 28. X-Axis PDM Frequency Response at 25°C, V<sub>S</sub> = 3.3 V

Figure 29. Y-Axis PDM Frequency Response at 25°C, V<sub>S</sub> = 3.3 V

Figure 30. Z-Axis PDM Frequency Response at 25°C, V<sub>S</sub> = 3.3 V

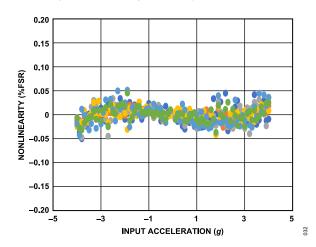

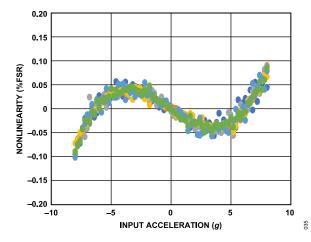

Figure 31. X-axis ±4 g Nonlinearity at 25°C, V<sub>S</sub> = 3.3 V

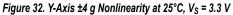

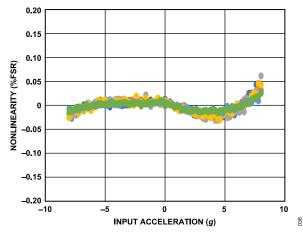

Figure 34. X-Axis ±8 g Nonlinearity at 25°C, V<sub>S</sub> = 3.3 V

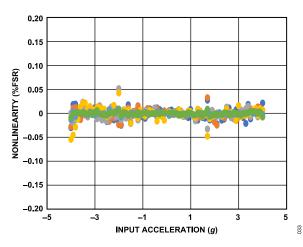

Figure 35. Y-Axis ±8 g Nonlinearity at 25°C, V<sub>S</sub> = 3.3 V

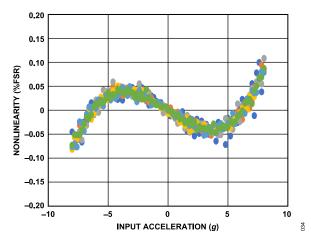

Figure 36. Z-Axis ±8 g Nonlinearity at 25°C, V<sub>S</sub> = 3.3 V

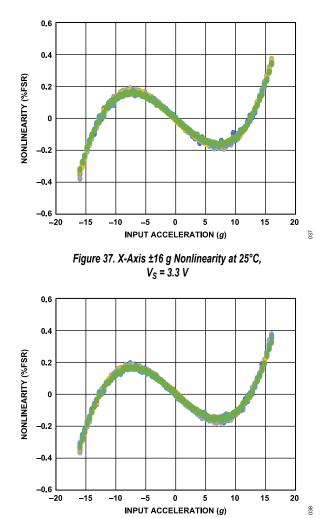

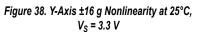

Figure 40. X-Axis Vibration Rectification Error, X-Axis in +1 g Field, ±4 g Range,  $V_{\rm S}$  = 3.3 V

Figure 41. Y-Axis Vibration Rectification Error, Y-Axis in +1 g Field, ±4 g Range,  $V_S$  = 3.3 V

Figure 42. Z-Axis Vibration Rectification Error, Z-Axis in +1 g Field, ±4 g Range,  $V_S$  = 3.3 V

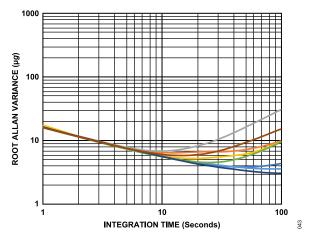

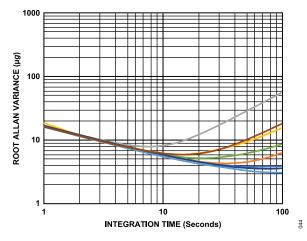

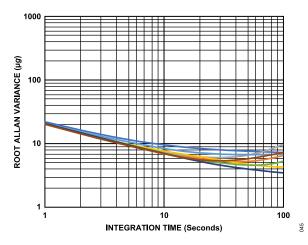

Figure 43. X-Axis Root Allan Variance at 25°C, V<sub>S</sub> = 3.3 V

Figure 44. Y-Axis Root Allan Variance at 25°C, V<sub>S</sub> = 3.3 V

Figure 45. Z-Axis Root Allan Variance at 25°C, V<sub>S</sub> = 3.3 V

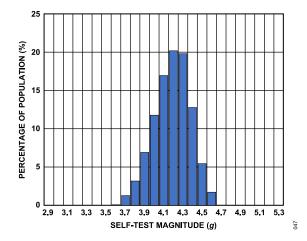

Figure 46. X-Axis Self-Test Magnitude at 25°C, V<sub>S</sub> = 3.3 V

Figure 47. Y-Axis Self-Test Magnitude at 25°C, V<sub>S</sub> = 3.3 V

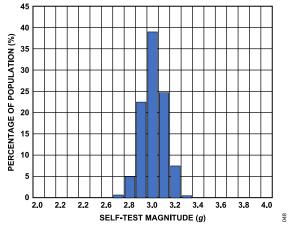

Figure 48. Z-Axis Self-Test Magnitude at 25°C, V<sub>S</sub> = 3.3 V

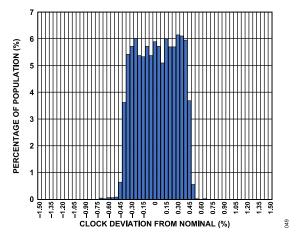

Figure 49. Clock Deviation from Nominal at 25°C, V<sub>S</sub> = 3.3 V

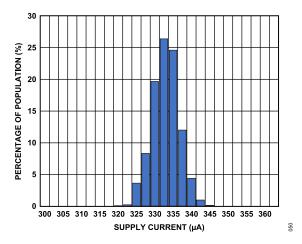

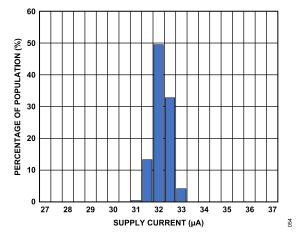

Figure 51. RBW Mode Supply Current at 25°C, 3-Axis, V<sub>S</sub> = 3.3 V

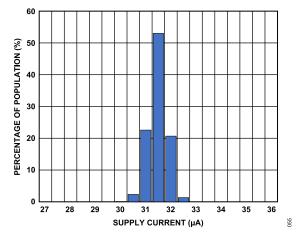

Figure 52. LP Mode Supply Current at 25°C, 3-Axis, V<sub>S</sub> = 3.3 V

Figure 53. VLP Mode Supply Current at 25°C, 3-Axis, V<sub>S</sub> = 3.3 V

Figure 54. ULP Mode Supply Current at 25°C, 3-Axis, V<sub>S</sub> = 3.3 V

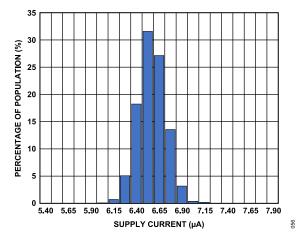

Figure 55. HS Mode Supply Current at 25°C, 1-Axis, V<sub>S</sub> = 3.3 V

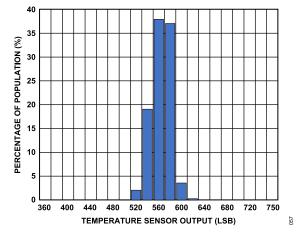

Figure 57. Temperature Sensor Output at 25°C, HIGH\_GAIN\_TEMP = 0,  $V_{\rm S}$  = 3.3 V

The ADXL380 is a complete 3-axis acceleration measurement system. The device measures both dynamic accelerations resulting from motion, shock, and vibration as well as static acceleration such as tilt. Acceleration is reported digitally from the device using SPI or I<sup>2</sup>C protocols and/or I<sup>2</sup>S/TDM/PDM. Built-in digital logic enables autonomous operation and implements functionality that enhances system level power savings.

The micromachined, sensing elements are fully differential, comprising the lateral x-axis and y-axis sensor and the vertical, teeter totter z-axis sensors. The x-axis and y-axis sensors and the z-axis sensors go through separate signal paths that minimize offset drift and noise.

The ADXL380 include anti-aliasing filters before the high resolution  $\Sigma$ - $\Delta$  ADC and a decimation filter after. The following two signal paths are supported:

- ► High performance using the 16-bit DSM

- ▶ Low power using the 12-bit SAR

These signal paths can be used independently or concurrently (see the Concurrent Operating Modes section for more information). User-selectable ODR and filter corners are provided.

#### MECHANICAL DEVICE OPERATION

The moving component of the sensor is a polysilicon surface-micromachined structure that is built on top of a silicon wafer. Polysilicon springs suspend the structure over the surface of the wafer and provide a resistance against acceleration forces.

Deflection of the structure is measured using differential capacitors that consist of independent fixed plates and plates attached to the moving mass. Acceleration deflects the structure and unbalances the differential capacitor, resulting in a sensor output whose amplitude is proportional to acceleration. Phase sensitive demodulation determines the magnitude and polarity of the acceleration.

## **OPERATING MODES**

The ADXL380 has seven primary operating modes with more modes available when operating concurrently (see the Concurrent Operating Modes section for more information).

#### Table 10. Operating Modes

| Mode                   | Signal Path                                |  |  |  |  |

|------------------------|--------------------------------------------|--|--|--|--|

| Standby                | Not applicable                             |  |  |  |  |

| High Performance (HP)  | 16-bit DSM (high performance signal chain) |  |  |  |  |

| Reduce Bandwidth (RBW) | 16-bit DSM (high performance signal chain) |  |  |  |  |

| Low Power (LP)         | 16-bit DSM (high performance signal chain) |  |  |  |  |

| Very Low Power (VLP)   | 12-bit SAR (low power signal chain)        |  |  |  |  |

| Ultra-Low Power (ULP)  | 12-bit SAR (low power signal chain)        |  |  |  |  |

| Heart Sounds (HS)      | 12-bit SAR (low power signal chain)        |  |  |  |  |

#### STANDBY MODE

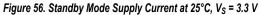

Placing the ADXL380 in standby suspends measurement and reduces current consumption to 6.8  $\mu$ A (typical). Standby mode is used for power conservation and device configuration. FIFO data is preserved and no new interrupts are generated (see Interrupts section for more details).

The ADXL380 powers up in standby with all sensor functions turned off. Note that any changes to the device configuration must be made with the device in standby. If changes are made while the ADXL380 is in measurement mode, these changes may be effective for only part of a measurement. Ensure that a change of the data capture configuration only occurs in standby mode.

#### **MEASUREMENT MODE**

Measurement mode refers to any of the operating modes that use the DSM or SAR signal path (every mode except standby mode in Table 10). When operating in measurement mode, the user can choose between several power consumption modes or operate in concurrent mode (one DSM mode and one SAR mode operating concurrently).

Note that after entering measurement mode, a 2 ms wait time must be observed before reading acceleration data to allow the output time to settle after entering measurement mode.

#### SELECTABLE MEASUREMENT RANGES

The ADXL380 has selectable measurement ranges of  $\pm 4 \text{ g}$ ,  $\pm 8 \text{ g}$ , and  $\pm 16 \text{ g}$ . Acceleration samples are always converted by an ADC; therefore, sensitivity scales with g range. Ranges and corresponding sensitivity values are listed in Table 1. When the input exceeds the full-scale range, the output data may not be accurate temporarily. The sensor is not damaged as long as the acceleration remains less than the absolute maximum rating. Table 6 lists the absolute maximum ratings for acceleration, indicating the acceleration level that can cause permanent damage to the ADXL380.

#### **DIGITAL OUTPUT**

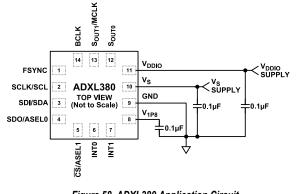

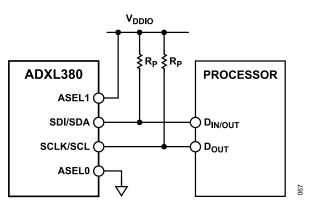

Figure 58 shows the ADXL380 application circuit. The communications interface is either SPI or I<sup>2</sup>C for the configuration, and the serial data interface is either SPI/I<sup>2</sup>C, I<sup>2</sup>S, or PDM (see the Serial Communications section for additional information).

The ADXL380 includes an internal configurable digital band-pass filter. Both the high-pass and low-pass poles of the filter are adjustable, as detailed in the Filter section. The ADXL380 powers up in standby mode. A particular mode can be chosen by setting the OP\_MODE register (Register 0x26).

Figure 58 shows a 0.1  $\mu$ F capacitor on the V<sub>S</sub>, V<sub>DDIO</sub>, and V<sub>1P8</sub> pins. If the power supply is noisy, additional filtering may be required. An additional 1  $\mu$ F capacitor can be added to the V<sub>S</sub> and V<sub>DDIO</sub> supplies in parallel with the 0.1  $\mu$ F capacitors.

58

#### **TEMPERATURE SENSOR**

The ADXL380 includes an integrated 12-bit temperature sensor, which the system designer can use to monitor the internal system temperature or to improve the temperature stability of the device via calibration.

The temperature sensor built in the ADXL380 is trimmed at room temperature before shipping; therefore, it can even be used to monitor the absolute temperature. To get even better accuracy, users can measure and calibrate the initial bias of the ADXL380 at some known temperature in mass production.

To use the temperature sensor for calibration of the acceleration signal, it is sufficient to correlate acceleration to temperature sensor output, rather than to absolute temperature. In this case, it is not necessary to convert the temperature reading to an absolute temperature; therefore, calibration of the initial bias is not required.

The designer can configure the device to save data from the temperature sensor in the FIFO. Temperature samples, whether read from the output registers or from the FIFO, update concurrently with acceleration (and ADC) samples, unless these samples are turned off. When the temperature channel is enabled, the ODR is always 100 Hz. If the ODR is faster than this on the other channels (x-axis, y-axis, or z-axis channels), temperature data is repeated until a new temperature sample is available.

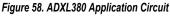

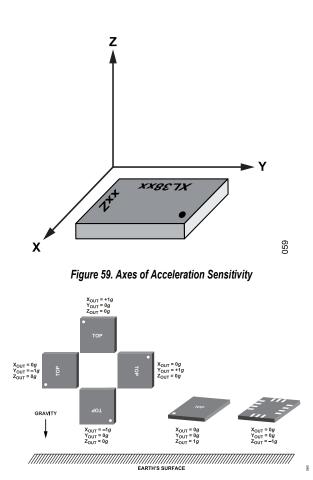

## AXES OF ACCELERATION SENSITIVITY

Figure 59 shows the axes of acceleration sensitivity. Note that the digital output increases when accelerated along the sensitive axis.

## POWER SEQUENCING

The ADXL380 uses internal LDO regulators to generate the 1.8 V power for the internal analog and digital supplies. This 1.8 V regulated voltage is sent to the V<sub>1P8</sub> pin as an output. When using the LDO regulator, connect V<sub>S</sub> to a voltage source between 2.25 V and 3.6 V.

To disable the internal LDO regulators, tie V<sub>S</sub> to ground before using an external 1.8 V supply to power V<sub>1P8</sub>. Refer to the Power Supply Requirements section for more information.

If necessary  $V_{1P8}$  and  $V_{DDIO}$  can be powered from the same external 1.8 V supply so that both are powered at the same time. In this case, proper decoupling and low frequency isolation are important to maintain the noise performance of the sensor.

$V_{\text{S}},\,V_{\text{DDIO}},\,\text{and}\,\,V_{1\text{P8}}\,(\text{if enabled as inputs})\,\text{can be powered up in any sequence.}$

#### POWER SUPPLY DESCRIPTION

The ADXL380 have three different power supply domains:  $V_S,\,V_{1P8},\,$  and  $V_{DDIO}.$  The internal analog and digital circuitry operates at 1.8 V nominal.

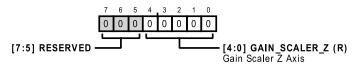

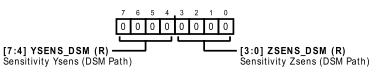

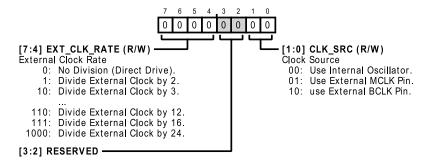

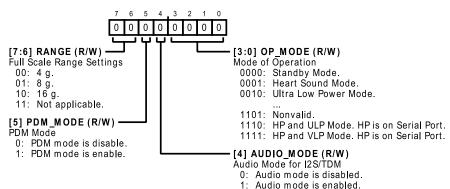

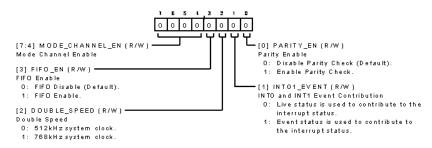

# Vs