# Buffered, 8-Channel Simultaneous Sampling, 16-Bit 1 MSPS DAS

#### **FEATURES**

- Complete 16-bit data acquisition system

- ► Simultaneous sampling of 8 internally buffered channels

- ▶ 1 MSPS per channel throughput

- ▶ Differential, wide common-mode range inputs

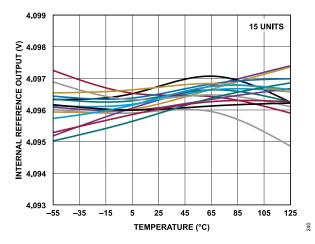

- ▶ ±75 pA typical input leakage at 25°C

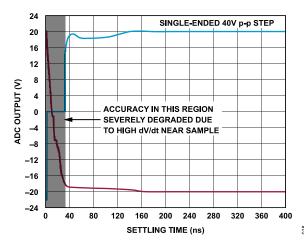

- ▶ Full-scale input step settling time < 300 ns

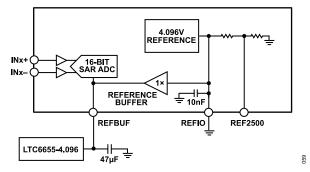

- Integrated reference and reference buffer (4.096 V)

- Integrated supply decoupling capacitors

- ▶ 45 mW per channel at 1 MSPS, power scales with throughput

- Minimal external signal conditioning

- Seamless high dynamic range

- Per sample, per channel automatic gain ranging

- Maintains ppm-level INL

- > Per channel SoftSpan input ranges, bipolar or unipolar

- ▶ ±40 V, ±25 V, ±20 V, ±12.5 V, ±10 V, ±6.25 V, ±5 V, ±2.5 V

- ▶ 0 V to 40 V, 25 V, 20 V, 12.5 V, 10 V, 6.25 V, 5 V, 2.5 V

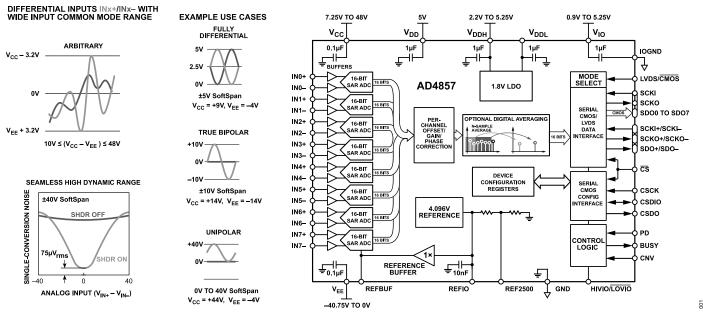

#### FUNCTIONAL BLOCK DIAGRAM

- Rail-to-rail input overdrive tolerance

- ▶ High performance

- INL: ±160 µV typical (±40 V range)

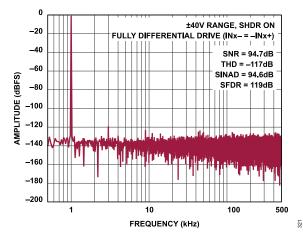

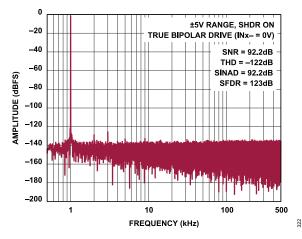

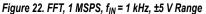

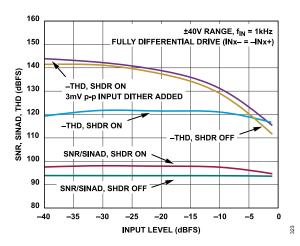

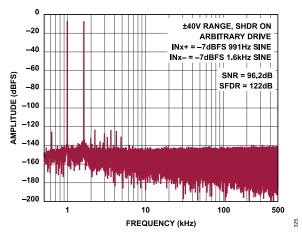

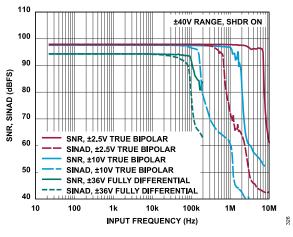

- SNR: 94.6 dB single-conversion typical (±40 V range)

- ▶ DR: 98.1 dB single-conversion typical (±40 V range)

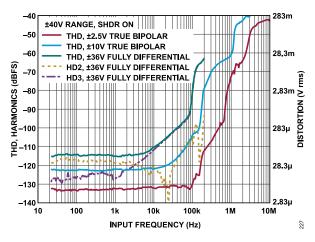

- ► THD: -117 dB typical (±40 V range)

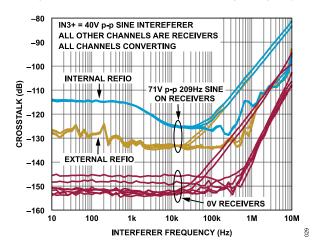

- CMRR: 120 dB typical

- Digital flexibility

- ▶ SPI CMOS (0.9 V to 5.25 V) and LVDS serial input and output

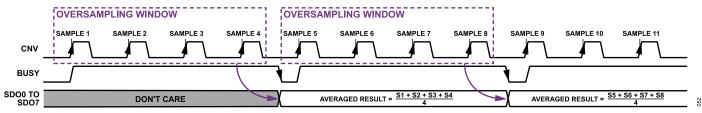

- Optional oversampling with 16-bit digital averaging

- Optional offset, gain, and phase correction

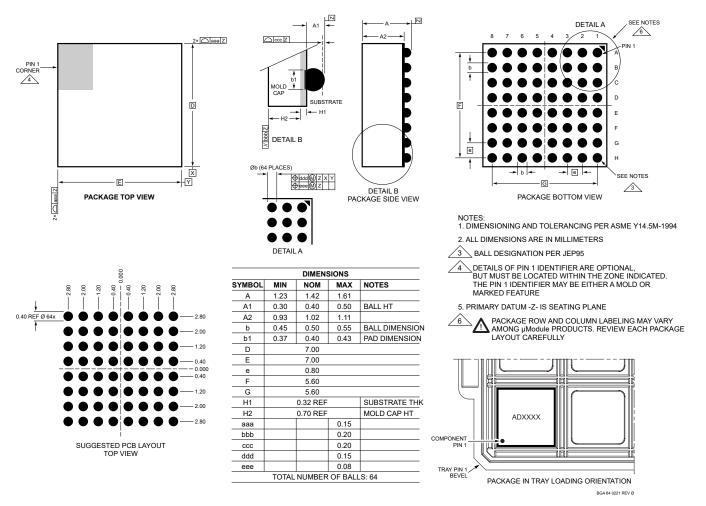

- ▶ 7.00 mm × 7.00 mm, 64-ball BGA full solution footprint

#### **APPLICATIONS**

- Automatic test equipment

- Avionics and aerospace

- Instrumentation and control systems

- Semiconductor manufacturing

- Test and measurement

Figure 1. Functional Block Diagram (Example Analog-Input Signal Use Cases Shown)

DOCUMENT FEEDBACK

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features                                    | 1    |

|---------------------------------------------|------|

| Applications                                | 1    |

| Functional Block Diagram                    | 1    |

| General Description                         |      |

| Companion Products                          | 3    |

| Specifications                              | 4    |

| Timing Specifications                       |      |

| Absolute Maximum Ratings                    | .18  |

| Junction Temperature                        | .18  |

| Thermal Resistance                          | . 18 |

| Electrostatic Discharge (ESD) Ratings       | 18   |

| ESD Caution                                 |      |

| Pin Configuration and Function Descriptions | . 19 |

| Typical Performance Characteristics         | . 22 |

| Terminology                                 | . 29 |

| Theory of Operation                         | .30  |

| Overview                                    |      |

| Converter Operation                         | .30  |

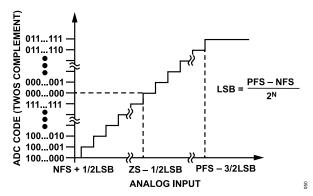

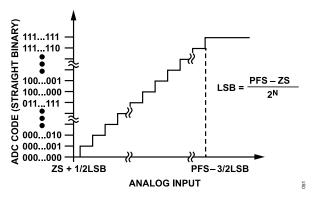

| Transfer Function                           | . 30 |

| SoftSpan                                    |      |

| Seamless High Dynamic Range                 | 31   |

| Digital Processing Features                 |      |

| Applications Information                    | . 36 |

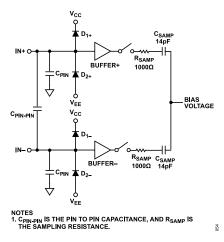

| Buffered Analog Inputs                      |      |

| Analog Input Drive Circuits                 |      |

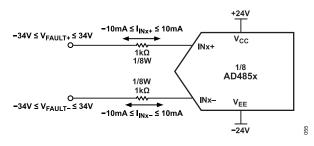

| Analog Input Overdrive Tolerance            |      |

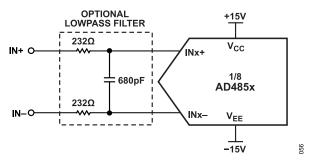

| Analog Input Filtering                      |      |

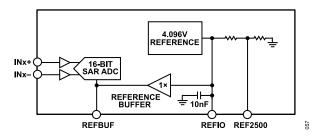

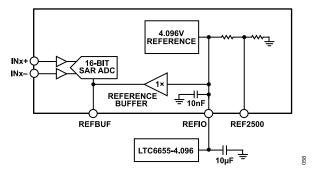

| DAS Reference                               |      |

| Power Considerations                        |      |

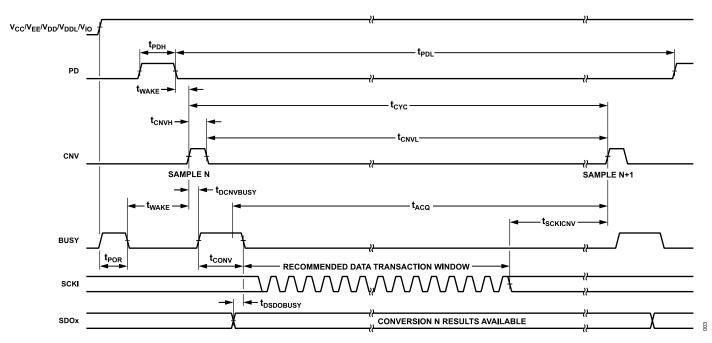

| Timing and Control                          |      |

| Digital Interface                           |      |

| CMOS Conversion Data Output Mode            |      |

| LVDS Conversion Data Output Mode            |      |

| Packet Format                               |      |

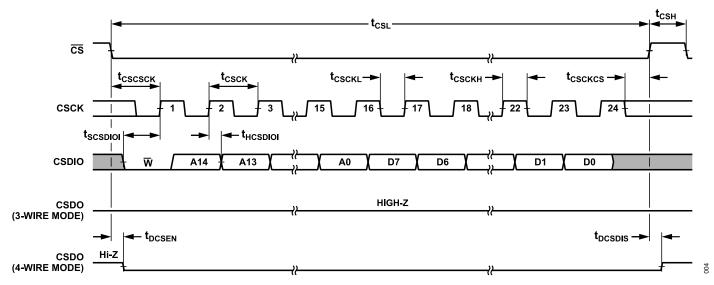

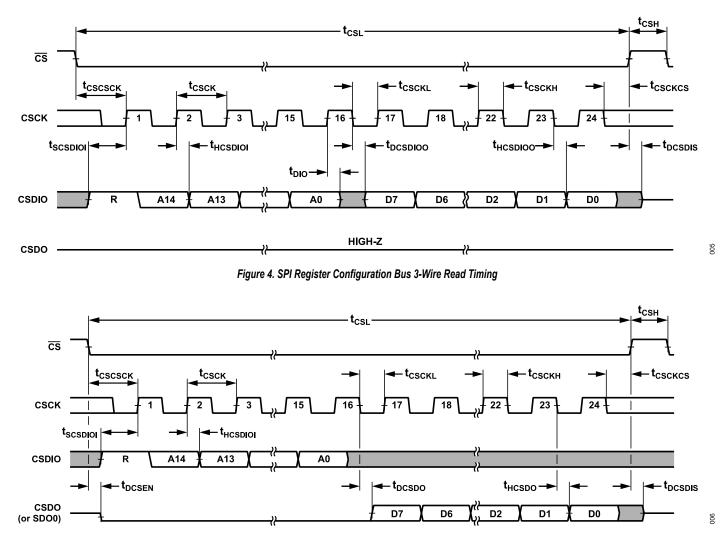

| SPI Register Configuration Bus              |      |

| Register Summary                            | .50  |

# **REVISION HISTORY**

6/2024—Revision 0: Initial Version

| Register Details<br>SPI Configuration A Register<br>SPI Configuration B Register<br>Device Configuration Register<br>Device Type Register<br>Product ID Low Register | . 54<br>. 55<br>55<br>. 55<br>. 56 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Product ID High Register<br>Device Grade Register<br>Scratch Pad Register<br>SPI Revision Register                                                                   | . 56<br>. 56                       |

| Vendor ID Low Register<br>Vendor ID High Register<br>Loop Configuration A Register                                                                                   | . 57<br>57                         |

| Loop Configuration B Register<br>SPI Configuration C Register<br>SPI Status Register                                                                                 | . 58<br>. 59                       |

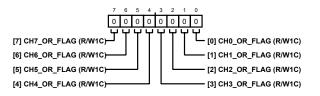

| SPI Configuration D Register<br>Device Status Register<br>Channel Overrange Status Register                                                                          | .60<br>.60                         |

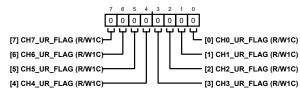

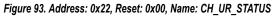

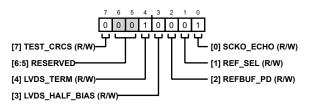

| Channel Underrange Status Register<br>Register Map CRC<br>Device Control Register                                                                                    | . 62<br>. 62                       |

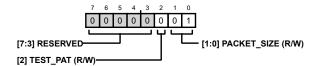

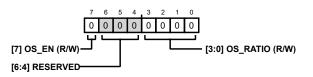

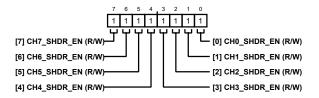

| Packet Format Register<br>Oversample Control Register<br>Seamless High Dynamic Range Register                                                                        | .63                                |

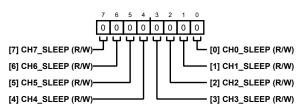

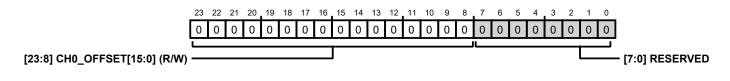

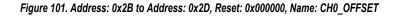

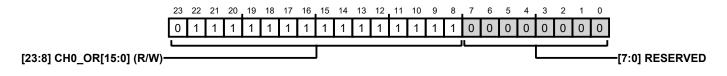

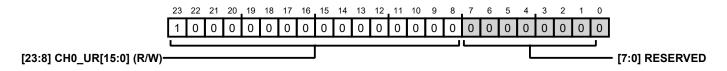

| Channel Sleep Register<br>Channel 0 SoftSpan Register<br>Channel 0 Offset Register<br>Channel 0 Gain Register                                                        | . 64<br>.65<br>.65<br>.66          |

| Channel 0 Phase Register<br>Channel 0 Overrange Limit Register<br>Channel 0 Underrange Limit Register<br>Channel 0 Test Pattern Register                             | .66<br>.67                         |

| Outline Dimensions<br>Ordering Guide<br>Evaluation Board                                                                                                             | . 68<br>.68                        |

# **GENERAL DESCRIPTION**

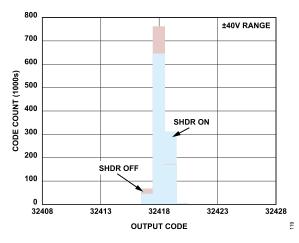

The AD4857 is a fully buffered, 8-channel simultaneous sampling, 16-bit, 1 MSPS data acquisition system (DAS) with differential, wide common-mode range inputs. Its functional architecture is shown in Figure 1. Operating from a 5 V low voltage supply, flexible input buffer supplies, and using the precision low drift internal reference and reference buffer, the AD4857 allows the SoftSpan range of each channel to be independently configured to match the native application signal swing, minimizing additional external signal conditioning. To further maximize single-conversion dynamic range, the AD4857 incorporates seamless high dynamic range (SHDR) technology. When enabled, the input signal path gain of the channel is automatically optimized on a sample-by-sample basis, minimizing converter noise on each sample without impacting linearity.

The 11 MHz bandwidth, picoamp input analog buffers, wide input common-mode range, and 120 dB common-mode rejection ratio (CMRR) of the AD4857 allow the DAS to directly digitize input signals with arbitrary swings on INx+ and INx-. Its input signal flexibility, combined with  $\pm$ 160 µV integral nonlinearity (INL), no missing codes at 16 bits, 94.6 dB signal to noise ratio (SNR), and 98.1 dB dynamic range, make the AD4857 an ideal choice for applications requiring high accuracy, throughput, and precision in a compact solution footprint. Enabling 16-bit oversampling offers further SNR and dynamic range improvements. Optional per channel offset, gain, and phase adjustment provide the ability to calibrate and remove system-level errors upstream to the DAS.

The AD4857 features a serial peripheral interface (SPI) register configuration bus (0.9 V to 5.25 V) and supports both low voltage differential signaling buses (LVDS) and complementary metal-oxide semiconductor (CMOS) conversion data output buses, selectable using the LVDS/CMOS pin. Between one and eight lines of data output can be employed in CMOS mode, allowing the user to optimize bus width and throughput.

The 7.00 mm × 7.00 mm, 64-ball, ball grid array (BGA) of the

AD4857 includes all critical power supply and reference bypass capacitors, minimizing full solution footprint and component count and reducing sensitivity to application printed circuit board (PCB) layout. The device operates over an extended industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

Note that throughout this data sheet, multifunction pins such as LVDS/CMOS are referred to either by the entire pin name or by a single function of the pin. For example, LVDS when only that function is relevant.

#### **COMPANION PRODUCTS**

- ► Voltage references: LTC6655-4.096 or ADR4540

- ▶ Power solutions: LT1761, LT8330, and/or LT3042

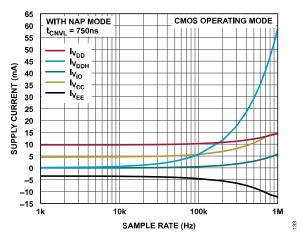

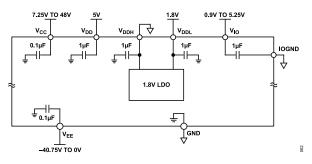

$V_{EE} = -40.75$  V to 0 V,  $V_{CC} = 7.25$  V to 48 V,  $(V_{CC} - V_{EE}) = 10$  V to 48 V,  $V_{DD} = 5$  V,  $V_{DDH} = 2.5$  V, 1.8 V low drop out (LDO) regulator enabled, and  $V_{IO} = 0.9$  V to 5.25 V. All channels convert at a sampling frequency ( $f_S$ ) = 1 MSPS, internal reference and reference buffer enabled, all SoftSpan ranges, fully-differential input signal drive in SoftSpan 15 and SoftSpan 13, true bipolar or unipolar signal drive in other bipolar or unipolar SoftSpan ranges, and all specifications T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C.

| Parameter                                              | Test Conditions/Comments                                       | Min                        | Тур    | Max                        | Uni  |

|--------------------------------------------------------|----------------------------------------------------------------|----------------------------|--------|----------------------------|------|

| RESOLUTION                                             |                                                                | 16                         |        |                            | Bits |

| ANALOG INPUTS                                          |                                                                |                            |        |                            |      |

| Absolute Input Voltage                                 | $V_{INx+1}$ , $V_{INx-2}$ to $V_{CC}$ and $V_{EE}$             | V <sub>EE</sub> + 3.2      |        | V <sub>CC</sub> - 3.2      | V    |

| Differential Input Range                               | $(V_{INx^+} - V_{INx^-}), V_{REF}^3 = V_{REFBUF}^4/1.024$      |                            |        |                            |      |

|                                                        | SoftSpan 15: ±10 × V <sub>REF</sub> range                      | −10 × V <sub>REF</sub>     |        | +10 × V <sub>REF</sub>     | V    |

|                                                        | SoftSpan 14: 0 V to 10 × V <sub>REF</sub> range                | 0                          |        | 10 × V <sub>REF</sub>      | V    |

|                                                        | SoftSpan 13: ±6.25 × V <sub>REF</sub> range                    | -6.25 × V <sub>REF</sub>   |        | +6.25 × V <sub>REF</sub>   | V    |

|                                                        | SoftSpan 12: 0 V to 6.25 × V <sub>REF</sub> range              | 0                          |        | 6.25 × V <sub>REF</sub>    | V    |

|                                                        | SoftSpan 11: ±5 × V <sub>REF</sub> range                       | -5 × V <sub>REF</sub>      |        | +5 × V <sub>REF</sub>      | V    |

|                                                        | SoftSpan 10: 0 V to 5 × V <sub>REF</sub> range                 | 0                          |        | 5 × V <sub>REF</sub>       | V    |

|                                                        | SoftSpan 9: ±3.125 × V <sub>REF</sub> range                    | -3.125 × V <sub>REF</sub>  |        | +3.125 × V <sub>REF</sub>  | V    |

|                                                        | SoftSpan 8: 0 V to 3.125 × V <sub>REF</sub> range              | 0                          |        | 3.125 × V <sub>REF</sub>   | V    |

|                                                        | SoftSpan 7: ±2.5 × V <sub>REF</sub> range                      | −2.5 × V <sub>REF</sub>    |        | +2.5 × V <sub>REF</sub>    | V    |

|                                                        | SoftSpan 6: 0 V to 2.5 × V <sub>REF</sub> range                | 0                          |        | 2.5 × V <sub>REF</sub>     | V    |

|                                                        | SoftSpan 5: ±1.5625 × V <sub>REF</sub> range                   | −1.5625 × V <sub>REF</sub> |        | +1.5625 × V <sub>REF</sub> | V    |

|                                                        | SoftSpan 4: 0 V to 1.5625 × V <sub>REF</sub> range             | 0                          |        | 1.5625 × V <sub>REF</sub>  | V    |

|                                                        | SoftSpan 3: ±1.25 × V <sub>REF</sub> range                     | −1.25 × V <sub>REF</sub>   |        | +1.25 × V <sub>REF</sub>   | V    |

|                                                        | SoftSpan 2: 0 V to 1.25 × V <sub>REF</sub> range               | 0                          |        | 1.25 × V <sub>REF</sub>    | V    |

|                                                        | SoftSpan 1: ±0.625 × V <sub>REF</sub> range                    | -0.625 × V <sub>REF</sub>  |        | +0.625 × V <sub>REF</sub>  | V    |

|                                                        | SoftSpan 0: 0 V to 0.625 × V <sub>REF</sub> range              | 0                          |        | 0.625 × V <sub>REF</sub>   | V    |

| Common-Mode Input Range                                | $V_{CM}^{5} = (V_{INx+} + V_{INx-})/2$                         | V <sub>EE</sub> + 3.2      |        | V <sub>CC</sub> - 3.2      | V    |

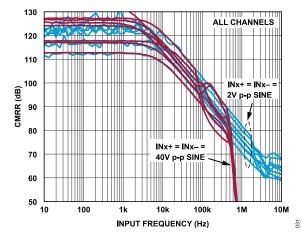

| CMRR                                                   | V <sub>CM</sub> = 36 V p-p, 200 Hz sine, SHDR on               | 100                        | 120    |                            | dB   |

| Differential Input Overdrive<br>Tolerance <sup>6</sup> | $(V_{INx+} - V_{INx-})$                                        | $-(V_{CC} - V_{EE})$       |        | $(V_{CC} - V_{EE})$        | V    |

| Input Overdrive Current<br>Tolerance <sup>6</sup>      | $V_{INx+}, V_{INx-} > V_{CC}$                                  |                            |        | 10                         | mA   |

|                                                        | V <sub>INx+</sub> , V <sub>INx-</sub> < V <sub>EE</sub>        | 0                          |        |                            | mA   |

| Input Leakage Current                                  | $V_{INx+}$ , $V_{INx-} = V_{CC}$ to $V_{EE}$                   | -40                        | ±0.075 | +40                        | nA   |

| Input Resistance                                       | $R_{INx+}^{+7}$ , $R_{INx-}^{-8}$ for each pin                 |                            | 1000   |                            | GΩ   |

| Input Capacitance                                      | $C_{INx^+}^9$ , $C_{INx^-}^{10}$ for each pin                  |                            | 4      |                            | pF   |

| OC ACCURACY                                            |                                                                |                            |        |                            |      |

| No Missing Codes                                       |                                                                | 16                         |        |                            | Bits |

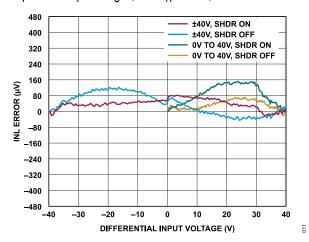

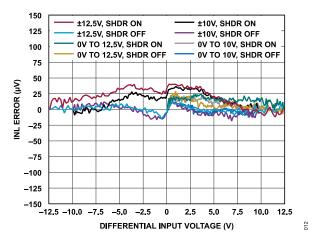

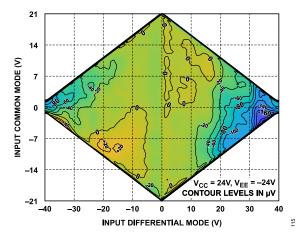

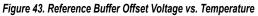

| INL Error                                              | SHDR on                                                        |                            |        |                            |      |

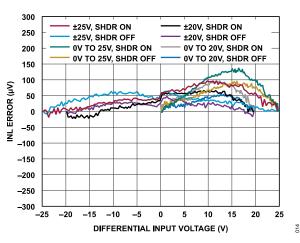

|                                                        | SoftSpan 15 and SoftSpan 14: $\pm 40$ V and 0 V to 40 V ranges | -1220                      | ±160   | +1220                      | μV   |

|                                                        | SoftSpan 13 and SoftSpan 12: $\pm 25$ V and 0 V to 25 V ranges | -763                       | ±100   | +763                       | μV   |

|                                                        | SoftSpan 11 and SoftSpan 10: ±20 V and 0 V to 20 V ranges      | -610                       | ±100   | +610                       | μV   |

|                                                        | SoftSpan 9 and SoftSpan 8: ±12.5 V and 0 V to 12.5 V ranges    | -381                       | ±50    | +381                       | μV   |

|                                                        | SoftSpan 7 and SoftSpan 6: ±10 V and 0 V to 10 V ranges        | -305                       | ±50    | +305                       | μV   |

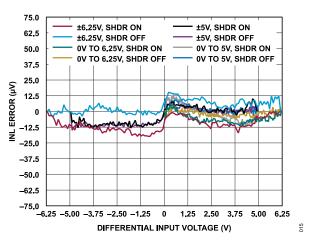

|                                                        | SoftSpan 5 and SoftSpan 4: ±6.25 V and 0 V to 6.25 V ranges    | -190                       | ±25    | +190                       | μV   |

| Parameter                                                         | Test Conditions/Comments                                                   | Min    | Тур                      | Мах    | Unit      |

|-------------------------------------------------------------------|----------------------------------------------------------------------------|--------|--------------------------|--------|-----------|

|                                                                   | SoftSpan 3 and SoftSpan 2: ±5 V and 0 V to 5 V ranges                      | -152   | ±25                      | +152   | μV        |

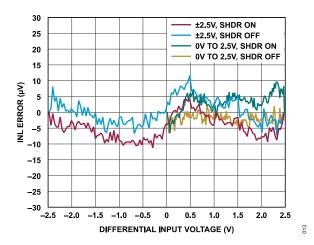

|                                                                   | SoftSpan 1 and SoftSpan 0: ±2.5 V and 0 V to 2.5 V                         | -76    | ±15                      | +76    | μV        |

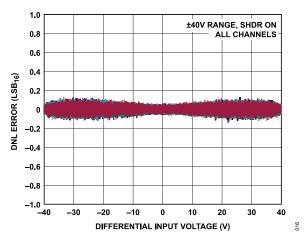

| Differential Nonlinearity (DNL)                                   | ranges                                                                     | -0.9   | ±0.2                     |        | LSB       |

| Error                                                             |                                                                            | 0.0    | ±0.2                     |        | LOD       |

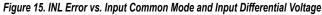

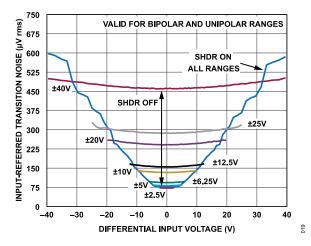

| Transition Noise <sup>11</sup>                                    | SHDR on, near zero-scale                                                   |        | 73                       |        | μV        |

|                                                                   |                                                                            |        |                          |        | RMS       |

|                                                                   | SHDR off, near zero-scale                                                  |        | 461                      |        | μV        |

|                                                                   | SoftSpan 15 and SoftSpan 14: ±40 V and 0 V to 40 V ranges                  |        | 401                      |        | RMS       |

|                                                                   | SoftSpan 13 and SoftSpan 12: ±25 V and 0 V to 25 V                         |        | 287                      |        | μV        |

|                                                                   | ranges                                                                     |        |                          |        | RMS       |

|                                                                   | SoftSpan 11 and SoftSpan 10: ±20 V and 0 V to 20 V                         |        | 241                      |        | μV        |

|                                                                   | ranges<br>SoftSpan 9 and SoftSpan 8: ±12.5 V and 0 V to 12.5 V             |        | 155                      |        | RMS<br>µV |

|                                                                   | ranges                                                                     |        | 155                      |        | RMS       |

|                                                                   | SoftSpan 7 and SoftSpan 6: ±10 V and 0 V to 10 V                           |        | 133                      |        | μV        |

|                                                                   | ranges                                                                     |        |                          |        | RMS       |

|                                                                   | SoftSpan 5 and SoftSpan 4: ±6.25 V and 0 V to 6.25 V                       |        | 94                       |        | μV        |

|                                                                   | ranges<br>SoftSpan 3 and SoftSpan 2: ±5 V and 0 V to 5 V ranges            |        | 81                       |        | RMS<br>µV |

|                                                                   | Solispan 5 and Solispan 2. 15 V and 0 V to 5 V langes                      |        | 01                       |        | RMS       |

|                                                                   | SoftSpan 1 and SoftSpan 0: ±2.5 V and 0 V to 2.5 V                         |        | 73                       |        | μV        |

|                                                                   | ranges                                                                     |        |                          |        | RMS       |

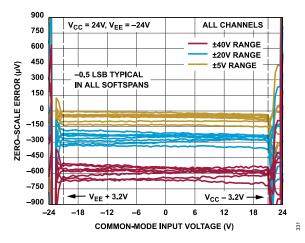

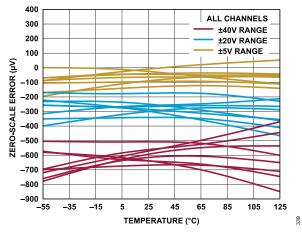

| Zero-Scale Error                                                  |                                                                            | -1300  | -0.5 × LSB <sup>12</sup> | +1300  | μV        |

| Zero-Scale Error Drift                                            |                                                                            |        | ±1.5                     |        | μV/°(     |

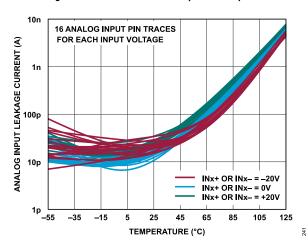

| Full-Scale Error <sup>13</sup>                                    | $V_{\text{REFIO}} = 4.096 \text{ V}, \text{REFIO} \text{ overdriven}^{14}$ | -0.035 | ±0.01                    | +0.035 | %FS       |

| Full-Scale Error Drift <sup>13</sup><br>AC ACCURACY <sup>15</sup> | V <sub>REFIO</sub> = 4.096 V, REFIO overdriven <sup>14</sup>               |        | ±1.5                     |        | ppm/      |

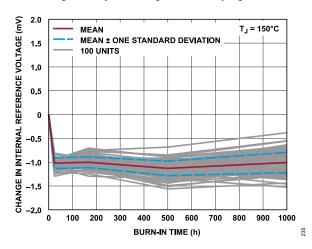

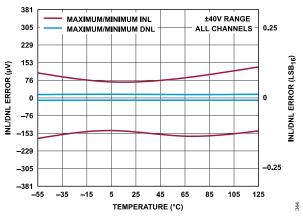

| Dynamic Range                                                     | SHDR on/off                                                                |        |                          |        |           |

| Dynamic Nange                                                     | SoftSpan 15: ±40 V range                                                   |        | 98.1/93.7                |        | dB        |

|                                                                   | SoftSpan 14: 0 V to 40 V range                                             |        | 97.6/89.1                |        | dB        |

|                                                                   | SoftSpan 13: ±25 V range                                                   |        | 97.9/93.8                |        | dB        |

|                                                                   |                                                                            |        |                          |        |           |

|                                                                   | SoftSpan 12: 0 V to 25 V range                                             |        | 96.7/89.1<br>07.6/03.5   |        | dB        |

|                                                                   | SoftSpan 11: ±20 V range                                                   |        | 97.6/93.5                |        | dB        |

|                                                                   | SoftSpan 10: 0 V to 20 V range                                             |        | 96.0/88.7                |        | dB        |

|                                                                   | SoftSpan 9: ±12.5 V range                                                  |        | 96.7/93.3                |        | dB        |

|                                                                   | SoftSpan 8: 0 V to 12.5 V range                                            |        | 93.7/88.5                |        | dB        |

|                                                                   | SoftSpan 7: ±10 V range                                                    |        | 95.9/92.9                |        | dB        |

|                                                                   | SoftSpan 6: 0 V to 10 V range                                              |        | 92.4/88.0                |        | dB        |

|                                                                   | SoftSpan 5: ±6.25 V range                                                  |        | 93.7/92.2                |        | dB        |

|                                                                   | SoftSpan 4: 0 V to 6.25 V range                                            |        | 89.1/87.1                |        | dB        |

|                                                                   | SoftSpan 3: ±5 V range                                                     |        | 92.3/91.6                |        | dB        |

|                                                                   | SoftSpan 2: 0 V to 5 V range                                               |        | 87.3/86.4                |        | dB        |

|                                                                   | SoftSpan 1: ±2.5 V range                                                   |        | 87.3/87.3                |        | dB        |

|                                                                   | SoftSpan 0: 0 V to 2.5 V range                                             |        | 81.6/81.6                |        | dB        |

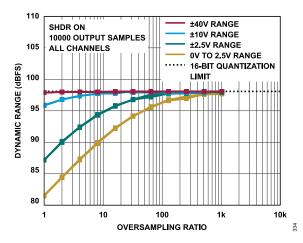

| Oversampled Dynamic Range <sup>16</sup>                           | OSR = 2, SoftSpan 0                                                        |        | Dynamic Range +          | · 3    | dB        |

|                                                                   | OSR = 2, SoftSpan 15                                                       |        | 98.1                     |        | dB        |

|                                                                   | OSR = 1024, All SoftSpans                                                  |        | 98.1                     |        | dB        |

# AD4857

# **SPECIFICATIONS**

| rameter                                         | Test Conditions/Comments                                     | Min  | Тур  | Max Ur |

|-------------------------------------------------|--------------------------------------------------------------|------|------|--------|

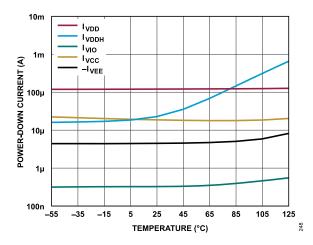

| Signal-to-Noise-and-Distortion<br>(SINAD) Ratio | SHDR on, input frequency (f <sub>IN</sub> ) = 1 kHz, -1 dBFS |      |      |        |

|                                                 | SoftSpan 15: ±40 V range                                     | 90.1 | 94.6 | dE     |

|                                                 | SoftSpan 14: 0 V to 40 V range                               | 85.1 | 90.9 | dE     |

|                                                 | SoftSpan 13: ±25 V range                                     | 91.5 | 94.7 | dE     |

|                                                 | SoftSpan 12: 0 V to 25 V range                               | 86.1 | 90.9 | dE     |

|                                                 | SoftSpan 11: ±20 V range                                     | 92.3 | 94.9 | dE     |

|                                                 | SoftSpan 10: 0 V to 20 V range                               | 86.9 | 90.9 | dE     |

|                                                 | SoftSpan 9: ±12.5 V range                                    | 92.8 | 94.5 | dE     |

|                                                 | SoftSpan 8: 0 V to 12.5 V range                              | 87.8 | 90.5 | dE     |

|                                                 | SoftSpan 7: ±10 V range                                      | 92.6 | 94.2 | dE     |

|                                                 | SoftSpan 6: 0 V to 10 V range                                | 87.7 | 90   | dE     |

|                                                 | SoftSpan 5: ±6.25 V range                                    | 91.4 | 92.8 | dE     |

|                                                 | SoftSpan 4: 0 V to 6.25 V range                              | 86.5 | 88.1 | dE     |

|                                                 | SoftSpan 3: ±5 V range                                       | 90.4 | 91.7 | dE     |

|                                                 | SoftSpan 2: 0 V to 5 V range                                 | 85.2 | 86.8 | dE     |

|                                                 | SoftSpan 1: ±2.5 V range                                     | 85.2 | 86.8 | dE     |

|                                                 | SoftSpan 0: 0 V to 2.5 V range                               | 79.7 | 81.4 | dE     |

|                                                 | SHDR off, f <sub>IN</sub> = 1 kHz, −1 dBFS                   |      |      |        |

|                                                 | SoftSpan 15: ±40 V range                                     | 92   | 93.4 | dE     |

|                                                 | SoftSpan 14: 0 V to 40 V range                               | 86.8 | 88.7 | dl     |

|                                                 | SoftSpan 13: ±25 V range                                     | 92   | 93.4 | df     |

|                                                 | SoftSpan 12: 0 V to 25 V range                               | 86.9 | 88.7 | dl     |

|                                                 | SoftSpan 11: ±20 V range                                     | 91.7 | 93.2 | dl     |

|                                                 | SoftSpan 10: 0 V to 20 V range                               | 86.6 | 88.3 | df     |

|                                                 | SoftSpan 9: ±12.5 V range                                    | 91.6 | 93   | dl     |

|                                                 | SoftSpan 8: 0 V to 12.5 V range                              | 86.5 | 88.2 | df     |

|                                                 | SoftSpan 7: ±10 V range                                      | 91.2 | 92.6 | dl     |

|                                                 | SoftSpan 6: 0 V to 10 V range                                | 85.9 | 87.7 | dE     |

|                                                 | SoftSpan 5: ±6.25 V range                                    | 90.4 | 91.7 | dl     |

|                                                 | SoftSpan 4: 0 V to 6.25 V range                              | 85.2 | 86.7 | dl     |

|                                                 | SoftSpan 3: ±5 V range                                       | 89.7 | 91.1 | dE     |

|                                                 | SoftSpan 2: 0 V to 5 V range                                 | 84.5 | 86.1 | dl     |

|                                                 | SoftSpan 1: ±2.5 V range                                     | 85.2 | 86.8 | dE     |

|                                                 | SoftSpan 0: 0 V to 2.5 V range                               | 79.7 | 81.4 | df     |

| ignal-to-Noise Ratio (SNR)                      | SHDR on, f <sub>IN</sub> = 1 kHz, −1 dBFS                    |      |      |        |

| ,                                               | SoftSpan 15: ±40 V range                                     | 90.1 | 94.6 | dE     |

|                                                 | SoftSpan 14: 0 V to 40 V range                               | 85.1 | 90.9 | dE     |

|                                                 | SoftSpan 13: ±25 V range                                     | 91.5 | 94.7 | dE     |

|                                                 | SoftSpan 12: 0 V to 25 V range                               | 86.1 | 90.9 | dE     |

|                                                 | SoftSpan 11: ±20 V range                                     | 92.3 | 94.9 | dE     |

|                                                 | SoftSpan 10: 0 V to 20 V range                               | 86.9 | 90.9 | dE     |

|                                                 | SoftSpan 9: ±12.5 V range                                    | 92.8 | 94.5 | dE     |

|                                                 | SoftSpan 8: 0 V to 12.5 V range                              | 87.8 | 90.5 | dE     |

|                                                 | SoftSpan 7: ±10 V range                                      | 92.6 | 94.2 | dE     |

|                                                 | SoftSpan 6: 0 V to 10 V range                                | 87.7 | 90.0 | dE     |

|                                                 | SoftSpan 5: ±6.25 V range                                    | 91.4 | 92.8 | dE     |

|                                                 | SoftSpan 4: 0 V to 6.25 V range                              | 86.5 | 88.1 | dE     |

|                                                 | SoftSpan 3: ±5 V range                                       | 90.4 | 91.7 | dE     |

| arameter                        | Test Conditions/Comments                   | Min  | Тур     | Max  | Un |

|---------------------------------|--------------------------------------------|------|---------|------|----|

|                                 | SoftSpan 2: 0 V to 5 V range               | 85.2 | 86.8    |      | dB |

|                                 | SoftSpan 1: ±2.5 V range                   | 85.2 | 86.8    |      | dB |

|                                 | SoftSpan 0: 0 V to 2.5V range              | 79.7 | 81.4    |      | dB |

|                                 | SHDR off, f <sub>IN</sub> = 1 kHz, −1 dBFS |      |         |      |    |

|                                 | SoftSpan 15: ±40 V range                   | 92.0 | 93.4    |      | dB |

|                                 | SoftSpan 14: 0 V to 40 V range             | 86.8 | 88.7    |      | dB |

|                                 | SoftSpan 13: ±25 V range                   | 92.0 | 93.4    |      | dB |

|                                 | SoftSpan 12: 0 V to 25 V range             | 86.9 | 88.7    |      | dB |

|                                 | SoftSpan 11: ±20 V range                   | 91.7 | 93.2    |      | dB |

|                                 | SoftSpan 10: 0 V to 20 V range             | 86.6 | 88.3    |      | dB |

|                                 | SoftSpan 9: ±12.5 V range                  | 91.6 | 93.0    |      | dB |

|                                 | SoftSpan 8: 0 V to 12.5 V range            | 86.5 | 88.2    |      | dB |

|                                 | SoftSpan 7: ±10 V range                    | 91.2 | 92.6    |      | dB |

|                                 | SoftSpan 6: 0 V to 10 V range              | 85.9 | 87.7    |      | dB |

|                                 | SoftSpan 5: ±6.25 V range                  | 90.4 | 91.7    |      | dE |

|                                 | SoftSpan 4: 0 V to 6.25 V range            | 85.2 | 86.7    |      | dE |

|                                 | SoftSpan 3: ±5 V range                     | 89.7 | 91.1    |      | dE |

|                                 | SoftSpan 2: 0 V to 5 V range               | 84.5 | 86.1    |      | dE |

|                                 | SoftSpan 1: ±2.5 V range                   | 85.2 | 86.8    |      | dE |

|                                 | SoftSpan 0: 0 V to 2.5 V range             | 79.7 | 81.4    |      | dE |

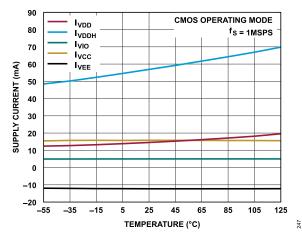

| Total Harmonic Distortion (THD) | $f_{IN} = 1 \text{ kHz}, -1 \text{ dBFS}$  |      | • • • • |      |    |

|                                 | SoftSpan 15: ±40 V range                   |      | -117    | -99  | dE |

|                                 | SoftSpan 14: 0 V to 40 V range             |      | -109    | -95  | dE |

|                                 | SoftSpan 13: ±25 V range                   |      | -117    | -100 | dE |

|                                 | SoftSpan 12: 0 V to 25 V range             |      | -111    | -98  | dE |

|                                 | SoftSpan 11: ±20 V range                   |      | -114    | -99  | dE |

|                                 | SoftSpan 10: 0 V to 20 V range             |      | -112    | -99  | dB |

|                                 | SoftSpan 9: ±12.5 V range                  |      | -114    | -100 | dE |

|                                 | SoftSpan 8: 0 V to 12.5 V range            |      | -113    | -100 | dB |

|                                 | SoftSpan 7: ±10 V range                    |      | -115    | -100 | dE |

|                                 | SoftSpan 6: 0 V to 10 V range              |      | -113    | -100 | dB |

|                                 | SoftSpan 5: ±6.25 V range                  |      | -115    | -99  | dB |

|                                 | SoftSpan 4: 0 V to 6.25 V range            |      | -113    | -99  | dE |

|                                 | SoftSpan 3: ±5 V range                     |      | -114    | -97  | dE |

|                                 | SoftSpan 2: 0 V to 5 V range               |      | -113    | -97  | dE |

|                                 | SoftSpan 1: ±2.5 V range                   |      | -109    | -92  | dB |

|                                 | SoftSpan 0: 0 V to 2.5 V range             |      | -110    | -92  | dB |

| Spurious-Free Dynamic Range     | $f_{IN} = 1 \text{ kHz}, -1 \text{ dBFS}$  |      | -110    | -92  | UD |

| (SFDR)                          |                                            |      |         |      |    |

|                                 | SoftSpan 15: ±40 V range                   | 101  | 119     |      | dB |

|                                 | SoftSpan 14: 0 V to 40 V range             | 99   | 113     |      | dB |

|                                 | SoftSpan 13: ±25 V range                   | 101  | 119     |      | dB |

|                                 | SoftSpan 12: 0 V to 25 V range             | 103  | 115     |      | dB |

|                                 | SoftSpan 11: ±20 V range                   | 103  | 119     |      | dB |

|                                 | SoftSpan 10: 0 V to 20 V range             | 103  | 116     |      | dB |

|                                 | SoftSpan 9: ±12.5 V range                  | 104  | 119     |      | dB |

|                                 | SoftSpan 8: 0 V to 12.5 V range            | 104  | 116     |      | dB |

|                                 | SoftSpan 7: ±10 V range                    | 105  | 119     |      | dB |

|                                 | SoftSpan 6: 0 V to 10 V range              | 105  | 116     |      | dB |

| Parameter                                                   | Test Conditions/Comments                               | Min   | Тур   | Max   | Unit   |

|-------------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|--------|

|                                                             | SoftSpan 5: ±6.25 V range                              | 103   | 118   |       | dB     |

|                                                             | SoftSpan 4: 0 V to 6.25 V range                        | 103   | 117   |       | dB     |

|                                                             | SoftSpan 3: ±5 V range                                 | 101   | 117   |       | dB     |

|                                                             | SoftSpan 2: 0 V to 5 V range                           | 101   | 117   |       | dB     |

|                                                             | SoftSpan 1: ±2.5 V range                               | 96    | 111   |       | dB     |

|                                                             | SoftSpan 0: 0 V to 2.5 V range                         | 96    | 113   |       | dB     |

| Channel-to-Channel Crosstalk                                | All channels converting <sup>17</sup>                  |       | -120  |       | dB     |

| −3 dB Small-Signal Input                                    |                                                        |       |       |       |        |

| Bandwidth                                                   |                                                        |       | 11    |       | MHz    |

| Aperture Delay                                              |                                                        |       | 1     |       | ns     |

| Aperture Delay Matching                                     |                                                        |       | 300   |       | ps     |

| Aperture Jitter                                             |                                                        |       | 1     |       | ps RMS |

| Full-Scale Input Step Settling<br>Time                      | Full-scale step, 50 ppm settling                       |       | 300   |       | ns     |

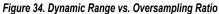

| INTERNAL REFERENCE                                          |                                                        |       |       |       |        |

| ENABLED                                                     |                                                        |       |       |       |        |

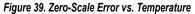

| Internal Reference Output<br>Voltage (V <sub>REFIO</sub> )  | T <sub>A</sub> = 25°C                                  | 4.093 | 4.096 | 4.099 | V      |

| Internal Reference Temperature<br>Coefficient <sup>18</sup> |                                                        | -10   | ±2    | +10   | ppm/°C |

| Internal Reference Line<br>Regulation                       | V <sub>DD</sub> = 4.75 V to 5.25 V                     |       | 50    |       | μV/V   |

| REFIO Output Resistance                                     |                                                        |       | 58    |       | Ω      |

| REFIO Output Capacitance                                    |                                                        |       | 10    |       | nF     |

| INTERNAL REFERENCE                                          | REFIO overdriven <sup>14</sup>                         |       |       |       |        |

| DISABLED                                                    |                                                        |       |       |       |        |

| REFIO Input Voltage (V <sub>REFIO</sub> )                   |                                                        | 4.071 | 4.096 | 4.121 | V      |

| REFIO Input Resistance                                      |                                                        |       | 38    |       | kΩ     |

| REFIO Input Capacitance                                     |                                                        |       | 10    |       | nF     |

| REFERENCE BUFFER ENABLED                                    |                                                        |       |       |       |        |

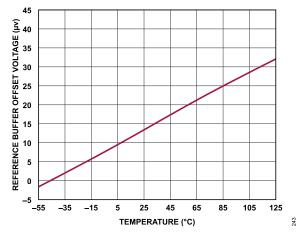

| Reference Buffer Offset Voltage                             | $V_{OS} = (V_{REFBUF} - V_{REFIO}), T_A = 25^{\circ}C$ | -100  | ±20   | +100  | μV     |

| (V <sub>OS</sub> )                                          |                                                        |       | · 0 F |       |        |

| Reference Buffer Offset Voltage<br>Drift                    |                                                        |       | ±0.5  |       | µV/°C  |

| REFERENCE BUFFER DISABLED                                   | REFBUF overdriven <sup>19</sup>                        |       |       |       |        |

| REFBUF Input Voltage                                        |                                                        | 4.071 | 4.096 | 4.121 | V      |

| (V <sub>REFBUF</sub> )                                      |                                                        | 4.071 | 4.090 | 4.121 | V      |

| REFBUF Input Current                                        | V <sub>REFBUF</sub> = 4.096 V, f <sub>S</sub> = 1 MSPS |       | 3.3   | 4.5   | mA     |

| (I <sub>REFBUF</sub> ) <sup>20</sup>                        |                                                        |       |       |       |        |

|                                                             | V <sub>REFBUF</sub> = 4.096 V, not converting          |       | 2.2   |       | mA     |

| SCALED REFERENCE OUTPUT                                     |                                                        |       |       |       |        |

| REF2500 Output Voltage                                      | T <sub>A</sub> = 25°C                                  | 2.497 | 2.5   | 2.503 | V      |

| (V <sub>REF2500</sub> )                                     |                                                        |       |       |       |        |

| REF2500 Temperature<br>Coefficient <sup>18</sup>            |                                                        | -10   | ±2    | +10   | ppm/°C |

| REF2500 Output Resistance                                   |                                                        |       | 26    |       | kΩ     |

| CMOS DIGITAL INPUTS                                         |                                                        |       |       |       |        |

| Input Voltage High (V <sub>IH</sub> )                       |                                                        |       |       |       |        |

| CNV                                                         |                                                        | 0.8   |       |       | V      |

| HIVIO/LOVIO                                                 |                                                        | 4     |       |       | V      |

# AD4857

# **SPECIFICATIONS**

| Parameter                                                 | Test Conditions/Comments                                                                  | Min                    | Тур  | Max                    | Unit |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------|------|------------------------|------|

| All Other Pins                                            |                                                                                           | 0.85 × V <sub>IO</sub> |      |                        | V    |

| Input Voltage Low (V <sub>IL</sub> )                      |                                                                                           |                        |      |                        |      |

| CNV                                                       |                                                                                           |                        |      | 0.4                    | V    |

| HIVIO/LOVIO                                               |                                                                                           |                        |      | 1                      | V    |

| All Other Pins                                            |                                                                                           |                        |      | 0.15 × V <sub>IO</sub> | V    |

| Digital Input Current (I <sub>IN</sub> )                  |                                                                                           |                        |      |                        |      |

| CNV                                                       |                                                                                           | -100                   |      | +100                   | μA   |

| HIVIO/LOVIO                                               |                                                                                           | -10                    |      | +10                    | μA   |

| All Other Pins                                            |                                                                                           | -10                    |      | +10                    | μA   |

| Digital Input Capacitance (CIN)                           |                                                                                           |                        | 2    |                        | pF   |

| CMOS DIGITAL OUTPUTS                                      |                                                                                           |                        |      |                        |      |

| Output Voltage High (V <sub>OH</sub> )                    | Source current (I <sub>SOURCE</sub> ) = 500 µA                                            | V <sub>IO</sub> – 0.2  |      |                        | V    |

| Output Voltage Low (V <sub>OL</sub> )                     | Sink current (I <sub>SINK</sub> ) = 500 µA                                                |                        |      | 0.2                    | V    |

| High-Z Output Leakage Current                             |                                                                                           | -10                    |      | +10                    | μA   |

| (I <sub>OZ</sub> )                                        |                                                                                           |                        |      |                        |      |

| LVDS DIGITAL INPUTS                                       |                                                                                           |                        |      |                        |      |

| Differential Input Voltage (VID)                          |                                                                                           | ±200                   | ±350 | ±600                   | mV   |

| Differential Termination<br>Resistance (R <sub>ID</sub> ) | $\overline{\text{CS}}$ = 0 V, V <sub>ICM</sub> = 1.2 V, termination enabled <sup>21</sup> | 95                     | 107  | 120                    | Ω    |

|                                                           | $\overline{CS} = V_{IO}$ or termination disabled <sup>21</sup>                            |                        | 10   |                        | MΩ   |

| Common-Mode Input Voltage<br>(V <sub>ICM</sub> )          | 1.71 V ≤ V <sub>IO</sub> < 2.5 V                                                          | 0.3                    | 1.2  | V <sub>IO</sub> – 0.3  | V    |

|                                                           | 2.5 V ≤ V <sub>IO</sub> ≤ 5.25V                                                           | 0.3                    | 1.2  | 2.2                    | V    |

| Common-Mode Input Current                                 |                                                                                           | -10                    |      | +10                    | μA   |

| (I <sub>ICM</sub> )                                       |                                                                                           |                        |      |                        |      |

| LVDS DIGITAL OUTPUTS                                      |                                                                                           |                        |      |                        |      |

| Differential Output Voltage (V <sub>OD</sub> )            | 100 $\Omega$ differential termination, full-bias mode <sup>21</sup>                       | ±260                   | ±330 | ±400                   | mV   |

|                                                           | 100 $\Omega$ differential termination, half-bias mode <sup>21</sup>                       | ±135                   | ±185 | ±235                   | mV   |

| Common-Mode Output Voltage<br>(V <sub>OCM</sub> )         | 100 $\Omega$ differential termination                                                     | 1.1                    | 1.25 | 1.4                    | V    |

| High-Z Output Leakage Current<br>(I <sub>OZ</sub> )       |                                                                                           | -10                    |      | +10                    | μA   |

| POWER SUPPLY VOLTAGES                                     |                                                                                           |                        |      |                        |      |

| V <sub>CC</sub>                                           |                                                                                           | 7.25                   |      | 48                     | V    |

| V <sub>EE</sub>                                           |                                                                                           | -40.75                 |      | 0                      | V    |

| V <sub>CC</sub> – V <sub>EE</sub>                         |                                                                                           | 10                     |      | 48                     | V    |

| V <sub>DD</sub>                                           |                                                                                           | 4.75                   | 5.0  | 5.25                   | V    |

| V <sub>DDH</sub>                                          | Disables 1.8 V LDO regulator                                                              |                        | 0    |                        | V    |

|                                                           | Enables 1.8 V LDO regulator                                                               | 2.2                    |      | 5.25                   | V    |

| V <sub>DDL</sub>                                          | Supplied externally, 1.8 V LDO regulator disabled                                         | 1.71                   | 1.8  | 1.89                   | V    |

|                                                           | Supplied by 1.8 V LDO regulator, no external connection                                   |                        | 1.8  |                        | V    |

| V <sub>IO</sub>                                           |                                                                                           |                        |      |                        |      |

| CMOS Conversion Data<br>Output                            | HIVIO/LOVIO = V <sub>DD</sub>                                                             | 1.71                   |      | 5.25                   | V    |

|                                                           | HIVIO/LOVIO = GND                                                                         | 0.9                    |      | 1.89                   | V    |

| LVDS Conversion Data<br>Output                            | $HIVIO/\overline{LOVIO} = V_{DD}$                                                         | 1.71                   |      | 5.25                   | V    |

| • p = -                                                   | HIVIO/LOVIO = GND                                                                         | 1.71                   |      | 1.89                   | V    |

# AD4857

# **SPECIFICATIONS**

| Parameter                                     | Test Conditions/Comments                                                                                     | Min   | Тур        | Max  | Unit    |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------|------------|------|---------|

| OWER SUPPLY CURRENTS                          |                                                                                                              |       |            |      |         |

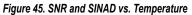

| CMOS Conversion Data Output                   | 25 pF load on CMOS outputs                                                                                   |       |            |      |         |

| Operating Mode <sup>22</sup>                  | f <sub>S</sub> = 1 MSPS, all channels converting                                                             |       |            |      |         |

| V <sub>CC</sub> Current (I <sub>Vcc</sub> )   | V <sub>CC</sub> = +24 V, V <sub>EE</sub> = -24 V                                                             |       | 14.9       | 19.6 | mA      |

|                                               | $V_{CC} = +15 V, V_{EE} = -15 V$                                                                             |       | 13         |      | mA      |

|                                               | $V_{CC} = +8.2 \text{ V}, V_{EE} = -3.2 \text{ V}$                                                           |       | 10.7       |      | mA      |

| V <sub>EE</sub> Current (I <sub>Vee</sub> )   | $V_{CC} = +24 \text{ V}, \text{ V}_{FF} = -24 \text{ V}$                                                     | -16.9 | -12        |      | mA      |

|                                               | $V_{CC} = +15 \text{ V}, \text{ V}_{FF} = -15 \text{ V}$                                                     |       | -10.2      |      | mA      |

|                                               | $V_{CC} = +8.2 \text{ V}, \text{ V}_{FF} = -3.2 \text{ V}$                                                   |       | -8         |      | mA      |

| V <sub>DD</sub> Current (I <sub>Vpp</sub> )   | Reference and reference buffer enabled                                                                       |       | 15.2       | 22.3 | mA      |

|                                               | V <sub>REFIO</sub> = 4.096 V, REFIO overdriven <sup>14</sup>                                                 |       | 13.2       |      | mA      |

|                                               | $V_{\text{REFBUF}} = 4.096 \text{ V}, \text{REFBUF overdriven}^{19}$                                         |       | 3.7        |      | mA      |

| V <sub>DDH</sub> Current (I <sub>VnnH</sub> ) | $V_{\text{DDH}}$ = 2.5 V, 1.8 V LDO regulator enabled                                                        |       | 57         | 78   | mA      |

| V <sub>DDL</sub> Current (I <sub>Vppi</sub> ) | $V_{\text{DDH}}$ = GND, 1.8 V LDO regulator disabled, $V_{\text{DDH}}$ = 1.8 V                               |       | 55         | 76   | mA      |

| V <sub>IO</sub> Current (I <sub>Vio</sub> )   | $V_{IO} = 2.5 \text{ V}$                                                                                     |       | 5.5        | 7.3  | mA      |

| Acquisition Mode                              |                                                                                                              |       |            |      |         |

| I <sub>Vcc</sub>                              | V <sub>CC</sub> = +24 V, V <sub>FF</sub> = -24 V                                                             |       | 9.4        |      | mA      |

| I <sub>VEE</sub>                              | $V_{CC} = +24 \text{ V}, V_{FF} = -24 \text{ V}$                                                             |       | -7.4       |      | mA      |

| I <sub>VDD</sub>                              | Reference and reference buffer enabled                                                                       |       | 10.8       |      | mA      |

| "V <sub>DD</sub>                              | $V_{\text{REFIO}} = 4.096$ V, REFIO overdriven <sup>14</sup>                                                 |       | 8.8        |      | mA      |

|                                               | $V_{\text{REFBUE}} = 4.096 \text{ V}, \text{REFBUF overdriven}^{19}$                                         |       | 1.4        |      | mA      |

| k.                                            | $V_{\text{DDH}} = 2.5 \text{ V}, 1.8 \text{ V} \text{ LDO regulator enabled}$                                |       | 72         |      | μA      |

| I <sub>VDDH</sub>                             | $V_{\text{DDH}}$ = GND, 1.8 V LDO regulator disabled, $V_{\text{DDH}}$ = 1.8 V                               |       | 16         |      | μΑ      |

| I <sub>VDDL</sub>                             | $V_{\text{IO}} = 2.5 \text{ V}$                                                                              |       | 10         |      | μΑ      |

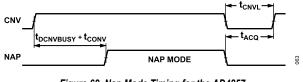

| Ι <sub>Vιο</sub><br>Nap Mode                  | VIO - 2.5 V                                                                                                  |       | I          |      | μ.<br>I |

|                                               | V <sub>CC</sub> = +24 V, V <sub>FF</sub> = -24 V                                                             |       | 4.5        |      | mA      |

| l <sub>Vcc</sub>                              | $V_{CC} = +24 V, V_{EE} = -24 V$<br>$V_{CC} = +24 V, V_{FF} = -24 V$                                         |       | -3.3       |      | mA      |

| I <sub>VEE</sub>                              | $v_{CC} = 124$ v, $v_{EE} = 124$ v<br>Reference and reference buffer enabled                                 |       | 10.3       |      | mA      |

| $I_{V_{DD}}$                                  | $V_{\text{REFIO}} = 4.096 \text{ V}, \text{REFIO overdriven}^{14}$                                           |       | 8.3        |      | mA      |

|                                               | $V_{\text{REFI0}} = 4.096 \text{ V}, \text{REFI0 Overdriven}^{19}$                                           |       | 0.5<br>1.0 |      |         |

| I                                             | $V_{\text{REFBUF}} = 4.090$ V, REFBUF Overdiverties<br>$V_{\text{DDH}} = 2.5$ V, 1.8 V LDO regulator enabled |       | 72         |      | mA      |

| I <sub>Vddh</sub>                             | $V_{\text{DDH}}$ = GND, 1.8 V LDO regulator disabled, $V_{\text{DDL}}$ = 1.8 V                               |       | 16         |      | μA      |

| I <sub>VDDL</sub>                             |                                                                                                              |       |            |      | μΑ      |

| I <sub>Vio</sub><br>Deure Deure Mada          | V <sub>IO</sub> = 2.5 V                                                                                      |       | 1          |      | μA      |

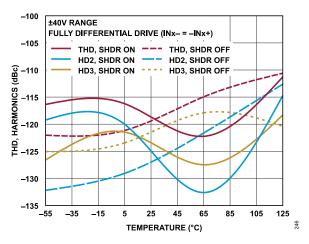

| Power-Down Mode                               | N                                                                                                            |       | 40         |      |         |

| I <sub>Vcc</sub>                              | $V_{CC} = +24 \text{ V}, V_{EE} = -24 \text{ V}$                                                             |       | 18         |      | μA      |

| I <sub>VEE</sub>                              | $V_{CC} = +24 \text{ V}, V_{EE} = -24 \text{ V}$                                                             |       | -4         |      | μA      |

| I <sub>VDD</sub>                              |                                                                                                              |       | 130        |      | μA      |

| I <sub>VDDH</sub>                             | $V_{\text{DDH}} = 2.5 \text{ V}, 1.8 \text{ V} \text{ LDO regulator enabled}$                                |       | 30         |      | μA      |

| I <sub>VDDL</sub>                             | $V_{DDH}$ = GND, 1.8 V LDO regulator disabled, $V_{DDL}$ = 1.8 V                                             |       | 16         |      | μA      |

|                                               | $V_{10} = 2.5 V$                                                                                             |       | 1          |      | μA      |

| LVDS Conversion Data Output                   | 100 $\Omega$ differential load on LVDS outputs                                                               |       |            |      |         |

| Operating Mode                                | $f_{S}$ = 1 MSPS, all channels converting                                                                    |       |            |      |         |

| I <sub>Vcc</sub>                              | $V_{CC} = +24 V, V_{EE} = -24 V$                                                                             |       | 14.9       | 19.6 | mA      |

|                                               | $V_{CC} = +15 V, V_{EE} = -15 V$                                                                             |       | 13         |      | mA      |

|                                               | $V_{CC} = +8.2 \text{ V}, V_{EE} = -3.2 \text{ V}$                                                           |       | 10.7       |      | mA      |

| I <sub>VEE</sub>                              | $V_{CC} = +24 \text{ V}, V_{EE} = -24 \text{ V}$                                                             | -16.9 | -12        |      | mA      |

|                                               | $V_{CC} = +15 \text{ V}, V_{EE} = -15 \text{ V}$                                                             |       | -10.2      |      | mA      |

|                                               | V <sub>CC</sub> = +8.2 V, V <sub>EE</sub> = -3.2 V                                                           |       | -8         |      | mA      |

| I <sub>VDD</sub>                              | Reference and reference buffer enabled                                                                       |       | 18.8       | 25.9 | mA      |

| Table 1. Specifications (Continued<br>Parameter | Test Conditions/Comments                                                       | Min | Тур  | Мах  | Unit |

|-------------------------------------------------|--------------------------------------------------------------------------------|-----|------|------|------|

|                                                 | V <sub>REFIO</sub> = 4.096 V, REFIO overdriven <sup>14</sup>                   |     | 16.8 |      | mA   |

|                                                 | $V_{\text{REFBUF}}$ = 4.096 V, REFBUF overdriven <sup>19</sup>                 |     | 7.3  |      | mA   |

| $I_{V_{DDH}}$                                   | V <sub>DDH</sub> = 2.5 V, 1.8 V LDO regulator enabled                          |     | 67   | 89   | mA   |

|                                                 | $V_{DDH}$ = GND, 1.8 V LDO regulator disabled, $V_{DDL}$ = 1.8 V               |     | 65   | 87   | mA   |

| I <sub>VIO</sub>                                | V <sub>IO</sub> = 2.5 V                                                        |     | 82   | 165  | μA   |

| Acquisition Mode                                |                                                                                |     |      |      |      |

| I <sub>Vcc</sub>                                | V <sub>CC</sub> = +24 V, V <sub>EE</sub> = -24 V                               |     | 9.4  |      | mA   |

| I <sub>VEE</sub>                                | $V_{CC} = +24 \text{ V}, V_{EE} = -24 \text{ V}$                               |     | -7.4 |      | mA   |

| I <sub>VDD</sub>                                | Reference and reference buffer enabled                                         |     | 11.6 |      | mA   |

| 55                                              | V <sub>REFIO</sub> = 4.096 V, REFIO overdriven <sup>14</sup>                   |     | 9.6  |      | mA   |

|                                                 | V <sub>REFBUF</sub> = 4.096 V, REFBUF overdriven <sup>19</sup>                 |     | 2.2  |      | mA   |

| $I_{V_{DDH}}$                                   | V <sub>DDH</sub> = 2.5 V, 1.8 V LDO regulator enabled                          |     | 8.4  |      | mA   |

| I <sub>VDDL</sub>                               | $V_{DDH}$ = GND, 1.8 V LDO regulator disabled, $V_{DDL}$ = 1.8 V               |     | 8.3  |      | mA   |

| I <sub>VIO</sub>                                | V <sub>IO</sub> = 2.5 V                                                        |     | 1    |      | μA   |

| Nap Mode                                        |                                                                                |     |      |      |      |

| I <sub>Vcc</sub>                                | V <sub>CC</sub> = +24 V, V <sub>EE</sub> = -24 V                               |     | 4.5  |      | mA   |

| I <sub>VEE</sub>                                | $V_{CC} = +24 \text{ V}, V_{EE} = -24 \text{ V}$                               |     | -3.3 |      | mA   |

| I <sub>VDD</sub>                                | Reference and reference buffer enabled                                         |     | 11.1 |      | mA   |

| 55                                              | V <sub>REFIO</sub> = 4.096 V, REFIO overdriven <sup>14</sup>                   |     | 9.1  |      | mA   |

|                                                 | V <sub>REFBUF</sub> = 4.096 V, REFBUF overdriven <sup>19</sup>                 |     | 1.8  |      | mA   |

| I <sub>Vddh</sub>                               | V <sub>DDH</sub> = 2.5 V, 1.8 V LDO regulator enabled                          |     | 8.4  |      | mA   |

| I <sub>VDDL</sub>                               | $V_{\text{DDH}}$ = GND, 1.8 V LDO regulator disabled, $V_{\text{DDL}}$ = 1.8 V |     | 8.3  |      | mA   |

| IVIO                                            | V <sub>IO</sub> = 2.5 V 1                                                      |     |      | μA   |      |

| Power-Down Mode                                 |                                                                                |     |      |      |      |

| I <sub>Vcc</sub>                                | V <sub>CC</sub> = +24 V, V <sub>EE</sub> = -24 V                               |     | 18   |      | μA   |

| I <sub>VEE</sub>                                | $V_{CC} = +24 \text{ V}, V_{EE} = -24 \text{ V}$                               |     | -4   |      | μA   |

| I <sub>VDD</sub>                                |                                                                                |     | 130  |      | μA   |

| I <sub>VDDH</sub>                               | V <sub>DDH</sub> = 2.5 V, 1.8 V LDO regulator enabled                          |     | 30   |      | μA   |

| I <sub>VDDL</sub>                               | $V_{\text{DDH}}$ = GND, 1.8 V LDO regulator disabled, $V_{\text{DDL}}$ = 1.8 V |     | 16   |      | μA   |

| I <sub>VIO</sub>                                | V <sub>IO</sub> = 2.5 V                                                        |     | 1    |      | μA   |

| POWER DISSIPATION                               | Reference and reference buffer enabled,                                        |     |      |      |      |

|                                                 | $V_{DDH}$ = 2.5 V, 1.8 V LDO regulator enabled, $V_{IO}$ = 2.5 V               |     |      |      |      |

| CMOS Conversion Data Output                     | 25 pF load on CMOS outputs                                                     |     |      |      |      |

| Operation Mode                                  | f <sub>S</sub> = 1 MSPS, all channels converting                               |     |      |      |      |

|                                                 | V <sub>CC</sub> = +24 V, V <sub>EE</sub> = -24 V                               |     | 878  | 1201 | mW   |

|                                                 | V <sub>CC</sub> = +15 V, V <sub>EE</sub> = -15 V                               |     | 580  |      | mW   |

|                                                 | V <sub>CC</sub> = +8.2 V, V <sub>EE</sub> = -3.2 V                             |     | 346  |      | mW   |

| Acquisition Mode                                | $V_{CC} = +24 \text{ V}, V_{EE} = -24 \text{ V}$                               |     | 457  |      | mW   |

| Nap Mode                                        | $V_{CC} = +24 V, V_{EE} = -24 V$                                               |     | 239  |      | mW   |

| Power-Down Mode                                 | $V_{CC} = +24 V, V_{EE} = -24 V$                                               |     | 1.3  |      | mW   |

| LVDS Conversion Data Output                     | 100 $\Omega$ differential load on LVDS outputs                                 |     |      |      |      |

| Operation Mode                                  | f <sub>S</sub> = 1 MSPS, all channels converting                               |     |      |      |      |

|                                                 | V <sub>CC</sub> = +24 V, V <sub>EE</sub> = -24 V                               |     | 907  | 1228 | mW   |

|                                                 | V <sub>CC</sub> = +15 V, V <sub>EE</sub> = -15 V                               |     | 610  |      | mW   |

|                                                 | $V_{CC} = +8.2 \text{ V}, V_{EE} = -3.2 \text{ V}$                             |     | 375  |      | mW   |

| Acquisition Mode                                | $V_{CC} = +24 \text{ V}, V_{EE} = -24 \text{ V}$                               |     | 482  |      | mW   |

| Nap Mode                                        | $V_{CC} = +24 \text{ V}, V_{EE} = -24 \text{ V}$                               |     | 264  |      | mW   |

| Power-Down Mode                                 | $V_{CC} = +24 \text{ V}, V_{EE} = -24 \text{ V}$                               |     | 1.3  |      | mW   |

#### Table 1. Specifications (Continued)

| Parameter                                    | Test Conditions/Comments | Min | Тур | Max  | Unit |

|----------------------------------------------|--------------------------|-----|-----|------|------|

| OPERATING TEMPERATURE<br>RANGE <sup>23</sup> |                          |     |     |      |      |

| T <sub>MIN</sub>                             |                          | -40 |     |      | °C   |

| T <sub>MAX</sub>                             |                          |     |     | +125 | °C   |

<sup>1</sup> Positive analog-input pin voltage.

<sup>2</sup> Negative analog-input pin voltage.

<sup>3</sup> REFBUF pin voltage scaled by (1/1.024), nominally 4 V.

- <sup>4</sup> REFBUF pin voltage, nominally 4.096 V.

- <sup>5</sup> Common-mode voltage of the positive analog-input pin and the negative analog-input pin.

- <sup>6</sup> Exceeding these limits on any channel may corrupt conversion results on other channels. Driving an analog input greater than V<sub>CC</sub> on any channel up to 10 mA does not affect conversion results on other channels. Driving an analog input less than V<sub>EE</sub> may corrupt conversion results on other channels. Refer to the Analog Input Overdrive Tolerance section for further details. Refer to the Absolute Maximum Ratings section for pin voltage and current limits related to device reliability.

- <sup>7</sup> Positive analog-input pin resistance.

- <sup>8</sup> Negative analog-input pin resistance.

- <sup>9</sup> Positive analog-input pin capacitance.

- <sup>10</sup> Negative analog-input pin capacitance.

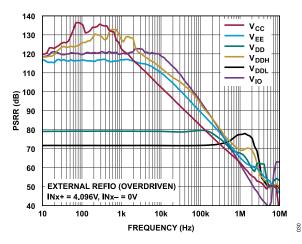

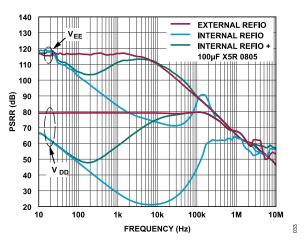

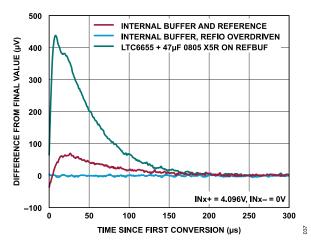

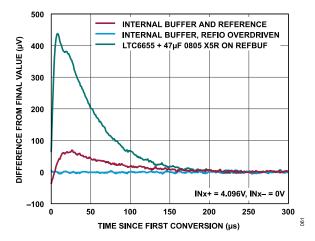

- <sup>11</sup> A plot of the input-referred transition noise vs. the differential input level with SHDR on and off is shown in Figure 18.

- <sup>12</sup> LSB vs. SoftSpan shown in Table 12.

- <sup>13</sup> These specifications are measured while externally supplying V<sub>REFIO</sub> = 4.096 V with the internal band-gap reference powered down. The specifications do not include nominal value or the temperature drift terms associated with the internal band-gap.

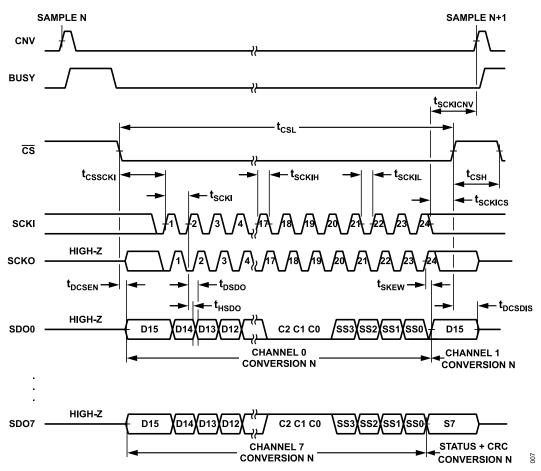

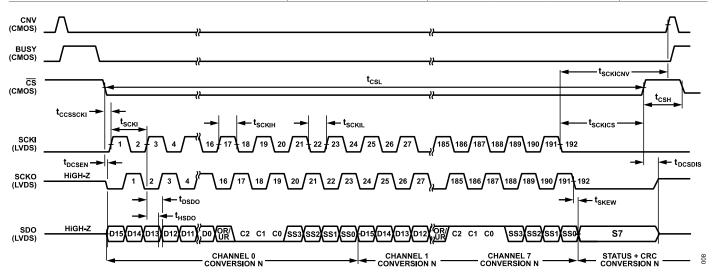

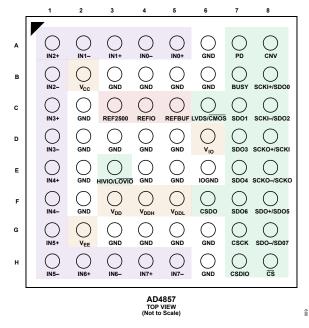

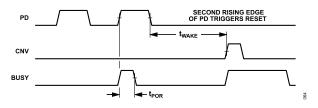

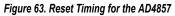

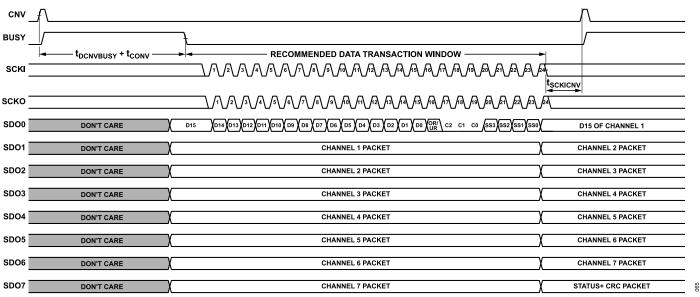

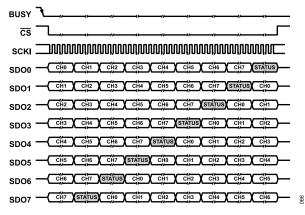

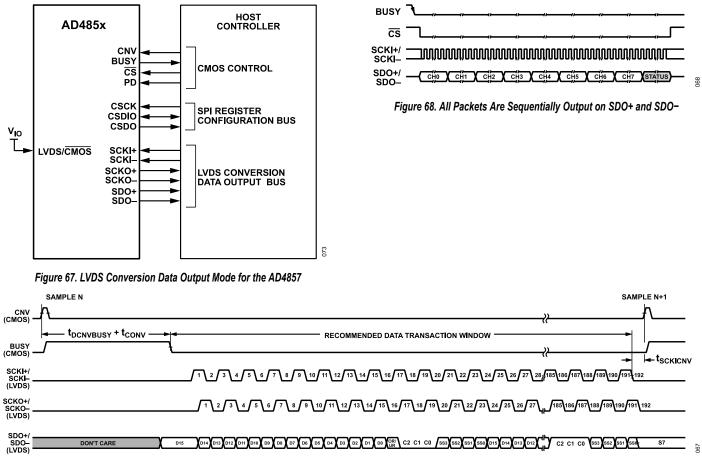

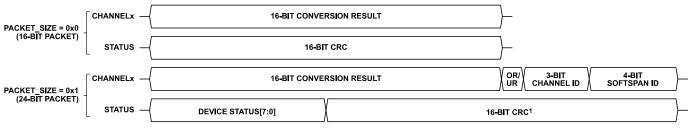

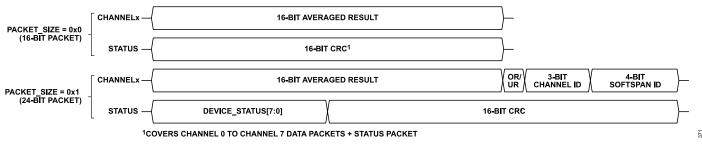

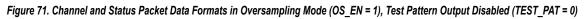

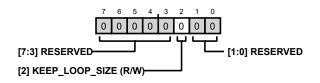

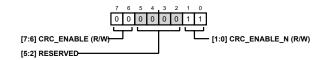

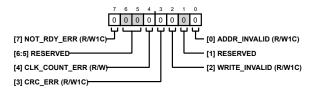

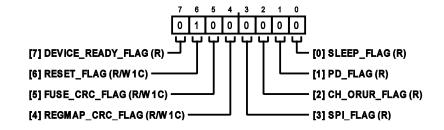

- <sup>14</sup> When REFIO is overdriven, the internal band-gap reference must be disabled using the Device Control Register.