|                                                         |                                | RI       | EVISIO  | ONS        |         |                                                                                           |               |         |        |       |                 |              |             |    |       |      |         |

|---------------------------------------------------------|--------------------------------|----------|---------|------------|---------|-------------------------------------------------------------------------------------------|---------------|---------|--------|-------|-----------------|--------------|-------------|----|-------|------|---------|

| LTR                                                     |                                | DE       | SCRIP   | TION       |         |                                                                                           |               |         |        | [     | DATE (          | YR-M         | O-DA)       |    | AF    | PRO  | /ED     |

|                                                         | utline Y. Ina<br>ument parag   |          |         |            |         |                                                                                           | ro            |         |        |       | 18              | 8-02-0       | 8           |    | C.    | SAF  | FLE     |

|                                                         | r part numbe<br>luantity colui |          |         |            |         |                                                                                           |               | ortatic | on     |       | 18              | 8-05-2       | 2           |    | C.    | SAF  | FLE     |

| C Add typical                                           | limits to test                 | ed paran | neters  | in Ta      | able I. |                                                                                           |               |         |        |       | 24              | -10-1        | 3           |    | J. ES | SCHN | IEYER   |

|                                                         | parameters                     |          | ditions | of V       | DD = 2  | 2.3 V                                                                                     | to 4.5        | V and   | ł      |       |                 |              |             |    |       |      |         |

|                                                         | to VDD to Taument to cu        |          | uirom   | onte       | ro      |                                                                                           |               |         |        |       |                 |              |             |    |       |      |         |

|                                                         |                                |          |         |            |         |                                                                                           |               |         |        |       |                 |              |             |    |       |      |         |

| Prepared in accordance wit<br>Revision Status of Sheets |                                | +.24     |         |            |         |                                                                                           |               |         |        |       |                 |              |             | v  | enuo  | nem  | Drawing |

| REV                                                     |                                |          |         |            |         |                                                                                           |               |         |        |       |                 |              |             |    |       |      |         |

| SHEET                                                   |                                |          |         |            |         |                                                                                           |               |         |        |       |                 |              |             |    |       |      |         |

|                                                         |                                | c c      | С       | С          | С       | С                                                                                         | С             | С       | С      | С     | С               | С            | С           | С  | С     |      |         |

| SHEET 1 2                                               |                                | 5 6      | 7       | 8          | 9       | 10                                                                                        | 11            | 12      | 13     | 14    | 15              | 16           | 17          | 18 | 19    |      |         |

| PMIC N/A                                                | PREPARED BY<br>RICK OFFICER    |          |         |            |         | DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990<br>https://www.dla.mil/landandmaritime |               |         |        |       |                 |              |             |    |       |      |         |

| Original date of drawing                                | CHECKE<br>RAJES                |          | ADIA    |            |         |                                                                                           | TITLE<br>MICF |         |        |       |                 |              |             |    |       |      |         |

| YY-MM-DD<br>12-11-15                                    | APPRO\<br>CHARL                |          |         | F          |         |                                                                                           | 8 CH          | ANN     | IEL, i | 250 I | kSPS            | S SAI        |             |    |       |      | GITAL,  |

| 12-11-13                                                | SIZE                           |          |         |            | DF      |                                                                                           | MON<br>DWG    |         |        | SILI  |                 | 1            |             |    |       |      |         |

|                                                         | A                              |          | -       | <b>236</b> |         |                                                                                           |               |         |        |       | V62             | <u>2/1</u> 2 | <u>26</u> 4 | 5  |       |      |         |

|                                                         | REV                            |          | (       | 2          |         |                                                                                           | PAC           | GE      | 1      | OF    | <sup>:</sup> 19 |              |             |    |       |      |         |

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

#### 1. SCOPE

1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance 14 bit, 8 channel 250 kilo samples per second (kSPS) successive approximation register (SAR) analog to digital converter (ADC) microcircuit, with an operating temperature range of -55°C to +125°C.

1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| <u>V62/12645</u>   | - <u>01</u> | Ť            | Ę.                                                                           |

|--------------------|-------------|--------------|------------------------------------------------------------------------------|

| Drawing            | Device type | Case outline | Lead finish                                                                  |

| number             | (See 1.2.1) | (See 1.2.2)  | (See 1.2.3)                                                                  |

| 1.2.1 Device type. |             |              |                                                                              |

| Device type        | Generic     |              | Circuit function                                                             |

| 01                 | AD7949      |              | channel 250 kSPS successive<br>mation register (SAR) analog to digital<br>er |

1.2.2 <u>Case outlines</u>. The case outlines are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95   | Package style                      |

|----------------|----------------|----------------|------------------------------------|

| X              | 20             | MO-220-VGGD-1  | Lead frame chip scale quad package |

| Y              | 20             | MO-220-WGGD-11 | Lead frame chip scale quad package |

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator               | <u>Material</u>                                                                                                          |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| A<br>B<br>C<br>D<br>E<br>F<br>Z | Hot solder dip<br>Tin-lead plate<br>Gold plate<br>Palladium<br>Gold flash palladium<br>Tin-lead alloy (BGA/CGA)<br>Other |

|                                 |                                                                                                                          |

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 | DWG NO.<br>V62/12645 |

|-----------------------------------------|-----------|--------------------|----------------------|

|                                         |           | REV C              | PAGE 2               |

#### 1.3 Absolute maximum ratings. 1/

| Analog inputs (INx) and common channel inputs (COMx)                           | GND – 0.3 V to VDD + 0.3 V or VDD $\pm$ 130 mA |

|--------------------------------------------------------------------------------|------------------------------------------------|

| Reference input/output (REF)                                                   | GND – 0.3 V to VDD + 0.3 V                     |

| Internal reference output / reference buffer input (REFIN)<br>Supply voltages: | GND – 0.3 V to V <sub>DD</sub> + 0.3 V         |

| Power supply (VDD) and input/output interface digital power (VIO) to GND       | 0.3 V to +7 V                                  |

| VIO to VDD                                                                     | 0.3 V to VDD + 0.3 V                           |

| Data input (DIN), convert input (CNV), serial data clock input (SCK) to GND    | 0.3 V to VIO + 0.3 V                           |

| Serial data output (SDO) to GND                                                | 0.3 V to VIO + 0.3 V                           |

| Junction temperature range (TJ)                                                | 150°C                                          |

| Storage temperature range (TSTG)                                               | 65°C to +150°C                                 |

| Thermal impedance, junction to case ( $\theta$ JC)                             | 4.4°C/W                                        |

| Thermal impedance, junction to ambient ( $\theta_{JA}$ )                       | 47.6°C/W                                       |

### 1.4 Recommended operating conditions. 2/

<sup>2/</sup> Use of this product beyond the manufacturers design rules or stated parameters is done at the user's risk. The manufacturer and/or distributor maintain no responsibility or liability for product used beyond the stated limits.

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 | DWG NO.<br>V62/12645 |  |

|-----------------------------------------|-----------|--------------------|----------------------|--|

|                                         |           | REV C              | PAGE 3               |  |

<sup>&</sup>lt;u>1</u>/ Stresses beyond those listed under "absolute maximum rating" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 2. APPLICABLE DOCUMENTS

JEDEC Solid State Technology Association

JEDEC PUB 95 - Registered and Standard Outlines for Semiconductor Devices

(Copies of these documents are available online at https://www.jedec.org.)

#### 3. REQUIREMENTS

3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

3.4 <u>Design, construction, and physical dimension</u>. The design, construction, and physical dimensions are as specified herein.

3.5 Diagrams.

3.5.1 <u>Case outlines</u>. The case outlines shall be as shown in 1.2.2 and figure 1.

3.5.2 Terminal connections. The terminal connections shall be as shown in figure 2.

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 | DWG NO.<br>V62/12645 |  |

|-----------------------------------------|-----------|--------------------|----------------------|--|

|                                         |           | REV C              | PAGE 4               |  |

| Test Symb                    |     | Conditions<br>VDD = 2.3 V to 5.5 V,<br>VIO = 1.8 V to VDD, | Temperature,<br>TA | Device<br>type | Lin                           | nits                          | Unit              |

|------------------------------|-----|------------------------------------------------------------|--------------------|----------------|-------------------------------|-------------------------------|-------------------|

|                              |     | VREF = VDD,<br>unless otherwise specified                  |                    |                | Min                           | Max                           |                   |

| Resolution                   |     |                                                            | -55°C to +125°C    | 01             | 14                            |                               | Bits              |

| Analog input.                |     |                                                            |                    |                |                               |                               |                   |

| Voltage range                |     | Unipolar mode                                              | -55°C to +125°C    | 01             | 0                             | +VREF                         | V                 |

|                              |     | Bipolar mode                                               |                    |                | -VREF /<br>2                  | +VREF /<br>2                  |                   |

| Absolute input voltage       |     | Positive input, unipolar and bipolar modes                 | -55°C to +125°C    | 01             | -0.1                          | VREF +<br>0.1                 | V                 |

|                              |     | Negative or COM input,<br>unipolar mode                    |                    |                | -0.1                          | +0.1                          |                   |

|                              |     | Negative or COM input, bipolar mode                        |                    |                | V <sub>REF</sub> / 2<br>- 0.1 | V <sub>REF</sub> / 2<br>+ 0.1 |                   |

|                              |     |                                                            |                    |                | VREF / 2 typical              |                               |                   |

| Analog input CMRR            |     | fin = 250 kHz                                              | -55°C to +125°C    | 01             | 68 typical                    |                               | dB                |

| Leakage current              | Ilk | Acquisition phase                                          | +25°C              | 01             | 1 typical                     |                               | nA                |

| Throughput                   |     |                                                            | •                  |                |                               |                               |                   |

| Conversion rate              |     |                                                            |                    |                |                               |                               |                   |

| Full bandwidth <u>2</u> /    | FBW | V <sub>DD</sub> = 4.5 V to 5.5 V                           | -55°C to +125°C    | 01             | 0                             | 250                           | kSPS              |

|                              |     | VDD = 2.3 V to 4.5 V                                       |                    |                | 0                             | 200                           |                   |

| 1/4 bandwidth <u>2</u> /     |     | V <sub>DD</sub> = 4.5 V to 5.5 V                           | -55°C to +125°C    | 01             | 0                             | 62.5                          | kSPS              |

|                              |     | VDD = 2.3 V to 4.5 V                                       |                    |                | 0                             | 50                            |                   |

| Transient response           |     | Full scale step, full bandwidth                            | -55°C to +125°C    | 01             |                               | 1.8                           | μs                |

|                              |     | Full scale step, 1/4 bandwidth                             |                    |                |                               | 14.5                          |                   |

| Accuracy                     |     |                                                            |                    |                |                               |                               |                   |

| No missing codes             | NMC |                                                            | -55°C to +125°C    | 01             | 14                            |                               | Bits              |

| Integral linearity error     | ILE |                                                            | -55°C to +125°C    | 01             | -1                            | +1                            | LSB<br><u>3</u> / |

|                              |     |                                                            |                    |                | ±0.5 t                        | ±0.5 typical                  |                   |

| Differential linearity error | DLE |                                                            | -55°C to +125°C    | 01             | -1                            | +1                            | LSB               |

|                              |     |                                                            |                    |                | ±0.25                         |                               |                   |

## TABLE I. Electrical performance characteristics. 1/

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 | DWG NO.<br>V62/12645 |  |

|-----------------------------------------|-----------|--------------------|----------------------|--|

|                                         |           | REV C              | PAGE 5               |  |

| Test                              | Symbol | ABLE I. <u>Electrical performance chara</u><br>Conditions                                 | Temperature,    | Device | Lir               | nits    | Unit          |

|-----------------------------------|--------|-------------------------------------------------------------------------------------------|-----------------|--------|-------------------|---------|---------------|

|                                   |        | VDD = 2.3 V to 5.5 V,<br>VIO = 1.8 V to VDD,<br>VREF = VDD,<br>unless otherwise specified | ТА              | type   | Min               | Max     | -             |

| Accuracy – continued.             | 1      |                                                                                           |                 |        |                   |         |               |

| Transition noise                  | NT     | REF = VDD = 5 V                                                                           | +25°C           | 01     | 0.1 t             | ypical  | LSB           |

| Gain error <u>4</u> /             | AE     |                                                                                           | -55°C to +125°C | 01     | -5                | +5      | LSB           |

|                                   |        |                                                                                           |                 |        | ±0.51             | typical |               |

| Gain error match                  | AEM    |                                                                                           | -55°C to +125°C | 01     | -1                | +1      | LSB           |

|                                   |        |                                                                                           |                 |        | ±0.21             | typical |               |

| Gain error temperature<br>drift   | ΔΑΕ/ΔΤ |                                                                                           | -55°C to +125°C | 01     | ±1 ty             | /pical  | ppm/<br>°C    |

| Offset error <u>4</u> /           | OE     |                                                                                           | -55°C to +125°C | 01     | ±0.51             | typical | LSB           |

| Offset error match                | OEM    |                                                                                           | -55°C to +125°C | 01     | -1                | +1      | LSB           |

|                                   |        |                                                                                           |                 |        | $\pm 0.2$ typical |         |               |

| Offset error<br>temperature drift | ΔΟΕ/ΔΤ |                                                                                           | -55°C to +125°C | 01     | ±1 typical        |         | ppm/<br>°C    |

| Power supply<br>sensitivity       | PSS    | $V_{DD}$ = 5 V ± 5%                                                                       | -55°C to +125°C | 01     | ±0.2 typical      |         | LSB           |

| AC Accuracy <u>5</u> /            |        |                                                                                           |                 |        |                   |         |               |

| Dynamic range                     | DR     |                                                                                           | -55°C to +125°C | 01     | 85.6              | typical | dB <u>6</u> / |

| Signal to noise                   | SN     | fin = 20 kHz, VREF = 5 V                                                                  | -55°C to +125°C | 01     | 84.5              |         | dB            |

|                                   |        |                                                                                           |                 |        | 85.5              | typical |               |

|                                   |        | fın = 20 kHz,<br>VREF = 4.096 V internal REF                                              |                 |        | 85 ty             | /pical  |               |

|                                   |        | fin = 20 kHz,<br>VREF = 2.5 V internal REF                                                |                 |        | 84 ty             | /pical  |               |

| Signal to noise and distortion    | SINAD  | fin = 20 kHz, VREF = 5 V                                                                  | -55°C to +125°C | 01     | 84                |         | dB            |

| distoluon                         |        |                                                                                           |                 |        | 85 ty             | /pical  |               |

|                                   |        | fin = 20 kHz,<br>VREF = 5 V, -60 dB input                                                 |                 |        | 33.51             | typical |               |

|                                   |        | fin = 20 kHz,<br>VREF = 4.096 V internal REF                                              |                 |        | 85 ty             | /pical  |               |

|                                   |        | fin = 20 kHz,<br>VREF = 2.5 V internal REF                                                |                 |        | 84 ty             | /pical  |               |

TABLE I. Electrical performance characteristics - Continued. 1/

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 | DWG NO.<br>V62/12645 |

|-----------------------------------------|-----------|--------------------|----------------------|

|                                         |           | REV C              | PAGE 6               |

| Test                               | Symbol        | Conditions<br>VDD = 2.3 V to 5.5 V,                              | Temperature,<br>TA | Device<br>type | Lin            | nits         | Unit   |

|------------------------------------|---------------|------------------------------------------------------------------|--------------------|----------------|----------------|--------------|--------|

|                                    |               | VIO = 1.8 V to VDD,<br>VREF = VDD,<br>unless otherwise specified |                    |                | Min            | Max          |        |

| AC Accuracy – continued            | d. <u>5</u> / |                                                                  |                    | 1              |                | I            |        |

| Total harmonic distortion          | THD           | fin = 20 kHz                                                     | -55°C to +125°C    | 01             | -100 t         | ypical       | dB     |

| Spurious free dynamic range        | SFDR          | fin = 20 kHz                                                     | -55°C to +125°C    | 01             | 108 t <u>y</u> | ypical       | dB     |

| Channel to channel crosstalk       | СССТ          | fin = 100 kHz on adjacent channel(s)                             | -55°C to +125°C    | 01             | -125 t         | ypical       | dB     |

| Sampling dynamics                  | •             |                                                                  |                    | 1              |                |              |        |

| -3 dB input bandwidth              |               | Full bandwidth                                                   | -55°C to +125°C    | 01             | 1.7 ty         | /pical       | MHz    |

|                                    |               | 1/4 bandwidth                                                    |                    |                | 0.425          | typical      |        |

| Aperature delay                    |               | V <sub>DD</sub> = 5 V                                            | -55°C to +125°C    | 01             | 2.5 ty         | /pical       | ns     |

| Internal reference                 |               |                                                                  |                    | •              |                |              |        |

| REF output voltage                 |               | 2.5 V                                                            | +25°C              | 01             | 2.490          | 2.510        | V      |

|                                    |               |                                                                  |                    |                | 2.500          | typical      |        |

|                                    |               | 4.096 V                                                          |                    |                | 4.086          | 4.106        |        |

|                                    |               |                                                                  |                    |                | 4.096          | typical      |        |

| REFIN output <u>7</u> /<br>voltage |               | 2.5 V                                                            | +25°C              | 01             | 1.2 ty         | /pical       | V      |

| voltage                            |               | 4.096 V                                                          |                    |                | 2.3 ty         | /pical       |        |

| REF output current                 |               |                                                                  | -55°C to +125°C    | 01             | ±300 f         | typical      | μA     |

| Temperature drift                  |               |                                                                  | -55°C to +125°C    | 01             | ±10 t          | ypical       | ppm/°C |

| Line regulation                    | VRLINE        | VDD = 5 V ± 5%                                                   | -55°C to +125°C    | 01             | ±15 t          | ypical       | ppm/V  |

| Long term drift                    |               | 1000 hours                                                       | -55°C to +125°C    | 01             | 50 ty          | rpical       | ppm    |

| Turn on settling time              | ton           | CREF = 10 μF                                                     | -55°C to +125°C    | 01             | 5 ty           | oical        | ms     |

| External reference                 |               |                                                                  |                    |                |                |              |        |

| Voltage reference                  |               | REF input                                                        | -55°C to +125°C    | 01             | 0.5            | VDD<br>+ 0.3 | V      |

|                                    |               | REFIN input (buffered)                                           |                    |                | 0.5            | Vdd<br>- 0.5 |        |

| Current drain                      |               | 250 kSPS, REF = 5 V                                              | -55°C to +125°C    | 01             | 50 ty          | pical        | μA     |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/12645 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 7    |

| Test                                    | SymbolConditionsTemperature,VDD = 2.3 V to 5.5 V,TAVIO = 1.8 V to VDD, |                                           | Device<br>type  | Lin | nits         | Unit          |           |

|-----------------------------------------|------------------------------------------------------------------------|-------------------------------------------|-----------------|-----|--------------|---------------|-----------|

|                                         |                                                                        | VREF = VDD,<br>unless otherwise specified |                 |     | Min          | Max           |           |

| Temperature sensor                      |                                                                        |                                           |                 |     |              |               |           |

| Output voltage <u>8</u> /               | Vout                                                                   |                                           | +25°C           | 01  | 283 t        | ypical        | mV        |

| Temperature sensitivity                 |                                                                        |                                           | -55°C to +125°C | 01  | 1 ty         | pical         | mV/<br>°C |

| Digital inputs                          |                                                                        |                                           |                 | I   | <b></b>      |               |           |

| Input low voltage                       | VIL                                                                    |                                           | -55°C to +125°C | 01  | -0.3         | +0.3 x<br>VIO | V         |

| Input high voltage                      | Viн                                                                    |                                           | -55°C to +125°C | 01  | 0.7 x<br>Vio | VIO +<br>0.3  | V         |

| Input low current                       | lı∟                                                                    |                                           | -55°C to +125°C | 01  | -1           | +1            | μA        |

| Input high current                      | Ін                                                                     |                                           | -55°C to +125°C | 01  | -1           | +1            | μA        |

| Digital outputs                         |                                                                        | I                                         |                 |     |              |               | 1         |

| Data format <u>9</u> /                  |                                                                        |                                           |                 |     |              |               |           |

| Pipeline delay <u>10</u> /              |                                                                        |                                           |                 |     |              |               |           |

| Output low voltage                      | Vol                                                                    | ISINK = +500 μA                           | -55°C to +125°C | 01  |              | 0.4           | V         |

| Output high voltage                     | Vон                                                                    | ISOURCE = -500 μA                         | -55°C to +125°C | 01  | VIO - 3      |               | V         |

| Power supplies                          |                                                                        |                                           |                 |     |              |               |           |

| Power supply voltage                    | Vdd                                                                    | Specified performance                     | -55°C to +125°C | 01  | 2.3          | 5.5           | V         |

| Input/output interface<br>digital power | Vio                                                                    | Specified performance                     | -55°C to +125°C | 01  | 2.3          | Vdd<br>+ 0.3  | V         |

|                                         |                                                                        | Operating range                           |                 |     | 1.8          | VDD<br>+ 0.3  |           |

| Standby <u>11/ 12/</u><br>current       | ISB                                                                    | VDD and VIO = 5 V                         | +25°C           | 01  | 50 ty        | pical         | nA        |

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |  |

|-----------------------|------|-----------|-----------|--|

|                       | A    | 16236     | V62/12645 |  |

| COLUMBUS, OHIO        |      | REV C     | PAGE 8    |  |

| Test                                    | Symbol | Conditions<br>VDD = 2.3 V to 5.5 V,<br>VIO = 1.8 V to VDD, | Temperature,<br>TA | Device<br>type | Lin    | nits   | Unit |  |

|-----------------------------------------|--------|------------------------------------------------------------|--------------------|----------------|--------|--------|------|--|

|                                         |        | VREF = VDD,<br>unless otherwise specified                  |                    |                | Min    | Max    |      |  |

| Power supplies – continu                | ued.   |                                                            |                    |                |        |        | 1    |  |

| Power dissipation                       | PD     | VDD = 2.5 V, 100 SPS throughput                            | -55°C to +125°C    | 01             | 1.5 ty | ypical | μW   |  |

|                                         |        | VDD = 2.5 V, 100 kSPS throughput                           |                    |                |        | 2.0    | mW   |  |

|                                         |        |                                                            |                    |                | 1.45 t | ypical |      |  |

|                                         |        | V <sub>DD</sub> = 2.5 V, 200 kSPS throughput               | -                  |                |        | 4.0    |      |  |

|                                         |        |                                                            |                    |                | 2.9 ty | ypical |      |  |

|                                         |        | VDD = 5 V, 250 kSPS throughput                             |                    |                |        | 12.5   |      |  |

|                                         |        |                                                            |                    |                | 10.8 t | ypical |      |  |

|                                         |        | VDD = 5 V, 250 kSPS throughput                             |                    |                |        |        | 15.5 |  |

|                                         |        | with internal reference                                    |                    |                | 13.5 t | ypical |      |  |

| Energy conversion                       |        |                                                            | -55°C to +125°C    | 01             | 50 ty  | /pical | nJ   |  |

| Temperature range specified performance |        |                                                            |                    | 01             | -55    | +125   | °C   |  |

TABLE I. Electrical performance characteristics - Continued. 1/

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 | DWG NO.<br>V62/12645 |

|-----------------------------------------|-----------|--------------------|----------------------|

|                                         |           | REV C              | PAGE 9               |

|                                                          | T.           | ABLE I. Electrical performance chara                                     | cteristics - Continued. | <u>1</u> /     |              |      |

|----------------------------------------------------------|--------------|--------------------------------------------------------------------------|-------------------------|----------------|--------------|------|

| Test                                                     | Symbol       | Conditions<br>VDD = 4.5 V to 5.5 V,                                      | Temperature,<br>TA      | Device<br>type | Lin          | nits |

|                                                          |              | VIO = 1.8 V to VDD,<br>see figures 3 and 4<br>unless otherwise specified |                         |                | Min          | Max  |

| Conversion time:<br>CNV rising edge to<br>data available | tCONV        |                                                                          | -55°C to +125°C         | 01             |              | 2.2  |

| Acquisition time                                         | tACQ         |                                                                          | -55°C to +125°C         | 01             | 1.8          |      |

| Time between conversion                                  | tCYC         |                                                                          | -55°C to +125°C         | 01             | 4.0          |      |

| Data write/read during conversion                        | tDATA        |                                                                          | -55°C to +125°C         | 01             |              | 1.0  |

| CNV pulse width                                          | <b>tCNVH</b> |                                                                          | -55°C to +125°C         | 01             | 10           |      |

| SCK period                                               | tSCK         |                                                                          | -55°C to +125°C         | 01             | tDSDO<br>+ 2 |      |

| SCK low time                                             | tSCKL        |                                                                          | -55°C to +125°C         | 01             | 11           |      |

| SCK high time                                            | tSCKH        |                                                                          | -55°C to +125°C         | 01             | 11           |      |

| SCK falling edge to data remains valid                   | tHSDO        |                                                                          | -55°C to +125°C         | 01             | 4            |      |

| SCK falling edge to data valid delay                     | tDSDO        | VIO above 2.7 V                                                          | -55°C to +125°C         | 01             |              | 18   |

|                                                          |              | VIO above 2.3 V                                                          |                         |                |              | 23   |

|                                                          |              | VIO above 1.8 V                                                          |                         |                |              | 28   |

| CNV low to SDO D15<br>MSB valid                          | tEN          | VIO above 2.7 V                                                          | -55°C to +125°C         | 01             |              | 18   |

|                                                          |              | VIO above 2.3 V                                                          |                         |                |              | 22   |

|                                                          |              | VIO above 1.8 V                                                          |                         |                |              | 25   |

| CNV high or last SCK                                     | tDIS         |                                                                          | -55°C to +125°C         | 01             |              | 32   |

. . . .. ~ ... . .

Unit

μs

μs

μs

μs

ns

See footnotes at end of table.

falling edge to SDO high impedance

CNV low to SCK rising

DIN valid setup time

DIN valid hold time

from SCK rising edge

from SCK rising edge

edge

**tCLSCK**

tsdin

thdin

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/12645 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 10   |

-55°C to +125°C

-55°C to +125°C

-55°C to +125°C

01

01

01

10

5

5

| Test                                                          | Symbol        | Conditions<br>VDD = 2.3 V to 4.5 V,                                      | Temperature,<br>TA | Device<br>type | Lin          | nits | Unit |

|---------------------------------------------------------------|---------------|--------------------------------------------------------------------------|--------------------|----------------|--------------|------|------|

|                                                               |               | VIO = 1.8 V to VDD,<br>see figures 3 and 4<br>unless otherwise specified |                    |                | Min          | Max  |      |

| Conversion time:<br>CNV rising edge to<br>data available      | tCONV         |                                                                          | -55°C to +125°C    | 01             |              | 3.2  | μs   |

| Acquisition time                                              | tACQ          |                                                                          | -55°C to +125°C    | 01             | 1.8          |      | μs   |

| Time between conversion                                       | tCYC          |                                                                          | -55°C to +125°C    | 01             | 5.0          |      | μs   |

| Data write/read during conversion                             | tDATA         |                                                                          | -55°C to +125°C    | 01             |              | 1.2  | μs   |

| CNV pulse width                                               | <b>t</b> CNVH |                                                                          | -55°C to +125°C    | 01             | 10           |      | ns   |

| SCK period                                                    | tSCK          |                                                                          | -55°C to +125°C    | 01             | tDSDO<br>+ 2 |      | ns   |

| SCK low time                                                  | tSCKL         |                                                                          | -55°C to +125°C    | 01             | 12           |      | ns   |

| SCK high time                                                 | tSCKH         |                                                                          | -55°C to +125°C    | 01             | 12           |      | ns   |

| SCK falling edge to<br>data remains valid                     | tHSDO         |                                                                          | -55°C to +125°C    | 01             | 5            |      | ns   |

| SCK falling edge to data valid delay                          | tDSDO         | ViO above 3 V                                                            | -55°C to +125°C    | 01             |              | 24   | ns   |

|                                                               |               | ViO above 2.7 V                                                          |                    |                |              | 30   |      |

|                                                               |               | VIO above 2.3 V                                                          |                    |                |              | 38   |      |

|                                                               |               | VIO above 1.8 V                                                          |                    |                |              | 48   |      |

| CNV low to SDO D15<br>MSB valid                               | tEN           | VIO above 3 V                                                            | -55°C to +125°C    | 01             |              | 21   | ns   |

|                                                               |               | VIO above 2.7 V                                                          |                    |                |              | 27   |      |

|                                                               |               | VIO above 2.3 V                                                          |                    |                |              | 35   |      |

|                                                               |               | VIO above 1.8 V                                                          |                    |                |              | 45   |      |

| CNV high or last SCK<br>falling edge to SDO<br>high impedance | tDIS          |                                                                          | -55°C to +125°C    | 01             |              | 50   | ns   |

| CNV low to SCK rising edge                                    | <b>tCLSCK</b> |                                                                          | -55°C to +125°C    | 01             | 10           |      | ns   |

| DIN valid setup time<br>from SCK rising edge                  | tSDIN         |                                                                          | -55°C to +125°C    | 01             | 5            |      | ns   |

| DIN valid hold time<br>from SCK rising edge                   | thdin         |                                                                          | -55°C to +125°C    | 01             | 5            |      | ns   |

TABLE I. Electrical performance characteristics - Continued. 1/

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/12645 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 11   |

- <u>1</u>/ Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- 2/ The bandwidth is set in the configuration register.

- $\underline{3}$ / LSB means least significant bit. With the 5 V input range, one LSB = 305  $\mu$ V.

- 4/ These specifications include full temperature range variation but, not the error contribution from the external reference.

- 5/ Unless otherwise specified, VDD = 5 V.

- 6/ Unless otherwise specified, all specifications expressed in decibels are referred to a full scale input FSR and tested with an input signal at 0.5 dB below full scale.

- $\underline{7}$  This is the output from the internal band gap.

- 8/ The output voltage is internal and present on a dedicated multiplexer input.

- <u>9</u>/ Unipolar mode: serial 14 bit straight binary. Bipolar mode: serial 14 bit two's complement.

- <u>10</u>/ Conversion results available immediately after completed conversion.

- 11/ With digital inputs forced to VIO or GND as required.

- 12/ During acquisition phase.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/12645 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 12   |

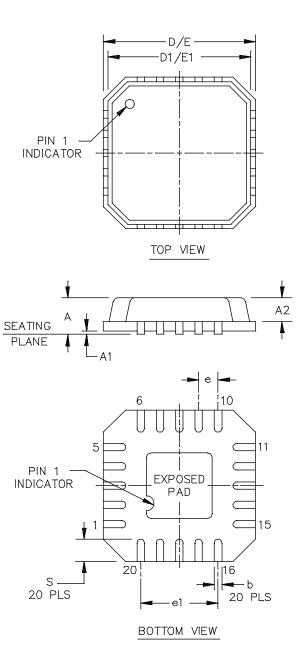

Case X

FIGURE 1. Case outlines.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/12645 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 13   |

Case X – continued.

|        | Dimensions |      |             |      |  |

|--------|------------|------|-------------|------|--|

| Symbol | Inch       | nes  | Millimeters |      |  |

|        | Min        | Max  | Min         | Max  |  |

| А      | .031       | .039 | 0.80        | 1.00 |  |

| A1     | .0007      | .001 | 0.02        | 0.05 |  |

| A2     | .025       | .031 | 0.65        | 0.80 |  |

| b      | .007       | .011 | 0.18        | 0.30 |  |

| D/E    | .157       | BSC  | 4.00 BSC    |      |  |

| D1/E1  | .147       | BSC  | 3.75        | BSC  |  |

| е      | .019 BSC   |      | 0.50        | BSC  |  |

| e1     | .092       | .104 | 2.35        | 2.65 |  |

| s      | .011       | .019 | 0.30        | 0.50 |  |

- NOTES:1. Controlling dimensions are millimeter, inch dimensions are given for reference only.2. Falls within reference to JEDEC MO-220-VGGD-1.

FIGURE 1. Case outlines - Continued.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/12645 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 14   |

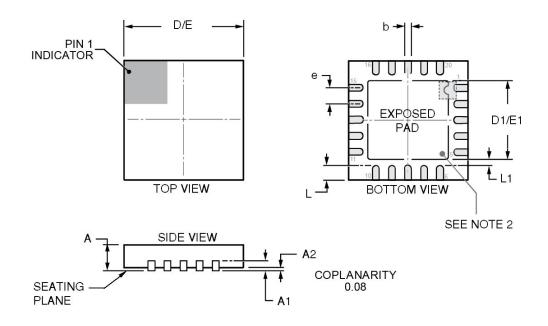

|        | Dimensions |           |         |          |             |         |  |

|--------|------------|-----------|---------|----------|-------------|---------|--|

| Symbol |            | Inches    |         |          | Millimeters |         |  |

|        | Minimum    | Nominal   | Maximum | Minimum  | Nominal     | Maximum |  |

| А      | .0275      | .0295     | .0314   | 0.70     | 0.75        | 0.80    |  |

| A1     | .0078 REF  |           |         | 0.20 REF |             |         |  |

| A2     |            | .0007 NOM | .0019   |          | 0.02 NOM    | 0.05    |  |

| b      | .0078      | .0098     | .0118   | 0.20     | 0.25        | 0.30    |  |

| D/E    | .1535      | .1574     | .1614   | 3.90     | 4.00        | 4.10    |  |

| D1/E1  | .0925      | .0984     | .1043   | 2.35     | 2.50        | 2.65    |  |

| е      | .0196 BSC  |           |         |          | 0.50 BSC    |         |  |

| L      | .0118      | .0157     | .0196   | 0.30     | 0.40        | 0.50    |  |

| L1     | .0098      |           |         | 0.25     |             |         |  |

NOTES:

1. Controlling dimensions are millimeter, inch dimensions are given for reference only.

2. For proper connection of the exposed pad. Refer to the pin configuration and function descriptions section of the manufacturer's datasheet.

3. Falls within reference to JEDEC MO-220-WGGD-11.

FIGURE 1. Case outlines - Continued.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/12645 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 15   |

| <b>F</b>        |                    |  |

|-----------------|--------------------|--|

| Device type     | 01                 |  |

| Case outlines   | X and Y            |  |

| Terminal number | Terminal<br>symbol |  |

| 1               | VDD                |  |

| 2               | REF                |  |

| 3               | REFIN              |  |

| 4               | GND                |  |

| 5               | GND                |  |

| 6               | IN 4               |  |

| 7               | IN 5               |  |

| 8               | IN 6               |  |

| 9               | IN 7               |  |

| 10              | COMM               |  |

| 11              | CNV                |  |

| 12              | DIN                |  |

| 13              | SCK                |  |

| 14              | SD0                |  |

| 15              | Vio                |  |

| 16              | IN 0               |  |

| 17              | IN 1               |  |

| 18              | IN 2               |  |

| 19              | IN 3               |  |

| 20              | VDD                |  |

NOTE: The exposed pad is not connected internally. For increased reliability of the solder joints, it is recommended that the pad be soldered to the system ground plane.

FIGURE 2. Terminal connections.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/12645 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 16   |

| Terminal<br>symbol | Туре                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VDD                | Power                   | Power supply. Nominally 2.5 V to 5.5 V when using an external reference and decoupled with 10 $\mu F$ and 100 nF capacitors. When using the internal reference for 2.5 V output, the minimum should be 3.0 V. When using the internal reference for 4.096 V output, the minimum should be 4.5 V.                                                                                                                                                                                                                                                             |  |

| REF                | Analog input/<br>output | Reference input/output. When the internal reference is enabled, this pin produce selectable system reference = 2.5 V or 4.096 V. When the internal reference is disabled and the buffer is enabled, REF produces buffered version of the voltage present on the REFIN pin (4.096 V maximum), useful when using low cost, low power references. For improved drift performance, connect a precision reference to REF (0.5 V to VDD). For any reference method, this pin needs decoupling with an external 10 capacitor connected as close to REF as possible. |  |

| REFIN              | Analog input/<br>output | Internal reference output/ reference buffer input.<br>When using the internal reference, the internal unbuffered reference voltage is<br>present and needs decoupling with a 0.1 $\mu$ F capacitor.<br>When using the internal reference buffer, apply a source between 0.5 V and                                                                                                                                                                                                                                                                            |  |

|                    | _                       | 4.096 V that is buffered to the REF pin as described above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| GND                | Power                   | Power supply ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| IN4 to IN7         | Analog input            | Channel 4 through channel 7 analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| СОМ                | Analog input            | Common channel input. All input channels; IN[7:0], can be referenced to a common mode point of 0 V or VREF / 2 V.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| CNV                | Digital input           | Convert input. On the rising edge, CNV initiates the conversion.<br>During conversion, if CNV is held high, the busy indicator is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| DIN                | Digital input           | Data input. This pin is used for writing to the 14 bits configuration register.<br>The configuration register can be written to during and after conversion.                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| SCK                | Digital input           | Serial data clock input. This input is used to clock out the data on SDO and clock in data on DIN in an MSB first fashion.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| SDO                | Digital output          | Serial data output. The conversion result is output on this pin, synchronized to SCK. In unipolar modes, conversion results are straight binary; in bipolar modes, conversion results are twos complement.                                                                                                                                                                                                                                                                                                                                                   |  |

| Vio                | Power                   | Input/output interface digital power. Nominally at the same supply as the host interface (1.8 V, 2.5 V, 3 V, or 5 V).                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| IN0 to IN3         | Analog input            | Channel 0 through channel 3 analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Exposed pad        | No connection           | The exposed pad is not connected internally. For increased reliability of the solder joints, it is recommended that the pad be soldered to the system ground plane.                                                                                                                                                                                                                                                                                                                                                                                          |  |

FIGURE 2. <u>Terminal connections</u> - continued.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/12645 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 17   |

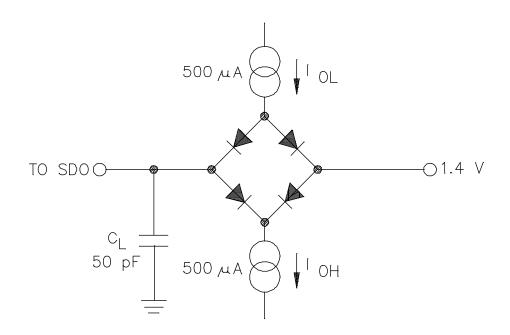

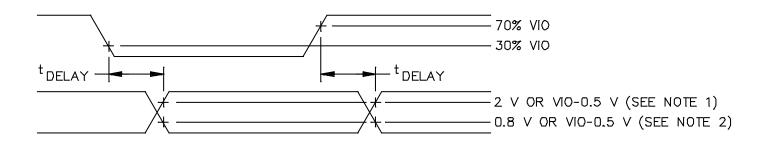

FIGURE 3. Load circuit for digital interface timing.

NOTES:

- 1. 2 V if VIO above 2.5 V, VIO 0.5 V if VIO below 2.5 V.

- 2. 0.8 V if VIO above 2.5 V, 0.5 V if VIO below 2.5 V.

FIGURE 4. Voltage levels for timing.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/12645 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 18   |

#### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

#### 5. PREPARATION FOR DELIVERY

5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

#### 6. NOTES

6.1 <u>ESDS</u>. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <u>https://landandmaritimeapps.dla.mil/programs/smcr/</u>.

| Vendor item drawing<br>administrative control<br>number <u>1</u> / | Device<br>manufacturer<br>CAGE code | Transportation<br>mode and<br>quantity | Vendor part number |

|--------------------------------------------------------------------|-------------------------------------|----------------------------------------|--------------------|

| V62/12645-01XE                                                     | <u>2</u> /                          |                                        | AD7949SCPZ-EP-RL7  |

| V62/12645-01YE                                                     | 24355                               | Reel, 1500 units                       | AD7949SCPZ-EP-RL7  |

| V62/12645-01YE                                                     | 24355                               | Reel, 250 units                        | AD7949SCPZ-EP-R2   |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

2/ Not available from an approved source of supply.

#### CAGE code

24355

#### Source of supply

Analog Devices Route 1 Industrial Park P.O. Box 9106 Norwood, MA 02062 Point of contact: 20 Alpha Road Chelmsford, MA 01824-4123

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/12645 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 19   |

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

AD7949SCPZ-EP-RL7 AD7949SCPZ-EP-R2