# Product Document

Published by ams OSRAM Group

### **TMD3702VC** Narrow ALS, Color and Proximity Sensor Module

#### **General Description**

The TMD3702VC features proximity detection, color sense (RGBC+IR), and digital ambient light sensing (ALS). The extremely narrow 1.44mm module incorporates an IR VCSEL and factory calibrated VCSEL driver. The proximity detection feature provides object detection (e.g. mobile device screen to user's ear) by photodiode detection of reflected IR energy (sourced by the integrated VCSEL). Detect/release events are interrupt driven, and occur when proximity result crosses upper and/or lower threshold settings. The proximity engine features a wide range offset adjustment to compensate for unwanted IR energy reflection at the sensor. Proximity results are further improved by automatic ambient light subtraction. The color photodiodes have UV and IR blocking filters and dedicated data converters producing 16-bit data. This architecture allows applications to accurately measure ambient light which enables devices to calculate illuminance and color temperature to control display backlight and chromaticity.

Ordering Information and Content Guide appear at end of datasheet.

#### **Key Benefits & Features**

The benefits and features of TMD3702VC, Narrow ALS, Color and Proximity Sensor Module are listed below:

Figure 1: Added Value of Using TMD3702VC

| Benefits                                  | Features                                                                                                                                                                                                                                      |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single device integrated optical solution | <ul> <li>ALS + color + proximity</li> <li>1.44mm x 2.84mm x 0.65mm module</li> <li>±48° field of view</li> <li>Integrated 940nm IR VCSEL</li> <li>Power management features</li> <li>I<sup>2</sup>C fast mode interface compatible</li> </ul> |

| Accurate ambient light sensing            | <ul> <li>5 channels (RGBC + IR)</li> <li>UV / IR blocking filters</li> <li>Programmable gain and integration time</li> </ul>                                                                                                                  |

| Reduced power consumption                 | <ul> <li>1.8V power supply with 1.8V I<sup>2</sup>C bus</li> <li>Sleep mode</li> </ul>                                                                                                                                                        |

#### Applications

The TMD3702VC applications include:

- Ambient light sensing

- Proximity sensing

- Mobile phone touch screen disable

- Color temperature measurement to assist display, backlight, camera, and flash control

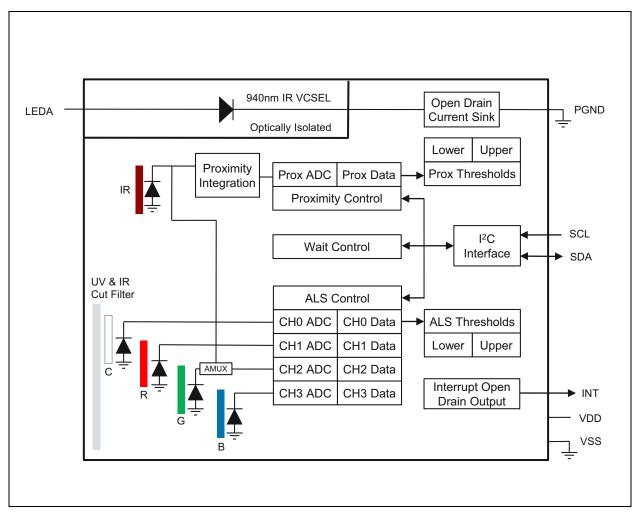

#### **Block Diagram**

The functional blocks of this device are shown below:

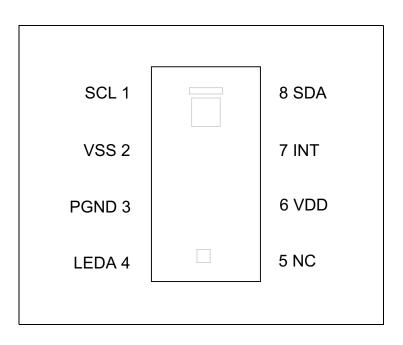

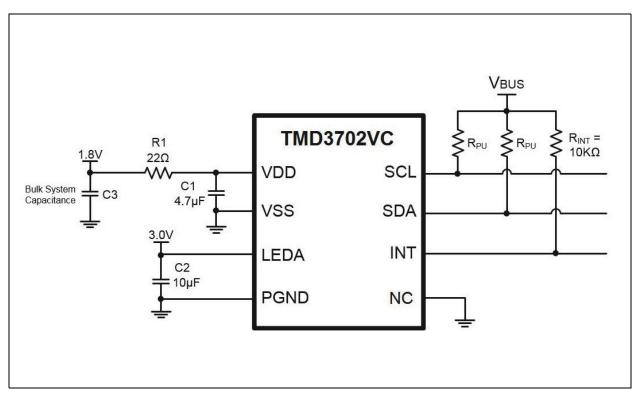

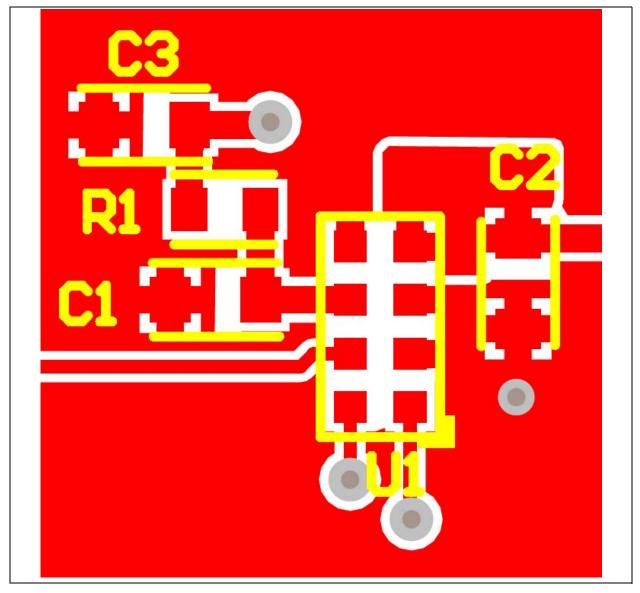

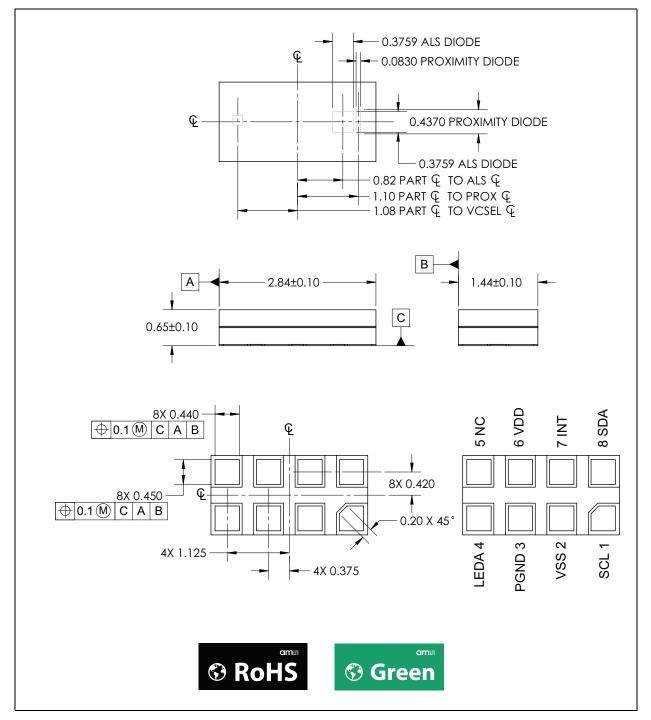

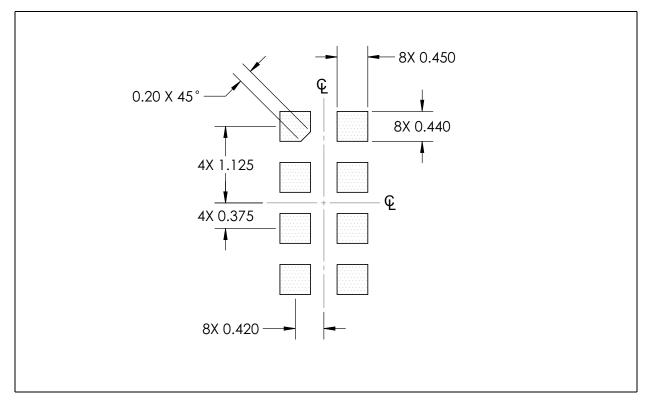

### Pin Assignment

Figure 3: Pin Diagram

#### Figure 4: Pin Description

| Pin Number | Pin Name | Description                                                                                              |

|------------|----------|----------------------------------------------------------------------------------------------------------|

| 1          | SCL      | I <sup>2</sup> C serial clock input terminal                                                             |

| 2          | VSS      | Ground. All voltages are referenced to VSS/PGND and both pins must                                       |

| 3          | PGND     | be connected to ground.                                                                                  |

| 4          | LEDA     | VCSEL anode                                                                                              |

| 5          | NC       | No connect. No internal electrical connection. For improved device<br>ESD protection, connect to ground. |

| 6          | VDD      | Supply voltage (1.8V)                                                                                    |

| 7          | INT      | Interrupt. Open drain output (active low)                                                                |

| 8          | SDA      | I <sup>2</sup> C serial data I/O terminal                                                                |

### Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other condition beyond those indicated under Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Figure 5: Absolute Maximum Ratings

| Symbol             | Parameter                             | Min   | Max      | Units | Comments                                                                                                                                                                                                                                            |

|--------------------|---------------------------------------|-------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD                | Supply voltage to ground              | -0.3  | -0.3 2.0 |       |                                                                                                                                                                                                                                                     |

| LEDA               | VCSEL voltage to PGND                 | -0.3  | 3.6      | V     |                                                                                                                                                                                                                                                     |

| V <sub>IO</sub>    | Digital I/O terminal voltage          | -0.3  | 3.6      | V     |                                                                                                                                                                                                                                                     |

| I <sub>IO</sub>    | Digital output terminal current       | -1    | 20       | mA    |                                                                                                                                                                                                                                                     |

| I <sub>VCSEL</sub> | VCSEL current                         |       | 30       | mA    |                                                                                                                                                                                                                                                     |

| I <sub>SCR</sub>   | Input current<br>(latch-up immunity)  | ± 100 |          | mA    | Class II JEDEC JESD78D                                                                                                                                                                                                                              |

| ESD <sub>HBM</sub> | HBM electrostatic discharge           | ± 2   | ± 2000   |       | JS-001-2014                                                                                                                                                                                                                                         |

| ESD <sub>CDM</sub> | CDM electrostatic discharge           | ± 5   | 500      | V     | JEDEC JESD22-C101F                                                                                                                                                                                                                                  |

| T <sub>STRG</sub>  | Storage temperature range             | -40   | 85       | °C    |                                                                                                                                                                                                                                                     |

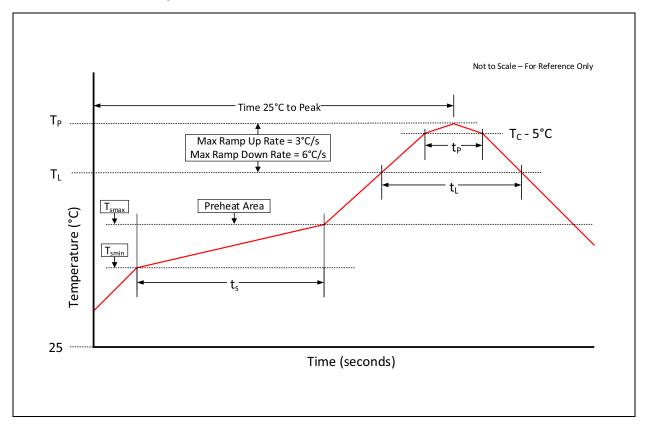

| T <sub>BODY</sub>  | Package body temperature              | 260   |          | °C    | IPC/JEDEC J-STD-020<br>The reflow peak soldering<br>temperature (body temperature)<br>is specified according to<br>IPC/JEDEC J-STD-020<br>"Moisture/Reflow Sensitivity<br>Classification for Non-hermetic<br>Solid State Surface Mount<br>Devices." |

| RH <sub>NC</sub>   | Relative humidity<br>(non-condensing) | 5     | 85       | %     |                                                                                                                                                                                                                                                     |

| P <sub>DISS</sub>  | Power dissipation                     |       | 200      | mW    | Average power dissipation over a 1 second period                                                                                                                                                                                                    |

### **Electrical Characteristics**

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 6:

**Recommended Operating Conditions**

| Symbol            | Parameter                                      | Min | Тур | Max | Units |

|-------------------|------------------------------------------------|-----|-----|-----|-------|

| VDD               | Supply voltage                                 | 1.7 | 1.8 | 2.0 | V     |

| V <sub>LEDA</sub> | Supply voltage to VCSEL anode (PLDRIVE = 19mA) | 3.0 | 3.3 | 3.6 | V     |

| LEDA              | Supply voltage to VCSEL anode (PLDRIVE = 14mA) | 2.8 | 3.3 | 3.6 | V     |

| P <sub>DISS</sub> | Average power dissipation <sup>(1)</sup>       |     |     | 100 | mW    |

| T <sub>A</sub>    | Operating ambient temperature                  | -30 |     | 85  | °C    |

#### Note(s):

1. Power dissipation averaged over 1 second period.

Figure 7:

Operating Characteristics ( $V_{DD} = 1.8V$ ,  $T_A = 25^{\circ}C$  unless otherwise noted)

| Symbol              | Parameter                                                        | Conditions                                            | Min  | Тур  | Max  | Unit |

|---------------------|------------------------------------------------------------------|-------------------------------------------------------|------|------|------|------|

| f <sub>OSC</sub>    | Oscillator frequency                                             |                                                       |      | 8.1  |      | MHz  |

|                     |                                                                  | Active ALS State<br>(PON=AEN=1, PEN=0) <sup>(2)</sup> |      | 105  | 150  |      |

| I <sub>DD</sub>     | Supply current <sup>(1)</sup>                                    | Idle State<br>(PON=1, AEN=PEN=0) <sup>(3)</sup> 35    |      |      | μΑ   |      |

|                     |                                                                  | Sleep State <sup>(4)</sup>                            |      | 0.54 |      |      |

| V <sub>OL</sub>     | INT, SDA output low voltage                                      | 6mA sink current                                      |      |      | 0.6  | V    |

| I <sub>LEAK</sub>   | Leakage current, SDA,SCL,INT                                     |                                                       | -5   |      | 5    | μΑ   |

| V <sub>IH</sub>     | SCL, SDA input high voltage <sup>(5)</sup>                       |                                                       | 1.26 |      |      | V    |

| V <sub>IL</sub>     | SCL, SDA input low voltage                                       |                                                       |      |      | 0.54 | V    |

| T <sub>Active</sub> | Time from power-on to ready to receive I <sup>2</sup> C commands |                                                       |      | 1.5  |      | ms   |

#### Note(s):

1. Values are shown at the VDD pin and do not include current through the IR VCSEL.

2. This parameter indicates the supply current during periods of ALS integration. If Wait is enabled (WEN=1), the supply current is lower during the Wait period.

3. Idle state occurs when PON=1 and all functions are not enabled.

4. Sleep state occurs when PON = 0 and  $I^2C$  bus is idle. If Sleep state has been entered as the result of operational flow, SAI = 1, PON will remain high.

5. Digital pins: SDA, SCL, INT are tolerant to a communication voltage up to 3.0V.

## Figure 8: Optical Characteristics ( $V_{DD} = 1.8V$ , $T_A = 25^{\circ}C$ unless otherwise noted)

| Parameter                | Conditions                                               | Min  | Тур  | Max  | Unit                            |  |  |  |

|--------------------------|----------------------------------------------------------|------|------|------|---------------------------------|--|--|--|

|                          | Clear Channel                                            |      |      |      |                                 |  |  |  |

|                          | $\lambda_D = 465 \text{ nm LED}, 53.8 \mu\text{W/cm}^2$  |      | 44.8 |      |                                 |  |  |  |

| Re                       | $\lambda_D = 530 \text{ nm LED}, 43.9 \mu \text{W/cm}^2$ |      | 86.0 |      | count/                          |  |  |  |

| Irradiance responsivity  | $\lambda_D = 620 \text{ nm LED}, 37.5 \mu \text{W/cm}^2$ |      | 104  |      | (µW/cm <sup>2</sup> )           |  |  |  |

| Settings:<br>AGAIN = 16x | Warm White LED, 45.6µW/cm <sup>2</sup>                   |      | 83.2 |      |                                 |  |  |  |

| ATIME = 150ms            | Warm White LED, 45.6µW/cm <sup>2</sup>                   | 3323 | 3792 | 4361 | counts                          |  |  |  |

|                          | IR Channel                                               |      |      |      |                                 |  |  |  |

|                          | $\lambda_D = 940 \text{ nm LED}, 21.1 \mu \text{W/cm}^2$ |      | 44.0 |      | count/<br>(µW/cm <sup>2</sup> ) |  |  |  |

Figure 9:

Color/ALS Sensor Characteristics ( $V_{DD} = 1.8V$ ,  $T_A = 25^{\circ}C$  unless otherwise noted)

| Parameter                     | Conditions                                               | Min    | Тур   | Max    | Unit                  |

|-------------------------------|----------------------------------------------------------|--------|-------|--------|-----------------------|

| Integration time step size    |                                                          | 2.68   | 2.78  | 2.90   | ms                    |

| Dark ADC count value          | Ee = 0μW/cm <sup>2</sup><br>AGAIN: 512x<br>ATIME = 100ms | 0      | 1     | 2      | counts <sup>(3)</sup> |

|                               | AGAIN = 1x                                               | 0.0145 | 0.016 | 0.0175 |                       |

|                               | AGAIN = 4x                                               | 0.060  | 0.064 | 0.068  |                       |

| Gain scaling, relative to 64x | AGAIN = 16x                                              | 0.240  | 0.255 | 0.270  | x                     |

| gain setting <sup>(1)</sup>   | AGAIN = 128x                                             | 1.8    | 2.0   | 2.2    | ^                     |

|                               | AGAIN = 256x                                             | 3.6    | 4.0   | 4.4    |                       |

|                               | AGAIN = 512x                                             | 7.0    | 7.7   | 8.4    |                       |

| ADC noise <sup>(2)</sup>      | AGAIN = 512x<br>ATIME = 100ms                            |        | 0.02  |        | % (σ)                 |

#### Note(s):

1. Test condition integration time = 27.8ms.

2. Representative result by characterization.

3. The typical value on 3-sigma distribution. An AGAIN setting of 16x correlates to a typically dark ADC count value less than or equal to 1.

#### Figure 10:

Proximity Optical Characteristics ( $V_{DD} = 1.8V$ , LEDA = 3.0V,  $T_A = 25^{\circ}$ C, unless otherwise noted)

| Parameter                             | Conditions                                                                                                                                                                                                                                                                       | Min | Тур | Max | Unit   |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| Part to Part Variation <sup>(1)</sup> | Conditions:<br>PGAIN = 2 (4x)<br>PLDRIVE = 8 (19mA)<br>PPULSE = 7 (8 pulses)<br>PPULSE_LEN = 3 (32µs)<br>d=23mm round target<br>30mm target distance                                                                                                                             | 65  | 100 | 135 | %      |

| Response, Absolute                    | Basic proximity measurement <sup>(2)</sup><br>Conditions:<br>PGAIN = 2 (4x),<br>PLDRIVE = 8 (19mA)<br>PPULSE = 7 (8 pulses)<br>PPULSE_LEN = 3 (32µs)<br>Target material:<br>90% reflective surface of Kodak<br>gray card<br>Target Size: 100mm x 100mm<br>Target Distance: 100mm | 250 | 312 | 374 | counts |

| Noise/Signal <sup>(3)</sup>           | PGAIN = 2 (4x)<br>PLDRIVE = 8 (19mA)<br>PPULSE = 7 (8 pulses)<br>PPULSE_LEN = 3 (32µs)<br>d=23mm round target<br>30mm target distance                                                                                                                                            |     |     | 2   | %      |

#### Note(s):

1. Production tested result is the average of 5 readings expressed relative to a calibrated response.

2. Representative result by characterization.

3. Production tested result is the average of 20 readings divided by the average response.

### Typical Operating Characteristics

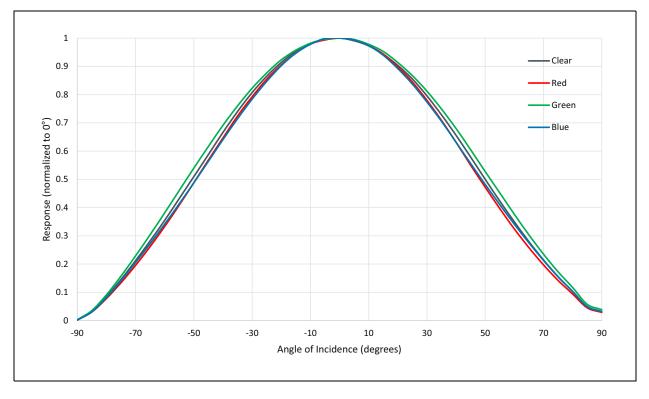

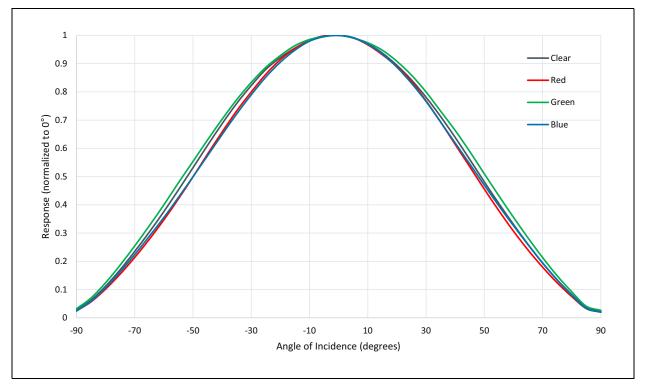

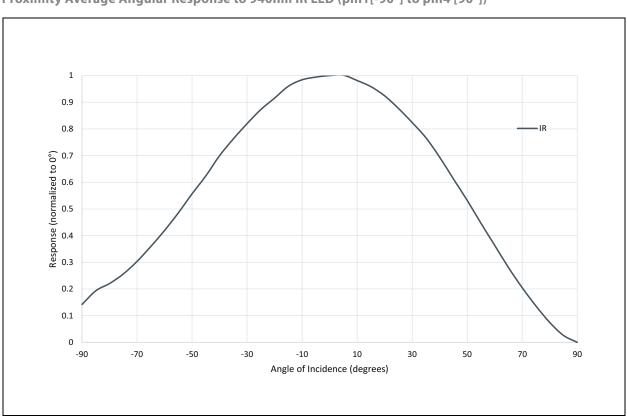

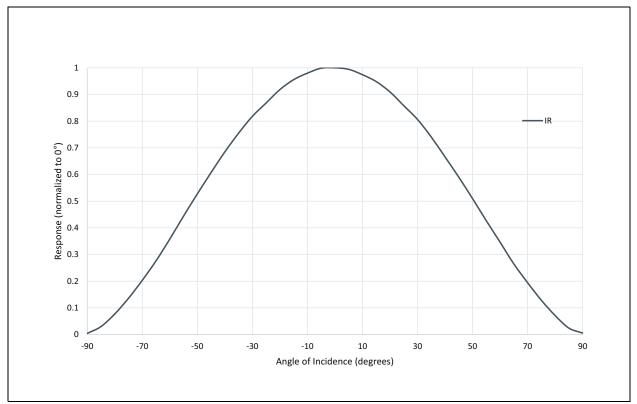

Figure 11:

ALS Average Angular Response to 2700K White LED (pin1[-90°] to pin4 [90°])

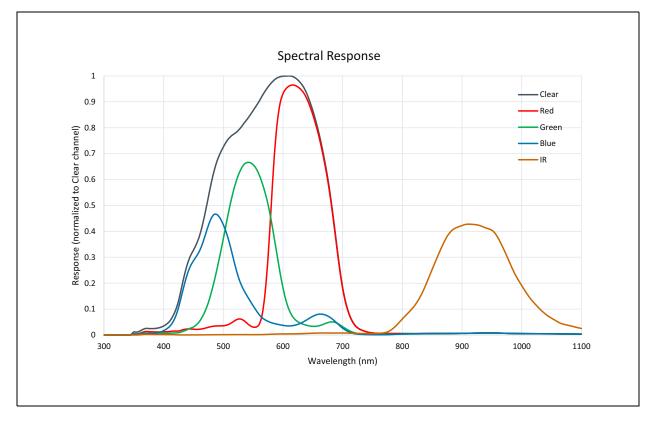

#### Figure 13: Spectral Responsivity

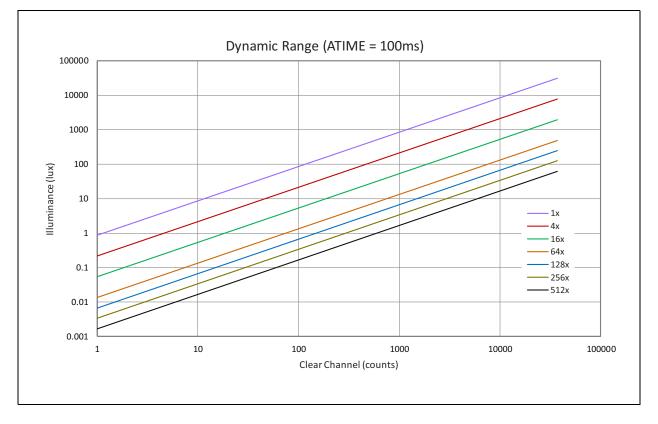

#### Figure 14:

Illuminance (Lux) vs. Counts (Clear Channel)

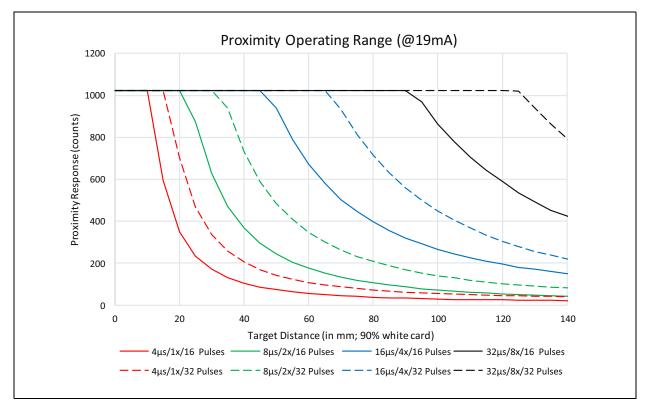

Figure 17: Proximity Operation

**Proximity Operation:** By varying Gain, VCSEL drive current, number of VCSEL pulses and VCSEL pulse duration the proximity detection range can be adjusted.

### **Detailed Description**

#### Proximity

Proximity results are affected by three fundamental factors: the integrated IR VCSEL emission, IR reception, and environmental factors, including target distance and surface reflectivity. The IR reception signal path begins with IR detection from a photodiode and ends with the 10-bit or 14-bit proximity result in PDATA register. Signal from the photodiode is amplified, and offset adjusted to optimize performance. Offset correction or cross-talk compensation is accomplished by adjustment to the POFFSET register. The analog circuitry of the device applies the offset value as a subtraction to the signal accumulation; therefore a positive offset value has the effect of decreasing the results.

#### **Color and Ambient Light Sense**

The color and ALS reception signal path begins as photodiodes receive filtered light and ends with 16-bit results. The IR photodiode primarily used for proximity sense, is multiplexed with the green channel's ADC to measure the IR content of ambient light. The color photodiodes are filtered with a UV and IR filters. The IR photodiode is filtered to receive only IR. Signal from the RGBC photodiodes simultaneously accumulate for a period of time set by the value in ATIME before the results are available. Measurement of IR must be done in a separate integration because it shares the ADC with the green photodiode. Gain is adjustable from 1x to 512x to facilitate operation over a wide range of lighting conditions. Based on the optical glass used on top of the device, custom equations are empirically derived to calculate the amount of ambient light, color temperature, as well as, determine the light type (e.g. LED, fluorescent, incandescent, etc.) using the ALS results.

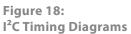

### I<sup>2</sup>C Characteristics

The device uses I<sup>2</sup>C serial communication protocol for communication. The device supports 7-bit chip addressing and both standard and fast clock frequency modes with a chip address of 0x49. Read and Write transactions comply with the standard set by Philips (now NXP).

Internal to the device, an 8-bit buffer stores the register address location of the desired byte to read or write. This buffer auto-increments upon each byte transfer and is retained between transaction events (i.e. valid even after the master issues a STOP command and the I<sup>2</sup>C bus is released). During consecutive Read transactions, the future/repeated I<sup>2</sup>C Read transaction may omit the memory address byte normally following the chip address byte; the buffer retains the last register address + 1.

#### **I<sup>2</sup>C Write Transaction**

A Write transaction consists of a START, CHIP-ADDRESS<sub>WRITE</sub>, REGISTER-ADDRESS, DATA BYTE(S), and STOP. Following each byte (9TH clock pulse) the slave places an ACKNOWLEDGE/ NOT-ACKNOWLEDGE (ACK/NACK) on the bus. If NACK is transmitted by the slave, the master may issue a STOP.

#### I<sup>2</sup>C Read Transaction

A Read transaction consists of a START, CHIP-ADDRESS<sub>WRITE</sub>, REGISTER-ADDRESS, START, CHIP-ADDRESS<sub>READ</sub>, DATA BYTE(S), and STOP. Following all but the final byte the master places an ACK on the bus (9TH clock pulse). Termination of the Read transaction is indicated by a NACK being placed on the bus by the master, followed by STOP.

Alternately, if the previous I<sup>2</sup>C transaction was a Read, the internal register address buffer is still valid, allowing the transaction to proceed without "re"-specifying the register address. In this case the transaction consists of a START, CHIP-ADDRESS<sub>READ</sub>, DATA BYTE(S), and STOP. Following all but the final byte the master places an ACK on the bus (9TH clock pulse). Termination of the Read transaction is indicated by a NACK being placed on the bus by the master, followed by STOP.

The I<sup>2</sup>C bus protocol was developed by Philips (now NXP). For a complete description of the I<sup>2</sup>C protocol, please review the NXP I<sup>2</sup>C design specification at: www.i2c-bus.org/references/

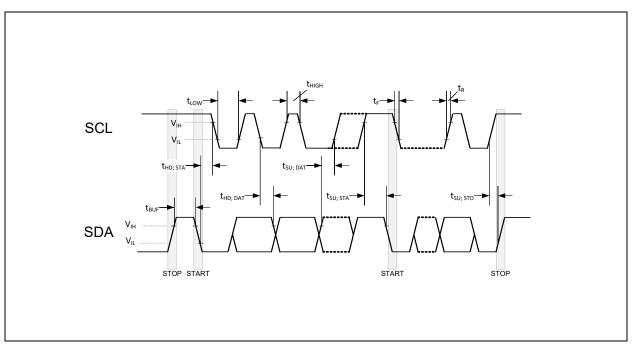

#### Figure 19: Simplified State Diagram

### **Register Description**

Figure 20: Register Overview

| Address | Register<br>Name | R/W   | Register Function                               | Reset<br>Value |

|---------|------------------|-------|-------------------------------------------------|----------------|

| 0x80    | ENABLE           | R/W   | Enables states                                  | 0x00           |

| 0x81    | ATIME            | R/W   | ADC integration time                            | 0x00           |

| 0x82    | PRATE            | R/W   | Proximity time                                  | 0x1F           |

| 0x83    | WTIME            | R/W   | Wait time                                       | 0x00           |

| 0x84    | AILTL            | R/W   | ALS interrupt low threshold low byte            | 0x00           |

| 0x85    | AILTH            | R/W   | ALS interrupt low threshold high byte           | 0x00           |

| 0x86    | AIHTL            | R/W   | ALS interrupt high threshold low byte           | 0x00           |

| 0x87    | AIHTH            | R/W   | ALS interrupt high threshold high byte          | 0x00           |

| 0x88    | PILTL            | R/W   | Proximity interrupt low threshold low byte      | 0x00           |

| 0x89    | PILTH            | R/W   | Proximity interrupt low threshold high byte     | 0x00           |

| 0x8A    | PIHTL            | R/W   | Proximity interrupt high threshold low byte     | 0x00           |

| 0x8B    | PIHTH            | R/W   | Proximity interrupt high threshold high byte    | 0x00           |

| 0x8C    | PERS             | R/W   | ALS and proximity interrupt persistence filters | 0x00           |

| 0x8D    | CFG0             | R/W   | Configuration zero                              | 0x40           |

| 0x8E    | PCFG0            | R/W   | Proximity configuration zero                    | 0x4F           |

| 0x8F    | PCFG1            | R/W   | Proximity configuration one                     | 0x80           |

| 0x90    | CFG1             | R/W   | Configuration one                               | 0x09           |

| 0x91    | REVID            | R     | Revision ID                                     | 0x01           |

| 0x92    | ID               | R     | Device ID                                       | 0x10           |

| 0x93    | STATUS           | R, SC | Device status                                   | 0x00           |

| 0x94    | CDATAL           | R     | Clear ADC low data                              | 0x00           |

| 0x95    | CDATAH           | R     | Clear ADC high data                             | 0x00           |

| 0x96    | RDATAL           | R     | Red ADC low data                                | 0x00           |

| 0x97    | RDATAH           | R     | Red ADC high data                               | 0x00           |

| 0x98    | GDATAL           | R     | Green (or IR) ADC low data                      | 0x00           |

| 0x99    | GDATAH           | R     | Green (or IR) ADC high data                     | 0x00           |

| 0x9A    | BDATAL           | R     | Blue ADC low data                               | 0x00           |

| Address | Register<br>Name | R/W | Register Function                        | Reset<br>Value  |

|---------|------------------|-----|------------------------------------------|-----------------|

| 0x9B    | BDATAH           | R   | Blue ADC high data                       | 0x00            |

| 0x9C    | PDATAL           | R   | Proximity ADC low data                   | 0x00            |

| 0x9D    | PDATAH           | R   | Proximity ADC high data                  | 0x00            |

| 0x9E    | REVID2           | R   | Revision ID two                          | 0x07            |

| 0x9F    | CFG2             | R/W | Configuration two                        | 0x00            |

| 0xA0    | SOFTRST          | R/W | Soft reset                               | 0x00            |

| 0xAB    | CFG3             | R/W | Configuration three                      | 0x04            |

| 0xAC    | CFG4             | R/W | Configuration four (must be set to 0x3D) | 0x3F            |

| 0xAE    | CFG6             | R/W | Configuration six                        | 0x3F            |

| 0xC0    | POFFSETL         | R/W | Proximity offset low data                | 0x00            |

| 0xC1    | POFFSETH         | R/W | Proximity offset high data               | 0x00            |

| 0xD7    | CALIB            | R/W | Proximity offset calibration             | 0x00            |

| 0xD9    | CALIBCFG         | R/W | Proximity offset calibration control     | 0x50            |

| 0xDC    | CALIBSTAT        | R   | Proximity offset calibration status      | 0x00            |

| 0xDD    | INTENAB          | R/W | Interrupt enables                        | 0x00            |

| 0xE6    | FAC_L            | R   | Factory data low (lot code data)         | 0x00 to<br>0xFF |

| 0xE7    | FAC_H            | R   | Factory data high (lot code data)        | 0x00 to<br>0xFF |

| 0xF2    | TEST3            | R/W | Test three (must be set to 0xC4)         | 0x44            |

#### Enable Register (Address 0x80)

Figure 21: Enable Register

| Addr:0x80 |          |         |        | Enable                                                                      |  |  |

|-----------|----------|---------|--------|-----------------------------------------------------------------------------|--|--|

| Bit       | Bit Name | Default | Access | Bit Description                                                             |  |  |

| 7:4       | Reserved | 0       | RW     | Reserved. Must be set to default value.                                     |  |  |

| 3         | WEN      | 0       | RW     | This bit activates the wait feature. Active high.                           |  |  |

| 2         | PEN      | 0       | RW     | This bit activates the proximity detection. Active high.                    |  |  |

| 1         | AEN      | 0       | RW     | This bit actives the ALS function. Active high.                             |  |  |

| 0         | PON      | 0       | RW     | This field activates the internal oscillator and ADC channels. Active high. |  |  |

Before activating AEN or PEN, preset each applicable operating mode registers and bits.

#### ATIME Register (Address 0x81)

Figure 22: ATIME Register

| Addr:0x81 |          | ATIME   |        |                                                                                                                                                                                                                                                                                                                      |                       |                     |                      |  |  |  |  |  |      |      |        |        |

|-----------|----------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|----------------------|--|--|--|--|--|------|------|--------|--------|

| Bit       | Bit Name | Default | Access |                                                                                                                                                                                                                                                                                                                      | Bit De                | scription           |                      |  |  |  |  |  |      |      |        |        |

|           |          | 0×00    |        | ALS/Color value that specifies the integration time in 2.78ms intervals. 0x00 indicates 2.78ms. The maximum ALS value depends on the integration time. For every 2.78ms, the maximum value increases by 1024. This means that to be able to reach ALS full scale, the integration time has to be at least 64*2.78ms. |                       |                     |                      |  |  |  |  |  |      |      |        |        |

|           |          |         |        | Value                                                                                                                                                                                                                                                                                                                | Integration<br>Cycles | Integration<br>Time | Maximum<br>ALS Value |  |  |  |  |  |      |      |        |        |

| 7:0       | ATIME    |         | RW     | 0x00                                                                                                                                                                                                                                                                                                                 | 1                     | 2.78ms              | 1023                 |  |  |  |  |  |      |      |        |        |

|           |          |         |        |                                                                                                                                                                                                                                                                                                                      |                       |                     |                      |  |  |  |  |  |      | 0x01 | 2      | 5.56ms |

|           |          |         |        |                                                                                                                                                                                                                                                                                                                      |                       |                     |                      |  |  |  |  |  | 0x11 | 18   | 50.0ms | 18431  |

|           |          |         |        | 0x23                                                                                                                                                                                                                                                                                                                 | 36                    | 100ms               | 36863                |  |  |  |  |  |      |      |        |        |

|           |          |         |        | 0x3F                                                                                                                                                                                                                                                                                                                 | 64                    | 178ms               | 65535                |  |  |  |  |  |      |      |        |        |

|           |          |         |        | 0xFF                                                                                                                                                                                                                                                                                                                 | 256                   | 712ms               | 65535                |  |  |  |  |  |      |      |        |        |

The ATIME register controls the integration time of the ALS ADCs. The timer is implemented with a down counter with 0x00 as the terminal count. The timer is clocked at a 2.78ms nominal rate. Loading 0x00 will generate a 2.78ms integration time, loading 0x01 will generate a 5.56ms integration time, and so forth.

#### PRATE Register (Address 0x82)

Figure 23: PRATE Register

| Addr:0x82 |          | PRATE   |        |                                                                                 |  |

|-----------|----------|---------|--------|---------------------------------------------------------------------------------|--|

| Bit       | Bit Name | Default | Access | Bit Description                                                                 |  |

| 7:0       | PRATE    | 0x1F    | RW     | This register defines the duration of 1 Prox Sample, which is (PRATE + 1)*88µs. |  |

#### WTIME Register (Address 0x83)

Figure 24: WTIME Register

| Ado | dr:0x83  |         |        | W                                                                                        | ГІМЕ       |                 |                 |

|-----|----------|---------|--------|------------------------------------------------------------------------------------------|------------|-----------------|-----------------|

| Bit | Bit Name | Default | Access | Bit Description                                                                          |            |                 |                 |

|     |          |         | RW     | Value that specifies the wait time between ALS and proximity cycles in 2.78ms increments |            |                 |                 |

|     |          |         |        | Value                                                                                    | Increments | Wait Time       |                 |

|     |          |         |        | 0x00                                                                                     | 1          | 2.78ms (33.4ms) |                 |

| 7:0 | WTIME    | 0x00    |        | RW                                                                                       | 0x01       | 2               | 5.56ms (66.7ms) |

|     |          |         |        | 0x11                                                                                     | 18         | 50.0ms (600ms)  |                 |

|     |          |         |        | 0x23                                                                                     | 36         | 100ms (1.20s)   |                 |

|     |          |         |        | 0x3F                                                                                     | 64         | 178ms (2.14s)   |                 |

|     |          |         |        | 0xFF                                                                                     | 256        | 712ms (8.54s)   |                 |

The wait timer is implemented using a down counter. Wait time = Increment x 2.78ms. If WLONG is enabled then, Wait time = Increment x 2.78ms x 12.

#### AILTL Register (Address 0x84)

Figure 25: AILTL Register

| Ado | dr:0x84  | AILTL   |        |                                                           |  |

|-----|----------|---------|--------|-----------------------------------------------------------|--|

| Bit | Bit Name | Default | Access | Bit Description                                           |  |

| 7:0 | AILTL    | 0x00    | RW     | This register sets the low byte of the LOW ALS threshold. |  |

#### AILTH Register (Address 0x85)

Figure 26: AILTH Register

| Addr: 0x85 |          | AILTH   |        |                                                            |  |

|------------|----------|---------|--------|------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                            |  |

| 7:0        | AILTH    | 0x00    | RW     | This register sets the high byte of the LOW ALS threshold. |  |

The Clear (C) channel is compared against low-going 16-bit threshold value set by AILTL and AILTH.

The contents of the AILTH and AILTL registers are combined and treated as a sixteen bit threshold value. If the value generated by the C channel is below the AILTL/H threshold and the APERS value is reached, the AINT bit is asserted. If AIEN is set, then the INT pin will also assert.

When setting the 16-bit ALS threshold AILTL must be written first, immediately followed by AILTH. Internally, the lower 8-bits are buffered until the upper 8-bits are written. As the upper 8-bits are written both the high and low bytes are simultaneously latched as a 16-bit value.

#### AIHTL Register (Address 0x86)

Figure 27: AIHTL Register

| Addr: 0x86 |          | AIHTL   |        |                                                            |  |

|------------|----------|---------|--------|------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                            |  |

| 7:0        | AIHTL    | 0x00    | RW     | This register sets the low byte of the HIGH ALS threshold. |  |

#### AIHTH Register (Address 0x87)

Figure 28: AIHTH Register

| Adc | Addr: 0x87 |         | AIHTH  |                                                             |  |  |

|-----|------------|---------|--------|-------------------------------------------------------------|--|--|

| Bit | Bit Name   | Default | Access | Bit Description                                             |  |  |

| 7:0 | AIHTH      | 0x00    | RW     | This register sets the high byte of the HIGH ALS threshold. |  |  |

The Clear (C) channel is compared against high-going 16-bit threshold value set by AIHTL and AIHTH.

The contents of the AIHTH and AIHTL registers are combined and treated as a sixteen bit threshold value. If the value generated by the C channel is above the AIHTL/H threshold and the APERS value is reached, the AINT bit is asserted. If AIEN is set, then the INT pin will also assert.

When setting the 16-bit ALS threshold AIHTL must be written first, immediately followed by AIHTH. Internally, the lower 8-bits are buffered until the upper 8-bits are written. As the upper 8-bits are written both the high and low bytes are simultaneously latched as a 16-bit value.

#### PILTL Register (Address 0x88)

Figure 29: PILTL Register

| ,   | ddr: 0x88 |         | PILTL  |                                                                                                                                                                                                                                                                           |  |  |

|-----|-----------|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bi  | Bit Name  | Default | Access | Bit Description                                                                                                                                                                                                                                                           |  |  |

| 7:0 | PILTL     | 0x00    | RW     | This register contains the low byte of the 14-bit<br>proximity LOW threshold when APC is enabled. If APC<br>is disabled, this register contains the LOW threshold<br>which is an 8-bit value which is compared against the<br>upper 8-bits of the 10-bit proximity value. |  |  |

#### PILTH Register (Address 0x89)

Figure 30: PILTH Register

| Addr: 0x89 |          | PILTH   |        |                                                                                                                                                        |  |

|------------|----------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                                                                                                                        |  |

| 7:6        | Reserved | 00      | RW     | Reserved. Must be set to default value.                                                                                                                |  |

| 5:0        | PILTH    | 0x00    | RW     | This register contains the upper 6 bits of the 14-bit<br>proximity LOW threshold when APC is enabled. If APC<br>is disabled, this register is ignored. |  |

The contents of the PILTH and PILTL registers are combined and treated as a fourteen (14) bit threshold low value. If the value generated by the proximity ADC (PDATA) is below the PILTL/H threshold and the PPERS value is reached, the PINT bit is asserted. If PIEN is set, then the INT pin will also assert. When setting the 14-bit proximity threshold, PILTL must be written first, immediately follow by PILTH. Internally, the lower 8-bits are buffered until the upper 8-bits are written. As the upper 8-bits are written both the high and low bytes are simultaneously latched as a 14-bit value.

If Automatic Pulse Control (APC) is disabled by setting bit 6 in CFG6 to 1, then the proximity data converts to a 10-bit value. PILTL contains a 8-bit threshold which is compared against the upper 8-bits of the 10-bit value. PILTH is ignored.

#### PIHTL Register (Address 0x8A)

Figure 31: PIHTL Register

| Ado | dr: 0x8A | PIHTL   |        |                                                                                                                                                                                                                                                                             |  |

|-----|----------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit | Bit Name | Default | Access | Bit Description                                                                                                                                                                                                                                                             |  |

| 7:0 | PIHTL    | 0x00    | RW     | This register contains the low byte of the 14-bit<br>proximity HIGH threshold when APC is enabled. If APC<br>is disabled, this register contains the HIGH threshold<br>which is an 8-bit value which is compared against the<br>upper 8-bits of the 10-bit proximity value. |  |

#### PIHTH Register (Address 0x8B)

Figure 32: PIHTH Register

| Addr: 0x8B |          | PIHTH   |        |                                                                                                                                                         |  |

|------------|----------|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                                                                                                                         |  |

| 7:6        | Reserved | 00      | RW     | Reserved. Must be set to default value.                                                                                                                 |  |

| 5:0        | PIHTH    | 0x00    | RW     | This register contains the upper 6 bits of the 14-bit<br>proximity HIGH threshold when APC is enabled. If APC<br>is disabled, this register is ignored. |  |

The contents of the PIHTH and PIHTL registers are combined and treated as a fourteen (14) bit threshold high value. If the value generated by the proximity ADC (PDATA) is above the PIHTL/H threshold and the PPERS value is reached, the PINT bit is asserted. If PIEN is set, then the INT pin will also assert. When setting the 14-bit proximity threshold, PIHTL must be written first, immediately follow by PIHTH. Internally, the lower 8-bits are buffered until the upper 8-bits are written. As the upper 8-bits are written both the high and low bytes are simultaneously latched as a 14-bit value.

If Automatic Pulse Control (APC) is disabled by setting bit 6 in CFG6 to 1, then the proximity data converts to a 10-bit value. PIHTL contains a 8-bit threshold which is compared against the upper 8-bits of the 10-bit value. PIHTH is ignored.

#### PERS Register (Address 0x8C)

Figure 33: PERS Register

| Add | r: 0x8C  |             |        |               | PERS                                         |

|-----|----------|-------------|--------|---------------|----------------------------------------------|

| Bit | Bit Name | Default     | Access |               | Bit Description                              |

|     |          |             |        | This register | r sets the proximity persistence filter.     |

|     |          |             |        | Value         | Interrupt                                    |

|     |          |             |        | 0 (0000)      | Every proximity cycle                        |

| 7:4 | PPERS    | 0           | RW     | 1 (0001)      | Any value outside proximity thresholds       |

| 7.4 | TT ENJ   | (0000)      |        | 2 (0010)      | 2 consecutive proximity values out of range  |

|     |          |             |        | 3 (0011)      | 3 consecutive proximity values out of range  |

|     |          |             |        |               |                                              |

|     |          |             |        | 15 (1111)     | 15 consecutive proximity values out of range |

|     |          |             |        | This register | r sets the ALS persistence filter.           |

|     |          |             |        | 0 (0000)      | Every ALS cycle                              |

|     |          |             |        | 1 (0001)      | Any value outside ALS thresholds             |

|     |          |             |        | 2 (0010)      | 2 consecutive ALS values out of range        |

|     |          |             |        | 3 (0011)      | 3 consecutive ALS values out of range        |

|     |          |             |        | 4 (0100)      | 5 consecutive ALS values out of range        |

| 3:0 | APERS    | 0<br>(0000) | RW     | 5 (0101)      | 10 consecutive ALS values out of range       |

|     |          |             |        | 6 (0110)      | 15 consecutive ALS values out of range       |

|     |          |             |        | 7 (0111)      | 20 consecutive ALS values out of range       |

|     |          |             |        |               |                                              |

|     |          |             |        | 13 (1101)     | 50 consecutive ALS values out of range       |

|     |          |             |        | 14 (1110)     | 55 consecutive ALS values out of range       |

|     |          |             |        | 15 (1111)     | 60 consecutive ALS values out of range       |

The frequency of consecutive proximity channel results outside of threshold limits are counted; this count value is compared against the PPERS value. If the counter is equal to the PPERS value an interrupt is asserted. Any time a proximity channel result is inside the threshold values the counter is cleared.

The frequency of consecutive Clear (C) channel results outside of threshold limits are counted; this count value is compared against the APERS value. If the counter is equal to the APERS setting an interrupt is asserted. Any time a Clear (C) channel result is inside the threshold values the counter is cleared.

#### CFG0 Register (Address 0x8D)

| Figure 34:    |  |

|---------------|--|

| CFG0 Register |  |

| Addr: 0x8D |                    | CFG0    |        |                                                                                                                                                      |  |

|------------|--------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name           | Default | Access | Bit Description                                                                                                                                      |  |

| 7:3        | Reserved           | 01000   | RW     | Reserved. Must be set to default value.                                                                                                              |  |

| 2          | WLONG              | 0       | RW     | When WLONG (Wait Long) is asserted the wait period as set by WTIME is increased by a factor of 12.                                                   |  |

| 1          | Reserved           | 0       | RW     | Reserved. Must be set to default value.                                                                                                              |  |

| 0          | PPULSE_<br>LEN_16x | 0       | RW     | When PPULSE_LEN_16X is asserted, the proximity pulse length is extended by a factor of 16. See the PPULSE_LEN bit description in the PCFG0 register. |  |

#### PCFG0 Register (Address 0x8E)

Figure 35: PCFG0 Register

| Addr: 0x8E |                     | PCFG0     |                        |             |                                                                                                      |  |

|------------|---------------------|-----------|------------------------|-------------|------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name            | Default   | Access Bit Description |             |                                                                                                      |  |

|            |                     |           |                        | extended by | se length. The pulse length can be<br>a factor of 16x with the assertion of the<br>_16x bit in CFG0. |  |

|            |                     |           |                        | Value       | Pulse Length                                                                                         |  |

| 7:6        | 7:6 PPULSE_LEN (01) | 1<br>(01) | RW                     | 0 (00)      | 4µs / 64µs                                                                                           |  |

|            |                     |           |                        | 1 (01)      | 8µs / 128µs                                                                                          |  |

|            |                     |           |                        | 2 (10)      | 16µs / 256µs                                                                                         |  |

|            |                     |           |                        | 3 (11)      | 32µs / 512µs                                                                                         |  |

| Addr: 0x8E |                     | PCFG0          |                                             |             |                                             |  |

|------------|---------------------|----------------|---------------------------------------------|-------------|---------------------------------------------|--|

| Bit        | Bit Name            | Default        | Access                                      |             | Bit Description                             |  |

|            |                     |                | Maximum number of pulses in a single proxin |             | mber of pulses in a single proximity cycle. |  |

|            |                     |                |                                             | Value       | Maximum Number of Pulses                    |  |

|            | 5:0 PPLUSE (001111) |                | RW                                          | 0 (000000)  | 1                                           |  |

| 5:0        |                     | 15<br>(001111) |                                             | 1 (000001)  | 2                                           |  |

|            |                     |                |                                             | 2 (000010)  | 3                                           |  |

|            |                     |                |                                             |             |                                             |  |

|            |                     |                |                                             | 63 (111111) | 64                                          |  |

The PPULSE\_LEN field sets the length (width) of all IR VCSEL pulses within the proximity cycle. Longer pulses result in increased proximity range and typically result in less electrical noise generated in the analog front end. If the PPULSE\_LEN\_ 16x bit in CFG0 is asserted, then the pulse length is extended by a factor of 16 times.

The PPULSE field sets the maximum number of IR VCSEL pulses that may occur in a proximity cycle. The proximity engine will automatically continue to add IR VCSEL pulses, up to the value set in PPULSE or if a near-saturation condition occurs. The dynamic range of the sensor is automatically adjusted to detect distant targets as well as prevent saturation from close targets. This operation also reduces power consumption because proximity integration period is automatically shortened when a target is either too close or far from the sensor.

If Automatic Pulse Control (APC) is disabled by setting bit 6 in CFG6 to 1, then PPULSE always determines the number of proximity to be transmitted.

### PCFG1 Register (Address 0x8F)

Figure 36: PCFG1 Register

| Addr: 0x8F |          | PCFG1       |        |                                                                                                                                                                                   |                                                                            |  |  |

|------------|----------|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|

| Bit        | Bit Name | Default     | Access | Bit Des                                                                                                                                                                           | cription                                                                   |  |  |

|            |          |             |        | This field sets the gain of th                                                                                                                                                    | e proximity IR sensor.                                                     |  |  |

|            |          |             |        | Value                                                                                                                                                                             | Gain                                                                       |  |  |

| 7:6        | PGAIN    | 2           | RW     | 0 (00)                                                                                                                                                                            | 1x                                                                         |  |  |

| 7.0        | 1 Grant  | (10)        |        | 1 (01)                                                                                                                                                                            | 2x                                                                         |  |  |

|            |          |             |        | 2 (10)                                                                                                                                                                            | 4x                                                                         |  |  |

|            |          |             |        | 3 (11)                                                                                                                                                                            | 8x                                                                         |  |  |

| 5:4        | Reserved | 00          | RW     | Reserved. Must be set to de                                                                                                                                                       | efault value.                                                              |  |  |

|            |          |             |        | This field sets the drive stre<br>current. Values are approxin<br>through VCSEL is factory tri<br>intensity.<br><b>Note:</b> Bit 5 in CFG1 must be<br>currents will be 2x the nom | mate; actual current<br>immed to normalize IR<br>e set to a 1 or the VCSEL |  |  |

|            |          |             |        | Value                                                                                                                                                                             | VCSEL Current                                                              |  |  |

|            |          |             |        | 0 (0000)                                                                                                                                                                          | 2mA                                                                        |  |  |

|            |          |             |        | 1 (0001)                                                                                                                                                                          | 4mA                                                                        |  |  |

| 3:0        | PLDRIVE  | 0<br>(0000) | RW     | 2 (0010)                                                                                                                                                                          | бmА                                                                        |  |  |

|            |          |             |        | 3 (0011)                                                                                                                                                                          | 8mA                                                                        |  |  |

|            |          |             |        | 4 (0100)                                                                                                                                                                          | 10mA                                                                       |  |  |

|            |          |             |        | 5 (0101)                                                                                                                                                                          | 12mA                                                                       |  |  |

|            |          |             |        | 6 (0110)                                                                                                                                                                          | 14mA                                                                       |  |  |

|            |          |             |        | 7 (0111)                                                                                                                                                                          | 17mA                                                                       |  |  |

|            |          |             |        | 8 (1000)                                                                                                                                                                          | 19mA                                                                       |  |  |

|            |          |             |        | All other values                                                                                                                                                                  | Reserved                                                                   |  |  |

#### CFG1 Register (Address 0x90)

Figure 37: CFG1 Register

| Addr: 0x90 |          | CFG1    |                                                                                                                                                                                                        |                                                                                                      |                            |  |

|------------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------|--|

| Bit        | Bit Name | Default | fault Access Bit Description                                                                                                                                                                           |                                                                                                      | cription                   |  |

| 7          | Reserved | 0       | RW                                                                                                                                                                                                     | Reserved. Must be set to def                                                                         | fault value.               |  |

| 6          | IR_MUX   | 0       | RW If set high, the IR (proximity) photodiode is switc<br>the Green channel's data converter. GDATAL/H r<br>will report IR content. Green photodiode is not<br>connected in this mode <sup>(1)</sup> . |                                                                                                      | nverter. GDATAL/H register |  |

| 5          | Reserved | 0       | RW                                                                                                                                                                                                     | Reserved. <b>Must be set to 1.</b> If this bit is 0, the VCSEL current will be 2x the nominal value. |                            |  |

|            |          |         | RW                                                                                                                                                                                                     | This field sets the gain of the                                                                      | e ALS/Color sensor.        |  |

|            |          |         |                                                                                                                                                                                                        | Value                                                                                                | ALS Gain                   |  |

|            |          |         |                                                                                                                                                                                                        | 1 (00001)                                                                                            | 1x                         |  |

|            |          |         |                                                                                                                                                                                                        | 3 (00011)                                                                                            | 4x                         |  |

| 4:0        | AGAIN    | 9       |                                                                                                                                                                                                        | 5 (00101)                                                                                            | 16x                        |  |

| 4:0        | AGAIN    | (01001) |                                                                                                                                                                                                        | 7 (00111)                                                                                            | 64x                        |  |

|            |          |         |                                                                                                                                                                                                        | 8 (01000)                                                                                            | 128x                       |  |

|            |          |         |                                                                                                                                                                                                        | 9 (01001)                                                                                            | 256x                       |  |

|            |          |         |                                                                                                                                                                                                        | 10 (01010)                                                                                           | 512x                       |  |

|            |          |         | -                                                                                                                                                                                                      | All other values                                                                                     | Reserved                   |  |

#### Note(s):

1. The IR multiplexer is not synchronized to the ALS/Color measurement sequencer. It is recommended that after the IR\_MUX bit is changed, to either discard the first ALS/color measurement or wait at least two ALS/color integration times before reading the results.

#### **REVID** Register (Address 0x91)

Figure 38: REVID Register

| Addr: 0x91 |          | REVID   |        |                         |  |

|------------|----------|---------|--------|-------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description         |  |

| 7:3        | Reserved | 00000   | RO     | Reserved.               |  |

| 2:0        | REV_ID   | 001     | RO     | Device revision number. |  |

#### ID Register (Address 0x92)

#### Figure 39: ID Register

| Addr: 0x92 |          | ID      |        |                             |  |  |

|------------|----------|---------|--------|-----------------------------|--|--|

| Bit        | Bit Name | Default | Access | Bit Description             |  |  |

| 7:2        | ID       | 000100  | RO     | Device type identification. |  |  |

| 1:0        | Reserved | 00      | RO     | Reserved                    |  |  |

#### Status Register (Address 0x93)

Figure 40: Status Register

| Addr: 0x93 |                 |         | Status Register |                                                                                                                                                          |  |  |

|------------|-----------------|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit        | Bit Name        | Default | Access          | Bit Description                                                                                                                                          |  |  |

| 7          | ASAT            | 0       | R, SC           | Analog saturation flag signals that the ALS/Color results may be unreliable due to saturation of the AFE.                                                |  |  |

| 6          | PSAT            | 0       | R, SC           | Proximity saturation flag indicates that an ambient- or reflective-saturation event occurred during a previous proximity cycle.                          |  |  |

| 5          | PINT            | 0       | R, SC           | Proximity interrupt flag indicates that proximity results have exceeded thresholds and persistence settings.                                             |  |  |

| 4          | AINT            | 0       | R, SC           | ALS interrupt flag indicates that ALS/Color results (clear channel) have exceeded thresholds and persistence settings.                                   |  |  |

| 3          | CINT            | 0       | R, SC           | Calibration interrupt flag indicates that calibration has completed.                                                                                     |  |  |

| 2          | ZINT            | 0       | R, SC           | Zero detection interrupt flag indicates that a zero value<br>in PDATA has caused the proximity offset to be<br>decremented (if AUTO_OFFSET_ADJ = 1).     |  |  |

| 1          | PSAT_REFLECTIVE | 0       | R, SC           | The reflective proximity saturation interrupt flag signals<br>that the AFE has saturated during the IR VCSEL active<br>portion of proximity integration. |  |  |

| 0          | PSAT_AMBIENT    | 0       | R, SC           | The ambient proximity saturation interrupt flag signals<br>that the AFE has saturated during the IR VCSEL inactive<br>portion of proximity integration.  |  |  |

All flags in this register can be cleared by setting the bit high. Alternatively, if the INT\_READ\_CLEAR in the CFG3 register bit is set, then simply reading this register automatically clears all eight flags.

#### CDATAL Register (Address 0x94)

Figure 41: CDATAL Register

| Addr: 0x94 |          | CDATAL  |        |                                                                       |  |

|------------|----------|---------|--------|-----------------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                                       |  |

| 7:0        | CDATAL   | 0x00    | RO     | This register contains the low byte of the 16-bit clear channel data. |  |

#### CDATAH Register (Address 0x95)

Figure 42: CDATAH Register

| Addr: 0x95 |          | СДАТАН  |        |                                                                        |  |

|------------|----------|---------|--------|------------------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                                        |  |

| 7:0        | CDATAH   | 0x00    | RO     | This register contains the high byte of the 16-bit clear channel data. |  |

#### RDATAL Register (Address 0x96)

Figure 43: RDATAL Register

| Addr: 0x96 |          | RDATAL  |        |                                                                     |  |

|------------|----------|---------|--------|---------------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                                     |  |

| 7:0        | RDATAL   | 0x00    | RO     | This register contains the low byte of the 16-bit red channel data. |  |

#### RDATAH Register (Address 0x97)

Figure 44: RDATAH Register

| Addr: 0x97 |          | RDATAH  |        |                                                                      |  |

|------------|----------|---------|--------|----------------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                                      |  |

| 7:0        | RDATAH   | 0x00    | RO     | This register contains the high byte of the 16-bit red channel data. |  |

#### GDATAL Register (Address 0x98)

Figure 45: GDATAL Register

| Ado | dr: 0x98 |         |        | GDATAL                                                                                                       |

|-----|----------|---------|--------|--------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Default | Access | Bit Description                                                                                              |

| 7:0 | GDATAL   | 0x00    | RO     | This register contains the low byte of the 16-bit green channel data (or IR data if IR_MUX bit in CFG1 = 1). |

#### GDATAH Register (Address 0x99)

Figure 46: GDATAH Register

| Addr: 0x99 |          |         |        | GDATAH                                                                                                        |

|------------|----------|---------|--------|---------------------------------------------------------------------------------------------------------------|

| Bit        | Bit Name | Default | Access | Bit Description                                                                                               |

| 7:0        | GDATAH   | 0x00    | RO     | This register contains the high byte of the 16-bit green channel data (or IR data if IR_MUX bit in CFG1 = 1). |