# Product Document

# **AS5171**

# **High-Resolution On-Axis Magnetic Angular Position Sensor**

# **General Description**

The AS5171 is a high-resolution angular position sensor for precise absolute angle measurement. The AS5171 is available with an analog output interface (AS5171E) or a digital output interface (AS5171B). The latter can be programmed as a PWM or a SENT-compliant output interface.

Based on a Hall sensor technology, this device measures the orthogonal component of the flux density (Bz) over a full-turn rotation and compensates for external stray magnetic fields with a robust architecture based on a 14-bit sensor array and analog front-end (AFE). A sub-range can be programmed to achieve the best resolution for the application. To measure the angle, only a simple two-pole magnet rotating over the center of the package is required. The magnet may be placed above or below the device. The absolute angle measurement provides an instant indication of the magnet's angular position. The AS5171 operates at a supply voltage of 5V, and the supply and output pins are protected against overvoltage up to +20V. In addition the supply pins are protected against reverse polarity up to -20V.

The AS5171E and AS5171B are available in a SIP package (System in Package). The package has integrated the AS5171 sensor die together with the decoupling capacitors necessary to pass system level ESD and EMC requirements. No additional components and PCB on the sensor side is needed. The product is defined as SEooC (Safety Element out of Context) according ISO26262.

Ordering Information and Content Guide appear at end of datasheet.

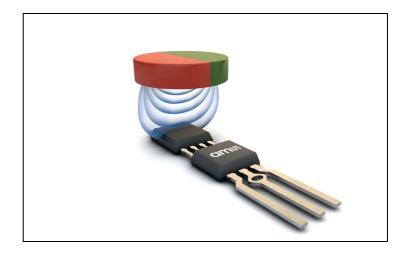

Figure 1:

Typical Arrangement of AS5171 and a Magnet

# **Key Benefits and Features**

The benefits and features of this device are listed below:

Figure 2: Added Value of Using AS5171

| Benefits                                                    | Features                                                            |

|-------------------------------------------------------------|---------------------------------------------------------------------|

| Resolve small angular excursion with high accuracy          | 12-bit resolution @90° minimum arc                                  |

| Accurate angle measurement                                  | Low output noise, low inherent INL                                  |

| Higher durability and lower system costs (no shield needed) | Magnetic stray field immunity                                       |

| Enabler for safety critical applications                    | Functional safety, diagnostics, dual redundant chip version         |

| Suitable for automotive applications                        | AEC-Q100 Grade 0 qualified                                          |

| SIP Package (sensor + decoupling capacitors<br>for ESD/EMC) | System cost reduction – no PCB and additional components are needed |

# **Applications**

The AS5171 is ideal for automotive applications like:

- Brake and Gas Pedals

- Throttle Valve and Tumble Flaps

- Steering Angle Sensors

- Chassis Ride

- EGR

- Fuel-Level Measurement Systems

- 2/4WD Switch

- Contactless Potentiometers

Page 2Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

# **Block Diagram**

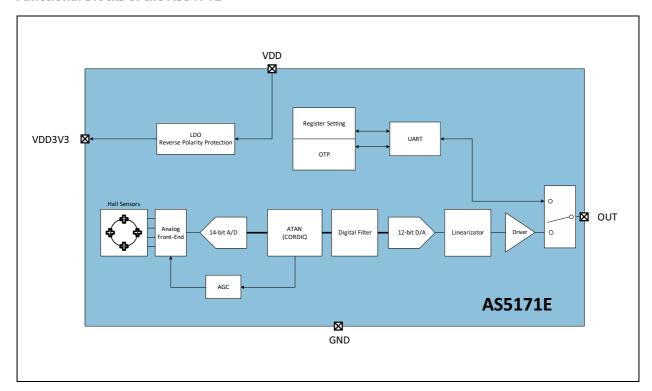

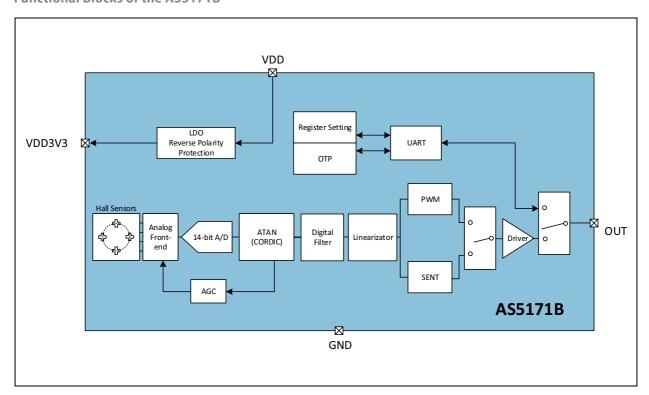

The functional blocks of the AS5171E and AS5171B are shown below:

Figure 3: Functional Blocks of the AS5171E

Figure 4: Functional Blocks of the AS5171B

Datasheet, PublicPage 3[v2-00] 2023-Sep-06Document Feedback

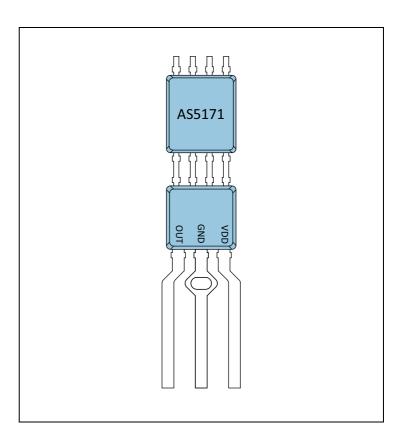

# **Pin Assignments**

Figure 5: AS5171E/B Pin Assignment (Top View, SIP)

Figure 6: AS5171E/B Pin Description

| Pin# | Pin Name | Pin Type                                            | Description      | Comments                                                           |

|------|----------|-----------------------------------------------------|------------------|--------------------------------------------------------------------|

| SIP  |          |                                                     |                  |                                                                    |

| 1    | VDD      | Supply                                              | Positive supply  | 5V supply – 100nF capacitor in SIP<br>Body                         |

| -    | TP1      | n.a.                                                | Test pin         |                                                                    |

| -    | TP2      | n.a.                                                | Test pin         |                                                                    |

| -    | TP3      | n.a.                                                | Test pin         |                                                                    |

| 3    | OUT      | Analog output (AS5171E)<br>Digital output (AS5171B) | Output interface | 4.7nF capacitor in SIP Body                                        |

| -    | TP4      | n.a.                                                | Test pin         |                                                                    |

| -    | VDD3V3   | Supply                                              |                  | 3.3V on-chip low-dropout (LDO) output. 100nF capacitor in SIP Body |

| 2    | GND      | Supply                                              | Ground           | Connected to ground                                                |

Page 4

Document Feedback

# **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Operating Conditions is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 7:

Absolute Maximum Ratings

| Symbol                              | Parameter                                                              | Min         | Max                    | Units   | Comments                                          |

|-------------------------------------|------------------------------------------------------------------------|-------------|------------------------|---------|---------------------------------------------------|

|                                     | Electri                                                                | cal Param   | eters                  |         |                                                   |

| VDD                                 | DC Supply Voltage at VDD pin                                           | -20         | 20                     | V       | Not operational                                   |

| VOUT                                | External DC voltage at OUT pin                                         | -0.3        | 20                     | V       | Permanent                                         |

| VDIFF                               | DC voltage difference between<br>VDD and OUT                           | -20         | 20                     | V       |                                                   |

| VREGOUT                             | DC voltage at the VDD3V3 pin                                           | -0.3        | 5.0                    | V       |                                                   |

| I <sub>SCR</sub>                    | Input Current (latch-up immunity)                                      | -100        | 100                    | mA      | AEC-Q100-004                                      |

|                                     | Continuous Power                                                       | Dissipation | on (T <sub>AMB</sub> = | 70°C)   |                                                   |

| P <sub>T</sub>                      | Continuous power dissipation                                           |             | 66                     |         | Calculated with IDDmax=12mA; VDD=5.5V             |

|                                     | Electro                                                                | static Disc | harge                  | •       |                                                   |

| ESD <sub>HBM on</sub><br>Chip level | Electrostatic discharge HBM                                            | <u> </u>    | -2                     | kV      | AEC-Q100-002                                      |

| ESD <sub>HBM</sub> system           | Electrostatic discharge HBM on<br>VDD, Out and GND (outer<br>connects) | ±           | -4                     | kV      | AEC-Q100-002                                      |

|                                     | Temperature Rang                                                       | es and Sto  | orage Cond             | litions |                                                   |

| T <sub>AMB</sub>                    | Operating temperature range                                            | -40         | 150                    | °C      | Ambient temperature                               |

| TaProg                              | Programming temperature                                                | 5 45        |                        | °C      | Programming@ Room<br>temperature<br>(25°C ± 20°C) |

| T <sub>STRG</sub>                   | Storage temperature range                                              | -55         | 150                    | °C      |                                                   |

Datasheet, PublicPage 5[v2-00] 2023-Sep-06Document Feedback

| Symbol            | Parameter                        | Min | Max | Units | Comments                                                                                                                                                                                                                                                                     |

|-------------------|----------------------------------|-----|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>BODY</sub> | Package body temperature         |     | 260 | °C    | The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices." The lead finish for Pb-free leaded packages is "Matte Tin" (100% Sn) |

| RH <sub>NC</sub>  | Relative humidity non-condensing | 5   | 85  | %     |                                                                                                                                                                                                                                                                              |

| MSL               | Moisture sensitivity level       |     | 3   |       | Represents a maximum<br>floor life time of<br>168 hours                                                                                                                                                                                                                      |

# **System Electrical and Timing Characteristics**

All in this datasheet defined tolerances for external components need to be assured over the whole operation conditions range and also over lifetime.

Overall condition: T<sub>AMB</sub> = -40°C to 150°C, VDD=4.5V to 5.5V; Components spec; unless otherwise noted

Figure 8: Operating Conditions

| Symbol | Parameter                  | Conditions                                                      | Min | Тур  | Max | Unit |

|--------|----------------------------|-----------------------------------------------------------------|-----|------|-----|------|

| VDD    | Positive supply voltage    |                                                                 | 4.5 | 5.0  | 5.5 | V    |

| VREG   | Regulated voltage          | VDD3V3 should not be loaded<br>by any external DC current       | 3.3 | 3.45 | 3.6 | V    |

| IDD_A  | Supply current AS5171E     | AGC=255 (no magnet placed);<br>no output load; no short circiut | 4   |      | 12  | mA   |

| IDD_B  | Supply current AS5171B     | AGC=255 (no magnet placed);<br>no output load; no short circiut | 4   |      | 10  | mA   |

| ISTART | Supply current at start-up | VREG = 2.25V                                                    | 2.5 | 5    | 10  | mA   |

| TSUP   | Start-up time              | Functional mode                                                 |     |      | 10  | ms   |

$T_{AMB}$ = -40°C to 150°C, VDD = 4.5 – 5.5V (5Voperation), Magnetic Characterization; unless otherwise noted

Page 6Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

Figure 9: Electrical System Characteristics

| Symbol  | Parameter                           | Conditions                                                                                                                 | Min  | Тур | Max | Unit |

|---------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| CRES    | Core resolution                     |                                                                                                                            |      |     | 14  | bit  |

| ARES    | Analog resolution<br>(AS5171E)      | Range > 90°                                                                                                                |      |     | 12  | bit  |

| DRES    | Digital resolution<br>(AS5171B)     |                                                                                                                            |      |     | 12  | bit  |

| INLopt  | Integral non-linearity<br>(optimum) | Best aligned reference magnet <sup>(1)</sup> at 25°C over full turn 360°                                                   | -0.5 |     | 0.5 | deg  |

| INLtemp | Integral non-linearity<br>(optimum) | Best aligned reference magnet <sup>(1)</sup><br>over temperature -40°C to 150°C<br>over full turn 360°                     | -0.9 |     | 0.9 | deg  |

| INL     | Integral non-linearity              | Best aligned reference magnet <sup>(1)</sup><br>over temperature -40°C to 150°C<br>over full turn 360° and<br>displacement | -1.4 |     | 1.4 | deg  |

| ON      | Output noise peak to peak           | Static conditions - filter on                                                                                              |      |     | 1   | LSB  |

| ST      | Sampling time                       |                                                                                                                            |      | 125 |     | μs   |

# Note(s):

1. Reference magnet: NdFeB, 6 mm diameter, 2.5 mm thickness

Figure 10:

Power Management – Supply Monitor - Timing

| Symbol  | Parameter                           | Conditions                                                          | Min | Тур | Max | Unit |

|---------|-------------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| VDDUVTH | VDD undervoltage upper<br>threshold |                                                                     | 3.5 | 4.0 | 4.5 | >    |

| VDDUVTL | VDD undervoltage lower threshold    |                                                                     | 3.0 | 3.5 | 4.0 | >    |

| VDDUH   | VDD undervoltage<br>hysteresis      |                                                                     | 300 | 500 | 900 | mV   |

| UVDT    | VDD undervoltage<br>detection time  | Time devices detects undervoltage VDD< VDDUVTH                      | 10  | 50  | 250 | μs   |

| UVRT    | Undervoltage recovery time          | Time device return into normal mode from failure band VDD > VDDUVTH | 10  | 50  | 250 | μs   |

| VDDOVTH | VDD overvoltage upper<br>threshold  |                                                                     | 6.0 | 6.5 | 7.0 | V    |

Datasheet, PublicPage 7[v2-00] 2023-Sep-06Document Feedback

| Symbol  | Parameter                        | Conditions                                                                | Min | Тур  | Max  | Unit |

|---------|----------------------------------|---------------------------------------------------------------------------|-----|------|------|------|

| VDDOVTL | VDD overvoltage lower threshold  |                                                                           | 5.5 | 6.0  | 6.5  | ٧    |

| VDDOH   | VDD overvoltage<br>hysteresis    |                                                                           | 300 | 500  | 900  | ٧    |

| OVDT    | VDD overvoltage detection time   | Time devices detects overvoltage VDD> VDDOVTL                             | 500 | 1000 | 2000 | μs   |

| OVRT    | VDD overvoltage recovery time    | Time device return into normal<br>mode from failure band VDD <<br>VDDOVTL | 500 | 1000 | 2000 | μs   |

| TDETWD  | WatchDog error<br>detection time | Time device detects oscillator failure till output is in failure band     |     |      | 12   | ms   |

$T_{AMB} = -40$  °C to 150 °C, VDD = 4.5V to 5.5V, unless otherwise noted.

Two-pole cylindrical diametrically magnetized source:

Figure 11: Magnetic Characteristics

| Symbol              | Parameter                                                | Conditions                                                                                                                                    | Min | Тур | Max | Unit |

|---------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Bz                  | Orthogonal magnetic field strength                       | Required orthogonal<br>component of the magnetic<br>field strength measured at the<br>package surface along a circle<br>of 1.25mm<br>MFER = 0 | 30  |     | 70  | mT   |

| BzE                 | Orthogonal magnetic<br>field strength – extended<br>mode | Required orthogonal<br>component of the magnetic<br>field strength measured at the<br>package surface along a circle<br>of 1.25mm<br>MFER = 1 | 10  |     | 90  | mT   |

| Disp <sup>(1)</sup> | Displacement radius                                      | Offset between defined device center and magnet axis. Dependent on the selected magnet.                                                       |     | 0.5 |     | mm   |

#### Note(s):

1. Reference magnet: NdFeB, 6 mm diameter, 2.5 mm thickness

Page 8Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

Figure 12: Electrical and Timing Characteristics Analog Output (AS5171E)

| Symbol              | Parameter                                             | Conditions                                                                                       | Min   | Тур | Max  | Unit |

|---------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------|-----|------|------|

| INLOS               | INL output stage                                      |                                                                                                  | -6    |     | +6   | LSB  |

| DNLOS               | DNL output stage                                      |                                                                                                  | -5    |     | +5   | LSB  |

| RERR <sup>(1)</sup> | Ratiometricity error                                  | Between 4% and 96% of VDD                                                                        | -0.5% |     | 0.5% | VDD  |

| BVPU                | Output voltage broken<br>VDD with pull-up<br>resistor | Pull-up resistor must be in the specified range (see Figure 38)                                  | 96    |     | 100  | %VDD |

| BGPD                | Output voltage broken ground with pull-down resistor  | Pull-down resistor must be in<br>the specified range<br>(see Figure 38)                          | 0     |     | 4    | %VDD |

| OSSCG               | Output short-circuit current GND                      | OUT = GND                                                                                        | -20   | -10 | -5   | mA   |

| OSSCV               | Output short-circuit current VDD                      | OUT = VDD                                                                                        | 5     | 10  | 20   | mA   |

| OSSDT               | Output short-circuit detection time                   | OUT = GND or OUT = VDD                                                                           | 20    | 200 | 600  | μs   |

| OSSRT               | Output short-circuit recovery time                    |                                                                                                  | 2     | 5   | 20   | ms   |

| OLCH                | Output level clamping high                            | Output current at OUT pin<br>-3 mA                                                               | 96    |     |      | %VDD |

| OLCL                | Output level clamping low                             | Output current at OUT pin 3 mA                                                                   |       |     | 4    | %VDD |

| OSPSR               | Output stage positive step response (driver only)     | From 0 to 90%VDD, measured at OUT pin, with RPUOUT = $4.7k\Omega$ , CLOAD = $1nF$ , VDD = $5V$   |       |     | 250  | μs   |

| OSNSR               | Output stage negative step response (driver only)     | From VDD to 10%VDD, measured at OUT pin, with RPUOUT = $4.7k\Omega$ , CLOAD = $1nF$ , VDD = $5V$ |       |     | 250  | μs   |

| OSTD                | Output stage<br>temperature drift                     | of value at mid code, info<br>parameter not tested in<br>production                              | -0.2  |     | 0.2  | %    |

## Note(s):

- For each code the ratiometricity error is defined as follows: VOUTRATE=((VOUTact - (VOUTtyp\*(VDDact/ VDDtyp)))/VDDtyp)\*100 Where:

- VOUTact is the actual output voltage

- VOUTtyp is the typical output voltage

- VDDact is the actual supply voltage

- VDDtyp is the typical supply voltage

Datasheet, PublicPage 9[v2-00] 2023-Sep-06Document Feedback

Figure 13: Electrical and Timing Characteristics PWM Output (AS5171B)

| Symbol   | Parameter                                      | Conditions                                                                                   | Min   | Тур  | Max   | Unit                 |

|----------|------------------------------------------------|----------------------------------------------------------------------------------------------|-------|------|-------|----------------------|

| PWMSSOCG | Short-circuit output current                   | OUT = GND                                                                                    | -20   | -10  | -5    | mA                   |

| PWMSSOCV | Short-circuit output current                   | OUT = VDD                                                                                    | 5     | 10   | 20    | mA                   |

| PWMSSDT  | PWM short-circuit detection time               | OUT = GND or<br>OUT = VDD                                                                    |       |      | 5     | % PWM<br>clock cycle |

| PWMSSRT  | PWM short circuit recovery time                |                                                                                              |       | 6    |       | % PWM<br>clock cycle |

| ВКРWMVOH | PWM output voltage<br>high in broken condition | Broken VDD or broken GND, OUT = high, PWMVOH=VDD-VOUT RPU = $10k\Omega$ or RPD = $10k\Omega$ | 0     |      | 0.4   | V                    |

| BKPWMVOL | PWM output voltage low in broken condition     | Broken VDD or broken GND, OUT = low, RPU = $10k\Omega$ or RPD = $10k\Omega$                  | 0     |      | 0.4   | V                    |

| PWMF7    | PWM frequency                                  | PWMFR = 111                                                                                  | 112.5 | 125  | 137.5 | Hz                   |

| PWMF6    | PWM frequency                                  | PWMFR = 110                                                                                  | 180   | 200  | 220   | Hz                   |

| PWMF5    | PWM frequency                                  | PWMFR = 101                                                                                  | 225   | 250  | 275   | Hz                   |

| PWMF4    | PWM frequency                                  | PWMFR = 100                                                                                  | 360   | 400  | 440   | Hz                   |

| PWMF3    | PWM frequency                                  | PWMFR = 011                                                                                  | 450   | 500  | 550   | Hz                   |

| PWMF2    | PWM frequency                                  | PWMFR = 010                                                                                  | 720   | 800  | 880   | Hz                   |

| PWMF1    | PWM frequency                                  | PWMFR = 001                                                                                  | 900   | 1000 | 1100  | Hz                   |

| PWMF0    | PWM frequency                                  | PWMFR = 000                                                                                  | 1800  | 2000 | 2200  | Hz                   |

| PWMVOH   | PWM output voltage<br>level high               | IOUT = 5 mA,<br>PWMVOH = VDD - VOUT                                                          | 0     |      | 0.4   | V                    |

| PWMVOL   | PWM output voltage<br>level low                | IOUT = 5 mA                                                                                  | 0     |      | 0.4   | V                    |

| PWMSRF   | PMM slew rate fast                             | Between 25% and 75% of VDD, RPUOUT = $4.7k\Omega$ , CLOUT1 = $4.7nF$ , PWMSR = $0$           | 1     | 2    | 4     | V/µs                 |

Page 10Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

| Symbol | Parameter          | Conditions                                                                       | Min | Тур | Max | Unit |

|--------|--------------------|----------------------------------------------------------------------------------|-----|-----|-----|------|

| PWMSRS | PWM slew rate slow | Between 25% and 75% of VDD, RPUOUT = $4.7k\Omega$ , CLOUT1 = $4.7nF$ , PWMSR = 1 | 0.5 | 1   | 2   | V/µs |

Figure 14: Electrical and Timing Characteristics SENT Output (AS5171B)

| Symbol    | Parameter                               | Conditions                                                       | Min | Тур | Max | Unit |

|-----------|-----------------------------------------|------------------------------------------------------------------|-----|-----|-----|------|

| SENTSSOC  | SENT short-circuit output               | OUT = 20V                                                        | 10  | 20  | 40  | mA   |

| SEIVISSOC | current                                 | OUT = 0V                                                         | -40 | -20 | -10 | mA   |

| BKSENTVOH | SENT output voltage in broken condition | Broken VDD or broken<br>GND, RPU = 50kΩ, SENT<br>constantly high | 0   |     | 1.2 | V    |

| SENTVOH   | SENT output voltage high                |                                                                  | 4.1 |     |     | V    |

| SENTVOL   | SENT output voltage low                 |                                                                  |     |     | 0.5 | V    |

| SENTFT    | SENT fall time                          |                                                                  |     |     | 6.5 | μs   |

| SENTRT    | SENT rise time                          |                                                                  |     |     | 18  | μs   |

Figure 15: Electrical and Timing Characteristics UART Interface

| Symbol                   | Parameter                      | Conditions | Min     | Тур | Max  | Unit |

|--------------------------|--------------------------------|------------|---------|-----|------|------|

| UARTVIH                  | UART high level input voltage  |            | 70      |     |      | %VDD |

| UARTVIL                  | UART low level input voltage   |            |         |     | 30   | %VDD |

| UARTVOH                  | UART high level output voltage |            | VDD-0.5 |     |      | V    |

| UARTVOL                  | UART low level output voltage  |            |         |     | 0.5  | V    |

| UARTBRLIM <sup>(1)</sup> | UART baud rate                 |            | 2400    |     | 9600 | Baud |

# Note(s):

1. Typ. error 1%. Indirect tested.

Datasheet, PublicPage 11[v2-00] 2023-Sep-06Document Feedback

## **Detailed Description**

The AS5171 is a Hall-based rotary magnetic position sensor using a CMOS technology. The lateral Hall sensor array converts the magnetic field component perpendicular to the surface of the chip into a voltage.

The signals coming from the Hall sensors are first amplified and filtered before being converted by the analog-to-digital converter (ADC). The output of the ADC is processed by the CORDIC block (Coordinate-Rotation Digital Computer) to compute the angule and magnitude of the magnetic field vector. The sensor and analog front-end (AFE) section works in a closed loop alongside an AGC to compensate for temperature and magnetic field variations. The calculated magnetic field strength (MAG), the automatic gain control (AGC) and the angle can be read through the output pin (OUT) in UART mode.

The magnetic field coordinates provided by the CORDIC block are fed to a digital filter which reduces noise. A linearization block generates the transfer function, including linearization. The AS5171 is available with two different output interfaces: analog ratiometric (AS5171E) or digital PWM or SENT (AS5171B).

The output of the AS5171 can be programmed to define a starting position (zero angle) and a stop position (maximum angle). An embedded linearization algorithm allows reducing the system INL error due, for example, to mechanical misalignment, magnet imperfections, etc.

The AS5171 can be programmed through the OUT pin with a UART interface which allows writing an on-chip non-volatile memory (OTP) where the specific settings are stored. The AS5171 can be programmed by the ams OSRAM programming tool, both at the component and board level.

Page 12

Document Feedback

[v2-00] 2023-Sep-06

# **Register Description**

The register description for AS5171E/B are explained below:

- Descriptions and Settings with Analog are supported by AS5171E

- Descriptions and Settings with PWM are supported by AS5171B

Figure 16: Non-Volatile Memory Register Description

| Address | Bit Position | Field   | Description                                                                                                           |

|---------|--------------|---------|-----------------------------------------------------------------------------------------------------------------------|

| 0x0A    | 7:0          | CUSTID0 | Customer ID byte 0                                                                                                    |

| 0x0B    | 7:0          | CUSTID1 | Customer ID byte 1                                                                                                    |

| 0x0C    | 7:0          | CUSTID2 | Customer ID byte 2                                                                                                    |

| 0x0D    | 7:0          | CUSTID3 | Customer ID byte 3                                                                                                    |

|         | 0            | PWMINV  | PWM inverted                                                                                                          |

|         | 1            | PWMSR   | PWM slew rate (0 = PWM slew rate fast PWMSRF, 1 = PWM slew rate slow PWMSRS)                                          |

| 0x0E    | 3:2          | DIGOS   | Digital output stage (00 = PWM push-pull 01 = PWM pull-down 10 = PWM pull-up 11= SENT) It applies to the AS5171B only |

|         | 6:4          | RBKDEB  | Analog read-back debouncing                                                                                           |

|         | 7            | NA      | Not used                                                                                                              |

|         | 0            | FBS     | Failure band selection (0 = lower failure band, 1 = upper failure band)                                               |

| 0x0F    | 2:1          | HYST    | Hysteresis across the brake point                                                                                     |

|         | 4:3          | QUAD    | Quadrant selection                                                                                                    |

|         | 7:5          | PWMFR   | PWM frequency selection                                                                                               |

|         | 1:0          | PWMRTH  | PWM rising threshold                                                                                                  |

| 0x10    | 3:2          | PWMFTH  | PWM falling threshold                                                                                                 |

|         | 7:4          | SENTMID | SENT message ID                                                                                                       |

|         | 4:0          | SENTTK  | SENT tick                                                                                                             |

|         | 5            | SENTESM | Enable SENT serial message                                                                                            |

| 0x11    | 6            | SENTPP  | SENT pause pulse enable (1 = enable, 0 = disable)                                                                     |

|         | 7            | SENTRC  | SENT rolling counter enable<br>(1 = enable, 0 = disable)                                                              |

Datasheet, PublicPage 13[v2-00] 2023-Sep-06Document Feedback

| Address | Bit Position | Field    | Description                                                                              |  |

|---------|--------------|----------|------------------------------------------------------------------------------------------|--|

| 0x12    | 3:0          | NA       | No use. Default 0                                                                        |  |

| UX12    | 6:4          | NA       | No use. Default 0                                                                        |  |

| 0x13    | 3:0          | NA       | No use. Default 0                                                                        |  |

| 0.13    | 6:4          | NA       | No use. Default 0                                                                        |  |

| 0x14    | 7:0          | CLMPH    | Clamping level high                                                                      |  |

| 0x15    | 3:0          | CLIVIPH  | Reg 0x14[0] =LSB<br>Reg 0x15[3]=MSN                                                      |  |

| OX13    | 7:4          | CLMPL    | Clamping level low<br>Reg 0x15[4] =LSB                                                   |  |

| 0x16    | 7:0          | CLIVIPL  | Reg 0x16[7]=MSN                                                                          |  |

| 0x17    | 7:0          |          | Post processing offset                                                                   |  |

| 0x18    | 7:0          | PPOFFSET | Reg 0x17[0] =LSB<br>Reg 0x19[3]=MSB                                                      |  |

| 0x19    | 3:0          |          | neg ox i a[2]—ivi3b                                                                      |  |

| 0,19    | 7:4          |          | Post processing gain                                                                     |  |

| 0x1A    | 7:0          | PPGAIN   | Reg 0x19[4] =LSB                                                                         |  |

| 0x1B    | 4:0          |          | Reg 0x1B[3]=MSB                                                                          |  |

| OXID    | 7:5          |          | Break point                                                                              |  |

| 0x1C    | 7:0          | ВР       | Reg 0x1B[5] =LSB                                                                         |  |

|         | 2:0          |          | Reg 0x1D[2]=MSB                                                                          |  |

|         | 3            | MFER     | Magnetic field extended range $(1 = Bz, 0 = BzE)$                                        |  |

| 0x1D    | 4            | AER      | Angle extended range (set to 1 if the maximum angle excursion is smaller than 22 degree) |  |

|         | 6:5          | FILTER   | Post processing filter                                                                   |  |

|         | 7            | CUSLOCK  | Customer settings lock                                                                   |  |

| 0x1E    | 7:0          | SIGN     | Signature                                                                                |  |

Page 14

Document Feedback

Figure 17: **Volatile Memory Register Description**

| Address | Bit Position | Field       | R/W | Description                              |

|---------|--------------|-------------|-----|------------------------------------------|

| 0x22    | 7:0          | DAC12IN     | R/W | Input word of the 12-bit output DAC      |

|         | 3:0          | DACIZIN     | R/W | (Reg0x23[3] = MSB, Reg0x22[0] = LSB)     |

|         | 4            | DAC12INSEL  | R/W | DAC 12 input buffer selection            |

| 0x23    | 5            | DSPRN       | R/W | Digital signal processing reset          |

|         | 6            | GLOAD       | R/W | Enable of gload                          |

|         | 7            | -           | -   | Not used                                 |

| 0x32    | 7:0          | ANGLECORDIC | R   | Angle of the CORDIC output block.        |

| 0x33    | 5:0          | ANGLLCONDIC |     | (Reg0x33[5] = MSB, Reg0x32[0] = LSB)     |

| 0,33    | 7:6          | -           | -   | Not used                                 |

| 0x34    | 7:0          | MAG         | R   | CORDIC magnitude                         |

| 0x35    | 7:0          | AGC         | R   | AGC value                                |

| 0x36    | 7:0          | ANGLEFILTER | R   | Angle of the digital filter output block |

| 0x37    | 3:0          | ANGLEFILIER | n n | (Reg0x37[3] = MSB, Reg0x36[0] = LSB)     |

| 0x37    | 7:4          | -           | -   | Not used                                 |

Figure 18: Special Functions

| Address | Bit Position | Field   | Description                    |  |  |  |

|---------|--------------|---------|--------------------------------|--|--|--|

| 0x60    | 7:0          | P2F     | Pass-to-Function, see UART     |  |  |  |

| 0x61    | 7:0          | 1 21    | Tuss to Function, see O/MT     |  |  |  |

| 0x62    | 7:0          | BURNOTP | Permanently burn OTP, see UART |  |  |  |

| 0x63    | 7:0          | BORNOTI | Termanently built on, see oath |  |  |  |

Datasheet, Public Page 15 [v2-00] 2023-Sep-06 Document Feedback

#### **UART Interface**

The AS5171 is equipped with a UART interface, which allows reading and writing the registers as well as permanently programming the non-volatile memory (OTP). By default (factory setting, customer\_ lock = 0) the AS5171 is in the so-called *Communication Mode* and the UART is connected at the output pin (OUT). In this mode, the device is in open-drain mode and therefore a pull-up resistor has to be connected on the output.

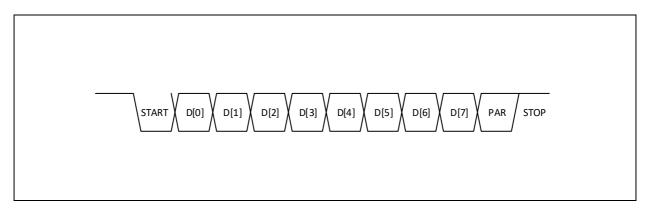

The UART interface allows reading and writing two consecutive addresses. The standard UART sequence consists of four frames. Each frame begins with a start bit (START), which is followed by 8 data bits (D[0:7]), one parity bit (PAR), and a stop bit (STOP), as shown in Figure 19.

Figure 19: UART Frame

The PAR bit is even parity calculated over the data bits (D[0:7]). Each frame is transferred from LSB to MSB.

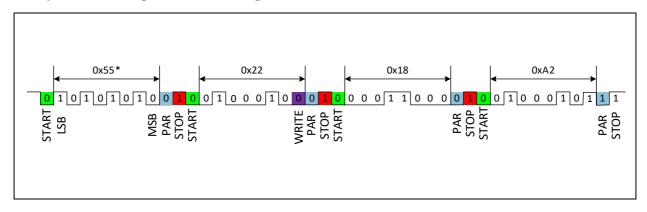

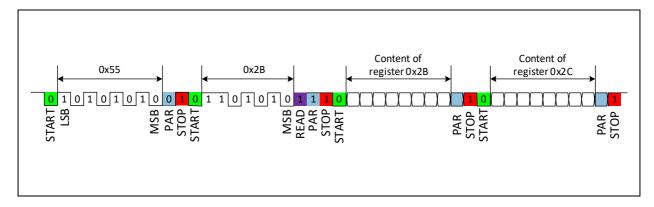

The four frames are shown in Figure 20.

Figure 20: UART Frame Sequence

| Frame Number | D[7]  | D[6]    | D[5] | D[4] | D[3]       | D[2] | D[1] | D[0] |

|--------------|-------|---------|------|------|------------|------|------|------|

| 1            |       |         |      | 0x5  | 5          |      |      |      |

| 2            | R/W   | ADDRESS |      |      |            |      |      |      |

| 3            | DATA1 |         |      |      |            |      |      |      |

| 4            |       |         |      | DATA | <b>A</b> 2 |      |      |      |

The first frame is the synchronization frame and consists of D[0:7] = 0x55 followed by the parity bit (PAR=0) and the stop bit. This frame synchronizes the baud rate between the AS5171 and the host microcontroller.

Page 16

Document Feedback

[v2-00] 2023-Sep-06

The second frame contains the read/write command (D[7] = 0 Write, D[7] = 1 Read) and the address of the register (D[6:0] = ADDRESS).

The content of the third and fourth frames (DATA1 and DATA2) will be written to or read from the location specified by ADDRESS and ADDRESS+1, respectively.

Figure 21 and Figure 22 show examples of read and write.

Figure 21: Example of Write (Reg[0x22] = 0x18, Reg[0x23] = 0xA2)

Figure 22: Example of Read (Reg[0x2B], Reg[0x2C])

## **Exiting Communication Mode**

Communication mode is exited and operational mode is entered with a Pass-to-function (P2F) command, by writing to the virtual registers 0x60 and 0x61:

P2F: write(0x60) = 0x70, write(0x61) = 0x51

No more commands can be sent after sending this command, because the device is permanently placed in operational mode.

## **Programming OTP Registers**

The BURNOTP command writes the OTP registers with their programmed values. The command is issued by writing to virtual registers 0x62 and 0x63:

BURNOTP: write(0x62) = 0x70, write(0x63) = 0x51.

Datasheet, PublicPage 17[v2-00] 2023-Sep-06Document Feedback

#### **Customer ID**

A specific identifier chosen by the user can be stored in the non-volatile memory. This identifier consists of 4 bytes and can be stored in the locations CUSTID0, CUSTID1, CUSTID2, and CUSTID3.

## **Output Linear Transfer Function**

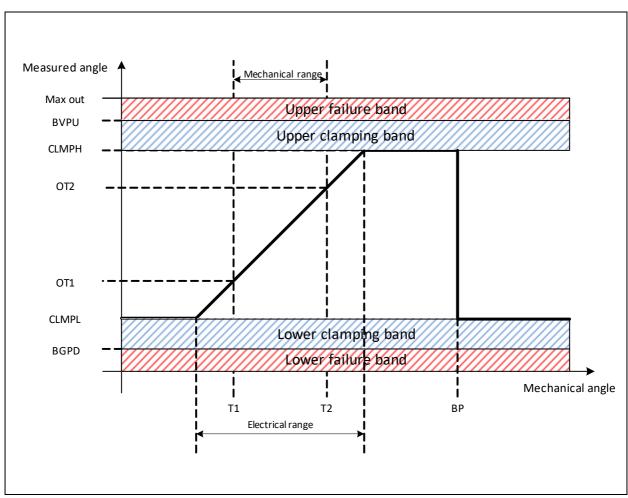

A linear transfer function controls the state of the output in response to the absolute orientation of the external magnet. The parameters which control this function are shown in Figure 23.

To calculate this settings into the corresponding sensor settings, ams OSRAM provides a programming tool, specific DLL or the complete source code. For more information, please contact ams OSRAM.

Figure 23: Transfer Function Control Parameters

| Symbol | Parameter                         | Resolution [bit] |

|--------|-----------------------------------|------------------|

| T1     | Mechanical angle starting point   | 14               |

| T2     | Mechanical angle stop point       | 14               |

| OT1    | Output at the starting point (T1) | 12               |

| OT2    | Output at the stop point (T2)     | 12               |

| CLMPL  | Clamping level low                | 12               |

| CLMPH  | Clamping level high               | 12               |

| ВР     | Breakpoint                        | 14               |

As shown in the Figure 24, the parameters T1, T2, OT1, and OT2 define the input-to-output linear transfer function. The dedicated programmer for the AS5171 uses the parameters from Figure 23 to generate the corresponding settings CLMPL, CLMPH, PPOFFSET, PPGAIN and BP (see Figure 24).

The clamping level parameters CLMPL and CLMPH define the absolute minimum and maximum level of the output. Both clamping levels can be set with the 12 LSBs out of the 12-bit output resolution. CLMPL and CLMPH must always be set outside of the lower and upper diagnostic failure band defined by the output broken wire voltage (see Figure 24, BGPD and BVPU).

Page 18Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

Figure 24: Output Transfer Function

The breakpoint BP sets the discontinuity point where the output jumps from one clamping level to the other. It is strongly recommended to set the breakpoint at the maximum distance from the start and stop position (T1 and T2). To handle the case of a full turn, a hysteresis function across the breakpoint can be used to avoid sudden jumps between the lower and upper clamping level.

Figure 25: Hysteresis Setting

| HYST | Hysteresis LSBs |

|------|-----------------|

| 00   | 0               |

| 01   | 56              |

| 10   | 91              |

| 11   | 137             |

The hysteresis LSB is based on the core resolution (14-bit).

Datasheet, PublicPage 19[v2-00] 2023-Sep-06Document Feedback

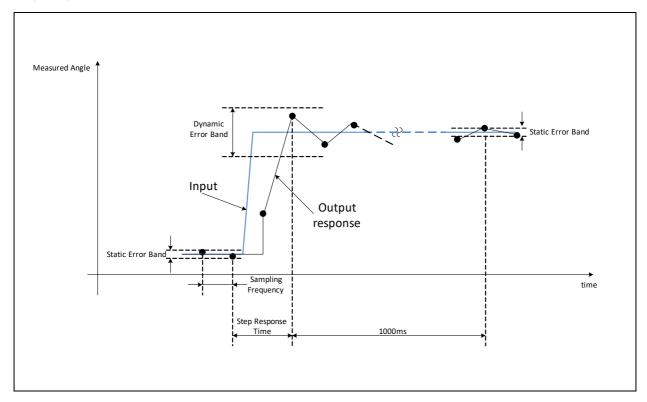

The AS5171 features a programmable digital filter. As shown in Figure 26 in a static condition (no change of the input), the static error band is  $\pm 0.5$  LSB (at 12-bit resolution). Whenever an input step occurs, the output (measured angle) follows the input (mechanical angle) entering a certain error band within the step response time. From the time when the output is within the static error band the output takes 1000 ms to settle to the static error band achieving again  $\pm 0.5$  LSB output noise. The filter is not usable in 360° range, if the Hysteresis setting is on.

Figure 26: Step Response

It is possible to optimize the step response time versus the dynamic error band with the FILTER setting.

Figure 27: FILTER Setting

| FILTER | Dynamic Error Band [LSB] | Step Response<br>Time [µs] |

|--------|--------------------------|----------------------------|

| 00     | Filter off               | Not applicable             |

| 01     | 23                       | 5 CORDIC cycles            |

Page 20Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

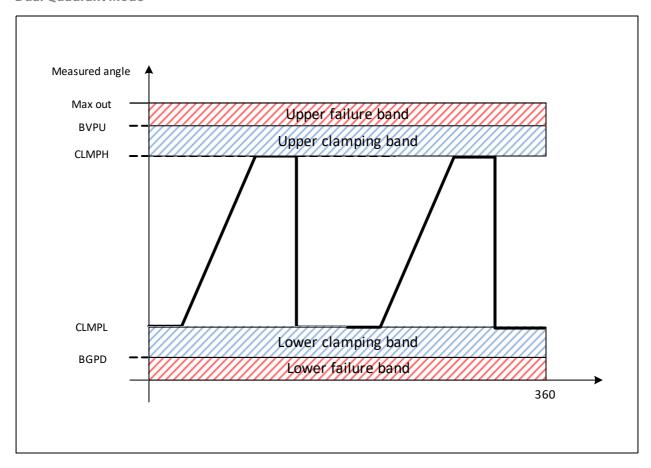

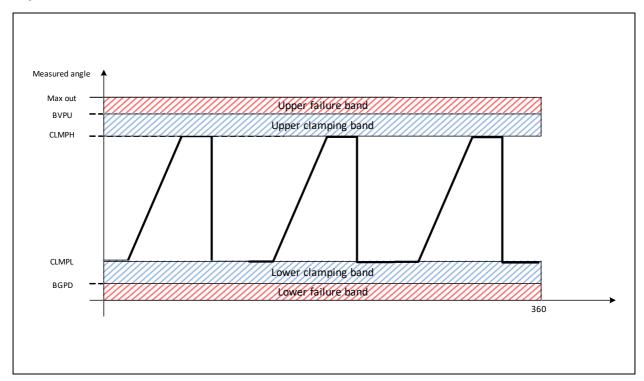

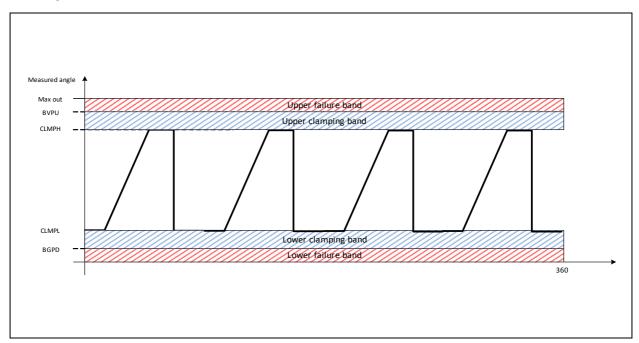

# **Multiple Quadrants**

The multiple quadrants option allows repeating the same output control parameters up to 4 times over the full turn rotation as shown in the Figure 29, Figure 30, and Figure 31. The QUAD parameter sets the number of quadrants, as shown in the Figure 28.

Figure 28: Number of Quadrants

| QUADEN | Number of Quadrants |

|--------|---------------------|

| 00     | Single              |

| 01     | Double              |

| 10     | Triple              |

| 11     | Quadruple           |

Figure 29: Dual Quadrant Mode

Datasheet, PublicPage 21[v2-00] 2023-Sep-06Document Feedback

Figure 30: Triple Quadrant Mode

Figure 31: Quadruple Quadrant Mode

Page 22 Document Feedback

## **Extended Magnetic Input Range**

The magnetic input field range can be boosted with the MFER bit. The extended magnetic field allows increasing the maximum air gap between the AS5171 and the magnet.

## Analog Output (AS5171E)

The AS5171E provides a linear analog ratiometric output signal. The output buffer features a push-pull analog output stage which can be loaded with a pull-down or a pull-up resistor. The output voltage represents the angular orientation of the magnet above the AS5171E on a linear absolute scale and is ratiometric to VDD.

#### PWM Output (AS5171B)

The AS5171B has a PWM output. With the DIGOS setting, the PWM output stage can be programmed as a push-pull, pull-down, or pull-up driver. The duty-cycle of each pulse is proportional to the absolute angular position of the external magnet.

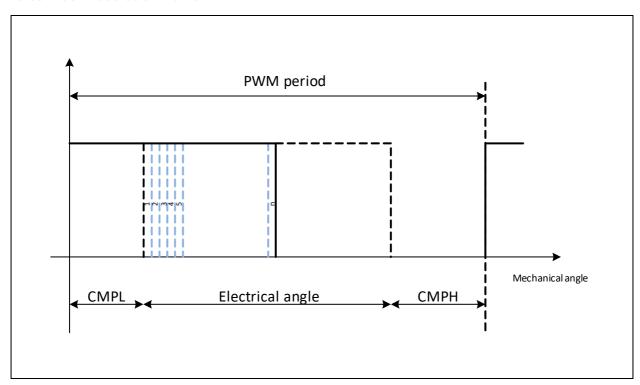

The PWM signal consists of a frame of 4096 clock periods as shown in Figure 32. The PWM frame begins with a certain number of clocks high, defined by the CLMPL, which is followed by the electrical angle information. The frame ends with a certain number of clock pulses low, as defined by the CLMPH. It is possible to invert the frame using the PWMINV setting.

Figure 32:

Pulse Width Modulation Frame

The PWMFR setting sets the duration of the PWM frequency. The PWMSR setting chooses between fast and slow steps.

Datasheet, PublicPage 23[v2-00] 2023-Sep-06Document Feedback

## **SENT Output**

The AS5171B provides a SENT-compatible output (Single Edge Nibble Transmission) interface which is compliant with the SAE-J2716 standard (Jan-2010) and features the Single Secure Sensor and the Single Sensor protocol (refer to SENT\_J2716\_ Standard - Appendix A.3 and A.4). SENT is a single-wire interface based on a unidirectional communication scheme from the sensor (transmitter) to the engine control unit (receiver). The sensor constantly transmits data to the receiver.

The SENT interface can be enabled on the AS5171B with the DIGOS setting.

The SENT frame consists of 8 nibbles in which each nibble is made up by 4 bits. The duration of the nibbles is variable and depends on its content and tick frequency. With the AS5171B, the tick frequency is selected by the SENTTK setting, as shown in the below figure.

Figure 33: SENT Tick Period

| SENTTK | SENT Tick Period (μs) |

|--------|-----------------------|

| 00000  | 3                     |

| 00001  | 4                     |

| 00010  | 4.5                   |

| 00011  | 5                     |

| 00100  | 5.5                   |

| 00101  | 5.75                  |

| 00110  | 6.5                   |

| 00111  | 6.75                  |

| 01000  | 7.5                   |

| 01001  | 8                     |

| 01010  | 8.5                   |

| 01011  | 9                     |

| 01100  | 9.5                   |

| 01101  | 10                    |

| 01110  | 10.25                 |

| 01111  | 10.5                  |

| 10000  | 10.75                 |

| 10001  | 11                    |

| SENTTK | SENT Tick Period (μs) |  |  |  |  |  |

|--------|-----------------------|--|--|--|--|--|

| 10010  | 11.25                 |  |  |  |  |  |

| 10011  | 11.5                  |  |  |  |  |  |

| 10100  | 11.75                 |  |  |  |  |  |

| 10101  | 12                    |  |  |  |  |  |

| 10110  | 12.25                 |  |  |  |  |  |

| 10111  | 12.5                  |  |  |  |  |  |

| 11000  | 2.25                  |  |  |  |  |  |

| 11001  | 2.5                   |  |  |  |  |  |

| 11010  | 2.75                  |  |  |  |  |  |

| 11011  | 3                     |  |  |  |  |  |

| 11100  | 3.25                  |  |  |  |  |  |

| 11101  | 3.5                   |  |  |  |  |  |

| 11110  | 3.5                   |  |  |  |  |  |

| 11111  | 3.5                   |  |  |  |  |  |

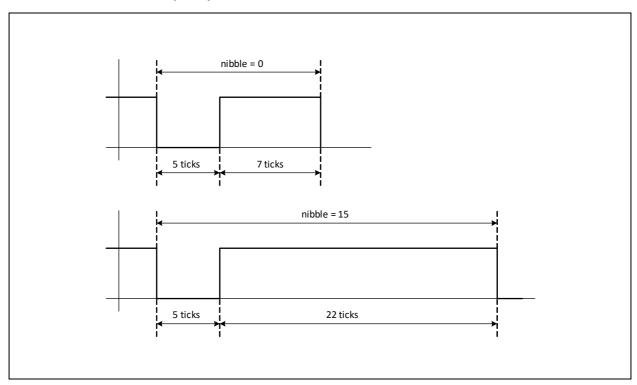

The nibble protocol consists of:

- 5 clock ticks low

- 7 clock ticks + n clock ticks high

Where n is the decimal representation of the 4-bit data. If the nibble data is zero (data = 0x00, n = 0) the nibble duration is 12 ticks, while if the nibble data is 15 (data = 0xFF, n = 15) its duration is 27 ticks.

Datasheet, PublicPage 25[v2-00] 2023-Sep-06Document Feedback

Figure 34: PWM Clock Period and Frequency

The SENT protocol consists of a 56-tick synchronization pulse followed by 8 nibbles. Each nibble is described in the below figure.

Figure 35: Nibble Description

| Nibble | Description                              |  |  |  |  |  |  |

|--------|------------------------------------------|--|--|--|--|--|--|

| 1      | Status and communication                 |  |  |  |  |  |  |

| 2      | Angle data most significant nibble       |  |  |  |  |  |  |

| 3      | Angle data middle significant nibble     |  |  |  |  |  |  |

| 4      | Angle data least significant nibble      |  |  |  |  |  |  |

| 5      | Rolling counter most significant nibble  |  |  |  |  |  |  |

| 6      | Rolling counter least significant nibble |  |  |  |  |  |  |

| 7      | Inverted nibble #2                       |  |  |  |  |  |  |

| 8      | CRC checksum                             |  |  |  |  |  |  |

The Status and Communication nibble includes diagnostic status and the Short Serial Message Format, as defined in the SAE J2716 protocol.

Page 26Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

Figure 36: **Status and Communication Nibble**

| Bit | Description                                      |  |  |  |  |  |

|-----|--------------------------------------------------|--|--|--|--|--|

| 0   | Error bit: 0 = No sensor error, 1 = Sensor error |  |  |  |  |  |

| 1   | 0 (always)                                       |  |  |  |  |  |

| 2   | Short Serial Message                             |  |  |  |  |  |

| 3   | Message Start                                    |  |  |  |  |  |

The Short Serial Message is transmitted one bit per SENT frame in bit 2 of consecutive frames and consists of 16 bits. The starting bit of a Short Serial Message is indicated by a 1 in bit 3 (Message Start) of the Status and Communication Nibble.

Figure 37: **Serial Message**

| SENT Message<br>Number     | 1 | 2    | 3    | 4 | 5 | 6 | 7 | 8 | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|----------------------------|---|------|------|---|---|---|---|---|----|----|----|----|----|----|----|----|

| Message Start              | 1 | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Short Serial<br>Message[2] |   | SENT | ΓMID | • |   |   | • | M | AG | •  |    |    |    | CF | RC |    |

The Short Serial Message consists of a message ID (SENTMID) and the magnitude of the magnetic field (MAG). The Short Serial Message is protected by a 4-bit CRC.

The SENTESM bit enables the Short Serial Message, which is otherwise by default disabled.

The angular information is contained in nibbles 2, 3 and 4. Nibbles 5 and 6 contain a rolling counter which counts the number of sent telegrams and rolls over to 0 after reaching the maximum value of 255. The rolling counter can be disabled, which is not needed in the Single Sensor mode, with the SENTRC bit. Because the tick clock period is 3 µs, the minimum duration of a SENT telegram is 456 µs, while the maximum duration is 816 µs. the SENTPP bit enables the Pause Pulse, which creates a SENT transmission with a constant duration of 272 ticks.

**Datasheet, Public** Page 27 **Document Feedback**

## **Diagnostic and Functional Safety**

AS5171 can be used in safety critical applications. For this reason, AS5171 is developed as SEooC (Safety element out of context) according the ISO26262, which assumed safety goals and assumed ASIL level.

The assumption of use (AoU) and the robust embedded self-diagnostic, to achieve a high ASIL level in the application, are described in the AS5171 safety manual.

For additional information regarding the ISO26262 flow at ams OSRAM and the SEooC relevant documents (e.g. FMEDA, safety manual) please contact the ams OSRAM technical support for magnetic position sensors.

Figure 38: Diagnostic Table

| SM   | Safety Mechanism                         | Recoverable                                                                                                   | Safe State                                                            |

|------|------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| SM1  | Watchdog failure                         | No, if a watchdog error is detected, the sensor provides the error information till a sensor reset happens    | Output is going into HIZ> failure band (depending on output resistor) |

| SM2  | Offset compensation not complete         | Yes, if the offset is below the specified threshold, sensor recovers the output                               | Output is forced in failure band. Depending on FBS setting            |

| SM3  | CORDIC overflow                          | Yes, if the magnetic input field is below<br>the specified threshold, sensor<br>recovers the output           | Output is forced in failure band. Depending on FBS setting            |

| SM4  | Magnetic input field<br>too high/too low | Yes, if the magnetic field is inside the specific range, after the recovery time the sensor leave the failure | Output is forced in failure band. Depending on FBS setting            |

| SM5  | Vreg undervoltage                        | Yes                                                                                                           | Hi-z: Failure band related to the out load                            |

| SM6  | Reverse polarity                         | Yes, if reverse polarity issue is solved.<br>No direct safety mechanism, it's a<br>protection!                | Hi-z: Failure band related to the out load                            |

| SM7  | VDD overvoltage                          | Yes, if the VDD is below the specified threshold.                                                             | Hi-z: Failure band related to the out load                            |

| SM8  | VDD undervoltage                         | Yes, if the VDD is above the specified threshold                                                              | Hi-z: Failure band related to the out load                            |

| SM9  | Broken VDD                               | Yes                                                                                                           | Hi-z: Failure band related to the out load                            |

| SM11 | Analog read fail                         | Yes                                                                                                           | Hi-z: Failure band related to the out load                            |

| SM12 | Short circuit                            | Yes                                                                                                           | Hi-z: Failure band related to the out load                            |

| SM13 | Signature                                | No, sensor stays in failure band till the sensor is resetting                                                 | Hi-z: Failure band related to the out load                            |

Page 28Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

| SM   | Safety Mechanism | Recoverable | Safe State                                 |

|------|------------------|-------------|--------------------------------------------|

| SM14 | Broken GND       | Yes         | Hi-z: Failure band related to the out load |

The FBS setting allows selecting the failure band (lower or upper) when the output goes into diagnostic mode.

## **Diagnostic Explanations**

For a detailed explanation of the diagnostic and the SPFM please contact the ams OSRAM application team for magnetic position sensor.

# Analog Read Fail (SM11)

This safety mechanism operates differently for AS5171E (analog) and AS5171B (digital):

For AS5171B readout failure: After a falling edge there

must be a rising edge after a defined time.

In case this is not respected output driver is kept in high

impedance. After a certain time this condition is checked

again.

The readout mechanism for AS5171B is defined by PWMRTH and PWMFTH, which set the maximum timeout period to wait for a falling/rising before triggering an error condition, according to the figures below.

Figure 39: PWMRTH Conditions

| PWM | IRTH | Delay (μs)                  |  |  |  |

|-----|------|-----------------------------|--|--|--|

| 0   | 0    | PWM Read Back rise disabled |  |  |  |

| 0   | 1    | 24-28                       |  |  |  |

| 1   | 0    | 56-60                       |  |  |  |

| 1   | 1    | 112-120                     |  |  |  |

Figure 40: PWMFTH Conditions

| PWM | 1FTH | Delay (μs)                  |

|-----|------|-----------------------------|

| 0   | 0    | PWM Read Back fall disabled |

| 0   | 1    | 24-28                       |

| 1   | 0    | 56-60                       |

| 1   | 1    | 112-120                     |

Datasheet, PublicPage 29[v2-00] 2023-Sep-06Document Feedback

• For AS5171E readout failure: Comparison of the analog output information versus the digital information of the sensor. If the difference is too high output driver is kept in high impedance. After a certain time this condition is checked again.

The readout mechanism for AS5171E is defined by RDBCKDEB, which set the maximum timeout period to wait before triggering an error condition, according to the tables below.

Figure 41: AS5171E Readout Mechanisms

| RDBCKDEB02 | RDBCKDEB01 | RDBCKDEB00 | CORDIC<br>Cycles <sup>(1)</sup> | Note                      |

|------------|------------|------------|---------------------------------|---------------------------|

| 0          | 0          | 0          | 0                               | Analog Read Back disabled |

| 0          | 0          | 1          | 1                               |                           |

| 0          | 1          | 0          | 2                               |                           |

| 0          | 1          | 1          | 4                               |                           |

| 1          | 0          | 0          | 8                               |                           |

| 1          | 0          | 1          | 16                              |                           |

| 1          | 1          | 0          | 32                              |                           |

| 1          | 1          | 1          | 64                              |                           |

#### Note(s):

1. 1 CORDIC cycle typ.:111µs

Page 30Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

# **Application Information**

# **Signature Calculation**

The OTP of AS5171E and AS5171B uses a BIST technique with Multiple Input Signature Register circuits.

To activate this BIST a calculation of the Signature Byte is necessary and has to store into the OTP during the programming sequence.

For calculating the signature byte the content of the whole memory (0x02 to 0x1D) has to be read.

Out of this information the following calculation has to be done.

Byte: 0x02 = data2 .... Byte: 0x1D = data29

```

Unsigned int signature (unsigned int * content)

unsigned int misr,misr_shift,misr_xor,misr_msb;

misr = 0;

for (int i=0; i<28; i++) {

misr_shift = (misr<<1);

misr_xor = (misr_shift ^ content[i])%256;

misr_msb = misr/(128);

if (misr_msb == 0)

misr = misr_xor;

else

misr = (misr_xor ^ 29)%256;

return misr;

}

content= {,data2,data3,data4,data5,data6,

data7,data8,data9,data10,data11,

data12,data13,data14,data15,data16,

data17,data18,data19,data20,data21,data22,

data23,data24,data25,data26,data27,data28,data29};

```

Datasheet, PublicPage 31[v2-00] 2023-Sep-06Document Feedback

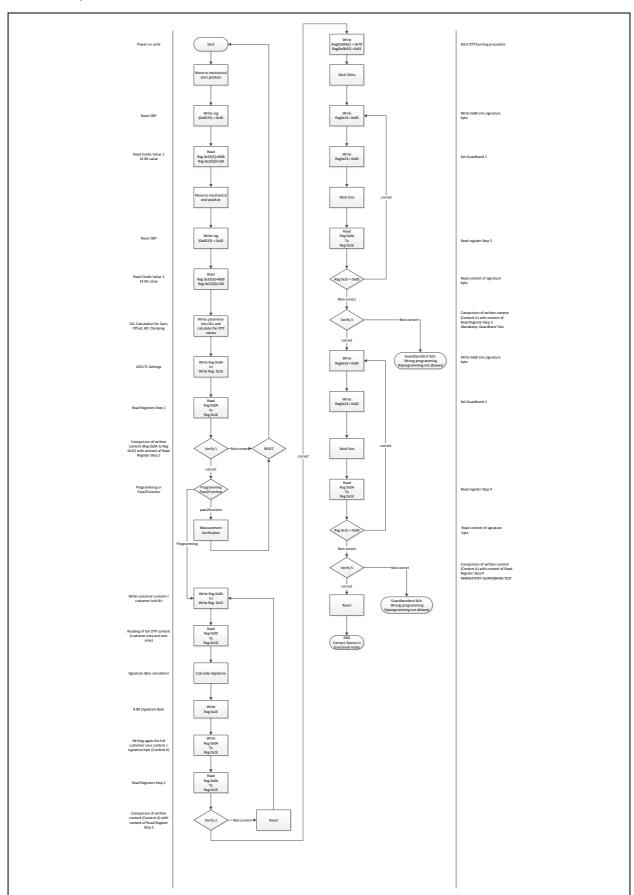

## **Programming Parameter**

The programming has to be performed in communication mode. If the cust\_lock=0, the sensor starts in communication mode.

The following procedure and the block diagram are showing the common 2 point calibration. For special calibration procedure:

AS5171E: Analog output driver calibration

AS5171E/AS5171B: Linearization.

Please go in contact with the ams OSRAM application team.

# **Burn and Verification of the OTP Memory**

- 1. Power on cycle

- 2. Move magnet to the first mechanical start position

- 3. Reset the DSP. Writing 0x20 into Reg(0x0023)

- 4. Read out the measured angle from ANGLECORDIC register: T1 Value

- 5. Moving of magnet to the second mechanical position (stop position)

- 6. Read out the measured angle from ANGLECORDIC register: T2 Value

- 7. Write T1,T2 and all other transfer parameter into the DLL: Calculation of GAIN, Offset, BP, Clamping

- 8. Write reg(0x000A) to reg (0x001E) with the custom settings and the calculated values from point 7. --> AS5171 Settings

- Read reg(0x000A) to reg (0x001E) ---> Read register step 1

- 10. Comparison of AS5171 settings with content of read register step 1

- 11. If point 10 is correct: Decision: pass 2 function (measurement verification) or programming. Programming sequence starts with point 12.

- 12. Write reg(0x000A) to reg (0x001E) with the custom settings and the calculated values from point 7 + customer lock Bit. --> AS5171 Settings\_Prog

- 13. Read reg(0x0000) to reg (0x001D) ---> Read register step 2

- 14. Calculation of Signature Byte out of Read register step2 content: Signature Byte

- 15. Write 8-bit Signature to reg(0x001E)

- 16. Write reg(0x000A) to reg (0x001E) with the custom settings and the calculated values from point 7 + customer lock Bit + Signature byte. --> AS5171 Settings\_ Prog\_final

Page 32Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

- 17. Read reg(0x000A) to reg (0x001E) ---> Read register step 3

- 18. Comparison of AS5171 Settings\_Prog\_final with content of read register step 3

- 19. If point 18 is correct, start the OTP burn procedure by writing: Reg(0x0062)=0x70 and Reg(0x0063)=0x51

- 20. Programming procedure is complete after 10ms

- 21. Clear the memory content writing 0x00 into reg (0x001E)

- 22. Write Reg0x23=0x40 to set the threshold for the guard band test (1)

- 23. 5ms wait time to refresh the non-volatile memory content with the OTP content

- 24. Read reg(0x000A) to reg (0x001E) ---> Read register step 4

- 25. If content from reg (0x001E) compares with content from "Signature Byte" refresh was successful

- 26. Comparison of AS5171 Settings\_Prog\_final with content of read register step 4. Mandatory: guard band test (1).

- 27. If point 26 fails, the test with the guard band (1) was not successful and the device is incorrectly programmed. A reprogramming is not allowed.

- 28. Clear the memory content writing 0x00 into reg (0x001E)

- 29. Write Reg0x23=0x00to set the threshold for the guard band test (1)

- 30. 5ms wait time to refresh the non-volatile memory content with the OTP content

- 31. Read reg(0x000A) to reg (0x001E) ---> Read register step 5

- 32. If content from reg (0x001E) compares with content from "Signature Byte" refresh was successful

- 33. Comparison of AS5171 Settings\_Prog\_final with content of read register step 5. Mandatory: guard band test (1)

- 34. If point 33 fails, the test with the guard band (1) was not successful and the device is incorrectly programmed. A reprogramming is not allowed.

- 35. Reset of the device. After power on the Sensor starts in functional mode

#### Note(s):

1. Guard band test: Restricted to temperature range:  $25^{\circ}C \pm 20^{\circ}C$  Right after the programming procedure (max. 1 hour with same Conditions  $25^{\circ}C \pm 20^{\circ}C$ ) Same VDD voltage

Datasheet, PublicPage 33[v2-00] 2023-Sep-06Document Feedback

The guard band test is only for the verification of the burned OTP fuses during the programming sequence.

A use of the guard band in other cases is not allowed.

Page 34 Datasheet, Public **Document Feedback** [v2-00] 2023-Sep-06

amu

Figure 42: OTP Memory Burn and Verification Flowchart

Datasheet, PublicPage 35[v2-00] 2023-Sep-06Document Feedback

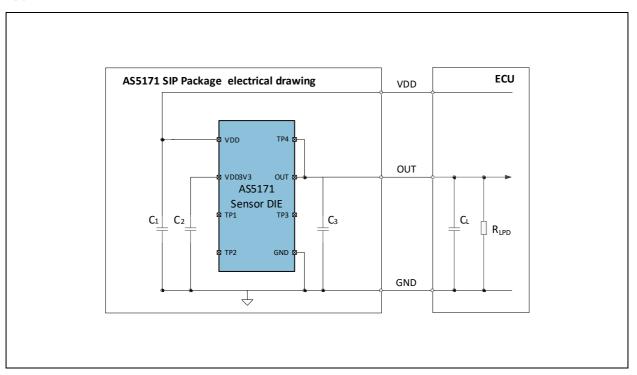

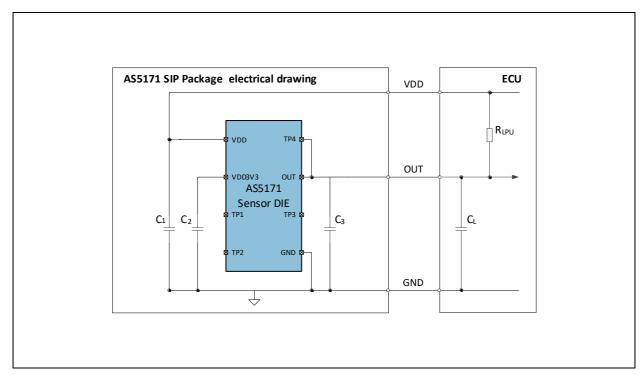

# Recommended Application Diagrams and Built-In Capacitors

Figure 43:

Application with Pull-Down Load Resistor

Figure 44:

Application with Pull-Up Load Resistor

Page 36Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

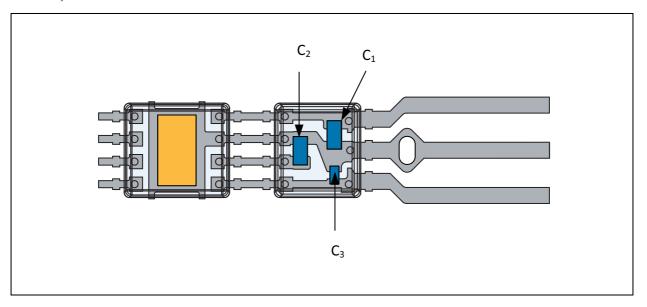

Figure 43 and Figure 44 show the recommended schematic in the application.  $C_1$ ,  $C_2$  and  $C_3$  are Built-in capacitors in the SIP Package as shown in Figure 49.

Figure 45: SIP Components

The built-in capacitors are ceramic multilayer type X8R. The capacitors build for high temperature applications up to 150°C

# **Components Spec**

Figure 46: SIP Components and Recommended ECU Components for AS5171E

| Component                       | Symbol           | Min  | Тур | Max  | Unit | Notes               |  |  |

|---------------------------------|------------------|------|-----|------|------|---------------------|--|--|

| SIP Component                   |                  |      |     |      |      |                     |  |  |

| VDD buffer capacitor            | C <sub>1</sub>   | 90   | 100 | 110  | nF   | Included in the SIP |  |  |

| VDD3V3 regulator capacitor      | C <sub>2</sub>   | 90   | 100 | 110  | nF   | Included in the SIP |  |  |

| OUT load capacitor (sensor PCB) | C <sub>3</sub>   | 4,23 | 4.7 | 5,17 | nF   | Included in the SIP |  |  |

| ECU Component                   |                  |      |     |      |      |                     |  |  |

| OUT load capacitor (ECU)        | C <sub>L</sub>   | 0    |     | 33   | nF   |                     |  |  |

| OUT pull-up resistance          | R <sub>LPU</sub> | 4    |     | 10   | kΩ   |                     |  |  |

| OUT pull-down resistance        | R <sub>LPD</sub> | 4    |     | 10   | kΩ   |                     |  |  |

Datasheet, PublicPage 37[v2-00] 2023-Sep-06Document Feedback

Figure 47: SIP Components and Recommended ECU Components for AS5171B With PWM

| Component                       | Symbol           | Min  | Тур | Max  | Unit | Notes               |  |

|---------------------------------|------------------|------|-----|------|------|---------------------|--|

| SIP Component                   |                  |      |     |      |      |                     |  |

| VDD buffer capacitor            | C <sub>1</sub>   | 90   | 100 | 110  | nF   | Included in the SIP |  |

| VDD3V3 regulator capacitor      | C <sub>2</sub>   | 90   | 100 | 110  | nF   | Included in the SIP |  |

| OUT load capacitor (sensor PCB) | C <sub>3</sub>   | 4,23 | 4.7 | 5,17 | nF   | Included in the SIP |  |

| ECU Component                   |                  |      |     |      |      |                     |  |

| OUT load capacitor (ECU)        | C <sub>L</sub>   | 0    |     | 33   | nF   |                     |  |

| OUT pull-up resistance          | R <sub>LPU</sub> | 1    |     | 10   | kΩ   |                     |  |

| OUT pull-down resistance        | R <sub>LPD</sub> | 1    |     | 10   | kΩ   |                     |  |

# Information Regarding Manufacturability of AS5171E and AS5171B

For the SIP Package which is used for AS5171E and AS5171B, please refer to the following document (available upon request):

Application Note SIP Dual Mold Package

Page 38Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

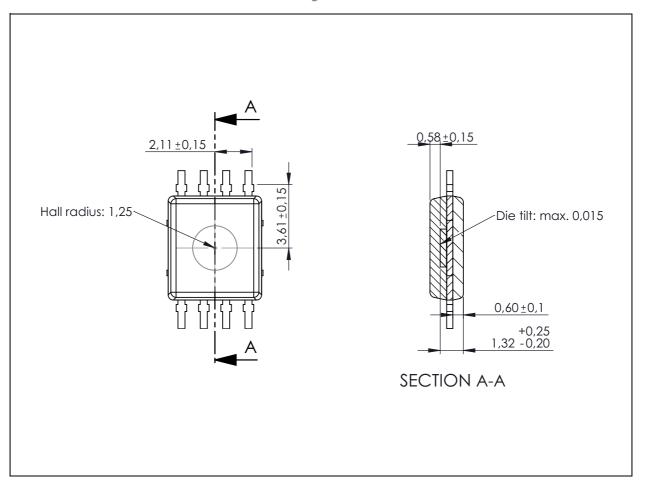

## **Mechanical Data**

The internal Hall elements are placed in the center of the header package on a circle with a radius of 1.25mm.

Figure 48: Hall Element Positions in the Header of SIP Package

#### Note(s):

- 1. All dimensions in mm.

- 2. Tolerances shown represent expected values and are to be verified. Tolerances will be guaranteed prior to product release.

Datasheet, PublicPage 39[v2-00] 2023-Sep-06Document Feedback

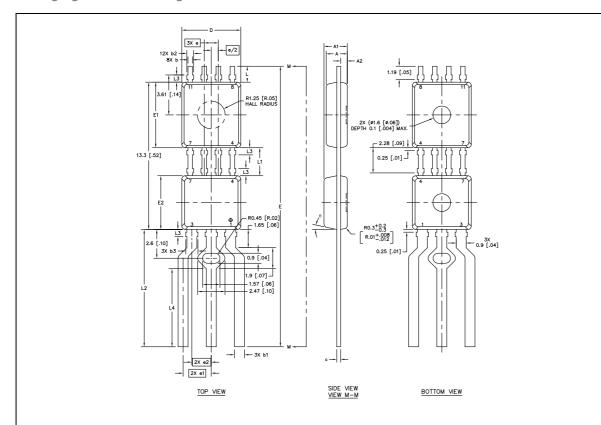

# **Package Drawings & Markings**

Figure 49: Packaging Outline Drawing (SIP)

|                 |            | Symbol | Min      | Nom      | Max   | Min       | Nom   | Max   |

|-----------------|------------|--------|----------|----------|-------|-----------|-------|-------|

| Total Thickness |            | Α      | 1.75     | 1.9      | 2.05  | 0.069     | 0.075 | 0.081 |

|                 |            | A1     | 1.95     | 2.1      | 2.25  | 0.077     | 0.083 | 0.089 |

| Mold Thicknes   | SS         | A2     | 0.5      | 0.6      | 0.7   | 0.020     | 0.024 | 0.028 |

|                 |            | b      | 0.35     | 0.4      | 0.45  | 0.014     | 0.016 | 0.018 |

| Lead Width      |            | b1     | 8.0      | 0.9      | 1     | 0.031     | 0.035 | 0.039 |

| Lead Width      |            | b2     | 0.45     | -        | 0.65  | 0.018     | -     | 0.026 |

|                 |            | b3     | 0.9      | -        | 1.2   | 0.035     | -     | 0.047 |

| L/F Thickness   |            | С      | 0.3      | 0.35     | 0.45  | 0.012     | 0.014 | 0.018 |

|                 | Х          | D      | 5.16     | 5.31     | 5.46  | 0.203     | 0.209 | 0.215 |

| Body Size       | Υ          | E1     | 5.77     | 5.92     | 6.07  | 0.227     | 0.233 | 0.239 |

|                 | Υ          | E2     | 4.7      | 4.85     | 5     | 0.185     | 0.191 | 0.197 |

|                 |            | E      | 25.19    | 25.34    | 25.49 | 0.992     | 0.998 | 1.004 |

| Lead Pitch      | Lead Pitch |        | 1.27 BSC |          |       | 0.050 BSC |       |       |

|                 |            | e1     | 2.54 BSC |          |       | 0.100 BSC |       |       |

|                 |            | e2     |          | 1.75 BSC |       | 0.069 BSC |       |       |

| Footprint       |            | L      | 1.29     | 1.44     | 1.64  | 0.051     | 0.057 | 0.065 |

|                 |            | L1     | 2.43     | 2.53     | 2.63  | 0.096     | 0.100 | 0.104 |

|                 |            | L2     | 10.4     | 10.6     | 10.85 | 0.409     | 0.417 | 0.427 |

|                 |            | L3     | 0.5      | 0.65     | 0.85  | 0.020     | 0.026 | 0.033 |

|                 |            | L4     | 6.85     | 7.05     | 7.3   | 0.270     | 0.278 | 0.287 |

|                 |            | θ      | 10°      | 12°      | 14°   | 10°       | 12°   | 14°   |

#### Note(s):

- 1. Dimension D does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.3mm (0.012in) per side.

- 2. Dimension b and b1 does not include dam bar protrusion an matte tin plating.

Allowable dam bar protrusion shall be 0.3mm (0.012in) total in excess of the b, b1, b2 and b3 dimension at maximum material condition.

- 3. Dimension E1 and E2 does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.3mm (0.012in) per side.

Page 40Datasheet, PublicDocument Feedback[v2-00] 2023-Sep-06

4. Dimension tolerance: ±0.15mm unless otherwise specified.

# Marking

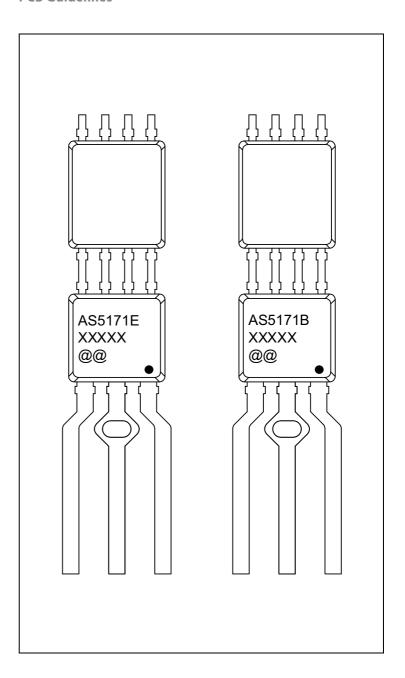

Figure 50: **PCB** Guidelines

Page 41 **Datasheet, Public** [v2-00] 2023-Sep-06 Document Feedback

Figure 51: Package Marking

Figure 52: Packaging Code

| XXXXX          | @@                |

|----------------|-------------------|

| TC_5 Tracecode | Sublot Identifier |

# **Ordering & Contact Information**

Figure 53: Ordering Information

| Ordering Code | Package | Marking | Delivery Form               | Delivery Quantity |

|---------------|---------|---------|-----------------------------|-------------------|

| AS5171E-HSIT  | SIP     | AS5171E | 13" Tape & Reel in dry pack | 2000 pcs/reel     |

| AS5171B-HSIT  | SIP     | AS5171B | 13" Tape & Reel in dry pack | 2000 pcs/reel     |

Please visit our website at ams-osram.com

For information about our products go to Products

For technical support use our Technical Support Form

For feedback about this document use Document Feedback

For sales offices and branches go to Sales Offices / Branches

For distributors and sales representatives go to Channel

Partners

#### Headquarters

ams-OSRAM AG Tobelbader Strasse 30 8141 Premstaetten Austria, Europe

Tel: +43 (0) 3136 500 0

Datasheet, PublicPage 43[v2-00] 2023-Sep-06Document Feedback

# ams OSRAM Semiconductor RoHS Compliance Statement

**RoHS Compliant:** The term RoHS compliant means that ams-OSRAM AG semiconductor products fully comply with current RoHS directives. Our semiconductor products do not contain any chemicals for all 6 substance categories plus additional 4 substance categories (per amendment EU 2015/863), including the requirement that lead not exceed 0.1% by weight in homogeneous materials.