## **AS1130**

# 132-LED Cross-Plexing Driver with Scrolling Function

#### **General Description**

The AS1130 is a compact LED driver for 132 single LEDs. The devices can be programmed via an I<sup>2</sup>C compatible interface. The AS1130 offers a 12x11 LED-matrix with 1/12 cycle rate. The required lines to drive all 132 LEDs are reduced to 12 by using the cross-plexing feature optimizing space on the PCB. The whole LED-matrix driving 132 LEDs can be analog dimmed from 0mA to 30mA in 256 steps (8 bit).

Additionally each of the 132 LEDs can be dimmed individually with 8-bit allowing 256 steps of linear dimming. To reduce CPU usage up to 6 frames can be stored with individual time delays between frames to play small animations automatically.

The AS1130 operates from 2.7V to 5.5V and features a very low shutdown and operational current.

The device offers a programmable IRQ pin. Via a register it can be set on what event (CP\_Request, Interface Timeout, Error-detection, POR, End of Frame or End of Movie) the IRQ is triggered.

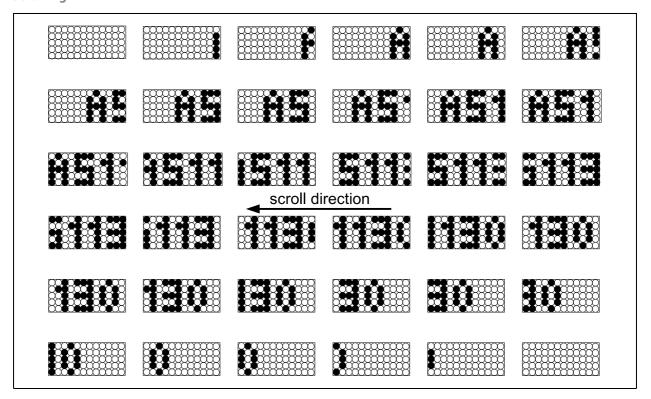

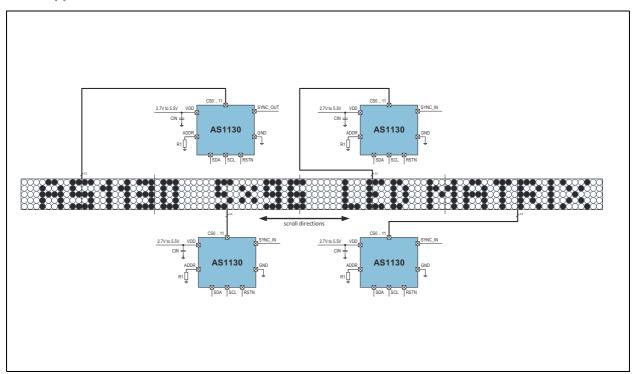

Also hardware scroll function is implemented in the AS1130.

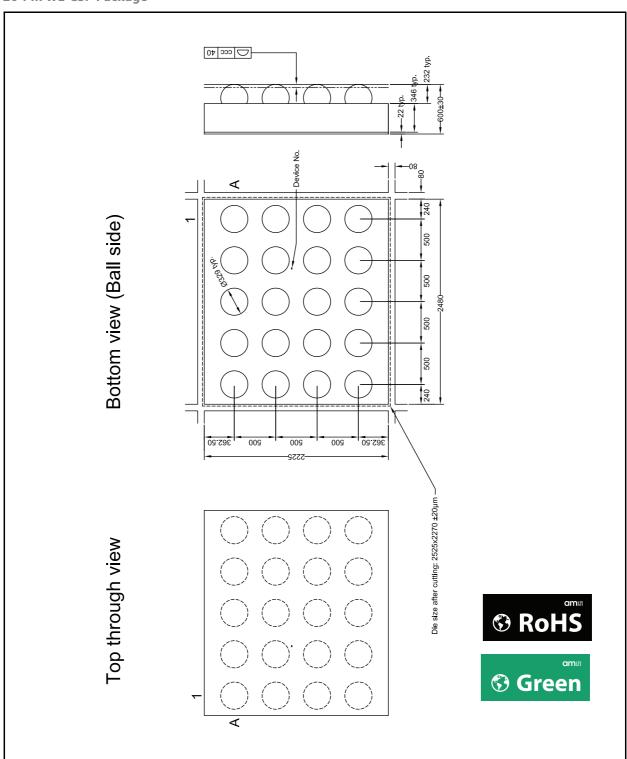

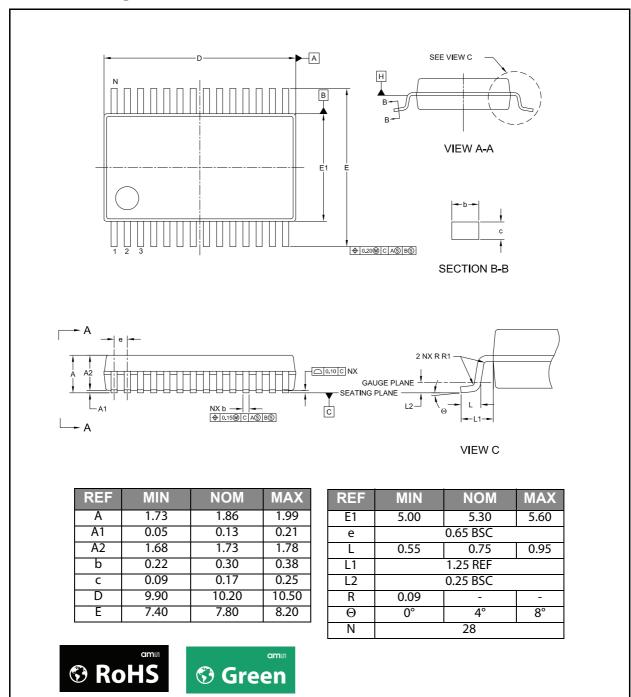

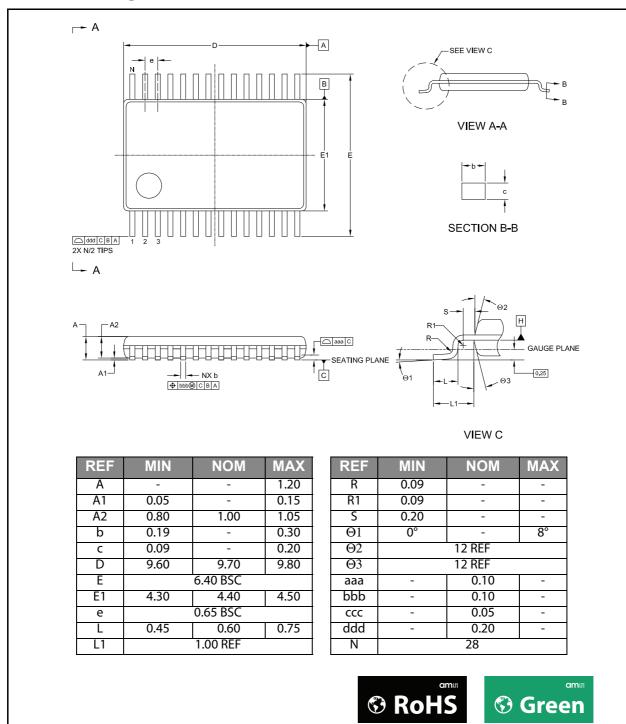

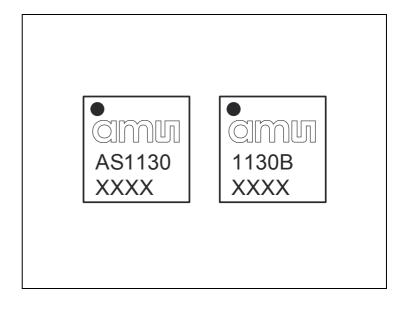

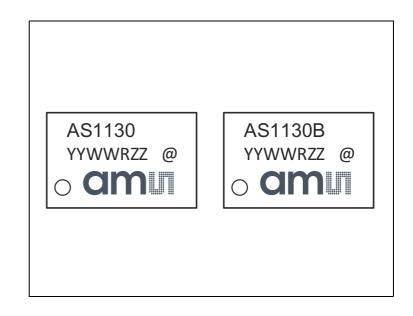

The device is available in an ultrasmall 20-Pin WL-CSP and an easy to solder 28-pin SSOP/TSSOP package.

Ordering Information and Content Guide appear at end of datasheet.

#### **Key Benefits & Features**

The benefits and features of AS1130, 132-LED Cross-Plexing Driver with Scrolling Function are listed below:

Figure 1: Added Value of Using AS1130

| Benefits                                                     | Features                                       |

|--------------------------------------------------------------|------------------------------------------------|

| Worlds lowest PCB real estate vs LED count                   | • Up to 132 LEDs in a 12x11 matrix             |

| 16.7M full color matrix with white balance                   | 8-bit PWM per LED and current control per line |

| Reduces MCU load and increases battery<br>lifetime           | 36 frames of memory with scrolling option      |

| Identifies defect LEDs and "removes" them<br>from the matrix | Error detection and correction                 |

### **Applications**

The AS1130 is ideal for dot matrix displays in mobile phones, personal electronics and toys.

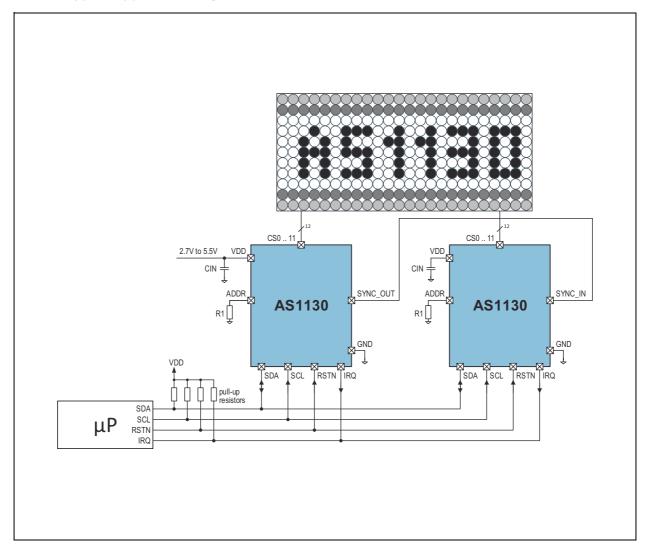

Figure 2: AS1130- Typical Application Diagram

Page 2ams DatasheetDocument Feedback[v2-01] 2016-Oct-12

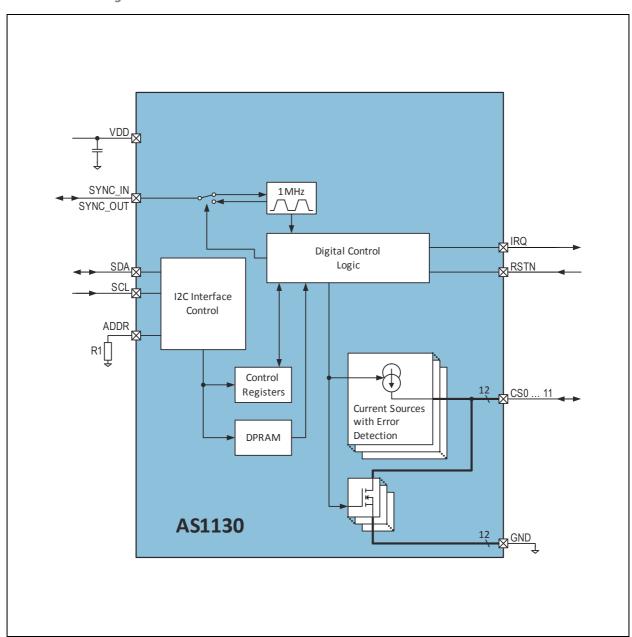

#### **Block Diagram**

The functional blocks of this device are shown below:

Figure 3: AS1130 Block Diagram

ams Datasheet Page 3

[v2-01] 2016-Oct-12

Document Feedback

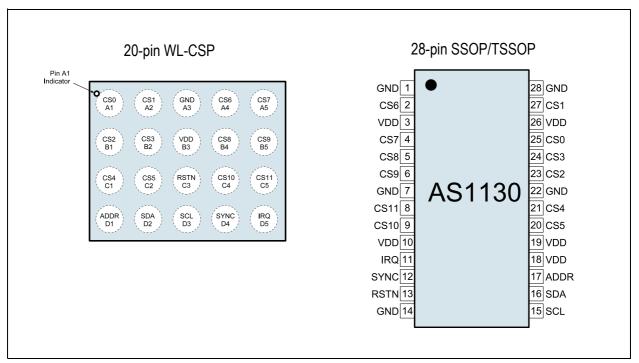

### **Pin Assignment**

Figure 4: Pin Diagram (Top View)

Figure 5: Pin Description

| Pin N            | lumber                    |          |                                                                                                                                                           |  |  |  |  |  |

|------------------|---------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 20-Pin<br>WL-CSP | 28-Pin<br>SSOP /<br>TSSOP | Pin Name | Description                                                                                                                                               |  |  |  |  |  |

| А3               | 1, 7, 14, 22, 28          | GND      | Ground                                                                                                                                                    |  |  |  |  |  |

| C3               | 13                        | RSTN     | <b>Reset Input</b> . Pull this pin to logic low to reset all control registers (set to default values). For normal operation pull this pin to VDD.        |  |  |  |  |  |

| D1               | 17                        | ADDR     | I <sup>2</sup> C Address. Connect to external resistor for I <sup>2</sup> C address selection. Up to 8 devices can be connected on one bus. See Figure 30 |  |  |  |  |  |

| D2               | 16                        | SDA      | <b>Serial-Data I/O</b> . Open drain digital I/O I <sup>2</sup> C data pin.                                                                                |  |  |  |  |  |

| D3               | 15                        | SCL      | Serial-Clock Input                                                                                                                                        |  |  |  |  |  |

Page 4ams DatasheetDocument Feedback[v2-01] 2016-Oct-12

| Pin N                                                | lumber                                         |                                                                    |                                                                                                                                                                                                                                       |

|------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-Pin<br>WL-CSP                                     | 28-Pin<br>SSOP /<br>TSSOP                      | Pin Name                                                           | Description                                                                                                                                                                                                                           |

| В3                                                   | 3, 10, 18, 19, 26                              | VDD                                                                | <b>Positive Supply Voltage</b> . Connect to a +2.7V to +5.5V supply. Bypass this pin with 10μF capacitance to GND.                                                                                                                    |

| D4                                                   | 12                                             | SYNC                                                               | Synchronization Clock Input or Output. The SYNC frequency for Input and Output is 1MHz. For SYNC_OUT the frequency can be reduced to 32kHz.                                                                                           |

| D5                                                   | 11                                             | IRQ                                                                | Interrupt Request. Programmable Open drain digital Output. It can be set via an register after which event (Interface Timeout, POR, CP_Request, Error Detection, End of Frame or End of Movie) the pin triggers an Interrupt Request. |

| A1, A2, A4, A5,<br>B1, B2, B4, B5,<br>C1, C2, C4, C5 | 25, 27, 2, 4,<br>23, 24, 5, 6,<br>21, 20, 9, 8 | CS0, CS1, CS6, CS7,<br>CS2, CS3, CS8, CS9,<br>CS4, CS5, CS10, CS11 | Sinks and Sources for 132 LEDs.                                                                                                                                                                                                       |

#### **Absolute Maximum Ratings**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 6: **Absolute Maximum Ratings**

| Parameter                                     | Min  | Max                           | Units       |                          | Comments                                                                                               |  |  |  |  |  |  |

|-----------------------------------------------|------|-------------------------------|-------------|--------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                               |      | Electri                       | ical Param  | eters                    |                                                                                                        |  |  |  |  |  |  |

| V <sub>DD</sub> to GND                        | -0.3 | 7                             | V           |                          |                                                                                                        |  |  |  |  |  |  |

| All other pins to GND                         | -0.3 | 7 or<br>V <sub>DD</sub> + 0.3 | V           |                          |                                                                                                        |  |  |  |  |  |  |

| Sink Current                                  |      | 500                           | mA          |                          |                                                                                                        |  |  |  |  |  |  |

| Segment Current                               |      | 100                           | mA          |                          |                                                                                                        |  |  |  |  |  |  |

| Input Current (latch-up immunity)             | -100 | 100                           | mA          | JEDEC 78                 |                                                                                                        |  |  |  |  |  |  |

| Electrostatic Discharge                       |      |                               |             |                          |                                                                                                        |  |  |  |  |  |  |

| Electrostatic Discharge<br>(human body model) |      | ±2                            | kV          | MIL 883 E method 3015    |                                                                                                        |  |  |  |  |  |  |

|                                               | Temp | erature Rang                  | ges and Sto | orage Condi              | tions                                                                                                  |  |  |  |  |  |  |

| Junction Temperature                          |      | 150                           | ۰C          |                          |                                                                                                        |  |  |  |  |  |  |

| Storage Temperature                           | -55  | 125                           | ۰C          | For 20-Pin               | WL-CSP                                                                                                 |  |  |  |  |  |  |

| Range                                         | -55  | 150                           | ۰C          | For 28-pin               | SSOP/TSSOP                                                                                             |  |  |  |  |  |  |

| Package Body<br>Temperature                   |      | 260                           | °C          | 28-pin<br>SSOP/<br>TSSOP | IPC/JEDEC J-STD-020 <sup>(1)</sup> The lead finish for Pb-free leaded packages is matte tin (100% Sn). |  |  |  |  |  |  |

| remperature                                   |      |                               |             | 20-Pin<br>WL-CSP         | IPC/JEDEC J-STD-020 <sup>(1)</sup>                                                                     |  |  |  |  |  |  |

| Relative Humidity<br>(non-condensing)         | 5    | 85                            | %           |                          |                                                                                                        |  |  |  |  |  |  |

|                                               |      | 1                             |             | 20-Pin<br>WL-CSP         | Represents an unlimited floor life time                                                                |  |  |  |  |  |  |

| Moisture Sensitivity Level                    |      | 3                             |             | 28-pin<br>SSOP/<br>TSSOP | Represents a max. floor life time of 168h                                                              |  |  |  |  |  |  |

ams Datasheet [v2-01] 2016-Oct-12

**Document Feedback**

$<sup>1.</sup> The reflow peak soldering temperature (body temperature) is specified according IPC/JEDEC J-STD-020 \verb§"Moisture/Reflow Sensitivity" according IPC/JEDEC J-STD-020 \verb§"Moisture/Reflow Sensitivity According IPC/JEDEC J-STD-020 \verb§"Moisture/Reflow Sensitivi$ Classification for Nonhermetic Solid State Surface Mount Devices".

#### **Electrical Characteristics**

$V_{DD}$  = 2.7V to 5.5V, typ. values are at  $T_{AMB}$  = 25°C (unless otherwise specified). All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 7: Electrical Characteristics

| Symbol               | Parameter                                                                                     | Conditions                                                                            | Min | Тур   | Max | Unit |

|----------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|-------|-----|------|

| T <sub>AMB</sub>     | Operating Temperature Range                                                                   |                                                                                       | -40 |       | 85  | °C   |

| Тј                   | Operating Junction<br>Temperature Range                                                       |                                                                                       | -40 |       | 125 | °C   |

| V <sub>DD</sub>      | Operating Supply Voltage                                                                      |                                                                                       | 2.7 |       | 5.5 | V    |

| I <sub>DD</sub>      | Operating Supply Current                                                                      | All current sources turned ON, @ V <sub>DD</sub> = 5.5V                               |     | 340   |     | mA   |

| -00                  | operating supply current                                                                      | All current sources<br>turned OFF, @ V <sub>DD</sub> = 5.5V                           |     | 0.5   |     |      |

| I <sub>DDSSD</sub>   | Software Shutdown Supply<br>Current                                                           | All digital inputs at $V_{DD}$ or GND @ $V_{DD} = 5.5V$                               |     | 7     | 15  | μΑ   |

| I <sub>DDFSD</sub>   | Full Shutdown Supply Current                                                                  | Pin RSTN = 0V,<br>$T_{AMB} = 25$ °C                                                   |     | 0.1   | 1   | μΑ   |

| I <sub>DIGIT</sub>   | Digit Drive Sink Current<br>(drive capability of all sources<br>of one digit <sup>(1)</sup> ) |                                                                                       |     |       | 360 | mA   |

| I <sub>SEG</sub>     | Segment Drive Source Current LED <sup>(2)</sup>                                               | V <sub>OUT</sub> = 1.8V to                                                            | 28  | 30    | 32  | mA   |

| $\Delta I_{SEG}$     | Segment Drive Current<br>Matching LED                                                         | V <sub>DD</sub> -400mV                                                                |     | 1     |     | %    |

| 7.256                | Device to Device Current<br>Matching LED                                                      | $V_{OUT} = 1.8V, V_{DD} = 3.3V$                                                       |     | 1     |     | %    |

| I <sub>LEAK</sub>    | Leakage Output Current                                                                        | All current sources OFF,<br>$V_{OUT} = 0V, V_{DD} = 5.5V,$<br>$T_{AMB} = 25^{\circ}C$ |     | 0.005 | 0.5 | μΑ   |

| $\Delta I_{LNR}$     | Line Regulation                                                                               | V <sub>OUT</sub> = 1.8V                                                               |     | 0.25  |     | %/V  |

| $\Delta I_{LDR}$     | Load Regulation                                                                               | $V_{OUT} = 1.8V \text{ to}$ $V_{DD}$ -400mV                                           |     | 0.25  |     | %/V  |

| V <sub>DSSAT</sub>   | Saturation Voltage                                                                            | Current = 30mA,<br>V <sub>DD</sub> = 3.3V                                             |     | 200   |     | mV   |

| R <sub>DSON(N)</sub> | Resistance for NMOS                                                                           |                                                                                       |     | 0.3   | 1   | W    |

| Symbol               | Parameter                          | Conditions   | Min                      | Тур                      | Max  | Unit |

|----------------------|------------------------------------|--------------|--------------------------|--------------------------|------|------|

|                      | Open Detection Level<br>Threshold  |              | V <sub>DD</sub> -<br>0.4 | V <sub>DD</sub> -<br>0.1 |      | V    |

|                      | Short Detection Level<br>Threshold |              |                          | 770                      | 900  | mV   |

| f <sub>OSC</sub>     | Oscillator Frequency               |              | 0.9                      | 1                        | 1.1  | MHz  |

| f <sub>REFRESH</sub> | Display Scan Rate                  | 12x11 matrix | 0.29                     | 0.33                     | 0.36 | kHz  |

| t <sub>RSTN</sub>    | Reset Pulse Width Low              |              | 500                      |                          |      | ns   |

#### Note(s):

1. Guaranteed by design.

$$I_{SEG} = \frac{I_{max} - I_{min}}{I_{max} + I_{min}} \times 100$$

Figure 8:

**Logic Inputs/Outputs Characteristics**

| Symbol                            | Parameter                                     | Conditions                       | Min                   | Тур | Max                   | Unit |

|-----------------------------------|-----------------------------------------------|----------------------------------|-----------------------|-----|-----------------------|------|

| I <sub>IH</sub> , I <sub>IL</sub> | Logic Input Current                           | $V_{IN} = 0V \text{ or } V_{DD}$ | -1                    |     | 1                     | μΑ   |

| V <sub>IH</sub>                   | CMOS Logic High Input Voltage                 |                                  | 0.7 x V <sub>DD</sub> |     |                       | V    |

| V <sub>IL</sub>                   | CMOS Logic Low Input Voltage                  |                                  |                       |     | 0.3 x V <sub>DD</sub> | V    |

| ΔVι                               | CMOS Hysteresis Voltage                       |                                  |                       | 0.3 |                       | V    |

| V <sub>IH</sub>                   | Mobile Logic High Input Voltage (1)           |                                  | 1.6                   |     |                       | V    |

| V <sub>IL</sub>                   | Mobile Logic Low Input Voltage <sup>(1)</sup> |                                  |                       |     | 0.6                   | V    |

| ΔVι                               | Hysteresis Voltage (1)                        |                                  |                       | 0.1 |                       | V    |

| V <sub>OL(SDA)</sub>              | SDA Output Low Voltage                        | I <sub>SINK</sub> = 3mA          |                       |     | 0.4                   | V    |

| V <sub>OL(IRQ)</sub>              | IRQ Output Low Voltage                        | I <sub>SINK</sub> = 3mA          |                       |     | 0.4                   | V    |

| V <sub>OL(SYNC_</sub>             | Sync Clock Output Low Voltage                 | I <sub>SINK</sub> = 1mA          |                       |     | 0.4                   | V    |

| V <sub>OH(SYNC_</sub>             | Sync Clock Output High Voltage                | I <sub>SOURCE</sub> = 1mA        |                       |     | V <sub>DD</sub> -0.4  | V    |

|                                   | Capacitive Load for Each Bus Line             |                                  |                       |     | 400                   | pF   |

#### Note(s):

1. Available on request, see Ordering & Contact Information.

Page 8ams DatasheetDocument Feedback[v2-01] 2016-Oct-12

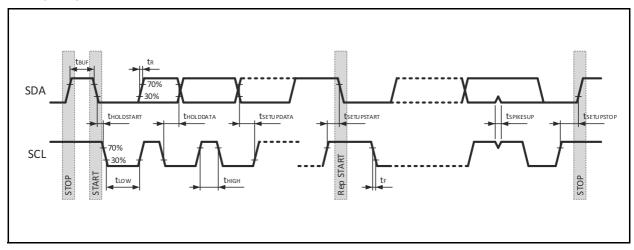

Figure 9: I<sup>2</sup>C Timing Characteristics

| Symbol                  | Parameter                                                            | Conditions | Min | Тур | Max  | Unit |

|-------------------------|----------------------------------------------------------------------|------------|-----|-----|------|------|

| f <sub>SCL</sub>        | SCL Frequency                                                        |            | 100 |     | 1000 | kHz  |

| t <sub>BUF</sub>        | Bus Free Time Between STOP and START Conditions                      |            | 1.3 |     |      | μs   |

| t <sub>HOLDSTART</sub>  | Hold Time for Repeated<br>START Condition                            |            | 260 |     |      | ns   |

| t <sub>LOW</sub>        | SCL Low Period                                                       |            | 500 |     |      | ns   |

| t <sub>HIGH</sub>       | SCL High Period                                                      |            | 260 |     |      | ns   |

| t <sub>SETUPSTART</sub> | Setup Time for Repeated<br>START Condition                           |            | 260 |     |      | ns   |

| t <sub>SETUPDATA</sub>  | Data Setup Time                                                      |            | 100 |     |      | ns   |

| t <sub>RISE(SCL)</sub>  | SCL Rise Time                                                        |            |     |     | 120  | ns   |

| t <sub>RISE(SCL1)</sub> | SCL Rise Time after Repeated START<br>Condition and After an ACK Bit |            |     |     | 120  | ns   |

| t <sub>FALL(SCL)</sub>  | SCL Fall Time                                                        |            |     |     | 120  | ns   |

| t <sub>RISE(SDA)</sub>  | SDA Rise Time                                                        |            |     |     | 120  | ns   |

| t <sub>FALL(SDA)</sub>  | SDA Fall Time                                                        |            |     |     | 120  | ns   |

| t <sub>SETUPSTOP</sub>  | STOP Condition Setup Time                                            |            | 260 |     |      | ns   |

| t <sub>SPIKESUP</sub>   | Pulse Width of Spike Suppressed                                      |            |     |     | 6    | ns   |

#### Note(s):

1. The Min / Max values of the Timing Characteristics are guaranteed by design.

Figure 10: Timing Diagram

ams Datasheet Page 9

[v2-01] 2016-Oct-12 Document Feedback

# Typical Operating Characteristics

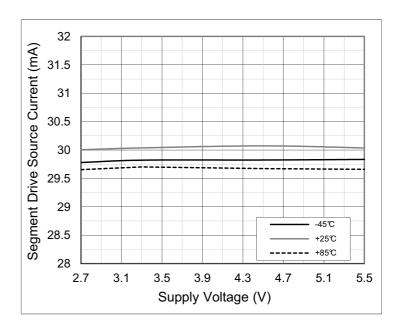

Figure 11: Segment Drive Current vs. Supply Voltage

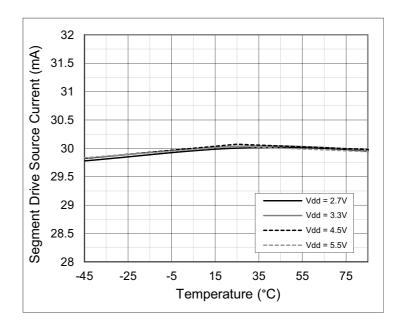

Figure 12: Segment Drive Current vs. Temperature

Page 10ams DatasheetDocument Feedback[v2-01] 2016-Oct-12

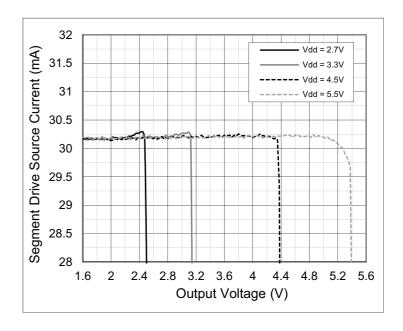

Figure 13: Segment Drive Current vs. Output Voltage

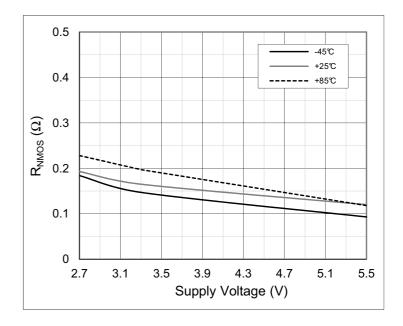

Figure 14: R<sub>ONNMOS</sub> vs. Supply Voltage

ams Datasheet Page 11

[v2-01] 2016-Oct-12 Document Feedback

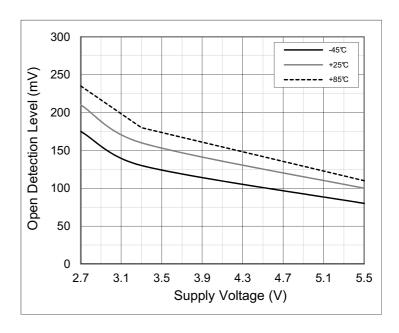

Figure 15:

Open Detection Level vs. Supply Voltage

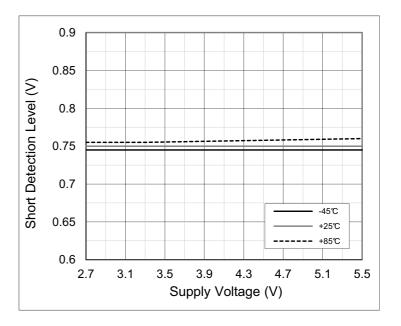

Figure 16: Short Detection Level vs. Supply Voltage

Page 12ams DatasheetDocument Feedback[v2-01] 2016-Oct-12

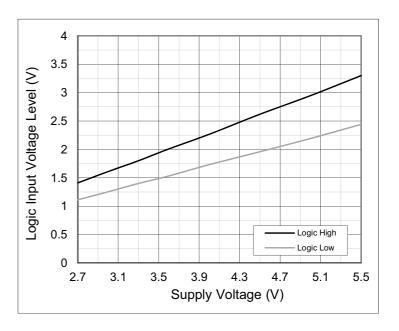

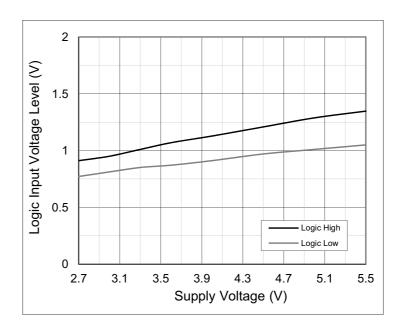

Figure 17: CMOS Logic Input Levels vs. Supply Voltage

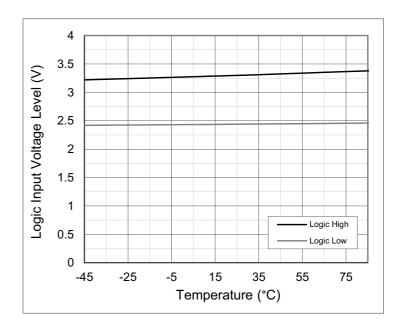

Figure 18: CMOS Logic Input Levels vs. Temperature

ams Datasheet Page 13

[v2-01] 2016-Oct-12 Document Feedback

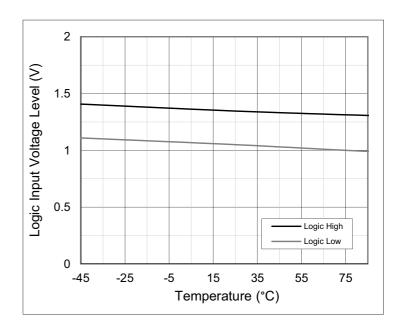

Figure 19: MOBILE Logic Input Levels vs. Supply Voltage

Figure 20: MOBILE Logic Input Levels vs. Temperature

Page 14ams DatasheetDocument Feedback[v2-01] 2016-Oct-12

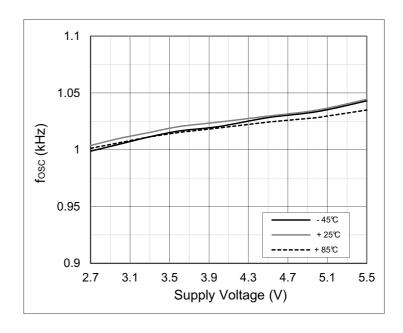

Figure 21:

Oscillator Frequency vs. Supply Voltage

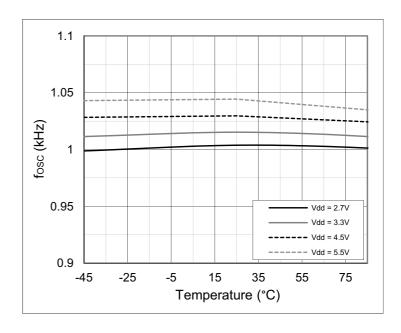

Figure 22: Oscillator Frequency vs. Temperature

ams Datasheet Page 15 [v2-01] 2016-Oct-12 Document Feedback

#### **Detailed Description**

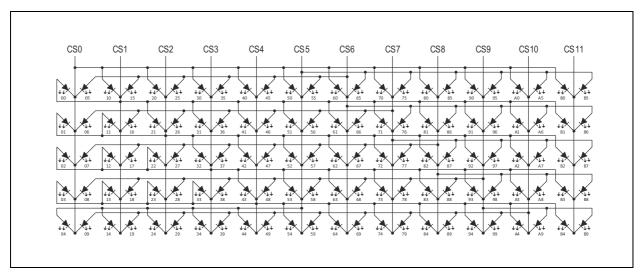

#### **Cross-Plexing Theorem**

The cross-plexing theorem is using the fact that a LED has a forward and backward direction. A LED will only glow if there is a current flowing in forward direction. A parallel LED in backward direction will block the current flow. This effect is used in a cross-plexed matrix of LEDs.

Each CSx pin (CS0 to CS11) can be switched to VDD via the internal current source ("high"), to GND ("low") or not connected ("highZ").

The mode of operation which is controlled by an internal state machine looks like following. CS0 is switched to GND and all other CSx pins (CS1 to CS11) are controlled according to the settings in the On/Off Frame and Blink & PWM registers (see Figure 31).

Than CS1 is switched to GND and all other CSx pins (CS0 and CS2 to CS11) are controlled according to the settings in the On/Off Frame and Blink & PWM registers.

In this manner all LEDs in the matrix are scanned and turned on/off depending on the register settings.

#### I<sup>2</sup>C Interface

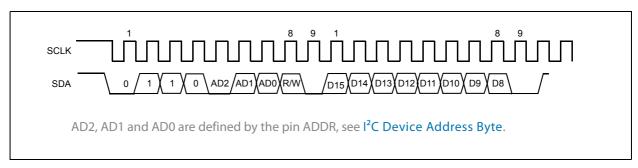

The AS1130 supports the I<sup>2</sup>C serial bus and data transmission protocol in fast mode at 1MHz. The AS1130 operates as a slave on the I<sup>2</sup>C bus. The bus must be controlled by a master device that generates the serial clock (SCLK), controls the bus access, and generates the START and STOP conditions. Connections to the bus are made via the open-drain I/O pins SCLK and SDA.

Figure 23: I<sup>2</sup>C Interface Initialization

Page 16

Document Feedback

[v2-01] 2016-Oct-12

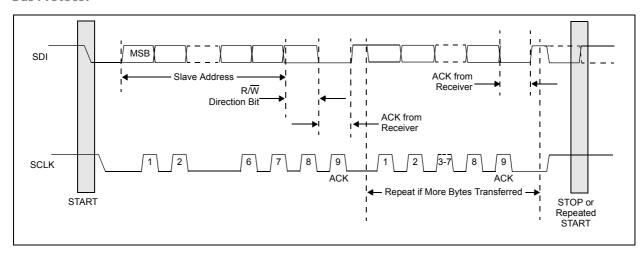

Figure 24: Bus Protocol

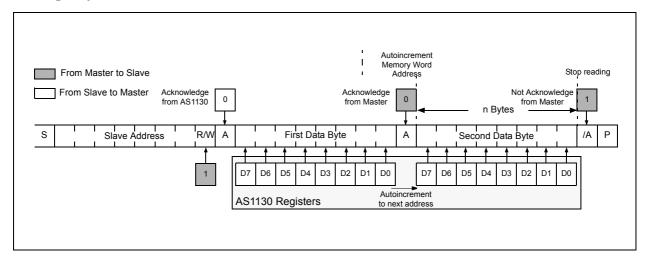

The bus protocol (as shown in Figure 24) is defined as:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as control signals.

The bus conditions are defined as:

- Bus Not Busy. Data and clock lines remain HIGH.

- **Start Data Transfer**. A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

- **Stop Data Transfe**r. A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

- **Data Valid.** The state of the data line represents valid data, when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. There is one clock pulse per bit of data. Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is not limited and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth-bit. Within the I<sup>2</sup>C bus specifications a high-speed mode (3.4MHz clock rate) is defined.

ams Datasheet Page 17

[v2-01] 2016-Oct-12 Document Feedback

- Acknowledge: Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit. A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

- Figure 24 details how data transfer is accomplished on the I<sup>2</sup>C bus. Depending upon the state of the R/W bit, two types of data transfer are possible:

- Master Transmitter to Slave Receiver. The first byte transmitted by the master is the slave address, followed by a number of data bytes. The slave returns an acknowledge bit after the slave address and each received byte.

- Slave Transmitter to Master Receiver. The first byte, the slave address, is transmitted by the master. The slave then returns an acknowledge bit. Next, a number of data bytes are transmitted by the slave to the master. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a not-acknowledge is returned. The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus will not be released.

The AS1130 can operate in the following slave modes:

- Slave Receiver Mode. Serial data and clock are received through SDA and SCL. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit.

- Slave Transmitter Mode. The first byte (the slave address) is received and handled as in the slave receiver mode. However, in this mode the direction bit will indicate that the transfer direction is reversed. Serial data is transmitted on SDA by the AS1130 while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer.

Page 18

Document Feedback [v2-01] 2016-Oct-12

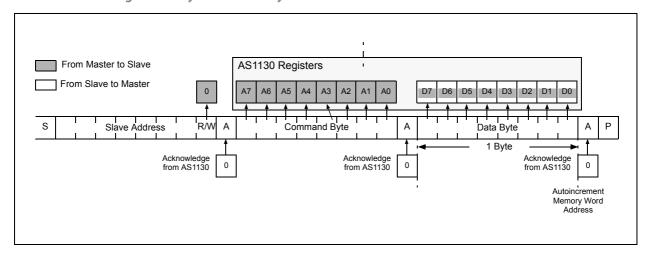

#### **Command Byte**

The AS1130 operation (see Figure 38) is determined by a command byte (see Figure 25).

Figure 25: Command Byte

| MSB | 6  | 5  | 4  | 3  | 2  | 1  | LSB |

|-----|----|----|----|----|----|----|-----|

| A7  | A6 | A5 | A4 | A3 | A2 | A1 | A0  |

Figure 26:

Command and Single Data Byte Received by AS1130

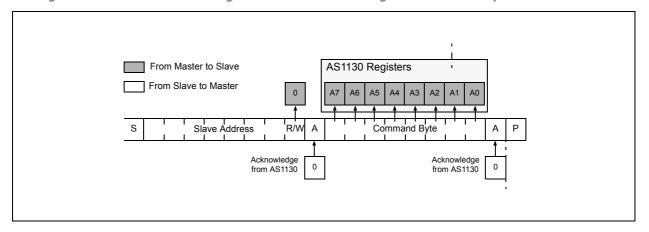

Figure 27:

Setting the Pointer to a Address Register to Select a Data Register for a Read Operation

ams Datasheet Page 19

[v2-01] 2016-Oct-12 Document Feedback

Figure 28: Reading N Bytes from AS1130

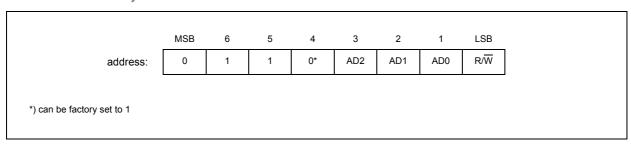

#### I<sup>2</sup>C Device Address Byte

The address byte (see Figure 29) is the first byte received following the START condition from the master device.

Figure 29: I<sup>2</sup>C Device Address Byte

The bit 1, 2 and 3 of the address byte are defined through the resistor @ the device select pin ADDR (see Figure 30). A maximum of 8 devices with the same pre-set code can be connected on the same bus at one time.

- The last bit of the address byte (R/W) define the operation to be performed. When set to a 1 a read operation is selected; when set to a 0 a write operation is selected.

- I<sup>2</sup>C Common address. All devices are responding on the address "0111111" if the function is enabled in the register AS1130 Config Register (0x06).

Following the START condition, the AS1130 monitors the  $I^2C$  bus, checking the device type identifier being transmitted. Upon receiving the address code, and the  $R/\overline{W}$  bit, the slave device outputs an acknowledge signal on the SDA line.

Page 20

Document Feedback

[v2-01] 2016-Oct-12

#### Figure 30: Device Address

|     | I2C Address |         |        |                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|-----|-------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Bit | Bit Name    | Default | Access | Description                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 3:1 | i2c_addr    | 000     | R      | Defines the I²C address of one device via an external resistor on pin ADDR 000: $1M\Omega$ or floating 001: $470k\Omega$ 010: $220k\Omega$ 011: $100k\Omega$ 100: $47k\Omega$ 101: $22k\Omega$ 101: $10k\Omega$ 111: $4.7k\Omega$ or GND |  |  |  |  |  |  |  |  |

The pin ADDR is scanned after start up (POR) and defines the address for the device. The device reacts to this address until a hardware reset (low on pin RSTN) is performed or the power-on-reset (POR) triggers again.

**Note(s):** The internal address decoder needs 5ms to identify the address and to set up the device for this address.

ams Datasheet Page 21 [v2-01] 2016-Oct-12 Document Feedback

#### **Initial Power-Up**

On initial power-up, the AS1130 registers are reset to their default values, the display is blanked, and the device goes into shutdown mode. At this time, all registers should be programmed for normal operation. To bring the device into normal operation the following sequence needs to be performed.

#### Start-Up Sequence

- Power-up the AS1130 (connect VDD to a source), the devices is in shutdown;

- After 5ms the address of the AS1130 is valid and the first I<sup>2</sup>C command can be send.

- Define RAM Configuration; bit mem\_conf in the AS1130 Config Register (see Figure 45)

- · On/Off Frames

- · Blink & PWM Sets

- · Dot Correction, if specified

- Define Control Register (see Figure 38)

- Current Source

- · Display options

- Display picture / play movie

- To light up the LEDs set the shdn bit to '1' for normal operation mode (see Figure 48).

#### **Shutdown Mode**

The AS1130 device features two different shutdown modes. A software shutdown via shutdown register (see Shutdown & Open/Short Register (0x09)) and a hardware shutdown via the RSTN pin.

The software shutdown disables all LEDs and stops the internal operation of the logic. A shutdown mode via the RSTN pin additionally powers down the power-on-reset (POR) of the device. In this shutdown mode the AS1130 consumes only 100nA (typ.).

Page 22

Document Feedback

[v2-01] 2016-Oct-12

### **Register Description**

#### **Register Selection**

Within this register the access to one of the RAM sections, the Dot Correction or to the Control register is selected. After one section is selected this section is valid as long as an other section is selected.

Figure 31: Register Selection Address Map

|                      |             |            |        | Ad     | dres   | SS     |        |        |        |             | Data   |     |     |        |        |        |        |        |                                         |  |  |

|----------------------|-------------|------------|--------|--------|--------|--------|--------|--------|--------|-------------|--------|-----|-----|--------|--------|--------|--------|--------|-----------------------------------------|--|--|

| Register<br>Section  | H<br>E<br>X | <b>A</b> 7 | A<br>6 | A<br>5 | A<br>4 | A<br>3 | A<br>2 | A<br>1 | A<br>0 | H<br>E<br>X | D<br>7 | D 6 | D 5 | D<br>4 | D<br>3 | D<br>2 | D<br>1 | D<br>0 | Description                             |  |  |

| NOP                  |             |            |        |        |        |        |        |        |        | 0x<br>00    | 0      | 0   | 0   | 0      | 0      | 0      | 0      | 0      | No operation                            |  |  |

| On/Off Frame 0       |             |            |        |        |        |        |        |        |        | 0x<br>01    | 0      | 0   | 0   | 0      | 0      | 0      | 0      | 1      |                                         |  |  |

| On/Off Frame 1       |             |            |        |        |        |        |        |        |        | 0x<br>02    | 0      | 0   | 0   | 0      | 0      | 0      | 1      | 0      |                                         |  |  |

| On/Off Frame 2       |             |            |        |        |        |        |        |        |        | 0x<br>03    | 0      | 0   | 0   | 0      | 0      | 0      | 1      | 1      | On/Off information for each frame (up   |  |  |

|                      |             |            |        |        |        |        |        |        |        |             |        |     |     | ••••   |        |        |        |        | to 36 frames)                           |  |  |

| On/Off Frame<br>34   |             |            |        |        |        |        |        |        |        | 0x<br>23    | 0      | 0   | 1   | 0      | 0      | 0      | 1      | 1      |                                         |  |  |

| On/Off Frame<br>35   |             |            |        |        |        |        |        |        |        | 0x<br>24    | 0      | 0   | 1   | 0      | 0      | 1      | 0      | 0      |                                         |  |  |

| Blink & PWM<br>Set 0 | 0x<br>FD    | 1          | 1      | 1      | 1      | 1      | 1      | 0      | 1      | 0x<br>40    | 0      | 1   | 0   | 0      | 0      | 0      | 0      | 0      |                                         |  |  |

| Blink & PWM<br>Set 1 |             |            |        |        |        |        |        |        |        | 0x<br>41    | 0      | 1   | 0   | 0      | 0      | 0      | 0      | 1      |                                         |  |  |

| Blink & PWM<br>Set 2 |             |            |        |        |        |        |        |        |        | 0x<br>42    | 0      | 1   | 0   | 0      | 0      | 0      | 1      | 0      | Blink & PWM<br>Information Sets         |  |  |

| Blink & PWM<br>Set 3 |             |            |        |        |        |        |        |        |        | 0x<br>43    | 0      | 1   | 0   | 0      | 0      | 0      | 1      | 1      | (up to 6 sets)                          |  |  |

| Blink & PWM<br>Set 4 |             |            |        |        |        |        |        |        |        | 0x<br>44    | 0      | 1   | 0   | 0      | 0      | 1      | 0      | 0      |                                         |  |  |

| Blink & PWM<br>Set 5 |             |            |        |        |        |        |        |        |        | 0x<br>45    | 0      | 1   | 0   | 0      | 0      | 1      | 0      | 1      |                                         |  |  |

| Dot Correction       |             |            |        |        |        |        |        |        |        | 0x<br>80    | 1      | 0   | 0   | 0      | 0      | 0      | 0      | 0      | Selection of Dot<br>Correction Register |  |  |

| Control<br>Register  |             |            |        |        |        |        |        |        |        | 0x<br>C0    | 1      | 1   | 0   | 0      | 0      | 0      | 0      | 0      | Selection of<br>Control Register        |  |  |

ams Datasheet Page 23

[v2-01] 2016-Oct-12 Document Feedback

#### **Data Definition of the Single Frames**

One frame consists of 2 datasets, the On/Off dataset and the Blink & PWM dataset. Where more On/Off frames can be linked to one PWM set. Depending on the used PWM sets more or less On/Off frames can be stored inside the AS1130 (see Figure 32).

Each On/Off frame needs to define the used Blink & PWM dataset.

Figure 32: RAM Configuration

| RAM Configuration | Blink & PWM Set | On/Off Frame | On/Off Frame<br>with Dot Correction |

|-------------------|-----------------|--------------|-------------------------------------|

| 1                 | 0               | 350          | 340                                 |

| 2                 | 1,0             | 290          | 280                                 |

| 3                 | 2,1,0           | 230          | 220                                 |

| 4                 | 30              | 170          | 160                                 |

| 5                 | 40              | 110          | 100                                 |

| 6                 | 50              | 50           | 40                                  |

It is necessary to define the RAM configuration before data can be written to the frame datasets. The RAM configuration is defined in the AS1130 config register (see Figure 45) via bit 2:0 and bit 4 for Dot Correction.

**Note(s):** After a first write of data to the frames, the configuration is locked in the AS1130 config register and can be changed only after a reset of the device. A change of the RAM configuration requires to re-write the frame datasets.

Page 24

Document Feedback

[v2-01] 2016-Oct-12

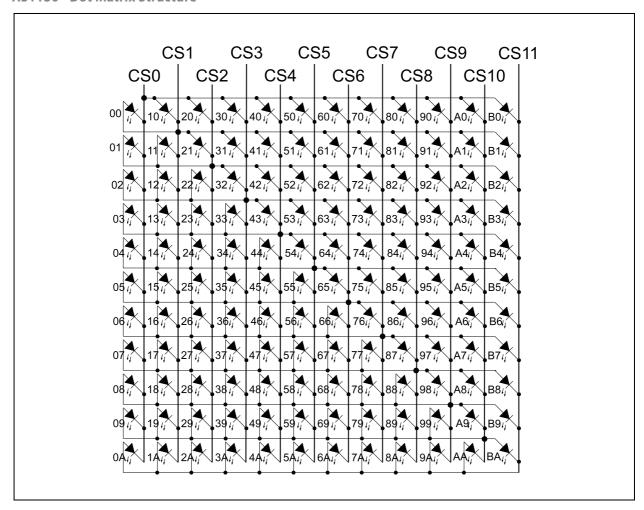

#### 12x11 LED Matrix

The AS1130 is configured to control one big LED matrix.

Figure 33: AS1130 - Dot Matrix Structure

In Figure 34 it is described which databit represents which LED in the matrix. Per default all databits are '0', meaning no LED is on. A '1' puts the LED on.

Each Current Segment of the LED Matrix consists of 11 LEDs, therefore 2 bytes of data are required for one Current Segment. CS0 is defined by the two bytes with address 0x00 and 0x01 and also includes the address of the used Blink & PWM dataset for this frame.

ams Datasheet Page 25

[v2-01] 2016-Oct-12 Document Feedback

Figure 34: LEDs On/Off Frame Register Format

| Comment |      |    |    | A  | Address |    |    |    |    |            |            |            | Da        | ata       |           |           |           |

|---------|------|----|----|----|---------|----|----|----|----|------------|------------|------------|-----------|-----------|-----------|-----------|-----------|

| Segment | HEX  | A7 | A6 | A5 | A4      | А3 | A2 | A1 | A0 | D7         | D6         | D5         | D4        | D3        | D2        | D1        | D0        |

| 0       | 0x00 | 0  | 0  | 0  | 0       | 0  | 0  | 0  | 0  | LED<br>07  | LED<br>06  | LED<br>05  | LED<br>04 | LED<br>03 | LED<br>02 | LED<br>01 | LED<br>00 |

|         | 0x01 | 0  | 0  | 0  | 0       | 0  | 0  | 0  | 1  | PWM<br>[2] | PWM<br>[1] | PWM<br>[0] | Х         | Х         | LED<br>0A | LED<br>09 | LED<br>08 |

| 1       | 0x02 | 0  | 0  | 0  | 0       | 0  | 0  | 1  | 0  | LED<br>17  | LED<br>16  | LED<br>15  | LED<br>14 | LED<br>13 | LED<br>12 | LED<br>11 | LED<br>10 |

| '       | 0x03 | 0  | 0  | 0  | 0       | 0  | 0  | 1  | 1  | Х          | Х          | Х          | Х         | Х         | LED<br>1A | LED<br>19 | LED<br>18 |

| 2       | 0x04 | 0  | 0  | 0  | 0       | 0  | 1  | 0  | 0  | LED<br>27  | LED<br>26  | LED<br>25  | LED<br>24 | LED<br>23 | LED<br>22 | LED<br>21 | LED<br>20 |

| 2       | 0x05 | 0  | 0  | 0  | 0       | 0  | 1  | 0  | 1  | Х          | Х          | Х          | Х         | Х         | LED<br>2A | LED<br>29 | LED<br>28 |

| 3       | 0x06 | 0  | 0  | 0  | 0       | 0  | 1  | 1  | 0  | LED<br>37  | LED<br>36  | LED<br>35  | LED<br>34 | LED<br>33 | LED<br>32 | LED<br>31 | LED<br>30 |

| ,       | 0x07 | 0  | 0  | 0  | 0       | 0  | 1  | 1  | 1  | Х          | Х          | Х          | Х         | Х         | LED<br>3A | LED<br>39 | LED<br>38 |

| 4       | 0x08 | 0  | 0  | 0  | 0       | 1  | 0  | 0  | 0  | LED<br>47  | LED<br>46  | LED<br>45  | LED<br>44 | LED<br>43 | LED<br>42 | LED<br>41 | LED<br>40 |

|         | 0x09 | 0  | 0  | 0  | 0       | 1  | 0  | 0  | 1  | Х          | Х          | Х          | Х         | Х         | LED<br>4A | LED<br>49 | LED<br>48 |

| Segment |      |    |    | A  | Address |    |    |    |    |           |           |           | Da        | ata       |           |           |           |

|---------|------|----|----|----|---------|----|----|----|----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Segment | HEX  | A7 | A6 | A5 | A4      | A3 | A2 | A1 | A0 | D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

| 5       | 0x0A | 0  | 0  | 0  | 0       | 1  | 0  | 1  | 0  | LED<br>57 | LED<br>56 | LED<br>55 | LED<br>54 | LED<br>53 | LED<br>52 | LED<br>51 | LED<br>50 |

| 3       | 0x0B | 0  | 0  | 0  | 0       | 1  | 0  | 1  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>5A | LED<br>59 | LED<br>58 |

| 6       | 0x0C | 0  | 0  | 0  | 0       | 1  | 1  | 0  | 0  | LED<br>67 | LED<br>66 | LED<br>65 | LED<br>64 | LED<br>63 | LED<br>62 | LED<br>61 | LED<br>60 |

|         | 0x0D | 0  | 0  | 0  | 0       | 1  | 1  | 0  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>6A | LED<br>69 | LED<br>68 |

| 7       | 0x0E | 0  | 0  | 0  | 0       | 1  | 1  | 1  | 0  | LED<br>77 | LED<br>76 | LED<br>75 | LED<br>74 | LED<br>73 | LED<br>72 | LED<br>71 | LED<br>70 |

| ,       | 0x0F | 0  | 0  | 0  | 0       | 1  | 1  | 1  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>7A | LED<br>79 | LED<br>78 |

| 8       | 0x10 | 0  | 0  | 0  | 1       | 0  | 0  | 0  | 0  | LED<br>87 | LED<br>86 | LED<br>85 | LED<br>84 | LED<br>83 | LED<br>82 | LED<br>81 | LED<br>80 |

|         | 0x11 | 0  | 0  | 0  | 1       | 0  | 0  | 0  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>8A | LED<br>89 | LED<br>88 |

| 9       | 0x12 | 0  | 0  | 0  | 1       | 0  | 0  | 1  | 0  | LED<br>97 | LED<br>96 | LED<br>95 | LED<br>94 | LED<br>93 | LED<br>92 | LED<br>91 | LED<br>90 |

|         | 0x13 | 0  | 0  | 0  | 1       | 0  | 0  | 1  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>9A | LED<br>99 | LED<br>98 |

| A       | 0x14 | 0  | 0  | 0  | 1       | 0  | 1  | 0  | 0  | LED<br>A7 | LED<br>A6 | LED<br>A5 | LED<br>A4 | LED<br>A3 | LED<br>A2 | LED<br>A1 | LED<br>A0 |

| ,       | 0x15 | 0  | 0  | 0  | 1       | 0  | 1  | 0  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>AA | LED<br>A9 | LED<br>A8 |

| Segment |      |    |    | <b>A</b> | Address |    |    |    |    |           |           |           | Da        | ata       |           |           |           |

|---------|------|----|----|----------|---------|----|----|----|----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Segment | HEX  | A7 | A6 | A5       | A4      | А3 | A2 | A1 | A0 | D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

| В       | 0x16 | 0  | 0  | 0        | 1       | 0  | 1  | 1  | 0  | LED<br>B7 | LED<br>B6 | LED<br>B5 | LED<br>B4 | LED<br>B3 | LED<br>B2 | LED<br>B1 | LED<br>B0 |

| , , ,   | 0x17 | 0  | 0  | 0        | 1       | 0  | 1  | 1  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>BA | LED<br>B9 | LED<br>B8 |

The Blink & PWM sets contain blink on/off and the digital PWM information for each LED in the matrix. The number of PWM datasets is flexible according to the defined RAM configuration (see Figure 32).

In the blink register (see Figure 35) every single LED can be set to blink. The blink period is set in the display option register (see Display Option Register Format).

Figure 35: LEDs Blink Frame Register Format

| Segment |      |    |    | A  | ddress |    |    |    |    |           |           |           | Da        | ata       |           |           |           |

|---------|------|----|----|----|--------|----|----|----|----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Segment | HEX  | A7 | A6 | A5 | A4     | A3 | A2 | A1 | A0 | D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

| 0       | 0x00 | 0  | 0  | 0  | 0      | 0  | 0  | 0  | 0  | LED<br>07 | LED<br>06 | LED<br>05 | LED<br>04 | LED<br>03 | LED<br>02 | LED<br>01 | LED<br>00 |

|         | 0x01 | 0  | 0  | 0  | 0      | 0  | 0  | 0  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>0A | LED<br>09 | LED<br>08 |

| 1       | 0x02 | 0  | 0  | 0  | 0      | 0  | 0  | 1  | 0  | LED<br>17 | LED<br>16 | LED<br>15 | LED<br>14 | LED<br>13 | LED<br>12 | LED<br>11 | LED<br>10 |

| '       | 0x03 | 0  | 0  | 0  | 0      | 0  | 0  | 1  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>1A | LED<br>19 | LED<br>18 |

| Commont |      |    |    | А  | .ddress   |    |    |    |    |           |           |           | Da        | ata       |           |           |           |

|---------|------|----|----|----|-----------|----|----|----|----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Segment | HEX  | A7 | A6 | A5 | <b>A4</b> | А3 | A2 | A1 | A0 | D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

| 2       | 0x04 | 0  | 0  | 0  | 0         | 0  | 1  | 0  | 0  | LED<br>27 | LED<br>26 | LED<br>25 | LED<br>24 | LED<br>23 | LED<br>22 | LED<br>21 | LED<br>20 |

| 2       | 0x05 | 0  | 0  | 0  | 0         | 0  | 1  | 0  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>2A | LED<br>29 | LED<br>28 |

| 3       | 0x06 | 0  | 0  | 0  | 0         | 0  | 1  | 1  | 0  | LED<br>37 | LED<br>36 | LED<br>35 | LED<br>34 | LED<br>33 | LED<br>32 | LED<br>31 | LED<br>30 |

| 3       | 0x07 | 0  | 0  | 0  | 0         | 0  | 1  | 1  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>3A | LED<br>39 | LED<br>38 |

| 4       | 0x08 | 0  | 0  | 0  | 0         | 1  | 0  | 0  | 0  | LED<br>47 | LED<br>46 | LED<br>45 | LED<br>44 | LED<br>43 | LED<br>42 | LED<br>41 | LED<br>40 |

| ·       | 0x09 | 0  | 0  | 0  | 0         | 1  | 0  | 0  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>4A | LED<br>49 | LED<br>48 |

| 5       | 0x0A | 0  | 0  | 0  | 0         | 1  | 0  | 1  | 0  | LED<br>57 | LED<br>56 | LED<br>55 | LED<br>54 | LED<br>53 | LED<br>52 | LED<br>51 | LED<br>50 |

| 3       | 0x0B | 0  | 0  | 0  | 0         | 1  | 0  | 1  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>5A | LED<br>59 | LED<br>58 |

| 6       | 0x0C | 0  | 0  | 0  | 0         | 1  | 1  | 0  | 0  | LED<br>67 | LED<br>66 | LED<br>65 | LED<br>64 | LED<br>63 | LED<br>62 | LED<br>61 | LED<br>60 |

|         | 0x0D | 0  | 0  | 0  | 0         | 1  | 1  | 0  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>6A | LED<br>69 | LED<br>68 |

| 7       | 0x0E | 0  | 0  | 0  | 0         | 1  | 1  | 1  | 0  | LED<br>77 | LED<br>76 | LED<br>75 | LED<br>74 | LED<br>73 | LED<br>72 | LED<br>71 | LED<br>70 |

| ,       | 0x0F | 0  | 0  | 0  | 0         | 1  | 1  | 1  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>7A | LED<br>79 | LED<br>78 |

| Sagment |      |    |    | A  | ddress    |    |    |    |    |           |           |           | Da        | ata       |           |           |           |

|---------|------|----|----|----|-----------|----|----|----|----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Segment | HEX  | A7 | A6 | A5 | <b>A4</b> | А3 | A2 | A1 | A0 | D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

| 8       | 0x10 | 0  | 0  | 0  | 1         | 0  | 0  | 0  | 0  | LED<br>87 | LED<br>86 | LED<br>85 | LED<br>84 | LED<br>83 | LED<br>82 | LED<br>81 | LED<br>80 |

| 0       | 0x11 | 0  | 0  | 0  | 1         | 0  | 0  | 0  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>8A | LED<br>89 | LED<br>88 |

| 9       | 0x12 | 0  | 0  | 0  | 1         | 0  | 0  | 1  | 0  | LED<br>97 | LED<br>96 | LED<br>95 | LED<br>94 | LED<br>93 | LED<br>92 | LED<br>91 | LED<br>90 |

| ,       | 0x13 | 0  | 0  | 0  | 1         | 0  | 0  | 1  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>9A | LED<br>99 | LED<br>98 |

| A       | 0x14 | 0  | 0  | 0  | 1         | 0  | 1  | 0  | 0  | LED<br>A7 | LED<br>A6 | LED<br>A5 | LED<br>A4 | LED<br>A3 | LED<br>A2 | LED<br>A1 | LED<br>A0 |

|         | 0x15 | 0  | 0  | 0  | 1         | 0  | 1  | 0  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>AA | LED<br>A9 | LED<br>A8 |

| В       | 0x16 | 0  | 0  | 0  | 1         | 0  | 1  | 1  | 0  | LED<br>B7 | LED<br>B6 | LED<br>B5 | LED<br>B4 | LED<br>B3 | LED<br>B2 | LED<br>B1 | LED<br>B0 |

| D       | 0x17 | 0  | 0  | 0  | 1         | 0  | 1  | 1  | 1  | Х         | Х         | Х         | Х         | Х         | LED<br>BA | LED<br>B9 | LED<br>B8 |

In the PWM register (see Figure 36) the brightness of every single LED can be set via a 8bit PWM (255 steps).

Figure 36: LEDs PWM Register Format

|         |       |         |            |        | Ado    | dres   | S      |        |        |        |        |        |        | Da     | ata          |        |        |        |

|---------|-------|---------|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------------|--------|--------|--------|

| Segment |       | HE<br>X | <b>A</b> 7 | A<br>6 | A<br>5 | A<br>4 | A<br>3 | A<br>2 | A<br>1 | A<br>0 | D<br>7 | D<br>6 | D<br>5 | D<br>4 | D<br>3       | D<br>2 | D<br>1 | D<br>0 |

|         | LED00 | 0x18    | 0          | 0      | 0      | 1      | 1      | 0      | 0      | 0      |        |        |        |        |              |        |        |        |

|         | LED01 | 0x19    | 0          | 0      | 0      | 1      | 1      | 0      | 0      | 1      |        |        |        |        |              |        |        |        |

|         | LED02 | 0x1A    | 0          | 0      | 0      | 1      | 1      | 0      | 1      | 0      |        |        |        |        |              |        |        |        |

|         | LED03 | 0x1B    | 0          | 0      | 0      | 1      | 1      | 0      | 1      | 1      |        |        |        |        |              |        |        |        |

|         | LED04 | 0x1C    | 0          | 0      | 0      | 1      | 1      | 1      | 0      | 0      |        |        |        |        |              |        |        |        |

| 0       | LED05 | 0x1D    | 0          | 0      | 0      | 1      | 1      | 1      | 0      | 1      | 25     | 5 ste  | ps fo  |        | ensity<br>ED | / eacl | h sing | gle    |

|         | LED06 | 0x1E    | 0          | 0      | 0      | 1      | 1      | 1      | 1      | 0      |        |        |        |        |              |        |        |        |

|         | LED07 | 0x1F    | 0          | 0      | 0      | 1      | 1      | 1      | 1      | 1      |        |        |        |        |              |        |        |        |

|         | LED08 | 0x20    | 0          | 0      | 1      | 0      | 0      | 0      | 0      | 0      |        |        |        |        |              |        |        |        |

|         | LED09 | 0x21    | 0          | 0      | 1      | 0      | 0      | 0      | 0      | 1      |        |        |        |        |              |        |        |        |

|         | LED0A | 0x22    | 0          | 0      | 1      | 0      | 0      | 0      | 1      | 0      |        |        |        |        |              |        |        |        |

|         | LED10 | 0x23    | 0          | 0      | 1      | 0      | 0      | 0      | 1      | 1      |        |        |        |        |              |        |        |        |

|         | LED11 | 0x24    | 0          | 0      | 1      | 0      | 0      | 1      | 0      | 0      |        |        |        |        |              |        |        |        |

|         | LED12 | 0x25    | 0          | 0      | 1      | 0      | 0      | 1      | 0      | 1      |        |        |        |        |              |        |        |        |

|         | LED13 | 0x26    | 0          | 0      | 1      | 0      | 0      | 1      | 1      | 0      |        |        |        |        |              |        |        |        |

|         | LED14 | 0x27    | 0          | 0      | 1      | 0      | 0      | 1      | 1      | 1      |        |        |        |        |              |        |        |        |

| 1       | LED15 | 0x28    | 0          | 0      | 1      | 0      | 1      | 0      | 0      | 0      | 25     | 5 ste  | ps fo  |        | ensity<br>ED | / eacl | h sing | gle    |

|         | LED16 | 0x29    | 0          | 0      | 1      | 0      | 1      | 0      | 0      | 1      |        |        |        |        |              |        |        |        |

|         | LED17 | 0x2A    | 0          | 0      | 1      | 0      | 1      | 0      | 1      | 0      |        |        |        |        |              |        |        |        |

|         | LED18 | 0x2B    | 0          | 0      | 1      | 0      | 1      | 0      | 1      | 1      |        |        |        |        |              |        |        |        |

|         | LED19 | 0x2C    | 0          | 0      | 1      | 0      | 1      | 1      | 0      | 0      |        |        |        |        |              |        |        |        |

|         | LED1A | 0x2D    | 0          | 0      | 1      | 0      | 1      | 1      | 0      | 1      |        |        |        |        |              |        |        |        |

|         |       |         |            |        | Ado    | dres   | s      |        |        |        |        |        |        | Da     | ata          |        |        |        |

|---------|-------|---------|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------------|--------|--------|--------|

| Segment |       | HE<br>X | <b>A</b> 7 | A<br>6 | A<br>5 | A<br>4 | A<br>3 | A<br>2 | A<br>1 | A<br>0 | D<br>7 | D<br>6 | D<br>5 | D<br>4 | D<br>3       | D<br>2 | D<br>1 | D<br>0 |

|         | LED20 | 0x2E    | 0          | 0      | 1      | 0      | 1      | 1      | 1      | 0      |        |        |        |        |              |        |        |        |

|         | LED21 | 0x2F    | 0          | 0      | 1      | 0      | 1      | 1      | 1      | 1      |        |        |        |        |              |        |        |        |

|         | LED22 | 0x30    | 0          | 0      | 1      | 1      | 0      | 0      | 0      | 0      |        |        |        |        |              |        |        |        |

|         | LED23 | 0x31    | 0          | 0      | 1      | 1      | 0      | 0      | 0      | 1      |        |        |        |        |              |        |        |        |

|         | LED24 | 0x32    | 0          | 0      | 1      | 1      | 0      | 0      | 1      | 0      |        |        |        |        |              |        |        |        |

| 2       | LED25 | 0x33    | 0          | 0      | 1      | 1      | 0      | 0      | 1      | 1      | 25     | 5 ste  | ps fo  |        | ensity<br>ED | eacl   | n sing | gle    |

|         | LED26 | 0x34    | 0          | 0      | 1      | 1      | 0      | 1      | 0      | 0      |        |        |        |        |              |        |        |        |

|         | LED27 | 0x35    | 0          | 0      | 1      | 1      | 0      | 1      | 0      | 1      |        |        |        |        |              |        |        |        |

|         | LED28 | 0x36    | 0          | 0      | 1      | 1      | 0      | 1      | 1      | 0      |        |        |        |        |              |        |        |        |

|         | LED29 | 0x37    | 0          | 0      | 1      | 1      | 0      | 1      | 1      | 1      |        |        |        |        |              |        |        |        |

|         | LED2A | 0x38    | 0          | 0      | 1      | 1      | 1      | 0      | 0      | 0      |        |        |        |        |              |        |        |        |

|         | LED30 | 0x39    | 0          | 0      | 1      | 1      | 1      | 0      | 0      | 1      |        |        |        |        |              |        |        |        |

|         | LED31 | 0x3A    | 0          | 0      | 1      | 1      | 1      | 0      | 1      | 0      |        |        |        |        |              |        |        |        |

|         | LED32 | 0x3B    | 0          | 0      | 1      | 1      | 1      | 0      | 1      | 1      |        |        |        |        |              |        |        |        |

|         | LED33 | 0x3C    | 0          | 0      | 1      | 1      | 1      | 1      | 0      | 0      |        |        |        |        |              |        |        |        |

|         | LED34 | 0x3D    | 0          | 0      | 1      | 1      | 1      | 1      | 0      | 1      |        |        |        |        |              |        |        |        |

| 3       | LED35 | 0x3E    | 0          | 0      | 1      | 1      | 1      | 1      | 1      | 0      | 25     | 5 ste  | ps fo  |        | ensity<br>ED | eacl   | n sing | gle    |

|         | LED36 | 0x3F    | 0          | 0      | 1      | 1      | 1      | 1      | 1      | 1      |        |        |        |        |              |        |        |        |

|         | LED37 | 0x40    | 0          | 1      | 0      | 0      | 0      | 0      | 0      | 0      |        |        |        |        |              |        |        |        |

|         | LED38 | 0x41    | 0          | 1      | 0      | 0      | 0      | 0      | 0      | 1      |        |        |        |        |              |        |        |        |

|         | LED39 | 0x42    | 0          | 1      | 0      | 0      | 0      | 0      | 1      | 0      |        |        |        |        |              |        |        |        |

|         | LED3A | 0x43    | 0          | 1      | 0      | 0      | 0      | 0      | 1      | 1      |        |        |        |        |              |        |        |        |

Page 32ams DatasheetDocument Feedback[v2-01] 2016-Oct-12

|         |       |         |            |        | Add    | dres   | s      |        |        |        |        |        |        | Da           | ata          |        |        |        |

|---------|-------|---------|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------------|--------------|--------|--------|--------|

| Segment |       | HE<br>X | <b>A</b> 7 | A<br>6 | A<br>5 | A<br>4 | A<br>3 | A<br>2 | A<br>1 | A<br>0 | D<br>7 | D<br>6 | D<br>5 | D<br>4       | D<br>3       | D<br>2 | D<br>1 | D<br>0 |

|         | LED40 | 0x44    | 0          | 1      | 0      | 0      | 0      | 1      | 0      | 0      |        |        |        |              |              |        |        |        |

|         | LED41 | 0x45    | 0          | 1      | 0      | 0      | 0      | 1      | 0      | 1      |        |        |        |              |              |        |        |        |

|         | LED42 | 0x46    | 0          | 1      | 0      | 0      | 0      | 1      | 1      | 0      |        |        |        |              |              |        |        |        |

|         | LED43 | 0x47    | 0          | 1      | 0      | 0      | 0      | 1      | 1      | 1      |        |        |        |              |              |        |        |        |

|         | LED44 | 0x48    | 0          | 1      | 0      | 0      | 1      | 0      | 0      | 0      |        |        |        |              |              |        |        |        |

| 4       | LED45 | 0x49    | 0          | 1      | 0      | 0      | 1      | 0      | 0      | 1      | 25     | 5 ste  | ps fo  | r inte<br>LE | ensity<br>ED | eacl   | n sing | gle    |

|         | LED46 | 0x4A    | 0          | 1      | 0      | 0      | 1      | 0      | 1      | 0      |        |        |        |              |              |        |        |        |

|         | LED47 | 0x4B    | 0          | 1      | 0      | 0      | 1      | 0      | 1      | 1      |        |        |        |              |              |        |        |        |

|         | LED48 | 0x4C    | 0          | 1      | 0      | 0      | 1      | 1      | 0      | 0      |        |        |        |              |              |        |        |        |

|         | LED49 | 0x4D    | 0          | 1      | 0      | 0      | 1      | 1      | 0      | 1      |        |        |        |              |              |        |        |        |

|         | LED4A | 0x4E    | 0          | 1      | 0      | 0      | 1      | 1      | 1      | 0      |        |        |        |              |              |        |        |        |

|         | LED50 | 0x4F    | 0          | 1      | 0      | 0      | 1      | 1      | 1      | 1      |        |        |        |              |              |        |        |        |

|         | LED51 | 0x50    | 0          | 1      | 0      | 1      | 0      | 0      | 0      | 0      |        |        |        |              |              |        |        |        |

|         | LED52 | 0x51    | 0          | 1      | 0      | 1      | 0      | 0      | 0      | 1      |        |        |        |              |              |        |        |        |

|         | LED53 | 0x52    | 0          | 1      | 0      | 1      | 0      | 0      | 1      | 0      |        |        |        |              |              |        |        |        |

|         | LED54 | 0x53    | 0          | 1      | 0      | 1      | 0      | 0      | 1      | 1      |        |        |        |              |              |        |        |        |

| 5       | LED55 | 0x54    | 0          | 1      | 0      | 1      | 0      | 1      | 0      | 0      | 25     | 5 ste  | ps fo  | r inte<br>LE | ensity<br>ED | eacl   | n sing | gle    |

|         | LED56 | 0x55    | 0          | 1      | 0      | 1      | 0      | 1      | 0      | 1      |        |        |        |              |              |        |        |        |

|         | LED57 | 0x56    | 0          | 1      | 0      | 1      | 0      | 1      | 1      | 0      |        |        |        |              |              |        |        |        |

|         | LED58 | 0x57    | 0          | 1      | 0      | 1      | 0      | 1      | 1      | 1      |        |        |        |              |              |        |        |        |

|         | LED59 | 0x58    | 0          | 1      | 0      | 1      | 1      | 0      | 0      | 0      |        |        |        |              |              |        |        |        |

|         | LED5A | 0x59    | 0          | 1      | 0      | 1      | 1      | 0      | 0      | 1      |        |        |        |              |              |        |        |        |

|         |       |         |            |        |        |        |        |        |        |        |        |        |        |              |              |        |        |        |

ams Datasheet Page 33

[v2-01] 2016-Oct-12

Document Feedback

|         |       |         |            |        | Ado    | dres   | s      |        |        |        |        |        |        | Da     | ata          |           |        |        |

|---------|-------|---------|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------------|-----------|--------|--------|

| Segment |       | HE<br>X | <b>A</b> 7 | A<br>6 | A<br>5 | A<br>4 | A<br>3 | A<br>2 | A<br>1 | A<br>0 | D<br>7 | D<br>6 | D<br>5 | D<br>4 | D<br>3       | D<br>2    | D<br>1 | D<br>0 |

|         | LEDA0 | 0x86    | 1          | 0      | 0      | 0      | 0      | 1      | 1      | 0      |        |        |        |        |              |           |        |        |

|         | LEDA1 | 0x87    | 1          | 0      | 0      | 0      | 0      | 1      | 1      | 1      |        |        |        |        |              |           |        |        |

|         | LEDA2 | 0x88    | 1          | 0      | 0      | 0      | 1      | 0      | 0      | 0      |        |        |        |        |              |           |        |        |

|         | LEDA3 | 0x89    | 1          | 0      | 0      | 0      | 1      | 0      | 0      | 1      |        |        |        |        |              |           |        |        |

|         | LEDA4 | 0x8A    | 1          | 0      | 0      | 0      | 1      | 0      | 1      | 0      |        |        |        |        |              |           |        |        |

| Α       | LEDA5 | 0x8B    | 1          | 0      | 0      | 0      | 1      | 0      | 1      | 1      | 25     | 5 ste  | ps fo  |        | ensity<br>ED | each each | n sing | gle    |

|         | LEDA6 | 0x8C    | 1          | 0      | 0      | 0      | 1      | 1      | 0      | 0      |        |        |        |        |              |           |        |        |

|         | LEDA7 | 0x8D    | 1          | 0      | 0      | 0      | 1      | 1      | 0      | 1      |        |        |        |        |              |           |        |        |

|         | LEDA8 | 0x8E    | 1          | 0      | 0      | 0      | 1      | 1      | 1      | 0      |        |        |        |        |              |           |        |        |

|         | LEDA9 | 0x8F    | 1          | 0      | 0      | 0      | 1      | 1      | 1      | 1      |        |        |        |        |              |           |        |        |

|         | LEDA0 | 0x90    | 1          | 0      | 0      | 1      | 0      | 0      | 0      | 0      |        |        |        |        |              |           |        |        |

|         | LEDB0 | 0x91    | 1          | 0      | 0      | 1      | 0      | 0      | 0      | 1      |        |        |        |        |              |           |        |        |

|         | LEDB1 | 0x92    | 1          | 0      | 0      | 1      | 0      | 0      | 1      | 0      |        |        |        |        |              |           |        |        |

|         | LEDB2 | 0x93    | 1          | 0      | 0      | 1      | 0      | 0      | 1      | 1      |        |        |        |        |              |           |        |        |

|         | LEDB3 | 0x94    | 1          | 0      | 0      | 1      | 0      | 1      | 0      | 0      |        |        |        |        |              |           |        |        |

|         | LEDB4 | 0x95    | 1          | 0      | 0      | 1      | 0      | 1      | 0      | 1      |        |        |        |        |              |           |        |        |

| В       | LEDB5 | 0x96    | 1          | 0      | 0      | 1      | 0      | 1      | 1      | 0      | 25     | 5 ste  | ps fo  |        | ensity<br>ED | eacl      | n sing | gle    |

|         | LEDB6 | 0x97    | 1          | 0      | 0      | 1      | 0      | 1      | 1      | 1      |        |        |        |        |              |           |        |        |

|         | LEDB7 | 0x98    | 1          | 0      | 0      | 1      | 1      | 0      | 0      | 0      |        |        |        |        |              |           |        |        |

|         | LEDB8 | 0x99    | 1          | 0      | 0      | 1      | 1      | 0      | 0      | 1      |        |        |        |        |              |           |        |        |

|         | LEDB9 | 0x9A    | 1          | 0      | 0      | 1      | 1      | 0      | 1      | 0      |        |        |        |        |              |           |        |        |

|         | LEDBA | 0x9B    | 1          | 0      | 0      | 1      | 1      | 0      | 1      | 1      |        |        |        |        |              |           |        |        |

Page 34ams DatasheetDocument Feedback[v2-01] 2016-Oct-12

#### **Dot Correction Register**

The AS1130 offers a feature to define a correction factor for the analog current for every segment. This correction factor is called Dot Correction and is defined in the Dot Correction register (see Figure 37). The Dot Correction Register is selected via data 128 on addr 253.

Figure 37:

Dot Correction Register Format

|         |      |        |        | Ad     | dress  | ;      |        |        |        | Data  D D D D D D D D D D D D D D D D D D D |  |       |       |        |      |  |        |  |  |  |

|---------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------------------------------|--|-------|-------|--------|------|--|--------|--|--|--|

| Segment | HEX  | A<br>7 | A<br>6 | A<br>5 | A<br>4 | A<br>3 | A<br>2 | A<br>1 | A<br>0 |                                             |  |       |       |        |      |  | D<br>0 |  |  |  |

| 0       | 0x00 | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |                                             |  | 8 bit | Dot ( | Correc | tion |  |        |  |  |  |

| 1       | 0x01 | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1      |                                             |  | 8 bit | Dot ( | Correc | tion |  |        |  |  |  |

| 2       | 0x02 | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 8 bit Dot Correction                        |  |       |       |        |      |  |        |  |  |  |

| 3       | 0x03 | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 8 bit Dot Correction                        |  |       |       |        |      |  |        |  |  |  |

| 4       | 0x04 | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      |                                             |  | 8 bit | Dot ( | Correc | tion |  |        |  |  |  |

| 5       | 0x05 | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 1      |                                             |  | 8 bit | Dot ( | Correc | tion |  |        |  |  |  |

| 6       | 0x06 | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 0      |                                             |  | 8 bit | Dot ( | Correc | tion |  |        |  |  |  |

| 7       | 0x07 | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 1      |                                             |  | 8 bit | Dot ( | Correc | tion |  |        |  |  |  |

| 8       | 0x08 | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 0      |                                             |  | 8 bit | Dot ( | Correc | tion |  |        |  |  |  |

| 9       | 0x09 | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 1      | 8 bit Dot Correction                        |  |       |       |        |      |  |        |  |  |  |

| А       | 0x0A | 0      | 0      | 0      | 0      | 1      | 0      | 1      | 0      | 8 bit Dot Correction                        |  |       |       |        |      |  |        |  |  |  |

| В       | 0x0B | 0      | 0      | 0      | 0      | 1      | 0      | 1      | 1      | 1 8 bit Dot Correction                      |  |       |       |        |      |  |        |  |  |  |

ams Datasheet Page 35

[v2-01] 2016-Oct-12 Document Feedback

#### **Control-Registers**

The AS1130 device contains 14 control registers which are listed in Figure 38. All registers are selected using a 8-bit address word, and communication is done via the serial interface. Select the Control Register via the Register Selection (see Figure 31).

The Control Register is selected via data 192 on addr 253.

Figure 38: Control Register Address Map

| Davieter News                            | LIEV |            |    | Reg | jister | Addr | ess |    |    | Register Data |

|------------------------------------------|------|------------|----|-----|--------|------|-----|----|----|---------------|

| Register Name                            | HEX  | <b>A</b> 7 | A6 | A5  | A4     | A3   | A2  | A1 | A0 | D7:D0         |

| Picture                                  | 0x00 | 0          | 0  | 0   | 0      | 0    | 0   | 0  | 0  | See Figure 39 |

| Movie                                    | 0x01 | 0          | 0  | 0   | 0      | 0    | 0   | 0  | 1  | See Figure 40 |

| Movie Mode                               | 0x02 | 0          | 0  | 0   | 0      | 0    | 0   | 1  | 0  | See Figure 41 |

| Frame Time / Scroll                      | 0x03 | 0          | 0  | 0   | 0      | 0    | 0   | 1  | 1  | See Figure 42 |

| Display Option                           | 0x04 | 0          | 0  | 0   | 0      | 0    | 1   | 0  | 0  | See Figure 43 |

| Current Source                           | 0x05 | 0          | 0  | 0   | 0      | 0    | 1   | 0  | 1  | See Figure 44 |