# **CLASS D AUDIO DRIVER WITH PRECISION DEAD-TIME GENERATOR**

#### Features

- 0.5 A peak output (Si8241)

- 4.0 A peak output (Si8244)

- PWM input

- High-precision linear programmable dead-time generator

- 0.4 ns to 1 µs

- High latchup immunity >100 V/ns

- Up to 1500 Vrms output-output isolation, supply voltage of ±750 V

#### Applications

Class D audio amplifiers

#### Description

The Si824x isolated driver family combines two isolated drivers in a single package. The Si8241/44 are high-side/low-side drivers specifically targeted at high-power (>30 W) audio applications. Versions with peak output currents of 0.5 A (Si8241) and 4.0 A (Si8244) are available. All drivers operate with a maximum supply voltage of 24 V.

Based on Silicon Labs' proprietary isolation technology, the Si824x audio drivers incorporate input-to-output and output-to-output isolation, which enables level-translation of signals without additional external circuits as well as use of bipolar supply voltage up to ±750 V. The Si824x audio drivers feature an integrated dead-time generator that provides highly precise control for achieving optimal THD. These products also have overlap protection that safeguards against shoot-through current damage. The CMOS-based design also provides robust immunity from latch-up and high-voltage transients. The extremely low propagation delays enable faster modulation frequencies for an enhanced audio experience. The TTL level compatible inputs with >400 mV hysteresis are available in PWM input configuration; other options include UVLO levels of 8 V or 10 V. These products are available in narrow body SOIC packages.

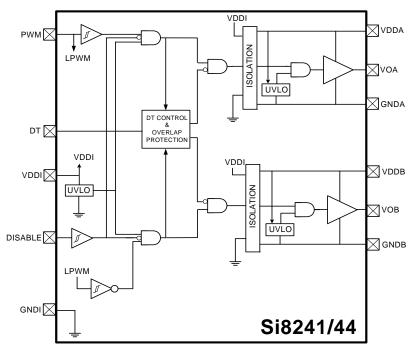

## **Functional Block Diagram**

- Input to output isolation for low noise (up to 2500 V)

- Up to 8 MHz operation

- Wide operating range

- -40 to +125 °C

- Transient immunity >45 kV/µs

- RoHS-compliant

- SOIC-16 narrow body

## Patents Pending

# TABLE OF CONTENTS

# Section

# <u>Page</u>

| 1. Top-Level Block Diagram                              | 4   |

|---------------------------------------------------------|-----|

| 2. Electrical Specifications                            | 5   |

| 2.1. Test Circuits                                      | 7   |

| 3. Functional Description                               | .12 |

| 3.1. Typical Performance Characteristics (0.5 Amp)      | .13 |

| 3.2. Typical Performance Characteristics (4.0 Amp)      | .15 |

| 3.3. Family Overview and Logic Operation During Startup |     |

| 3.4. Power Supply Connections                           |     |

| 3.5. Power Dissipation Considerations                   | .18 |

| 3.6. Layout Considerations                              |     |

| 3.7. Undervoltage Lockout Operation                     | .20 |

| 3.8. Programmable Dead Time and Overlap Protection      |     |

| 4. Applications                                         |     |

| 4.1. Class D Digital Audio Driver                       |     |

| 5. Pin Descriptions                                     |     |

| 6. Ordering Guide                                       |     |

| 7. Package Outline: 16-Pin Narrow Body SOIC             |     |

| 8. Land Pattern: 16-Pin Narrow Body SOIC                |     |

| 9. Top Marking: 16-Pin Narrow Body SOIC                 |     |

| 9.1. Si824x Top Marking (16-Pin Narrow Body SOIC)       |     |

| 9.2. Top Marking Explanation (16-Pin Narrow Body SOIC)  |     |

| Document Change List                                    |     |

| Contact Information                                     |     |

|                                                         | .50 |

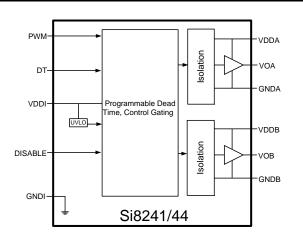

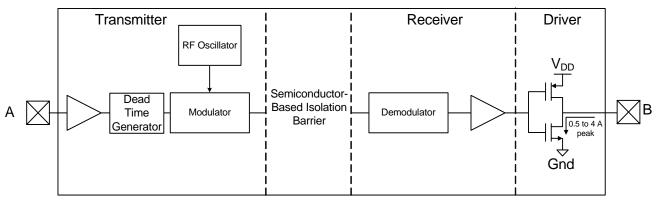

# 1. Top-Level Block Diagram

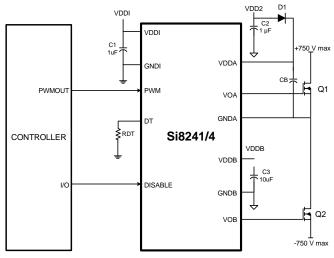

Figure 1. Si8241/44 Single-Input High-Side/Low-Side Isolated Drivers

# 2. Electrical Specifications

## Table 1. Electrical Characteristics<sup>1</sup>

4.5 V < VDDI < 5.5 V, VDDA = VDDB = 12 V or 15 V. TA = -40 to +125 °C. Typical specs at 25 °C

| Parameter                               | Symbol                  | Test Conditions                                                                  | Min                       | Тур  | Max  | Units |

|-----------------------------------------|-------------------------|----------------------------------------------------------------------------------|---------------------------|------|------|-------|

| DC Specifications                       |                         |                                                                                  |                           |      |      |       |

| Input-Side Power Supply<br>Voltage      | VDDI                    |                                                                                  | 4.5                       | _    | 5.5  | V     |

| Driver Supply Voltage                   | VDDA, VDDB              | Voltage between VDDA and<br>GNDA, and VDDB and GNDB<br>(See "6. Ordering Guide") | 6.5                       | _    | 24   | v     |

| Input Supply Quiescent<br>Current       | IDDI(Q)                 | (Q) Si8241/44                                                                    |                           | 2    | 3    | mA    |

| Output Supply Quiescent<br>Current      | IDDA(Q),<br>IDDB(Q)     | Current per channel                                                              |                           | _    | 3.0  | mA    |

| Input Supply Active Current             | IDDI                    | PWM freq = 500 kHz                                                               | —                         | 2.5  |      | mA    |

| Output Supply Active Current            | IDDO                    | PWM freq = 500 kHz                                                               | —                         | 3.6  |      | mA    |

| Input Pin Leakage Current               | IPWM                    |                                                                                  | -10                       | _    | +10  | µA dc |

| Input Pin Leakage Current               | IDISABLE                |                                                                                  | -10                       | —    | +10  | µA dc |

| Logic High Input Threshold              | VIH                     |                                                                                  | 2.0                       | —    |      | V     |

| Logic Low Input Threshold               | VIL                     |                                                                                  | _                         | —    | 0.8  | V     |

| Input Hysteresis                        | VI <sub>HYST</sub>      |                                                                                  | 400                       | 450  |      | mV    |

| Logic High Output Voltage VOAH,<br>VOBH |                         | IOA, IOB = -1 mA                                                                 | (VDDA<br>/VDDB)<br>— 0.04 | _    |      | V     |

| Logic Low Output Voltage                | VOAL, VOBL              | IOA, IOB = 1 mA                                                                  | —                         | —    | 0.04 | V     |

| Output Short-Circuit Pulsed             | IOA(SCL),               | Si8241, Figure 2                                                                 | —                         | 0.5  |      | А     |

| Sink Current                            | IOB(SCL)                | Si8244, Figure 2                                                                 | —                         | 4.0  |      | А     |

| Output Short-Circuit Pulsed             | IOA(SCH),               | Si8241, Figure 3                                                                 | —                         | 0.25 |      | А     |

| Source Current                          | IOB(SCH)                | Si8244, Figure 3                                                                 | —                         | 2.0  |      | А     |

| Output Sink Desistance                  | D                       | Si8241                                                                           | —                         | 5.0  |      | Ω     |

| Output Sink Resistance                  | R <sub>ON(SINK)</sub>   | Si8244                                                                           | —                         | 1.0  | —    | Ω     |

| Output Source Desistence                | P                       | Si8241                                                                           | —                         | 15   | —    | Ω     |

| Output Source Resistance                | R <sub>ON(SOURCE)</sub> | Si8244                                                                           | _                         | 2.7  |      | Ω     |

**1.** VDDA = VDDB = 12 V for 8 V UVLO and 10 V UVLO devices.

**2.** The largest RDT resistor that can be used is 220 k $\Omega$ .

Table 1. Electrical Characteristics<sup>1</sup> (Continued)4.5 V < VDDI < 5.5 V, VDDA = VDDB = 12 V or 15 V. TA = -40 to +125 °C. Typical specs at 25 °C</td>

| Parameter                                                      | Symbol                                       | Test Conditions                                                        | Min  | Тур  | Мах  | Units |

|----------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------|------|------|------|-------|

| VDDI Undervoltage Threshold                                    | VDDI <sub>UV+</sub>                          | VDDI rising                                                            | 3.60 | 4.0  | 4.45 | V     |

| VDDI Undervoltage Threshold                                    | VDDI <sub>UV-</sub>                          | VDDI falling                                                           | 3.30 | 3.70 | 4.15 | V     |

| VDDI Lockout Hysteresis                                        | VDDI <sub>HYS</sub>                          |                                                                        |      | 250  | _    | mV    |

| VDDA, VDDB Undervoltage<br>Threshold                           | VDDA <sub>UV+</sub> ,<br>VDDB <sub>UV+</sub> | VDDA, VDDB rising                                                      |      |      |      |       |

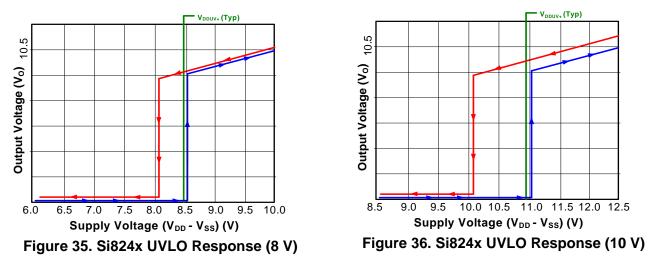

| 8 V Threshold                                                  |                                              | See Figure 35 on page 21.                                              | 7.50 | 8.60 | 9.40 | V     |

| 10 V Threshold                                                 |                                              | See Figure 36 on page 21.                                              | 9.60 | 11.1 | 12.2 | V     |

| VDDA, VDDB Undervoltage<br>Threshold                           | VDDA <sub>UV-</sub> ,<br>VDDB <sub>UV-</sub> | VDDA, VDDB falling                                                     |      |      |      |       |

| 8 V Threshold                                                  |                                              | See Figure 35 on page 21.                                              | 7.20 | 8.10 | 8.70 | V     |

| 10 V Threshold                                                 |                                              | See Figure 36 on page 21.                                              | 9.40 | 10.1 | 10.9 | V     |

| VDDA, VDDB<br>Lockout Hysteresis                               | VDDA <sub>HYS</sub> ,<br>VDDB <sub>HYS</sub> | UVLO voltage = 8 V                                                     |      | 600  | _    | mV    |

| VDDA, VDDB<br>Lockout Hysteresis                               | VDDA <sub>HYS</sub> ,<br>VDDB <sub>HYS</sub> | UVLO voltage = 10 V                                                    | _    | 1000 | _    | mV    |

| AC Specifications                                              |                                              |                                                                        |      | 1    | L    |       |

| Minimum Pulse Width                                            |                                              |                                                                        | —    | 10   |      | ns    |

| Propagation Delay                                              | t <sub>PHL</sub> , t <sub>PLH</sub>          | CL = 1 nF                                                              | _    | 25   | 60   | ns    |

| Pulse Width Distortion<br> t <sub>PLH</sub> - t <sub>PHL</sub> | PWD                                          |                                                                        |      | 1.0  | 5.60 | ns    |

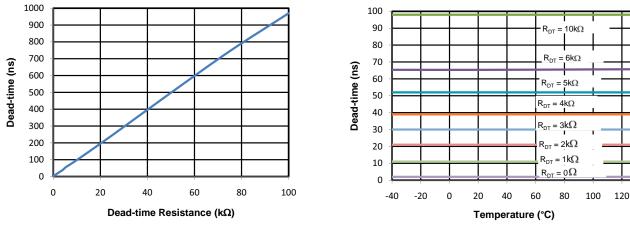

| Programmed Dead Time <sup>2</sup>                              | DT                                           | See Figures 37 and 38                                                  | 0.4  | _    | 1000 | ns    |

|                                                                |                                              | C <sub>L</sub> = 1 nF (Si8241)                                         | —    | _    | 20   | ns    |

| Output Rise and Fall Time                                      | t <sub>R</sub> ,t <sub>F</sub>               | C <sub>L</sub> = 1 nF (Si8244)                                         |      | —    | 12   | ns    |

| Shutdown Time from<br>Disable True                             | t <sub>SD</sub>                              |                                                                        | _    | _    | 60   | ns    |

| Restart Time from<br>Disable False                             | t <sub>RESTART</sub>                         |                                                                        |      | _    | 60   | ns    |

| Device Start-up Time                                           | t <sub>START</sub>                           | Time from VDD_ = VDD_UV+<br>to VOA, VOB = VIA, VIB                     | _    | 5    | 7    | μs    |

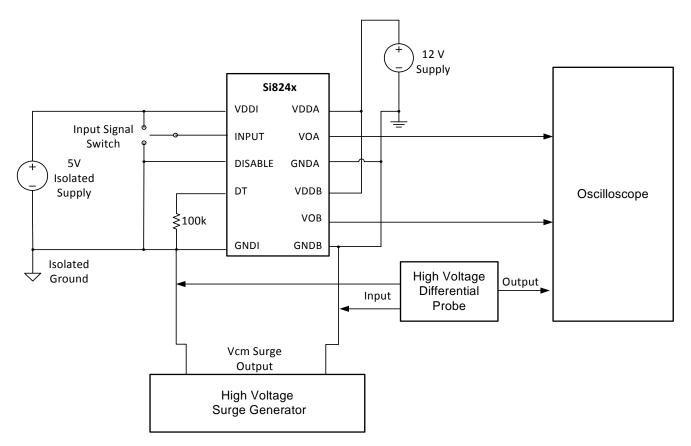

| Common Mode<br>Transient Immunity                              | СМТІ                                         | VIA, VIB, PWM = VDDI or 0 V<br>V <sub>CM</sub> = 1500 V (see Figure 4) | 25   | 45   | _    | kV/µs |

1. VDDA = VDDB = 12 V for 8 V UVLO and 10 V UVLO devices.

2. The largest RDT resistor that can be used is 220 k $\Omega$ .

## 2.1. Test Circuits

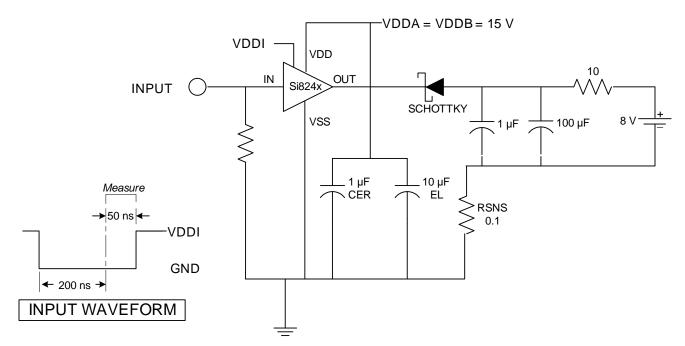

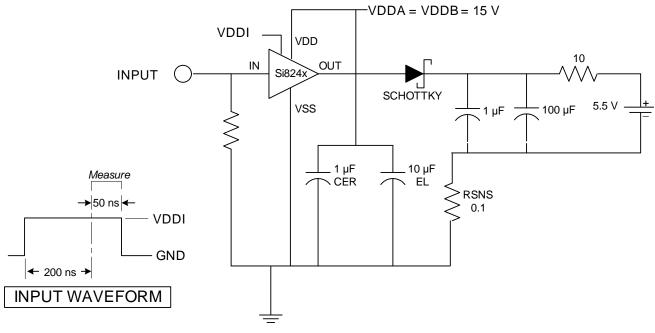

Figures 2 and 3 depict sink current and source current test circuits.

Figure 3. IOH Source Current Test Circuit

## Figure 4. Common Mode Transient Immunity Test Circuit

## Table 2. Regulatory Information\*

The Si824x is certified under CSA Component Acceptance Notice 5A. For more details, see File 232873.

61010-1: Up to 300  $V_{RMS}$  reinforced insulation working voltage; up to 600  $V_{RMS}$  basic insulation working voltage.

60950-1: Up to 300 V<sub>RMS</sub> reinforced insulation working voltage; up to 600 V<sub>RMS</sub> basic insulation working voltage. **VDE**

The Si824x is certified according to IEC 60747-5-2. For more details, see File 5006301-4880-0001.

60747-5-2: Up to 560  $V_{\text{peak}}$  for basic insulation working voltage.

UL

CSA

The Si824x is certified under UL1577 component recognition program. For more details, see File E257455.

Rated up to 2500  $V_{RMS}$  isolation voltage for basic protection.

\*Note: Regulatory Certifications apply to 2.5 kV<sub>RMS</sub> rated devices, which are production tested to 3.0 kV<sub>RMS</sub> for 1 sec. For more information, see "6.Ordering Guide" on page 25.

|                                                   |                 |                | Value                              |      |

|---------------------------------------------------|-----------------|----------------|------------------------------------|------|

| Parameter                                         | Symbol          | Test Condition | NBSOIC-16<br>2.5 kV <sub>RMS</sub> | Unit |

| Nominal Air Gap<br>(Clearance) <sup>1</sup>       | L(101)          |                | 4.01                               | mm   |

| Nominal External Tracking (Creepage) <sup>1</sup> | L(1O2)          |                | 4.01                               | mm   |

| Minimum Internal Gap<br>(Internal Clearance)      |                 |                | 0.011                              | mm   |

| Tracking Resistance<br>(Proof Tracking Index)     | PTI             | IEC60112       | 600                                | V    |

| Erosion Depth                                     | ED              |                | 0.019                              | mm   |

| Resistance<br>(Input-Output) <sup>2</sup>         | R <sub>IO</sub> |                | 10 <sup>12</sup>                   | Ω    |

| Capacitance<br>(Input-Output) <sup>2</sup>        | C <sub>IO</sub> | f = 1 MHz      | 1.4                                | pF   |

| Input Capacitance <sup>3</sup>                    | Cl              |                | 4.0                                | pF   |

#### Table 3. Insulation and Safety-Related Specifications

Notes:

The values in this table correspond to the nominal creepage and clearance values as detailed in "7. Package Outline: 16-Pin Narrow Body SOIC". VDE certifies the clearance and creepage limits as 4.7 mm minimum for the NB SOIC-16. UL does not impose a clearance and creepage minimum for component level certifications. CSA certifies the clearance and creepage limits as 3.9 mm minimum for the NB SOIC 16.

2. To determine resistance and capacitance, the Si824x is converted into a 2-terminal device. Pins 1–8 are shorted together to form the first terminal and pins 9–16 are shorted together to form the second terminal. The parameters are then measured between these two terminals.

3. Measured from input pin to ground.

## Table 4. IEC 60664-1 (VDE 0884 Part 2) Ratings

| Parameter                   | Test Conditions                                  | Specification |

|-----------------------------|--------------------------------------------------|---------------|

| Falameter                   |                                                  | NB SOIC-16    |

| Basic Isolation Group       | Material Group                                   | Ι             |

|                             | Rated Mains Voltages $\leq$ 150 V <sub>RMS</sub> | I-IV          |

| Installation Classification | Rated Mains Voltages $\leq$ 300 V <sub>RMS</sub> | 1-111         |

| Installation Classification | Rated Mains Voltages $\leq$ 400 V <sub>RMS</sub> | 1-11          |

|                             | Rated Mains Voltages $\leq$ 600 V <sub>RMS</sub> | 1-11          |

## Table 5. IEC 60747-5-2 Insulation Characteristics\*

| Parameter                                                            | Symbol            | Test Condition                                                                                                                               | Characteristic             | Unit   |

|----------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------|

| Farameter                                                            | Symbol            | lest Condition                                                                                                                               | NB SOIC-16                 | - Unit |

| Maximum Working Insulation Voltage                                   | V <sub>IORM</sub> |                                                                                                                                              | 560                        | V peak |

| Input to Output Test Voltage                                         | V <sub>PR</sub>   | Method b1<br>(V <sub>IORM</sub> x 1.875 = V <sub>PR</sub> ,<br>100%<br>Production Test, t <sub>m</sub> = 1 sec,<br>Partial Discharge < 5 pC) | 1050                       | V peak |

| Transient Overvoltage                                                | V <sub>IOTM</sub> | t = 60 sec                                                                                                                                   | 4000                       | V peak |

| Pollution Degree<br>(DIN VDE 0110, Table 1)                          |                   |                                                                                                                                              | 2                          |        |

| Insulation Resistance at T <sub>S</sub> ,<br>V <sub>IO</sub> = 500 V | R <sub>S</sub>    |                                                                                                                                              | >10 <sup>9</sup>           | Ω      |

| *Note: Maintenance of the safety data is e 40/125/21.                | ensured by pr     | otective circuits. The Si824x prov                                                                                                           | ides a climate classificat | ion of |

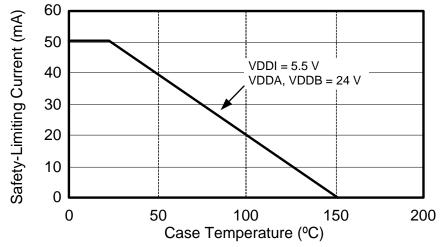

# Table 6. IEC Safety Limiting Values<sup>1</sup>

| Symbol         | Test Condition                                                                                                                                                             | NB SOIC-16                                                                                                                                                                   | Unit                                                                                                                                                                                                                           |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Τ <sub>S</sub> |                                                                                                                                                                            | 150                                                                                                                                                                          | °C                                                                                                                                                                                                                             |

| I <sub>S</sub> | $\theta_{JA} = 105 \text{ °C/W} (NB \text{ SOIC-16}),$<br>$V_{DDI} = 5.5 \text{ V},$<br>$V_{DDA} = V_{DDB} = 24 \text{ V},$<br>$T_J = 150 \text{ °C}, T_A = 25 \text{ °C}$ | 50                                                                                                                                                                           | mA                                                                                                                                                                                                                             |

| PD             |                                                                                                                                                                            | 1.2                                                                                                                                                                          | W                                                                                                                                                                                                                              |

|                | T <sub>S</sub>                                                                                                                                                             | $T_{S} = \frac{\theta_{JA} = 105 \text{ °C/W (NB SOIC-16)},}{V_{DDI} = 5.5 \text{ V},}$ $V_{DDA} = V_{DDB} = 24 \text{ V},}$ $T_{J} = 150 \text{ °C}, T_{A} = 25 \text{ °C}$ | $T_{S} = 105 \text{ °C/W (NB SOIC-16),} \\ I_{S} = V_{DDA} = 105 \text{ °C/W (NB SOIC-16),} \\ V_{DDI} = 5.5 \text{ V,} \\ V_{DDA} = V_{DDB} = 24 \text{ V,} \\ T_{J} = 150 \text{ °C,} T_{A} = 25 \text{ °C} \end{cases} $ 50 |

Notes:

1. Maximum value allowed in the event of a failure. Refer to the thermal derating curve in Figure 5. 2. The Si82xx is tested with  $V_{DDI} = 5.5 \text{ V}$ ,  $V_{DDA} = V_{DDB} = 24 \text{ V}$ ,  $T_J = 150 \text{ °C}$ ,  $C_L = 100 \text{ pF}$ , input 2 MHz 50% duty cycle square wave.

Table 7. Thermal Characteristics

| Parameter                                | Symbol        | NB<br>SOIC-16 | Unit |

|------------------------------------------|---------------|---------------|------|

| IC Junction-to-Air<br>Thermal Resistance | $\theta_{JA}$ | 105           | °C/W |

Figure 5. NB SOIC-16, Thermal Derating Curve, Dependence of Safety Limiting Values with Case Temperature per DIN EN 60747-5-2

| Table 8. Absolute | Maximum | Ratings <sup>1</sup> |

|-------------------|---------|----------------------|

|-------------------|---------|----------------------|

| Parameter                                 | Symbol           | Min  | Тур | Max       | Units            |

|-------------------------------------------|------------------|------|-----|-----------|------------------|

| Storage Temperature <sup>2</sup>          | T <sub>STG</sub> | -65  | _   | +150      | °C               |

| Ambient Temperature under Bias            | T <sub>A</sub>   | -40  | _   | +125      | °C               |

| Input-side Supply Voltage                 | VDDI             | -0.6 | _   | 6.0       | V                |

| Driver-side Supply Voltage                | VDDA, VDDB       | -0.6 | _   | 30        | V                |

| Voltage on any Pin with respect to Ground | VIN              | -0.5 | _   | VDD + 0.5 | V                |

| Output Drive Current per Channel          | Ι <sub>Ο</sub>   | _    | _   | 10        | mA               |

| Lead Solder Temperature (10 sec)          |                  | _    | _   | 260       | °C               |

| Latchup Immunity <sup>3</sup>             |                  | —    |     | 100       | V/ns             |

| Maximum Isolation (Input to Output)       |                  | —    |     | 2500      | V <sub>RMS</sub> |

| Maximum Isolation (Output to Output)      |                  | —    |     | 1500      | V <sub>RMS</sub> |

Notes:

1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**2.** VDE certifies storage temperature from –40 to 150 °C.

3. Latchup immunity specification is for slew rate applied across GNDI and GNDA or GNDB.

# 3. Functional Description

The operation of an Si824x channel is analogous to that of an opto coupler and gate driver, except an RF carrier is modulated instead of light. This simple architecture provides a robust isolated data path and requires no special considerations or initialization at start-up. A simplified block diagram for a single Si824x channel is shown in Figure 6.

Figure 6. Simplified Channel Diagram

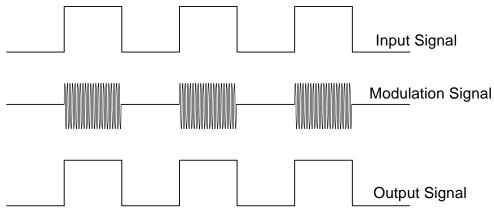

A channel consists of an RF Transmitter and RF Receiver separated by a semiconductor-based isolation barrier. Referring to the Transmitter, input A modulates the carrier provided by an RF oscillator using on/off keying. The Receiver contains a demodulator that decodes the input state according to its RF energy content and applies the result to output B via the output driver. This RF on/off keying scheme is superior to pulse code schemes as it provides best-in-class noise immunity, low power consumption, and better immunity to magnetic fields. See Figure 7 for more details.

Figure 7. Modulation Scheme

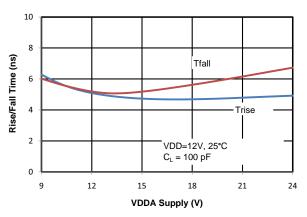

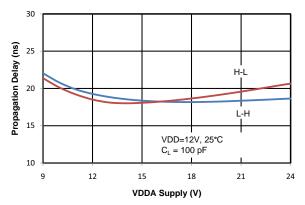

# 3.1. Typical Performance Characteristics (0.5 Amp)

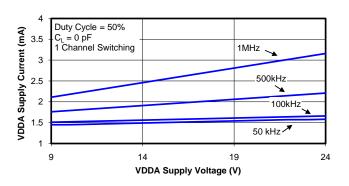

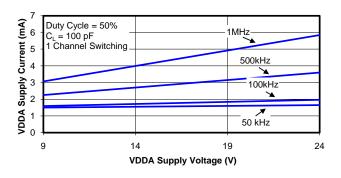

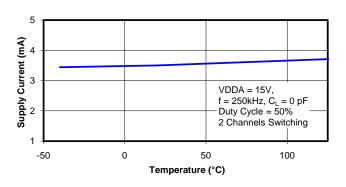

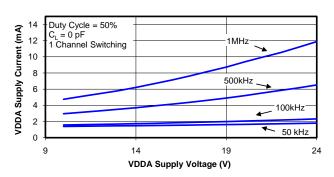

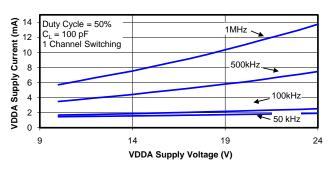

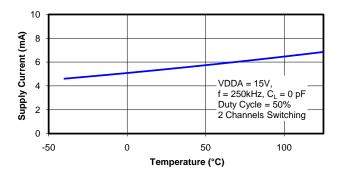

The typical performance characteristics depicted in Figures 8 through 19 are for information purposes only. Refer to Table 1 on page 5 for actual specification limits.

Figure 8. Rise/Fall Time vs. Supply Voltage

Figure 9. Propagation Delay vs. Supply Voltage

Figure 10. Supply Current vs. Supply Voltage

Figure 11. Supply Current vs. Supply Voltage

Figure 12. Supply Current vs. Temperature

Figure 13. Rise/Fall Time vs. Load

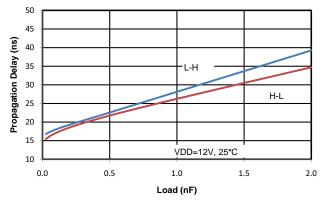

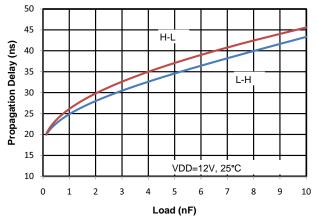

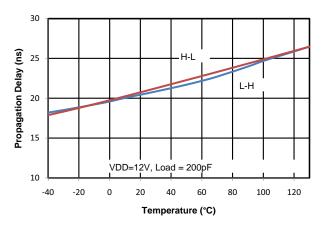

Figure 14. Propagation Delay vs. Load

Figure 15. Propagation Delay vs. Temperature

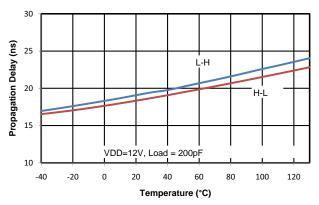

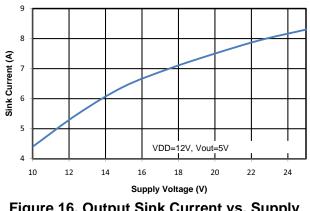

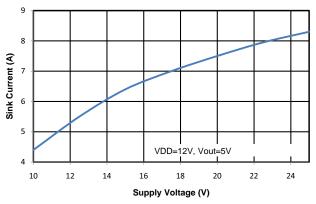

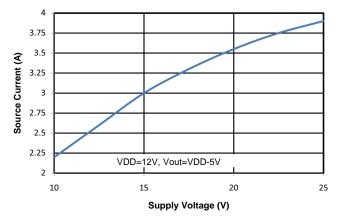

Figure 16. Output Sink Current vs. Supply Voltage

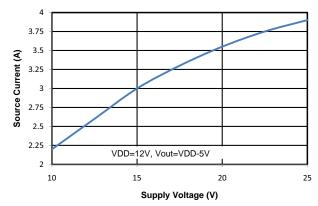

Figure 17. Output Source Current vs. Supply Voltage

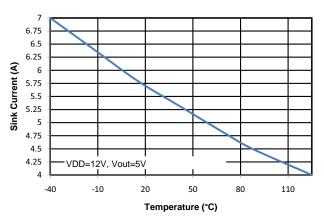

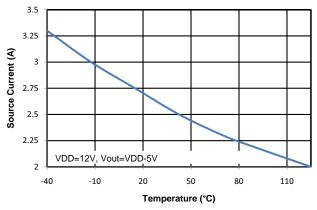

Figure 18. Output Sink Current vs. Temperature

Figure 19. Output Source Current vs. Temperature

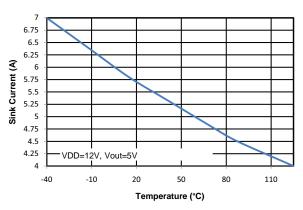

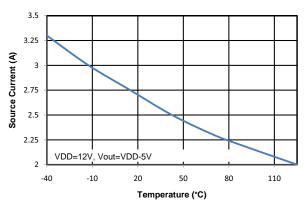

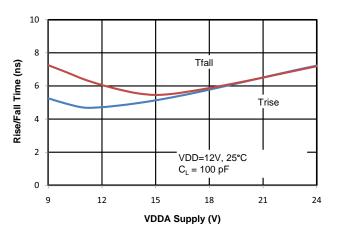

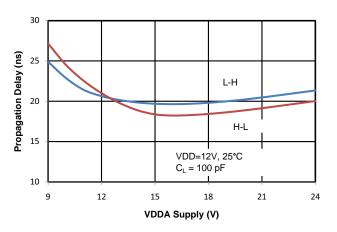

# 3.2. Typical Performance Characteristics (4.0 Amp)

The typical performance characteristics depicted in Figures 20 through 31 are for information purposes only. Refer to Table 1 on page 5 for actual specification limits.

Figure 21. Propagation Delay vs. Supply Voltage

Figure 22. Supply Current vs. Supply Voltage

Figure 23. Supply Current vs. Supply Voltage

Figure 24. Supply Current vs. Temperature

Figure 25. Rise/Fall Time vs. Load

Figure 26. Propagation Delay vs. Load

Figure 27. Propagation Delay vs. Temperature

Figure 28. Output Sink Current vs. Supply Voltage

Figure 29. Output Source Current vs. Supply Voltage

Figure 30. Output Sink Current vs. Temperature

Figure 31. Output Source Current vs. Temperature

## 3.3. Family Overview and Logic Operation During Startup

The Si824x family of isolated drivers consists of high-side, low-side, and dual driver configurations.

#### 3.3.1. Products

Table 9 shows the configuration and functional overview for each product in this family.

| Part Number | Configuration      | UVLO Voltage | Programmable<br>Dead Time | Inputs | Peak Output<br>Current (A) |

|-------------|--------------------|--------------|---------------------------|--------|----------------------------|

| Si8241      | High-Side/Low-Side | 8 V/10 V     | $\checkmark$              | PWM    | 0.5                        |

| Si8244      | High-Side/Low-Side | 8 V/10 V     | $\checkmark$              | PWM    | 4.0                        |

#### Table 9. Si824x Family Overview

#### 3.3.2. Device Behavior

Table 10 contains truth tables for the Si8241/4 families.

## Table 10. Si824x Family Truth Table\*

| PWM Input  | VDDI State | Disable | Out     | put | Notes                                                                     |

|------------|------------|---------|---------|-----|---------------------------------------------------------------------------|

| r www.mput | VDDI State | Disable | VOA VOB |     |                                                                           |

| Н          | Powered    | L       | Н       | L   | Output transition occurs after internal dead time expires.                |

| L          | Powered    | L       | L       | Н   | Output transition occurs after internal dead time expires.                |

| Х          | Unpowered  | Х       | L       | L   | Output returns to input state within 7 $\mu$ s of VDDI power restoration. |

| Х          | Powered    | Н       | L       | L   | Device is disabled.                                                       |

## 3.4. Power Supply Connections

Isolation requirements mandate individual supplies for VDDI, VDDA, and VDDB. The decoupling caps for these supplies must be placed as close to the VDD and GND pins of the Si824x as possible. The optimum values for these capacitors depend on load current and the distance between the chip and the regulator that powers it. Low effective series resistance (ESR) capacitors, such as Tantalum, are recommended.

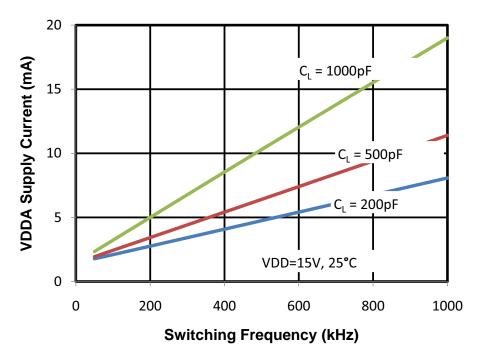

## 3.5. Power Dissipation Considerations

Proper system design must assure that the Si824x operates within safe thermal limits across the entire load range. The Si824x total power dissipation is the sum of the power dissipated by bias supply current, internal switching losses, and power delivered to the load. Equation 1 shows total Si824x power dissipation. In a non-overlapping system, such as a high-side/low-side driver, n = 1.

$$P_{D} = V_{DDI}I_{DDI} + 2(V_{DDO}I_{QOUT} + C_{int}V_{DDO}^{2}F) + 2n(C_{L}V_{DDO}^{2}F)$$

where:

$P_D$  is the total Si824x device power dissipation (W)

I<sub>DDI</sub> is the input-side maximum bias current (3 mA)

$I_{OOUT}$  is the driver die maximum bias current (2.5 mA)

C<sub>int</sub> is the internal parasitic capacitance (75 pF for the 0.5 A driver and 370 pF for the 4.0 A driver)

$V_{DDI}$  is the input-side VDD supply voltage (4.5 to 5.5 V)

V<sub>DDO</sub> is the driver-side supply voltage (10 to 24 V)

F is the switching frequency (Hz)

n is the overlap constant (max value = 2)

#### Equation 1.

The maximum power dissipation allowable for the Si824x is a function of the package thermal resistance, ambient temperature, and maximum allowable junction temperature, as shown in Equation 2:

$$\begin{split} & \mathsf{P}_{\mathsf{Dmax}} \leq \frac{\mathsf{T}_{\mathsf{jmax}} - \mathsf{T}_{\mathsf{A}}}{\mathsf{\theta} \mathsf{ja}} \\ & \mathsf{where:} \\ & \mathsf{P}_{\mathsf{Dmax}} = \mathsf{Maximum} \; \mathsf{Si824x} \; \mathsf{power} \; \mathsf{dissipation} \; (\mathsf{W}) \\ & \mathsf{T}_{\mathsf{jmax}} = \mathsf{Si824x} \; \mathsf{maximum} \; \mathsf{junction} \; \mathsf{temperature} \; (150 \; ^\circ\mathsf{C}) \\ & \mathsf{T}_{\mathsf{A}} = \; \mathsf{Ambient} \; \mathsf{temperature} \; (^\circ\mathsf{C}) \\ & \mathsf{\theta} \mathsf{ja} = \; \mathsf{Si824x} \; \mathsf{junction-to-air} \; \mathsf{thermal} \; \mathsf{resistance} \; (105 \; ^\circ\mathsf{C/W}) \\ & \mathsf{F} = \; \mathsf{Si824x} \; \mathsf{switching} \; \mathsf{frequency} \; (\mathsf{Hz}) \end{split}$$

#### Equation 2.

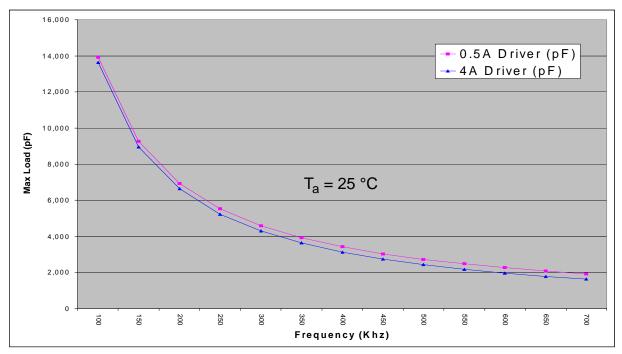

Substituting values for  $P_{Dmax}$   $T_{jmax}$ ,  $T_A$ , and  $\theta_{ja}$  into Equation 2 results in a maximum allowable total power dissipation of 1.19 W. Maximum allowable load is found by substituting this limit and the appropriate datasheet values from Table 1 on page 5 into Equation 1 and simplifying. The result is Equation 3 (0.5 A driver) and Equation 4 (4.0 A driver), both of which assume VDDI = 5 V and VDDA = VDDB = 18 V.

$$C_{L(MAX)} = \frac{1.4 \times 10^{-3}}{F} - 7.5 \times 10^{-11}$$

Equation 3.

$$C_{L(MAX)} \; = \; \frac{1.4 \times 10^{-3}}{F} - 3.7 \times 10^{-10}$$

Equation 4.

Equation 1 and Equation 2 are graphed in Figure 32 where the points along the load line represent the package dissipation-limited value of CL for the corresponding switching frequency.

Figure 32. Max Load vs. Switching Frequency

Figure 33. Switching Frequency vs. Load Current

# 3.6. Layout Considerations

It is most important to minimize ringing in the drive path and noise on the Si824x VDD lines. Care must be taken to minimize parasitic inductance in these paths by locating the Si824x as close to the device it is driving as possible. In addition, the VDD supply and ground trace paths must be kept short. For this reason, the use of power and ground planes is highly recommended. A split ground plane system having separate ground and VDD planes for power devices and small signal components provides the best overall noise performance.

## 3.7. Undervoltage Lockout Operation

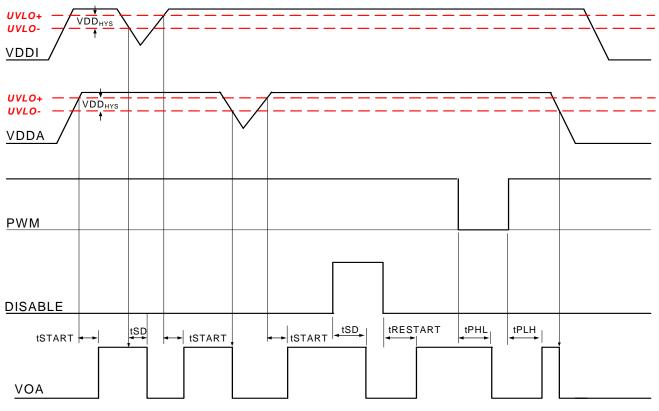

Device behavior during start-up, normal operation and shutdown is shown in Figure 34, where UVLO+ and UVLOare the positive-going and negative-going thresholds respectively. Note that outputs VOA and VOB default low when input side power supply (VDDI) is not present.

## 3.7.1. Device Startup

Outputs VOA and VOB are held low during power-up until VDD is above the UVLO threshold for time period tSTART. Following this, the outputs follow the states of inputs VIA and VIB.

#### 3.7.2. Undervoltage Lockout

Undervoltage Lockout (UVLO) is provided to prevent erroneous operation during device startup and shutdown or when VDD is below its specified operating circuits range. The input (control) side, Driver A and Driver B, each have their own undervoltage lockout monitors.

The Si824x input side enters UVLO when VDDI  $\leq$  VDDI<sub>UV-</sub>, and exits UVLO when VDDI > VDDI<sub>UV+</sub>. The driver outputs, VOA and VOB, remain low when the input side of the Si824x is in UVLO and their respective VDD supply (VDDA, VDDB) is within tolerance. Each driver output can enter or exit UVLO independently. For example, VOA unconditionally enters UVLO when VDDA falls below VDDA<sub>UV-</sub> and exits UVLO when VDDA rises above VDDA<sub>UV+</sub>.

Figure 34. Device Behavior during Normal Operation and Shutdown

#### 3.7.3. Undervoltage Lockout (UVLO)

The UVLO circuit unconditionally drives VO low when VDD is below the lockout threshold. Referring to Figures 35 and 36, upon power up, the Si824x is maintained in UVLO until VDD rises above  $VDD_{UV+}$ . During power down, the Si824x enters UVLO when VDD falls below the UVLO threshold plus hysteresis (i.e.,  $VDD \leq VDD_{UV+} - VDD_{HYS}$ ).

#### 3.7.4. Control Inputs

PWM inputs are high-true, TTL level-compatible logic inputs. VOA is high and VOB is low when the PWM input is high, and VOA is low and VOB is high when the PWM input is low.

#### 3.7.5. Disable Input

When brought high, the DISABLE input unconditionally drives VOA and VOB low regardless of the states of input. Device operation terminates within tSD after DISABLE =  $V_{IH}$  and resumes within tRESTART after DISABLE =  $V_{IL}$ . The DISABLE input has no effect if VDDI is below its UVLO level (i.e. VOA, VOB remain low). The DISABLE input is typically connected to external protection circuitry to unconditionally halt driver operation in the event of a fault.

## 3.8. Programmable Dead Time and Overlap Protection

All high-side/low-side drivers (Si8241/4) include programmable overlap protection to prevent outputs VOA and VOB from being high at the same time. These devices also include programmable dead time, which adds a userprogrammable delay between transitions of VOA and VOB. When enabled, dead time is present on all transitions, even after overlap recovery. The amount of dead time delay (DT) is programmed by a single resistor (RDT) connected from the DT input to ground per Equation 5. Minimum dead time (approximately 400 ps) can be achieved by connecting the DT pin to VDDI. Note that dead time accuracy is limited by the resistor's (R<sub>DT</sub>) tolerance and temperature coefficient. See Figures 37 and 38 for additional information about dead time operation.

$DT\approx 10\times RDT$  where:  $DT=\mbox{ dead time (ns)}$  and  $RDT=\mbox{ dead time programming resistor }(k\Omega)$

Equation 5.

Figure 37. Dead Time vs.Resistance (R<sub>DT</sub>)

Figure 38. Dead Time vs. Temperature

# 4. Applications

The following examples illustrate typical circuit configurations using the Si824x.

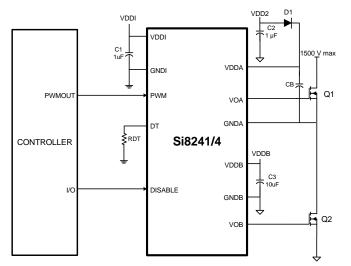

## 4.1. Class D Digital Audio Driver

Figures 39 and 40 show the Si8241/4 controlled by a single PWM signal. Supply can be unipolar (0 to 1500 V) or bipolar ( $\pm$  750 V).

Figure 39. Si824x in Half-Bridge Audio Application

Figure 40. Si824x in Half-Bridge Audio Application

D1 and CB form a conventional bootstrap circuit that allows VOA to operate as a high-side driver for Q1, which has a maximum drain voltage of 1500 V. VOB is connected as a conventional low-side driver. Note that the input side of the Si824x requires VDD in the range of 4.5 to 5.5 V, while the VDDA and VDDB output side supplies must be between 6.5 and 24 V with respect to their respective grounds. The boot-strap start up time will depend on the CB cap chosen. VDD2 is usually the same as VDDB. Also note that the bypass capacitors on the Si824x should be located as close to the chip as possible. Moreover, it is recommended that 0.1 and 10  $\mu$ F bypass capacitors be used to reduce high frequency noise and maximize performance. The D1 diode should be a fast-recovery diode; it should be able to withstand the maximum high voltage (e.g. 1500 V) and be low-loss. See "AN486: High-Side Bootstrap Design Using Si823x ISODrivers in Power Delivery Systems" for more details in selecting the bootstrap cap (CB) and diode (D1).

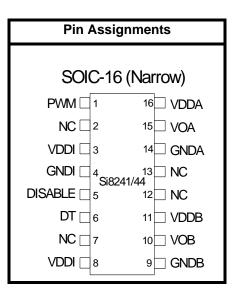

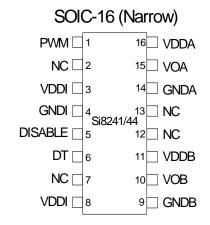

# 5. Pin Descriptions

## Table 11. Si8241/44 PWM Input HS/LS Isolated Driver (SOIC-16)

| Pin | Name    | Description                                                                                                                                                                                                                                                                           |  |  |  |  |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | PWM     | PWM input.                                                                                                                                                                                                                                                                            |  |  |  |  |

| 2   | NC      | No connection.                                                                                                                                                                                                                                                                        |  |  |  |  |

| 3   | VDDI    | nput-side power supply terminal; connect to a source of 4.5 to 5.5 V.                                                                                                                                                                                                                 |  |  |  |  |

| 4   | GNDI    | Input-side ground terminal.                                                                                                                                                                                                                                                           |  |  |  |  |

| 5   | DISABLE | Device Disable. When high, this input unconditionally drives outputs VOA, VOB LOW. It is strongly recommended that this input be connected to external logic level to avoid erroneous operation due to capacitive noise coupling.                                                     |  |  |  |  |

| 6   | DT      | Dead time programming input. The value of the resistor connected from DT to ground sets the dead time between output transitions of VOA and VOB. Defaults to 1 ns dead time when connected to VDDI or left open (see "3.8.Programmable Dead Time and Overlap Protection" on page 22). |  |  |  |  |

| 7   | NC      | No connection.                                                                                                                                                                                                                                                                        |  |  |  |  |

| 8   | VDDI    | Input-side power supply terminal; connect to a source of 4.5 to 5.5 V.                                                                                                                                                                                                                |  |  |  |  |

| 9   | GNDB    | Ground terminal for Driver B.                                                                                                                                                                                                                                                         |  |  |  |  |

| 10  | VOB     | Driver B output (low-side driver).                                                                                                                                                                                                                                                    |  |  |  |  |

| 11  | VDDB    | Driver B power supply voltage terminal; connect to a source of 6.5 to 24 V.                                                                                                                                                                                                           |  |  |  |  |

| 12  | NC      | No connection.                                                                                                                                                                                                                                                                        |  |  |  |  |

| 13  | NC      | No connection.                                                                                                                                                                                                                                                                        |  |  |  |  |

| 14  | GNDA    | Ground terminal for Driver A.                                                                                                                                                                                                                                                         |  |  |  |  |

| 15  | VOA     | Driver A output (high-side driver).                                                                                                                                                                                                                                                   |  |  |  |  |

| 16  | VDDA    | Driver A power supply voltage terminal; connect to a source of 6.5 to 24 V.                                                                                                                                                                                                           |  |  |  |  |

# 6. Ordering Guide

The currently available OPNs are listed in Table 12.

| Ordering Part<br>Number (OPN)                                                                                                                                                                                                                                                                          | Input Type | Package    | Drive<br>Strength | Output               | UVLO<br>Voltage | Isolation<br>Rating<br>(Input to<br>Output) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-------------------|----------------------|-----------------|---------------------------------------------|

| Si8241BB-D-IS1                                                                                                                                                                                                                                                                                         | PWM        | NB SOIC-16 | 0.5 A             |                      | 8 V             | 2.5 kVrms                                   |

| Si8241CB-D-IS1                                                                                                                                                                                                                                                                                         | PWM        | NB SOIC-16 | 0.5 A             | - High-Side/Low-Side | 10 V            |                                             |

| Si8244BB-D-IS1                                                                                                                                                                                                                                                                                         | PWM        | NB SOIC-16 | 4 A               |                      | 8 V             |                                             |

| Si8244CB-D-IS1                                                                                                                                                                                                                                                                                         | PWM        | NB SOIC-16 | 47                |                      | 10 V            |                                             |

| *Note: All packages are RoHS-compliant with peak reflow temperatures of 260 °C according to the JEDEC industry standard classifications and peak solder temperatures. Tape and reel options are specified by adding an "R" suffix to the ordering part number. "Si" and "SI" are used interchangeably. |            |            |                   |                      |                 |                                             |

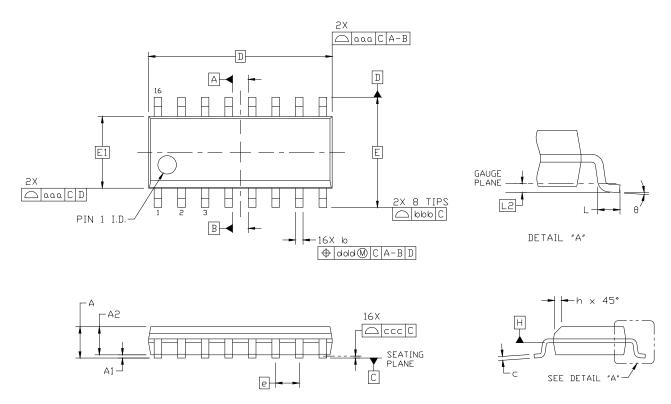

# 7. Package Outline: 16-Pin Narrow Body SOIC

Figure 41 illustrates the package details for the Si824x in a 16-pin narrow-body SOIC (SO-16). Table 13 lists the values for the dimensions shown in the illustration.

Figure 41. 16-pin Small Outline Integrated Circuit (SOIC) Package

| Dimension | Min      | Max  | Dimension | Min  | Max  |

|-----------|----------|------|-----------|------|------|

| A         |          | 1.75 | L         | 0.40 | 1.27 |

| A1        | 0.10     | 0.25 | L2        | 0.25 | BSC  |

| A2        | 1.25     | _    | h         | 0.25 | 0.50 |

| b         | 0.31     | 0.51 | θ         | 0°   | 8°   |

| С         | 0.17     | 0.25 | aaa       | 0.10 |      |

| D         | 9.90 BSC |      | bbb       | 0.20 |      |

| E         | 6.00 BSC |      | ccc       | 0.10 |      |

| E1        | 3.90 BSC |      | ddd       | 0.25 |      |

| е         | 1.27 BSC |      |           |      |      |

## **Table 13. Package Diagram Dimensions**

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

This drawing conforms to the JEDEC Solid State Outline MS-012, Variation AC. 3.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

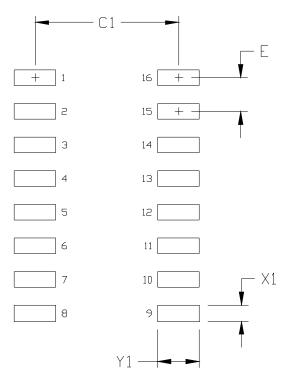

# 8. Land Pattern: 16-Pin Narrow Body SOIC

Figure 42 illustrates the recommended land pattern details for the Si824x in a 16-pin narrow-body SOIC. Table 14 lists the values for the dimensions shown in the illustration.

## Figure 42. 16-Pin Narrow Body SOIC PCB Land Pattern

## Table 14. 16-Pin Narrow Body SOIC Land Pattern Dimensions

| Dimension                                                                                                                                                                                                                                                                                          | Feature            | (mm) |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|--|--|--|

| C1                                                                                                                                                                                                                                                                                                 | Pad Column Spacing | 5.40 |  |  |  |

| E Pad Row Pitch                                                                                                                                                                                                                                                                                    |                    | 1.27 |  |  |  |

| X1                                                                                                                                                                                                                                                                                                 | Pad Width          | 0.60 |  |  |  |

| Y1                                                                                                                                                                                                                                                                                                 | Pad Length         | 1.55 |  |  |  |

| <ul> <li>Notes:</li> <li>1. This Land Pattern Design is based on IPC-7351 pattern SOIC127P600X165-16N for Density Level B (Median Land Protrusion).</li> <li>2. All feature sizes shown are at Maximum Material Condition (MMC) and a card fabrication tolerance of 0.05 mm is assumed.</li> </ul> |                    |      |  |  |  |

# 9. Top Marking: 16-Pin Narrow Body SOIC

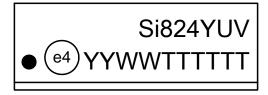

# 9.1. Si824x Top Marking (16-Pin Narrow Body SOIC)

# 9.2. Top Marking Explanation (16-Pin Narrow Body SOIC)

| Line 1 Marking: | Base Part Number<br>Ordering Options<br>See Ordering Guide for more<br>information. | Si824 = ISOdriver product series<br>Y = Peak output current<br>1 = $0.5 \text{ A}$<br>4 = $4.0 \text{ A}$<br>U = UVLO level<br>B = $8 \text{ V}$ ; C = $10 \text{ V}$<br>V = Isolation rating<br>B = $2.5 \text{ kV}$ |  |  |

|-----------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Line 2 Marking: | YY = Year<br>WW = Workweek                                                          | Assigned by the Assembly House. Corresponds to the year and workweek of the mold date.                                                                                                                                |  |  |

| Line 2 Marking. | TTTTTT = Mfg Code                                                                   | Manufacturing Code from Assembly Purchase Order form.                                                                                                                                                                 |  |  |

# DOCUMENT CHANGE LIST

# **Revision 0.1 to Revision 0.2**

- Deleted Table 3.

- Added Tables 2 through 7.

- Added Figure 5.

- Updated common-mode transient immunity specification throughout.

## **Revision 0.2 to Revision 0.3**

- Updated Figures 2 and 3 on page 7.

- Added Figure 4 on page 8.

- Updated Table 12 on page 25.

## Revision 0.3 to Revision 1.0

- Updated Table 12, Ordering Part Numbers.

- Added Revision D Ordering Part Numbers.

- Removed all Ordering Part Numbers of previous revisions.

- Removed moisture sensitivity level table notes.

# **CONTACT INFORMATION**

Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500 Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

#### Patent Notice

Silicon Labs invests in research and development to help our customers differentiate in the market with innovative low-power, small size, analogintensive mixed-signal solutions. Silicon Labs' extensive patent portfolio is a testament to our unique approach and world-class engineering team.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Skyworks:

<u>SI8241CB-B-IS1R</u> <u>SI8241BB-B-IS1R</u> <u>SI8244BB-C-IS1R</u> <u>SI8244CB-C-IS1R</u> <u>SI8244CB-C-IS1</u> <u>SI8244CB-C-IS1</u> <u>SI8241CB-B-IS1</u> SI8244BB-C-IS1 SI8241BB-B-IS1