## **1.8V / 2.5V Differential 2:1** Mux Input to 1:6 CML Clock/Data Fanout Buffer/Translator

# Multi-Level Inputs w/ Internal Termination Description

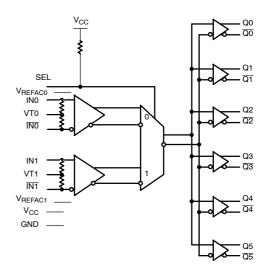

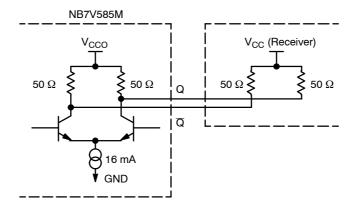

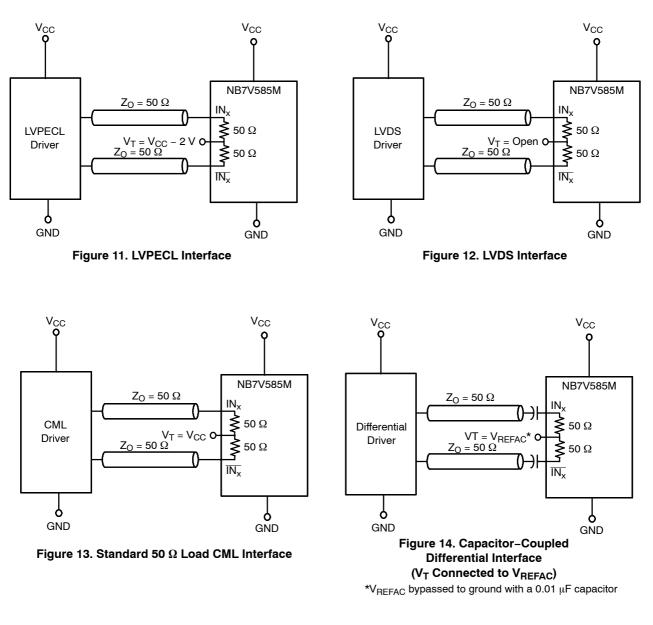

The NB7V585M is a differential 1-to-6 CML clock/data distribution chip featuring a 2:1 Clock/Data input multiplexer with an input select pin. The INx/INx inputs incorporate internal 50  $\Omega$  termination resistors and will accept LVPECL, CML, or LVDS logic levels (see Figure 9). The NB7V585M produces six identical output copies of clock or data operating up to 6 GHz or 10 Gb/s, respectively. As such, NB7V585M is ideal for SONET, GigE, Fiber Channel, Backplane and other clock/data distribution applications. The 16 mA differential CML output structure provides matching internal 50  $\Omega$  source terminations, 400 mV output swings when externally terminated with a 50  $\Omega$  resistor to V<sub>CC</sub> (see Figure 14) and is optimized for low skew and minimal jitter. The NB7V585M is powered with either 1.8 V or 2.5 V supply and is offered in a low profile 5x5 mm 32-pin QFN package.

Application notes, models, and support documentation are available at www.onsemi.com.

The NB7V585M is a member of the GigaComm<sup>™</sup> family of high performance clock products.

### Features

- Maximum Input Data Rate > 10 Gb/s

- Data Dependent Jitter < 10 ps

- Maximum Input Clock Frequency > 6 GHz

- Random Clock Jitter < 0.8 ps RMS, Max

- Low Skew 1:6 CML Outputs, 20 ps Max

- 2:1 Multi-Level Mux Inputs

- 175 ps Typical Propagation Delay

- 50 ps Typical Rise and Fall Times

- Differential CML Outputs, 330 mV Peak-to-Peak, Typical

- Operating Range:  $V_{CC} = 1.71$  V to 1.89 V

- Internal 50 Ω Input Termination Resistors

- V<sub>REFAC</sub> Reference Output

- QFN32 Package, 5 mm x 5 mm

- -40°C to +85°C Ambient Operating Temperature

- These are Pb-Free Devices

### **ON Semiconductor®**

http://onsemi.com

\*For additional marking information, refer to Application Note AND8002/D.

### SIMPLIFIED LOGIC DIAGRAM

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.

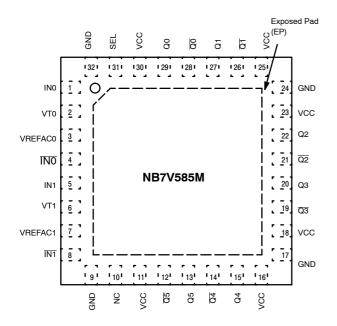

Figure 1. 32-Lead QFN Pinout (Top View)

#### Table 2. PIN DESCRIPTION

#### I/O Pin Name Description INO. INO LVPECL, CML, 1.4 Non-inverted, Inverted, Differential Inputs 5,8 IN1, IN1 LVDS Input 2,6 VT0, VT1 Internal 100 $\Omega$ Center-tapped Termination Pin for IN0/IN0 and IN1/IN1 LVTTL/LVCMOS 31 SEL Input Select pin; LOW for IN0 Inputs, HIGH for IN1 Inputs; defaults HIGH when left open Input NC 10 No Connect \_ 11, 16, 18 VCC Positive Supply Voltage. 23, 25, 30 29, 28 Q0, Q0 CML Output Non-inverted, Inverted Differential Outputs (Note 1). 27, 26 Q1, Q1 Q2, Q2 Non-inverted, Inverted Differential Outputs (Note 1). 22, 21 CML Output 20, 19 Q3. Q3 15, 14 Q4, Q4 CML Output Non-inverted, Inverted Differential Outputs (Note 1). Q5, Q5 13, 12 9, 17 GND Negative Supply Voltage, connected to Ground 24, 32 З VREFAC0 \_ Output Voltage Reference for Capacitor-Coupled Inputs, only 7 VREFAC1 The Exposed Pad (EP) on the QFN-32 package bottom is thermally connected to the EP die for improved heat transfer out of package. The exposed pad must be attached to a heat-sinking conduit. The pad is electrically connected to the die, and must be electrically and thermally connected to GND on the PC board.

In the differential configuration when the input termination pins (VT0, VT1) are connected to a common termination voltage or left open, and if no signal is applied on INn/INn input, then, the device will be susceptible to self-oscillation. Qn/Qn outputs have internal 50 Ω source termination resistors.

2. All  $V_{CC}$  and GND pins must be externally connected to a power supply for proper operation.

### 1

**Table 1. INPUT SELECT FUNCTION TABLE**

**CLK Input Selected**

IN0

IN1

\*Defaults HIGH when left open.

SEL\*

0

### Table 3. ATTRIBUTES

| Characte                                               | Value                  |                      |  |  |

|--------------------------------------------------------|------------------------|----------------------|--|--|

| ESD Protection Human Body Model<br>Machine Model       |                        | > 4 kV<br>> 200 V    |  |  |

| Input Pullup Resistor (R <sub>PU</sub> )               |                        | 75 kΩ                |  |  |

| Moisture Sensitivity (Note 3)                          |                        | Level 1              |  |  |

| Flammability Rating                                    | Oxygen Index: 28 to 34 | UL 94 V-0 @ 0.125 in |  |  |

| Transistor Count                                       | 308                    |                      |  |  |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test |                        |                      |  |  |

3. For additional information, see Application Note AND8003/D.

### **Table 4. MAXIMUM RATINGS**

| Symbol            | Parameter                                                     | Condition 1         | Condition 2                          | Rating                        | Unit         |

|-------------------|---------------------------------------------------------------|---------------------|--------------------------------------|-------------------------------|--------------|

| V <sub>CC</sub>   | Positive Power Supply                                         | GND = 0 V           |                                      | 3.0                           | V            |

| V <sub>IO</sub>   | Input/Output Voltage                                          | GND = 0 V           | $-0.5 \leq V_{IO} \leq V_{CC} + 0.5$ | -0.5 to V <sub>CC</sub> + 0.5 | V            |

| V <sub>INPP</sub> | Differential Input Voltage  IN <sub>x</sub> - IN <sub>x</sub> |                     |                                      | 1.89                          | V            |

| I <sub>IN</sub>   | Input Current Through $R_T$ (50 $\Omega$ Resistor)            |                     |                                      | ±40                           | mA           |

| I <sub>OUT</sub>  | Output Current                                                | Continuous<br>Surge |                                      | 34<br>40                      | mA           |

| IVFREFAC          | V <sub>REFAC</sub> Sink/Source Current                        |                     |                                      | ±1.5                          | mA           |

| T <sub>A</sub>    | Operating Temperature Range                                   |                     |                                      | -40 to +85                    | °C           |

| T <sub>stg</sub>  | Storage Temperature Range                                     |                     |                                      | -65 to +150                   | °C           |

| $\theta_{JA}$     | Thermal Resistance (Junction-to-Ambient)<br>(Note 4)          | 0 lfpm<br>500 lfpm  | QFN-32<br>QFN-32                     | 31<br>27                      | °C/W<br>°C/W |

| θJC               | Thermal Resistance (Junction-to-Case)<br>(Note 4)             | Standard Board      | QFN-32                               | 12                            | °C/W         |

| T <sub>sol</sub>  | Wave Solder Pb-Free                                           |                     |                                      | 265                           | °C           |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

4. JEDEC standard multilayer board – 2S2P (2 signal, 2 power) with 8 filled thermal vias under exposed pad.

| Symbol             | Characteristic                                                                         | Min                                   | Тур                                   | Max                                   | Unit                                         |

|--------------------|----------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------------|

| POWER              | SUPPLY CURRENT                                                                         |                                       |                                       |                                       |                                              |

| I <sub>CC</sub>    | Power Supply Current (Inputs and Outputs Open) $$V_{CC}$$ = 2.65 V $$V_{CC}$$ = 1.89 V |                                       | 235<br>210                            | 260                                   | mA                                           |

| CML OUT            | rPUTS (Note 6)                                                                         |                                       |                                       |                                       | <u>.                                    </u> |

| V <sub>OH</sub>    | Output HIGH Voltage $$V_{CC}$$ = 2.5 V $$V_{CC}$$ = 1.8 V                              | V <sub>CC</sub> – 40<br>2460<br>1760  | V <sub>CC</sub> – 20<br>2480<br>1780  | V <sub>CC</sub><br>2500<br>1800       | mV                                           |

| V <sub>OL</sub>    | Output LOW Voltage $V_{CC} = 2.5 V$<br>$V_{CC} = 1.8 V$                                | V <sub>CC</sub> – 500<br>2000<br>1300 | V <sub>CC</sub> – 400<br>2100<br>1400 | V <sub>CC</sub> – 275<br>2200<br>1500 | mV                                           |

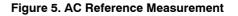

| DIFFERE            | NTIAL INPUTS DRIVEN SINGLE-ENDED (Note 7) (Figure 6)                                   |                                       |                                       |                                       | -                                            |

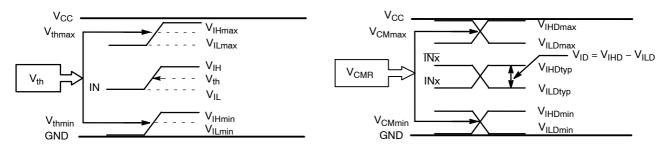

| V <sub>th</sub>    | Input Threshold Reference Voltage Range (Note 8)                                       | 1050                                  |                                       | V <sub>CC</sub> – 100                 | mV                                           |

| V <sub>IH</sub>    | Single-Ended Input HIGH Voltage                                                        | V <sub>th</sub> + 100                 |                                       | V <sub>CC</sub>                       | mV                                           |

| V <sub>IL</sub>    | Single-Ended Input LOW Voltage                                                         | GND                                   |                                       | V <sub>th</sub> – 100                 | mV                                           |

| V <sub>ISE</sub>   | Single-Ended Input Voltage (V <sub>IH</sub> - V <sub>IL</sub> )                        | 200                                   |                                       | 1200                                  | mV                                           |

| V <sub>REFAC</sub> |                                                                                        |                                       |                                       |                                       |                                              |

| V <sub>REFAC</sub> | Output Reference Voltage @ 100 $\mu\text{A}$ for Capacitor – Coupled Inputs, Only      | V <sub>CC</sub> - 625                 | V <sub>CC</sub> – 500                 | V <sub>CC</sub> – 400                 | mV                                           |

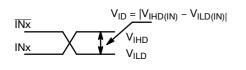

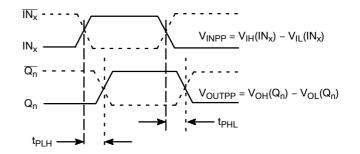

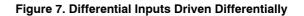

| DIFFERE            | NTIAL INPUTS DRIVEN DIFFERENTIALLY (Note 9) (Figures 4 and                             | l 7)                                  |                                       |                                       |                                              |

| V <sub>IHD</sub>   | Differential Input HIGH Voltage (IN, IN)                                               | 1100                                  |                                       | V <sub>CC</sub>                       | mV                                           |

| V <sub>ILD</sub>   | Differential Input LOW Voltage (IN, IN)                                                | GND                                   |                                       | V <sub>CC</sub> – 100                 | mV                                           |

| V <sub>ID</sub>    | Differential Input Voltage (IN, IN) (V <sub>IHD</sub> - V <sub>ILD</sub> )             | 100                                   |                                       | 1200                                  | mV                                           |

| V <sub>CMR</sub>   | Input Common Mode Range (Differential Configuration, Note 10)<br>(Figure 9)            | 1050                                  |                                       | V <sub>CC</sub> – 50                  | mV                                           |

| I <sub>IH</sub>    | Input HIGH Current IN/IN (VTO / VT1 Open)                                              | -150                                  |                                       | 150                                   | μA                                           |

| IIL                | Input LOW Current IN/IN (VTO / VT1 Open)                                               | -150                                  |                                       | 150                                   | μA                                           |

| CONTRO             | LINPUT (SEL Pin)                                                                       |                                       |                                       |                                       |                                              |

| V <sub>IH</sub>    | Input HIGH Voltage for Control Pin                                                     | V <sub>CC</sub> x 0.65                |                                       | V <sub>CC</sub>                       | mV                                           |

| V <sub>IL</sub>    | Input LOW Voltage for Control Pin                                                      | GND                                   |                                       | V <sub>CC</sub> x 0.35                | mV                                           |

| I <sub>IH</sub>    | Input HIGH Current                                                                     | -150                                  | 20                                    | +150                                  | μΑ                                           |

| IIL                | Input LOW Current                                                                      | -150                                  | 5                                     | +150                                  | μA                                           |

| TERMINA            | TION RESISTORS                                                                         |                                       |                                       |                                       |                                              |

| R <sub>TIN</sub>   | Internal Input Termination Resistor (Measured from INx to VTx)                         | 45                                    | 50                                    | 55                                    | Ω                                            |

| R <sub>TOUT</sub>  | Internal Output Termination Resistor                                                   | 45                                    | 50                                    | 55                                    | Ω                                            |

board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

5. Input and output parameters vary 1:1 with  $V_{CC}$ .

6. CML outputs (Qn/Qn) have internal 50 Ω source termination resistors and must be externally terminated with 50 Ω to V<sub>CCO</sub> for proper operation.

V<sub>th</sub>, V<sub>IH</sub>, V<sub>IL</sub> and V<sub>ISE</sub> parameters must be complied with simultaneously.

V<sub>th</sub> is applied to the complementary input when operating in single–ended mode.

V<sub>III</sub> V<sub>ILD</sub>, V<sub>ILD</sub>, V<sub>ID</sub> and V<sub>CMR</sub> parameters must be complied with simultaneously.

V<sub>CMR</sub> min varies 1:1 with GND, V<sub>CMR</sub> max varies 1:1 with V<sub>CC</sub>. The V<sub>CMR</sub> range is referenced to the most positive side of the differential input signal.

| Symbol                              | Characteristic                                                                                                                                                                         | Min        | Тур        | Max        | Unit               |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|--------------------|

| f <sub>MAX</sub>                    | Maximum Input Clock Frequency, $V_{OUTPP} \ge 200 \text{ mV}$                                                                                                                          | 6.0        | 7.0        |            | GHz                |

| f <sub>DATAMAX</sub>                | Maximum Operating Input Data Rate (PRBS23)                                                                                                                                             | 10         |            |            | Gbps               |

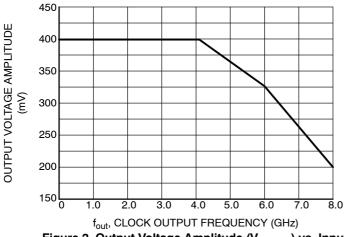

| V <sub>OUTPP</sub>                  | Output Voltage Amplitude (See Figures 4, Note 15) $$f_{in} \le 4.0~\text{GHz}$ $f_{in} \le 6.0~\text{GHz}$$                                                                            | 250<br>200 | 400<br>325 |            | mV                 |

| t <sub>PLH</sub> , t <sub>PHL</sub> | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                   | 125        | 175<br>200 | 250<br>300 | ps                 |

| t <sub>PLH</sub> TC                 | Propagation Delay Temperature Coefficient                                                                                                                                              |            | 100        |            | fs/°C              |

| t <sub>SKEW</sub>                   | Output – Output Skew (Within Device) (Note 12)<br>Device – Device Skew (t <sub>pd</sub> Max – t <sub>pdmin</sub> )                                                                     |            |            | 30<br>50   | ps                 |

| t <sub>DC</sub>                     | Output Clock Duty Cycle (Reference Duty Cycle = 50%) $~f_{in} \leq 4.0~\text{GHz}$                                                                                                     | 45         | 50         | 55         | %                  |

| t <sub>JITTER</sub>                 | $ \begin{array}{ll} \mbox{Output Random Jitter (RJ) (Note 13)} & f_{in} \leq 6.0 \mbox{ GHz} \\ \mbox{Deterministic Jitter (DJ) (Note 14)} & f_{in} \leq 10 \mbox{ Gbps} \end{array} $ |            | 0.2        | 0.8<br>10  | ps rms<br>ps pk–pk |

| V <sub>INPP</sub>                   | Input Voltage Swing (Differential Configuration) (Note 15)                                                                                                                             | 100        |            | 1200       | mV                 |

| t <sub>r</sub> , t <sub>f</sub>     | Output Rise/Fall Times @ 1 GHz (20% – 80%) $Q_n, \overline{Q_n}$                                                                                                                       |            | 50         | 65         | ps                 |

| Table 6. AC CHARACTERISTICS V <sub>CC</sub> = 1.8 V $\pm$ 5% or 2.5 V $\pm$ 5% | %, GND = 0 V, $T_A = -40^{\circ}C$ to $85^{\circ}C$ (Note 11) |

|--------------------------------------------------------------------------------|---------------------------------------------------------------|

|--------------------------------------------------------------------------------|---------------------------------------------------------------|

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

Measured using a 400 mV source, 50% duty cycle clock source. All outputs must be loaded with external 50 Ω to V<sub>CC</sub>. Input edge rates 40 ps (20% – 80%).

12. Skew is measured between outputs under identical transitions and conditions. Duty cycle skew is defined only for differential operation when the delays are measured from cross-point of the inputs to the crosspoint of the outputs.

13. Additive RMS jitter with 50% duty cycle clock signal.

14. Additive Peak-to-Peak data dependent jitter with input NRZ data at PRBS23.

15. Input and output voltage swing is a single-ended measurement operating in differential mode.

Figure 2. Output Voltage Amplitude (V<sub>OUTPP</sub>) vs. Input Frequency (f<sub>in</sub>) at Ambient Temperature (Typical)

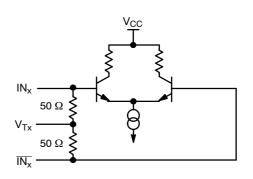

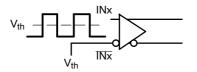

**Figure 3. Input Structure**

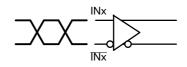

Figure 6. Differential Input Driven Single-Ended

Figure 9. V<sub>CMR</sub> Diagram

Figure 10. Typical CML Output Structure and Termination

#### **ORDERING INFORMATION**

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NB7V585MMNG   | QFN32<br>(Pb-Free) | 74 Units / Rail       |

| NB7V585MMNR4G | QFN32<br>(Pb-Free) | 1000 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

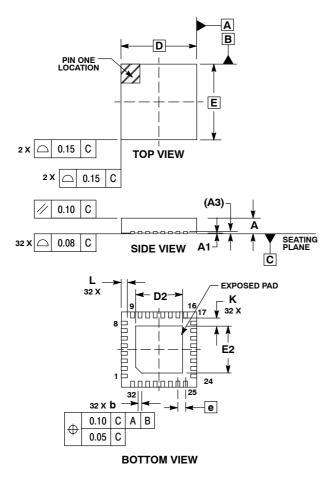

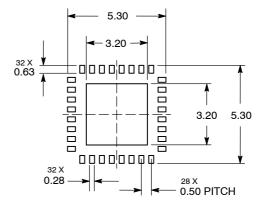

#### PACKAGE DIMENSIONS

QFN32 5\*5\*1 0.5 P CASE 488AM-01 **ISSUE O**

NOTES 1. DIMENSIONS AND TOLERANCING PER

- ASME Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS. 2.

- CONTROLLING DIMENSION: MILLINE TERS. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM TERMINAL COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS. З.

- 4.

|     | MILLIMETERS |       |       |  |

|-----|-------------|-------|-------|--|

| DIM | MIN NOM MA  |       |       |  |

| Α   | 0.800       | 0.900 | 1.000 |  |

| A1  | 0.000       | 0.025 | 0.050 |  |

| A3  | 0.200 REF   |       |       |  |

| b   | 0.180       | 0.250 | 0.300 |  |

| D   | 5.00 BSC    |       |       |  |

| D2  | 2.950       | 3.100 | 3.250 |  |

| Е   | 5.00 BSC    |       |       |  |

| E2  | 2.950       | 3.100 | 3.250 |  |

| е   | 0.500 BSC   |       |       |  |

| κ   | 0.200       |       |       |  |

| L   | 0.300       | 0.400 | 0.500 |  |

#### SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

GigaComm is a trademark of Semiconductor Components Industries, LLC (SCILLC).

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILC does not convey any license under its patent rights or the rights of others. SCILC products are not designed, intended, or authorized for use a components in systems intended for surgical implant into the body, or other applications. intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ON Semiconductor: <u>NB7V585MMNR4G</u> <u>NB7V585MMNG</u>