# onsemi

## 1/6-inch 720p High-Definition (HD) System-On-a-Chip (SOC) Digital Image Sensor

## MT9M114

The MT9M114 from **onsemi** is a 1/6–inch 1.26 Mp CMOS digital image sensor with an active–pixel array of 1296 (H)  $\times$  976 (V). It includes sophisticated camera functions such as auto exposure control, auto white balance, black level control, flicker avoidance, and defect correction. It is designed for low light performance. The MT9M114 produces extraordinarily clear, sharp digital pictures, making it the perfect choice for a wide range of applications, including mobile phones, PC and notebook cameras, and gaming systems.

| Table 1. KEY | PERFORMANCE P | ARAMETERS |

|--------------|---------------|-----------|

|              |               |           |

| Parameter                                                  | Typical Value                                                                 |

|------------------------------------------------------------|-------------------------------------------------------------------------------|

| Optical Format                                             | 1/6-inch                                                                      |

| Active Pixels                                              | 1296 (H) × 976 (V) = 1.26 Mp                                                  |

| Pixel Size                                                 | 1.9 μm x 1.9 μm                                                               |

| Color Filter Array                                         | RGB Bayer                                                                     |

| Shutter                                                    | Electronic Rolling Shutter (ERS)                                              |

| Input Clock Range                                          | 6–54 MHz                                                                      |

| Output MIPI Data Rate Maximum                              | 768 Mb/s                                                                      |

| Max. Frame Rate                                            | 30 fps Full Res<br>36.7 fps 720p<br>75 fps VGA<br>120 fps QVGA (Note 2)       |

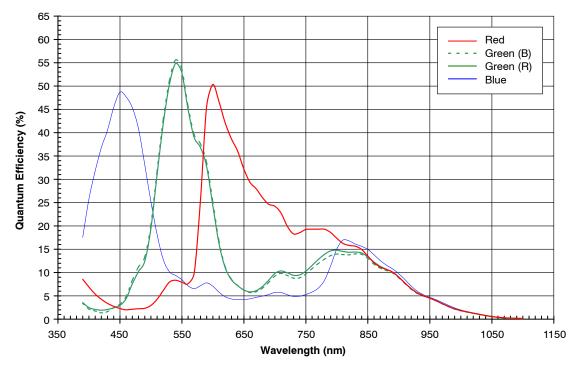

| Responsivity                                               | 2.24 V/Lux-sec (550 nm)                                                       |

| SNR <sub>MAX</sub>                                         | 37 dB                                                                         |

| Dynamic Range                                              | 70.8 dB                                                                       |

| Supply Voltage<br>Digital<br>Analog<br>I/O<br>PLL<br>PHY   | 1.7–1.95 V<br>2.5–3.1 V<br>1.7–1.95 V or 2.5–3.1 V<br>2.5–3.1 V<br>1.7–1.95 V |

| Power Consumption                                          | 135 mW (Note 1)                                                               |

| Operating Temperature Range<br>(Junction) – T <sub>J</sub> | –30°C to 70°C                                                                 |

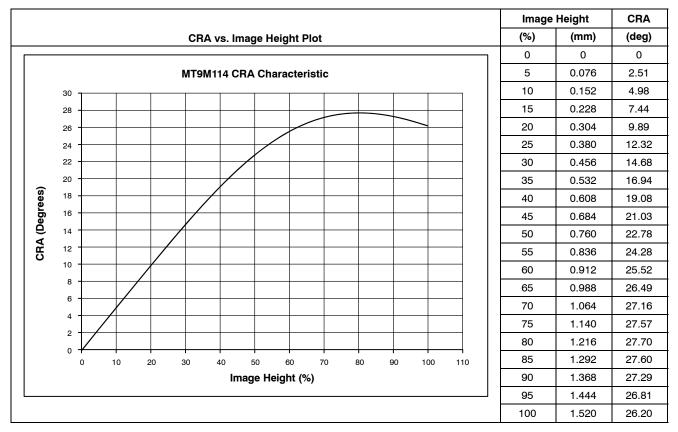

| Chief Ray Angle                                            | 27.7°                                                                         |

| Active Imager Size                                         | 2.46 mm (H) × 1.85 mm (V),<br>3.08 mm Diagonal                                |

| Package Options                                            | Bare Die, CSP                                                                 |

1. Power consumption for typical voltages and 720p output.

2. Reduced FOV.

#### Features

- Superior Low-light Performance

- Ultra-low Power

- 720p HD Video at 30 fps

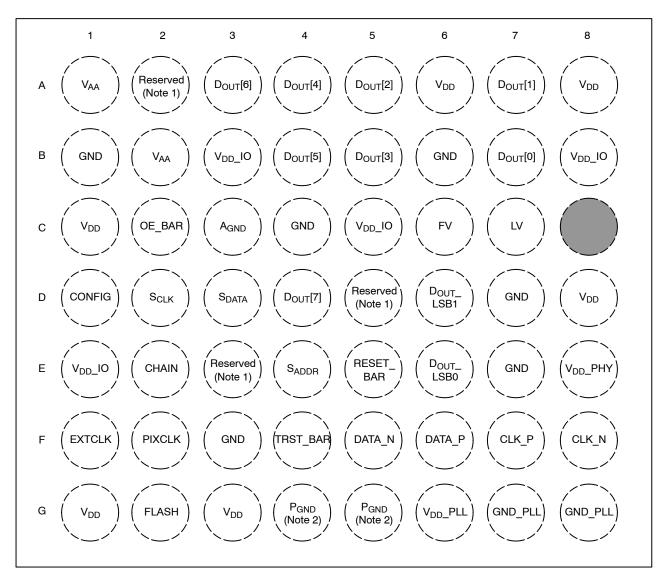

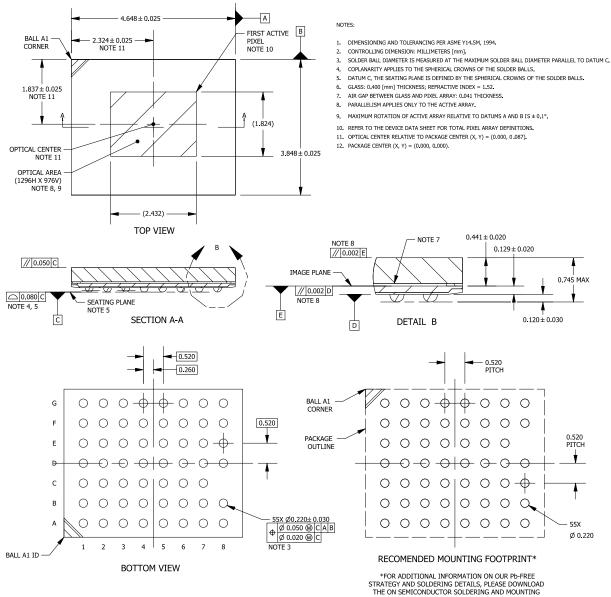

ODCSP55 4.7x3.9 CASE 570BP

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

- Internal Master Clock Generated by On-chip Phase-locked Loop (PLL) Oscillator

- Electronic Rolling Shutter (ERS), Progressive Scan

- Integrated Image Flow Processor (IFP) for Single-die Camera Module

- Automatic Image Correction and Enhancement

- Arbitrary Image Scaling with Anti-aliasing

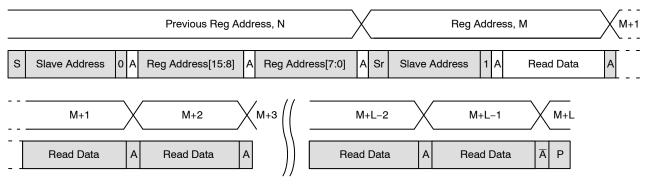

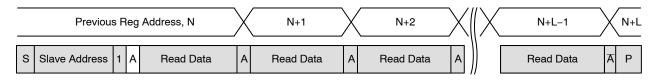

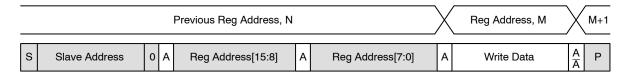

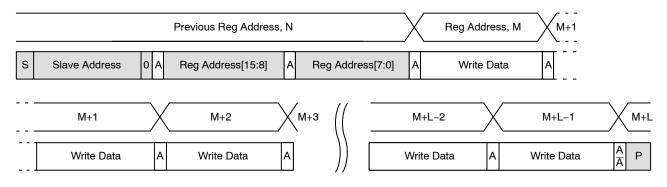

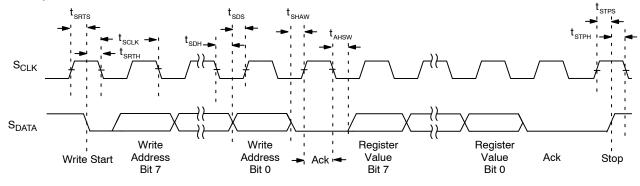

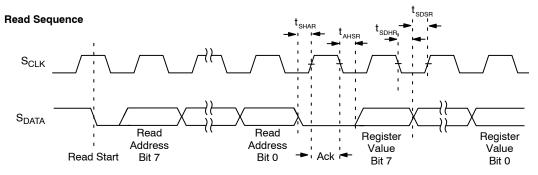

- Two-wire Serial Interface Providing Access to Registers and Microcontroller Memory

- Selectable Output Data Format: YCbCr, 565RGB, 555RGB, 444RGB, Processed Bayer, BT656, RAW8– and RAW8+2–bit

- Parallel and MIPI Data Output

- Independently Configurable Gamma Correction

- Adaptive Polynomial Lens Shading Correction

- UVC Interface

- Perspective Correction

- Multi-camera Synchronization

## Applications

- Embedded Notebook, Netbook, and Desktop Monitor Cameras

- Tethered PC Cameras

- Game Consoles

- Cell Phones, Mobile Devices, and Consumer Video Communications

- Surveillance, Medical, and Industrial Applications

#### **ORDERING INFORMATION**

#### Table 2. AVAILABLE PART NUMBERS

| Part Number              | Product Description | Orderable Product Attribute Description |

|--------------------------|---------------------|-----------------------------------------|

| MT9M114D00STCZK24BC1-200 | 1 MP 1/6" SOC       | Die Sales, 200 μm Thickness             |

| MT9M114EBLSTCZ-CR1       | 1 MP 1/6" SOC CIS   | Chip Tray without Protective Film       |

| MT9M114EBLSTCZ-CR        | 1 MP 1/6" SOC CIS   | Chip Tray without Protective Film       |

See the **onsemi** Device Nomenclature document (<u>TND310/D</u>) for a full description of the naming convention used for image sensors. For reference documentation, including information on evaluation kits, please visit our web site at <u>www.onsemi.com</u>.

#### **FUNCTIONAL DESCRIPTION**

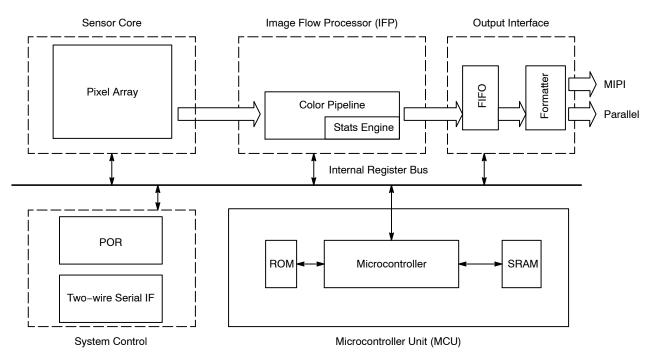

The MT9M114 from **onsemi** is a 1/6-inch 1.26 Mp CMOS digital image sensor with an integrated advanced camera system. This camera system features a microcontroller (MCU), a sophisticated image flow processor (IFP), MIPI and parallel output ports (only one output port can be used at a time). The microcontroller manages all functions of the camera system and sets key operation parameters for the sensor core to optimize the quality of raw image data entering the IFP. The IFP will be responsible for processing and enhancing the image.

The entire system-on-a-chip (SOC) has superior low-light performance that is particularly suitable for PC camera applications. The MT9M114 features **onsemi**'s breakthrough low-noise CMOS imaging technology that achieves near–CCD image quality (based on signal–to–noise ratio and low–light sensitivity) while maintaining the inherent size, cost, and integration advantages of CMOS.

The MT9M114 can be operated in its default mode or programmed for frame size, exposure, gain, and other parameters. The default mode output is a 720p image size at 30 frames per second (fps), assuming a 24 MHz input clock. It outputs 8-bit data, using the parallel output port.

#### **ARCHITECTURE OVERVIEW**

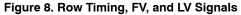

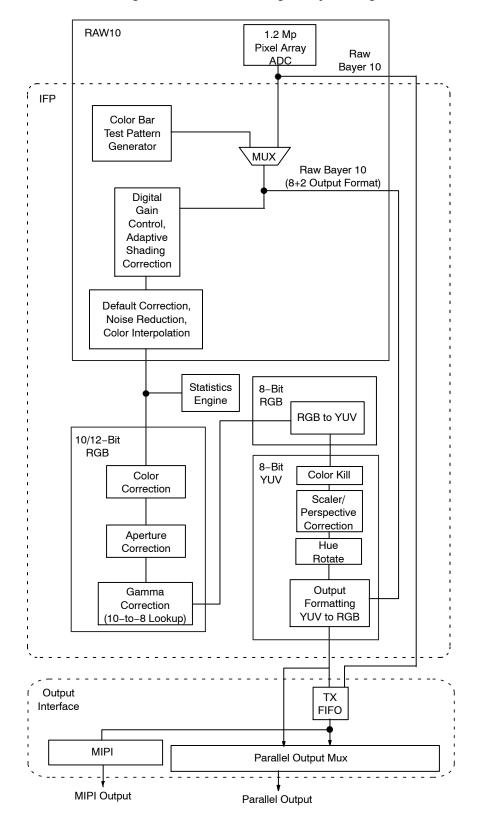

The MT9M114 combines a 1.26 Mp sensor core with an IFP to form a stand-alone solution for both image acquisition and processing. Both the sensor core and the IFP have internal registers that can be controlled by the user. In normal operation, an integrated microcontroller autonomously controls most aspects of operation. The processed image data is transmitted to the host system either through the parallel or MIPI interface. Figure 1 shows the major functional blocks of the MT9M114.

Figure 1. MT9M114 Block Diagram

#### Sensor Core

The MT9M114 has a color image sensor with a Bayer color filter arrangement and a 1.2 Mp active-pixel array

with electronic rolling shutter (ERS). The sensor core readout is 10 bits and can be flipped and/or mirrored. The

sensor core also supports separate analog and digital gain for all four color channels (R, Gr, Gb, B).

#### Image Flow Processor (IFP)

The advanced IFP features and flexible programmability of the MT9M114 can enhance and optimize the image sensor performance. Built–in optimization algorithms enable the MT9M114 to operate with factory settings as a fully automatic and highly adaptable system–on–a–chip (SOC) for most camera systems.

These algorithms include black level conditioning, shading correction, defect correction, color interpolation, edge detection, color correction, vertical perspective correction, aperture correction, and image formatting with cropping and scaling.

#### **Microcontroller Unit (MCU)**

The MCU communicates with all functional blocks by way of an internal **onsemi** proprietary bus interface. The MCU firmware configures all the registers in the sensor core and IFP.

#### System Control

The MT9M114 has a phase–locked loop (PLL) oscillator that can generate the internal sensor clock from a common wireless system clock. The PLL adjusts the incoming clock frequency up, allowing the MT9M114 to run at almost any desired resolution and frame rate within the sensor's capabilities. Low–power consumption is a very important requirement.

The MT9M114 provides power-conserving features including a soft standby mode. A two-wire serial interface

bus enables read and write access to the MT9M114's internal registers and variables. The internal registers control the sensor core, the color pipeline flow, and the output interface. Variables are located in the microcontroller's RAM memory and are used to configure and control the auto–algorithms and camera control functions.

### **Output Interface**

The output interface block can select either raw data or processed data. Image data is provided to the host system either by an 8-bit parallel port or by a serial MIPI port. The parallel output port provides 8-bit RGB data or extended 10-bit Bayer data.

The MT9M114 also includes programmable I/O slew rate to minimize EMI.

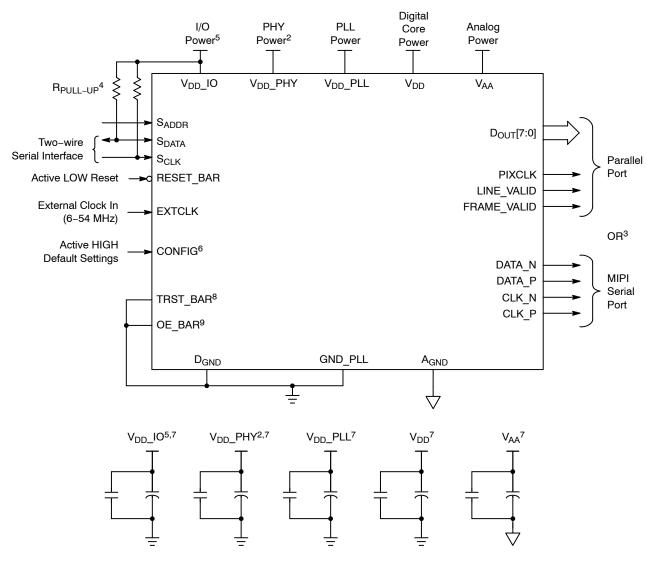

#### System Interfaces

Figure 2 shows typical MT9M114 device connections. For low–noise operation, the MT9M114 requires separate power supplies for analog and digital sections of the die. Both power supply rails must be decoupled from ground using capacitors as close as possible to the die. The use of inductance filters is not recommended on the power supplies or output signals.

The MT9M114 provides dedicated signals for digital core, PHY, and I/O power domains that can be at different voltages. The PLL and analog circuitry require clean power sources. Table 3 provides the signal descriptions for the MT9M114.

#### Notes:

- 1. This typical configuration shows only one scenario out of multiple possible variations for this sensor.

- 2. If a MIPI Interface is not required, the following signals must be left floating: DATA\_P, DATA\_N, CLK\_P, and CLK\_N. The V<sub>DD</sub>\_PHY power signal must always be connected to the 1.8 V supply.

- 3. Only one of the output modes (serial or parallel) can be used at any time.

- 4. **onsemi** recommends a 1.5 kΩ resistor value for the two–wire serial interface R<sub>PULL-UP</sub>; however, greater values may be used for slower transmission speed.

- 5. All inputs must be configured with  $V_{DD}$ IO.

- 6. RESET\_BAR and CONFIG both have internal pull-up resistors and can be left floating.

- 7. **onsemi** recommends that 0.1 μF and 1 μF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and numbers may vary depending on layout and design considerations.

- 8. TRST\_BAR connects to GND for normal operation.

- 9. OE\_BAR should be connected HIGH when using MIPI interface.

#### **Figure 2. Typical Configuration**

#### **Table 3. PIN DESCRIPTIONS**

| Name                         | Туре      | Description                                                                                                                                                                                   |  |

|------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EXTCLK                       | Input     | Input clock signal                                                                                                                                                                            |  |

| RESET_BAR                    | Input/PU  | Master reset signal, active LOW. This signal has an internal pull up                                                                                                                          |  |

| OE_BAR                       | Input     | Parallel interface enable pad, active LOW                                                                                                                                                     |  |

| S <sub>CLK</sub>             | Input     | Two-wire serial interface clock                                                                                                                                                               |  |

| S <sub>DATA</sub>            | I/O       | Two-wire serial interface data                                                                                                                                                                |  |

| S <sub>ADDR</sub>            | Input     | Selects device address for the two-wire serial interface                                                                                                                                      |  |

| FRAME_VALID (FV)             | Output    | Identifies rows in the active image. Data can be sampled with PIXCLK when both LV and FV are high (except when BT656 is used)                                                                 |  |

| LINE_VALID (LV)              | Output    | Identifies pixels in the active line. Data can be sampled with PIXCLK when both LV and FV are high (except when BT656 is used)                                                                |  |

| PIXCLK                       | Output    | Pixel clock                                                                                                                                                                                   |  |

| D <sub>OUT</sub> [7:0]       | Output    | D <sub>OUT</sub> [7:0] for 8-bit image data output or D <sub>OUT</sub> [9:2] for 10-bit image data output                                                                                     |  |

| D <sub>OUT</sub> _LSB[1:0]   | Output    | LSBs when outputting 10-bit image data                                                                                                                                                        |  |

| CLK_N (Note 4)               | Output    | Differential MIPI clock (sub-LVDS, negative)                                                                                                                                                  |  |

| CLK_P (Note 4)               | Output    | Differential MIPI clock (sub-LVDS, positive)                                                                                                                                                  |  |

| DATA_N (Note 4)              | Output    | Differential MIPI data (sub-LVDS, negative                                                                                                                                                    |  |

| DATA_P (Note 4)              | Output    | Differential MIPI data (sub-LVDS, positive)                                                                                                                                                   |  |

| CONFIG (Note 6)              | Input/PU  | If on power-up CONFIG = 1 then the part shall go into streaming (default option, PU ensures this will occur). If CONFIG = 0 then the part will go to standby state waiting for host to update |  |

| FLASH (Note 4)               | Output    | Used as a flash signal                                                                                                                                                                        |  |

| CHAIN (Note 4)               | Output/PU | To synchronize a number of sensors together                                                                                                                                                   |  |

| TRST_BAR                     | Input     | Must be tied to GND in normal operation                                                                                                                                                       |  |

| V <sub>DD</sub>              | Supply    | Digital power                                                                                                                                                                                 |  |

| D <sub>GND</sub> (Note 3)    | Supply    | Digital ground                                                                                                                                                                                |  |

| V <sub>DD</sub> _IO          | Supply    | I/O power supply                                                                                                                                                                              |  |

| GND_IO                       | Supply    | I/O ground                                                                                                                                                                                    |  |

| V <sub>AA</sub>              | Supply    | Analog power                                                                                                                                                                                  |  |

| A <sub>GND</sub> (Note 3)    | Supply    | Analog ground                                                                                                                                                                                 |  |

| V <sub>DD</sub> _PLL         | Supply    | PLL supply                                                                                                                                                                                    |  |

| GND_PLL                      | Supply    | PLL GND                                                                                                                                                                                       |  |

| V <sub>DD</sub> PHY (Note 5) | Supply    | I/O power supply for the MIPI interface                                                                                                                                                       |  |

A<sub>GND</sub> and D<sub>GND</sub> are not connected internally.

To be left floating if not using feature. If not using the feature, then there is no need to bond out the relevant pads.

Must always be connected even when not using MIPI.

When CONFIG = 1 the EXTCLK must be in the range 20–24 MHz.

## DECOUPLING CAPACITOR RECOMMENDATIONS

It is important to provide clean, well regulated power to each power supply. The **onsemi** recommendation for capacitor placement and values are based on our internal demo camera design and verified in hardware. Note: Because hardware design is influenced by many factors, such as layout, operating conditions, and component selection, the customer is ultimately responsible to ensure that clean power is provided for their own designs.

In order of preference, onsemi recommends:

- 1. Mount 0.1  $\mu$ F and 1  $\mu$ F decoupling capacitors for each power supply as close as possible to the pad and place a 10  $\mu$ F capacitor nearby off-module.

- 2. If module limitations allow for only six decoupling capacitors for a three–regulator design use a 0.1  $\mu$ F and 1  $\mu$ F capacitor for each of the three regulated supplies. **onsemi** also recommends placing a 10  $\mu$ F capacitor for each supply off–module, but close to each supply.

- 3. If module limitations allow for only three decoupling capacitors, use a 1  $\mu$ F capacitor (preferred) or a 0.1  $\mu$ F capacitor for each of the three regulated supplies. **onsemi** recommends placing a 10  $\mu$ F capacitor for each supply off-module but close to each supply.

- 4. Give priority to the V<sub>AA</sub> supply for additional decoupling capacitors.

- 5. Inductive filtering components are not recommended.

- 6. Follow best practices when performing physical layout. Refer to application note AND9503/D.

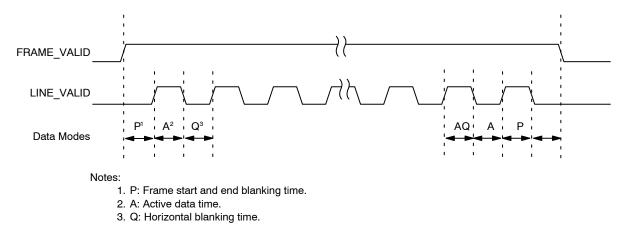

## **Output Data Format**

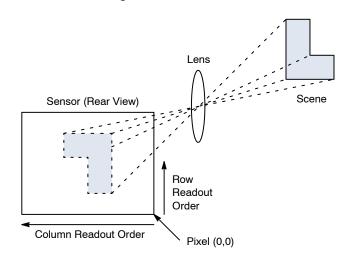

The MT9M114 image data is read out in a progressive scan. Valid image data is surrounded by horizontal blanking and vertical blanking, as shown in Figure 3.

LINE\_VALID is HIGH in the shaded region of the figure.

| P <sub>0,0</sub> P <sub>0,1</sub> P <sub>0,2</sub><br>P <sub>1,0</sub> P <sub>1,1</sub> P <sub>1,2</sub><br>:  | P <sub>0,n-1</sub> P <sub>0,n</sub><br>P <sub>1,n-1</sub> P <sub>1,n</sub>     | 00 00 00 00 00 00<br>00 00 00 00 00 00                                                                                                   |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Valid Image                                                                                                    |                                                                                | Horizontal Blanking                                                                                                                      |

| P <sub>m-1,0</sub> P <sub>m-1,1</sub> P <sub>m-1,2</sub><br>P <sub>m,0</sub> P <sub>m,1</sub> P <sub>m,2</sub> | P <sub>m-1,n-1</sub> P <sub>m-1,n</sub><br>P <sub>m,n-1</sub> P <sub>m,n</sub> | 00 00 00 00 00 00<br>00 00 00 00 00 00                                                                                                   |

| 00 00 00<br>00 00 00                                                                                           | 00 00 00<br>00 00 00                                                           | 00         00          00         00         00           00         00         00          00         00         00                     |

| E Vertical Blanking                                                                                            |                                                                                | Vertical/Horizontal<br>Blanking                                                                                                          |

| 00 00 00<br>00 00 00                                                                                           | 00 00 00<br>00 00 00                                                           | 00         00         00         00         00         00           00         00         00         00         00         00         00 |

Figure 3. Spatial Illustration of Image Readout

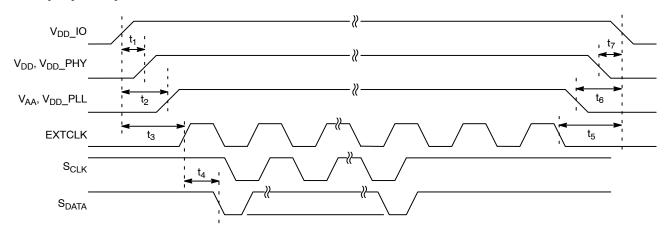

## POWER-UP AND POWER-DOWN SEQUENCE

Powering up and powering down the sensor requires voltages to be applied in a particular order, as seen in Figure 4. The timing requirements are shown in Table 4. The sensor includes a power-on reset feature that initiates a reset upon power up of the sensor

Figure 4. Power–Up and Power–Down Sequence

#### Table 4. POWER-UP AND DOWER-DOWN SIGNAL TIMING

| Symbol         | Parameter                                             | Min            | Тур  | Max | Unit |

|----------------|-------------------------------------------------------|----------------|------|-----|------|

| t <sub>1</sub> | Delay from $V_{DD}$ _IO to $V_{DD}$ and $V_{DD}$ _PHY | 0              | -    | 50  | ms   |

| t <sub>2</sub> | Delay from V_DD_IO to V_AA and V_DD_PLL               | 0              | _    | 50  | ms   |

| t <sub>3</sub> | EXTCLK Activation                                     | t <sub>2</sub> | -    | —   | ms   |

| t <sub>4</sub> | First Serial Command (Notes 7, 8)                     | -              | 44.5 | —   | ms   |

| t <sub>5</sub> | EXTCLK Cutoff                                         | t <sub>6</sub> | -    | —   | ms   |

| t <sub>6</sub> | Delay from $V_{AA}$ and $V_{DD}$ _PLL to $V_{DD}$ _IO | 0              | _    | 50  | ms   |

| t <sub>7</sub> | Delay from $V_{DD}$ and $V_{DD}$ _PHY to $V_{DD}$ _IO | 0              | _    | 50  | ms   |

7. Under the condition of EXTCLK = 24 MHz and default settings with CONFIG = 1.

8. The host should poll the Command register to determine when the device is initialized.

## Reset

The MT9M114 has 3 types of reset available:

- A hard reset is issued by toggling the RESET\_BAR signal;

- A soft reset is issued by writing commands through the two-wire serial interface;

- An internal power-on reset. The output states during hard reset are shown in Table 5.

## Table 5. STATUS OF OUTPUT SIGNALS DURING HARD RESET, SOFT STANDBY, AND POWER OFF

| Signal                     | Reset  | Soft Standby<br>(EXTCLK Running) | Soft Standby<br>(Without EXTCLK)                                          | Power Off |

|----------------------------|--------|----------------------------------|---------------------------------------------------------------------------|-----------|

| D <sub>OUT</sub> [7:0]     | High–Z | High–Z                           | High-Z                                                                    | High–Z    |

| PIXCLK                     | High–Z | High–Z                           | High–Z                                                                    | High–Z    |

| LV                         | High–Z | High–Z                           | High-Z                                                                    | High–Z    |

| FV                         | High–Z | High–Z                           | High-Z                                                                    | High–Z    |

| D <sub>OUT</sub> _LSB[1:0] | High–Z | High–Z                           | High-Z                                                                    | High–Z    |

| DATA_N                     | 0      | 0                                | 0                                                                         | High–Z    |

| DATA_P                     | 0      | 0                                | 0                                                                         | High–Z    |

| CLK_N                      | 0      | 0                                | 0                                                                         | High–Z    |

| CLK_P                      | 0      | 0                                | 0                                                                         | High–Z    |

| S <sub>CLK</sub>           | Input  | Active                           | Active (Pads are active, but due to no EXTCLK serial comms will not work) | High-Z    |

| S <sub>DATA</sub>          | Input  | Active                           | Active (Pads are active, but due to no EXTCLK serial comms will not work) | High-Z    |

A soft reset sequence to the sensor has the same effect as the hard reset and can be activated by writing to a register through the two-wire serial interface. On-chip power-on-reset circuitry can generate an internal reset signal in case an external reset is not provided. The RESET\_BAR and CONFIG signals have internal pull-up resistors and can be left floating.

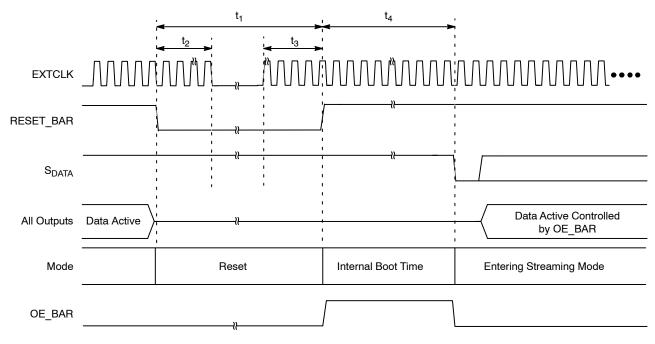

## Hard Reset

The MT9M114 enters the reset state when the external RESET\_BAR signal is asserted LOW, as shown in Figure 5. All the output signals will be in High–Z state. When OE\_BAR is in HIGH state, the outputs pins will be High–Z during the internal boot time

#### Figure 5. Hard Reset Operation

#### Table 6. POWER-UP AND DOWER-DOWN SIGNAL TIMING

| Symbol         | Parameter                                           | Min | Тур  | Max | Unit   |

|----------------|-----------------------------------------------------|-----|------|-----|--------|

| t <sub>1</sub> | RESET_BAR Pulse Width                               | 50  | -    | -   | EXTCLK |

| t <sub>2</sub> | Active EXTCLK Required after RESET_BAR Asserted     | 10  | -    | -   | cycles |

| t <sub>3</sub> | Active EXTCLK Required before RESET_BAR De-asserted | 10  | -    | -   |        |

| t <sub>4</sub> | Internal Boot Time (Notes 9, 10)                    | =   | 44.5 | =   | ms     |

9. Under the condition of EXTCLK = 24 MHz and default settings with CONFIG = 1.

10. The host should poll the Command register to determine when the device is initialized.

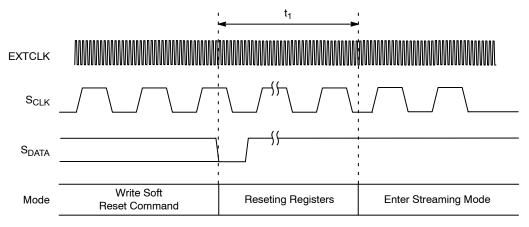

## Soft Reset

The host processor can reset the MT9M114 using the two-wire serial interface by writing to SYSCTL 0x001A. SYSCTL 0x001A[0] is used to reset the MT9M114 which is similar to external RESET BAR signal.

- 1. Set SYSCTL 0x001A[0] to 0x1 to initiate internal reset cycle.

- 2. Reset SYSCTL 0x001A[0] to 0x0 for normal operation.

- 3. Delay of 44.5 ms.

## Figure 6. Soft Reset Operation

#### Table 7. SOFT RESET SIGNAL TIMING

| Symbol         | Parameter                      | Min | Тур  | Мах | Unit |

|----------------|--------------------------------|-----|------|-----|------|

| t <sub>1</sub> | Soft Reset Time (Notes 11, 12) | -   | 44.5 | -   | ms   |

11. Under the condition of EXTCLK = 24 MHz and default settings with CONFIG = 1.

12. The host should poll the Command register to determine when the device is initialized.

#### Soft Standby Mode

The MT9M114 can enter soft standby mode by receiving a host command through the two-wire serial interface. EXTCLK can be stopped to reduce the power consumption during soft standby mode. However, since two-wire serial interface requires EXTCLK to operate, **onsemi** recommends that EXTCLK run continuously.

#### Entering Standby Mode

- 1. Send the sequence [Enter Standby] to put the MT9M114 into standby.

- 2. After the part is in standby for 100 EXTCLK cycles the EXTCLK can be turned off.

#### [Enter Standby]

FIELD\_WR=SYSMGR\_NEXT\_STATE, 0x50

//(Optional) First check that the FW is ready to accept a new command ERROR\_IF=COMMAND\_REGISTER, HOST\_COMMAND\_1, !=0, "Set State cmd bit is already set"

//(Mandatory) Issue the Set State command

//We set the 'OK' bit so we can detect if the command fails

//Note 0x8002 is equivalent to (HOST\_COMMAND\_OK | HOST\_COMMAND\_1)

FIELD\_WR=COMMAND\_REGISTER, 0x8002

//Wait for the FW to complete the command (clear the HOST\_COMMAND\_1 bit)

POLL\_FIELD=COMMAND\_REGISTER, HOST\_COMMAND\_1, !=0, DELAY=10, TIMEOUT=100

//Check the 'OK' bit to see if the command was successful

ERROR\_IF=COMMAND\_REGISTER, HOST\_COMMAND\_OK, !=1, "Set State cmd failed",

//Wait for the FW to fully-enter standby (SYSMGR\_CURRENT\_STATE=0x52)

POLL\_FIELD=SYSMGR\_CURRENT\_STATE,!=0x52,DELAY=50,TIMEOUT=10

#### Exiting Standby Mode

1. Turn EXTCLK on.

2. After 100 EXTCLK cycles send the following sequence entitled [Exit Standby] to bring the MT9M114 out of standby.

#### [Exit Standby]

FIELD\_WR=SYSMGR\_NEXT\_STATE, 0x54

//(Optional) First check that the FW is ready to accept a new command ERROR\_IF=COMMAND\_REGISTER, HOST\_COMMAND\_1, !=0, "Set State cmd bit is already set"

//(Mandatory) Issue the Set State command //We set the 'OK' bit so we can detect if the command fails //Note 0x8002 is equivalent to (HOST\_COMMAND\_OK | HOST\_COMMAND\_1) FIELD\_WR=COMMAND\_REGISTER, 0x8002

//Wait for the FW to complete the command (clear the HOST\_COMMAND\_1 bit)

POLL\_FIELD=COMMAND\_REGISTER, HOST\_COMMAND\_1, !=0, DELAY=10, TIMEOUT=100

//Check the 'OK' bit to see if the command was successful ERROR\_IF=COMMAND\_REGISTER, HOST\_COMMAND\_OK, !=1, "Set State cmd failed", ERROR IF=SYSMGR CURRENT STATE, !=0x31, "System state is not STREAMING"

#### **IMAGE DATA OUTPUT INTERFACE**

The user can select either the 8-bit parallel or serial MIPI output to transmit the sensor image data to host system. Only one of the output modes can be used at any time. The MT9M114 has an output FIFO to retain a constant pixel output clock independent from the data output rate variations due to scaling factor.

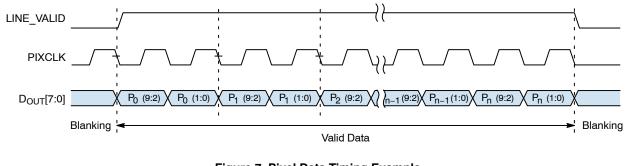

## Parallel Port

The MT9M114 image data is read out in a progressive scan mode. Valid image data is surrounded by horizontal

blanking and vertical blanking. The amount of horizontal blanking and vertical blanking are programmable.

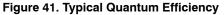

MT9M114 output data is synchronized with the PIXCLK output. When LV is HIGH, one pixel value is output on the 8-bit D<sub>OUT</sub> port every TWO PIXCLK periods as shown in Figure 7. PIXCLK is continuously running, even during the blanking period. (If the user wishes to have PIXCLK turned off during blanking this is possible through a variable setting) PIXCLK phase can be varied by 50 percent, controlled using a register.

Figure 7. Pixel Data Timing Example

#### Serial Port

This section describes how frames of pixel data are represented on the high-speed MIPI serial interface. The MIPI output transmitter implements a serial differential sub-LVDS transmitter capable of up to 768 Mb/s. It supports multiple formats, error checking, and custom short packets. MT9M114 is designed to MIPI D-PHY version v1.0.

When the sensor is in the software standby system state, the MIPI signals (CLK\_P, CLK\_N, DATA\_P, DATA\_N) indicate ultra low-power state (ULPS) corresponding to (nominal) 0 V levels being driven on CLK\_P, CLK\_N, DATA\_P, and DATA\_N. This is equivalent to signaling code LP-00. When the sensor enters the streaming system state, the interface goes through the following transitions:

- 1. After the PLL has locked and the bias generator for the MIPI drivers has stabilized, the MIPI interface transitions from the ULPS state to the ULPS-exit state (signaling code LP-10).

- 2. After a delay (TWAKEUP), the MIPI interface transitions from the ULPS-exit state to the TX-stop state (signaling code LP-11).

- 3. After a short period of time (the programmed integration time plus a fixed overhead), frames of pixel data start to be transmitted on the MIPI interface. Each frame of pixel data is transmitted as a number of high-speed packets. The transition from the TX-stop state to the high-speed signaling states occurs in accordance with the MIPI specifications. Between high-speed packets and

between frames, the MIPI interface idles in the TX-stop state. The transition from the high-speed signaling states and the TX-stop state takes place in accordance with the MIPI specifications.

- 4. If the sensor is reset, any frame in progress is aborted immediately and the MIPI signals switch to indicate the ULPS.

- 5. If the sensor is taken out of the streaming system state and reset\_register[4] = 1 (standby end-of-frame), any frame in progress is completed and the MIPI signals switch to indicate the ULPS.

If the sensor is taken out of the streaming system state and reset\_register[4] = 0 (standby end-of-frame), any frame in progress is aborted as follows:

- 1. Any long packet in transmission is completed.

- 2. The end of frame short packet is transmitted.

After the frame has been aborted, the MIPI signals switch to indicate the ULPS.

#### Sensor Control

The sensor core of the MT9M114 is a progressive–scan sensor that generates a stream of pixel data at a constant frame rate. Figure 9 shows a block diagram of the sensor core. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in the row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. Once a row has been selected, the data from each column is sequenced through an analog signal chain, including offset correction, gain adjustment, and ADC. The final stage of sensor core converts the output of the ADC into 10-bit data for each pixel in the array.

The pixel array contains optically active and light-shielded (dark) pixels. The dark pixels are used to provide data for the offset-correction algorithms (black level control).

The sensor core contains a set of control and status registers that can be used to control many aspects of the sensor behavior including the frame size, exposure, and gain setting. These registers are controlled by the MCU firmware and are also accessible by the host processor through the two-wire serial interface.

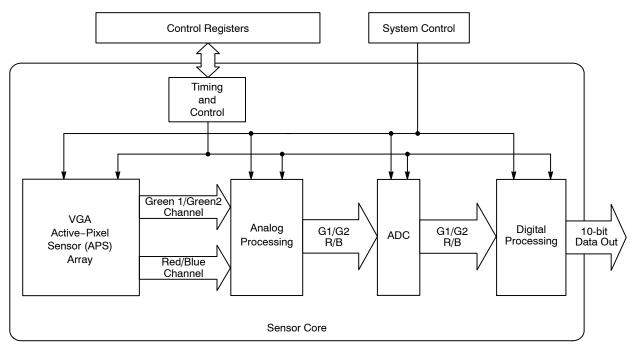

The output from the sensor core is a Bayer pattern; alternate rows are a sequence of either green and red pixels or blue and green pixels. The offset and gain stages of the analog signal chain provide per-color control of the pixel data.

Figure 9. Sensor Core Block Diagram

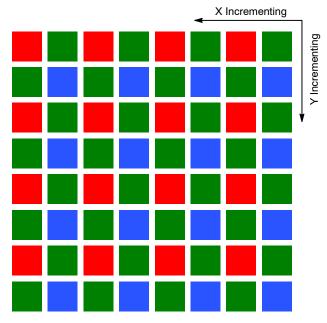

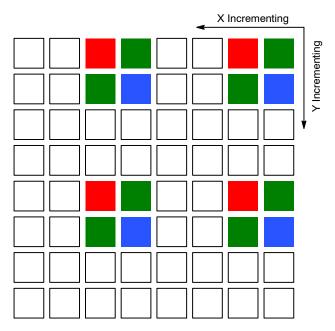

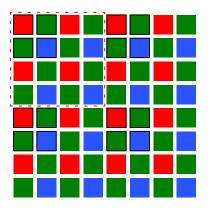

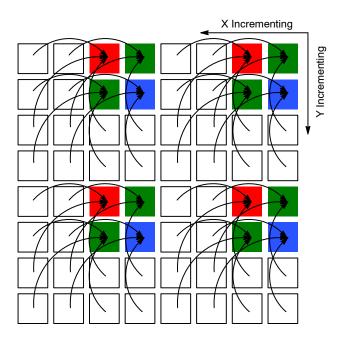

The sensor core uses a Bayer color pattern, as shown in Figure 10. The even–numbered rows contain green and red pixels; odd–numbered rows contain blue and green pixels.

Even–numbered columns contain green and blue pixels; odd–numbered columns contain red and green pixels.

Figure 10. Pixel Color Pattern Detail (Bottom Left Corner)

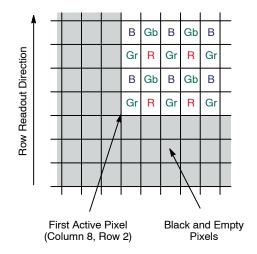

For the MT9M114 the first active pixel is defined as the first pixel that would be used as part of the demosaic border. When the sensor is operating in a system, the active

surface of the sensor faces the scene as shown in Figure 11.

When the image is read out of the sensor, it is read one row at a time, with the rows and columns sequenced.

Figure 11. Imaging a Scene

The sensor core supports different readout options to modify the image before it is sent to the IFP. The readout can be limited to a specific window size of the original pixel array.

By changing the readout directions, the image can be flipped in the vertical direction and/or mirrored in the horizontal direction.

The image output size is set by programming row and column start and end address variables.

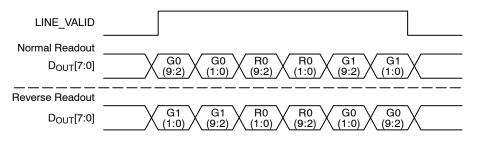

When the sensor is configured to mirror the image horizontally, the order of pixel readout within a row is reversed, so that readout starts from the last column address and ends at the first column address. Figure 12 shows a sequence of three pixels being read out with normal readout and reverse readout. This change in sensor core output is corrected by the IFP.

Figure 12. Three Pixels in Normal and Column Mirror Readout Mode

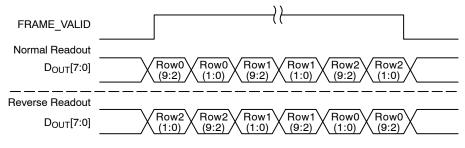

When the sensor is configured to flip the image vertically, the order in which pixel rows are read out is reversed, so that row readout starts from the last row address and ends at the first row address. Figure 13 shows a sequence of 3 rows being read out with normal readout and reverse readout. This change in sensor core output is corrected by the IFP.

Figure 13. Three Rows in Normal and Row Mirror Readout Mode

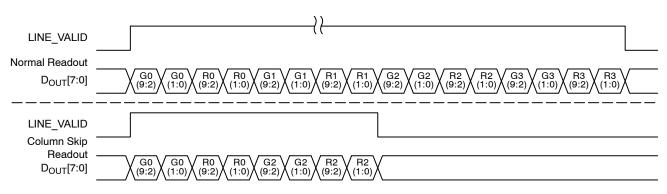

The MT9M114 sensor core supports subsampling with skipping to increase the frame rate. The proper image output size and cropped size must be programmed before enabling subsampling mode. Figure 14 shows the readout with 2X skipping.

Figure 14. Eight Pixels in Normal and Column Skip 2X Readout Modes

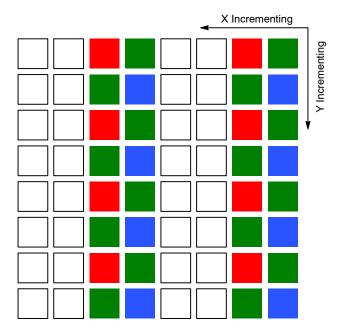

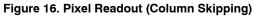

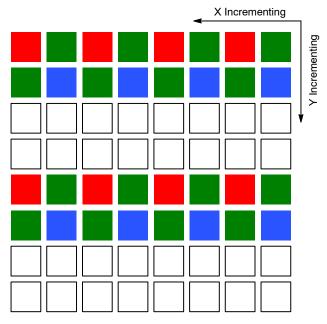

## **Pixel Readouts**

The following diagrams show a sequence of data being read out with no skipping. The effect of the different

subsampling on the pixel array readout is shown in Figure 15 through Figure 20.

Figure 15. Pixel Readout (No Skipping)

Figure 17. Pixel Readout (Row Skipping)

Figure 18. Pixel Readout (Column and Row Skipping)

## Binning and Summing

The MT9M114 sensor core supports binning and summing. Binning has many of the same characteristics as subsampling but it gathers image data from all pixels in the active window (rather than a subset of them).

Pixel binning will sample pixels and average the value together in the analog domain. Summing will add the charge

2 x 2 Binning and Summing

Figure 19. Pixel Binning and Summing

Figure 20. Pixel Readout (Column and Row Binning)

or voltage values of the neighboring pixels together. ( $\Sigma e$  means "charge summing",  $\Sigma v$  means "voltage summing", and *avg* means "digital averaging (post ADC). The advantage of using summing is that the pixel data is added together and up to 4X increase in responsivity is achieved.

#### IMAGE FLOW PROCESSOR

Image control processing in the MT9M114 is implemented in the IFP hardware logic. For normal

operation, the microcontroller automatically adjusts the operational parameters of the IFP. Figure 21 shows the image data processing flow within the IFP.

Figure 21. Image Flow Processor

For normal operation of the MT9M114, streams of raw image data from the sensor core are continuously fed into the color pipeline. The MT9M114 features an automatic color bar test pattern generation function to emulate sensor images as shown in Table 8. The color bar test pattern is fed to the IFP for testing the image pipeline without sensor operation.

| Color bar test pattern generation can be selected by     |  |  |  |

|----------------------------------------------------------|--|--|--|

| programming variables. To select enter test pattern mode |  |  |  |

| R0xC84C = 0x02; to exit this mode $R0xC84C$ must be set  |  |  |  |

| to 0x00.                                                 |  |  |  |

A Change–Config command needs to be issued when switching to CAM mode to enable test pattern as well as when exiting.

| Test Pattern        | Registers/Variables                                                                                                                                                                             | Example |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Flat Field          | R0xC84C = 0x02 $R0xC84D = 0x01$ $R0xC84E = 0x01FF$ $R0xC850 = 0x01FF$ $R0xC852 = 0x01FF$ $Load = Change-Config$ $Changing the values in 0x4E-0x52 will$ $change the color of the test pattern.$ |         |

| 100% Color Bar      | R0xC84C = 0x02<br>R0xC84D = 0x04<br>Load = Change-Config                                                                                                                                        |         |

| Pseudo-Random       | R0xC84C = 0x02<br>R0xC84D = 0x05<br>Load = Change-Config                                                                                                                                        |         |

| Fade-to-Gray        | R0xC84C = 0x02<br>R0xC84D = 0x08<br>Load = Change-Config                                                                                                                                        |         |

| Walking Ones 10-bit | R0xC84C = 0x02<br>R0xC84D = 0x0A<br>Load = Change-Config                                                                                                                                        |         |

| Walking Ones 8-bit  | R0xC84C = 0x02<br>R0xC84D = 0x0B<br>Load = Change-Config                                                                                                                                        |         |

#### Table 8. COLOR BAR TEST PATTERN

#### **Digital Gain**

Image stream processing starts with multiplication of all pixel values by a programmable digital gain. Independent color channel digital gain can be adjusted with registers.

#### Adaptive PGA (APGA)

Lenses tend to produce images whose brightness is significantly attenuated near the edges. There are also other factors causing fixed pattern signal gradients in images captured by image sensors. The cumulative result of all these factors is known as image shading. The MT9M114 has an embedded shading correction module that can be programmed to counter the shading effects on each individual R, Gb, Gr, and B color signal.

In some cases, different illuminants can introduce different color shading response. The APGA feature on the MT9M114 will compensate for the dependency of the lens shading of the illuminant. The MT9M114 will allow for up to three different illuminants to be compensated.

#### Color Interpolation and Edge Detection

In the raw data stream fed by the sensor core to the IFP, each pixel is represented by a 10-bit integer, which can be considered proportional to the pixel's response to a one-color light stimulus, red, green, or blue, depending on the pixel's position under the color filter array. Initial data processing steps, up to and including the defect correction, preserve the one-color-per-pixel nature of the data stream, but after the defect correction it must be converted to a three-colors-per-pixel stream appropriate for standard color processing. The conversion is done by an edge-sensitive color interpolation module. The module adds the incomplete color information available for each pixel with information extracted from an appropriate set of neighboring pixels. The algorithm used to select this set and extract the information seeks the best compromise between preserving edges and filtering out high-frequency noise in flat field areas. The edge threshold can be set through variable settings.

#### Color Correction and Aperture Correction

To achieve good color fidelity of the IFP output, interpolated RGB values of all pixels are subjected to color correction. The IFP multiplies each vector of three pixel colors by a  $3 \times 3$  color correction matrix. The three components of the resulting color vector are all sums of three 10-bit numbers. Since such sums can have up to 12 significant bits, the bit width of the image data stream is widened to 12 bits per color (36 bits per pixel). The color correction matrix can either be programmed by the user or automatically selected by the AWB algorithm implemented in the IFP. Traditionally this would have been based off two sets of CCM, one for Warm light like Tungsten and the other for Daylight (the part would interpolate between the two matrixes). This is not an optimal solution for cameras used in a Cool White Fluorescent (CWF) environment, for example when using a webcam. A better solution is to provide three CCMs, which would include a matrix for CWF (interpolation now between three matrixes). The MT9M114 offers this feature which will give the user improved color fidelity when under CWF type lighting.

Color correction should ideally produce output colors that are independent of the spectral sensitivity and color crosstalk characteristics of the image sensor. The optimal values of the color correction matrix elements depend on those sensor characteristics and on the spectrum of light incident on the sensor. The color correction settings can be adjusted using variables.

To increase image sharpness, a programmable 2D aperture correction (sharpening filter) is applied. The gain and threshold for 2D correction can be defined through variable settings.

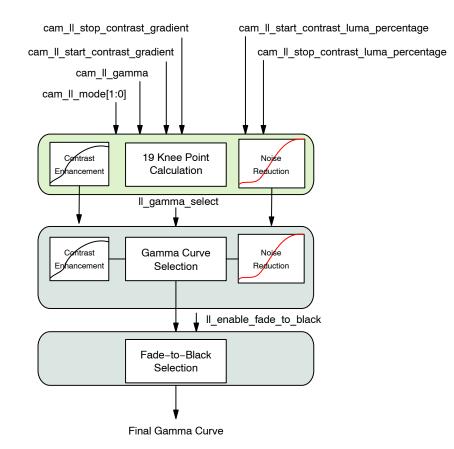

#### Gamma Correction

The gamma correction curve (as shown in Figure 22) is implemented as a piecewise linear function with 19 knee points, taking 12-bit arguments and mapping them to 8-bit output. The abscissas of the knee points are fixed at 0, 64, 128, 256, 512, 768, 1024, 1280, 1536, 1792, 2048, 2304, 2560, 2816, 3072, 3328, 3584, 3840, and 4096. The 8-bit ordinates are programmable through variables.

The MT9M114 IFP includes a block for gamma correction that has the capability to adjust its shape, based on brightness, to enhance the performance under certain lighting conditions.

Two custom gamma correction tables may be uploaded, one corresponding to a contrast curve for brighter lighting conditions, the other one corresponding to a noise reduction curve for lower lighting conditions. Also included in this block is a Fade–to–Black curve which sets all knee points to zero and causes the image to go black in extreme low light conditions.

The MT9M114 has the ability to calculate the 19 point knee points based on a small number of variable inputs from the host, another option is for the host to program one or both of the 19 knee points. The diagram below shows how the gamma feature interacts in MT9M114.

#### Figure 22. Gamma Interaction

#### **Gamma Knee Point Calculation**

The MT9M114 allows for the 19 knee point curves to be programmed based off a small number of variables. The table below shows the variables which are required.

#### Table 9. VARIABLES REQUIRED FOR GAMMA KNEE POINT CALCULATION

| Variable                         | Name                                  | Function                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAR(0x12,0x0124)<br>or (R0xC924) | cam_II_IImode                         | <ul> <li>0x00: User will program 19 knee point gamma curves</li> <li>0x01: MT9M114 will calculate 19 knee point for contrast curve (first curve or table)</li> <li>0x02: MT9M114 will calculate 19 knee point for noise reduction curve (second curve or table)</li> <li>0x03: MT9M114 will calculate both 19 knee point curves.</li> </ul> |

| VAR(0x12,0x013C)<br>or (R0xC93C) | cam_II_start_contrast_bm              | Interpolation start point for first curve                                                                                                                                                                                                                                                                                                   |

| VAR(0x12,0x013E)<br>or (R0xC93E) | cam_II_stop_contrast_bm               | Interpolation stop point for second curve                                                                                                                                                                                                                                                                                                   |

| VAR(0x12,0x0140)<br>or (R0xC940) | cam_II_gamma                          | The value of the gamma curve, this is applied to both 19 knee point curves. The default is 220, this equates to a gamma of 2.2                                                                                                                                                                                                              |

| VAR(0x12,0x0142)<br>or (R0xC942) | cam_II_start_contrast_gradient        | The value of the contrast gradient which would be used for the first curve                                                                                                                                                                                                                                                                  |

| VAR(0x12,0x0143)<br>or (R0xC943) | cam_II_stop_contrast_gradient         | The value of the contrast gradient which would be used for the second curve                                                                                                                                                                                                                                                                 |

| VAR(0x12,0x0144)<br>or (R0xC944) | cam_ll_start_contrast_luma_percentage | The percentage of target luma for the inflexion point in the first curve                                                                                                                                                                                                                                                                    |

| VAR(0x12,0x0145)<br>or (R0xC945) | cam_ll_start_contrast_luma_percentage | The percentage of target luma for the inflexion point second curve                                                                                                                                                                                                                                                                          |

| VAR(0x12,0x0156)<br>or (R0xC956) | cam_ll_inv_brightness_metric          | Measure of scene brightness, reference points for<br>cam_II_start_contrast_bm and cam_II_stop_contrast_bm                                                                                                                                                                                                                                   |

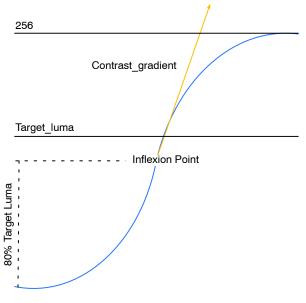

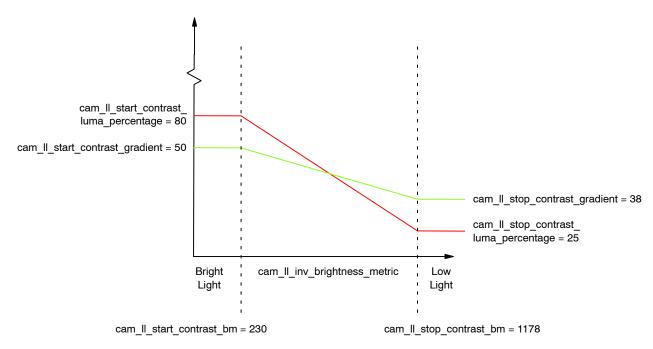

The concept of how the variables cam\_ll\_XX\_contrast\_ gradient and cam\_ll\_XX\_contrast\_luma\_percentage interact to produce a curve is shown below.

Figure 23. Automatic Gamma Curve

Figure 24 shows the interaction of the variables and cam\_ll\_inv\_brightness\_metric.

Figure 24. Gamma Reference Variables against Brightness Metric

**onsemi** would recommend that cam\_ll\_start\_ contrast\_bm is set at 100 lux and cam\_ll\_stop\_contrast\_bm is set at 20 lux, but due to the flexibility of the MT9M114 it is at the discretion of the user. **onsemi** recommends setting cam\_ll\_mode = 0x03 as this will allow the MT9M114 to calculate both of the 19 knee point curves based on the user inputs, otherwise the user will have to program both of the 19-knee-point curves.

#### Gamma Curve Selection

The MT9M114 allows the user to select between the two-curve interpolation or either of the curves

#### Table 10. GAMMA CURVE SELECTION

| Variable                         | Name            | Function                                                                                                                                                                                                           |

|----------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAR(0x0F,0x0007)<br>or (R0xBC07) | ll_gamma_select | 0x00: Auto curve select. The curves will interpolate based on settings of<br>cam_II_start_contrast_bm and cam_II_stop_contrast_bm<br>0x01: Contrast curve is only used<br>0x02: Noise reduction curve is only used |

#### Fade to Black Selection

The final stage of the gamma flow is the enabling and use of Fade-to-Black. The MT9M114 IFP allows for the image to fade to black under extreme low-light conditions. This feature enables users to optimize the performance of the sensor under low-light conditions. It minimizes the perception of noise and artifacts while the available illumination is diminishing. This feature has two user-set points that reference the brightness of the scene. When the Fade-to-Black starts, it will interpolate to the end point as the light falls until it gets to the end point. When at the end point, the image will be black.

| Variable                                                        | Name                            | Function                                                                                                                |

|-----------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| VAR(0x0F,0x0007) II_mode<br>or (R0xBC07)                        |                                 | When bit $3 = 1$ , this will enable the Fade-to-Black feature                                                           |

| VAR(0x12,0x014A)<br>or (R0xC94A)                                | cam_ll_start_fade_to_black_luma | Starting point for Fade-to-Black to begin                                                                               |

| VAR(0x12,0x014C)<br>or (R0xC94C) cam_II_stop_fade_to_black_luma |                                 | End point for Fade-to-Black, after this point the image will be black                                                   |

| VAR(0x0F,0x003A)<br>or (R0xBC3A)                                | II_average_luma_fade_to_black   | Measure of scene brightness, reference points for<br>cam_II_start_fade_to_black_luma and cam_II_stop_fade_to_black_luma |

**onsemi** would recommend that cam\_ll\_start\_fade\_to\_black\_luma is set at 3 lux and cam\_ll\_stop\_fade\_to\_black\_luma is set at 1 lux, but due to the flexibility of the MT9M114 it is at the discretion of the user.

#### Image Scaling and Cropping

To ensure that the size of images output by the MT9M114 can be tailored to the needs of all users, the IFP includes a scaler module. When enabled, this module performs rescaling of incoming images – shrinks them to the selected width (the output widths should be in multiples of 4) and height without reducing the field of view and without discarding any pixel values.

## be achieved. The location of the cropped window is configurable so that panning is also supported. The height and width definitions for the output window must be equal to or smaller than the cropped image. The image cropping and scaler module can be used together to implement a digital zoom and pan. *Hue Rotate*

By configuring the cropped and output windows to

various sizes, different zooming levels for 4×, 2×, and 1× can

The MT9M114 has integrated hue rotate. This feature will help for improving the color image quality and give customers the flexibility for fine color adjustment and special color effects.

## Table 12. HUE CONTROL

| Variable                     | Name      | Function                                                                                                       |

|------------------------------|-----------|----------------------------------------------------------------------------------------------------------------|

| VAR(0x12,0x73)<br>or R0xC873 | Hue Angle | Adjusts the global hue angle adjustment:<br>$0xEA = -22^{\circ}$<br>$0x00 = 0^{\circ}$<br>$0x16 = +22^{\circ}$ |

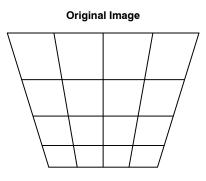

## Vertical Perspective Correction

The MT9M114 has vertical perspective correction (VPC) also known as the Tilt Connection; this allows the user to correct (within limits) for an off-horizontal axis camera.

**VPC Corrected Image**

#### Figure 25. Vertical Perspective Correction

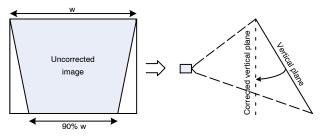

VPC is performed using a mixture of scale and crop, the variables that control this are:

#### Table 13. VERTICAL PERSPECTIVE CORRECTION

| Variable                         | Name                                 | Function                                                                                                                                                                                                                                             |

|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAR(0x12,0x005E)<br>or (R0xC85E) | cam_scale_vertical_tc_mode           | When set, the vertical stretching factor is applied to the center of the image, so top/bottom lines are cropped. When clear, the crop occurs in the top or bottom of the scene dependent on the percentage value (cam_scale_vertical_tc_percentage). |

| VAR(0x12,0x0060)<br>or (R0xC860) | cam_scale_vertical_tc_percentage     | The amount of tilt (perspective) correction to be applied. If negative, this value represents % of FOV reduction with the bottom line unaffected. If positive, this value represents % of FOV reduction with the top line unaffected.                |

| VAR(0x12,0x0062)<br>or (R0xC862) | cam_scale_vertical_tc_stretch_factor | Ratio of vertical stretching against the percentage applied. Vertical stretching = stretch factor $\times$ percentage/2.                                                                                                                             |

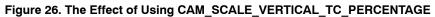

The effect of using cam\_scale\_vertical\_tc\_percentage can be seen below.

Uncorrected image

#### Case1: CAM\_SCALE\_VERTICAL\_TC\_PERCENTAGE = 10%

Vertical plane is tilted–away from the camera – therefore the bottom row of image represents the nearest point. The nearest point appears bigger in the uncorrected image, therefore top/bottom ratio will be greater than 1.0.

#### Case2: CAM\_SCALE\_VERTICAL\_TC\_PERCENTAGE = -10%

Vertical plane is tilted-towards the camera – therefore the top row of image represents the nearest point. The nearest point appears bigger in the uncorrected image, therefore the top/bottom ratio with be less than 1.0

Cam\_scale\_vertical\_tc\_percentage defines how much tilt needs to be corrected for in percentage terms.

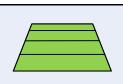

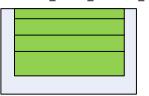

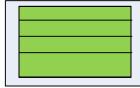

The effect of using cam\_scale\_vertical\_tc\_mode can be seen below.

**Original Scene Tilted**

MODE STRETCH FROM CENTRE EN = 0

MODE\_STRETCH\_FROM\_CENTRE\_EN = 1

Figure 27. The Effect of Using CAM SCALE VERTICAL TC MODE

#### **CAMERA CONTROL AND AUTO FUNCTIONS**

#### Auto Exposure

The auto exposure algorithm performs automatic adjustments of the image brightness by controlling exposure time and analog gains of the sensor core as well as digital gains applied to the image.

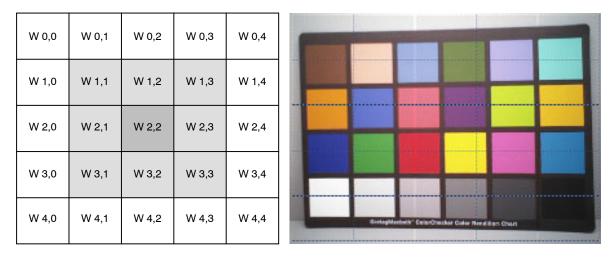

Auto exposure is implemented by a firmware driver that analyzes image statistics collected by the exposure measurement engine, makes a decision, and programs the sensor core and color pipeline to achieve the desired exposure. The measurement engine subdivides the image into 25 windows organized as a  $5 \times 5$  grid.

Four auto exposure algorithm modes are available:

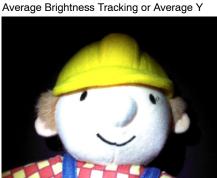

• Average brightness tracking (ABT) or Average Y (ae\_rule\_algo VAR = 9, 0x0004, 0x0000 or

#### REG = 0xA404, 0x0000)

The average brightness tracking AE uses a constant average tracking algorithm where a target brightness value is compared to a current brightness value, and the gain and integration time are adjusted accordingly to meet the target requirement.

• Weighted Average Brightness (ae\_rule\_algo VAR = 9, 0x0004, 0x0001 or REG = 0xA404, 0x0001) Each of the 25 windows can be assigned a weight relative to other window weights, which can be changed independently of each other. For example, the weights can be set to allow the center of the image to be weighted higher than the periphery. See Figure 28.

Figure 28. 5 × 5 Grid

- Adaptive Weighted AE for highlights (ae\_rule\_algo VAR = 9, 0x0004, 0x0002 or REG = 0xA404, 0x0002) The scene will be exposed based on the brightness of each window, and will adapt to correctly expose the highlights (brighter windows). This would correctly expose the foreground of an image when the background is dark.

- Adaptive Weighted AE for lowlights (ae\_rule\_algo VAR = 9, 0x0004, 0x0003 or REG = 0xA404, 0x0003) The scene will be exposed based on the brightness of each window, and will adapt to correctly expose the lowlights. This would correctly expose the foreground of an image when the background is brighter.

Sample images below show the benefits of the different AE modes.

Weighted Average Brightness (Centre)

Average Brightness Tracking or Average Y

Average Weighted Based on Zone Luma (Highlights)

Adaptive Weighted Based on Zone Luma (Lowlights)

NOTE: This mode is intended to expose the background vs. the

#### Figure 29. Light Background

In the use case above the Adaptive weighted for lowlights exposes the face slightly better when compared to the Weighted Average Brightness. However, if the foreground subject is moved off-center:

Figure 30.

This shows the advantage of using the Adaptive Weighted AE for lowlights (ae\_rule\_algo = 0x03); when the face moves off center it still is exposed correctly.

Average Weighted Based on Zone Luma (Highlights)

Adaptive Weighted Based on Zone Luma (Lowlights)

NOTE: This mode is correctly exposing the background of the image, hence you can see the shadows.

#### Figure 31. Dark Background

In this use case the Adaptive Weighted AE for highlights will expose the face the best when compared to the other options.

#### **AE Track Driver**

Other algorithm features include the rejection of fast fluctuations in illumination (time averaging), control of speed of response, and control of the sensitivity to the small changes. While the default settings are adequate in most situations, the user can program target brightness, measurement window, and other parameters described above.

The driver changes AE parameters (integration time, gains, and so on) to drive scene brightness to the programmable target.

To avoid unwanted reaction of AE on small fluctuations of scene brightness or momentary scene changes, the AE track driver uses a temporal filter for luma and a threshold around the AE luma target. The driver changes AE parameters only if the filtered luma is larger than the AE target step and pushes the luma beyond the threshold.

#### Auto White Balance

The MT9M114 has a built–in AWB algorithm designed to compensate for the effects of changing spectra of the scene illumination on the quality of the color rendition. The algorithm consists of two major parts: a measurement engine performing statistical analysis of the image and a driver performing the selection of the optimal color correction matrix and SOC digital gain. While default settings of these algorithms are adequate in most situations, the user can reprogram base color correction matrices, place limits on color channel gains, and control the speed of both matrix and gain adjustments. The MT9M114 AWB displays the current AWB position in color temperature, the range of which will be defined when programming the CCM matrixes.

#### Flicker Avoidance

Flicker occurs when the integration time is not an integer multiple of the period of the light intensity. The MT9M114 can be programmed to avoid flicker for 50 or 60 Hz. For integration times below the light intensity period (10 ms for 50 Hz environment), flicker cannot be avoided. The MT9M114 supports an indoor AE mode, that will ensure flicker-free operation (VAR8 = 18, 0x0078[0] = 0x1 or REG = 0xC878[0] = 0x1). The MT9M114 will calculate all flicker parameters based on the sensor settings which are programmed in the Cam Control variables. This means the user only needs to select if 50- or 60-Hz flicker needs to be avoided (VAR 0x12, 0x008B or R0xC88B = 50 for 50-Hz flicker avoidance and 60 for 60-Hz avoidance).

#### **Output Conversion and Formatting**

The YUV data stream can either exit the color pipeline as is or be converted before exit to an alternative YUV or RGB data format.

#### Color Conversion Formulas

#### Y'U'V':

This conversion is BT 601 scaled to make YUV range from 0 through 255. This setting is recommended for JPEG encoding and is the most popular, although it is not well defined and often misused in various operating systems.

$\begin{array}{ll} Y' \,=\, 0.299 \,\times\, R' \,+\, 0.587 \,\times\, G' \,+\, 0.114 \,\times\, B' & (eq. \, 1) \\ \\ U' \,=\, 0.564 \,\times\, (B' \,-\, Y') \,+\, 128 & (eq. \, 2) \end{array}$

$V' = 0.713 \times (R' - Y') + 128$  (eq. 3)

There is an option where 128 is not added to U'V'.

#### Y'Cb'Cr' Using sRGB Formulas:

The MT9M114 implements the sRGB standard. This option provides YCbCr coefficients for a correct 4:2:2 transmission.

#### Table 14. YCbCr OUTPUT DATA ORDERING

NOTE: 16 < Y601< 235; 16 < Cb < 240; 16 < Cr < 240; and 0 < = RGB < = 255.

$$\begin{array}{l} Y' \;=\; (0.2126\,\times\,R'\,+\,0.7152\,\times\,G'\,+\,0.0722\,\times\,B')\,\times \\ & \times\;(219/256)\,+\,16 \end{array} \tag{eq. 4}$$

$$Cb' = 0.5389 \times (B' - Y') \times (224/256) + 128$$

(eq. 5)

$$Cr' = 0.635 \times (R' - Y') \times (224/256) + 128$$

(eq. 6)

#### Y'U'V' Using sRGB Formulas:

These are similar to the previous set of formulas, but have YUV spanning a range of 0 through 255.

$$Y' \,=\, 0.2126 \,\times\, R' \,+\, 0.7152 \,\times\, G' \,+\, 0.0722 \,\times\, B' \qquad (\text{eq. 7})$$

$$U' = 0.5389 \times (B' - Y') + 128 = (eq. 8)$$

= - 0.1146 × B' - 0.3854 × G' + 0.5 × B' + 128

$$V' = 0.635 \times (R' - Y') + 128 = (eq. 9)$$

$$= 0.5 \times R' - 0.4542 \times G' - 0.0458 \times B' + 128$$

There is an option to disable adding 128 to U'V'. The reverse transform is as follows:

$R' = Y + 1.5748 \times (V - 128)$  (eq. 10)

$$G'\,=\,Y\,-\,0.1873\,\times\,(U\,-\,128)\,-\,0.4681\,\times\,(V\,-\,128)$$

(eq. 11)

$$B' = Y + 1.8556 \times (U - 128)$$

(eq. 12)

#### Uncompressed YUV/RGB Data Ordering

The MT9M114 supports swapping YCbCr mode, as illustrated in Table 14.

| Mode              | Data Sequence   |                 |                  |                  |

|-------------------|-----------------|-----------------|------------------|------------------|

| Default (No Swap) | Cb <sub>i</sub> | Y <sub>i</sub>  | Cr <sub>i</sub>  | Y <sub>i+1</sub> |

| Swapped CrCb      | Cr <sub>i</sub> | Y <sub>i</sub>  | Cb <sub>i</sub>  | Y <sub>i+1</sub> |

| Swapped YC        | Yi              | Cb <sub>i</sub> | Y <sub>i+1</sub> | Cr <sub>i</sub>  |

| Swapped CrCb, YC  | Yi              | Cr <sub>i</sub> | Y <sub>i+1</sub> | Cb <sub>i</sub>  |

The RGB output data ordering in default mode is shown in Table 15. The odd and even bytes are swapped when luma/chroma swap is enabled. R and B channels are bitwise swapped when chroma swap is enabled.

#### Table 15. RGB ORDERING IN DEFAULT MODE

| Mode (Swap Disabled) | Byte | D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> |

|----------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| 565RGB               | Odd  | $R_7 R_6 R_5 R_4 R_3 G_7 G_6 G_5$                                                                                       |

|                      | Even | $G_4 G_3 G_2 B_7 B_6 B_5 B_4 B_3$                                                                                       |

| 555RGB               | Odd  | 0 R <sub>7</sub> R <sub>6</sub> R <sub>5</sub> R <sub>4</sub> R <sub>3</sub> G <sub>7</sub> G <sub>6</sub>              |

|                      | Even | $G_4 G_3 G_2 B_7 B_6 B_5 B_4 B_3$                                                                                       |

| 444xRGB              | Odd  | $R_7 R_6 R_5 R_4 G_7 G_6 G5 G_4$                                                                                        |

|                      | Even | B <sub>7</sub> B <sub>6</sub> B <sub>5</sub> B <sub>4</sub> 0 0 0 0                                                     |

| x444RGB              | Odd  | 0 0 0 0 R <sub>7</sub> R <sub>6</sub> R <sub>5</sub> R <sub>4</sub>                                                     |

|                      | Even | $G_7 G_6 G_5 G_4 B_7 B_6 B_5 B_4$                                                                                       |

## Uncompressed Raw Bayer Bypass Output

Raw 10-bit Bayer data from the sensor core can be output in bypass mode by:

- 1. Using both D<sub>OUT</sub>[7:0] and D<sub>OUT</sub>\_LSB[1:0].

- 2. Using only  $D_{OUT}[7:0]$  with a special 8 + 2 data

- format, shown in Table 16.

- 3. Using the MIPI interface.

#### Table 16. 2–BYTE BAYER FORMAT

| 2–Byte Bayer Format | Bits Used                   | Bit Sequence                              |  |

|---------------------|-----------------------------|-------------------------------------------|--|

| Odd bytes           | 8 Data Bits                 | $D_9 D_8 D_7 D_6 D_5 D_4 D_3 D_2$         |  |

| Even bytes          | 2 Data Bits + 6 Unused Bits | 0 0 0 0 0 0 D <sub>1</sub> D <sub>0</sub> |  |

## **UVC INTERFACE**

The MT9M114 supports a set of UVC (USB Video Class) controls in order to simplify the integration of the MT9M114 with a host's USB bridge (or ISP) device.

The MT9M114 firmware includes a 'UVC Control' component that augments the CamControl variables. The UVC Control component sits above the CamControl interface (in terms of abstraction) and acts as a 'virtual host'. The intention is that CamControl and all other components are unaware of the UVC Control component.

UVC Control exposes a 'UVC control' page of shared variables to the host. This page contains variables compliant with the UVC 1.1 specification (where possible). The variables on this page are named to match the UVC specification, and have matching data sizes, units and ranges as required. Each UVC variable is 'virtual' – it does not control any MT9M114 function directly.

MT9M114 therefore provides a 'dual-personality' host interface:

- The primary CamControl interface, this interface exposes the full feature-set of the device.

- The secondary UVC Control interface, which simplifies integration of MT9M114 into a PC-Cam application.

More details on this topic can be found in the Developer Guide.

| Variable                    | Name                                       |

|-----------------------------|--------------------------------------------|

| R0xCC00<br>VAR(0x13,0x0000) | UVC_AE_MODE_CONTROL                        |

| R0xCC01<br>VAR(0x13,0x0001) | UVC_WHITE_BALANCE_TEMPERATURE_AUTO_CONTROL |

| R0xCC02<br>VAR(0x13,0x0002) | UVC_AE_PRIORITY_CONTROL                    |

| R0xCC03<br>VAR(0x13,0x0003) | UVC_POWER_LINE_FREQUENCY_CONTROL           |

| R0xCC04<br>VAR(0x13,0x0004) | UVC_EXPOSURE_TIME_ABSOLUTE_CONTROL         |

| R0xCC08<br>VAR(0x13,0x0008) | UVC_BACKLIGHT_COMPENSATION_CONTROL         |

| R0xCC0A<br>VAR(0x13,0x000A) | UVC_BRIGHTNESS_CONTROL                     |

| R0xCC0C<br>VAR(0x13,0x000C) | UVC_CONTRAST_CONTROL                       |

| R0xCC0E<br>VAR(0x13,0x000E) | UVC_GAIN_CONTROL UINT16                    |

| R0xCC10<br>VAR(0x13,0x0010) | UVC_HUE_CONTROL                            |

| R0xCC12<br>VAR(0x13,0x0012) | UVC_SATURATION_CONTROL UINT16              |

## Table 17. SUMMARY OF UVC COMMANDS

| Variable                    | Name                                  |

|-----------------------------|---------------------------------------|

| R0xCC14<br>VAR(0x13,0x0014) | UVC_SHARPNESS_CONTROL                 |

| R0xCC16<br>VAR(0x13,0x0016) | UVC_GAMMA_CONTROL                     |

| R0xCC18<br>VAR(0x13,0x0018) | UVC_WHITE_BALANCE_TEMPERATURE_CONTROL |

| R0xCC1C<br>VAR(0x13,0x001C) | UVC_FRAME_INTERVAL_CONTROL            |

| R0xCC20<br>VAR(0x13,0x0020) | UVC_MANUAL_EXPOSURE_CONFIG            |

| R0xCC21<br>VAR(0x13,0x0021) | UVC_FLICKER_AVOIDANCE_CONFIG          |

#### Table 17. SUMMARY OF UVC COMMANDS (continued)

## **MULTI-CAMERA SYNC**

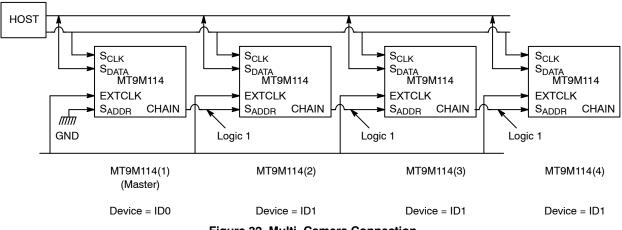

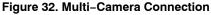

The MT9M114 supports more than one device to be connected in a "daisy-chain" type configuration. One of the devices will act as the master and the remainder will be slaves.

A typical connection diagram is shown in Figure 32. All of the MT9M114 that are to communicate are:

- Connected in a daisy-chain using S<sub>ADDR</sub> as an input and CHAIN as an output

- Clocked from a common clock source

- Controlled from a single master, presumed to be under software control of a host system

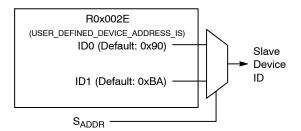

$S_{ADDR}$  is normally used as a static input that selects between two slave device addresses (See Figure 33. In order to implement the multi–sync function this input now has additional functionality that does not interfere with its use as device address selection.

There is a single register to control this function, named CHAIN\_CONTROL (R0x31FC). This register is controlled by the host. The register field assignment is shown in Table 18.

Figure 33. Normal Use of SADDR

## Table 18. CHAIN\_CONTROL REGISTER

| Bit  | Name         | Default | Description                                                                                                                                                                                                                                                                                                                                                    |

|------|--------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | chain_enable | 0       | 0: multi-camera daisy-chain communication function is disabled<br>1: multi-camera daisy-chain communication function is enabled<br>The result of toggling this bit while the sensor is streaming is UNDEFINED.                                                                                                                                                 |