# LE24512AQF

## Two Wire Serial Interface EEPROM (512k EEPROM)

## Overview

The LE24512AQF (hereinafter referred to as "this device") is a two-wire serial interface EEPROM (Electrically Erasable and Programmable ROM). This device realizes high speed and a high level reliability by high performance CMOS EEPROM technology. This device is compatible with I<sup>2</sup>C memory protocol, therefore it is best suited for application that requires re-writable nonvolatile parameter memory.

## **Functions**

- Capacity: 512k bits (64k × 8 bits)

- Single supply voltage: 1.7V to 3.6V

- Operating temperature: -40 to +85°C

- Interface: Two wire serial interface (I<sup>2</sup>C Bus\*)

- Operating clock frequency: 400kHz

- Low power consumption

- : Standby: 2µA (max)

- : Active (Read): 0.5mA (max)

- Automatic page write mode: 128 Bytes

- Read mode: Sequential read and random read

- Erase/Write cycles: 10<sup>6</sup> cycles (Page write)

- Data Retention: 20 years

- High reliability: Adopts proprietary symmetric memory array configuration (USP6947325)

- Noise filters connected to SCL and SDA pins

- Incorporates a feature to prohibit write operations under low voltage conditions.

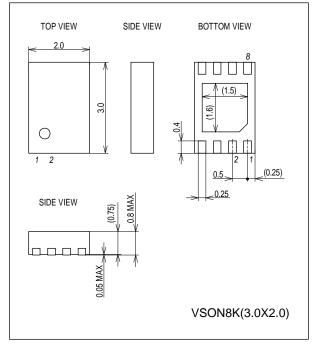

- Package : VSON8K $(3.0 \times 2.0)$

\* I<sup>2</sup>C Bus is a trademark of Philips Corporation.

\* This product is licensed from Silicon Storage Technology, Inc. (USA).

## Package Dimensions

unit : mm (typ)

3437

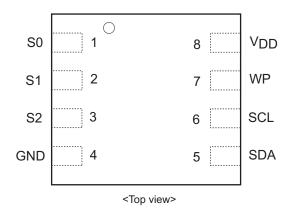

## **Pin Assignment**

## **Pin Descriptions**

| PIN.1 | S0              | Slave Device Address 0   |

|-------|-----------------|--------------------------|

| PIN.2 | S1              | Slave Device Address 1   |

| PIN.3 | S2              | Slave Device Address 2   |

| PIN.4 | GND             | Ground                   |

| PIN.5 | SDA             | Serial data input/output |

| PIN.6 | SCL             | Serial clock input       |

| PIN.7 | WP              | Write protect pin        |

| PIN.8 | V <sub>DD</sub> | Power supply             |

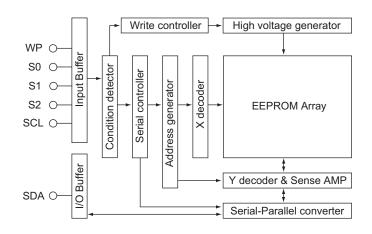

## **Block Diagram**

## **Specifications**

## Absolute Maximum Ratings

| Parameter           | Symbol | Conditions | Ratings                      | unit |

|---------------------|--------|------------|------------------------------|------|

| Supply voltage      |        |            | -0.5 to +4.6                 | V    |

| DC input voltage    |        |            | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Over-shoot voltage  |        | Below 20ns | -1.0 to V <sub>DD</sub> +1.0 | V    |

| Storage temperature | Tstg   |            | -65 to +150                  | °C   |

Note: If an electrical stress exceeding the maximum rating is applied, the device may be damaged.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

## **Operating Conditions**

| Parameter                | Symbol | Conditions | Ratings    | unit |

|--------------------------|--------|------------|------------|------|

| Operating supply voltage |        |            | 1.7 to 3.6 | V    |

| Operating temperature    |        |            | -40 to +85 | °C   |

## **DC Electrical Characteristics**

| Parameter                    | Complete d        | One ditions                                           | Spec.                |     |                      |      |

|------------------------------|-------------------|-------------------------------------------------------|----------------------|-----|----------------------|------|

|                              | Symbol            | Conditions                                            | min                  | typ | max                  | unit |

| Supply current at reading    | I <sub>CC</sub> 1 | f=400kHz, $V_{DD} = V_{DD} max$                       |                      |     | 0.5                  | mA   |

| Supply current at writing    | I <sub>CC</sub> 2 | f=400kHz, t <sub>WC</sub> =5ms, $V_{DD} = V_{DD} max$ |                      |     | 5                    | mA   |

| Standby current              | I <sub>SB</sub>   | V <sub>IN</sub> =V <sub>DD</sub> or GND               |                      |     | 2                    | μΑ   |

| Input leakage current (SCL)  | ι <sub>LI</sub>   | $V_{IN}$ =GND to $V_{DD}$ , $V_{DD}$ = $V_{DD}$ max   | -2.0                 |     | +2.0                 | μΑ   |

| Output leakage current (SDA) | ILO               | $V_{OUT}$ =GND to $V_{DD}$ , $V_{DD}$ = $V_{DD}$ max  | -2.0                 |     | +2.0                 | μΑ   |

| Input low voltage            | VIL               |                                                       |                      |     | V <sub>DD</sub> *0.3 | V    |

| Input high voltage           | VIH               |                                                       | V <sub>DD</sub> *0.7 |     |                      | V    |

|                              |                   | I <sub>OL</sub> =0.7mA, V <sub>DD</sub> =1.7V         |                      |     | 0.2                  | V    |

| Output low voltage           | VOL               | I <sub>OL</sub> =1.0mA, V <sub>DD</sub> =1.7V         |                      |     | 0.4                  | V    |

|                              |                   | I <sub>OL</sub> =2.0mA, V <sub>DD</sub> =2.5V         |                      |     | 0.4                  | V    |

### $\textbf{Capacitance}/Ta{=}25^{\circ}C,\,f{=}1MHz$

| Parameter                 | Symbol           | Conditions                           | max | unit |

|---------------------------|------------------|--------------------------------------|-----|------|

| In/Output pin capacitance | C <sub>I/O</sub> | V <sub>I/O</sub> =0V (SDA)           | 10  | pF   |

| Input pin capacitance     | Cl               | V <sub>IN</sub> =0V (other than SDA) | 10  | pF   |

Note: This parameter is sampled and not 100% tested.

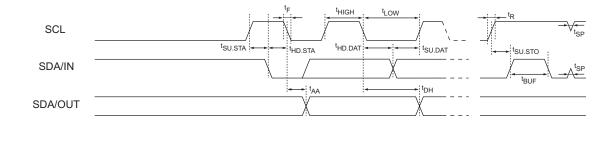

## **AC Electric Characteristics**

| Input pulse level            | 0.1×V <sub>DD</sub> to 0.9×V <sub>DD</sub> |

|------------------------------|--------------------------------------------|

| Input pulse rise / fall time | 20ns                                       |

| Output detection voltage     | 0.5×V <sub>DD</sub>                        |

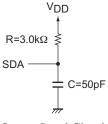

| Output load                  | 50pF+Pull up resistor 3.0k $\Omega$        |

Output Load Circuit

## Fast Mode

| Parameter                      | Symbol              |      | unit |     |      |

|--------------------------------|---------------------|------|------|-----|------|

| Parameter                      | Symbol              | min  | typ  | max | unit |

| Slave mode SCL clock frequency | <sup>f</sup> SCLS   | 0    |      | 400 | kHz  |

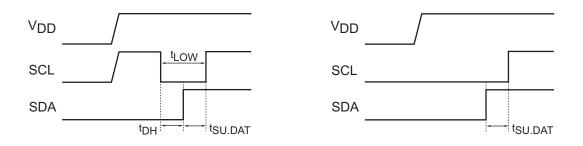

| SCL clock low time             | <sup>t</sup> LOW    | 1200 |      |     | ns   |

| SCL clock high time            | tHIGH               | 600  |      |     | ns   |

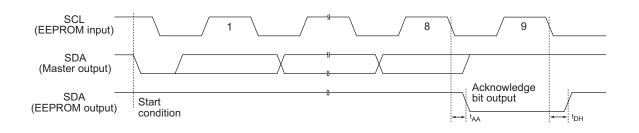

| SDA output delay time          | t <sub>AA</sub>     | 100  |      | 900 | ns   |

| SDA data output hold time      | <sup>t</sup> DH     | 100  |      |     | ns   |

| Start condition setup time     | <sup>t</sup> SU.STA | 600  |      |     | ns   |

| Start condition hold time      | <sup>t</sup> HD.STA | 600  |      |     | ns   |

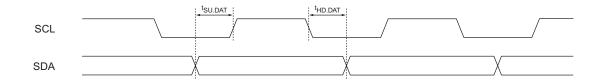

| Data in setup time             | <sup>t</sup> SU.DAT | 100  |      |     | ns   |

| Data in hold time              | <sup>t</sup> HD.DAT | 0    |      |     | ns   |

| Stop condition setup time      | <sup>t</sup> SU.STO | 600  |      |     | ns   |

| SCL SDA rise time              | t <sub>R</sub>      |      |      | 300 | ns   |

| SCL SDA fall time              | t <sub>F</sub>      |      |      | 300 | ns   |

| Bus release time               | <sup>t</sup> BUF    | 1200 |      |     | ns   |

| Noise suppression time         | t <sub>SP</sub>     |      |      | 100 | ns   |

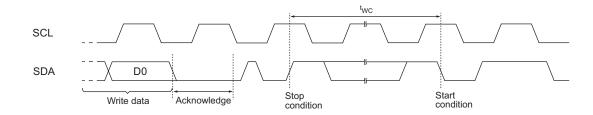

| Write cycle time               | tWC                 |      |      | 5   | ms   |

## **Standard Mode**

| Parameter                      | Cumhal              |      |     |      |      |

|--------------------------------|---------------------|------|-----|------|------|

| Parameter                      | Symbol              | min  | typ | max  | unit |

| Slave mode SCL clock frequency | <sup>f</sup> SCLS   | 0    |     | 100  | kHz  |

| SCL clock low time             | <sup>t</sup> LOW    | 4700 |     |      | ns   |

| SCL clock high time            | thigh               | 4000 |     |      | ns   |

| SDA output delay time          | t <sub>AA</sub>     | 100  |     | 3500 | ns   |

| SDA data output hold time      | <sup>t</sup> DH     | 100  |     |      | ns   |

| Start condition setup time     | <sup>t</sup> SU.STA | 4700 |     |      | ns   |

| Start condition hold time      | <sup>t</sup> HD.STA | 4000 |     |      | ns   |

| Data in setup time             | <sup>t</sup> SU.DAT | 250  |     |      | ns   |

| Data in hold time              | <sup>t</sup> HD.DAT | 0    |     |      | ns   |

| Stop condition setup time      | <sup>t</sup> SU.STO | 4000 |     |      | ns   |

| SCL SDA rise time              | <sup>t</sup> R      |      |     | 1000 | ns   |

| SCL SDA fall time              | tF                  |      |     | 300  | ns   |

| Bus release time               | <sup>t</sup> BUF    | 4700 |     |      | ns   |

| Noise suppression time         | t <sub>SP</sub>     |      |     | 100  | ns   |

| Write cycle time               | tWC                 |      |     | 5    | ms   |

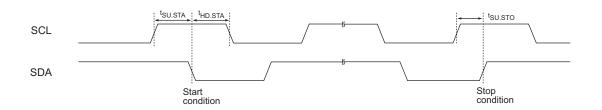

## **Bus Timing**

## Write Timing

## **Pin Functions**

#### SCL (serial clock input) pin

The SCL signal is used to control serial input data timing. The SCL is used to latch input data synchronously at the rising edge and read output data synchronously at the falling edge.

#### SDA (serial data input/output) pin

The SDA pin is bidirectional for serial data transfer. It is an open-drain structure that needs to be pulled up by resistor.

#### WP (write protect) pin

When the WP signal is high, write protection are enabled. When this signal is low, write operations for all memory arrays are allowed. The read operation is always activated irrespective of the WP pin status.

#### S0/S1/S2 (Slave Address) pin

When many devices are connected on the same bus, the S0/S1/S2 are used to select the device. The S0/S1/S2 must be tied to  $V_{\mbox{DD}}$  or GND

## **Functional Description**

The device supports the  $I^2C$  protocol. Any device that sends data on to the bus is defined to be a transmitter, and any device that reads the data to a receiver. The device that controls the data transfer is known as the bus master, and the other as the slave device.

#### 1 Start condition

A start condition needs to start the EEPROM operation, it is to set falling edge of the SDA while the SCL is stable in the high status.

#### 2 Stop condition

A start condition is identified by rising edge of the SDA signal while the SCL is stable in the high status. The device becomes the standby mode from a read operation by a stop condition. In a write sequence, a stop condition is trigger to terminate the write data inputs and it is trigger to start the internal write cycle. After the internally write cycle time which is specified as tWC, the device enters a standby mode.

#### 3 Data input

During data input, the device latches the SDA on the rising edge of the SCL. For correct the operation, the SDA must be stable during the rising edge of the SCL.

4 Acknowledge bit (ACK)

The Acknowledge bit is used to indicate a successful byte data transfer. The receiver sends a zero to acknowledge that it has received each word (Device code, Slave address etc) from the transmitter.

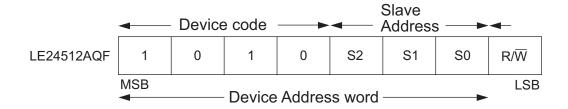

### 5 Device addressing

To transmit between the bus master and slave device (EEPROM), the master must send a start condition to the EEPROM. The device address word of the EEPROM consists of 4-bit device code, 3-bit slave device address code and 1-bit read/write code. By sending there, it becomes possible to communicate between the bus master and the EEPROM.

The upper 4-bits of the device address word are called the device code, the device code of the EEPROM uses "1010b" fixed code. This device has the 3-bit of the slave device address as the slave address (S0,S1,S2), so it can connect up to eight devices on the bus.

When the device code is received on the SDA, the device only responds if slave address pin tied to  $V_{DD}$  or GND is the same as the slave address signal input. The 8<sup>th</sup> bit is the read/write bit. The bit is set to 1 for read operation and 0 for write operation. If a match occurs on the device code, the corresponding devices give an acknowledgement on SDA during the 9<sup>th</sup> bit time. If device does not match the device code, it deselects itself from the bus, and goes into the standby mode. Use the random read command when you execute reading after the slave device was switched.

## 6 EEPROM write operation

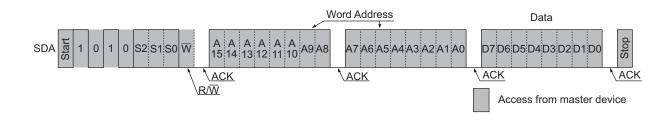

### 6-1. Byte writing

The write operation requires a 7-bit device address word with the  $8^{th}$  bit=0 (write). Then the EEPROM sends acknowledgement 0 at the  $9^{th}$  clock cycle. After these, the EEPROM receives word address (A15 to A8), and the EEPROM outputs acknowledgement 0. And then, the EEPROM receives word address (A7 to A0), and the EEPROM outputs acknowledgement 0. Then the EEPROM receives 8-bit write data, the EEPROM outputs acknowledgement 0 after receipt of write data. If the EEPROM receives a stop condition, the EEPROM enters an internally timed (t<sub>WC</sub>) write cycle and terminates receipt of inputs until completion of the write cycle.

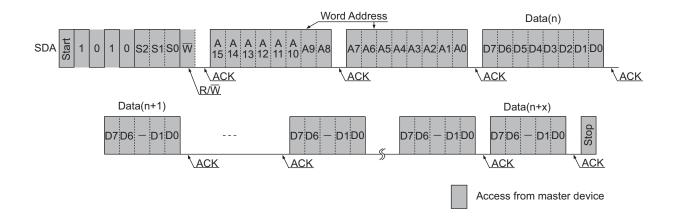

#### 6-2. Page writing

The page write allows up to 128 bytes to be written in a single write cycle. The page write is the same sequences as the byte write except for inputting the more write data. The page write is initiated by a start condition, device code, device address, memory address (n) and write every 9<sup>th</sup> bit acknowledgement. The device enters the page write operation if this device receives more write data (n+1) instead of receiving a stop condition. The page address (A0 to A6) bits are automatically incremented on receiving write data (n+1). The device can continue to receive write data up to 128 bytes. If the page address bit reaches the last address of the page, the page address bits will roll over to the first address of the same page and previous write data will be overwritten. After these, if the device receives a stop condition, the device enters an internally timed (t<sub>WC</sub> × (n+x)) write cycle and terminates receipt of inputs until completion of the write cycle.

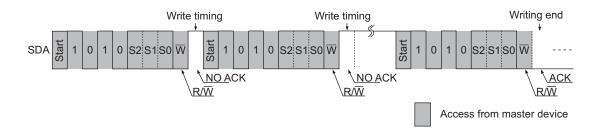

## 6-3. Acknowledge polling

Acknowledge polling operation is used to show if the EEPROM is in an internally timed write cycle or not. This operation is initiated by the stop condition after inputting write data. This requires the 8-bit device address word with the  $8^{th}$  bit = 0 (write) following the start condition during an internally timed write cycle. If the EEPROM is busy with the internal write cycle, no acknowledge will be returned. If the EEPROM has terminated the internal write cycle, it responds with an acknowledge. The terminated write cycle of the EEPROM can be known by this operation.

### 7 EEPROM read operations

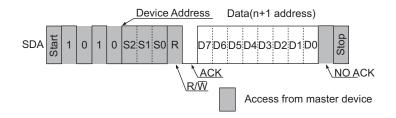

#### 7-1. Current address read

The device has an internal address counter. It maintains that last address during the last read or write operation, with incremented by one. The current address read accesses the address kept by the internal address counter. After receiving a start condition and the device address word with the  $8^{th}$  bit = 1 (read), the EEPROM outputs the 8-bit current address data from following acknowledgement 0. If the EEPROM receives acknowledgement 1 and a following stop condition, the EEPROM stops the read operation and is returned to a standby mode. In case the EEPROM has accessed the last address of the last page at previous read operation, the current address will roll over and returns to zero address. In case EEPROM has accessed the last address of the last address of the last address of the same page. The current address is valid while power is on. After power on, the current address will be reset (all 0).

\*: If the write data is 1 or more bytes but less than 128 bytes, the current address after page writing is the address equivalent to the number of bytes to be written in the specified word address +1. If the write data is 128 or more bytes, it is the designated word address. If the last address (A6-A0=111111b) on the page has been designated by byte write as the word address, the first address (A6-A0=000000b) on the page serves as the internal address after writing.

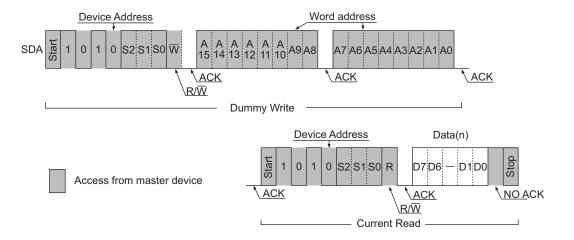

#### 7-2. Random read

The random read requires a dummy write to set read address. The EEPROM receives a start condition and the device address word with the  $8^{th}$  bit = 0 (write), the memory address. The EEPROM outputs acknowledgement 0 after receiving memory address then enters a current address read with receiving a start condition. The EEPROM outputs the read data of the address which was defined in the dummy write operation. After receiving no acknowledgement and a following stop condition, the EEPROM stops the random read operation and returns to a standby mode.

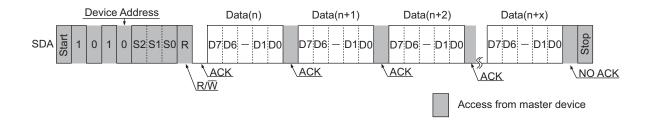

## 7-3. Sequential read

The sequential read operation is initiated by either a current address read or random read. If the EEPROM receives acknowledgement 0 after 8-bit read data, the read address is incremented and the next 8-bit read data outputs. The current address will roll over and returns address zero if it reaches the last address of the last page. The sequential read can be continued after roll over. The sequential read is terminated if the EEPROM receives no acknowledgement and a following stop condition.

## **Application Notes**

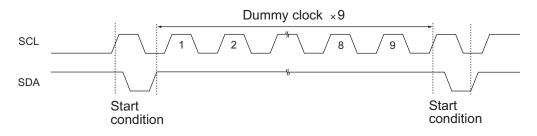

1) Software reset function

Software reset (start condition + 9 dummy clock cycles + start condition), shown in the figure below, is executed in order to avoid erroneous operation after power-on and to reset while the command input sequence. During the dummy clock input period, the SDA bus must be opened (set to high by a pull-up resistor). Since it is possible for the ACK output and read data to be output from the EEPROM during the dummy clock period, forcibly entering H will result in an overcurrent flow.

Note that this software reset function does not work during the internal write cycle.

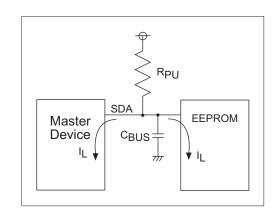

2) Pull-up resistor of SDA pin

Due to the demands of the  $I^2C$  bus protocol function, the SDA pin must be connected to a pull-up resistor (with a resistance from several k $\Omega$  to several tens of k $\Omega$ ) without fail. The appropriate value must be selected for this resistance (RpU) on the basis of the V<sub>IL</sub> and I<sub>IL</sub> of the microcontroller and other devices controlling this product as well as the V<sub>OL</sub>–I<sub>OL</sub> characteristics of the product. Generally, when the resistance is too high, the operating frequency will be restricted; conversely, when it is too low, the operating current consumption will increase.

#### RpU maximum resistance

The maximum resistance must be set in such a way that the bus potential, which is determined by the sum total  $(I_L)$  of the input leaks of the devices connected to the SDA bus and by RPU, can completely satisfy the input high level  $(V_{IH} \text{ min})$  of the microcontroller and EEPROM. However, a resistance value that satisfies SDA rise time t<sub>R</sub> and fall time t<sub>F</sub> must be set.

RPU maximum value =  $(V_{DD} - V_{IH})/I_L$

Example: When  $V_{DD}$ =3.0V and  $I_L$ = 2 $\mu$ A RpU maximum value = (3.0V - 3.0V × 0.8)/2 $\mu$ A = 300k $\Omega$

RpU minimum value

A resistance corresponding to the low-level output voltage (V<sub>OL</sub> max) of EEPROM must be set.

RPU minimum value =  $(V_{DD} - V_{OL})/I_{OL}$

Example: When  $V_{DD}$ =3.0V,  $V_{OL}$  = 0.4V and  $I_{OL}$  = 1mA RPU minimum value = (3.0V - 0.4)/1mA = 2.6k $\Omega$

#### Recommended RpU setting

RpU is set to strike a good balance between the operating frequency requirements and power consumption. If it is assumed that the SDA load capacitance is 50pF and the SDA output data strobe time is 500ns, RpU will be about RpU =  $500ns/50pF = 10k\Omega$ .

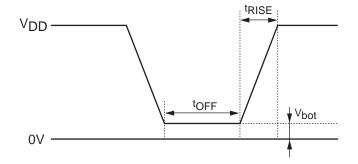

## 3) Precautions when turning on the power

This product contains a power-on reset circuit for preventing the inadvertent writing of data when the power is turned on. The following conditions must be met in order to ensure stable operation of this circuit. No data guarantees are given in the event of an instantaneous power failure during the internal write operation.

| Item                 | Symbol            |     | unit |     |      |

|----------------------|-------------------|-----|------|-----|------|

|                      |                   | min | typ  | max | unit |

| Power rise time      | <sup>t</sup> RISE |     |      | 100 | ms   |

| Power off time       | <sup>t</sup> OFF  | 10  |      |     | ms   |

| Power bottom voltage | V <sub>bot</sub>  |     |      | 0.2 | V    |

Notes:

- 1) The SDA pin must be set to high and the SCL pin to low or high.

- 2) Steps must be taken to ensure that the SDA and SCL pins are not placed in a high-impedance state.

- A. If it is not possible to satisfy the instruction 1 in Note above, and SDA is set to low during power rise. After the power has stabilized, the SCL and SDA pins must be controlled as shown below, with both pins set to high.

- B. If it is not possible to satisfy the instruction 2 in Note above After the power has stabilized, software reset must be executed.

- C. If it is not possible to satisfy the instructions both 1 and 2 in Note above. After the power has stabilized, the steps in A must be executed, then software reset must be executed.

- 4) Noise filter for the SCL and SDA pins This product contains a filter circuit for eliminating noise at the SCL and SDA pins. Pulses of 100ns or less are not recognized because of this function.

- 5) Function to inhibit writing when supply voltage is low This product contains a supply voltage monitoring circuit that inhibits inadvertent writing below the guaranteed operating supply voltage range. The data is protected by ensuring that write operations are not started at voltages (typ.) of 1.3V and below.

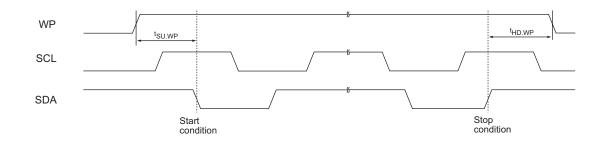

#### 6) Notes on write protect operation

This product prohibits all memory array writing when the WP pin is high. To ensure full write protection, the WP is set high for all periods from the start condition to the stop condition, and the conditions below must be satisfied.

| ltom          | Symbol             |     | mit |     |      |

|---------------|--------------------|-----|-----|-----|------|

| ltem          |                    | min | typ | max | unit |

| WP Setup time | <sup>t</sup> SU.WP | 600 |     |     | ns   |

| WP Hold time  | <sup>t</sup> HD.WP | 600 |     |     | ns   |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affimative Action Employeer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ON Semiconductor: LE24512AQF-AH