# AN10911

# SD(HC)-memory card and MMC interface conditioning Rev. 2 — 4 April 2013 Applica

**Application note**

#### **Document information**

| Info     | Content                                                                                                                                                                                                                                                                              |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | SD-memory card, Multi Media Card (MMC), ElectroStatic Discharge (ESD) protection, ElectroMagnetic Interference (EMI) filtering                                                                                                                                                       |

| Abstract | This document gives an overview about different ESD protection and EMI filter devices optimized for SD-memory card and MMC interfaces. These devices cover the range from 1-bit to current standard 4-bit (SD-memory card, SD 2.0) or 8-bit (MMC) high-speed memory card interfaces. |

### SD(HC)-memory card and MMC interface conditioning

### **Revision history**

| Rev | Date     | Description                   |

|-----|----------|-------------------------------|

| 2   | 20130404 | Discontinued products removed |

| 1   | 20100429 | Initial version               |

### **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

### SD(HC)-memory card and MMC interface conditioning

### 1. Introduction

The SD-memory card and MMC are the most popular memory cards in modern communication, computer and consumer appliances. They support state-of-the-art security and capacity requirements of modern audio and video applications in consumer and communication products.

SD-memory cards support content protection, prevention of illegal use of content and security systems based on, for example ISO-7816. An embedded version of MMC is eMMC, according to the JESD84-A43. It offers up to 8-bit wide interface and can be applied in SD-memory card compatible hardware interfaces.

While the SD-memory card adds an advanced data storage function to an application, there is a more general Secure Digital Input Output (SDIO) card.

The SDIO card specification provides separately a specified interface to different I/O units. It provides various functions to an SD host, including memory storage that is compatible with the SD-memory card specification. Even if an SD host is not SDIO compatible (just supporting SD-memory cards), no physical damage or disruption of operation will occur.

An SD-memory card communication is based on an advanced 8/9-pin interface (clock, command, 1- or 4-bit data and  $2/3 \times power/GND$ ) designed to operate at a maximum operating frequency of 50 MHz according to SD 2.0 specification.

The MMC works with an up to 52 MHz clock but supports in its latest versions up to 8 data bits in a 13-pin interface (clock, command, 1-, 4- or 8-bit data,  $3 \times power/GND$ ).

While the SD-memory card can contain some ESD protection (see chapter 8.1.3. of Ref. 1 "SD specifications, part 1, Physical Layer Specification version 2.00, May 9, 2006"), SD host interfaces require an additional high-level ESD protection according to the IEC61000-4-2 standard in addition to the host-interface integrated ESD protection which is typically very weak.

Strict EMI regulations and system requirements, as specified in GSM mobile phones, request filters that reduce the radiated and/or conducted EMI but still comply with the electrical requirements of the interface specification.

The continuing trend in miniaturization of portable appliances implies that interface devices offering ESD protection and EMI filtering should also, where possible, integrate biasing circuits or resistors into a single small-sized package.

NXP Semiconductors SD-memory card interface conditioning devices explained in this document fully support this continuing trend and offer interface conditioning functions such as:

- High-level ESD protection according the IEC61000-4-2 standard, often exceeding the highest specified level 4

- EMI filtering, suppressing unwanted Radio Frequencies (RF), in combination with SD interface compliant physical signaling

- Integrated biasing resistor networks to reduce the component count and to free up additional space on the Printed-Circuit Board (PCB) surface

### SD(HC)-memory card and MMC interface conditioning

### 2. SD-memory card electrical interface

Today many appliances use 2.7 V to 3.6 V operating mode. It enables the use of a fixed voltage interface and power supply to reduce cost and complexity of the control circuitry.

All further descriptions are related to this high-voltage range: 2.7 V to 3.6 V supply voltage operated interfaces.

A list of SD-memory card threshold levels for this range is listed in Table 2.

### 2.1 SD-memory card and microSD card interfaces

The SD-memory card exhibits nine pins (eight pins in case of microSD card) that are used to support electrical communication in two alternative communication protocols: SD and SPI (Serial Peripheral Interface). The host system can choose either one of these modes. The card detects which mode is requested by the host when the reset command is received and expects all further communication to be in the same communication mode (see Ref. 1).

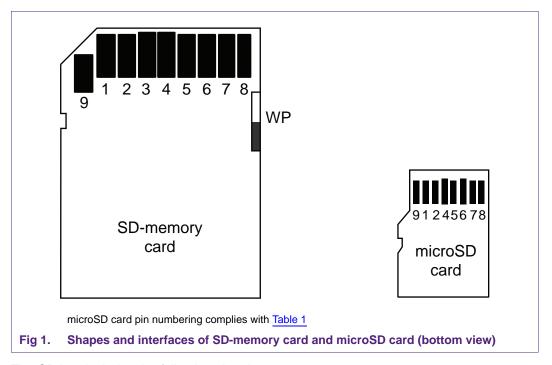

Figure 1 shows an SD-memory card and microSD card with the interface pins.

The SD bus includes the following signals:

- CLK: host to card clock signal

- CMD: bidirectional command/response signal

- DAT0 DAT3: four bidirectional data signals

- $\bullet~$   $V_{DD},\,V_{SS1},\,V_{SS2}\!\!:$  power and ground signals

### SD(HC)-memory card and MMC interface conditioning

The SPI bus includes the following signals:

CS: host to card chip select signal

• CLK: host to card clock signal

DataIn: host to card data signal

DataOut: card to host data signal

The SPI interface uses 7 out of the SD 9 signals (DAT1 and DAT 2 are not used, DAT3 is the CS signal) of the SD bus.

<u>Table 1</u> summarizes the pins of the SD card interface as used in SD and SPI modes:

Table 1. Interface pins of an SD-memory card and microSD card

| number<br>1 | Name      |        |                                | SPI mode |      |                          |  |

|-------------|-----------|--------|--------------------------------|----------|------|--------------------------|--|

| 1           |           | Type   | Description                    | Name     | Туре | Description              |  |

|             | CD/DAT3   | I/O/PP | card-detect / data line (bit3) | CS       | I    | chip select (active low) |  |

| 2           | CMD       | PP     | command/response               | DI       | I    | data in                  |  |

| 3           | GND1/VSS1 | S      | supply voltage ground          | VSS      | S    | supply voltage ground    |  |

| 4           | VDD       | S      | supply voltage                 |          | S    | supply voltage           |  |

| 5           | CLK       | I      | clock                          | SCLK     | I    | clock                    |  |

| 6           | GND2/VSS2 | S      | supply voltage ground          |          | S    | supply voltage ground    |  |

| 7           | DAT0      | I/O/PP | data line (bit 0)              | DO       | O/PP | data out                 |  |

| 8           | DAT1      | I/O/PP | data line (bit 1)              | RSV      | -    | reserved                 |  |

| 9           | DAT2      | I/O/PP | data line (bit 2)              | RSV      | -    | reserved                 |  |

<sup>[1]</sup> I: input, O: output, PP: input / output using push-pull drivers, S: power supply.

The signals listed in <u>Table 1</u> are directly provided from the SD-memory card itself. Additionally card holder can provide mechanical switches for card detection (CD) and write protection (WP) mechanisms.

### 2.2 Bus operation conditions

The minimum output level of the driving device and the input level of the receiving device are specified in Table 2 (see Ref. 1).

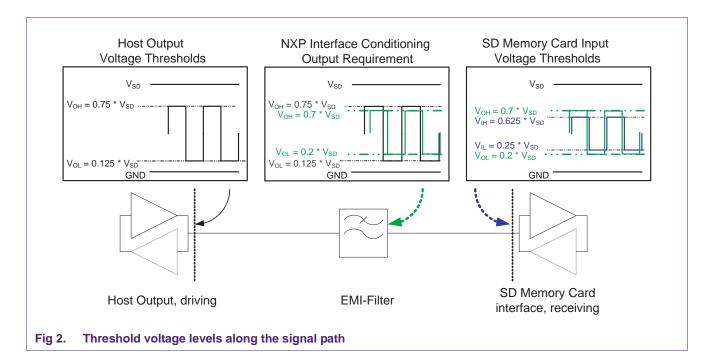

To decouple the SD-memory card interface specification from the signal-conditioning device (EMI filter, ESD protection, etc.), an intermediate signal threshold is specified in <a href="Table 3">Table 3</a>. This "EMI filter, card interface side" leveling is taken as a minimum requirement for an SD-memory card compliant interface conditioning device.

As ESD protection and EMI filter devices should be placed as close as possible to the contacts of the protected interface and integrate a major portion of the total bus capacitance  $C_{\text{BUS}}$ , they are responsible, as any other filter device, for most of the voltage drop.

Then the high-level and the low-level output voltages of the filter or conditioning device can be reduced (refer to  $V_{OH}$  and  $V_{OL}$  in <u>Table 3</u>) comparing to the output threshold levels (see <u>Table 2</u>) and still exceed the input voltage level requirements.

### SD(HC)-memory card and MMC interface conditioning

A detailed graphical overview of the different threshold levels at different positions of the signal path is depicted in <u>Figure 2</u>, starting with the driver output on the left side and ending with the receiving side on the right side of the drawing.

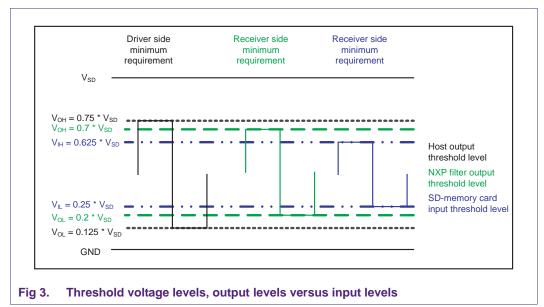

Three different threshold levels are shown in relation to each other in <u>Figure 3</u>, comparing the SD-memory card output, the NXP Semiconductors signal-conditioning device output and the SD-memory card input threshold levels.

Table 2. SD-memory card threshold levels for high-voltage range Values taken from Ref. 1

| Symbol           | Parameter                     | Condition                                  | Min                   | Max                   | Unit |

|------------------|-------------------------------|--------------------------------------------|-----------------------|-----------------------|------|

| $V_{SD}$         | SD-memory card supply voltage |                                            | 2.7                   | 3.6                   | V    |

| V <sub>OH</sub>  | high-level output voltage     | $I_{OH} = -100 \mu A;$<br>$V_{SD} = 2.7 V$ | $0.75 \times V_{SD}$  | -                     | V    |

| V <sub>OL</sub>  | low-level output voltage      | $I_{OL} = 100 \mu A;$<br>$V_{SD} = 2.7 V$  | -                     | $0.125 \times V_{SD}$ | V    |

| V <sub>IH</sub>  | high-level input voltage      |                                            | $0.625 \times V_{SD}$ | •                     | V    |

| V <sub>IL</sub>  | low-level input voltage       |                                            | -                     | $0.25 \times V_{SD}$  | V    |

| t <sub>Pup</sub> | power up time                 | $0~V \leq V_{SD} \leq 2.7~V$               | -                     | 250                   | ms   |

Table 3. SD-memory card operating conditions

| Symbol                  | Parameter                                                                    |        | Min                 | Max                 | Unit |

|-------------------------|------------------------------------------------------------------------------|--------|---------------------|---------------------|------|

| $V_{SD}$                | SD-memory card supply voltage                                                |        | 2.7                 | 3.6                 | V    |

| I <sub>DD</sub>         | supply current in high-speed mode                                            |        | -                   | 200                 | mA   |

| V <sub>OH</sub>         | high-level output voltage                                                    | [1][3] | $0.7 \times V_{SD}$ | -                   | V    |

| $V_{OL}$                | low-level output voltage                                                     | [2][3] | -                   | $0.2 \times V_{SD}$ | V    |

| $C_L$                   | load capacitance                                                             |        | -                   | 40                  | pF   |

| $C_{CARD}$              | SD-memory card signal line capacitance                                       |        | -                   | 10                  | pF   |

| C <sub>HOST + BUS</sub> | capacitance of host interface and signal bus                                 |        | -                   | 30                  | pF   |

| R <sub>CMD</sub>        | external pull-up resistor value to prevent bus floating                      |        | 10                  | 100                 | kΩ   |

| R <sub>DAT</sub>        | external pull-up resistor value to prevent bus floating; DAT0, DAT1 and DAT2 |        | 10                  | 100                 | kΩ   |

| R <sub>DAT3</sub>       | SD-memory card internal pull-up resistor value DAT3/CD pin only              |        | 10                  | 90                  | kΩ   |

| L <sub>ch</sub>         | single line inductance                                                       |        | -                   | 16                  | nΗ   |

<sup>[1]</sup> SD-memory card specification is:  $V_{OH}$  minimum is  $0.75 \times V_{SD}$  and  $V_{IH}$  minimum is  $0.625 \times V_{SD}$  in Ref. 1; NXP Semiconductors  $V_{OH}$  minimum is  $0.7 \times V_{SD}$ .

<sup>[2]</sup> SD-memory card specification is:  $V_{OL}$  maximum is  $0.125 \times V_{SD}$  and  $V_{IL}$  maximum is  $0.25 \times V_{SD}$  in Ref. 1; NXP Semiconductors  $V_{OL}$  minimum is  $0.2 \times V_{SD}$ .

<sup>[3] 20 %</sup> to 70 % limits are chosen also to cover MMC specification.

### SD(HC)-memory card and MMC interface conditioning

All further considerations are based on a chosen 20 % and 70 % threshold respectively, related to the SD-memory card supply voltage  $V_{SD}$ , as specified in <u>Table 3</u>, unless otherwise indicated. These relative voltage levels also simplify an alignment with the MMC specification.

### SD(HC)-memory card and MMC interface conditioning

### 2.3 SD-memory card bus timing conditions

The SD-memory card interface has different timing requirements for the default mode and for the high-speed mode up to 50 MHz clock frequency.

Special attention should be paid to the clock signal rise time and fall time requirements (3 ns maximum).

All NXP Semiconductors devices support both the high-speed mode and the default mode requirements. Since high-speed mode requirements contain default mode requirements, only the former considered in this document.

Table 4. SD-memory card timing conditions (high-speed mode)[1]

| Symbol          | Parameter                 | Condition                       | Min   | Max | Unit |

|-----------------|---------------------------|---------------------------------|-------|-----|------|

| f <sub>PP</sub> | operating clock frequency |                                 | 0     | 50  | MHz  |

| t <sub>r</sub>  | rise time                 | 20 % to 70 % of $V_{DD}$        | [2] _ | 3   | ns   |

| t <sub>f</sub>  | fall time                 | 70 % to 20 % of V <sub>DD</sub> | [2]   | 3   | ns   |

<sup>[1]</sup> Other timing parameters such as hold time, set-up time, high-level and low-level are dependent on the host and SD-memory card interface and not significantly influenced by the NXP Semiconductors interface conditioning devices.

### 2.4 Capacitive load at the interface conditioning device output

NXP Semiconductors devices, such as IP4352CX24, have rise time and fall time requirements specified similarly to the data shown in <u>Table 5</u>.

Table 5. Time domain response

$T_{amb}$  = 25 °C,  $V_{CC}$  = 1.8 V,  $V_{BAT}$  = 3.5 V,  $V_{SD}$  = 2.9 V; 20 % to 70 % LOW-to-HIGH limits.

| Symbol     | Parameter            | Test conditions                      | Min | Тур | Max | Unit |

|------------|----------------------|--------------------------------------|-----|-----|-----|------|

| $t_r,t_f$  | rise time, fall time | $Z_{load}$ = 20 pF    100 k $\Omega$ | -   | 1.5 | 2.5 | ns   |

| $t_r, t_f$ | rise time, fall time | $Z_{load}$ = 40 pF    100 k $\Omega$ | -   | 2.7 | 3.6 | ns   |

The following abbreviations are used:

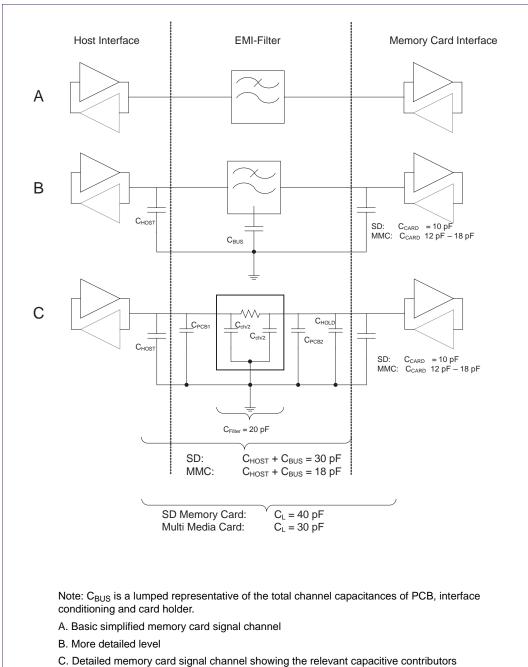

- Z<sub>load</sub>: capacitive load representing C<sub>PCB2</sub> + C<sub>HOLD</sub> + C<sub>CARD</sub> in NXP Semiconductors data sheets

- C<sub>PCBx</sub>: PCB trace capacitance

- C<sub>HOLD</sub>: card holder capacitance

- C<sub>BUS</sub>: total single bus channel capacitance excluding the SD-memory card

- $\bullet$   $\,$   $C_L$  : total single bus channel capacitance including the SD-memory card

For further details refer to Figure 4.

In this specification, Z<sub>load</sub> represents C<sub>CARD</sub> and a part of C<sub>BUS</sub>.

Figure 4 depicts the various basic capacitances of the signal path summing up to:

$$C_{BUS} = C_{PCB1} + C_{CH/2} + C_{CH/2} + C_{PCB2} + C_{HOLD} \le 30 \text{ pF}$$

<sup>[2]</sup> Values refer to V<sub>OH</sub> and V<sub>OL</sub> specified for the EMI filter output.

### SD(HC)-memory card and MMC interface conditioning

Note that a significant portion (NXP Semiconductors assumption 20 % to 30 %) of the SD-memory cards available on the market today have a card capacitance ( $C_{CARD}$ ) of more than 10 pF.

According to the SD-memory card specification (refer to chapter 6.5.5 of  $\underline{\text{Ref. 1}}$ ), the total channel capacitance  $C_L$  is defined as:

$$C_L = C_{BUS} + C_{CARD} \le 40 \text{ pF}$$

Assuming that state-of-the-art host interfaces show a capacitance of  $C_{HOST} \le 4~\mathrm{pF}$  and the NXP Semiconductors interface-conditioning devices add a capacitance in the range of  $C_{CH} = 2 \times C_{CH/2} \le 20~\mathrm{pF}$ , a capacitance of  $C_{PCB1} + C_{PCB2} + C_{HOLD} \le 6~\mathrm{pF}$  is left for the routing on the PCB and the card holder, which can already amount to 3 pF to 5 pF.

Due to  $Z_{load}$  representing a lumped capacitance of 20 pF in addition to the filter channel capacitance, it is obvious that the rise time and fall time requirement of 3 ns can be easily fulfilled.

AN10911 **NXP Semiconductors**

### SD(HC)-memory card and MMC interface conditioning

Fig 4. Basic signal channel depicted in three different detail levels

### SD(HC)-memory card and MMC interface conditioning

### 2.5 SD-memory card-detect mechanism

To detect an SD-memory card two different mechanisms can be used.

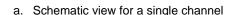

The conventional detection mechanism uses a mechanical switch in the card holder. The other mechanism is based on the pull-up resistor integrated into the SD-memory card. This resistor is connected to the DAT3/CD pin (where CD is card-detect). A detailed schematic showing both detection mechanisms is depicted in Figure 6.

If MMC and SD-memory card are used in the same holder, only the mechanical switch-based card detection can be used.

In contrast to the SD-memory card specification, the MMC specification does not specify any internal pull-up resistors for an electrical card detection mechanism.

Additionally, the SD-memory card specification gives clear priority to the mechanical switch detection method.

### 3. MMC electrical interface

Advanced appliances optimized for low-power consumption can operate MMCs at two different supply voltages with small disadvantage of the increased control effort and a selectable supply voltage. A number of MMC threshold levels for the high-voltage range are listed in Table 6.

### 3.1 Bus operating conditions

The minimum output level of the driving device, together with the receiving device input level is specified in <u>Table 6</u> (see <u>Ref. 2 "Multi Media Card System Specification version 4.3, JESD84-A43, November 2007")</u>.

Similar considerations as shown in <u>Section 2.3 "SD-memory card bus timing conditions"</u>, are also applicable to the MMC.

For high-voltage operation mode the threshold conditions are identical to the SD-memory card conditions. Therefore both can be operated if connected to the same physical interface as long as the electrical card detection mechanism is not used.

### SD(HC)-memory card and MMC interface conditioning

Table 6. MMC threshold levels (values taken from Ref. 2)

| Symbol          | Parameter                                          | Condition                               | Min                    | Max                    | Unit |

|-----------------|----------------------------------------------------|-----------------------------------------|------------------------|------------------------|------|

| $V_{MMC}$       | MMC supply voltage                                 |                                         |                        |                        |      |

|                 | high-voltage range                                 |                                         | 2.7                    | 3.6                    | V    |

|                 | low-voltage range                                  | [1]                                     | 1.7                    | 1.95                   | V    |

| Push-pull       | mode bus signal level fo                           | or high-voltage MMC                     |                        |                        |      |

| V <sub>OH</sub> | high-level output voltage                          | $I_{OH} = -100 \mu A;$ $V_{MMCmin}$     | $0.75 \times V_{MMC}$  | -                      | V    |

| V <sub>OL</sub> | low-level output voltage                           | $I_{OL}$ = 100 $\mu$ A;<br>$V_{MMCmin}$ | -                      | 0.125*V <sub>MMC</sub> | V    |

| $V_{IH}$        | high-level input voltage                           |                                         | $0.625 \times V_{MMC}$ | $V_{MMC} + 0.3$        | V    |

| $V_{IL}$        | low-level input voltage                            |                                         | $V_{SS}-0.3$           | $0.25 \times V_{MMC}$  | V    |

|                 | mode bus signal level for ge specified above for h | _                                       | C in 1.70 V to 1       | .95 V mode for         | •    |

| V <sub>OH</sub> | high-level output<br>voltage                       | $I_{OH} = -100 \mu A;$<br>$V_{MMCmin}$  | V <sub>MMC</sub> - 0.2 | -                      | V    |

| V <sub>OL</sub> | low-level output voltage                           | $I_{OL}$ = 100 $\mu$ A;<br>$V_{MMCmin}$ | -                      | 0.2                    | V    |

| V <sub>IH</sub> | high-level input voltage                           |                                         | $0.7 \times V_{MMC}$   | $V_{MMC} + 0.3$        | V    |

| V <sub>IL</sub> | low-level input voltage                            |                                         | $V_{SS}-0.3$           | $0.3 \times V_{MMC}$   | V    |

<sup>[1]</sup> Low-voltage levels are part of the dual voltage range card specification including high-voltage range. The voltage range from 1.95 V to 2.7 V is not specified.

Compared to the SD-memory card, the MMC bus is limited to a maximum of 30 pF (SD-memory card is 40 pF maximum).

Two basic differences between MMC and SD-memory card are:

- minimum resistor value of R<sub>CMD</sub> which is less than a half of the specified minimum of the SD-memory card specification

- DAT0 to DAT7 pull-up resistor values, starting at 50 k $\Omega$  instead of 10 k $\Omega$  in the SD-memory card specification (see <u>Table 3</u>).

The Embedded Multi Media Card (eMMC) contains internal pull-up resistors at the pins DAT1 to DAT7 to prevent floating of unconnected data lines (see Ref. 2). All other MMCs do not contain any pull-up resistors to prevent bus floating.

### SD(HC)-memory card and MMC interface conditioning

Table 7. MMC operating conditions

| Symbol                 | Parameter                                         |     | Min | Max | Unit |

|------------------------|---------------------------------------------------|-----|-----|-----|------|

| $C_L$                  | total bus capacitance for each signal line        |     | -   | 30  | pF   |

| C <sub>CARD</sub>      | single card signal line capacitance               |     |     |     |      |

|                        | C <sub>MICRO</sub>                                |     | -   | 12  | pF   |

|                        | C <sub>MOBILE</sub>                               |     | -   | 18  | pF   |

|                        | C <sub>BGA</sub>                                  |     | -   | 12  | pF   |

| R <sub>CMD</sub>       | CMD pull-up resistor value                        |     | 4.7 | 100 | kΩ   |

| R <sub>DAT7-DAT0</sub> | external DAT7 to DAT0 pull-up resistor value      | [1] | 50  | 100 | kΩ   |

| R <sub>intDAT</sub>    | eMMC internal DAT7 to DAT0 pull-up resistor value |     | 50  | 150 | kΩ   |

| L <sub>ch</sub>        | maximum signal line capacitance                   |     | -   | 16  | nΗ   |

<sup>[1]</sup> except eMMC

### 3.2 Bus timing conditions

The MMC interface has different timing requirements for the default mode and for the high-speed mode running up to 52 MHz. Special attention should be paid to the clock signal rise and fall time requirement (3 ns maximum) which is similar to the high-voltage range cards and the SD-memory card timing conditions (see <u>Table 4</u>).

Also, a reduced clock speed of up to 26 MHz can be used with these cards to save power in appliances that do not require high data rates.

All NXP Semiconductors devices support both the high-speed mode and the default mode requirements. Since high-speed mode requirements contain default mode requirements, only the former considered in this document.

Table 8. MMC timing conditions (high-speed mode)[1]

| Symbol            | Parameter                       | Min   | Max | Unit |

|-------------------|---------------------------------|-------|-----|------|

| $f_{PP}$          | operating clock frequency       | 0     | 52  | MHz  |

| t <sub>rise</sub> | high-speed mode clock rise time | [2] - | 3   | ns   |

| t <sub>fall</sub> | high-speed mode clock fall time | -     | 3   | ns   |

<sup>[1]</sup> Other timing parameters such as hold time, set-up time, high-time and low-time depend on the host and MMC interface. They are not significantly influenced by NXP Semiconductors interface conditioning devices.

### 3.3 Capacitive load at the interface conditioning device output

Refer to Section 2.4 for a detailed overview and calculation.

The drawing depicted in Figure 4 shows that it is difficult to build an MMC specification-compliant bus system that includes high-level ESD protection and EMI filtering. Nevertheless, most implementations used are related to the SD-memory card application and use only slightly higher total channel capacitances, reaching the SD specification for the value of  $C_{HOST} + C_{BUS}$ .

<sup>[2]</sup> Refer to Ref. 2, chapter 12.7.1 for further details.

### SD(HC)-memory card and MMC interface conditioning

### 4. SD-memory card and MMC interface comparison

A short summary of the main electrical interface parameters of the SD-memory card versus the MMC are listed in the following table:

Table 9. SD-memory card and MMC electrical parameters comparison

| Symbol                 | Parameter                                                              |     | SD-memory card | ММС        | Unit |

|------------------------|------------------------------------------------------------------------|-----|----------------|------------|------|

| $V_{\rm sd/MMC}$       | memory card supply voltage                                             |     |                |            |      |

|                        | high-voltage range                                                     |     | 2.7 - 3.6      | 2.7 - 3.6  | V    |

|                        | low-voltage range                                                      |     | -              | 1.7 - 1.95 | V    |

| f <sub>PP</sub>        | maximum operating clock frequency                                      |     | 50             | 52         | MHz  |

| t <sub>rise</sub>      | maximum high-speed mode clock rise time                                |     | 3              | 3          | ns   |

| t <sub>fall</sub>      | maximum high-speed mode clock fall time                                |     | 3              | 3          | ns   |

| C <sub>L</sub>         | maximum total bus capacitance for each signal line                     |     | 40             | 30         | pF   |

| C <sub>CARD</sub>      | maximum capacitance single card signal line                            |     | 10             | -          | pF   |

|                        | C <sub>MICRO</sub>                                                     |     | -              | 12         | pF   |

|                        | C <sub>MOBILE</sub>                                                    |     | -              | 18         | pF   |

|                        | $C_{BGA}$                                                              |     | -              | 12         | pF   |

| R <sub>CMD</sub>       | CMD pull-up resistor value                                             |     | 10 - 100       | 4.7 - 100  | kΩ   |

| R <sub>DAT7(3)-0</sub> | external DAT7(3) - DAT0 pull-up resistor value to prevent bus floating | [1] | 10 - 100       | 50 - 100   | kΩ   |

| R <sub>intDAT3</sub>   | eMMC internal DAT7- DAT0 pull-up resistor value                        |     | -              | 50 - 150   | kΩ   |

|                        | DAT3/CD (SD)                                                           |     | 10 - 90        | -          | kΩ   |

| L <sub>ch</sub>        | maximum signal line inductance                                         |     | 16             | 16         | nH   |

<sup>[1]</sup> except eMMC

### 5. Passive ESD protection and EMI filter devices

NXP Semiconductors offers a wide range of devices for the interface conditioning of the SD-memory card and/or MMC interface. The product range covers EMI filters and ESD protection devices, such as IP4252CZ12-6 or IP4252CZ16-8.

These devices can be also used for Serial Peripheral Interface (SPI)-based interface operation modes. In this case 4-channel devices can be used although this is not the preferred method of data exchange with SD-memory cards due to the lower speed and single bit access.

An overview is given in <u>Table 10</u> and a detailed description is given in the next chapters. These filter devices are available in leadless plastic packages (DFN) and Wafer Level Chip Size Packages (WLCSP).

### SD(HC)-memory card and MMC interface conditioning

Even though the MMC and SD-memory card specifications state exact minimum and maximum values for the various internal and external pull-up and pull-down resistors, a majority of implemented interfaces in available appliances do not follow these recommendations. This is especially true for the minimum CMD signal pull-up resistor value, which is often undercut to guarantee a sufficiently short rise time in an open-drain communication mode. The minimum values of the external pull-up resistor values of the MMC specification are also sometimes replaced by values from the SD-memory card specification range.

Therefore most NXP Semiconductors devices can be used in both interface applications, MMCs and SD-memory cards, even though data sheets are referring to just one interface type.

Modern memory cards typically support interfaces which are slightly out of the related general interface specification.

Table 10. SD-memory card and MMC interface devices overview

| Product name | Device type                                                               | Additional features    | Number<br>of filter<br>channels | Package type and size                                         |

|--------------|---------------------------------------------------------------------------|------------------------|---------------------------------|---------------------------------------------------------------|

|              | erface ESD protection and EMI filt<br>evel > 15 kV contact, far exceeding |                        |                                 |                                                               |

| IP4340CX15   | ESD protection and EMI filter                                             |                        | 6                               | CSP, 0.4 mm pitch $1.56 \times 1.56 \times 0.47 \text{ mm}^3$ |

| IP4350CX24   | ESD protection and EMI filter                                             | including<br>WP and CD | 6 (+5) <sup>[1]</sup>           | CSP, 0.4 mm pitch $2.01 \times 2.02 \times 0.61 \text{ mm}^3$ |

| IP4352CX24   | ESD protection and EMI filter                                             | including<br>WP and CD | 6 (+5) <sup>[1]</sup>           | CSP, 0.4 mm pitch<br>2.01 × 2.02 mm <sup>2</sup>              |

| IP4357CX17   | ESD protection and EMI filter                                             |                        |                                 | CSP, 0.4 mm pitch (staggered) $1.1 \times 2.4 \text{ mm}^2$   |

| •            | erface ESD protection and EMI filt<br>kV air discharge)                   | er devices, ESD pr     | otection level                  | according IEC61000-4-2, level 4                               |

| IP4252CZ8-4  | ESD protection and EMI filter                                             |                        | 4                               | DFN, 0.4 mm pitch<br>1.35 × 1.7 × 0.5 mm <sup>3</sup>         |

| IP4252CZ12-6 | ESD protection and EMI filter                                             |                        | 6                               | DFN, 0.4 mm pitch $1.35 \times 2.5 \times 0.5 \text{ mm}^3$   |

| IP4252CZ16-8 | ESD protection and EMI filter                                             |                        | 8                               | DFN, 0.4 mm pitch $1.35 \times 3.3 \times 0.5 \text{ mm}^3$   |

<sup>[1]</sup> Numbers in brackets represent additional channels such as pull-up and pull-down channels, WP and CD that are not required for the basic data communication.

#### SD(HC)-memory card and MMC interface conditioning

# 5.1 ESD protection EMI filter devices in plastic package IP4252CZ8-4, IP4252CZ12-6, IP4252CZ16-8

If pull-up resistors are integrated in the host interface, then ESD protection and EMI filtering devices such as IP4252 family are recommended. These devices are available in 4-, 6- and 8-channel versions: IP4252CZ8-4, IP4252CZ12-6 and IP4252CZ16-8.

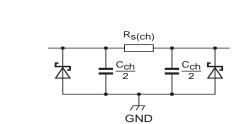

They all contain an RC-based pi-filter (also called Capacitor-Resistor-Capacitor (CRC) filter) consisting of two ESD protection diodes, acting as filter capacitors, and a serial channel resistor connected between the cathodes of these diodes.

Single filter channel schematic is shown in  $\underline{\text{Figure 5}}$  (left side) together with DFN plastic packages (right side). These packages have 0.4 mm contact pitch and 0.5 mm maximum package height.

b. IP4252CZ8-4, IP4252CZ12-6 and IP4252CZ16-8 package (top to bottom)

Fig 5. IP4252: schematic view and package photograph

Table 11. IP4252 parameters

| Symbol             | Parameter                                  | Conditions                                     | Min  | Тур | Max  | Unit |

|--------------------|--------------------------------------------|------------------------------------------------|------|-----|------|------|

| $V_{CC}$           | supply voltage                             |                                                | -0.5 | -   | +5.6 | V    |

| V <sub>ESD</sub>   | electrostatic<br>discharge voltage         | IEC 61000-4-2, level 4; all pins to ground     |      |     |      |      |

|                    |                                            | contact discharge                              | -8   | -   | +8   | kV   |

|                    |                                            | air discharge                                  | -15  | -   | +15  | kV   |

| R <sub>s(ch)</sub> | channel series resistance                  |                                                | 32   | 40  | 48   | Ω    |

| C <sub>ch</sub>    | channel capacitance $= 2*\frac{C_{ch}}{2}$ | $V_{bias(DC)} = 0 V,$<br>f = 100 kHz           | -    | 18  | -    | pF   |

|                    |                                            | $V_{bias(DC)} = 2.5 \text{ V},$<br>f = 100 kHz | -    | 12  | -    | pF   |

<sup>[1]</sup> Total channel capacitance is distributed between both ports of the channels, see  $\underline{\text{Figure 5}}$ .

Due to the integrated symmetrical pi-filter structure (often referred to as CRC structure) all NXP Semiconductors IP4252 devices offer a direction-independent and symmetrical ESD protection as well as a direction-independent and symmetrical EMI filter performance.

Integrated pi-filter structures provide very low ESD clamping voltage compared to single diode ESD protection implementations and/or devices.

AN10911

### SD(HC)-memory card and MMC interface conditioning

### 5.1.1 Application details of IP4252CZ12-6 and IP4252CZ16-8

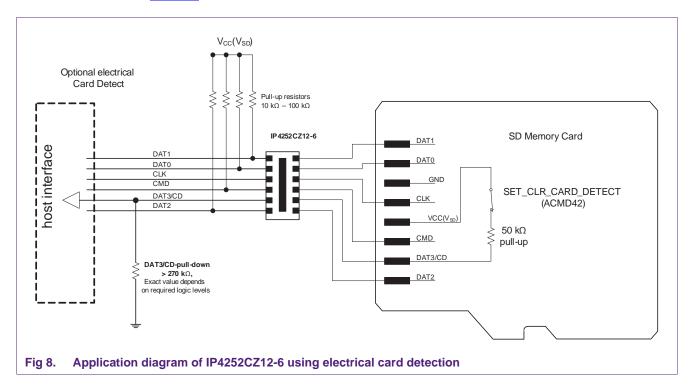

<u>Figure 6</u> shows a typical application of IP4252CZ12-6 and/or IP4252CZ16-8 in an SD-memory card interface including both options for card detection. The grey-colored components are optional and depend on the exact details of the interface implementation. Especially with respect to the card-detect mechanism, either using a mechanical switch in the card holder (preferred, see <u>Ref. 1</u>) or using integrated pull-up resistor at pin DAT3/CD in combination with selectable pull-down / pull-up resistors. The exact resistor values have to be aligned with all details described in <u>Ref. 1</u>.

This schematic does not include details concerning card-supply and typical power-supply decoupling capacitors.

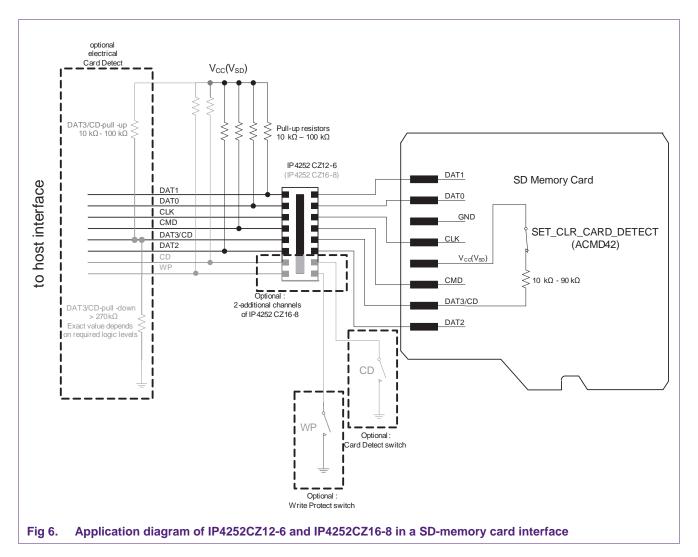

For the basic SD-memory card operation an IP4252CZ12-6 and 4 pull-up resistors (10  $k\Omega$  to 100  $k\Omega$ ) are sufficient for the digital data transmission from and to the SD-memory card. MMCs require higher pull-up resistor values starting at 50  $k\Omega$ . The card detection mechanism has to be implemented using a CD channel as shown in Figure 7, based on a mechanical card detection switch, in case SD-memory card and MMC are used with the same interface.

AN10911

### SD(HC)-memory card and MMC interface conditioning

The implementation of write protection contact is only possible in applications supporting standard-size SD-memory cards. Smaller form-factor versions such as miniSD or microSD do not support this feature. In case the mechanical slider mechanism of the standard-size SD-memory card is used, a pull-up resistor is connected to the host supply and a mechanical contact to ground. This contact is open until a WP slider is closing it (mechanical adaptors converting a micro or mini SD-memory card into a standard SD-card size typically do not support this feature).

In case a mechanical card detection switch is not possible to apply (for example, due to size constraints for the card holder), an electrical card detection can be used but only for an SD-memory card interface.

After power-up DAT3/CD is connected to a 50 k $\Omega$  (nominal value, specified range is 10 k $\Omega$  to 90 k $\Omega$ ) pull-up resistor inside the card. In case DAT3/CD is connected to a high-ohmic pull-down resistor, the connected host can detect a logic level change from low to high level<sup>1</sup>. The card internal pull-up resistor should be disconnected during regular data transmission with SET\_CLR\_CARD\_DETECT (ACMD42) command.

AN10911

All information provided in this document is subject to legal disclaimers.

It is recommended that pull-down resistor is >270 kΩ to fulfill the logic voltage level requirements. The exact value depends on the logic level requirements.

### SD(HC)-memory card and MMC interface conditioning

Figure 8 shows a diagram for this implementation.

For the latest 8-bit MMC interface, 10 channels have to be ESD-protected and EMI-filtered. A combination of IP4252CZ8-4 (4-channel) and IP4252CZ12-6 (6-channel) is best-matching filter combination to cover the full interface (see Figure 9).

AN10911

### SD(HC)-memory card and MMC interface conditioning

### 5.2 MicroSD card ESD protection and EMI filter device IP4340CX15

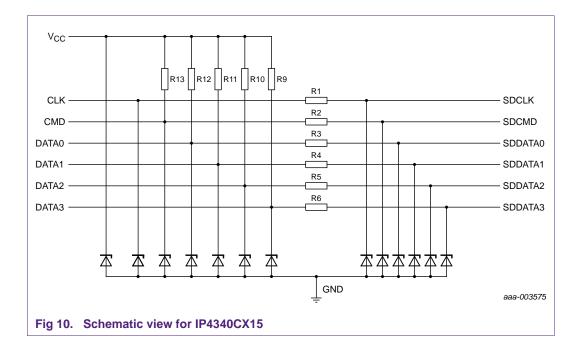

The IP4340CX15 is a 6-channel microSD card ESD protection and EMI filter device with 5 additionally integrated pull-up resistors in a tiny 0.4 mm ball pitch CSP.

The only channel without a pull-up resistor is the clock channel (see <u>Figure 10</u>). Due to the pull-up resistor implementation, the electrical card detection method cannot be used. Detection using a mechanical switch is mandatory.

The maximum filter channel capacitance is 14 pF which makes the device suitable to work in high clock speed applications, too.

Table 12. IP4340CX15 electrical parameters

| Symbol             | Parameter                          | Conditions                                                                                 | Min  | Тур | Max  | Unit |

|--------------------|------------------------------------|--------------------------------------------------------------------------------------------|------|-----|------|------|

| $V_{I}$            | input voltage                      |                                                                                            | -0.5 | -   | +5.0 | V    |

| V <sub>ESD</sub>   | electrostatic discharge<br>voltage | IEC 61000-4-2, level 4, pins on microSD card side                                          |      |     |      |      |

|                    |                                    | contact discharge                                                                          | -15  | -   | +15  | kV   |

|                    |                                    | air discharge                                                                              | -15  | -   | +15  | kV   |

| R <sub>s(ch)</sub> | channel series resistance          | R1 to R6                                                                                   | 36   | 40  | 44   | Ω    |

| R <sub>pu</sub>    | pull-up resistance                 | R9 to R12                                                                                  | 40   | 50  | 60   | kΩ   |

|                    |                                    | R13                                                                                        | 12   | 15  | 18   | kΩ   |

| C <sub>line</sub>  | line capacitance                   | including diode capacitance; $V_I = 0 \text{ V}; f = 1 \text{ MHz};$ $V_{CC} = \text{GND}$ | 8    | 11  | 14   | pF   |

### SD(HC)-memory card and MMC interface conditioning

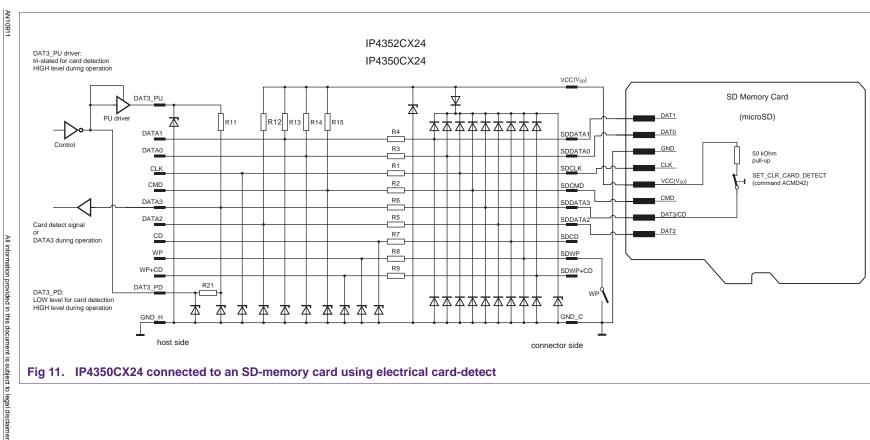

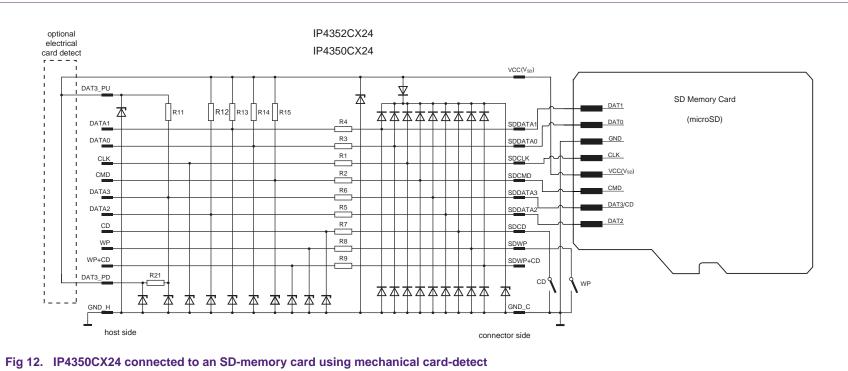

### 5.3 Very highly integrated memory card interface device IP4350CX24

The IP4350CX24 demonstrates the highest level of integration, consisting of ESD protection, EMI filter and biasing resistors in a passive device. As the package is a 0.4 mm pitch CSP type, the total device size is only  $1.95 \times 2.11 \text{ mm}^2$ .

This device fully supports high-speed memory card interfaces working with clock speed up to 52 MHz.

A special diode structure using a rail-to-rail (also known as "crow-bar") diode concept on the high-level ESD protection side in combination with single diodes on the low-level ESD protection side guarantee a balanced distribution of the channel capacitance. This leads to symmetrical EMI filter performance which is independent from the read/write direction.

IP4350CX24 supports electrical card detection of an SD-memory card using the pins DAT3\_PD and R21 connected to GND. Figure 11 shows detailed schematic with the driver and control circuitry required to use electrical card detection. Electrical card-detect is available as long as the "control" inverter output is low and 'driver\_pu' is 3-stated, so R21 is acting as a pull-down to GND.

If normal operation is needed, the "control" inverter drives a high signal to enable the 'driver \_pu' buffer, drives a high signal at R11 and also drives R21 to a high level to avoid any unnecessary quiescent current.

The maximum voltage at the pin to the host interface may exceed the host supply voltage as it is derived from:  $V_{SD} \times (R_{II}/(R_{II}+R_{DAT3/CDpu}))$  . In this case a voltage tolerant input has to be selected.

If electrical card detection is not required, DAT3\_PU (R11) should be connected to  $V_{SD}$  instead.

Since the CMD line is connected to the pull-up resistor R15, which is typically 15 k $\Omega$ , IP4350CX24 can also be used in combination with an MMC. The MMC can be initialized using a 400 kHz open-drain mode.

The channels for the mechanical WP, CD and the combined WP+CD require an additional pull-up resistor which is not integrated. Often pull-up resistors integrated into the GPIOs of the host processor are used for this purpose as they can be switched off after detection.

The lower CMD pull-up resistor value and lower total line capacitance value make the IP4350CX24 an excellent match for MMC interfaces in case a compliance with the latest standard specification is mandatory.

Three additional channels support any configuration of CD and WP switches for the various memory card holders (see Figure 11).

The most important electrical parameters are listed in Table 13.

### SD(HC)-memory card and MMC interface conditioning

Table 13. IP4350CX24 electrical parameters

| Symbol             | Parameter                          | Conditions                                                        | Min  | Тур | Max  | Unit |

|--------------------|------------------------------------|-------------------------------------------------------------------|------|-----|------|------|

| $V_{I}$            | input voltage                      |                                                                   | -0.5 | -   | +5.0 | V    |

| V <sub>ESD</sub>   | electrostatic discharge<br>voltage | IEC 61000-4-2, level 4<br>SDxxx pins to GND                       |      |     |      |      |

|                    |                                    | contact discharge                                                 | -8   | -   | +8   | kV   |

|                    |                                    | air discharge                                                     | -15  | -   | +15  | kV   |

| R <sub>s(ch)</sub> | channel series resistance          | R1 to R9                                                          | 12   | 15  | 18   | Ω    |

|                    |                                    | R11 to R14                                                        | 35   | 50  | 65   | kΩ   |

|                    |                                    | R15                                                               | 3.29 | 4.7 | 6.11 | kΩ   |

|                    |                                    | R21                                                               | 329  | 470 | 611  | kΩ   |

| C <sub>ch</sub>    | channel capacitance                | including diode capacitance;<br>V <sub>I</sub> = 0 V; f = 100 kHz |      |     |      |      |

|                    |                                    | each data channel from SD card to I/O interface                   | -    | 8.8 | -    | pF   |

|                    |                                    | CLK channel                                                       | -    | 7.8 | -    | pF   |

SD(HC)-memory card and MMC interface conditioning

NXP

Semiconductors

Fig 11. IP4350CX24 connected to an SD-memory card using electrical card-detect

SD(HC)-memory card and MMC interface conditioning

Rev. 2 -

4 April 2013

Application note

### SD(HC)-memory card and MMC interface conditioning

### 6. Conclusion

NXP Semiconductors offers a comprehensive portfolio of SD-memory card and MMC compatible interface conditioning and protection devices.

These devices are optimized for compliance with their respective memory card interface in terms of channel capacitance, serial resistance and biasing resistor values.

Passive devices explained in this document protect from destruction from system level ESD and also prevent disturbance of, for example wireless interfaces, from the harmonics of the digital memory interfaces. Integrated biasing resistors contribute to gain the maximum space savings comparing to discrete solutions.

All devices presented support a simple PCB layout, reduce the risk of EMI due to complex layout of scattered discrete components and allow to minimize compliance testing.

The high integration level and the final test of each device before shipment also improve the overall quality. The integrated protection and filter components reduce the number of individual components, solder joints and pick-and-place processes.

### 7. References

- [1] SD specifications, part 1, Physical Layer Specification version 2.00, May 9, 2006

- [2] Multi Media Card System Specification version 4.3, JESD84-A43, November 2007

### SD(HC)-memory card and MMC interface conditioning

### 8. Legal information

### 8.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 8.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

#### 8.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

AN10911 **NXP Semiconductors**

### SD(HC)-memory card and MMC interface conditioning

### **Contents**

| 1          | Introduction                                                   | 3  |

|------------|----------------------------------------------------------------|----|

| 2          | SD-memory card electrical interface                            | 4  |

| 2.1        | SD-memory card and microSD card interfaces                     | 4  |

| 2.2        | Bus operation conditions                                       |    |

| 2.3        | SD-memory card bus timing conditions                           | 8  |

| 2.4        | Capacitive load at the interface conditioning                  |    |

|            | device output                                                  |    |

| 2.5        | SD-memory card-detect mechanism                                |    |

| 3          | MMC electrical interface                                       | 11 |

| 3.1        | Bus operating conditions                                       | 11 |

| 3.2        | Bus timing conditions                                          | 13 |

| 3.3        | Capacitive load at the interface conditioning                  |    |

|            | device output                                                  | 13 |

| 4          | SD-memory card and MMC interface                               |    |

|            | comparison                                                     | 14 |

| 5          | Passive ESD protection and EMI filter                          |    |

|            | devices                                                        | 14 |

| 5.1        | ESD protection EMI filter devices in plastic                   |    |

|            | package IP4252CZ8-4, IP4252CZ12-6,                             |    |

|            | IP4252CZ16-8                                                   | 16 |

| 5.1.1      | Application details of IP4252CZ12-6 and                        |    |

| <b>5</b> 0 | IP4252CZ16-8                                                   | 17 |

| 5.2        | MicroSD card ESD protection and EMI filter                     | 20 |

| 5.3        |                                                                | 20 |

| 5.3        | Very highly integrated memory card interface device IP4350CX24 | 21 |

| •          |                                                                |    |

| 6          | Conclusion                                                     |    |

| 7          | References                                                     |    |

| 8          | 9                                                              | 26 |

| 8.1        | Definitions                                                    | _  |

| 8.2        | Disclaimers                                                    |    |

| 8.3        | Trademarks                                                     | 26 |

| 9          | Contents                                                       | 27 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

### **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

### NXP:

IP4052CX20/LF,135 IP4051CX11/LF,135