# Analog Signal Input Class-D Amplifier for Piezo Speaker with DC-DC Converter

#### ■ GENERAL DESCRIPTION

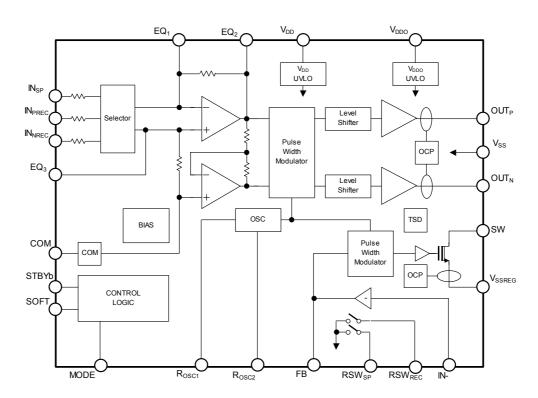

The NJW1263 is an analog signal input monaural class-D amplifier for Piezo speaker. And a built-in DC-DC converter generates variable output voltage (up to 20 V) with input voltage (3.0 to 4.2V).

The NJW1263 incorporates BTL amplifier, which eliminate AC coupling capacitors, and it is capable of driving Piezo speaker with simple external LC low-pass filters.

Class-D operation achieves lower power operation for Piezo speaker, thus the NJW1263 is suited for battery-powered applications.

#### FEATURES

- Output Voltage VDD=3.0V to 4.2V

VDD=3.0V to 4.2V

- VDDO=8.0 to 20.0V@SP MODE VDDO=4.5V@REC MODE

- Analog Audio Signal Input

- 2input selector (Speaker Mode and Receiver Mode)

- 1-channel BTL Output, Piezo Speaker Driving

- Built-in DC-DC Converter

- Built-in Low Voltage Detector

- Standby (Hi-Z), Soft Start, Soft Mute Control

- Built-in Pop noise reduction

- Built-in Short Protector)

- Built-in Thermal Protection

- Package Outline: WCSP42

#### BLOCK DIAGRAM

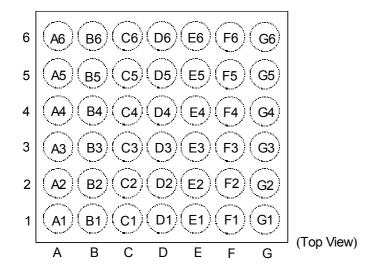

# PACKAGE OUTLINE

#### NJW1263WLC1

# ■ PIN CONFIGURATION

| No.                              | SYMBOL                    | I/O | 機能                                                                                                                                             |

|----------------------------------|---------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|

| A5                               | V <sub>DD</sub>           | -   | Power supply:V <sub>DD</sub> =3.7 V                                                                                                            |

| D5,D6                            | V <sub>DDO</sub>          | -   | Output Power supply:V <sub>DDO</sub> =8.0 to 20.0 V                                                                                            |

| F1                               | IN <sub>SP</sub>          | I   | Noninverted signal input (SP Mode) terminal                                                                                                    |

| G2                               | <b>IN</b> <sub>PREC</sub> | I   | Noninverted signal input (REC Mode) terminal                                                                                                   |

| G3                               | <b>IN<sub>NREC</sub></b>  | I   | Inversion signal Input (REC Mode)                                                                                                              |

| E1                               | EQ <sub>1</sub>           | I/O | LPF Setting terminal                                                                                                                           |

| E2                               | EQ <sub>2</sub>           | I/O | LPF Setting terminal                                                                                                                           |

| D1                               | $EQ_3$                    | I/O | LPF Setting terminal                                                                                                                           |

| G4                               | COM                       | I/O | Bias terminal                                                                                                                                  |

| C3                               | SOFT                      | I/O | Capacitor connection terminal for soft start                                                                                                   |

| F3                               | STBYb                     | 1   | Standby control terminal<br>(STBYb =L: Standby)                                                                                                |

| E3                               | MODE                      | 1   | SP/REC mode switch terminal<br>(MODE =H: SP Mode, MODE =L: REC Mode)<br>The mode maintains the logic when the STBYb terminal<br>is started up. |

| A4                               | R <sub>osc1</sub>         | I/O | Resistance connection terminal for Class-D Amp.                                                                                                |

| F2                               | R <sub>OSC2</sub>         | I/O | Resistance connection terminal for switching regulator                                                                                         |

| A2,B3,B5,B6,C4<br>D4,E4,F4,F5,F6 | V <sub>SS</sub>           | -   | GND:V <sub>SS</sub> =0 V                                                                                                                       |

| E5,E6                            | OUT <sub>P</sub>          | 0   | Noninverted signal output terminal                                                                                                             |

| C5,C6                            | OUT <sub>N</sub>          | 0   | Inversion signal output terminal                                                                                                               |

| A1,B1,B2                         | SW                        | 0   | Inductor connection terminal                                                                                                                   |

| C1,C2                            | V <sub>SSREG</sub>        | -   | GND:V <sub>SSREG</sub> =0 V                                                                                                                    |

| B4                               | IN-                       | I/O | Resistance connection terminal for DC/DC                                                                                                       |

| A3                               | FB                        | I/O | Phase compensating device connection terminal for switching regulator                                                                          |

| G5                               | RSW <sub>REC</sub>        | I/O | Resistance connection terminal to adjust DC/DC                                                                                                 |

| D2                               | RSW <sub>SP</sub>         | I/O | Resistance connection terminal to adjust DC/DC                                                                                                 |

| D3                               | TEST1                     | Ι   | Test Pin (50k $\Omega$ ground)<br>Should be floating or V <sub>SS</sub> fixation.                                                              |

| A6,G1,G6                         | NC                        | -   | NC pin Should be floating or $V_{SS}$ fixation.                                                                                                |

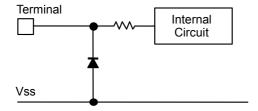

Note:  $V_{BAT} = V_{DD}$ Note: Do not do floating the input terminal.

#### ■ TERMINAL CONFIGURATION

#### **INPUT TERMINAL**

## ABSOLUTE MAXIMUM RATINGS

| (Ta=25°               |                                     |                                                                                                                            |                              |       |  |  |  |

|-----------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------|-------|--|--|--|

| PARAMETER             | SYMBOL                              | CONDITIONS                                                                                                                 | RATING                       | UNIT  |  |  |  |

| Supply Voltage        | V <sub>DD</sub><br>V <sub>DDO</sub> | V <sub>DD</sub><br>V <sub>DDO</sub>                                                                                        | -0.3 to +5.5<br>-0.3 to +36  | V     |  |  |  |

| Input Voltage         | V <sub>IN</sub>                     | IN <sub>SP</sub> , IN <sub>PREC</sub> , IN <sub>NREC</sub> ,<br>STBYb, IN-, RSW <sub>REC</sub> ,<br>RSW <sub>SP</sub> MODE | -0.3 to V <sub>DD</sub> +0.3 | V     |  |  |  |

| Operating Temperature | Topr                                |                                                                                                                            | -40 to +85                   | °C    |  |  |  |

| Storage Temperature   | Tstg                                |                                                                                                                            | -40 to +125                  | O°    |  |  |  |

| Power Dissipation     | P <sub>DMAX2</sub>                  | 2 layers (EIAJ), T <sub>i</sub> = 125°C                                                                                    | 610                          | mW    |  |  |  |

| Power Dissipation     | P <sub>DMAX4</sub>                  | 4 layers (EIAJ), T <sub>j</sub> = 125°C                                                                                    | 1200                         | mW    |  |  |  |

| Thermal resistance    | $\theta_{ja2}$                      | 2 layers (EIAJ), T <sub>i</sub> = 125°C                                                                                    | 164.5                        | °C /W |  |  |  |

| Thermai resistance    | $\theta_{ja4}$                      | 4 layers (EIAJ), T <sub>j</sub> = 125°C                                                                                    | 81.8                         | °C /W |  |  |  |

Note 1) All voltage are relative to " $V_{SS}$  =0V" reference.

Note 2) The LSI must be used within the "Absolute maximum ratings". Otherwise, a stress may cause permanent damage to the LSI. Mounted on 2-layer/ 4-layer board based on EIA/JEDEC

Note 3) The IC must be used inside of the "Absolute maximum ratings". Otherwise, a stress may cause permanent damage to the LSI.

Note 4) De-coupling capacitors must be connected between each power supply terminal and GND ( $V_{DD}$ - $V_{SS}$ ,  $V_{DDO}$ - $V_{SS}$ ).

Note 5) The maximum power dissipation in the system is calculated, as shown below.

$$P_{DMAX} = \frac{T_{jMAX} [°C] - T_a [°C]}{\theta_{ia} [°C/W]}$$

Pdmax: Maximum Power Dissipation, Tjmax: Junction Temperature =  $125^{\circ}C$ Ta: Ambient Temperature,  $\theta$ ja: Thermal Resistance of package =  $164.5^{\circ}C/W$

$$P_{D} = \frac{125 - 50}{164.5 / W} = 456 [mW]$$

Note 6 ) The W-CSP package must not be illuminated by light because the characteristic may be affected by the photoelectric effect.

# **ELECTRICAL CHARACTERISTICS**

#### • DC Characteristics

$\begin{array}{l} T_{a}=25\ ^{\circ}\text{C},\ V_{\text{DD}}=3.7\ \text{V},\ V_{\text{DDO}}=13.0\ \text{V}(\text{SP Mode: }R_{\text{SW}}=180\ \text{k}\Omega,\ R_{\text{SP}}=15\ \text{k}\Omega) \\ V_{\text{DDO}}=4.5\ \text{V}\ (\text{REC Mode: }R_{\text{SW}}=180\ \text{k}\Omega,\ R_{\text{REC}}=51\ \text{k}\Omega),\ V_{\text{SS}}=0.0\ \text{V},\ \text{Load Impedance}=1.5\ \mu\text{F} \\ R_{\text{OSC1}}=82\ \text{k}\Omega,\ R_{\text{OSC2}}=82\ \text{k}\Omega,\ C_{\text{LPF}}=330\ \text{pF},\ \text{Cc}=0.033\ \mu\text{F},\ \text{Output Filter: }[L_{\text{OUT}}=22\mu\text{H},\ R_{\text{DAMP}}=3.9\Omega] \\ \text{SW regulator: }[L_{\text{SW}}=6.8\mu\text{H},\ C_{\text{SW}}=20\mu\text{F}+0.1\mu\text{F},\ C_{\text{cmpn1}}=10\ \text{nF},\ C_{\text{cmpn2}}=33\ \text{pF},\ R_{\text{cmpn}}=33\ \text{k}\Omega] \\ \text{Input Signal: }IN_{\text{SP}}=100\ \text{mVrms},\ \text{IN}_{\text{PREC}}=IN0\ \text{mVrms},\ \text{Input Frequency}=1\ \text{kHz} \end{array}$

| PARAMETER                                                | SYMBOL              | CONDITIONS                                                                    | MIN. | TYP. | MAX. | UNIT |

|----------------------------------------------------------|---------------------|-------------------------------------------------------------------------------|------|------|------|------|

| $V_{DD}, V_{DDO}$ Supply Voltage                         | V <sub>DD</sub>     |                                                                               | 3.0  | 3.7  | 4.2  | V    |

|                                                          | V                   | SP Mode                                                                       | 8.0  | 13.0 | 20.0 | V    |

|                                                          | $V_{DDO}$           | REC Mode                                                                      | 4.2  | 4.5  | 4.8  | V    |

| Output Driver On-state<br>Resistance (High-side)         | R <sub>ONHSP</sub>  | SP Mode, $OUT_P$ , $OUT_N$<br>V <sub>OUTP, N</sub> = V <sub>DDO</sub> - 0.1 V | 1.3  | 2.0  | 2.4  | Ω    |

|                                                          | R <sub>ONHREC</sub> | REC Mode, $OUT_P$ , $OUT_N$<br>$V_{OUTP, N} = V_{DDO} - 0.1 V$                | 1.3  | 2.2  | 2.8  | Ω    |

| Output Driver On-state<br>Resistance (Low-side)          | R <sub>ONLSP</sub>  | SP Mode, $OUT_P$ , $OUT_N$<br>V <sub>OUTP, N</sub> = 0.1 V                    | 1.3  | 2.0  | 2.4  | Ω    |

|                                                          | R <sub>ONLREC</sub> | REC Mode, OUT <sub>P</sub> , OUT <sub>N</sub><br>V <sub>OUTP, N</sub> =0.1 V  | 1.3  | 2.2  | 2.8  | Ω    |

| Switching Regulator Output<br>Driver On-state Resistance | R <sub>ONSW</sub>   | SW<br>V <sub>SW</sub> = 0.1 V                                                 | 0.05 | 0.4  | 0.7  | Ω    |

| Input Impedance                                          | R <sub>INSP</sub>   | IN <sub>SP</sub>                                                              | 90   | 120  | 150  | kΩ   |

|                                                          | RINPREC             | IN <sub>PREC</sub>                                                            | 180  | 240  | 300  | kΩ   |

|                                                          | RINNREC             | IN <sub>NREC</sub>                                                            | 280  | 360  | 440  | kΩ   |

| Operating Current (Standby)                              | I <sub>ST</sub>     | STBYb: "L",No Load                                                            | -    | -    | 1    | μA   |

| Operating Current (No signal input)                      | I <sub>BATSP</sub>  | SP Mode,<br>Non-LC Filter, No Load                                            | -    | 13.0 | 16.5 | mA   |

|                                                          | IBATREC             | REC Mode<br>Non-LC Filter, No Load                                            | -    | 4.0  | 5.0  | mA   |

| PARAMETER                                    | SYMBOL             | CONDITIONS           | MIN. | TYP. | MAX.            | UNIT |

|----------------------------------------------|--------------------|----------------------|------|------|-----------------|------|

| Input Voltage                                | V <sub>IH</sub>    | STBYb,MODE Pin       | 1.5  | -    | V <sub>DD</sub> | V    |

|                                              | V <sub>IL</sub>    | STBYb,MODE Pin       | 0    | -    | 0.5             | V    |

| Input Leakage Current                        | I <sub>LK</sub>    | STBYb, MODE Pin      | -    | -    | ±1              | μA   |

| SW Off Leak Current                          | I <sub>LKSW</sub>  | SW Pin               | -    | -    | -               | μA   |

| OUT <sub>P</sub> Ground Resistance           | R <sub>OUTP</sub>  | OUT <sub>P</sub> Pin | 70   | 100  | 130             | kΩ   |

| OUT <sub>N</sub> Ground Resistance           | R <sub>OUTN</sub>  |                      | 70   | 100  | 130             | kΩ   |

| Class-D Amplifier<br>Oscillation Frequency   | f <sub>OSCD</sub>  |                      | 180  | 250  | 320             | kHz  |

| Switching Regulator<br>Oscillation Frequency | f <sub>OSCSW</sub> |                      | 500  | 600  | 750             | kHz  |

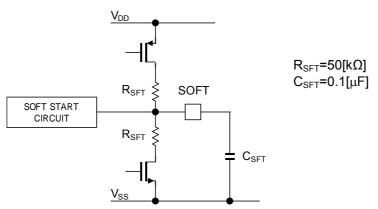

| Soft Start Resistance                        | R <sub>SST</sub>   | SOFT Pin             | 35   | 50   | 65              | kΩ   |

| Soft Mute Resistance                         | R <sub>SMT</sub>   | SOFT Pin             | 35   | 50   | 65              | kΩ   |

| Start-up Time                                | T <sub>ON</sub>    |                      | 5.0  | 6.7  | 8.4             | ms   |

| Stop Time                                    | T <sub>OFF</sub>   |                      | 10.0 | 13.3 | 16.6            | ms   |

| Class-D Amplifier Voltage Gain               | Av <sub>SP</sub>   | SP Mode, No Load     | -    | 27.6 | -               | dB   |

|                                              | AV <sub>REC</sub>  | REC Mode, No Load    | -    | 5.1  | -               | dB   |

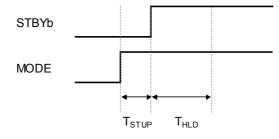

| MODE Setup Time                              | T <sub>STUP</sub>  | Refer to Figure 1.   | 10   | -    | -               | μS   |

| MODE Holding Time                            | T <sub>HLD</sub>   | Refer to Figure 1.   | 50   | -    | -               | μS   |

Figure 1: STBYb/MODE input timing

#### • AC Characteristics

$\begin{array}{l} \mathsf{T}_{a}=25\ ^{\circ}\text{C},\ \mathsf{V}_{\text{DD}}=3.7\ \mathsf{V},\ \mathsf{V}_{\text{DDO}}=13.0\ \mathsf{V}(\text{SP Mode: }\mathsf{R}_{\text{SW}}=180\ \text{k}\Omega,\ \mathsf{R}_{\text{SP}}=15\ \text{k}\Omega) \\ \mathsf{V}_{\text{DDO}}=4.5\ \mathsf{V}\ (\text{REC Mode: }\mathsf{R}_{\text{SW}}=180\ \text{k}\Omega,\ \mathsf{R}_{\text{REC}}=51\ \text{k}\Omega),\ \mathsf{V}_{\text{SS}}=0.0\ \text{V},\ \text{Load Impedance}=1.5\ \mu\text{F} \\ \mathsf{R}_{\text{OSC1}}=82\ \text{k}\Omega,\ \mathsf{R}_{\text{OSC2}}=82\ \text{k}\Omega,\ \mathsf{C}_{\text{LPF}}=330\ \text{pF},\ \text{Cc}=0.033\ \mu\text{F},\ \text{Output Filter: }[\mathsf{L}_{\text{OUT}}=22\mu\text{H},\ \mathsf{R}_{\text{DAMP}}=3.9\Omega] \\ \text{SW regulator: }[\mathsf{L}_{\text{SW}}=6.8\mu\text{H},\ \mathsf{C}_{\text{SW}}=20\mu\text{F}+0.1\mu\text{F},\ \mathsf{C}_{\text{cmpn1}}=10\ \text{nF},\ \mathsf{C}_{\text{cmpn2}}=33\ \text{pF},\ \mathsf{R}_{\text{cmpn}}=33\ \text{k}\Omega] \\ \text{Input Signal: }\mathsf{IN}_{\text{SP}}=100\ \text{mVrms},\ \mathsf{IN}_{\text{PREC}}=\mathsf{IN}_{\text{NREC}}=100\ \text{mVrms},\ \mathsf{Input Frequency}=1\ \text{kHz} \end{array}$

| PARAMETER              | SYMBOL               | CONDITIONS                                        | MIN. | TYP. | MAX. | UNIT     |

|------------------------|----------------------|---------------------------------------------------|------|------|------|----------|

| THD+N                  | THD+N <sub>SP</sub>  | SP Mode,<br>V <sub>OUTSP</sub> =3 Vrms            | -    | 0.1  | -    | %        |

|                        | THD+N <sub>REC</sub> | REC Mode<br>V <sub>OUTREC</sub> =1 Vrms           | -    | 0.05 | -    | %        |

| Maximum Output Voltage | V <sub>OUTSP</sub>   | SP Mode,<br>THD+N=1%                              | -    | 20   | -    | $V_{PP}$ |

|                        | V <sub>OUTREC</sub>  | REC Mode,<br>THD+N=1%                             | -    | 2.7  | -    | Vrms     |

| S/N                    | SN                   | REC MODE, A-weight<br>V <sub>OUTREC</sub> =1 Vrms | -    | 80   | -    | dB       |

| Noise Floor            | V <sub>N</sub>       | REC MODE, A-weight                                | -    | 100  | -    | μVrms    |

#### ■ FUNCTIONAL DESCRIPTION

Signal Input Terminal (IN<sub>SP</sub>, IN<sub>PREC</sub>, IN<sub>NREC</sub>) Analog signal input. The input signal is selected by the operational mode.

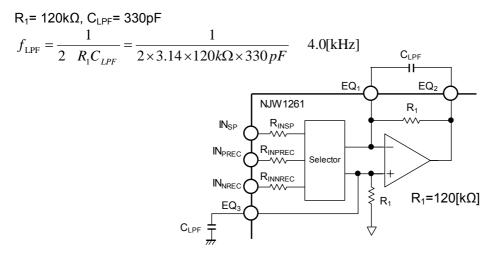

• Capacitor connection terminal for LPF (EQ1, EQ2, EQ3)

The amount of current passing through a capacitive load increases proportionately with frequency of audio signal. Input filters should be put in the input line to reduce load current at high frequency-band. The input low pass filters are composed of feedback resister ( $R_1$ ) and capacitor ( $C_{LPF}$ ).

Refer to the following expression.

Figure 2: Input LPF composition

### ● Signal Output Terminal (OUT<sub>P</sub>, OUT<sub>N</sub>)

The output signals are PWM signals, which will be converted to analog signal via external 2nd-order or higher LC filter. Should be connected to the damping resistor (R<sub>DAMP</sub>) between OUT<sub>P</sub> pin and coil, and between OUT<sub>N</sub> pin and coil to reduce the current consumption with signal-input close to cutoff-frequency of LPF (f<sub>c</sub>). Set the value of LOUT, CL, and RDAMP to become Q<1.

Refer to the following expression.

$L_{OUT}$  =22 $\mu$ H, C<sub>L</sub>=1.5 $\mu$ F, R<sub>DAMP</sub>=3.9 $\Omega$ , Equivalent direct resistance of L (R<sub>DCR</sub>) =0.5 $\Omega$

$$f_{\rm c} = \frac{1}{2 \sqrt{2L_{OUT}C_L}} = \frac{1}{2 \times 3.14 \times \sqrt{2 \times 22\,\mu H \times 1.5\,\mu F}} \qquad 19.6[\rm kHz]$$

$$Q = \frac{1}{R_{\rm DAMP} + R_{DCR}} \sqrt{\frac{L_{OUT}}{2C_L}} = \frac{1}{3.9 + 0.5} \times \sqrt{\frac{22\,\mu H}{2 \times 1.5\,\mu F}} \qquad 0.61$$

New Japan Radio Co., Ltd.

#### Standby Terminal (STBYb)

By setting the STBYb pin to "L" level, it switches the NJW1261 into standby condition. During the standby condition, output pins (OUT<sub>P</sub>, OUT<sub>N</sub>, SW) become high impedance and class-D amplifier output is connected with  $V_{SS}$  with about 100k $\Omega$ . Keep the STBYb pin to "L" level at least 13.3ms once switched into the standby condition. For normal operation, the STBYb pin requires "H" level. Time from the standby release to class-D power amplifier operation is 6.7ms(TYP). Do not change to the standby mode until the power amplifier operation. Set the standby mode at power supply ON/OFF.

Capacitor connection terminal for soft start (SOFT) Capacitor connection terminal for soft start and soft mute

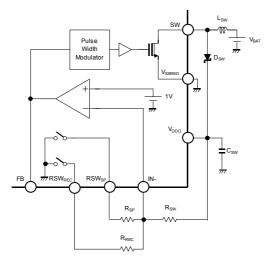

• Step-up switching regulator

The switching regulator is used as power supply  $(V_{DDO})$  for power amplifier of class-D. The PFM controlled switching regulator works with external components, which are coil, capacitor, Schottky barrier diode and step-up voltage setting resistance.

## Mode

SP/REC mode selection terminal. The output power-supply voltage, the input selector, and the voltage gain change when the mode is switched.

MODE="H":SP(Speaker)Mode Audio input terminal: IN<sub>SP</sub>(Shingle end input) Class-D amplifier output power-supply voltage: Step-up switching regulator

$$V_{SWSP} = 1.0V \times \left(1 + \frac{R_{SW}}{R_{SP}}\right)$$

$R_{SW}$  +  $R_{SP}$  = 100 Kohm to 1300 Kohm. Voltage gain: 27.6 dB (TYP)

MODE="L":REC(Receiver)Mode Audio input terminal: IN<sub>PREC</sub>, IN<sub>NREC</sub>(Difference input) Class-D amplifier output power-supply voltageStep-up switching regulator

$$V_{SWREC} = 1.0V \times \left(1 + \frac{R_{SW}}{R_{REC}}\right)$$

Set the 4.5V(TYP) DC/DC voltage by  $R_{SW}$  and  $R_{SP}$ . RSW + RSP = 100 Kohm to 1300 Kohm. Voltage gain: 5.1 dB (TYP)

#### Switching regulator circuit

Note) Set the Step-up switching regulator voltage within the range of the VDDO operation voltage. Note) Reset it when you switch MODE. (STBYb"L")

#### Low Voltage Detector

When the power-supply voltage drops down to below  $V_{DD}$ , the output driver is turned off output pins (OUT<sub>P</sub>, OUT<sub>N</sub>, SW) become high impedance and class-D amplifier output is connected with V<sub>SS</sub> with about 100k $\Omega$ .

#### Short Circuit Protection

The short-circuit protection circuit operates at the condition of the following.

- -Short between  $OUT_P$  and  $OUT_N$

- Power supply short and earth fault of OUT<sub>P</sub> terminal

- Power supply short and earth fault of  $OUT_N$  terminal

- Power supply short of SW terminal

When  $OUT_P$  and  $OUT_N$  of the short-circuit protection circuit operates, the  $OUT_P$  and  $OUT_N$  become high impedance and class-D amplifier output is connected with  $V_{SS}$  with about  $100k\Omega$ . It restarts by pulse-by-pulse of built-in clock of class-D amplifier.

When SW terminal of the short-circuit protection circuit operates, the SW terminal become high impedance and class-D amplifier output is connected with  $V_{SS}$  with about 100k $\Omega$ . It restarts by pulse-by-pulse of built-in clock of the switching regulator.

#### Note)

\*1 The detectable current and the period for the protection depend on the power supply voltage, chip temperature and ambient temperature.

\*2 The short protector is not effective for a long term short-circuit current but for an instantaneous accident. Continuous high current may cause permanent damage to the NJW1261.

#### Thermal protection

When the junction temperature is more than specified value, the output driver is turned off output pins (OUT<sub>P</sub>, OUT<sub>N</sub>, SW) become high impedance and class-D amplifier output is connected with  $V_{SS}$  with about 100k $\Omega$ . When the junction temperature is less than specified value, protection is released.

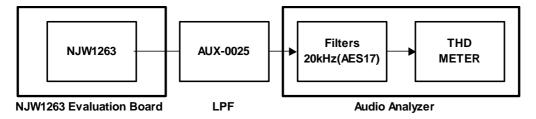

#### ■ TOTAL HARMONIC DISTORTION MEASUREMENT CIRCUIT

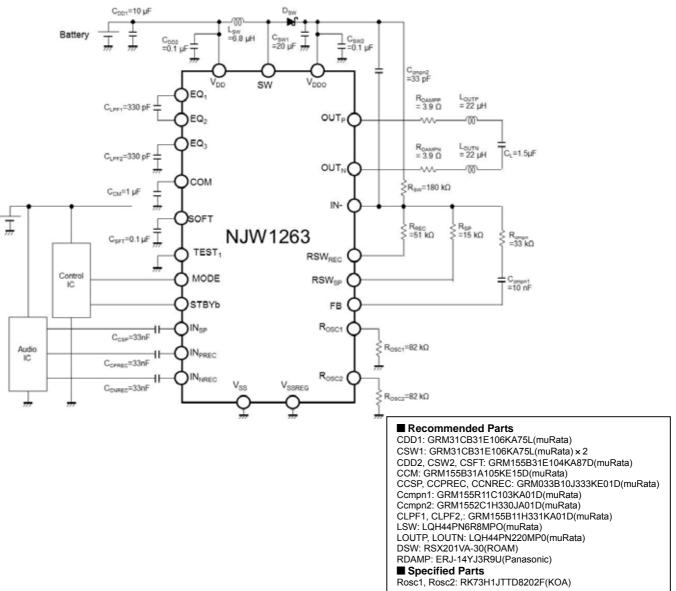

#### TYPICAL APPLICATION CIRCUIT

- Note) De-coupling capacitors must be connected between each power supply terminal and GND ( $V_{DD}$ - $V_{SS}$ ,  $V_{DDO}$ - $V_{SS}$ ).

- Note) V<sub>SS</sub> should be connected at a nearest point to the IC on PCB.

- Note)  $IN_{SP}$ ,  $IN_{PREC}$ ,  $IN_{NREC}$ ,  $EQ_1$ ,  $EQ_2$  and  $EQ_3$  should be not designed near  $OUT_POUT_N$  and SW, which emit PWM noise.

- Note) The transition time for MODE and STBYb signals must be less than  $100\mu s$ . Otherwise, a malfunction may be occurred.

- Note) The above circuit shows only application example and does not guarantee the any electrical characteristics. Therefore, please test the circuit carefully to fit your application.

- Note) RDAMP includes the resistance of the current limitation series of the piezoelectric element and the direct current resistance of coil LOUT. Decide the value of RDAMP considering the piezo and the value of the coil.

- Note) The speaker should be designed at a near the IC.

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.

New Japan Radio Co., Ltd.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

NJR: NJW1263WLC1-TE2