# VSC7416-01

## 7-Port Layer-2 Carrier Ethernet Switch with MPLS/ MPLS-TP Support and VeriTime

## INTRODUCTION

This document consists of descriptions and specifications for both functional and physical aspects of the VSC7416-01 device. It is intended for system designers and software developers.

In addition to the datasheet, Microchip maintains an extensive part-specific library of support and collateral materials that you may find useful in developing your own product. Depending upon the Microchip device, this library may include:

- Application notes that provide detailed descriptions of the use of the particular Microchip product to solve realworld problems

- White papers published by industry experts that provide ancillary and background information useful in developing products that take full advantage of Microchip product designs and capabilities

- · User guides that describe specific techniques for interfacing to the particular Microchip products

- Reference designs showing the Microchip device built in to applications in ways intended to exploit its relative strengths

- · Software Development Kits with sample commands and scripts

- Presentations highlighting the operational features and specifications of the device to assist in developing your own product road map

- Input/Output Buffer Information specification (IBIS) models to help you create and support the interfaces available on the particular Microchip product

Visit and register as a user on the Microchip Web site to keep abreast of the latest innovations from research and development teams and the most current product and application documentation. The address of the Microchip Web site is https://www.microchip.com/.

## **Register Notation**

This datasheet uses the following general register notation:

<TARGET>:<REGISTER\_GROUP>:<REGISTER>.<FIELD>

<REGISTER\_GROUP> is not always present. In that case, the following notation is used:

<TARGET>::<REGISTER>.<FIELD>

When a register group does exist, it is always prepended with a target in the notation.

In sections where only one register is discussed, or the target (and register group) is known from the context, the <TARGET>:<REGISTER\_GROUP>: may be omitted for brevity, and uses the following notation:

```

<REGISTER>.<FIELD>

```

Also, when a register contains only one field, the .<FIELD> is not included in the notation.

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## Contents

| Intro | duction                          | 1     |

|-------|----------------------------------|-------|

| 1.0   | Product Overview                 | 5     |

|       | 1.1 General Features             | 5     |

|       | 1.2 Applications                 | 8     |

|       | 1.3 Functional Overview          |       |

| 2.0   | Functional Descriptions          |       |

|       | 2.1 Port Modules                 |       |

|       | 2.2 SERDES1G                     |       |

|       | 2.3 SERDES6G                     |       |

|       | 2.4 Statistics                   |       |

|       | 2.5 MPLS-TP Classifier           |       |

|       | 2.6 Basic Classifier             |       |

|       | 2.7 VCAP                         |       |

|       | 2.8 Analyzer                     |       |

|       | 2.9 Policers                     |       |

|       | 2.10 Shared Queue System         |       |

|       | 2.11Scheduler and Shapers        |       |

|       | 2.12Rewriter                     |       |

|       | 2.13Versatile OAM Processor      |       |

|       | 2.14CPU Port Module              |       |

|       | 2.14CPO Port Module              |       |

|       |                                  |       |

|       | 2.16Layer-1 Timing               |       |

|       | 2.17Hardware Timestamping        |       |

| ~ ~   | 2.18Clocking and Reset           |       |

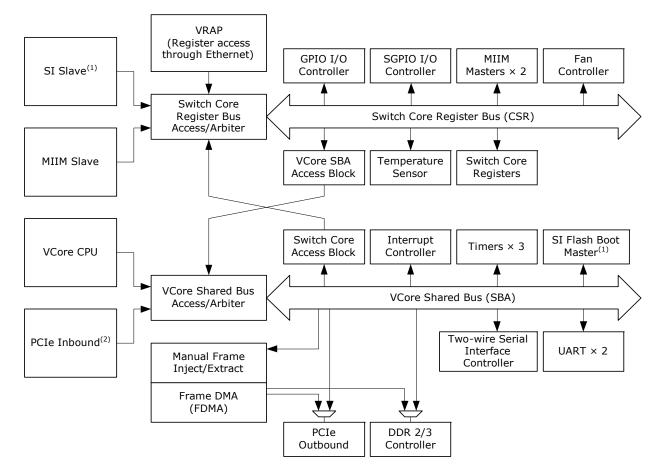

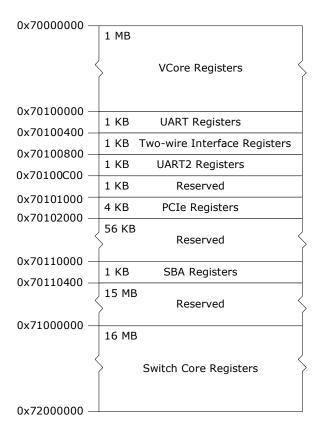

| 3.0   | VCore System and CPU Interfaces  |       |

|       | 3.1 VCore Configurations         |       |

|       | 3.2 Clocking and Reset           |       |

|       | 3.3 Shared Bus                   |       |

|       | 3.4 VCore CPU                    |       |

|       | 3.5 External CPU Support         |       |

|       | 3.6 PCIe Endpoint Controller     |       |

|       | 3.7 Frame DMA                    |       |

|       | 3.8 VCore System Peripherals     |       |

| 4.0   | Features                         |       |

|       | 4.1 Switch Control               |       |

|       | 4.2 Port Module Control          |       |

|       | 4.3 Layer-2 Switch               |       |

|       | 4.4 IGMP and MLD Snooping        | . 298 |

|       | 4.5 Quality of Service (QoS)     | . 299 |

|       | 4.6 VCAP Applications            | . 302 |

|       | 4.7 CPU Extraction and Injection | . 309 |

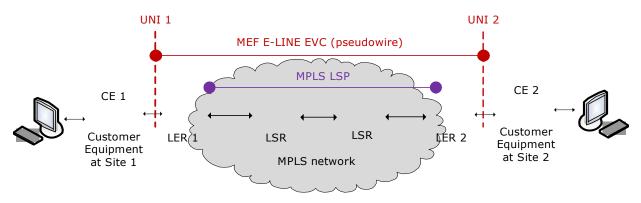

|       | 4.8 MPLS Operation               | . 312 |

|       | 4.9 Ethernet over MPLS Service   | . 312 |

| 5.0   | Registers                        |       |

|       | 5.1 ANA                          | . 321 |

|       | 5.2 DEV                          |       |

|       | 5.3 DEVCPU GCB                   |       |

|       | 5.4 DEVCPU ORG                   |       |

|       | 5.5 DEVCPU_QS                    |       |

|       | 5.6 HSIO                         |       |

|       | 5.7 ICPU CFG                     |       |

|       | 5.8 VCAP CORE                    |       |

|       | 5.8 VCAP_CORE                    |       |

|       | 5.9 OAM_MEP                      |       |

|       |                                  |       |

|       | 5.11QSYS                         | . 551 |

| 5.12REW                              | 569   |

|--------------------------------------|-------|

| 5.13SBA                              |       |

| 5.14SYS                              |       |

| 5.15TWI                              |       |

| 5.16UART                             |       |

| 6.0 Electrical Specifications        |       |

| 6.1 DC Characteristics               |       |

| 6.2 AC Characteristics               |       |

| 6.3 Current and Power Consumption    |       |

| 6.4 Operating Conditions             |       |

| 6.5 Stress Ratings                   |       |

| 7.0 Pin Descriptions                 |       |

| 7.1 Pin Diagram                      |       |

| 7.2 Pins by Function                 | 645   |

| 7.3 Pins by Number                   | . 652 |

| 7.4 Pins by Name                     | . 655 |

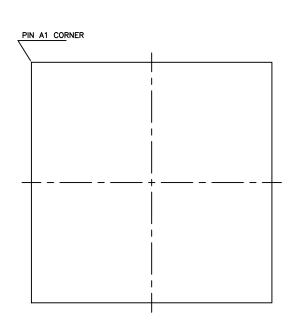

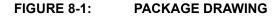

| 8.0 Package Information              | . 658 |

| 8.1 Package Drawing                  | . 658 |

| 8.2 Thermal Specifications           | . 660 |

| 8.3 Moisture Sensitivity             | . 660 |

| 9.0 Design Guidelines                | . 661 |

| 9.1 Power Supplies                   | 661   |

| 9.2 Power Supply Decoupling          | . 661 |

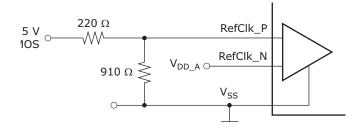

| 9.3 Reference Clock                  |       |

| 9.4 Interfaces                       | . 662 |

| 10.0 Ordering Information            | . 667 |

| 11.0 Design Considerations           | . 668 |

| Appendix A: Revision History         | . 670 |

| The Microchip WebSite                | . 671 |

| Customer Change Notification Service | . 671 |

| Customer Support                     | . 671 |

## 1.0 PRODUCT OVERVIEW

The VSC7416-01 Carrier Ethernet switch contains four 10/100/1000 Mbps SGMII/SerDes Ethernet ports, two 10/100/ 1000/2500 Mbps SGMII/SerDes ports, and one 10/100/1000 Mbps SGMII/SerDes Node Processor Interface (NPI) Ethernet port. The NPI port can operate as a 5<sup>th</sup> triple-speed Ethernet port. The device provides a rich set of Carrier Ethernet switching features such as MPLS-TP, MEF Ethernet services, hierarchical QoS scheduling, provider bridging, protection switching, OAM, 1588 precision time protocol, and synchronous Ethernet. Advanced TCAM-based service, VLAN, and QoS processing enable delivery of differentiated services with per-service SLA guarantees. Security is assured through frame processing using a TCAM-based Microchip Content Aware Processor (VCAP). In addition, the device contains a powerful 416 MHz CPU enabling full management of the switch.

## 1.1 General Features

- 4× 1G Ethernet ports, which are tri-speed 10/100/1000 Mbps ports

- 2× 2.5G Ethernet ports, which are quad-speed 10/100/1000/2500 Mbps ports

- 1× 1G Node Processor Interface Ethernet port, which is a tri-speed 10/100/1000 Mbps port

- All ports support both 100-BASE-FX and 1000-BASE-X-SERDES

- · Eight megabits of integrated shared packet memory

- Fully nonblocking wire-speed switching performance with weighted random early detection (WRED) for all frame sizes

- · Eight QoS classes with 2616 queues that can be assigned to ports, QoS classes, and services

- 330 dual leaky bucket policers, per service, per QoS class, and per port

- · 64 dual leaky bucket policers, flow-based through TCAM matching

- Hierarchical QoS scheduling with up to three levels of scheduling

- 256 scheduling elements, each with a DWRR/strict priority scheduler and a dual leaky bucket shaper. All combinations of DWRR vs. strict scheduling between QoS classes, services or ingress ports are possible.

- MPLS-TP LER (Ethernet pseudo-wires) and LSR with up to 128 unidirectional label switched paths and up to 128 bidirectional Ethernet pseudowires

- · Up to 1024 TCAM-based classification entries for service, Quality of Service (QoS) and VLAN membership

- · Up to 1024 host identity entries for source IP guarding

- · Up to 512 TCAM-based security enforcement entries

- Up to 1024 TCAM-based egress tagging and MPLS label stack entries

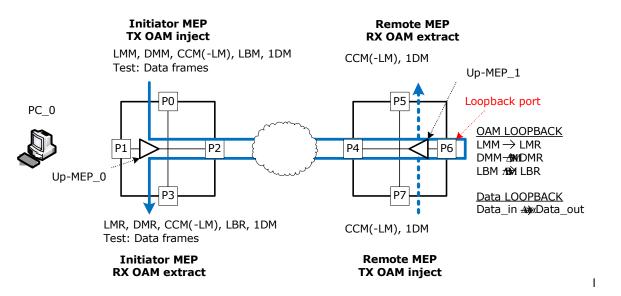

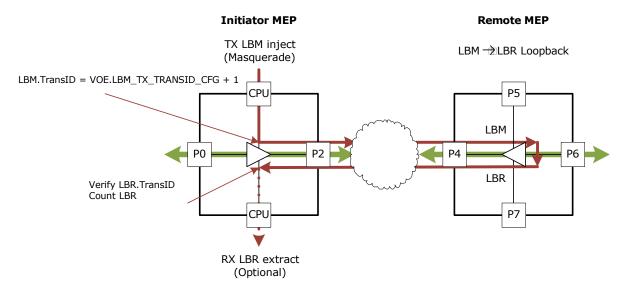

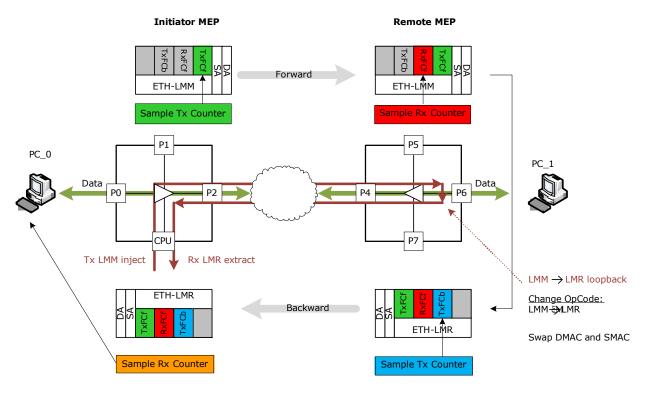

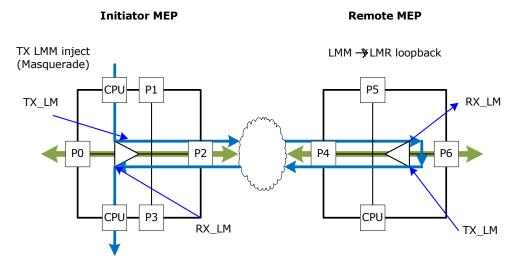

- · OAM Up and Down-MEP support for CCM, loss measurements, delay measurements, and loopback

- · Service Activation Test frames generation and checking

- L1 Synchronous Ethernet

- VeriTime—Microchip's patent-pending distributed timing technology that delivers the industry's most accurate IEEE 1588v2 timing implementation for both one-step and two-step clocks

- Energy Efficient Ethernet (IEEE 802.3az) supported by the switch core

- VCore-III CPU system with integrated 416 MHz MIPS 24KEc™ CPU with MMU and DDR3 SDRAM controller

- PCIe 1.x CPU interface

## 1.1.1 LAYER 2 SWITCHING

- 8,192 MAC addresses

- 4,096 VLANs (IEEE 802.1Q)

- · Push/pop/translate up to two VLAN tags; translation on ingress and/or on egress

- TCAM-based VLAN classification and translation with pattern matching against Layer 2 through Layer 4 information such as MAC addresses, VLAN tag headers, EtherType, DSCP, IP addresses, and TCP/UDP ports and ranges

- Up to 1024 QoS and VLAN TCAM entries

- Up to 1024 VLAN egress tagging TCAM entries

- Link aggregation (IEEE 802.3ad)

- Link aggregation traffic distribution is programmable and based on Layer 2 through Layer 4 information

- · Wire-speed hardware-based learning and CPU-based learning configurable per port

- · Independent and shared VLAN learning

## VSC7416-01

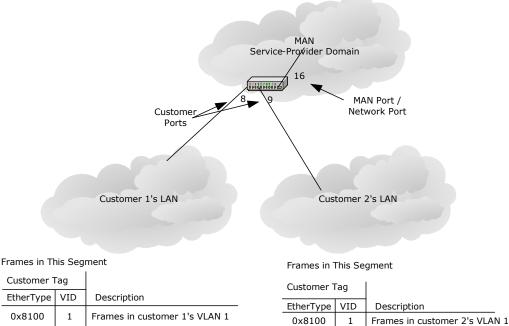

- Provider Bridging (VLAN Q-in-Q) support (IEEE 802.1ad)

- Rapid Spanning Tree Protocol support (IEEE 802.1w)

- Multiple Spanning Tree Protocol support (IEEE 802.1s)

- · Jumbo frame support up to 10 kilobytes (kB) with programmable MTU per port

## 1.1.2 LAYER 2 MULTICAST

- Up to 8,192 Layer 2 multicast groups with up to 64 port masks

- Up to 8,192 IPv4/IPv6 (G) multicast groups and port masks

- Up to 8,192 IPv4/IPv6 (S, G) multicast groups and port masks with up to 512 unique sources

- Internet Group Management Protocol version 2 (IGMPv2) support

- · Internet Group Management Protocol version 3 (IGMPv3) support with source specific multicast forwarding

- Multicast Listener Discovery (MLDv1) support

- Multicast Listener Discovery (MLDv2) support with source specific forwarding

## 1.1.3 CARRIER ETHERNET

• Provider Bridge (Q-in-Q) switch

8K MACs, 4K VLANs

• MPLS-TP switch

Label Edge Router (LER) with Ethernet pseudo-wires

Label Switch Router (LSR)

H-VPLS MTU-s (H-VPLS edge) functions

MPLS-TP forwarding in a Ethernet-based ring, where the Ethernet layer supports Drop and Continue

MPLS-TP Point-to-Multipoint (P2MP)

32 MPLS Link Layers, each defined by destination and source MAC address, and up to one VLAN tag

128 uni-directional Label Switched Paths (LSPs), each path defined by up to three labels

Extract LSP OAM frames to CPU (GAL)

128 Ethernet pseudo-wires (PWE)

Switched Provider Edge (S-PE; multisegment pseudo-wire)

Terminating Provider Edge (T-PE)

Extract PW OAM frames to CPU (GAL, VCCV1, VCCV2, VCCV3) • 256 MEF E-LAN, E-LINE, E-TREE service points

128 bidirectional E-LINEs or 64 E-LANs/E-TREEs each with four ports

256 dual leaky bucket service policers

PCP and DSCP remarking per service point

Statistics and tagging options per service point

Versatile OAM processor (VOP) with hardware for generating and checking CCM messages, frame delay measurements, loss measurements, and loopback

Down MEP support for 7 ports

Up-MEP and Down-MEP support for 16 paths and services

• Hardware-assisted linear protection (ITU-T G.8031) and ring protection (ITU-T G.8032)

Service, path and port protection with few milliseconds restoration time

- Fully hardware-supported CCM frame generation and checking with sub-millisecond CCM intervals.

- L1 Synchronous Ethernet with up to 10 recovered clock outputs

- L2 IEEE 1588 timestamping hardware, with one-step and two-step clock support

Independent clock domains for data path forwarding (L1 Sync Ethernet) and timing (IEEE 1588)

Nanosecond precision timestamping

Asymmetry correction support in hardware

IEEE 1588 over MPLS-TP and IP/MPLS support

Enhanced Carrier Ethernet software API

## 1.1.4 QUALITY OF SERVICE

- Eight QoS classes and two drop precedence levels

- Strict, deficit weighted round-robin (DWRR), or frame based round-robin (FBRR) scheduling

- TCAM-based QoS classification with pattern matching against Layer 2 through Layer 4 information

- · Up to 1024 QoS and VLAN TCAM entries

- · DSCP translation, both ingress and/or egress

- DSCP remarking based on QoS class and drop precedence level

- VLAN (PCP, DEI, and VID) translation, both ingress and egress

- PCP and DEI remarking based on QoS class and drop precedence level

- 392 policers, selectable per QoS class per port, per port, per service point, and per security entry through TCAMbased pattern matching, programmable in steps of 33.3 kbps

- Three-level hierarchical QoS scheduling (QoS classes, services, ingress ports, or service groups) with 256 dual leaky bucket shapers and DWRR/FBRR/strict scheduling

- Full-duplex flow control (IEEE 802.3X) and half-duplex backpressure, symmetric and asymmetric

- · Priority-based full-duplex flow control (IEEE 802.1Qbb)

## 1.1.5 SECURITY

Versatile Content Aware Processor (VCAP) packet filtering engine using ACLs for ingress and egress packet inspection:

Up to 512security VCAP entries

Up to 1024 source IP guarding entries

64 shared VCAP rate policers with rate measurements in frames per second or bits per second

Eight shared range checkers supporting ranges based on TCP/UDP port numbers, DSCP values, and VLAN identifiers

VCAP match patterns supporting generic MAC, ARP, IPv4, and IPv6 protocols

VCAP actions including permit/deny, police, count, CPU-copy, and mirror

Special support for IP fragments, UDP/TCP port ranges, and ARP sanity check

Extensive CPU DoS prevention by VCAP rate policers and hit-me-once functions

Surveillance functions supported by 32-bit VCAP counters

• Generic storm controllers for flooded broadcast, flooded multicast, and flooded unicast traffic

## VSC7416-01

- · Selectable CPU extraction queues for segregation of CPU redirected traffic, with 8 extraction queues supported

- Per-port, per-address registration for copying/redirecting/discarding of reserved IEEE MAC addresses (BPDU, GARP, CCM/Link trace)

- · Port-based and MAC-based access control (IEEE 802.1X)

- Per-port CPU-based learning with option for secure CPU-based learning

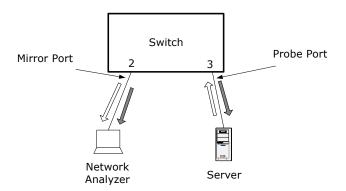

- Per-port ingress and egress mirroring

- Mirroring per VLAN and per VCAP match

## 1.1.6 MANAGEMENT

- MIPS 24KEc<sup>™</sup> CPU system with memory management unit (MMU), and 32 kilobytes of instruction cache (lcache) and 32 kilobytes of data cache (D-cache)

- PCIe 1.x enabling frame injection/extraction and register access from external CPU

- CPU frame extraction (eight queues) and injection (two queues) through DMA, which enables efficient data transfer between Ethernet ports and CPU/PCIe

- · EJTAG debug interface

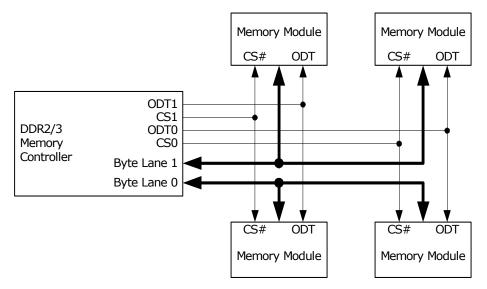

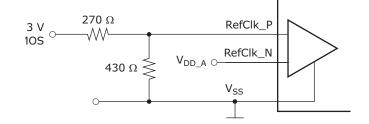

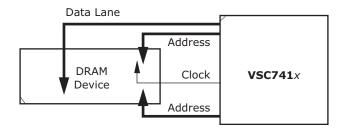

- · Configurable 16-bit or 8-bit DDR2/3 SDRAM interface supporting up to one gigabyte (GB) of memory

- Thirty-two pin-shared general-purpose I/Os

Serial GPIO and LED controller controlling up to 32 ports with four LEDs each

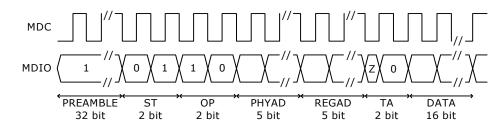

Dual PHY management controller (MIIM)

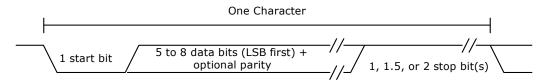

Dual UART

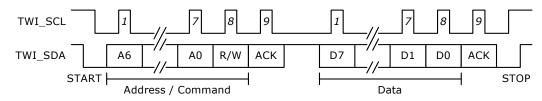

Built-in two wire serial interface multiplexer

External interrupts

1588 synchronization I/Os

SFP loss of signal inputs

- External access to registers through PCIe, SPI, MIIM, or through an Ethernet port with inline Versatile Register Access Protocol

- Per-port 32-bit counter set with support for the RMON statistics group (RFC 2819) and SNMP interfaces group (RFC 2863)

- Support CPU models with internal CPU only, external CPU only, or dual CPU

## 1.2 Applications

VSC7416-01's target applications are:

- Microwave Backhaul (ODU/IDU) and all-integrated ODU

- Network Interface Devices (NID) and Ethernet Access Devices (EAD)

- Ethernet/MPLS demarcation

- Customer Premise Equipment (CPE) and Business VPN service Equipment

- Fiber Backhaul Equipment

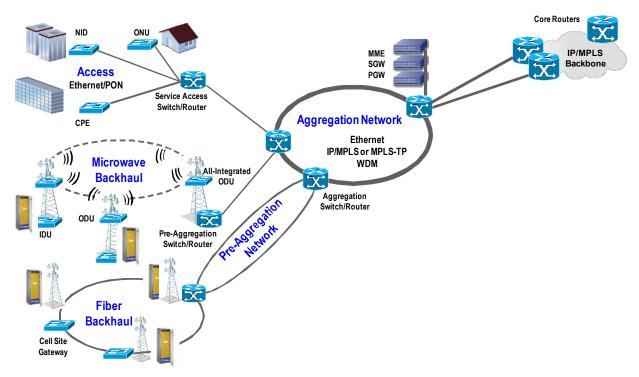

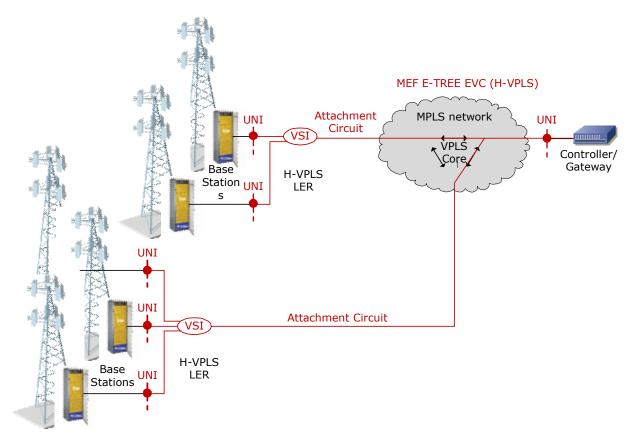

The following illustration shows the target applications in an access and aggregation network.

## FIGURE 1-1: ACCESS AND AGGREGATION NETWORK

VSC7416-01 provides the required set of User to Network Interface (UNI) and Network to Network Interface (NNI) features in a cost-effective manner:

Maps Customer frame formats into Provider frame formats

Classifies frames and map to appropriate QoS profiles

Applies Provider Bridge (Q-in-Q) encapsulations

Applies MPLS pseudowire, MPLS Label stack, and MPLS Link-Layer Ethernet encapsulations • Meters the customer traffic and ensures that the customer Service Level Agreement (SLA) is met

Polices using MEF-defined Dual Leaky Bucket algorithm

Marks frames as Committed (Green) or Discard Eligible (Yellow)

Provides correct QoS treatment (traffic management)

Provides traffic statistics per customer in a manner consistent with the SLA

Shapes using MEF-defined Dual Leaky Bucket shaping algorithm

- · Enables end-to-end Service OAM by the customer

- · Implements the service as defined by the SLA

E-LINE for point-point or backhaul services

E-LAN for multipoint/bridged services

E-TREE for video distribution or backhaul services

· Enables management and protection schemes as required by the Provider

Link aggregation or other port protection schemes if used for access

OAM at the Operator and Service Provider levels for remote management, fault diagnosis, and protection switching

• Supports network timing and synchronization requirement

Synchronous Ethernet and IEEE 1588 functionality

## 1.2.1 NETWORK INTERFACE DEVICE, ETHERNET ACCESS DEVICE

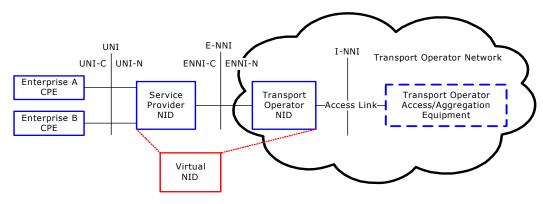

The following illustration is an example of how an Enterprise VPN service can be provided through an access and aggregation network. Enterprise VPN services provide connectivity between corporate headquarters and branch offices, as well as providing voice, video, internet, storage, and other network-hosted applications.

The example in the illustration shows one operator (the "Service Provider") who sells services directly to the Enterprise, and a second operator (the "transport operator") who sells local access to the Service Provider for a location where the Service Provider does not have direct access to the customer's corporate office.

In general, NIDs provide demarcation between a Customer and a Network. In this example, one NID interfaces between the Service Provider (the Network) and the Enterprise customer (the Customer). A second NID interfaces between the Transport Operator (the Network for NID) and the Service Provider (the Customer for this NID).

The NIDs are located at the customer site. One NID is owned/managed by the Service Provider, the second by the Transport Operator. This two-box model is prevalent, but a one-box Virtual NID concept is emerging, as shown in red. In the Virtual NID concept, the Transport Operator owns the NID but there are separate management domains for each operator.

## FIGURE 1-2: NID APPLICATION

Transport Operator Networks predominantly uses Provider Bridging (Q-in-Q) and/or MPLS-TP technology for backhauling customer traffic further into the network.

The CPE and NIDs shown in this example would likely have a relatively low port count and bandwidth. It is also possible to have CPE and NIDs with many customer-facing ports and perhaps two network-facing ports.

Very limited switching and networking functionality is present in these devices, because their purpose is simply to isolate customers from one another and from the network and allow the network operator to monitor and manage the customers' traffic.

For NID and Virtual NID applications, VSC7416-01 provides the following features.

- Highly flexible classification, tagging and encapsulation for Provider Bridges (Q-Q), MPLS pseudowires and MPLS-TP transport.

- · Fully-featured Ethernet-based OAM. Hardware OAM implementation is required for precision and scale.

- At the UNI-C and ENNI-C, MEF-compliant DLB shaping and Down-MEP functions. Down-MEP allows the Customer to monitor the service purchased from the Network.

- At the UNI-N and ENNI-N, MEF-compliant DLB policing and Up-MEP functions. Up-MEP functions allow the network to monitor the service sold to the customer. In the virtual NID model, the ENNI is an internal interface to the device.

- At the UNI-C and ENNI-C some applications require per-service queuing for separation.

- · Per-service and color statistics both ingress, discarded and egress.

- · Service Activation Measurements.

- IEEE-1588 network timing functions.

- Linear and Ring protection mechanisms as well as path and port protection for dual-homed NID and EAD installations.

- · Integrated CPU sub-system for management and control.

## 1.2.2 OUTDOOR UNIT FOR MICROWAVE BACKHAUL

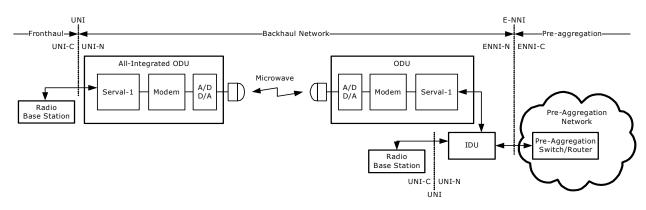

Both traditional ODUs for split-mount and all integrated ODUs for 4G/LTE equipment are target applications for the VSC7416-01 Carrier Ethernet switch. The following illustration shows a split-mount IDU and ODU installation to the right, and an all-integrated Outdoor Unit is shown to the left. In some larger installations, the Radio Base Station and the all-integrated ODU functionality (shown to the left) is built into a single piece of equipment. In the illustration, the three networks (fronthaul, backhaul, and pre-aggregation) are all operated by separate network providers. The backhaul network provides a transport service between the radio base station and the pre-aggregation network. Other models of network ownership are possible. VSC7416-01 supports UNI, I-NNI, and E-NNI functions as defined by Metro Ethernet Forum to support all of these models. Only one microwave link is shown in the following illustration, however, applications with multiple microwave interfaces exist supporting link aggregation and protection, as well as ring and mesh network topologies.

## FIGURE 1-3: ODU AND IDU APPLICATIONS

Microwave radio links are highly susceptible to weather and use adaptive modulation techniques to deliver data reliably during bad weather. As a result, the microwave data transfer rate (link speed) can change rapidly creating jitter problems for IEEE 1588 and QoS problems for the networking gear. The link speed is also limited to a few hundred Mbps per microwave link under good weather conditions, so link bundling and load balancing are common. Next generation ODUs must support timing and synchronization such as synchronous Ethernet and IEEE 1588 packet-based timing.

Small IDUs (pizzaboxes) generally supports a carrier Ethernet feature set similar to the NID devices previously described. In addition, IDU functionality can include MPLS-TP functionality.

Integrated ODU/IDU equipment also exists, especially for 4G/LTE femtocell deployment. These units will likely have a low port count but advanced features such as MPLS-TP, protection switching mechanisms, and strong QoS.

VSC7416-01 supports the following key features for the Microwave-based Mobile Backhaul application.

- · Low size, low cost, and low power, especially for the ODUs.

- Ethernet and MPLS-TP carrier features at the IDUs and all-integrated ODUs.

- UNI/NNI and Ethernet OAM as previously described for NIDs.

- IEEE-1588 functionality is critical to deliver timing to Base Stations as required for 4G/LTE networks. Various proprietary techniques are supported by VSC7416-01 for combating the jitter created by adaptive modulation on the microwave link.VSC7416-01 supports different methods to provide IEEE 1588 transparent clock over a microwave link.

- Strong QoS is required. QoS may be statically configured to handle the varying link speed. 802.1Qbb prioritybased flow control may be used as in-band dynamic flow control. Versatile Register Access Protocol (VRAP) can also be used as in-band dynamic scheduler/shaper rate adjustment. Hierarchical queuing can also be helpful for customer separation in IDUs and all-integrated ODUs.

- · Linear and Ring protection mechanisms

## VSC7416-01

- Due to the microwave link being throttled frequently, a larger buffer memory and advanced congestion avoidance mechanisms are required to efficiently utilize bandwidth when available, while not jeopardizing low latency traffic such as voice. VSC7416-01 has a large amount of integrated memory, supports WRED and advanced scheduling and shaping. External packet memory may be required in some applications.

- · Industrial temperature.

## 1.2.3 CARRIER ETHERNET SWITCH WITH MPLS-TP

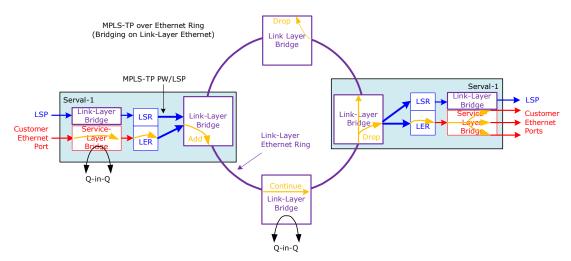

The following illustration is an example where VSC7416-01 adds and drops Ethernet-over-MPLS traffic onto an Ethernet Ring using MPLS pseudowires (EoMPLS PW LER operation). When using VSC7416-01 the Ethernet ring can be operated at 1 Gbps or 2.5 Gbps. Two independent Ethernet layers are shown. The outermost Ethernet layer is the (MPLS) Link Layer Ethernet (LL-Ethernet). The inner layer Ethernet is the (MPLS) Service Layer Ethernet (SL-Ethernet). VSC7416-01's service concept is required to establish MPLS pseudowires for carrying SL-Ethernet traffic over LL-Ethernet.

MPLS Label Switch Router (LSR) operation is also supported by VSC7416-01's service concept. VSC7416-01 can operate as a LSR front-end to an attached routing function within a Carrier Ethernet Switch Router (CESR) application.

## FIGURE 1-4: MPLS OVER ETHERNET RING

Any traffic carried over Ethernet can be forwarded within the bridge attached to the frame's arrival port without the use of VSC7416-01's service concept. That is, both LL- and SL-Ethernet bridge are fully featured provider bridges (Q-in-Q). The illustration shows examples of provider bridging within both the LL-Ethernet bridge and SL-Ethernet bridge.

The orange arrows show how an EoMPLS PW E-TREE service can be carried over an Ethernet ring using drop-andcontinue forwarding at the Link-Layer Ethernet. At the ingress ring node the E-TREE service traffic arrives at the SL-Ethernet bridge and is classified to an Ethernet pseudowire. A PW label, an MPLS label stack, and a Link-layer Ethernet multicast header are pushed before the service traffic is forwarded to the Link-Layer bridge.

Whether the E-TREE service is forwarded clock-wise or counter clock-wise around the Link-Layer ring can be determined entirely by Ethernet ring protection mechanisms (G.8032) implemented at the Link-Layer of the ingress node. In the illustration, counter clock-wise direction is shown.

In the next ring node, there are no attached subscribers for this E-TREE service and the traffic is "continued" on the ring using bridging (L2 multicasting) in the LL-Ethernet Bridge.

At the next ring node (shown to the right in the illustration), a "continue" copy of the E-TREE service is again provided by L2 multicasting in the LL-Ethernet Bridge. Also, LER operation "drop" is performed as subscribers to the E-TREE service exists. The LL-Ethernet header, the MPLS label stack, and the PW label are popped in the LER block and only the original customer frame is forwarded to the Service Layer bridge. In this example, multiple copies are generated to subscribers of the L2 multicast flow within the E-TREE service.

VSC7416-01 provides the following capabilities for use in MPLS and/or Carrier Ethernet edge equipment:

- EoMPLS PW LER (Single-Segment and Multi-Segment Pseudowire)

- MPLS LSR

- Hierarchical VPLS (H-VPLS)

- · Separate MAC-tables and VLAN-tables for MPLS Link-Layer Ethernet and Service-Layer Ethernet

- Service concept Per Service ingress dual leaky bucket policing Per-service and color statistics both ingress, discarded and egress

- Protection switching

1:1 PW protection (Service Layer protection)

1:1 LSP protection (Path Layer protection)

Facility Bypass protection per RFC-4090 (a group of services at a time)

Ethernet Linear protection (ITU-T G.8031)

Ethernet Ring protection (ITU-T G.8032)

• OAM

Fully-featured Ethernet-based OAM. Hardware OAM implementation is required for precision and scale. MPLS-TP OAM assist functions for internal/external CPU software or external MPLS-TP OAM processor

- · Service Activation Measurements

- · IEEE-1588 network timing functions

- Integrated CPU sub-system for management and control

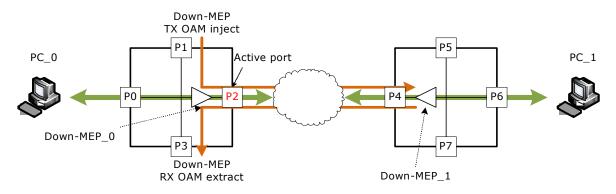

## 1.2.4 OAM ENGINE

VSC7416-01's OAM functionality described as part of this application is also supported in all other applications of VSC7416-01 previously described even though not detailed as part of those descriptions.

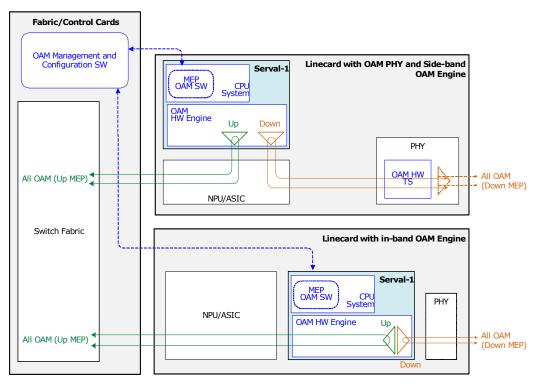

VSC7416-01 can be used as a powerful OAM off-load engine in new designs or to upgrade existing systems to become OAM aware. The following illustration shows two different usages of VSC7416-01 as an Ethernet OAM engine on a line card. Similar pizzabox models exist.

For the linecard at the top of the illustration, VSC7416-01 is side-band to the data flow. In this model, VSC7416-01 processes OAMs redirected by the NPU/ASIC and pseudo Up-MEPs and Down-MEPs can be supported fully in hardware. If used in combination with a Microchip Carrier Ethernet PHY, hardware accurate Down-MEP delay measurements and delay variation measurements (DMM/DMR) can be supported using this model. Continuity check (CCMs), synthetic loss measurements using LMM/LMR, and loopback (LBM/LBR) is also supported fully in hardware using VSC7416-01's Ethernet OAM capabilities.

The line card shown at the bottom in the illustration depicts VSC7416-01 used as an in-band OAM engine. In this model, true Up-MEPs and Down-MEPs can be supported all in hardware and with hardware accuracy and scale for continuity check, delay measurements, loss measurements, and loopback.

For both OAM models shown, OAM software can reside in VSC7416-01's integrated CPU system. This enables a distributed OAM model for chassis applications considerably reducing the OAM processing requirements to a central OAM management entity.

For the in-band OAM engine model, VSC7416-01 can also assist MPLS-TP OAM implementations. VSC7416-01 detects and redirects MPLS-TP OAM and Pseudowire OAM to internal CPU or external OAM processor, which implements actual OAM protocol handling. When extracting MPLS-TP OAM, VSC7416-01 provides arrival port information and service classification results to the internal CPU or external device. In addition, when MPLS-TP OAM is injected to VSC7416-01, the internal CPU or external device can include proprietary service mapping information. As a result, the internal CPU or MPLS-TP OAM processing device can dictate parameters such as destination port or ports, QOS and queuing, per egress port encapsulation, and statistics for each frame.

The following are some of the advanced features of VSC7416-01 used in OAM engine applications.

- Fully-featured Ethernet-based OAM. All hardware OAM generation and checking functions. Hardware OAM implementation is required for precision.

- MPLS-TP OAM assist functions for internal or external CPU software or external MPLS-TP OAM processor.

- Multiple concurrent Maintenance Entity Group (MEG) Levels for port, path, and service OAM.

- · OAM loopback.

- Generalized loopback functions not only applicable to LBM/LBR handling.

- Automatic timer-based hardware OAM frame generation targeted at CCMs, LMM, DMM, and LBM/TST generation.

- FDMA assisted OAM frame generation for Service Activation Measurements.

- Integrated CPU system running OAM software.

## 1.3 Functional Overview

This section provides an overview of all major blocks and functions involved in the forwarding operation in the same order as a frame traverses through the VSC7416-01 device. It also outlines other major functionality of the device such as the CPU port module, the CPU system, and CPU interfaces.

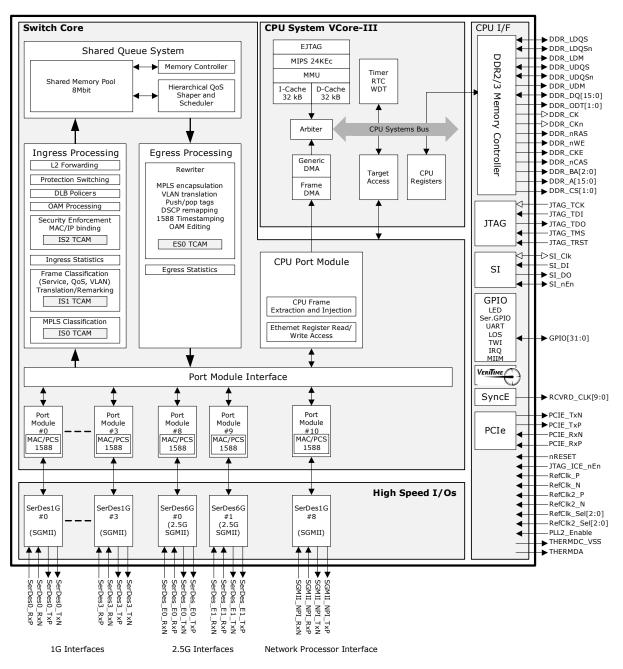

The following illustration shows the block diagram for the VSC7416-01 device.

## 1.3.1 FRAME ARRIVAL

The Ethernet interfaces receive incoming frames and forward these to the port modules. The 1G SGMII and 2.5G SGMII ports support both 100BASE-X and 1000BASE-X-SERDES.

Each port module contains a Media Access Controller (MAC) that performs a full suite of checks, such as VLAN Tag aware frame size checking, Frame Check Sequence (FCS) checking, and Pause frame identification.

Each port module connects to a SerDes block and contains a Physical Coding Sublayer (PCS), which perform 8 bits/ 10 bits encoding, auto-negotiation of link speed and duplex mode, and monitoring of the link status.

Full-duplex is supported for all speeds, and half-duplex is supported for 10 Mbps and 100 Mbps. Symmetric and asymmetric pause flow control are both supported as well as priority-based flow control (IEEE 802.1Qbb).

## VSC7416-01

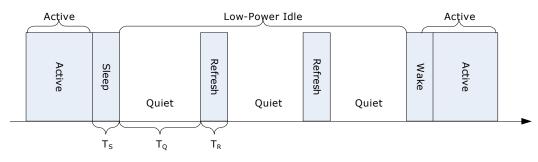

All Ethernet ports support Energy Efficient Ethernet (EEE) according to IEEE 802.3az. The shared queue system is capable of controlling the operating states, active or low-power, of the PCS. The PCS understands the line signaling as required for EEE. This includes signaling of active, sleep, quiet, refresh, and wake.

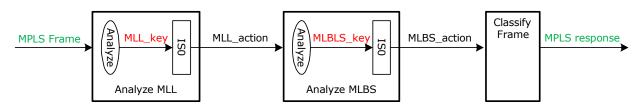

## 1.3.2 MPLS-TP CLASSIFICATION

On ports where MPLS is enabled, incoming MPLS-encapsulated frames are sent to the MPLS-TP classifier in the ingress processing module. Non-MPLS-encapsulated frames bypass the MPLS-TP classifier and are sent directly to the basic classifier.

Based on the MPLS Link Layer and MPLS label stack, the MPLS-TP classifier determines if the frame is to be forwarded using the MPLS Link Layer Ethernet (outer Ethernet), MPLS layer, or Service Layer Ethernet (inner/customer Ethernet for Ethernet pseudowire). In some cases forwarding at two layers simultaneously is possible.

The MPLS-TP classification is based on up to three MPLS labels and 1 reserved label.

Based on the MPLS-TP classification, any Ethernet pseudo-wire (PW) can be terminated and the MPLS-TP label stack popped (LER). The frame is then forwarded based on the customer ethernet encapsulation. The forwarding function can forward the frame into a new pseudo-wire (S-PE function) or to a customer port (T-PE). When terminating a PW, VSC7416-01 can pop the MPLS link layer, 3 MPLS labels and the control word.

This implementation of customer Ethernet forwarding function supports E-LAN over MPLS (VPLS). Forwarding is limited to one pseudo-wire per physical port per E-LAN enabling a low-cost H-VPLS MTU-s edge.

Based on MPLS-TP classification, any LSP can be forwarded to an MPLS port and the MPLS label stack is modified. The MPLS label stack operation can include terminating up to 2 tunnels and initiating up to 2 new tunnels in addition to label swapping and TTL processing (LSR).

The MPLS-TP classifier supports Ethernet Link Layer drop and continue for any LSP, allowing a copy of the frame to be forwarded to a network port based on the Ethernet layer.

The MPLS-TP classifier can extract PW OAM (GAL, VCCV1, VCCV2, VCCV3), LSP OAM (GAL) and Segment OAM (GAL) to the CPU. Further, the MPLS-TP classifier can be configured to extract MPLS-TP frames with any reserved label in the MPLS label stack.

## 1.3.3 BASIC AND ADVANCED FRAME CLASSIFICATION

The basic and advanced frame classification in the ingress processing module receive all frames except frames for which the MPLS-TP classifier has indicated that further processing is not required. The basic and advanced classifiers determine a range of frame properties such as arrival service point, VLAN, and Quality of Service (QoS) class, and drop precedence level. This information is carried through the switch together with the frame and affects policing, drop precedence marking, statistics collecting, security enforcement, Layer-2 forwarding, and rewriting.

The classification is a combination of a basic classification using configurable logic and more advanced classification using a TCAM.

The classification engine understands up to two VLAN tags and can look for Layer-3 and Layer-4 information behind two VLAN tags. If frames are triple tagged, the higher-layer protocol information is not extracted.

Ethernet pseudo-wire LER frames are terminated by the MPLS-TP classifier and then processed at the Service Ethernet layer (inner) by the basic and advanced classifier. MPLS-encapsulated frames may also be processed purely at the MPLS Link Layer (outer Ethernet) by the MPLS-TP classifier or the basic and advanced classifier.

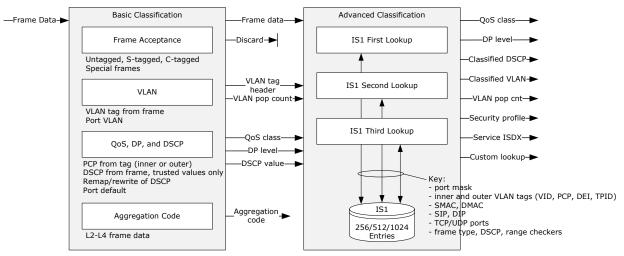

The following illustration shows the basic and advanced frame classification.

## FIGURE 1-7: BASIC AND ADVANCED FRAME CLASSIFICATION

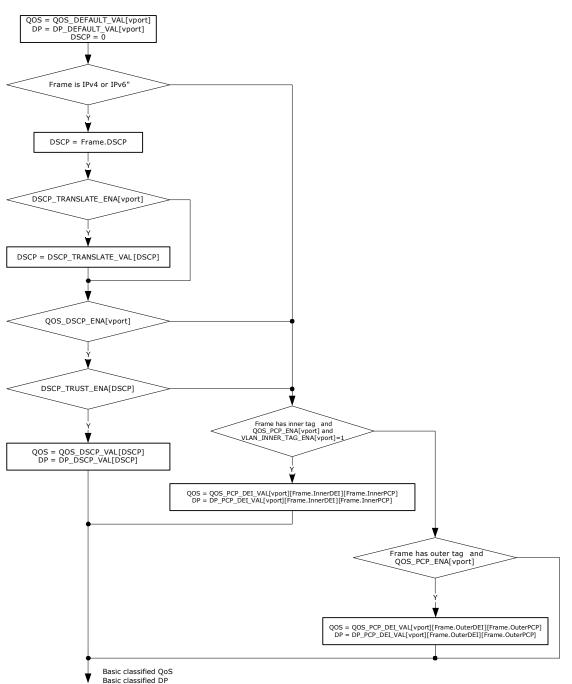

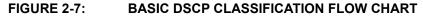

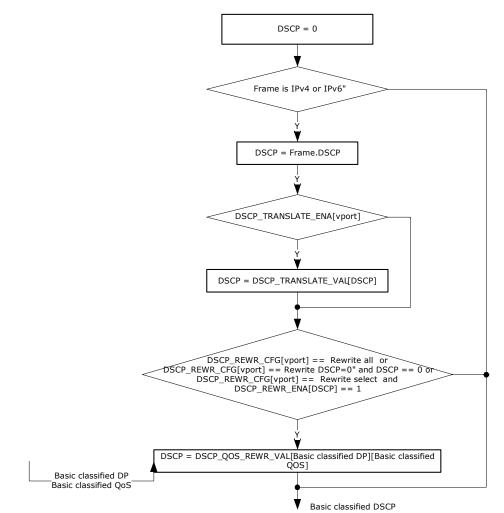

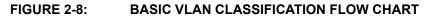

The basic classification classifies each frame to a VLAN, a QoS class, a drop precedence (DP) level, DSCP value, and an aggregation code. The basic classification also performs a general frame acceptance check. The output from the basic classification may be overwritten or changed by the more intelligent advanced classification using the IS1 TCAM.

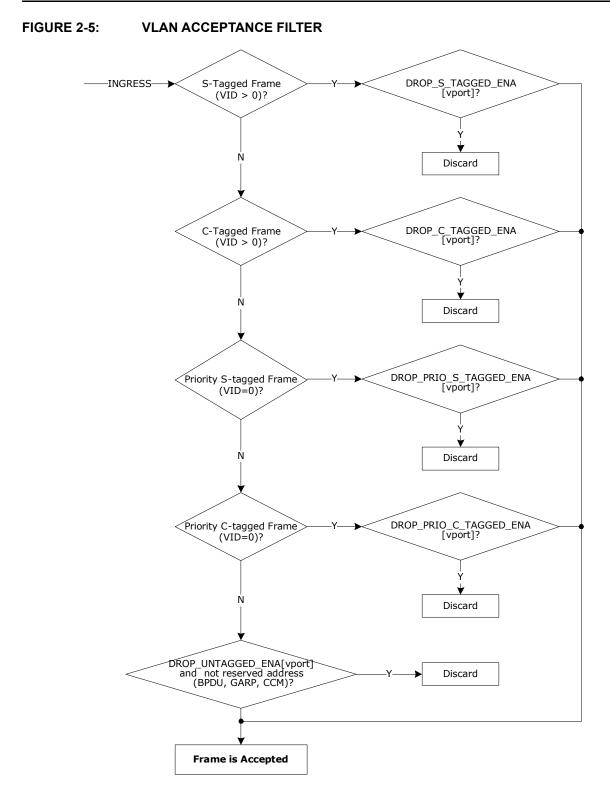

**Frame Acceptance** The frame acceptance filter checks for valid combinations of VLAN tags against the ingress port's VLAN acceptance filter where it is possible to configure rules for accepting untagged, priority-tagged, C-, and S-tagged frames. In addition, the filter also enables discarding of frames with illegal MAC addresses (for instance null MAC address or multicast source MAC address).

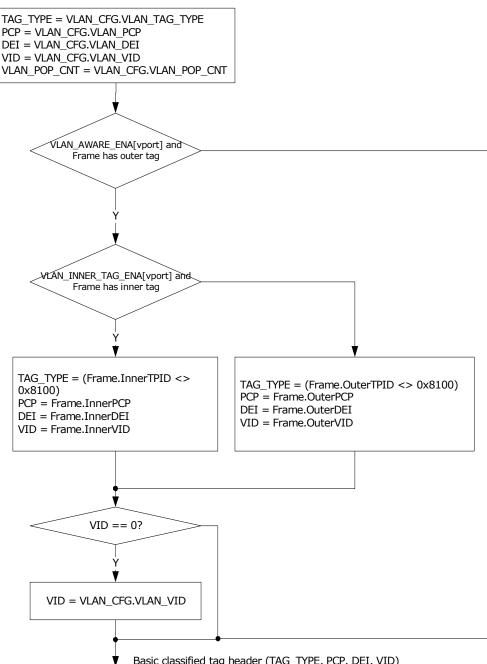

**VLAN** Every incoming frame is classified to a VLAN by the basic VLAN classification. This is based on the VLAN in the frame, or if the frame is untagged or the ingress port is VLAN unaware, it is based on the ingress port's default VLAN. A VLAN classification includes the whole TCI (PCP, DEI, and VID) and also the TPID (C-tag or S-tag).

For double-tagged frames, it is selectable whether the inner or the outer tag is used.

The device can recognize S-tagged frames with the standard TPID (0x88A8) or S-tagged frames using a custom programmable value. One custom value is supported by the device.

**QoS, DP, and DSCP** Each frame is classified to a Quality of Service (QoS) class and a drop precedence level (frame color: green/yellow). The QoS class and DP level are used throughout the device for providing queuing, scheduling, and congestion control guarantees to the frame according to what is configured for that specific QoS class and color.

The QoS class and DP level in the basic classification are based on the class of service information in the frame's VLAN tags (PCP and DEI) and/or the DSCP values from the IP header. Both IPv4 and IPv6 are supported. If the frame is non-IP or untagged, the port's default QoS class and DP level are used.

The DSCP values can be remapped before being used for QoS. This is done using a common table mapping the incoming DSCP to a new value. Remapping is enabled per port. In addition, for each DSCP value, it is possible to specify whether the value is trusted for QoS purposes.

Each IP frame is also classified to an internal DSCP value. By default, this value is taken from the IP header but it may be remapped using the common DSCP mapping table or rewritten based on the assigned QoS class. The classified DSCP value may be written into the frame at egress – this is programmable in the rewriter.

**Aggregation Code** The basic classification calculates an aggregation code, which is used to select between ports that are member of a link aggregation group. The aggregation code is based on selected Layer-2 through Layer-4 information, such as MAC addresses, IP addresses, IPv6 flow label, ISDX, and TCP/UDP port numbers. The aggregation code ensures that frames belonging to the same conversation are using the same physical ports in a link aggregation group.

## 1.3.3.1 Advanced Classification

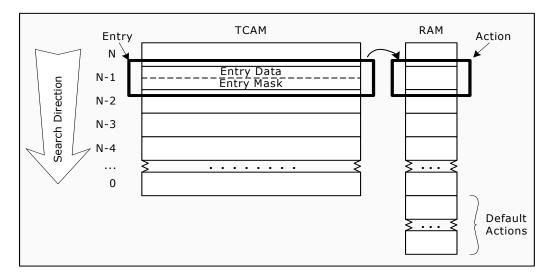

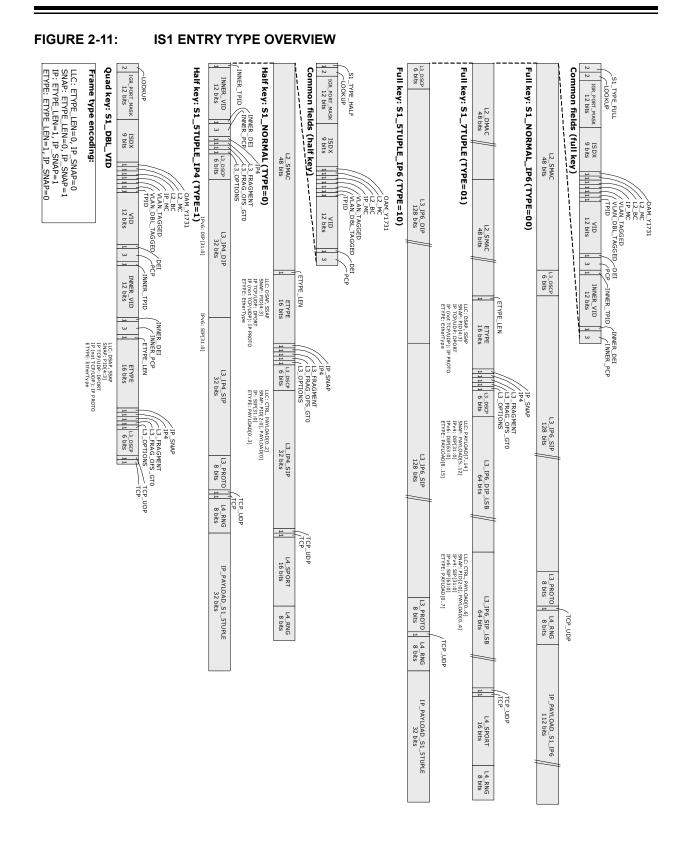

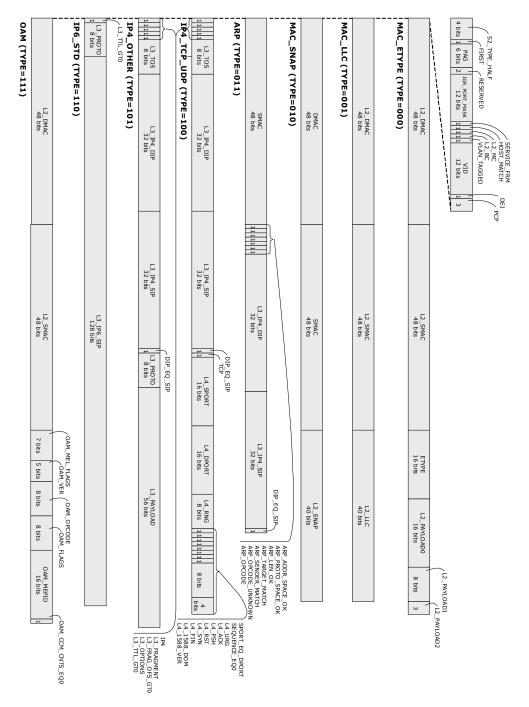

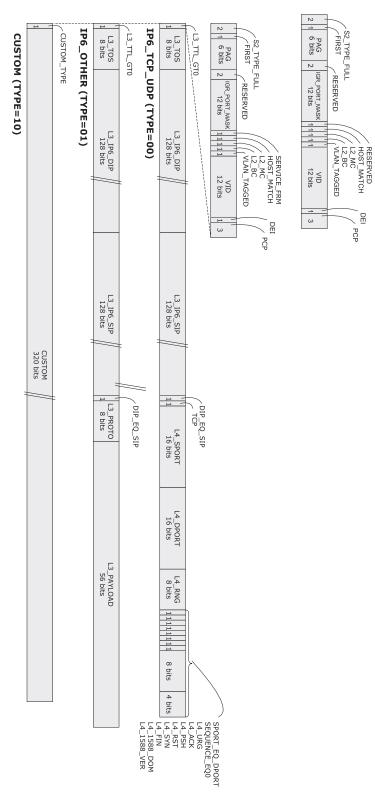

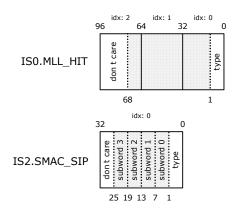

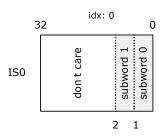

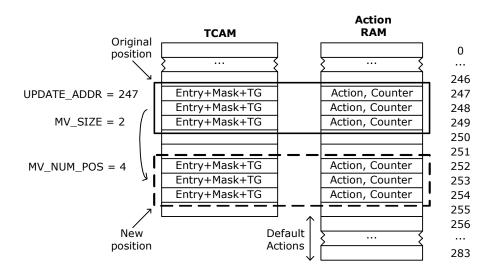

Following basic classification, Layer-2 and Layer-4 information is extracted from each frame and matched against a TCAM, IS1, with one of the following six different IS1 keys:

- NORMAL. Up to 512 entries with primary fields in key consisting of SMAC, outer VLAN tag, 32-bit source IP address, IP protocol, TCP/UDP source and destination port

- NORMAL\_IP6. Up to 256 entries with primary fields in key consisting of SMAC, inner and outer VLAN tags, 128-

bit source IP address, IP protocol, TCP/UDP source and destination port

- 7TUPLE. Up to 256 entries with primary fields in key consisting of source and destination MAC addresses, inner and outer VLAN tags, 64-bit source and destination IP addresses, IP protocol, TCP/UDP source and destination port

- 5TUPLE\_IP4. Up to 512 entries with primary fields in key consisting of inner and outer VLAN tags, 32-bit source and destination IP addresses, IP protocol, TCP/UDP source and destination port

- 5TUPLE\_IP6. Up to 256 entries with primary fields in key consisting of inner and outer VLAN tags, 128-bit source and destination IP addresses, IP protocol, TCP/UDP source and destination port

- S1\_DBL\_VID. Up to 1024 entries with primary fields in key consisting of inner and outer VLAN tags

The TCAM embeds powerful protocol awareness for well-known protocols such as LLC, SNAP, IPv4, IPv6, and UDP/ TCP. For each frame, three keys are generated and matched against the TCAM. The keys are selectable per ingress port per frame type (IPv4, IPv6, non-IP) per IS1 lookup.

The actions associated with each entry (programmed into the TCAM action RAM) include the ability to select a service (ISDX), overwrite or translate the classified VLAN, overwrite the priority code point (PCP) or the drop eligibility indicator (DEI), overwrite the QoS class and DP level, or overwrite the DSCP value. Each of these actions is enabled individually for each of the three lookup.

In addition, a policy association group (PAG) is assigned to the frame. The PAG identifies a security profile to which the frame belongs. The PAG is used in the succeeding security frame processor, IS2, to select which access control lists to apply to the frame. The PAG enables creating efficient ACLs that only are applicable to frames with the same PAG.

A lookup in IS1 can enable the use of a custom lookup in IS2 - the security enforcement TCAM. The custom lookup can match against selectable frame fields from the incoming frame. In total, 40 bytes from the frame are matched against the TCAM. This is a powerful future-proofing feature enabling handling of new protocols.

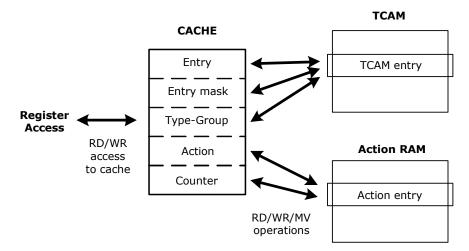

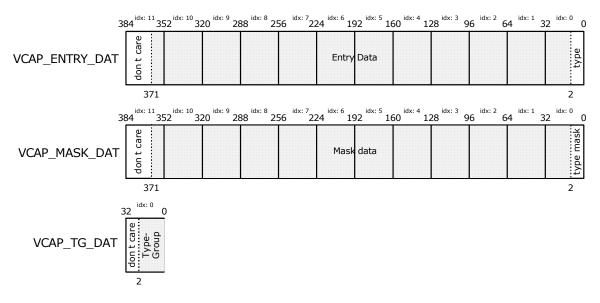

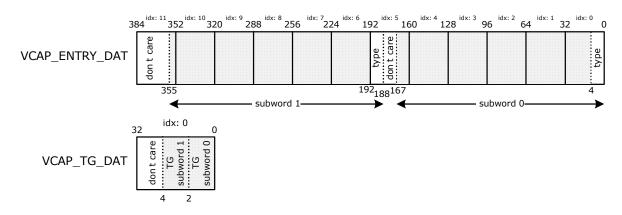

## 1.3.4 VERSATILE CONTENT AWARE PROCESSOR (VCAP)

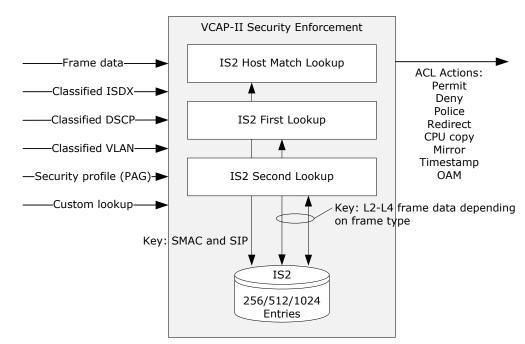

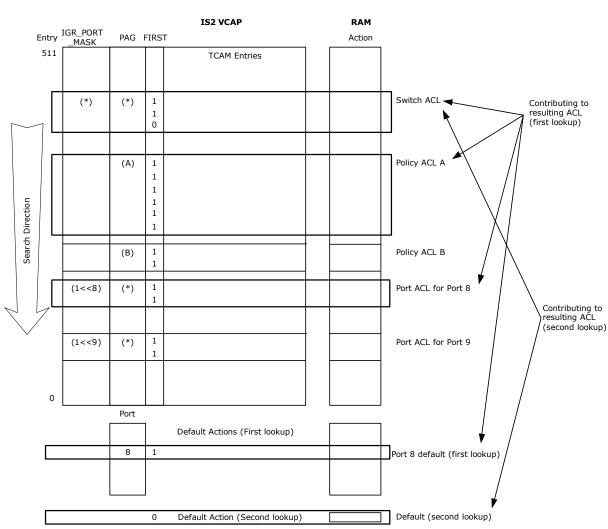

All frames are inspected by the VCAP IS2 before they are passed on to the Layer-2 forwarding. The following illustration depicts VCAP security enforcement.

## FIGURE 1-8: VCAP SECURITY ENFORCEMENT

The VCAP uses a TCAM-based frame processor enabling implementation of a rich set of security features. The flexible VCAP engine supports wire-speed frame inspection based on Layer 2-4 frame information, including the ability to perform longest prefix matching and identifying port ranges. The action associated with each VCAP entry (programmed

into the VCAP action RAM) includes the ability to do frame filtering, dual leaky bucket rate limitation (frame or byte based), snooping to CPU, redirection to CPU, mirroring, 1588 timestamping, OAM actions, and accounting. Even though the VCAP is located in the ingress path of the device, it possesses both ingress and egress capabilities.

The VCAP embeds powerful protocol awareness for well-known protocols such as LLC, SNAP, ARP, IPv4, IPv6, and UDP/TCP. IPv6 is supported with full matching against both the source and the destination IP addresses.

Each frame is looked up three times in IS2. The first lookup is a host match lookup for IPv4 and IPv6 frames enabling MAC/IP binding and IP source guarding. The key consists of information identifying the source host: ingress port number, source MAC address, and full source IP address. The output is an action informing the following two lookups in IS2 of whether the host is accepted into the network. The following two lookups in IS2 construct a key based on the frame type (LLC, SNAP, ARP, IPv4, IPv6, UDP/TCP, OAM, custom) extracting relevant information. IS2 supports up to 1024 host match entries, 512 LLC, SNAP, ARP, IPv4-TCP/UDP, or OAM entries, and 256 IPv6-TCP/UDP and custom entries.

## 1.3.5 ETHERNET OAM ENGINE

VSC7416-01 supports various OAM layer interactions as defined in ITU-T Y.1731, MEF E-LMI, ITU-T Y.1564 (Y.156sam), IEEE 802.3ah, and IEEE 802.1ag. The following OAM functions are supported in hardware:

- Continuity check frame generation and checking with sub-millisecond transmission periods.

- · Loopback with frame generation and checking for both LBM and LBR.

- Frame loss measurements with support for both single-ended and dual-ended with hardware accurate counter readings for both LMM and LMR. Dual-ended loss measurements use CCM.

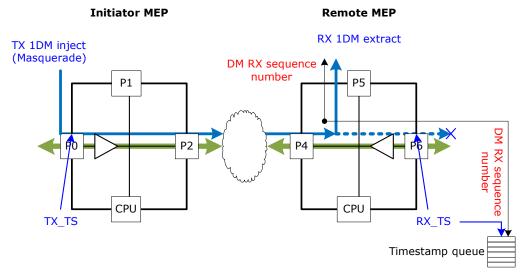

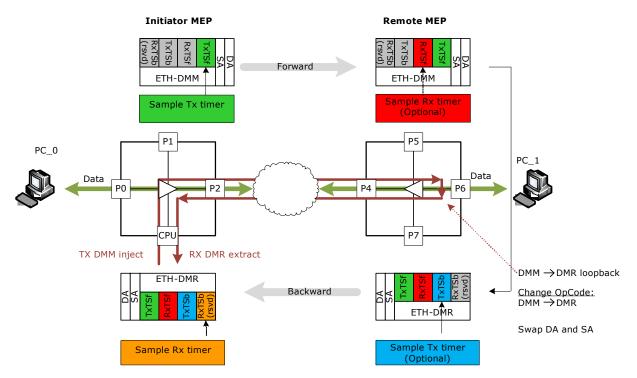

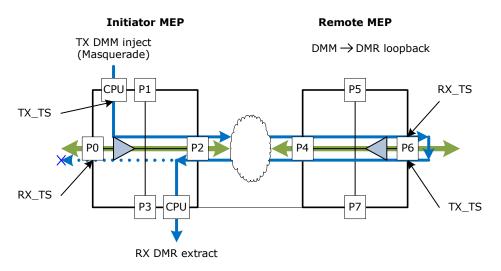

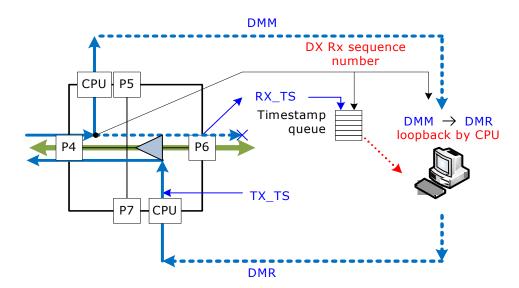

- Frame delay measurements with support for both one-way and two-way delay measurements with hardware accurate timestamps for both 1DM, DMM, and DMR.

Other OAM functions are supported but require CPU interaction.

VSC7416-01 contains 23 Versatile OAM endpoints (VOE), each handling the OAM functions of a MEG endpoint (MEP). Both port, path, and service MEP monitoring levels are supported and a MEP can be either an up or a down MEP. Each incoming OAM frames is processed by the assigned VOE, which include verification of the frame contents against configurations, forwarding based on the MEG level, and processing according to the received OAM type.

## 1.3.6 POLICING

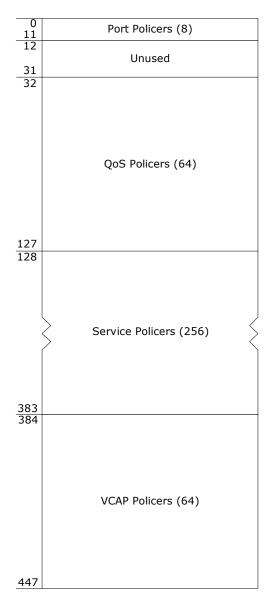

Each frame is subject to a number of different policing operations. The device features 392 programmable policers. The policers are split into the followings groups:

- 256 service policers: Ingress service index (ISDX) selects which policer to use.

- 64 queue policers: Ingress port number and QoS class determine which policer to use.

- 8 port policers: Ingress port number determines which policer to use.

- 64 VCAP IS2 policers: An IS2 action can point to a policer.

The internal CPU port is the 8th port and also includes port and queue policers. The policers can measure frame rates or bit rates.

Each frame can trigger up to three policers: A service or queue policer, a port policer, and a VCAP IS2 policer.

Each policer is a MEF-compliant dual leaky bucket policer supporting both color-blind and color-aware operation. The initial frame color is derived from the drop precedence level from the frame classification. For color-aware operation, a coupling mode is configurable for each policer.

Using these policers ensures Service Level Agreement (SLA) compliance. The outcome of this policing operation is to mark each accepted frame as in-profile (green) or out-of-profile (yellow). Yellow frames are treated as excess or discardeligible and green frames are committed. Frames that exceed the yellow/excess limits are discarded (red).

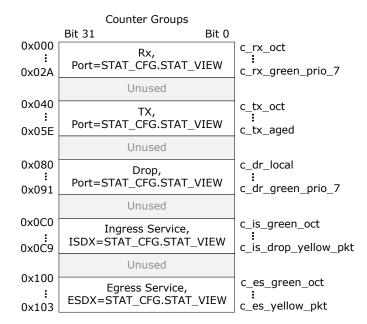

Each frame is counted in associated statistics reflecting the arrival service point (ISDX), and the frame's color (green, yellow, red). This statistics counts bytes and frames. In addition, each frame is also counted in statistics reflecting the ingress port, the QoS class, and the frame's color (green, yellow, red). This statistics can count bytes or frames.

Finally, the analyzer contains a group of storm control policers that are capable of policing various kinds of flooding traffic as well as CPU directed learn traffic. These policers are global policers working on all frames received by the switch. Storm policers measure frame rates.

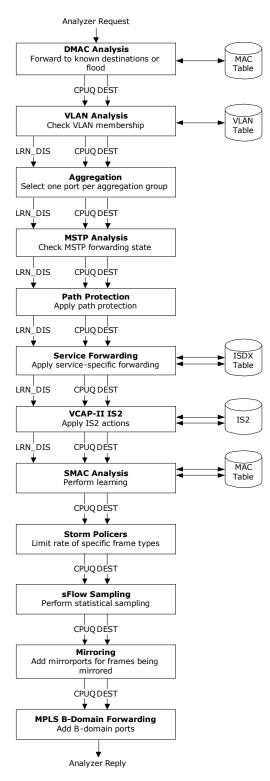

## 1.3.7 LAYER-2 FORWARDING

After the policers, the Layer-2 forwarding block (the analyzer) handles all fundamental forwarding operations and maintains the associated MAC table, the VLAN table, the ISDX table, and the aggregation table. The device implements an 8K MAC table and a 4K VLAN table.

The main task of the analyzer is to determine the destination port set of each frame. This forwarding decision is based on various information such as the frame's ingress port, the source MAC address, the destination MAC address, the VLAN identifier, and the ISDX, as well as the frame's VCAP action, mirroring, and the destination port's link aggregation configuration.

The switch performs Layer-2 forwarding of frames. For unicast and Layer-2 multicast frames, this means forwarding based on the destination MAC address and the VLAN. For IPv4 and IPv6 multicast frames, the switch performs Layer-2 forwarding, but based on Layer-3 information, such as the source IP address. The latter enables source-specific IPv4 multicast forwarding (IGMPv3) and source-specific IPv6 multicast forwarding (MLDv2).

The following are some of the contributions to the Layer-2 forwarding.

- VLAN classification. VLAN-based forward filtering includes source port filtering, destination port filtering, VLAN mirroring, asymmetric VLANs, and so on.

- Service classification. Service-based forward filtering includes destination port filtering and forced forwarding.

- Security enforcement. The security decision made by the VCAP can, for example, redirect the frame to the CPU based on some abnormality detection filters.

- MSTP. The VLAN identifier maps to a Multiple Spanning Tree instance, which determines MSTP-based destination port filtering.

- MPLS-TP. Destination set determined by the MPLS-TP classifier.

- MAC addresses. Destination and source MAC address lookups in the MAC table determine if a frame is a learn frame, a flood frame, a multicast frame, or a unicast frame.

- Learning. By default, the device performs wire-speed learning on all ports. However, certain ports could be configured with secure learning enabled, where an incoming frame with unknown source MAC address is classified as a "learn frame" and is redirected to the CPU. The CPU performs the learning decision and also decides whether the frame is forwarded.

Learning can also be disabled. In that case, it does not matter if the source MAC address is in the MAC table.

- Link aggregation. A frame targeted at a link aggregate is further processed to determine which of the link aggregate group ports the frame must be forwarded to.

- Mirroring. Mirror probes may be set up in different places in the forwarding path for monitoring purposes. As part of a mirror a copy of the frame is sent either to the CPU or to another port.

## 1.3.8 SHARED QUEUE SYSTEM AND HIERARCHICAL EGRESS SCHEDULER

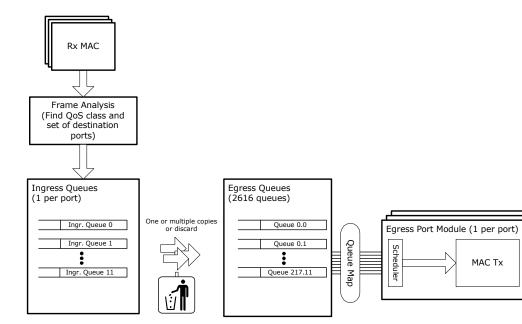

The analyzer provides the destination port set of a frame to the shared queue system. It is the queue system's task to control the frame forwarding to all destination ports.

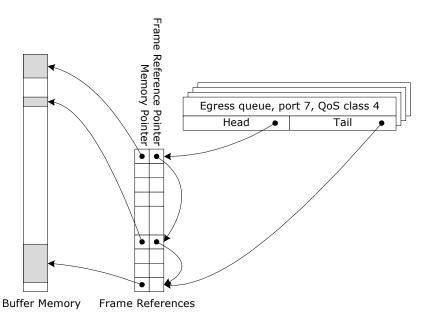

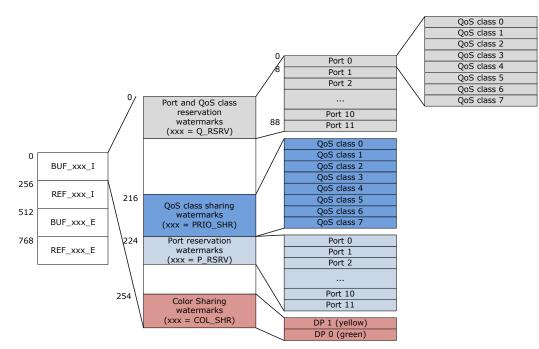

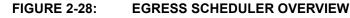

The shared queue system embeds 8 megabits of memory that can be shared between all queues and ports. The queue system consists of 2616 queues with programmable use. Frames are mapped to queues through a programmable mapping function allowing ingress ports, egress ports, QoS classes, and services to be taken into account. The sharing of resources between queues and ports is controlled by an extensive set of thresholds.

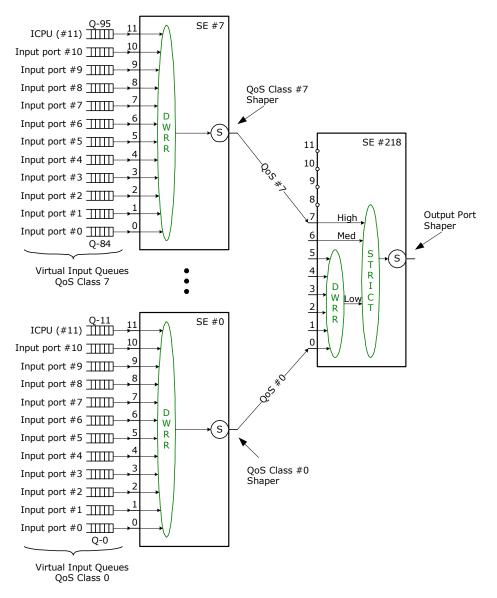

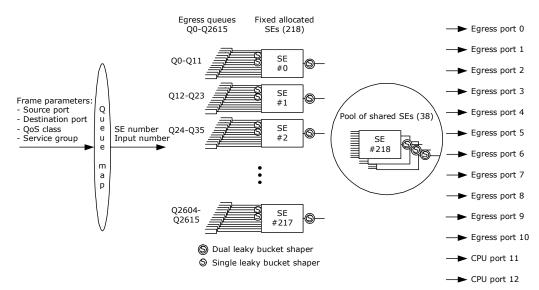

Each egress port implements a default scheduler and shapers, as shown in the following illustration. Per egress port, the scheduler sees the outcome of aggregating the egress queues (one per ingress port per Qos class) into eight QoS classes. By default, aggregation is done in a deficit weighted round-robin fashion (DWRR) with equal weights to all ingress ports within a QoS class. As a result, byte-based round robin between ingress ports is performed for each QoS class. Scheduling between QoS classes for the port is by default a combination of strict and DWRR scheduling. QoS classes 7 and 6 have strict highest priority, and QoS classes 5 through 0 are scheduled using deficit weighted round-robin.

#### FIGURE 1-9: DEFAULT EGRESS SCHEDULER AND SHAPER CONFIGURATION

Scheduling between QoS classes within the port can use one of three methods:

- Strict. Frames with the highest QoS class are always transmitted before frames with lower QoS class.

- Combination of strict and Deficit Weighted Round Robin (DWRR) scheduling. Any split between strict and DWRR QoS classes can be configured. Each QoS class serviced using DWRR sets a DWRR weight ranging from 0 to 31.

- Combination of strict and Frame Based Round Robin scheduling (FBRR) scheduling. Any split between strict and FBRR QoS classes can be configured.

All shapers shown in Figure 1-9, are dual leaky bucket shapers.

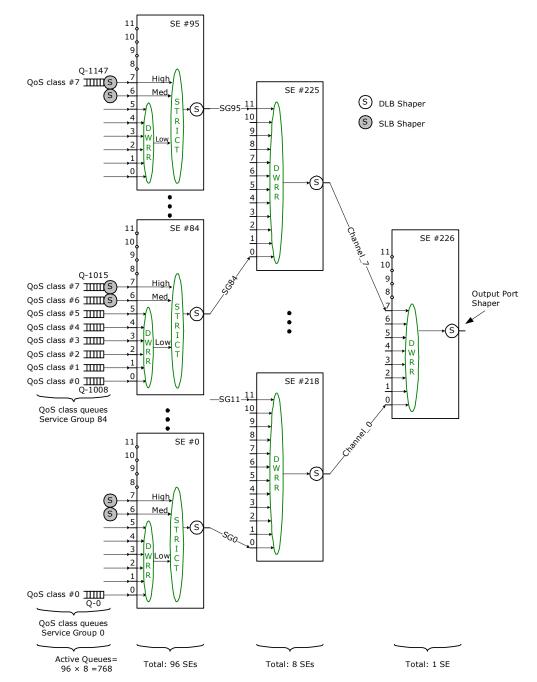

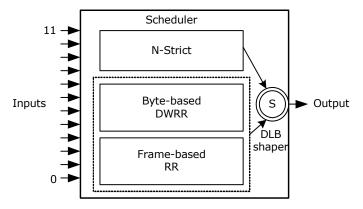

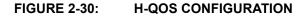

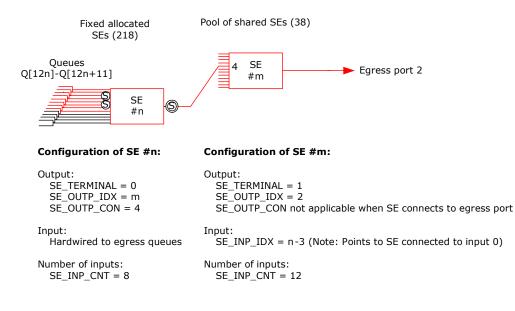

It is also possible to configure a hierarchical Quality of Service (H-QoS) egress scheduler on a few egress ports, such as network facing ports. There are a total pool of 256 scheduler elements (SE). The first 218 scheduler elements connect to the 2616 queues in the queue system. The remaining 38 SEs are highly flexible and can be used to build H-QoS scheduling. Each scheduler element has 12 inputs and 1 output. The output contains a dual leaky bucket shaper. The scheduling algorithm within each element can be strict, deficit weighted round robin (DWRR), or frame based round robin (FBRR). Combinations of strict versus DWRR/FBRR scheduling is supported as described above for the scheduling between QoS classes.

The scheduler elements are programmed to connect to each other (output of one element is input to another and so on) to achieve the overall desired scheduling hierarchy. The following illustration shows an example of a three-level hierarchy on an egress port implementing a queue system for 96 service groups with each eight QoS classes. A total of 768 egress queues is associated with the port in this example. This H-QoS scheduler utilizes 13 flexible SEs and 96 fixed SEs.

## FIGURE 1-10: ADVANCED SERVICE-BASED EGRESS SCHEDULER AND SHAPER

In addition to the dual leaky bucket shaper per scheduler element, the queue system also implements in total 436 single leaky bucket shapers, which enables dedicated shaping on QoS class 6 and 7.

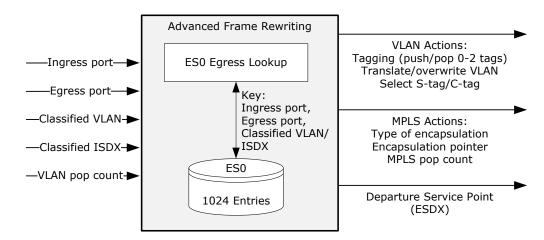

## 1.3.9 REWRITER AND FRAME DEPARTURE

Before transmitting the frame on the egress line, the rewriter can modify selected fields in the frame, such as MPLS encapsulation, VLAN tags, DSCP value, timestamping, OAM fields, and FCS.

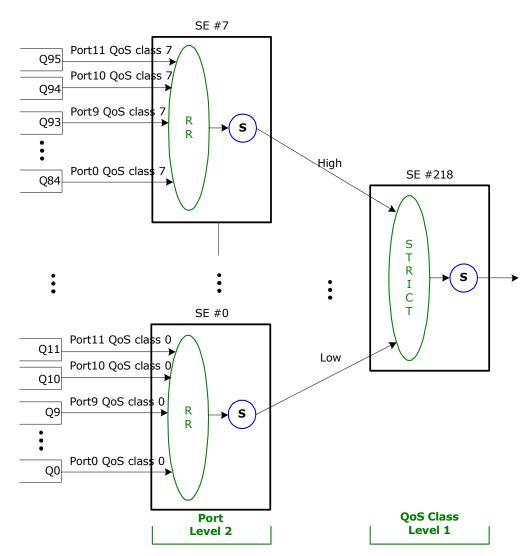

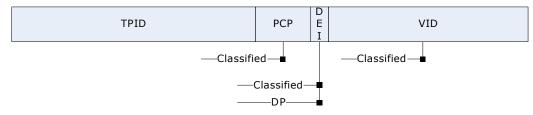

The rewriter controls the final VLAN tagging of frames based on the classified VLAN, the VLAN pop count, and egressdetermined VLAN actions from the ES0 TCAM lookup. The egress VLAN actions are by default given by the egress port settings. These include normal VLAN operations such as pushing a VLAN tag, untagging for specific VLANs, and simple translations of DEI and PCP.

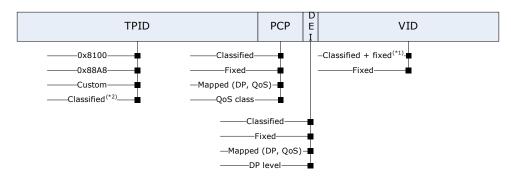

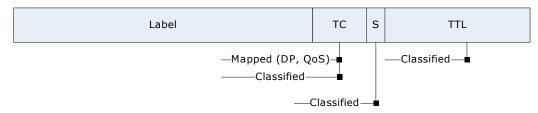

## FIGURE 1-11: ADVANCED FRAME REWRITING

By using the egress TCAM, ES0, much more advanced VLAN tagging operations can be achieved. ES0 enables pushing up to two VLAN tags and allows for a flexible translation of the VLAN tag header. The key into ES0 is the combination of the ingress port, the egress port, and either the classified VLAN tag header or the classified service.

The PCP and DEI bits in the VLAN tag are subject to remarking based on translating the classified tag header or by using the classified QoS value and the frame's drop precedence level from ingress.

MPLS popping and pushing is handled by the ES0 TCAM. Up to 3 MPLS labels and 1 control word can be popped and pushed as well as an Ethernet link layer header (DMAC, SMAC, VLAN tag, and MPLS EtherType).

The TC bits in the MPLS labels are subject to remarking based on the classified values, a mapping to new values based on QoS class and drop precedence level, or new programmable values. The S bit in the MPLS labels can either use the classified value or a new programmable value.

In addition, the DSCP value in IP frames can be updated using the classified DSCP value and the frame's drop precedence level from ingress. The DSCP value can be remapped at egress before writing it into the frame.

Finally, the rewriter updates the FCS if the frame was modified before the frame is transmitted.

The egress port module controls the flow control exchange of pause frames with a neighboring device when the interconnection link operates in full-duplex flow control mode. When the connected device triggers flow control through transmission of a pause frame, the MAC stops the egress scheduler's forwarding of frames out of the port. Traffic then builds up in the queue system but sufficient queuing is available to ensure wire speed loss-less operation.

In half-duplex operation, the port module's egress path responds to back pressure generation from a connected device by collision detection and frame retransmission.

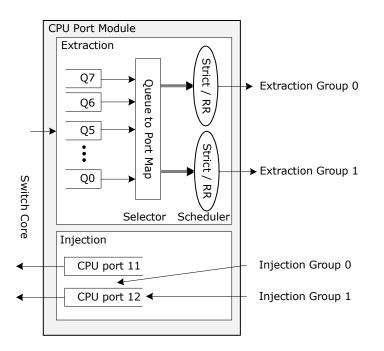

## 1.3.10 CPU PORT MODULE

The CPU port module contains eight CPU extraction queues and two CPU injection queues. These queues provide an interface for exchanging frames between the internal CPU system and the switch core. An external CPU using the serial interface can also inject and extract frames to and from the switch core by using the CPU port module. Any Ethernet interface on the device can also be used for extracting and injecting frames.

The switch core can intercept a variety of different frame types and copy or redirect these to the CPU extraction queues. The classifier can identify a set of well-known frames such as IEEE reserved destination MAC addresses (BPDUs, GARPs, CCM/Link trace), as well as IP-specific frames (IGMP, MLD). The security TCAM, IS2, provides another very

flexible way of intercepting all kinds of frames, for instance specific OAM frames, ARP frames or explicit applications based on TCP/UDP port numbers. In addition, frames can be intercepted based on the MAC table, the VLAN table, or the learning process.

Whenever a frame is copied or redirected to the CPU, a CPU extraction queue number is associated with the frame and used by the CPU port module when enqueuing the frame into the 8 CPU extraction queues. The CPU extraction queue number is programmable for every interception option in the switch core.

## 1.3.11 SYNCHRONOUS ETHERNET AND PRECISION TIME PROTOCOL

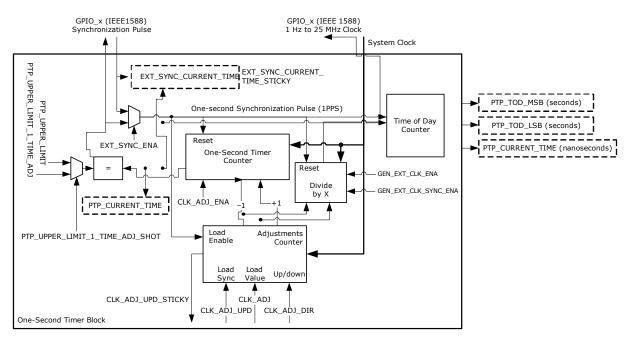

The device supports Layer-1 ITU-T G.8261 Synchronous Ethernet and Layer-2 IEEE 1588 Precision Time Protocol for synchronizing network timing throughout a network.

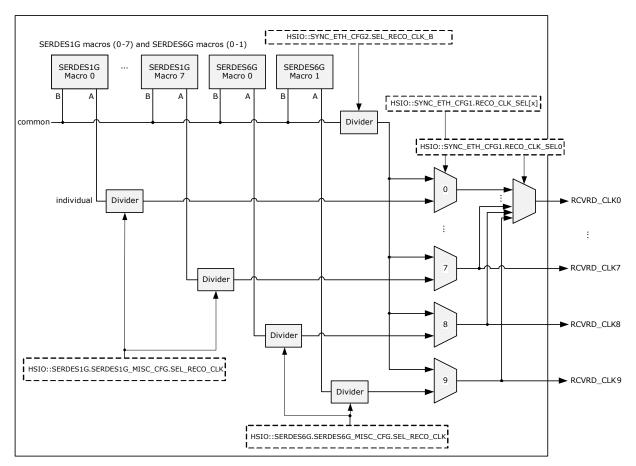

Synchronous Ethernet allows for the transfer of network timing from one reference to all network elements. In VSC7416-01, each port can recover its ingress clock and output the recovered clock to one of up to ten recovered clock output pins. External circuitry can then generate a stable reference clock input used for egress and core logic timing in VSC7416-01.

The Precision Time Protocol (PTP) allows for the network-wide synchronization of precise time of day. It is also possible to derive network timing. PTP can operate with a one-step clock or a two-step clock. For one-step clocks, a frame's residence time is calculated and stamped into the frame at departure. For two-step clocks, a frame's residence time is simply recorded and provided to the CPU for further processing. The CPU can then initiate a follow-up message with the recorded timing.

PTP is supported for a range of encapsulations including PTP over Ethernet/IEEE 802.3 and PTP over UDP over IPv4/ IPv6, and PTP over UDP over IP/MPLS.

The VSC7416-01 device contains two separate timing domains; one for Synchronous Ethernet and data path forwarding, and one for PTP timing synchronization.

## 1.3.12 CPU SYSTEM AND INTERFACES

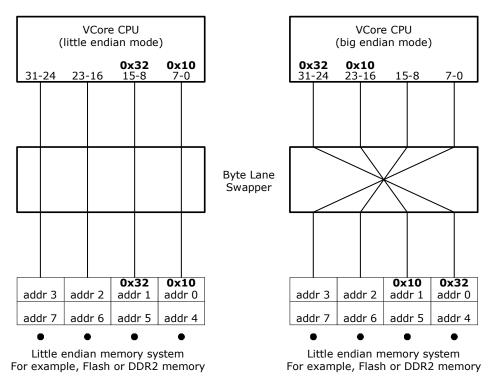

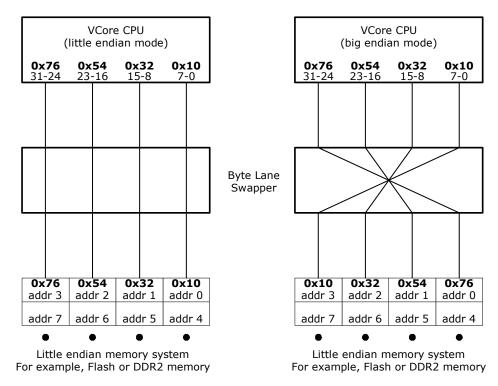

The device features a VCore-III CPU system containing a powerful 416 MHz MIPS 24KEc<sup>™</sup> CPU. It is suitable for lightly managed and fully managed applications.

VCore-III includes a general-purpose direct memory access engine (GPDMA) that also supports frame-based direct memory access (FMDA) operations. The FMDA offloads the CPU when injecting and extracting frames to and from the switch core. VCore-III boots from a serial flash and uses an 8-bit or 16-bit DDR2/3 SDRAM for memory, in addition to its built-in 32 kilobytes of instruction cache and 32 kilobytes of data cache. An external debugger can be attached to the EJTAG interface.

In addition to the integrated processor, the CPU system permits the attachment of an external CPU. For configuration of switch register, an external CPU can use either a serial interface, an MII Management interface, a PCIe interface, or an SGMII port.

When using an SGMII port, the Versatile Register Access Protocol (VRAP) allows an external CPU to access registers in VSC7416-01 using VRAP Ethernet frames. No internal CPU is required. Each VRAP request frame contains a list of read, read-modify-write, and write commands that are processed by the hardware. For each request frame, a VRAP reply frame is generated containing the results of the requests. Each frame can contain multiple commands only restricted by the MTU size.

For frame transfers, the external CPU has the option of using the serial interface, an MII Management interface, a PCIe interface, or an SGMII port.

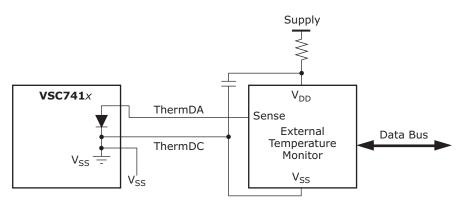

The VSC7416-01 device includes a GPIO interface with 32 individually configurable pins. Through the GPIO pins, VSC7416-01 supports the following interfaces:

- Two-wire serial interface (two GPIO pins)

- Dual UART (four GPIO pins)

- External interrupts (two interrupt pins)

- Serial GPIO (SGPIO) and LED interface (four GPIO pins)

- MII Management slave interface for accessing switch registers from an external CPU (three GPIO pins)

- Dual MII Management master interface for controlling external PHYs (four GPIO pins)

- SFP signal detect per SerDes for fast detect and reaction to loss of signal (11 GPIO pins)

- IEEE 1588 pins with programmable synchronized 1588 clocks (two GPIO pins)

- · IEEE 1588 pins with load-and-store functionality of 1588 clocks for synchronizing with external equipment (two

## GPIO pins)

The serial GPIO and LED interfaces can be used specifically for driving external LEDs for external copper PHYs or for serializing external interrupts. For instance, link down events from external PHYs, before being input to the device.

## 2.0 FUNCTIONAL DESCRIPTIONS

This section provides information about the functional aspects of the VSC7416-01 Carrier Ethernet switch device, available configurations, operational features, and testing functionality.

## 2.1 Port Modules

The port modules contain the following functional blocks.

- MAC

- PCS

## 2.1.1 PORT MODULE NUMBERING AND MACRO CONNECTIONS

The port modules connect to the interface macros, which can be of two types:

- SERDES6G

- SERDES1G

The interface macros connect to the external interface pins. For more information about the SerDes macros, see Section 2.2, SERDES1G and Section 2.3, SERDES6G.

The following table lists the mapping from the switch core port modules to the interface macros. The number next to the interface macro type (for example, "8" in cell "SERDES1G, 8") indicates the macro number that must be used when addressing the macros.

## TABLE 2-1:PORT MAPPING FROM SWITCH CORE PORT MODULE TO INTERFACE MACROS

| Switch Core Port Module | VSC7416-01        |

|-------------------------|-------------------|

| 0-3                     | SERDES1G, 0-3     |

| 8-9                     | SERDES6G, 0-1     |

| 10                      | SERDES1G, NPI     |

| 11                      | Internal CPU port |

## 2.1.2 MAC

This section provides information about the high-level functionality and the configuration options of the Media Access Controller (MAC) that is used in each of the port modules.

The MAC supports the following speeds and duplex modes:

- SERDES1G ports: 10/100/1000 Mbps in full-duplex mode and 10/100 Mbps in half-duplex mode

- SERDES6G ports: 10/100/1000/2500 Mbps in full-duplex mode and 10/100 Mbps in half-duplex mode.

The following table lists the registers associated with configuring the MAC.

## TABLE 2-2: MAC CONFIGURATION REGISTERS

| Register                 | Description                      | Replication |

|--------------------------|----------------------------------|-------------|

| DEV::CLOCK_CFG           | Reset and speed configuration    | Per port    |

| DEV::MAC_ENA_CFG         | Enabling of Rx and Tx data paths | Per port    |

| DEV::MAC_MODE_CFG        | Port mode configuration          | Per port    |

| DEV::MAC_MAXLEN_CFG      | Maximum length configuration     | Per port    |

| DEV::MAC_TAGS_CFG        | VLAN tag length configuration    | Per port    |

| DEV::MAC_ADV_CHK_CFG     | Type length configuration        | Per port    |

| DEV::MAC_IFG_CFG         | Interframe gap configuration     | Per port    |

| DEV::MAC_HDX_CFG         | Half-duplex configuration        | Per port    |

| SYS::MAC_FC_CFG          | Flow control configuration       | Per port    |

| DEV::MAC_FC_MAC_LOW_CFG  | LSB of SMAC used in pause frames | Per port    |

| DEV::MAC_FC_MAC_HIGH_CFG | MSB of SMAC used in pause frames | Per port    |

| DEV::MAC_STICKY          | Sticky bit recordings            | Per port    |

## 2.1.2.1 Reset

There are a number of resets in the port module. All of the resets can be set and cleared simultaneously. By default, all blocks are in the reset state. With reference to register CLOCK\_CFG, the resets are as follows:

- MAC\_RX\_RST: Reset of the MAC receiver

- MAC TX RST: Reset of the MAC transmitter

- PORT\_RST: Reset of the ingress and egress queues

- PCS\_RX\_RST: Reset of the PCS decoder

- PCS\_TX\_RST: Reset of the PCS encoder

When changing the MAC configuration, the port must go through a reset cycle. This is done by writing register CLOCK\_CFG twice. On the first write, the reset bits are set. On the second write, the reset bits are cleared. Bits that are not reset bits in CLOCK\_CFG must keep their new value for both writes.

For more information about resetting a port, see Section 4.2.3, Port Reset Procedure.

## 2.1.2.2 Port Mode Configuration

The MAC provides a number of handles for configuring the port mode. With reference to the MAC\_MODE\_CFG, MAC\_IFG\_CFG, and MAC\_ENA\_CFG registers, the handles are as follows:

- Duplex mode (FDX\_ENA). Half or full duplex.

- Data sampling (GIGA\_MODE\_ENA). Must be 1 in 1 Gbps and 2.5 Gbps and 0 in 10 Mbps and 100 Mbps.

- Enabling transmission and reception of frames (TX\_ENA/RX\_ENA). Clearing RX\_ENA stops the reception of frames and further frames are discarded. An ongoing frame reception is interrupted. Clearing TX\_ENA stops the dequeuing of frames from the egress queues, which means that frames are held back in the egress queues. An ongoing frame transmission is completed.

- Tx-to-Tx inter-frame gap (TX\_IFG)

The link speed is configured using CLOCK\_CFG.LINK\_SPEED with the following options.

• Link speed (CLOCK\_CFG.LINK\_SPEED) 1 Gbps (125 MHz clock)

Ports 8 and 9: 1 Gbps or 2.5 Gbps (125 MHz or 312.5 MHz clock). The actual clock frequency depends on the SerDes configuration.

100 Mbps (25 MHz clock)

10 Mbps (2.5 MHz clock)

## 2.1.2.3 Half Duplex

A number of special configuration options are available for half-duplex (HDX) mode:

- Seed for back-off randomizer. Field MAC\_HDX\_CFG.SEED seeds the randomizer used by the backoff algorithm. Use MAC\_HDX\_CFG.SEED\_LOAD to load a new seed value.

- **Backoff after excessive collision**. Field MAC\_HDX\_CFG.WEXC\_DIS determines whether the MAC backs off after an excessive collision has occurred. If set, backoff is disabled after excessive collisions.

- Retransmission of frame after excessive collision. Field MAC\_HDX\_CFG.RETRY\_AFTER\_EXC\_COL\_ENA determines whether the MAC retransmits frames after an excessive collision has occurred. If set, a frame is not dropped after excessive collisions, but the backoff sequence is restarted. This is a violation of IEEE 802.3, but is useful in non-dropping half-duplex flow control operation.

- Late collision timing. Field MAC\_HDX\_CFG.LATE\_COL\_POS adjusts the border between a collision and a late collision in steps of 1 byte. According to IEEE 802.3, section 21.3, this border is permitted to be on data byte 56 (counting frame data from 1); that is, a frame experiencing a collision on data byte 55 is always retransmitted, but it is never retransmitted when the collision is on byte 57. For each higher LATE\_COL\_POS value, the border is moved 1 byte higher.

- **Rx-to-Tx inter-frame gap**. The sum of MAC\_IFG\_CFG.RX\_IFG1 and MAC\_IFG\_CFG.RX\_IFG2 establishes the time for the Rx-to-Tx inter-frame gap. RX\_IFG1 is the first part of half-duplex Rx-to-Tx inter-frame gap. Within RX\_IFG1, this timing is restarted if carrier sense (CRS) has multiple high-low transitions (due to noise). RX\_IFG2 is the second part of half-duplex Rx-to-Tx inter-frame gap. Within RX\_IFG2, transitions on CRS are ignored.

When enabling a port for half-duplex mode, the switch core must also be enabled (SYS::FRONT\_PORT\_MODE.HDX-\_MODE).

## 2.1.2.4 Frame and Type/Length Check

The MAC supports frame lengths of up to 16 kilobytes. The maximum length accepted by the MAC is configurable in MAC\_MACLEN\_CFG.MAX\_LEN.

The MAC allows tagged frames to be 4 bytes longer and double-tagged frames to be 8 bytes longer than the specified maximum length (MAC\_TAGS\_CFG.VLAN\_LEN\_AWR\_ENA). The MAC must be configured to look for VLAN tags. By default, EtherType 0x8100 identifies a VLAN tag. In addition, a custom EtherType can be configured in MAC\_TAGS\_CFG.TAG\_ID. The MAC can be configured to look for none, or two tags (MAC\_TAG\_CFG.VLAN\_AW-R\_ENA).

The type/length check (MAC\_ADV\_CHK\_CFG.LEN\_DROP\_ENA) causes the MAC to discard frames with type/length errors (in-range and out-of-range errors).

## 2.1.2.5 Flow Control (IEEE 802.3x)

VSC7416-01 supports both standard full-duplex flow control (IEEE 802.3x) and priority-based flow control (IEEE 802.1Qbb). This section describes standard full-duplex flow control, and Section 2.1.2.6, Priority-Based Flow Control (IEEE 802.1Qbb) describes priority-based flow control.

In full-duplex mode, the MAC provides independent support for transmission of pause frames and reaction to incoming pause frames. This allows for asymmetric flow control configurations.

The MAC obeys received pause frames (MAC\_FC\_CFG.RX\_FC\_ENA) by pausing the egress traffic according to the timer values specified in the pause frames. In order to evaluate the pause time in the incoming pause frames, the link speed must be specified (SYS::MAC\_FC\_CFG.FC\_LINK\_SPEED).

The transmission of pause frames is triggered by assertion of a flow control condition in the ingress queues caused by a queue filling exceeding a watermark. For more information, see Section 2.10.7, Ingress Pause Request Generation. The MAC handles the formatting and transmission of the pause frame. The following configuration options are available:

- Transmission of pause frames (MAC\_CFG\_CFG.TX\_FC\_ENA).

- Pause timer value used in transmitted pause frames (MAC\_FC\_CFG.PAUSE\_VAL\_CFG).

- Flow control cancellation when the ingress queues de-assert the flow control condition by transmission of a pause frame with timer value 0 (MAC\_FC\_CFG.ZERO\_PAUSE\_ENA).

- Source MAC address used in transmitted pause frames (MAC\_FC\_MAC\_HIGH\_CFG, MAC\_F-C\_MAC\_LOW\_CFG).

The MAC has the option to discard incoming frames when the remote link partner is not obeying the pause frames transmitted by the MAC. The MAC discards an incoming frame if a Start-of-Frame is seen after the pause frame was transmitted. It is configurable how long reaction time is given to the link partner (MAC\_FC\_CFG.FC\_LATENCY\_CFG). The benefit of this approach is that the queue system is not risking being overloaded with frames due to a non-complying link partner.

In half-duplex mode, the MAC does not react to received pause frames. If the flow control condition is asserted by the ingress queues, the industry-standard backpressure mechanism is used. Together with the ability to retransmit frames after excessive collisions (MAC\_HDX\_CFG.RETRY\_AFTER\_EXC\_COL\_ENA), this enables non-dropping half-duplex flow control.

## 2.1.2.6 Priority-Based Flow Control (IEEE 802.1Qbb)

VSC7416-01 supports priority-based flow control on all ports for all QoS classes. The following table lists the specific registers associated with priority-based flow control.

| Register                 | Description                                                        | Replication |

|--------------------------|--------------------------------------------------------------------|-------------|

| SYS::MAC_FC_CFG          | Flow control configuration                                         | Per port    |

| DEV::MAC_FC_MAC_LOW_CFG  | LSB of SMAC used in pause frames                                   | Per port    |

| DEV::MAC_FC_MAC_HIGH_CFG | MSB of SMAC used in pause frames                                   | Per port    |

| ANA::PFC_CFG             | Configuration of Rx priority-based flow con-<br>trol per priority. | Per port    |

TABLE 2-3: PRIORITY-BASED FLOW CONTROL CONFIGURATION REGISTERS

## TABLE 2-3: PRIORITY-BASED FLOW CONTROL CONFIGURATION REGISTERS (CONTINUED)

| Register                         | Description                                                           | Replication |

|----------------------------------|-----------------------------------------------------------------------|-------------|

| QSYS:SWITCH_PORT_MODE            | Configuration of Tx priority-based flow con-<br>trol per priority     | Per port    |

| DEV::PORT_MISC.FWD_C-<br>TRL_ENA | Enabling forwarding of priority-based pause frames to analyzer.       | Per port    |

| ANA::CPU_FWD_BPDU_CFG            | Disable forwarding of priority-based pause frames beyond the analyzer | Per port    |

VSC7416-01 provides independent support for transmission of pause frames and reaction to incoming pause frames, which allows asymmetric flow control configurations.

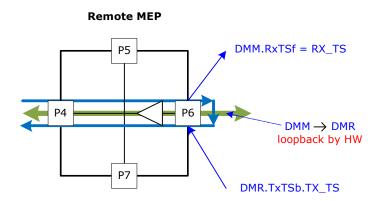

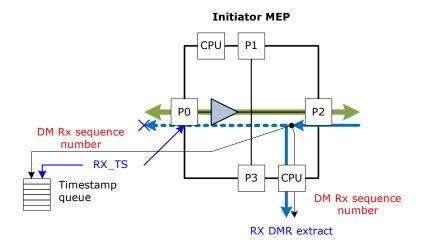

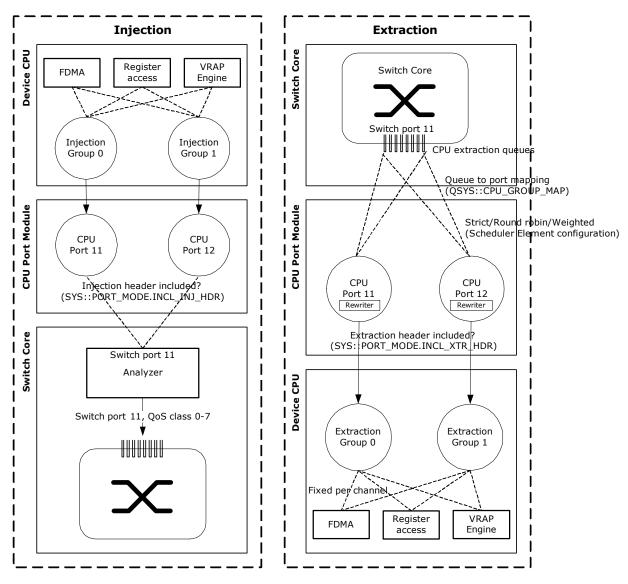

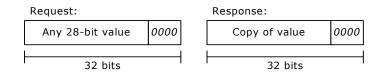

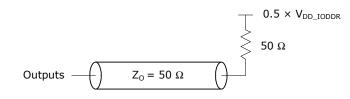

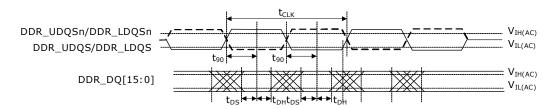

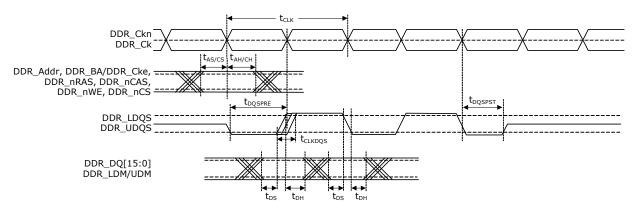

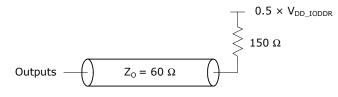

The device obeys received pause frames per priority (ANA::PFC\_CFG.RX\_PFC\_ENA) by pausing the egress traffic according to the timer values specified in the pause frames. Transmission of frames belonging to QoS class n is paused if bit *n* is set in the priority\_enable\_vector in the incoming pause frame. The pause time for QoS class *n* is given by time[*n*] from the pause frame. The link speed must be specified in order to evaluate the pause times (ANA::PFC\_CFG.FC\_LINK\_SPEED).