# VSC8484 Datasheet Quad Channel WAN/LAN/Backplane XAUI to SFP+/KR Transceiver

Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com www.microsemi.com

©2018 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revisi | on His   | tory                                              | . 1  |

|---|--------|----------|---------------------------------------------------|------|

|   | 1.1    | Revision | n 4.4                                             | 1    |

|   | 1.2    |          | n 4.3                                             |      |

|   | 1.3    |          | n 4.2                                             |      |

|   | -      |          |                                                   |      |

|   | 1.4    |          | n 4.1                                             |      |

|   | 1.5    | Revision | n 4.0                                             | 1    |

|   | 1.6    | Revision | n 2.0                                             | 2    |

| _ | Б.     |          |                                                   | _    |

| 2 |        |          | rview                                             |      |

|   | 2.1    | Major A  | pplications                                       | 4    |

|   | 2.2    | Feature  | s and Benefits                                    | 5    |

| _ | - 0    |          |                                                   | _    |

| 3 | Functi |          | escriptions                                       |      |

|   | 3.1    | Transm   | it Operation for XAUI to SFI Mode                 | 7    |

|   | 3.2    | Receive  | Operation for SFI to XAUI Mode                    | 8    |

|   | 3.3    |          | ·                                                 |      |

|   | 0.0    | 3.3.1    | Supported Data Rates and Standards                |      |

|   |        | 3.3.2    | Rate Auto-Negotiation                             |      |

|   |        | 3.3.3    | Receiver (Rx) Subsection                          |      |

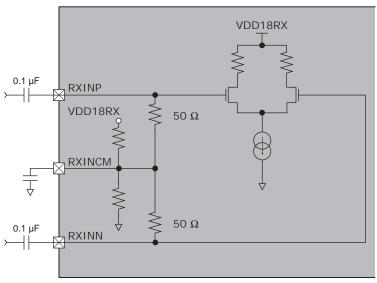

|   |        | 3.3.4    | Variable Gain Amplifier Input Receiver            |      |

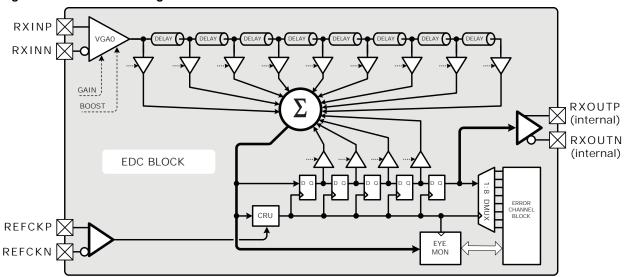

|   |        | 3.3.5    | Rx Equalizer                                      |      |

|   |        | 3.3.6    | Rx Clock and Data Recovery                        |      |

|   |        | 3.3.7    | Rx Data Rate Selection                            |      |

|   |        | 3.3.8    | Rx Data Path Control                              | . 13 |

|   |        | 3.3.9    | External Capacitors                               | . 13 |

|   |        | 3.3.10   | VScope Input Signal Monitoring Integrated Circuit |      |

|   |        | 3.3.11   | Unity Gain Amplifier                              | . 13 |

|   |        | 3.3.12   | Link Monitor                                      | . 13 |

|   |        | 3.3.13   | Transmitter (Tx) Subsection                       |      |

|   |        | 3.3.14   | Tx Data Rate Selection                            | . 14 |

|   |        | 3.3.15   | Tx Data Path Control                              |      |

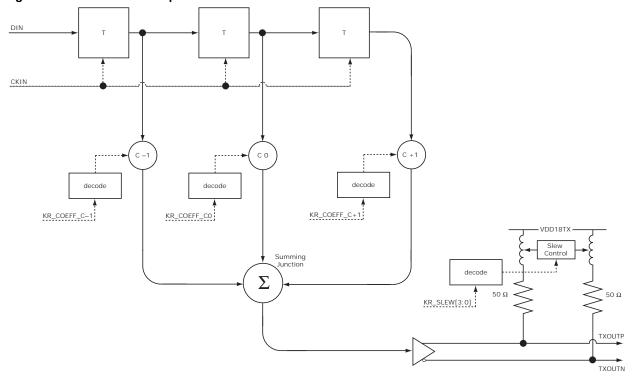

|   |        | 3.3.16   | 10BASE-KR Output Driver                           |      |

|   |        | 3.3.17   | PMA Loopback                                      | . 17 |

|   |        | 3.3.18   | PMA Linetime                                      |      |

|   |        | 3.3.19   | External Capacitors                               |      |

|   |        | 3.3.20   | Reference Clock                                   |      |

|   |        | 3.3.21   | Reference Clock Inputs                            |      |

|   |        | 3.3.22   | Clock Output                                      |      |

|   |        | 3.3.23   | Synchronous Ethernet Support                      |      |

|   |        | 3.3.24   | 1.25 Gbps Mode                                    |      |

|   |        | 3.3.25   | Power Down Mode                                   |      |

|   |        | 3.3.26   | Clock Distribution                                |      |

|   |        | 3.3.27   | Operation Modes                                   |      |

|   | 3.4    |          | terface Sublayer (WIS)                            |      |

|   |        | 3.4.1    | Operation                                         |      |

|   |        | 3.4.2    | Section Overhead                                  |      |

|   |        | 3.4.3    | A1, A2 (Frame Alignment)                          |      |

|   |        | 3.4.4    | Loss of Signal (LOS)                              |      |

|   |        | 3.4.5    | Loss of Optical Carrier (LOPC)                    |      |

|   |        | 3.4.6    | Severely Errored Frame (SEF)                      |      |

|   |        | 3.4.7    | Loss of Frame (LOF)                               | . 32 |

| 3.4.8    | J0 (Section Trace)                                                 |    |

|----------|--------------------------------------------------------------------|----|

| 3.4.9    | Z0 (Reserved for Section Growth)                                   | 33 |

| 3.4.10   | Scrambling/Descrambling                                            | 33 |

| 3.4.11   | B1 (Section Error Monitoring)                                      | 33 |

| 3.4.12   | E1 (Section Orderwire)                                             |    |

| 3.4.13   | F1 (Section User Channel)                                          | 33 |

| 3.4.14   | DCC-S (Section Data Communication Channel)                         | 33 |

| 3.4.15   | Reserved, National, and Unused Octets                              |    |

| 3.4.16   | Line Overhead                                                      | 34 |

| 3.4.17   | B2 (Line Error Monitoring)                                         | 35 |

| 3.4.18   | K1, K2 (APS Channel and Line Remote Defect Identifier)             | 35 |

| 3.4.19   | D4 to D12 (Line Data Communications Channel)                       | 37 |

| 3.4.20   | M0 and M1 (STS-1/N Line Remote Error Indication)                   | 37 |

| 3.4.21   | S1 (Synchronization Messaging)                                     | 37 |

| 3.4.22   | Z1 and Z2 (Reserved for Line Growth)                               | 37 |

| 3.4.23   | E2 (Orderwire)                                                     | 37 |

| 3.4.24   | SPE Pointer                                                        | 37 |

| 3.4.25   | Bit Designations within Payload Pointer                            | 38 |

| 3.4.26   | Pointer Types                                                      | 39 |

| 3.4.27   | Pointer Adjustment Rule                                            | 39 |

| 3.4.28   | Pointer Increment/Decrement Majority Rules                         | 39 |

| 3.4.29   | Pointer Interpretation States                                      | 40 |

| 3.4.30   | Valid Pointer Definition for Interpreter State Diagram Transitions | 40 |

| 3.4.31   | Path Overhead                                                      | 4′ |

| 3.4.32   | J1 (Overhead Octet)                                                | 42 |

| 3.4.33   | B3 (STS Path Error Monitoring)                                     | 42 |

| 3.4.34   | C2 (STS Path Signal Label and Path Label Mismatch)                 |    |

| 3.4.35   | G1 (Remote Path Error Indication)                                  | 43 |

| 3.4.36   | G1 (Path Status)                                                   |    |

| 3.4.37   | F2 (Path User Channel)                                             | 45 |

| 3.4.38   | H4 (Multiframe Indicator)                                          | 45 |

| 3.4.39   | Z3-Z4 (Reserved for Path Growth)                                   |    |

| 3.4.40   | N1 (Tandem Connection Maintenance/Path Data Channel)               | 45 |

| 3.4.41   | Loss of Code Group Delineation                                     | 45 |

| 3.4.42   | Reading Statistical Counters                                       | 45 |

| 3.4.43   | Defects and Anomalies                                              | 47 |

| 3.4.44   | Interrupt Pins and Interrupt Masking                               |    |

| 3.4.45   | Overhead Serial Interfaces                                         | 49 |

| 3.4.46   | Transmit Overhead Serial Interface (TOSI)                          | 49 |

| 3.4.47   | Receive Overhead Serial Interface (ROSI)                           |    |

| 3.4.48   | Pattern Generator and Checker                                      | 52 |

| Physical | Coding Sublayer (64B/66B PCS)                                      | 53 |

| 3.5.1    | Control Codes                                                      |    |

| 3.5.2    | Transmit Path                                                      | 54 |

| 3.5.3    | Receive Path                                                       | 55 |

| 3.5.4    | PCS Standard Test Modes                                            | 56 |

| 3.5.5    | PCS XGMII BIST                                                     | 56 |

| Client/H | ost Interface (XAUI)                                               | 58 |

| 3.6.1    | XGMII Extender Sublayer (PHY XS)                                   |    |

| 3.6.2    | XAUI Receiver                                                      |    |

| 3.6.3    | XAUI Receiver Equalization                                         |    |

| 3.6.4    | XAUI Clock and Data Recovery                                       |    |

| 3.6.5    | XAUI Code Group Synchronization                                    |    |

| 3.6.6    | XAUI Lane Deskew                                                   |    |

| 3.6.7    | 10B/8B Decoder                                                     |    |

| 3.6.8    | 8b/10b Encoder and Serializer                                      |    |

| 3.6.9    | XAUI Transmitter                                                   |    |

|          | XAUI Transmitter Pre-Emphasis                                      |    |

3.5

3.6

| 62<br>65<br>66<br>66<br>67<br>67<br>68<br>68<br>68 |

|----------------------------------------------------|

| 65<br>66<br>66<br>67<br>67<br>68<br>68<br>68       |

|                                                    |

|                                                    |

| 67<br>                                             |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

| 70                                                 |

|                                                    |

| 71                                                 |

|                                                    |

| 71                                                 |

| 73                                                 |

| 74                                                 |

| 75                                                 |

| 75                                                 |

| 76                                                 |

|                                                    |

| 76                                                 |

| 76                                                 |

| 76                                                 |

| 76                                                 |

| 77                                                 |

| 77                                                 |

| 77                                                 |

| 78                                                 |

| 79                                                 |

| 81                                                 |

| 82                                                 |

| 83                                                 |

|                                                    |

| 83                                                 |

| 84                                                 |

| 84                                                 |

| 85                                                 |

| 85                                                 |

| 85                                                 |

|                                                    |

|                                                    |

| 87                                                 |

|                                                    |

| 87                                                 |

|                                                    |

| 88                                                 |

|                                                    |

| 88                                                 |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|   |       | 5.1.2<br>5.1.3                                      | Reference Clock MDIO Interface                                                                                                               |                          |

|---|-------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|   | 5.2   | AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5 | Aracteristics Receiver Specifications Transmitter Specifications Timing and Reference Clock Two-Wire Serial (Slave) Interface MDIO Interface | 304<br>304<br>308<br>314 |

|   | 5.3   |                                                     | ing Conditions                                                                                                                               |                          |

|   | 5.4   | •                                                   | Ratings                                                                                                                                      |                          |

| 6 | Pin D | escript                                             | ions                                                                                                                                         | 320                      |

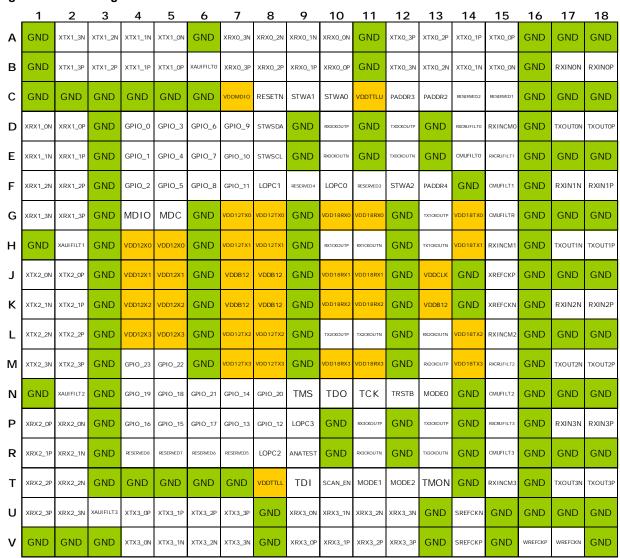

| • | 6.1   | -                                                   | gram                                                                                                                                         |                          |

|   | 6.2   |                                                     | r Function                                                                                                                                   |                          |

|   | V     | 6.2.1                                               | General Purpose Inputs and Outputs                                                                                                           |                          |

|   |       | 6.2.2                                               | JTAG Interface                                                                                                                               |                          |

|   |       | 6.2.3                                               | Management Interface                                                                                                                         | 322                      |

|   |       | 6.2.4                                               | Ground                                                                                                                                       |                          |

|   |       | 6.2.5                                               | Power Supply                                                                                                                                 | 323                      |

|   |       | 6.2.6                                               | Receive Path                                                                                                                                 |                          |

|   |       | 6.2.7                                               | Reference Clock                                                                                                                              |                          |

|   |       | 6.2.8                                               | Clock Outputs                                                                                                                                |                          |

|   |       | 6.2.9                                               | Test and Mode Control                                                                                                                        |                          |

|   |       | 6.2.10                                              | Transmit Path                                                                                                                                |                          |

|   |       | 6.2.11<br>6.2.12                                    | XAUI Channel                                                                                                                                 |                          |

| _ | Б     |                                                     |                                                                                                                                              |                          |

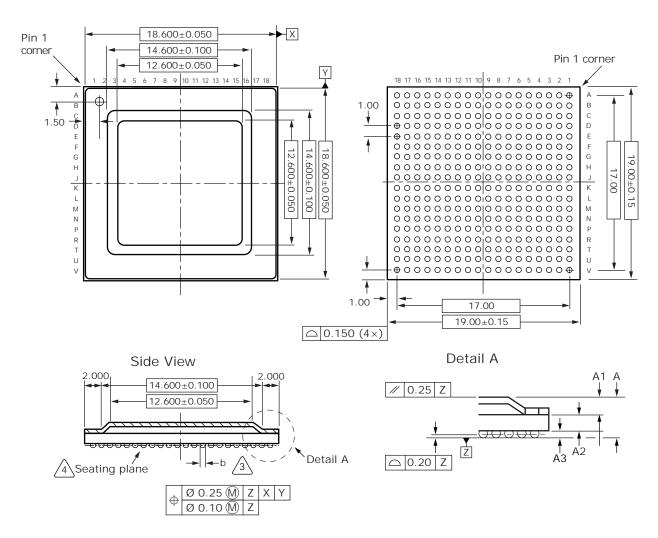

| 7 | Раска | age into                                            | ormation                                                                                                                                     | 330                      |

|   | 7.1   | Packag                                              | e Drawing                                                                                                                                    | 330                      |

|   | 7.2   | Therma                                              | al Specifications                                                                                                                            | 331                      |

|   | 7.3   | Moistur                                             | re Sensitivity                                                                                                                               | 332                      |

| 8 | Desig | n Guid                                              | lelines                                                                                                                                      | 333                      |

| - | 8.1   |                                                     | in LAN Mode                                                                                                                                  |                          |

|   | 8.2   | ,                                                   | in WAN Mode                                                                                                                                  |                          |

| 9 | Order | ina Info                                            | ormation                                                                                                                                     | 335                      |

# **Figures**

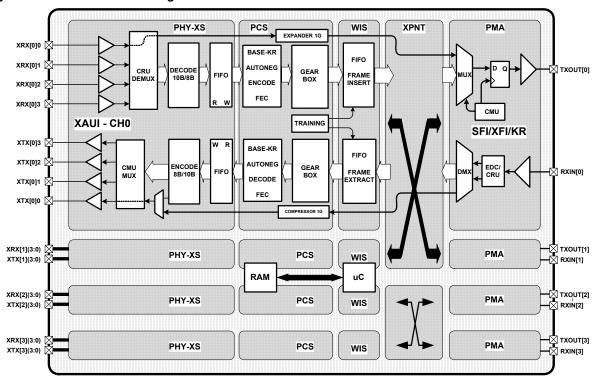

| Figure 1  | VSC8484 Block Diagram                               | 4    |

|-----------|-----------------------------------------------------|------|

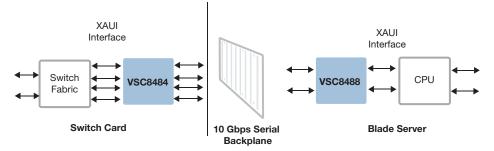

| Figure 2  | Backplane Equalization Application Diagram          | 4    |

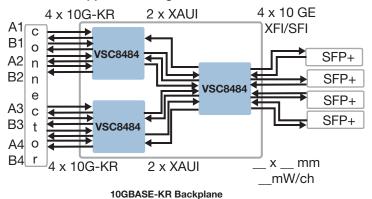

| Figure 3  | KR Backplane to SFP+ Application Diagram            | 5    |

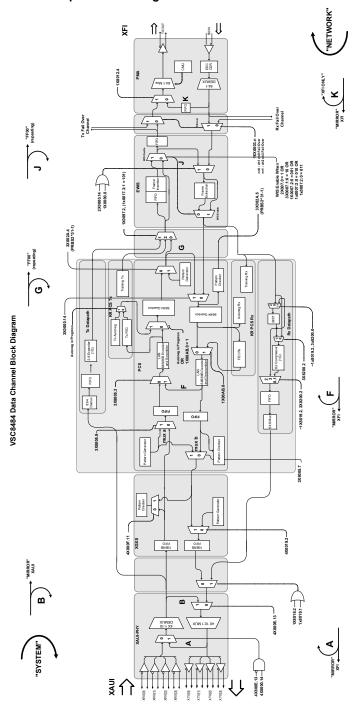

| Figure 4  | VSC8484 Channel Datapath Block Diagram              | 7    |

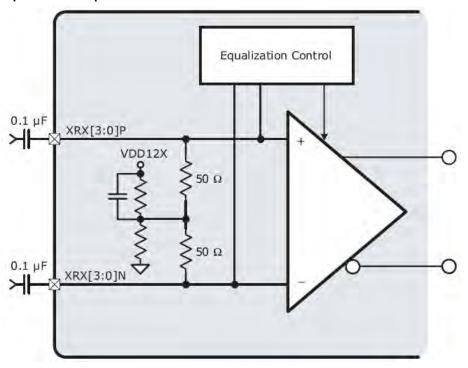

| Figure 5  | Rx Input Receiver                                   |      |

| Figure 6  | EDC Block Diagram                                   |      |

| Figure 7  | 10BASE-KR Output Driver                             | . 15 |

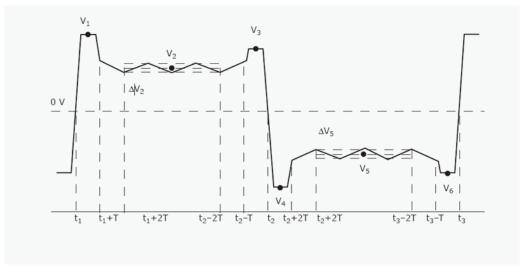

| Figure 8  | KR Test Pattern                                     |      |

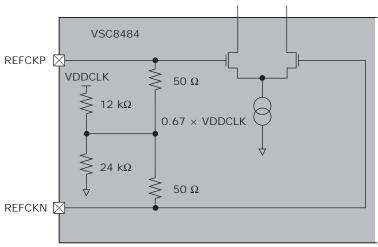

| Figure 9  | Reference Clock Input Receiver                      |      |

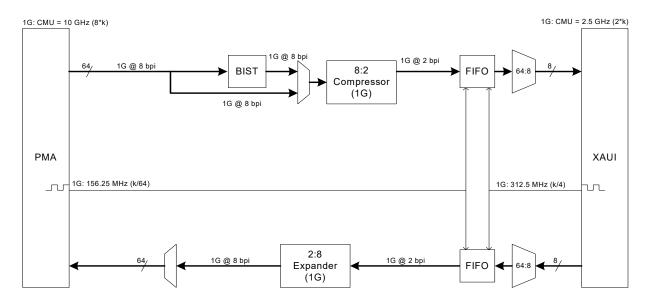

| Figure 10 | 1G Mode                                             |      |

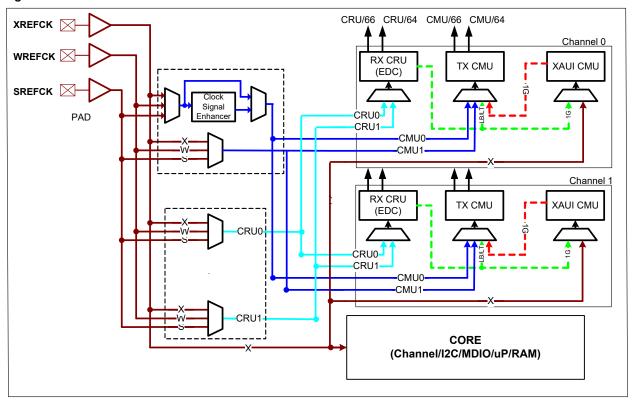

| Figure 11 | REFCLK Distribution                                 |      |

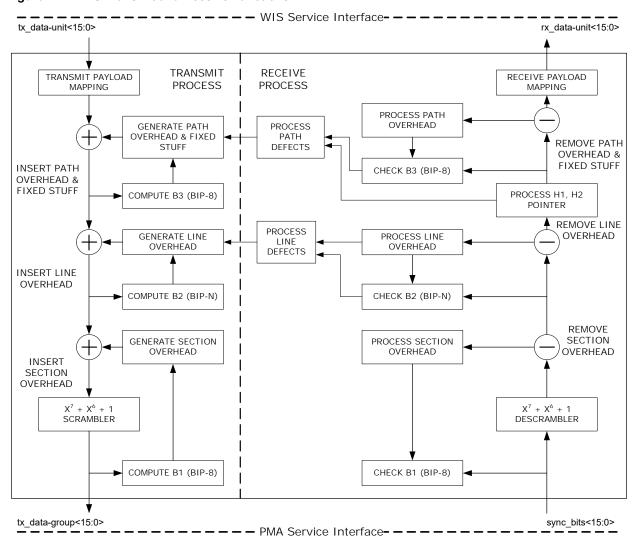

| Figure 12 | WIS Transmit and Receive Functions                  |      |

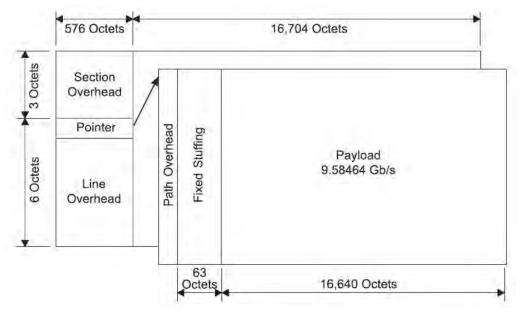

| Figure 13 | WIS Frame Structure                                 |      |

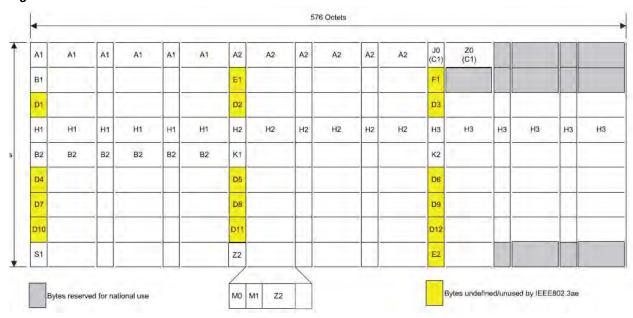

| Figure 14 | STS-192c/STM-64 Section and Line Overhead Structure |      |

| Figure 15 | Path Overhead Octets                                |      |

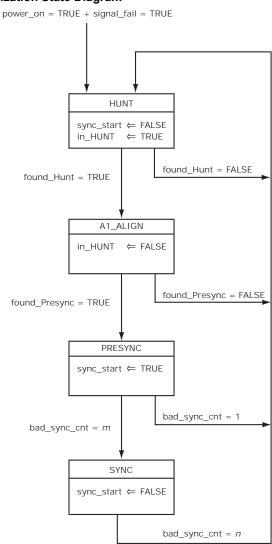

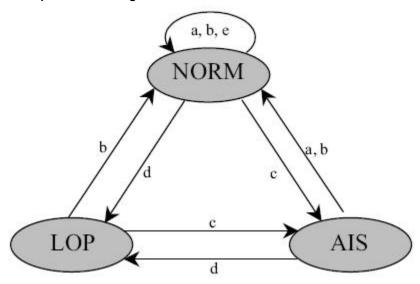

| Figure 16 | Primary Synchronization State Diagram               |      |

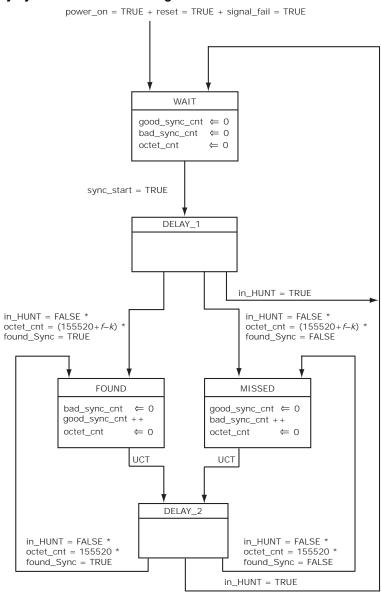

| Figure 17 | Secondary Synchronization State Diagram             |      |

| Figure 18 | 16-bit Designations within Payload Pointer          |      |

| Figure 19 | Pointer Interpreter State Diagram                   |      |

| Figure 20 | Path Status (G1) Byte for ERDI RDIN = 0             |      |

| Figure 21 | Path Status (G1) Byte for ERDI_RDIN = 1             |      |

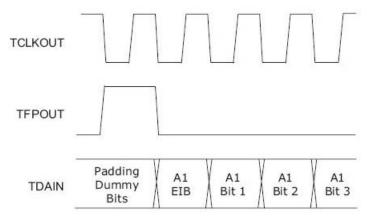

| Figure 22 | TOSI Timing Diagram                                 |      |

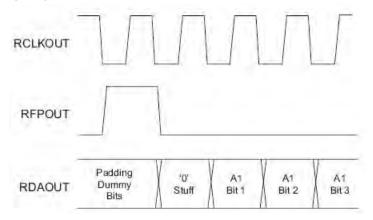

| Figure 23 | ROSI Timing Diagram                                 |      |

| Figure 24 | PCS Block Diagram                                   |      |

| Figure 25 | 64B/66B Block Formats                               |      |

| Figure 26 | Simplified XAUI Inputs                              |      |

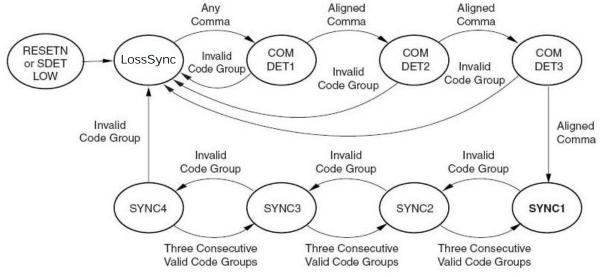

| Figure 27 | Loss of Synchronization State Diagram               |      |

|           |                                                     |      |

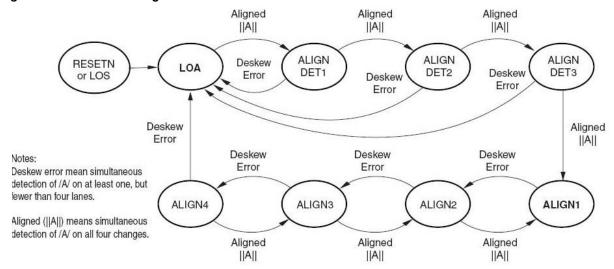

| Figure 28 | LOA State Diagram                                   |      |

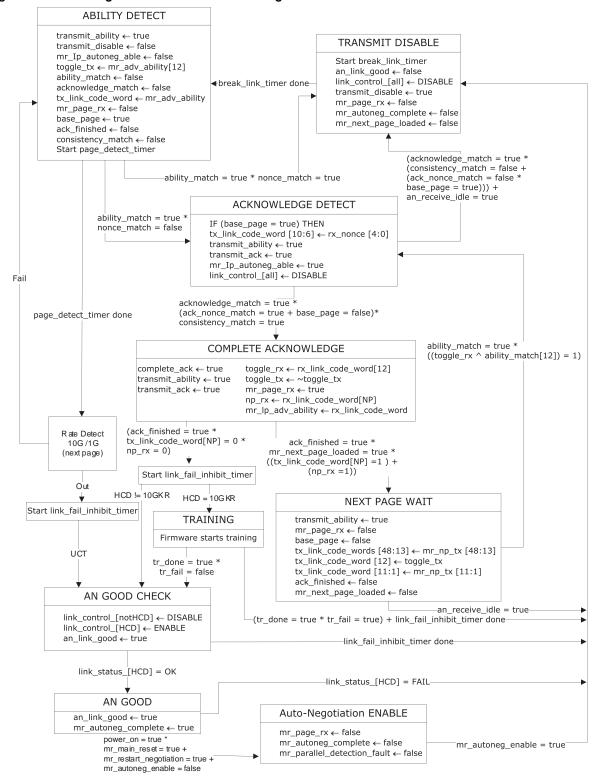

| Figure 29 | Auto-negotiation Arbitration State Diagram          |      |

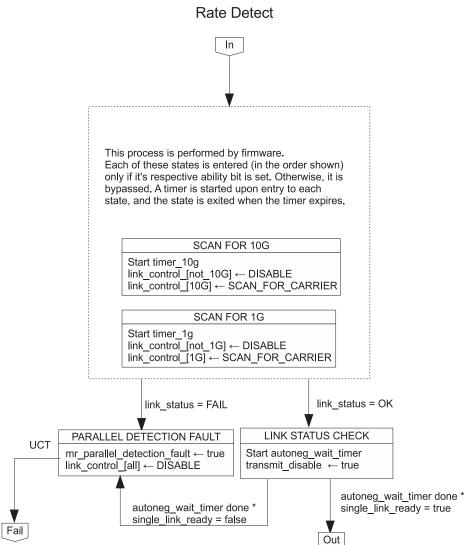

| Figure 30 | Rate Detection                                      |      |

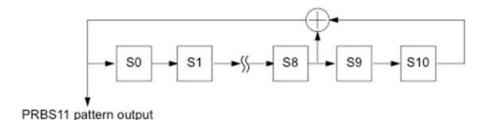

| Figure 31 | PRBS Pattern Generator                              |      |

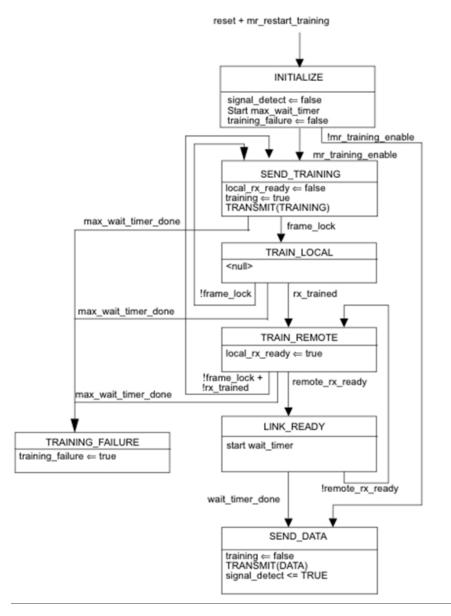

| Figure 32 | Training State Diagram                              |      |

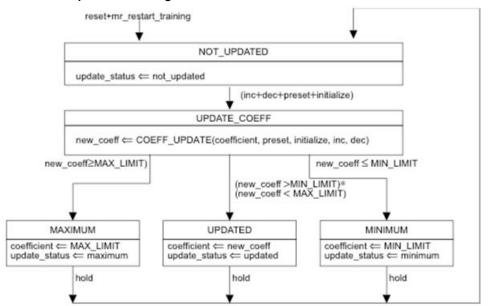

| Figure 33 | Coefficient Update State Diagram                    |      |

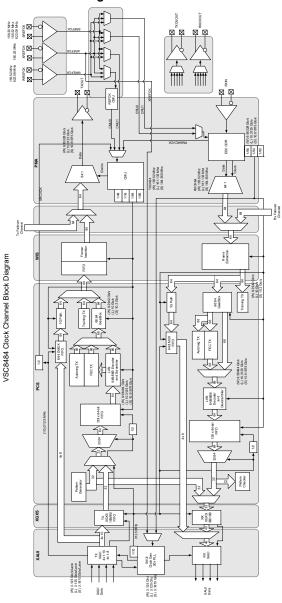

| Figure 34 | VSC8484 Channel Clock Block Diagram                 |      |

| Figure 35 | MDIO Frame Format                                   |      |

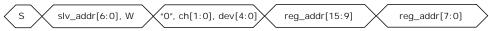

| Figure 36 | Two-Wire Serial (slave) Register Addressing Format  |      |

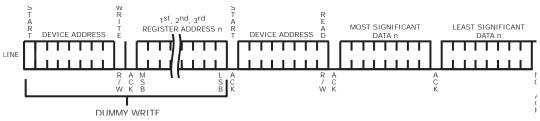

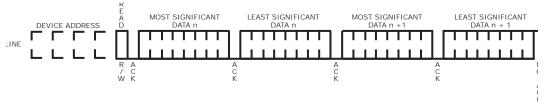

| Figure 37 | Write Instruction                                   |      |

| Figure 38 | Sequential Write Instruction                        |      |

| Figure 39 | Read Instruction                                    |      |

| Figure 40 | Sequential Read Instruction                         |      |

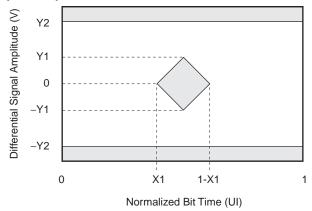

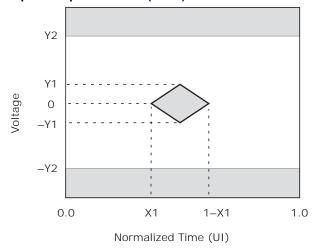

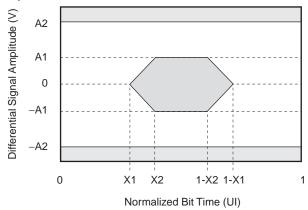

| Figure 41 | Receive Path Input Compliance Mask                  |      |

| Figure 42 | 10-Gigabit Data Input Compliance Mask (SFP+)        |      |

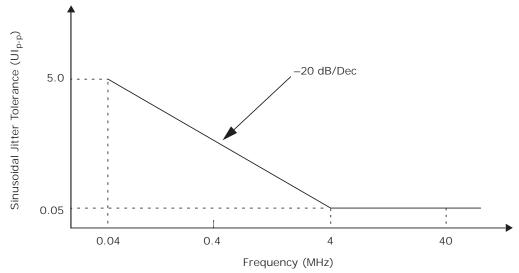

| Figure 43 | SFI Datacom Sinusoidal Jitter Tolerance             |      |

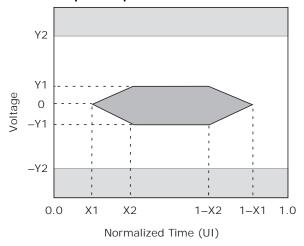

| Figure 44 | SFI Transmit Differential Output Compliance Mask    |      |

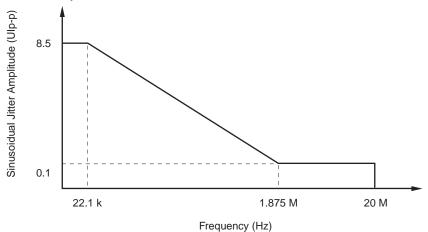

| Figure 45 | XAUI Receiver Input Sinusoidal Jitter Tolerance     |      |

| Figure 46 | XAUI Output Compliance Mask                         |      |

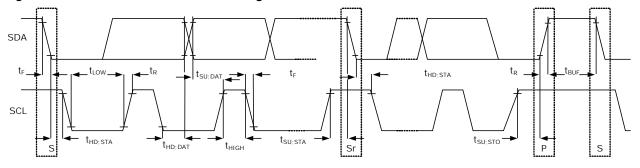

| Figure 47 | Two-Wire Serial Interface Timing                    |      |

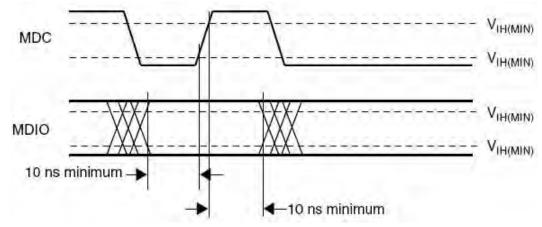

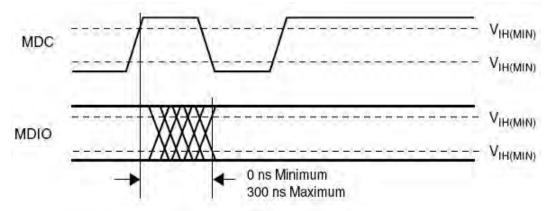

| Figure 48 | Timing with MDIO Sourced by STA                     |      |

| Figure 49 | Timing with MDIO Sourced by MMD                     |      |

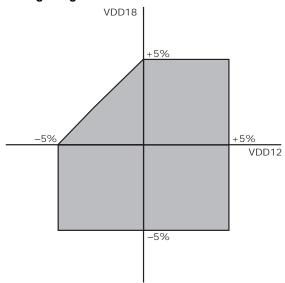

| Figure 50 | Power Supply Operating Range                        |      |

| Figure 51 | Pin Diagram                                         |      |

| Figure 52 | Package Drawing                                     |      |

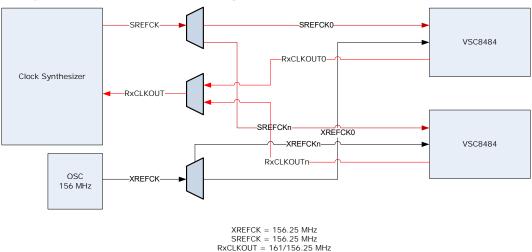

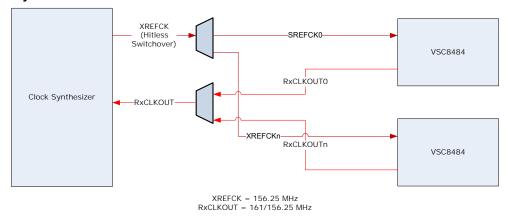

| Figure 53 | Sync-E LAN Mode with Free-Running Clock             |      |

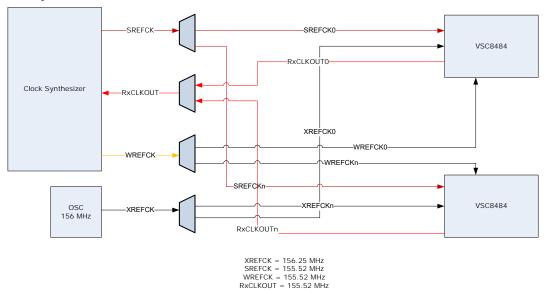

| Figure 54 | Sync-E LAN Mode with Hitless Clock                  | 334  |

# **Tables**

| Table 1  | Supported Data Rates and Standards                        | . 9 |

|----------|-----------------------------------------------------------|-----|

| Table 2  | Rx CDR Lock to Reference Settings                         | 11  |

| Table 3  | Rx Loss of Lock Detection Settings                        | 11  |

| Table 4  | Rx CDR Reference Clock Source Selection                   | 12  |

| Table 5  | Rx CDR Divide Ratio and Rate Selection                    | 12  |

| Table 6  | Rx Data Bus Control                                       |     |

| Table 7  | Tx Loss of Lock Detection Settings                        |     |

| Table 8  | Tx CMU Reference Clock Source Selection                   | 14  |

| Table 9  | Tx CMU Divide Ratio Selection                             |     |

| Table 10 | Tx Transmit Data Bus Control                              |     |

| Table 11 | Tx Transmit Output Waveform Changes by Coefficient Update |     |

| Table 12 | Tx Output Slew Rate Control Setting                       |     |

| Table 13 | Tx Output Driver Rise/Fall Time Control                   |     |

| Table 14 | Tx Transmit Data Bus Control                              |     |

| Table 15 | PMA Loopback                                              |     |

| Table 16 | PMA LINETIME                                              |     |

| Table 17 | CRU0 and CRU1 Paths Source Selection                      |     |

| Table 18 | CMU0 Path Source Selection                                |     |

| Table 19 | CMU1 Path Source Selection                                |     |

| Table 20 | PMA Reference Clock Rates and Modes                       |     |

| Table 21 | PMA Clock Output Setting                                  |     |

| Table 21 | PMA Rx Data Rate Mode                                     |     |

| Table 22 | Recommended Clock Operation Modes                         |     |

| Table 23 | WAN Mode Enable Logic                                     |     |

| Table 25 |                                                           |     |

| Table 25 | Section Overhead                                          |     |

|          | Framing Parameter Description and Values                  |     |

| Table 27 | Line Overhead Octets                                      |     |

| Table 28 | K2 Encodings                                              |     |

| Table 29 | SONET/SDH Pointer Mode Differences                        |     |

| Table 30 | H1/H2 Pointer Types                                       |     |

| Table 31 | Concatenation Indication Types                            |     |

| Table 32 | Pointer Interpreter State Diagram Transitions             |     |

| Table 33 | STS Path Overhead Octets                                  |     |

| Table 34 | RDI-P and ERDI-P Bit Settings and Interpretation          |     |

| Table 35 | PMTICK Counters                                           |     |

| Table 36 | Defects and Anomalies                                     |     |

| Table 37 | TOSI/ROSI Addresses                                       |     |

| Table 38 | Control Codes                                             |     |

| Table 39 | Checker Status Bits                                       |     |

| Table 40 | Status Register States                                    |     |

| Table 41 | Failover Modes                                            | 62  |

| Table 42 | Technology Ability Field                                  |     |

| Table 43 | Auto-negotiation Timers                                   |     |

| Table 44 | Advertised Ability Fields                                 |     |

| Table 45 | Training Frame Lengths                                    |     |

| Table 46 | Local Transmitter Equalization Registers and Bits         |     |

| Table 47 | Coefficient Update Field                                  |     |

| Table 48 | Increment/Decrement Register States                       |     |

| Table 49 | Status Report Field                                       | 71  |

| Table 50 | Register Settings for Training                            |     |

| Table 51 | 1x8097 (Shadowed to 1x0097)                               |     |

| Table 52 | Tx Output Waveform Requirements by Coefficient Update     |     |

| Table 53 | Tx Output Waveform Requirements by Coefficient Status     |     |

| Table 54 | System Loopback Summary                                   | 76  |

| Table 55  | Network Loopback Summary                             |       |

|-----------|------------------------------------------------------|-------|

| Table 56  | MDIO Port Addresses Per Channel                      | 79    |

| Table 57  | Management Frame Format for Indirect Register Access |       |

| Table 58  | MDIO Register Address to RAM Address Mapping         | 8′    |

| Table 59  | JTAG Instruction Codes                               |       |

| Table 60  | Operating Modes for Pin Control                      | 85    |

| Table 61  | GPIO Functions                                       | 88    |

| Table 62  | Rx PCS Activity Monitor States                       | 91    |

| Table 63  | Tx PCS Activity Monitor States                       |       |

| Table 64  | Temperature Monitor                                  |       |

| Table 65  | Digital Temperature Monitor Control Register         |       |

| Table 66  | Temperature Alarm Threshold Register                 |       |

| Table 67  | Temperature Alarm Register                           | 93    |

| Table 68  | Device ID (1Ex0000)                                  |       |

| Table 69  | Device Revision (1Ex0001)                            |       |

| Table 70  | Block Level Software Reset (1Ex0002)                 |       |

| Table 71  | Failover Crosspoint Control (1Ex0003)                |       |

| Table 72  | Timer Control (1Ex0004)                              |       |

| Table 73  | GPIO 0 Config/ Status (1Ex0100)                      | 97    |

| Table 74  | GPIO 0 Config2 (1Ex0101)                             | 98    |

| Table 75  | GPIO 1 Config/ Status (1Ex0102)                      | 100   |

| Table 76  | GPIO 1 Config2 (1Ex0103)                             |       |

| Table 77  | GPIO 2 Config/ Status (1Ex0104)                      |       |

| Table 78  | GPIO 2 Config2 (1Ex0105)                             |       |

| Table 79  | GPIO 3 Config/ Status (1Ex0106)                      |       |

| Table 80  | GPIO 3 Config2 (1Ex0107)                             |       |

| Table 81  | GPIO 4 Config/ Status (1Ex0108)                      |       |

| Table 82  | GPIO 4 Config2 (1Ex0109)                             |       |

| Table 83  | GPIO 5 Config/ Status (1Ex010A)                      |       |

| Table 84  | GPIO 5 Config2 (1Ex010B)                             |       |

| Table 85  | GPIO 6 Config/ Status (1Ex010C)                      |       |

| Table 86  | GPIO 6 Config2 (1Ex010D)                             |       |

| Table 87  |                                                      |       |

| Table 88  | GPIO 7 Config/ Status (1Ex010E)                      |       |

|           | GPIO 7 Config2 (1Ex010F)                             | 1 1 t |

| Table 89  | GPIO 8 Config/ Status (1Ex0110)                      | 12    |

| Table 90  | GPIO 8 Config2 (1Ex0111)                             | 124   |

| Table 91  | GPIO 9 Config/ Status (1Ex0112)                      |       |

| Table 92  | GPIO 9 Config2 (1Ex0113)                             |       |

| Table 93  | GPIO 10 Config/ Status (1Ex0114)                     |       |

| Table 94  | GPIO 10 Config2 (1Ex0115)                            |       |

| Table 95  | GPIO 11 Config/ Status (1Ex0116)                     | 130   |

| Table 96  | GPIO 11 Config2 (1Ex0117)                            |       |

| Table 97  | GPIO 12 Config/ Status (1Ex0118)                     |       |

| Table 98  | GPIO 12 Config2 (1Ex0119)                            |       |

| Table 99  | GPIO 13 Config/ Status (1Ex011A)                     |       |

| Table 100 | GPIO 13 Config2 (1Ex011B)                            |       |

| Table 101 | GPIO 14 Config/ Status (1Ex011C)                     |       |

| Table 102 | GPIO 14 Config2 (1Ex011D)                            |       |

| Table 103 | GPIO 15 Config/ Status (1Ex011E)                     |       |

| Table 104 | GPIO 15 Config2 (1Ex011F)                            |       |

| Table 105 | GPIO 16 Config/ Status (1Ex0120)                     |       |

| Table 106 | GPIO 16 Config2 (1Ex0121)                            |       |

| Table 107 | GPIO 17 Config/ Status (1Ex0122)                     |       |

| Table 108 | GPIO 17 Config2 (1Ex0123)                            |       |

| Table 109 | GPIO 18 Config/ Status (1Ex0124)                     |       |

| Table 110 | GPIO 18 Config2 (1Ex0125)                            |       |

| Table 111 | GPIO 19 Config/ Status (1Ex0126)                     | 153   |

| Table 112 | GPIO 19 Config2 (1Ex0127)                            |       |

| Table 113 | GPIO 20 Config/ Status (1Ex0128)                     | 157   |

| Table 114 | GPIO 20 Config2 (1Ex0129)                            |     |

|-----------|------------------------------------------------------|-----|

| Table 115 | GPIO 21 Config/ Status (1Ex012A)                     |     |

| Table 116 | GPIO 21 Config2 (1Ex012B)                            |     |

| Table 117 | GPIO 22 Config/ Status (1Ex012C)                     | 163 |

| Table 118 | GPIO 22 Config2 (1Ex012D)                            | 164 |

| Table 119 | GPIO 23 Config/ Status (1Ex012E)                     | 166 |

| Table 120 | GPIO 23 Config2 (1Ex012F)                            |     |

| Table 121 | PMA Global Spare Control 0 (1Ex7F00)                 |     |

| Table 122 | PMA Global Spare Control 1 (1Ex7F01)                 |     |

| Table 123 | PMA Global Spare Status 0 (1Ex7F02)                  |     |

| Table 124 | PMA Global Refclk Select (1Ex7F10)                   |     |

| Table 125 | PMA Global Refclk CMU Control (1Ex7F11)              |     |

| Table 126 | Factory Test Register (1Ex7FD4)                      |     |

| Table 127 | Temperature Monitor Threshold Settings (1Ex7FD5)     | 170 |

| Table 128 | Temperature Monitor Regs (1Ex7FD6)                   |     |

| Table 129 | Factory Test Only (1Ex7FD7)                          |     |

| Table 129 | Checksum Control (1Ex7FE0)                           |     |

|           |                                                      |     |

| Table 131 | Watchdog Counter (1Ex7FE1)                           |     |

| Table 132 | PMA_CTRL1: PMA Control 1 (1x0000)                    |     |

| Table 133 | PMA_STAT1: PMA Status 1 (1x0001)                     |     |

| Table 134 | PMA Device Identifier 1 (1x0002)                     |     |

| Table 135 | PMA Device Identifier 2 (1x0003)                     |     |

| Table 136 | PMA/PMD Speed Ability (1x0004)                       |     |

| Table 137 | PMA/PMD Devices in Package (1x0005)                  |     |

| Table 138 | PMA/PMD Devices in Package (1x0006)                  |     |

| Table 139 | PMA/PMD Control 2 (1x0007)                           |     |

| Table 140 | PMA/PMD Status 2 (1x0008)                            |     |

| Table 141 | PMD Transmit Disable (1x0009)                        |     |

| Table 142 | PMD Receive Signal Detect (1x000A)                   | 177 |

| Table 143 | PMA/PMD Package Identifier (1x000E)                  | 177 |

| Table 144 | PMA/PMD Package Identifier (1x000F)                  | 177 |

| Table 145 | KR Training Control (1x0096)                         | 177 |

| Table 146 | KR Training Status (1x0097)                          | 177 |

| Table 147 | KR Training LP Coeff Update (1x0098)                 |     |

| Table 148 | KR Training LP Status Report (1x0099)                | 178 |

| Table 149 | KR Training LD Coeff Update (1x009A)                 | 178 |

| Table 150 | KR Training LD Status Report (1x009B)                | 179 |

| Table 151 | KR Training Status (from Firmware) (1x8097)          | 179 |

| Table 152 | KR Training LD Coeff Update (from Firmware) (1x809A) |     |

| Table 153 | KR Training Control 2 (1x8201)                       |     |

| Table 154 | KR Training Status 2 (1x8208)                        |     |

| Table 155 | KR Training Pattern Error Count (1x8209)             |     |

| Table 156 | KR Training Frames Counted (1x820A)                  |     |

| Table 157 | KR Training Frames to Count (1x820B)                 |     |

| Table 158 | KR Training wait_timer Setting (1x820C)              |     |

| Table 159 | KR Training max_wait_timer Setting 1 (1x820D)        | 181 |

| Table 160 | KR Training max_wait_timer Setting 2 (1x820E)        |     |

| Table 161 | KR FEC Ability (1x00AA)                              |     |

| Table 162 | KR FEC Control 1 (1x00AB)                            |     |

| Table 163 | KR FEC Corrected Lower (1x00AC)                      |     |

| Table 163 | KR FEC Corrected Upper (1x00AD)                      |     |

| Table 164 | KR FEC Uncorrected Lower (1x00AE)                    |     |

|           |                                                      |     |

| Table 166 | KR FEC Uncorrected Upper (1x00AF)                    |     |

| Table 167 | KR FEC Control 2 (1x8300)                            |     |

| Table 168 | PMA_reset_LH (1x8000)                                |     |

| Table 169 | PMA_TXSTAT: PMA Tx Status (1x8001)                   |     |

| Table 170 | PMA_RXSTAT: PMA Rx Status (1x8002)                   | 183 |

| Table 171 | PMA_RXEDCCTRL: PMA Rx EDC Control (1x8003)           | 183 |

| Table 172 | PMA_RXDATACTRL: PMA Rx Data Control (1x8004)         | 184 |

| Table 173              | PMA_FIFOCTRL: PMA FIFO Control (1x8011)                                                   |     |

|------------------------|-------------------------------------------------------------------------------------------|-----|

| Table 174              | PMA_TXDATACTRL: PMA Tx Data Control (1x8012)                                              | 184 |

| Table 175              | PMA_TXOUTCTRL1: PMA Tx Output Driver Control 1 (1x8013)                                   | 185 |

| Table 176              | PMA_TXOUTCTRL2: PMA Tx Output Driver Control 2 (1x8014)                                   |     |

| Table 177              | PMA_TXRATECTRL: PMA Tx Rate Control (1x8015)                                              |     |

| Table 178              | PMA_TXRATECTRL: PMA Tx Rate Control (1x8017)                                              |     |

| Table 179              | PMA_TXRATECTRL: PMA Tx Rate Control (1x8018)                                              |     |

| Table 180              | PMA_RXRATECTRL: PMA Rx Rate Control (1x8019)                                              |     |

| Table 181              | Factory Test Register (1x8030)                                                            |     |

| Table 182              | Factory Test Register (1x8031)                                                            |     |

| Table 183              | Factory Test Register (1x8034)                                                            |     |

| Table 184              | Factory Test Register (1x8035)                                                            |     |

| Table 185              | Factory Test Register (1x8036)                                                            |     |

| Table 186              | Factory Test Register (1x8037)                                                            |     |

| Table 187              | Factory Test Register (1x8038)                                                            |     |

| Table 188              | Factory Test Register (1x8039)                                                            |     |

| Table 189              | Factory Test Register (1x8034)                                                            |     |

| Table 199              | Factory Test Register (1x803B)                                                            |     |

|                        |                                                                                           |     |

| Table 191              | LOS Status (1x8141)                                                                       |     |

| Table 192              | LOS_Detection_Source (1x8142)                                                             |     |

| Table 193              | Factory Test Register (1x8151)                                                            |     |

| Table 194              | Driver Coeff PRESET Settings for CM1 (1x8210)                                             |     |

| Table 195              | Driver Coeff PRESET Settings for C0 and CP1 (1x8211)                                      |     |

| Table 196              | Driver Coeff INITIALIZE Settings for CM1 (1x8212)                                         |     |

| Table 197              | Driver Coeff INITIALIZE Settings for C0 and CP1 (1x8213)                                  |     |

| Table 198              | Driver Coeff Step Size (1x8214)                                                           |     |

| Table 199              | RX_ALARM Control Register (1x9000)                                                        |     |

| Table 200              | TX_ALARM Control Register (1x9001)                                                        |     |

| Table 201              | RX_ALARM Status Register (1x9003)                                                         |     |

| Table 202              | TX_ALARM Status Register (1x9004)                                                         |     |

| Table 203              | Rx Clock Output Control (1xA008)                                                          |     |

| Table 204              | Tx Clock Output Control (1xA009)                                                          |     |

| Table 205              | Vendor Specific PMA Control 2 (1xA100)                                                    |     |

| Table 206              | Vendor Specific PMA Status 2 (1xA101)                                                     | 193 |

| Table 207              | Vendor Specific LOPC Status (1xA200)                                                      |     |

| Table 208              | Vendor Specific LOPC Control (1xA201)                                                     |     |

| Table 209              | Reset (1xAE00)                                                                            |     |

| Table 210              | WIS_CTRL1: WIS Control 1 (2x0000)                                                         |     |

| Table 211<br>Table 212 | WIS_STAT1: WIS Status 1 (2x0001)                                                          |     |

| Table 212              | WIS_DEVID1: WIS Device Identifier 1 (2x0002) WIS_DEVID2: WIS Device Identifier 2 (2x0003) |     |

| Table 213              | WIS SPEED: WIS Speed Capability (2x0004)                                                  |     |

| Table 214              | WIS_DEVPKG1: WIS Devices in Package 1 (2x0005)                                            |     |

| Table 216              | WIS DEVPKG2: WIS Devices in Package 1 (2x0003)                                            |     |

| Table 217              | WIS_CTRL2: WIS Control 2 (2x0007)                                                         |     |

| Table 217              | WIS STAT2: WIS Status 2 (2x0007)                                                          |     |

| Table 219              | WIS_TSTPAT_CNT: WIS Test Pattern Error Counter (2x0009)                                   |     |

| Table 219              | WIS_PKGID1: WIS Package Identifier 1 (2x000E)                                             |     |

| Table 221              | WIS_PKGID2: WIS Package Identifier 2 (2x000F)                                             |     |

| Table 221              | WIS STAT3: WIS Status 3 (2x0021)                                                          |     |

| Table 223              | WIS_REI_CNT: WIS Far-End Path Block Error Count (2x0025)                                  |     |

| Table 223              | WIS_TXJ1: WIS Tx J1s (Octets 13-0) (2x0027-002D)                                          |     |

| Table 224              | WIS_TXJ1B: WIS Tx J1s (Octets 15-0) (2x0027-002D)                                         |     |

| Table 225              | WIS_RXJ1: WIS Rx J1s (Octets 15-14) (2x002E)                                              |     |

| Table 227              | WIS_REIL_CNT1: WIS Far-End Line BIP Errors 1 (2x0037)                                     |     |

| Table 228              | WIS_REIL_CNT0: WIS Far-End Line BIP Errors 0 (2x0038)                                     |     |

| Table 229              | WIS_B2_CNT1: WIS L-BIP Error Count 1 (2x0039)                                             |     |

| Table 230              | WIS_B2_CNT0: WIS L-BIP Error Count 0 (2x003A)                                             |     |

| Table 231              | WIS_B3_CNT: WIS P-BIP Block Error Count (2x003B)                                          |     |

|                        |                                                                                           |     |

| Table 232 | WIS_B1_CNT: WIS S-BIP Error Count (2x003C)                      |                 |

|-----------|-----------------------------------------------------------------|-----------------|

| Table 233 | WIS_TXJ0: WIS Tx J0s (Octets 13-0) (2x0040-0046)                |                 |

| Table 234 | WIS_TXJ0B: WIS Tx J0s (Octets 15-14) (2x0047)                   | . 204           |

| Table 235 | WIS_RXJ0: WIS Rx J0s (2x0048-004F)                              | . 205           |

| Table 236 | EWIS_TXCTRL1: WIS Vendor Specific Tx Control 1 (2xE5FF)         | . 205           |

| Table 237 | EWIS_TXCTRL2: WIS Vendor Specific Tx Control 2 (2xE600)         | . 205           |

| Table 238 | Factory Test Register (2xE601)                                  |                 |

| Table 239 | Factory Test Register (2xE602)                                  | . 206           |

| Table 240 | Factory Test Register (2xE603)                                  | . 207           |

| Table 241 | Factory Test Register (2xE604)                                  | . 207           |

| Table 242 | Factory Test Register (2xE605)                                  | . 207           |

| Table 243 | Factory Test Register (2xE606)                                  |                 |

| Table 244 | EWIS_TX_A1_A2: E-WIS Tx A1/A2 Octets (2xE611)                   | . 207           |

| Table 245 | EWIS_TX_Z0_E1: E-WIS Tx Z0/E1 Octets (2xE612)                   | . 207           |

| Table 246 | EWIS_TX_F1_D1: E-WIS Tx F1/D1 Octets (2xE613)                   |                 |

| Table 247 | EWIS_TX_D2_D3: E-WIS Tx D2/D3 Octets (2xE614)                   |                 |

| Table 248 | EWIS_TX_C2_H1: E-WIS Tx C2/H1 Octets (2xE615)                   |                 |

| Table 249 | EWIS_TX_H2_H3: E-WIS Tx H2/H3 Octets (2xE616)                   |                 |

| Table 250 | EWIS_TX_G1_K1: E-WIS Tx G1/K1 Octets (2xE617)                   |                 |

| Table 251 | EWIS_TX_K2_F2: E-WIS Tx K2/F2 Octets (2xE618)                   |                 |

| Table 252 | EWIS_TX_D4_D5: E-WIS Tx D4/D5 Octets (2xE619)                   |                 |

| Table 253 | EWIS_TX_D6_H4: E-WIS Tx D6/H4 Octets (2xE61A)                   |                 |

| Table 254 | EWIS_TX_D7_D8: E-WIS Tx D7/D8 Octets (2xE61B)                   |                 |

| Table 255 | EWIS_TX_D9_Z3: E-WIS Tx D9/Z3 Octets (2xE61C)                   |                 |

| Table 256 | EWIS_TX_D10_D11: E-WIS Tx D10/D11 Octets (2xE61D)               |                 |

| Table 257 | EWIS_TX_D12_Z4: E-WIS Tx D12/Z4 Octets (2xE61E)                 |                 |

| Table 258 | EWIS_TX_S1_Z1: E-WIS Tx S1/Z1 Octets (2xE61F)                   |                 |

| Table 259 | EWIS_TX_Z2_E2: E-WIS Tx Z2/E2 Octets (2xE620)                   |                 |

| Table 260 | EWIS_TX_N1: E-WIS Tx N1 Octet (2xE621)                          |                 |

| Table 261 | Reserved (2xE622)                                               |                 |

| Table 261 | EWIS_TX_MSGLEN: E-WIS Tx Trace Message Length Control (2xE700)  |                 |

| Table 263 | EWIS_TX_INSGLEN. E-WIS TX Trace Message Length Control (2xE700) |                 |

| Table 264 | EWIS_RXJ0: E-WIS Rx J0s 16-63 (2xE900-E917)                     |                 |

| Table 265 | EWIS_TXJ1: E-WIS Tx WIS J1s 16-63 (2xEA00-EA17)                 |                 |

| Table 266 | EWIS_RXJ1: E-WIS Rx J1s 16-63 (2xEB00-EB17)                     |                 |

| Table 267 |                                                                 |                 |

|           | EWIS_RX_FRM_CTRL1: E-WIS Rx Framer Control 1 (2xEC00)           |                 |

| Table 268 | EWIS_RX_FRM_CTRL2: E-WIS Rx Framer Control 2 (2xEC01)           | . ∠ I o<br>24.4 |

| Table 269 |                                                                 |                 |

| Table 270 | EWIS_LOF_CTRL2: E-WIS Loss of Frame Control 2 (2xEC03)          |                 |

| Table 271 | EWIS_RX_CTRL1: E-WIS Rx Control 1 (2xEC10)                      | . 210           |

| Table 272 | EWIS_RX_MSGLEN: E-WIS Rx Trace Message Length Control (2xEC20)  | . 215           |

| Table 273 | EWIS_RX_ERR_FRC1: E-WIS Rx Error Force Control 1 (2xEC30)       |                 |

| Table 274 | EWIS_RX_ERR_FRC2: E-WIS Rx Error Force Control 2 (2xEC31)       |                 |

| Table 275 | EWIS_MODE_CTRL: E-WIS Mode Control (2xEC40)                     |                 |

| Table 276 | Factory Test Register (2xEC41)                                  | . 219           |

| Table 277 | EWIS_PRBS31_ANA_CTRL: E-WIS PRBS31 Analyzer Control (2xEC50)    |                 |

| Table 278 | EWIS_PRBS31_ANA_STAT: E-WIS PRBS31 Analyzer Status (2xEC51)     |                 |

| Table 279 | EWIS_PMTICK_CTRL: E-WIS Performance Monitor Control (2xEC60)    |                 |

| Table 280 | EWIS_CNT_CFG: E-WIS Counter Configuration (2xEC61)              |                 |

| Table 281 | EWIS_CNT_STAT: E-WIS Counter Status (2xEC62)                    |                 |

| Table 282 | EWIS_REIP_CNT1: E-WIS P-REI Counter 1 (MSW) (2xEC80)            |                 |

| Table 283 | EWIS_REIP_CNT0: E-WIS P-REI Counter 0 (LSW) (2xEC81)            | . 222           |

| Table 284 | EWIS_REIL_CNT1: E-WIS L-REI Counter 1 (MSW) (2xEC90)            |                 |

| Table 285 | EWIS_REIL_CNT0: E-WIS L-REI Counter 0 (LSW) (2xEC91)            |                 |

| Table 286 | B2 Rx debug (2xECA0)                                            |                 |

| Table 287 | EWIS_B1_ERR_CNT1: E-WIS S-BIP Error Counter 1 (MSW) (2xECB0)    |                 |

| Table 288 | EWIS_B1_ERR_CNT0: E-WIS S-BIP Error Counter 0 (LSW) (2xECB1)    |                 |

| Table 289 | EWIS_B2_ERR_CNT1: E-WIS L-BIP Error Counter 1 (MSW) (2xECB2)    |                 |

| Table 290 | EWIS_B2_ERR_CNT0: E-WIS L-BIP Error Counter 0 (LSW) (2xECB3)    | . 223           |

|           |                                                                 |                 |

| Table 291 | EWIS_B3_ERR_CNT1: E-WIS P-BIP Error Counter 1 (MSW) (2xECB4) |     |

|-----------|--------------------------------------------------------------|-----|

| Table 292 | EWIS_B3_ERR_CNT0: E-WIS P-BIP Error Counter 0 (LSW) (2xECB5) |     |

| Table 293 | Framer Debug 1 (2xED00)                                      |     |

| Table 294 | Framer Debug 2 (2xED01)                                      |     |

| Table 295 | Framer Debug 3 (2xED02)                                      |     |

| Table 296 | Framer Debug 4 (2xED03)                                      | 224 |

| Table 297 | Framer Debug 5 (2xED04)                                      | 224 |

| Table 298 | Rx SPE Debug Bus 1 (2xED05)                                  | 224 |

| Table 299 | Rx SPE Debug Bus 1 (2xED06)                                  | 225 |

| Table 300 | Rx SPE Debug Bus 2 (2xED07)                                  | 225 |

| Table 301 | Rx SPE Debug Bus 2 (2xED08)                                  | 225 |

| Table 302 | EWIS_RXTX_CTRL: E-WIS Rx to Tx Control (2xEDFF)              | 225 |

| Table 303 | EWIS_INTR_PEND1: E-WIS Interrupt Pending 1 (2xEE00)          |     |

| Table 304 | EWIS_INTR_MASKA_1: E-WIS Interrupt Mask A 1 (2xEE01)         | 227 |

| Table 305 | EWIS_INTR_MASKB_1: E-WIS Interrupt Mask B 1 (2xEE02)         | 229 |

| Table 306 | EWIS_INTR_STAT2: E-WIS Interrupt Status 2 (2xEE03)           | 230 |

| Table 307 | EWIS_INTR_PEND2: E-WIS Interrupt Pending 2 (2xEE04)          |     |

| Table 308 | EWIS_INTR_MASKA_2: E-WIS Interrupt Mask A 2 (2xEE05)         |     |

| Table 309 | EWIS_INTR_MASKB_2: E-WIS Interrupt Mask B 2 (2xEE06)         | 234 |

| Table 310 | WIS_FAULT_MASK (2xEE07)                                      | 236 |

| Table 311 | EWIS_INTR_PEND2: E-WIS Interrupt Pending 3 (2xEE08)          |     |

| Table 312 | EWIS_INTR_MASKA_3: E-WIS Interrupt Mask A 3 (2xEE09)         |     |

| Table 313 | EWIS_INTR_MASKB_3: E-WIS Interrupt Mask B 3 (2xEE0A)         |     |

| Table 314 | Threshold Error Status (2xEE0B)                              |     |

| Table 315 | WIS REI-P Threshold Level 1 (2xEE10)                         |     |

| Table 316 | WIS REI-P Threshold Level 2 (2xEE11)                         |     |

| Table 317 | WIS REI-L Threshold Level 1 (2xEE12)                         | 240 |

| Table 318 | WIS REI-L Threshold Level 2 (2xEE13)                         |     |

| Table 319 | WIS B1 Threshold Level 1 (2xEE14)                            | 240 |

| Table 320 | WIS B1 Threshold Level 2 (2xEE15)                            |     |

| Table 321 | WIS B2 Threshold Level 1 (2xEE16)                            |     |

| Table 322 | WIS B2 Threshold Level 2 (2xEE17)                            |     |

| Table 323 | WIS B3 Threshold Level 1 (2xEE18)                            |     |

| Table 324 | WIS B3 Threshold Level 2 (2xEE19)                            |     |

| Table 325 | Factory Test Registers (2xEF00 to 2xEF15)                    |     |

| Table 326 | PCS_CTRL1: PCS Control 1 (3x0000)                            |     |

| Table 327 | PCS Status 1 (3x0001)                                        |     |

| Table 328 | PCS Device Identifier 1 (3x0002)                             |     |

| Table 329 | PCS Device Identifier 2 (3x0003)                             |     |

| Table 330 | PCS Speed Ability (3x0004)                                   |     |

| Table 331 | PCS Devices in Package (3x0005)                              |     |

| Table 332 | PCS Devices in Package (3x0006)                              | 244 |

| Table 333 | PCS Control 2 Register (3x0007)                              |     |

| Table 334 | PCS Status 2 Register (3x0008)                               |     |

| Table 335 | PCS Package Identifier (3x000É)                              |     |

| Table 336 | PCS Package Identifier (3x000F)                              |     |

| Table 337 | 10GBASE-X Status (3x0018)                                    |     |

| Table 338 | 10GBASE-X Control (3x0019)                                   |     |

| Table 339 | 10GBASE-R PCS Status 1 (3x0020)                              |     |

| Table 340 | 10GBASE-R PCS Status 2 (3x0021)                              |     |

| Table 341 | 10GBASE-R PCS Test Pattern Seed A 3 (3x0022)                 |     |

| Table 342 | 10GBASE-R PCS Test Pattern Seed A 2 (3x0023)                 |     |

| Table 343 | 10GBASE-R PCS Test Pattern Seed A 2 (3x0024)                 |     |

| Table 344 | 10GBASE-R PCS Test Pattern Seed A 2 (3x0025)                 |     |

| Table 345 | 10GBASE-R PCS Test Pattern Seed B 3 (3x0026)                 |     |

| Table 346 | 10GBASE-R PCS Test Pattern Seed B 2 (3x0027)                 |     |

| Table 347 | 10GBASE-R PCS Test Pattern Seed B 1 (3x0028)                 |     |

| Table 348 | 10GBASE-R PCS Test Pattern Seed B 0 (3x0029)                 |     |

| Table 349 | 10GBASE-R PCS Test Pattern Control (3x002A)                  |     |

| Table 350 | 10GBASE-R PCS Test Pattern Counter (3x002B)              |       |

|-----------|----------------------------------------------------------|-------|

| Table 351 | Vendor Specific USR Test (3x8000)                        | . 248 |

| Table 352 | Vendor Specific USR Test (3x8001)                        |       |

| Table 353 | Vendor Specific USR Test (3x8002)                        | . 249 |

| Table 354 | Vendor Specific USR Test (3x8003)                        |       |

| Table 355 | Square Wave Pulse Width (3x8004)                         |       |

| Table 356 | Vendor Specific PCS Control (3x8005)                     | . 249 |

| Table 357 | Vendor Specific Test Error Counter 0 (3x8007)            | . 250 |

| Table 358 | Vendor Specific Test Error Counter 1 (3x8008)            | . 250 |

| Table 359 | Factory Test Only (3x8009)                               | . 251 |

| Table 360 | Factory Test Only (3x800C)                               | . 251 |

| Table 361 | Factory Test Only (3x800D)                               | . 251 |

| Table 362 | Factory Test Only (3x800E)                               |       |

| Table 363 | Factory Test Only (3x800F)                               | . 251 |

| Table 364 | Factory Test Only (3x8010)                               | . 251 |

| Table 365 | Factory Test Only (3x8011)                               | . 251 |

| Table 366 | Factory Test Only (3x8012)                               | . 251 |

| Table 367 | Factory Test Only (3x8013)                               | . 252 |

| Table 368 | Factory Test Only (3x8014)                               | . 252 |

| Table 369 | Factory Test Only (3x8015)                               | . 252 |

| Table 370 | Loopback FIFOs Stat/Ctrl (3x8016)                        | . 252 |

| Table 371 | Vendor Specific PCS 1G BIST Control (3x8200)             | . 252 |

| Table 372 | Vendor Specific PCS 1G BIST Status (3x8201)              |       |

| Table 373 | (3xE600)                                                 | 253   |

| Table 374 | PCS BIST Control 1 (3xE61A)                              |       |

| Table 375 | PCS BIST Control 2 (3xE61B)                              | . 254 |

| Table 376 | PCS BIST Error Counter (3xE61C)                          | . 254 |

| Table 377 | PCS BIST Status (3xE61D)                                 | . 254 |

| Table 378 | PCS Interrupt Pending 1 (3xEE00)                         |       |

| Table 379 | PCS Interrupt WIS_INT0 Mask 1 (3xEE01)                   | . 256 |

| Table 380 | PCS Interrupt WIS_INT1 Mask 1 (3xEE02)                   | . 257 |

| Table 381 | PCS Interrupt Error Status (3xEE03)                      |       |

| Table 382 | Tx Sequencing Error Count Threshold (3xEE04)             | . 258 |

| Table 383 | Rx Sequencing Error Count Threshold (3xEE05)             | . 258 |

| Table 384 | Tx Block Encode Error Count Threshold (3xEE06)           | . 258 |

| Table 385 | Rx Block Encode Error Count Threshold (3xEE07)           | . 258 |

| Table 386 | Tx Character Encode Error Count Threshold (3xEE08)       | . 258 |

| Table 387 | Rx Character Encode Error Count Threshold (3xEE09)       | . 259 |

| Table 388 | FEC Fixed Error Count Threshold (3xEE0A)                 | . 259 |

| Table 389 | FEC Fixed Error Count Threshold (3xEE0B)                 | . 259 |

| Table 390 | FEC Unfixable Error Count Threshold (3xEE0C)             | . 259 |

| Table 391 | FEC Unfixable Error Count Threshold (3xEE0D)             | . 259 |

| Table 392 | PCS Spare Control/Status (3xEF00 to 3xEF15)              | . 259 |

| Table 393 | PHYXS_CTRL1: PHY XS Control 1 (4x0000)                   | . 259 |

| Table 394 | PHYXS_STAT1: PHY XS Status1 (4x0001)                     | . 260 |

| Table 395 | PHYXS_DEVID1: PHY XS Device Identifier 1 (4x0002)        | . 261 |

| Table 396 | PHYXS_DEVID2: PHY XS Device Identifier 2 (4x0003)        | . 261 |

| Table 397 | PHYXS_SPEED: PHY XS Speed Capability (4x0004)            | . 261 |

| Table 398 | PHYXS_DEVPKG1: PHY XS Devices in Package 1 (4x0005)      |       |

| Table 399 | PHYXS_DEVPKG2: PHY XS Devices in Package 2 (4x0006)      | . 262 |

| Table 400 | PHYXS_STAT2: PHY XS Status 2 (4x0008)                    |       |

| Table 401 | PHYXS_PKGID1: WIS Package Identifier 1 (4x000E)          |       |

| Table 402 | PHYXS_PKGID2: WIS Package Identifier 2 (4x000F)          | . 263 |

| Table 403 | PHYXS_STAT3: PHY XS Status 3 (4x0018)                    |       |

| Table 404 | PHYXS_TSTCTRL1: PHY XGXS Test Control 1 (4x0019)         |       |

| Table 405 | PHYXS_TSTCTRL2: PHY XS Test Control 2 (4x8000)           |       |

| Table 406 | PHYXS_TSTSTAT: PHY XS Test Pattern Check Status (4x8001) |       |

| Table 407 | Factory Test Register (4x8002)                           |       |

| Table 408 | Factory Test Register (4x8003)                           | . 265 |

| Table 400 | Factory Test Degister (4y9004)                                       | 266 |

|-----------|----------------------------------------------------------------------|-----|

| Table 409 | Factory Test Register (4x8004)                                       |     |

| Table 410 | Factory Test Register (4x8005)                                       |     |

| Table 411 | Factory Test Register (4x8006)                                       |     |

| Table 412 | Factory Test Register (4x8007)                                       |     |

| Table 413 | Factory Test Register (4x8008)                                       |     |

| Table 414 | Factory Test Register (4x8009)                                       |     |

| Table 415 | Factory Test Register (4x800A)                                       | 267 |

| Table 416 | PHYXS_TPERR_CTRL: PHY XS Test Pattern Error Counter Control (4x800B) | 267 |

| Table 417 | PHYXS_TPERR_CNT0: PHY XS Test Pattern Error Counter 0 (LSW) (4x800C) |     |

| Table 418 | PHYXS TPERR CNT0: PHY XS Test Pattern Error Counter 1 (MSW) (4x800D) |     |

| Table 419 | PHYXS_XAUI_CTRL1: PHY XS XAUI Control 1 (4x800E)                     |     |

| Table 420 | PHYXS_XAUI_CTRL2: PHY XS XAUI Control 2 (4x800F)                     |     |

| Table 421 | PHYXS_RXEQ_CTRL: PHY XS XAUI Rx Equalization Control (4x8010)        |     |

| Table 422 | PHYXS_TXPE_CTRL: PHY XS XAUI Tx Pre-emphasis Control (4x8011)        |     |

| Table 423 | PHYXS_RXLOS_STAT: PHY XS Rx Loss of Signal Status (4x8012)           |     |

| Table 424 | PHYXS_RXSD_STAT: PHY XS Rx Signal Detect Status (4xE600)             | 271 |

| Table 425 | Factory Test Register (4xE601)                                       |     |

|           | PHYXS_TXPD_CTRL: PHY XS XAUI Tx Power Down Control (4xE602)          |     |

| Table 426 |                                                                      |     |

| Table 427 | PHYXS_RXPD_CTRL: PHY XS XAUI Rx Power Down Control (4xE603)          |     |

| Table 428 | FC_CJPAT_SEL (4xE604)                                                |     |

| Table 429 | Factory Test Registers (4xE610 to 4xEF15)                            |     |

| Table 430 | Auto-Negotiation Control (7x0000)                                    |     |

| Table 431 | AN Status (7x0001)                                                   |     |

| Table 432 | AN Advertisement Register 1 (7x0010)                                 |     |

| Table 433 | AN Advertisement Register 2 (7x0011)                                 |     |

| Table 434 | AN Advertisement Register 3 (7x0012)                                 |     |

| Table 435 | AN LP Base Page Ability Register 1 (7x0013)                          | 276 |

| Table 436 | AN LP Base Page Ability Register 2 (7x0014)                          | 276 |

| Table 437 | AN LP Base Page Ability Register 3 (7x0015)                          | 276 |

| Table 438 | AN XNP Transmit Register 1 (7x0016)                                  | 276 |

| Table 439 | AN XNP Transmit Register 2 (7x0017)                                  |     |

| Table 440 | AN XNP Transmit Register 3 (7x0018)                                  |     |

| Table 441 | AN LP XNP Ability Register 1 (7x0019)                                |     |

| Table 442 | AN LP XNP Ability Register 2 (7x001A)                                |     |

| Table 443 | AN LP XNP Ability Register 3 (7x001B)                                |     |

| Table 444 | BPS (7x0030)                                                         |     |

| Table 445 | Factory Test Register (7x8001)                                       |     |

| Table 446 | Factory Test Register (7x8013)                                       |     |

| Table 447 | Factory Test Register (7x8014)                                       |     |

| Table 448 | Factory Test Register (7x8015)                                       |     |

| Table 449 | Factory Test Register (7x8019)                                       |     |

| Table 449 |                                                                      |     |

|           | , ,                                                                  |     |

| Table 451 | Factory Test Register (7x801B)                                       |     |

| Table 452 | Factory Test Register (7x8030)                                       |     |

| Table 453 | Factory Test Register (7x8040)                                       |     |

| Table 454 | Factory Test Register (7x8041)                                       |     |

| Table 455 | Factory Test Register (7x8042)                                       |     |

| Table 456 | Factory Test Register (7x8043)                                       |     |

| Table 457 | Factory Test Register (7x8044)                                       |     |

| Table 458 | Factory Test Register (7x8045)                                       | 280 |

| Table 459 | Factory Test Register (7x8046)                                       |     |

| Table 460 | Factory Test Register (7x8047)                                       |     |

| Table 461 | Factory Test Register (7x8048)                                       | 280 |

| Table 462 | AN Vendor Status (7x8100)                                            | 280 |

| Table 463 | AN break_link_timer Setting 1 (7x810E)                               | 280 |

| Table 464 | AN break_link_timer Setting 2 (7x810F)                               | 280 |

| Table 465 | AN an_wait_timer Setting 1 (7x8110)                                  |     |

| Table 466 | AN an_wait_timer Setting 2 (7x8111)                                  |     |

| Table 467 | AN link_fail_inhibit_short_timer Setting 1 (7x8112)                  |     |

| Table 468 | AN link_fail_inhibit_short_timer Setting 2 (7x8113)  |     |

|-----------|------------------------------------------------------|-----|

| Table 469 | AN link_fail_inhibit_long_timer Setting 1 (7x8114)   |     |

| Table 470 | AN link_fail_inhibit_long_timer Setting 2 (7x8115)   | 281 |

| Table 471 | AN page_detect_timer Setting 1 (7x8116)              | 281 |

| Table 472 | AN page_detect_timer Setting 2 (7x8117)              | 281 |

| Table 473 | AN link_status_10G_timer Setting 1 (7x8118)          |     |

| Table 474 | AN link status 10G timer Setting 2 (7x8119)          |     |

| Table 475 | AN link_status_3G_timer Setting 1 (7x811A)           |     |

| Table 476 | Reserved (7x811B)                                    |     |

| Table 477 | Reserved (7x811C)                                    |     |

| Table 478 | AN link_status_1G_timer Setting 2 (7x811D)           |     |

| Table 479 | Factory Test Register (7x811E)                       |     |

| Table 480 | Factory Test Register (7x811F)                       |     |

| Table 481 | AN Hardware Arbitration State Machine State (7x8120) |     |

| Table 482 | Factory Test Register (7x8200)                       |     |

| Table 483 | Factory Test Register (7x8201)                       |     |

|           | Factory Test Register (7x8203)                       | 204 |

| Table 484 |                                                      |     |

| Table 485 | Factory Test Register (7x8204)                       |     |

| Table 486 | Factory Test Register (7x8205)                       |     |

| Table 487 | Factory Test Register (7x8220)                       |     |

| Table 488 | Factory Test Register (7xEF00)                       |     |

| Table 489 | Factory Test Register (7xEF01)                       |     |

| Table 490 | Factory Test Register (7xEF02)                       |     |

| Table 491 | Factory Test Register (7xEF03)                       |     |

| Table 492 | Factory Test Register (7xEF10)                       |     |

| Table 493 | Factory Test Register (7xEF11)                       |     |

| Table 494 | Factory Test Register (7xEF12)                       |     |

| Table 495 | Factory Test Register (7xEF13)                       |     |

| Table 496 | DC_AGC_LOS Config1 (1xB0C0)                          |     |

| Table 497 | DC_OFF_Timer1 (1xB0C1)                               |     |

| Table 498 | DC_OFF_Timer2 (1xB0C2)                               |     |

| Table 499 | AGC_Config2 (1xB0C3)                                 |     |

| Table 500 | AGC_Config3 (1xB0C4)                                 |     |

| Table 501 | AGC_Config4 (1xB0C5)                                 |     |

| Table 502 | LOS_Config2 (1xB0C6)                                 |     |

| Table 503 | FFE DAC 0 Control (1xB000)                           |     |

| Table 504 | FFE DAC 1 Control (1xB002)                           |     |

| Table 505 | FFE DAC 2 Control (1xB004)                           |     |

| Table 506 | FFE DAC 3 Control (1xB006)                           |     |

| Table 507 | FFE DAC 4 Control (1xB008)                           |     |

| Table 508 | FFE DAC 5 Control (1xB00A)                           |     |

| Table 509 | FFE DAC 6 Control (1xB00C)                           |     |

| Table 510 | FFE DAC 7 Control (1xB00E)                           |     |

| Table 511 | FFE DAC 8 Control (1xB010)                           |     |

| Table 512 | DFE DAC 0 Control (1xB018)                           |     |

| Table 513 | DFE DAC 1 Control (1xB01A)                           | 293 |

| Table 514 | DFE DAC 2 Control (1xB01C)                           |     |

| Table 515 | DFE DAC 3 Control (1xB01E)                           |     |

| Table 516 | FFE 0 Offset Control (1xB020)                        |     |

| Table 517 | FFE 1 Offset Control (1xB022)                        |     |

| Table 518 | FFE 2 Offset Control (1xB024)                        |     |

| Table 519 | FFE 3 Offset Control (1xB026)                        |     |

| Table 520 | FFE 4 Offset Control (1xB028)                        |     |

| Table 521 | FFE 5 Offset Control (1xB02A)                        |     |

| Table 522 | FFE 6 Offset Control (1xB02C)                        |     |

| Table 523 | FFE 7 Offset Control (1xB02E)                        |     |

| Table 524 | FFE 8 Offset Control (1xB030)                        |     |

| Table 525 | DFE 0 Offset Control (1xB038)                        |     |

| Table 526 | DFE 1 Offset Control (1xB03A)                        | 297 |

| Table 527 | DFE 2 Offset Control (1xB03C)                                  |       |

|-----------|----------------------------------------------------------------|-------|

| Table 528 | DFE 3 Offset Control (1xB03E)                                  |       |

| Table 529 | DC Sense Mux (1xB040)                                          | . 297 |

| Table 530 | Peak Detect (1xB042)                                           | . 298 |

| Table 531 | VGA0 Gain (1xB044)                                             | . 298 |

| Table 532 | VGA0 Boost (1xB046)                                            | . 298 |