Click here to ask an associate for production status of specific part numbers.

#### MAX20430

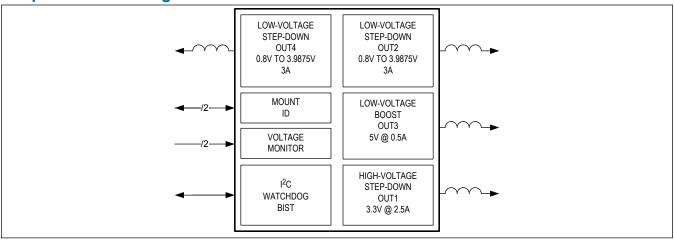

# Four-Output Mini PMIC for Safety Applications

# **General Description**

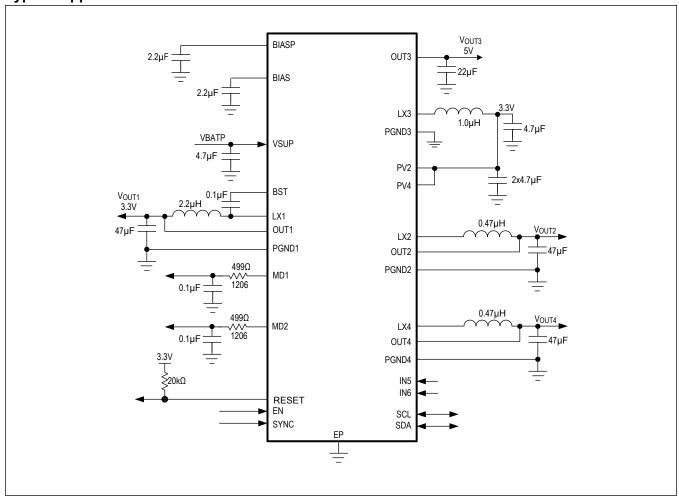

The MAX20430 is a high-efficiency, four-output DC-DC converter and windowed watchdog. OUT1 is a synchronous step-down converter that converts vehicle battery voltage to 3.3V at up to 2.5A. OUT3 boosts OUT1 to 5V at up to 500mA, while OUT2 and OUT4 low-voltage synchronous step-down converters operate from OUT1 and provide a 0.8V to 3.9875V output voltage range at up to 3A. All outputs achieve ±1.5% output error over load, line, and temperature range.

The device features 2.1MHz fixed-frequency PWM mode for all DC-DC outputs for better noise immunity and load-transient response. The 2.1MHz frequency operation allows for the use of all ceramic capacitors and minimizes external components. The programmable spread-spectrum frequency modulation minimizes radiated electromagnetic emissions. Integrated low R<sub>DSON</sub> switches improve efficiency at heavy loads and make the layout much simpler with respect to discrete solutions.

The device is offered with factory-preset output voltages. Other features include soft-start, overcurrent, and overtemperature protections.

# **Applications**

ADAS

# **Benefits and Features**

- Multiple Functions for Small Size

- Synchronous High-Voltage Buck Converter up to 2.5A

- Input Voltage Range 3.5V to 40V

- Output Voltage of 3.3V

- 5V Synchronous 500mA Boost Converter

- Dual Synchronous Buck Converters up to 3A

- 0.8V to 3.9875V in 12.5mV Steps

- Flexible Power Sequencer for OUT2, OUT3, and OUT4

- Programmable Challenge/Response or Windowed Watchdog

- Two Free Programmable UV/OV Voltage Monitors

- 0.8V to 3.9875V in 12.5mV Steps

- I<sup>2</sup>C Fast Mode Plus Compatible Interface with Packet Error-Checking Option (PEC)

- 2.1MHz Internal Operation with Spread-Spectrum Option

- RESET Output

- Current Mode, Forced PWM Operation

- High-Precision for ASIL Applications

- ±1.5% Output Voltage Accuracy

- ±1% OV/UV Monitoring

- Diagnostics and Redundant Circuits

- ASIL C Compliant

- Redundant Reference

- · BIST Diagnostics

- · Fail Safe on Open Pins

- Shorted Pin Detection on RESET

- Mount ID Location Detection

- Robust for the Automotive Environment

- Overtemperature and Short-Circuit Protection

- 5mm x 5mm Side-Wettable TQFN Package

- -40°C to +125°C Grade 1 Automotive Temperature Range

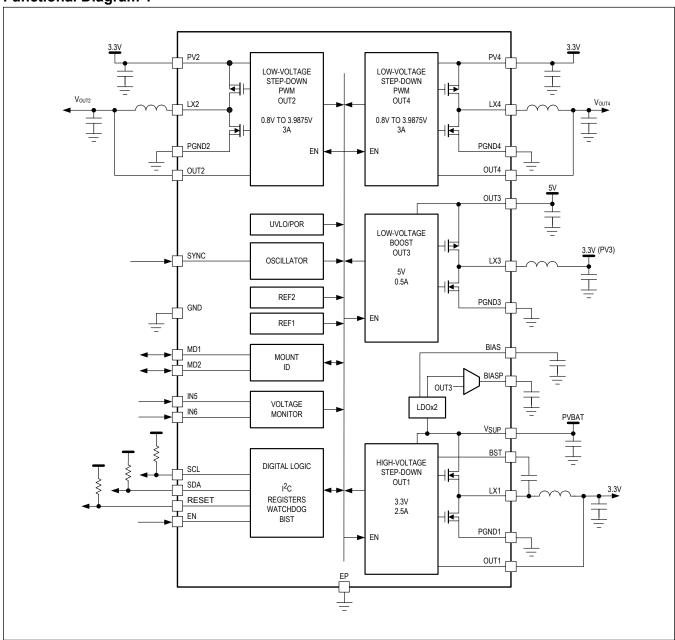

# **Simplified Block Diagram**

# **TABLE OF CONTENTS**

| General Description                           |    |

|-----------------------------------------------|----|

| Applications                                  |    |

| Benefits and Features                         |    |

| Simplified Block Diagram                      |    |

| Absolute Maximum Ratings                      |    |

| Package Information                           |    |

| 28-QFN-EP                                     |    |

| Electrical Characteristics                    |    |

| Typical Operating Characteristics             |    |

| Pin Configuration                             |    |

| MAX20430                                      |    |

| Pin Description                               |    |

| Functional Diagrams                           |    |

| Functional Diagram 1                          |    |

| Detailed Description                          |    |

| Challenge/Response Watchdog and Reset Control |    |

| Flexible Power Sequencer (FPS)                |    |

| Flexible Power Sequencer Timing               | 20 |

| RESET Output                                  | 20 |

| Enable Input Pin (EN)                         | 20 |

| Mount ID Input Pins (MD1, MD2)                | 21 |

| Mount ID Diagram                              | 22 |

| OFF Comparators                               | 22 |

| OV Shutdown Comparators                       | 22 |

| UV/OV Comparators                             | 22 |

| Internal Oscillator                           | 22 |

| Overtemperature Protection                    | 22 |

| I <sup>2</sup> C Interface                    | 23 |

| Timing Diagram                                | 23 |

| Bit Transfer                                  | 23 |

| STOP and START Conditions                     | 23 |

| START, STOP, and REPEATED START Conditions    | 24 |

| Early STOP Condition                          | 24 |

| Clock Stretching                              |    |

| I <sup>2</sup> C General Call Address         |    |

| Packet Error Checking (PEC)                   |    |

| Slave Address                                 | 24 |

| Acknowledge                                   | 24 |

| Acknowledge Condition                         |    |

# TABLE OF CONTENTS (CONTINUED)

| Write Data Format                         |    |

|-------------------------------------------|----|

| Read Data Format                          | 25 |

| Data Format of I <sup>2</sup> C Interface | 26 |

| Register Map                              | 27 |

| USER                                      | 27 |

| Register Details                          | 27 |

| Applications Information                  |    |

| Input Capacitors                          |    |

| Inductor Selection                        |    |

| Output Capacitors                         |    |

| Typical Application Circuits              |    |

| Typical Application Circuit               |    |

| Ordering Information                      |    |

| Revision History                          | 40 |

|                                           |    |

# LIST OF FIGURES

| 2.0. 0. 1.00%20                                      |      |

|------------------------------------------------------|------|

| Figure 1. Watchdog Control                           |      |

| Figure 2. Flexible Power Sequencer Timing            | . 20 |

| Figure 3. Power-On Control State Diagram             | . 21 |

| Figure 4. Mount ID Detection (One Channel Shown)     | . 22 |

| Figure 5. I <sup>2</sup> C Timing Diagram            | . 23 |

| Figure 6. START, STOP, and REPEATED START Conditions | . 24 |

| Figure 7. Acknowledge Condition                      | . 25 |

| Figure 8. Data Format of I <sup>2</sup> C Interface  | . 26 |

| MAX20430                         | Four-Output Mini PMIC for Safety | Applications |

|----------------------------------|----------------------------------|--------------|

|                                  |                                  |              |

|                                  | LIST OF TABLES                   |              |

| Table 1 Output Canacitor Selecti | on                               | 37           |

# **Absolute Maximum Ratings**

| V <sub>SUP</sub> , EN to GND | 0.3V to +40V                    | LX3 to PGND3 (Note 1)                            | 0.3V to OUT3 + 0.3V   |

|------------------------------|---------------------------------|--------------------------------------------------|-----------------------|

| BST to LX1                   |                                 | LX4 to PGND4 (Note 1)                            | 0.3V to PV4 + 0.3V    |

| PV2, PV4 to PGND             | 0.3V to +6V                     | GND to PGND                                      | 0.3V to +0.3V         |

| BIAS, BIASP to GND           | 0.3V to +6V                     | Output Short-Circuit Duration                    | Continuous            |

| IN5, IN6 to GND              | 0.3V to BIAS + 0.3V             | Continuous Power Dissipation (T <sub>A</sub> = + | -70°C)                |

| MD1, MD2 to GND              | 0.3V to +40V                    | 28-TQFN-EP (Single-Layer Boar                    | rd) (derate 65mW/°C > |

| SCL, SDA, SYNC, RESET to GND | 0.3V to +6V                     | 70°C)                                            | 1702.1mW              |

| OUT1 to GND                  | 0.3V to BIAS+0.3V               | 28-TQFN-EP (Multilayer Board)                    | (derate 34.5mW/°C >   |

| OUT2 to GND                  | 0.3V to PV2 + 0.3V              | 70°C.)                                           | 2758mW                |

| OUT4 to GND                  | 0.3V to PV4 + 0.3V              | Operating Temperature Range                      | 40°C to 125°C         |

| OUT3 to GND                  | 0.3V to +6V                     | Junction Temperature                             | +150°C                |

| LX1 to PGND1 (Note 1)        | 0.3V to V <sub>SUP</sub> + 0.3V | Storage Temperature Range                        | 65°C to +150°C        |

| LX2 to PGND2 (Note 1)        | 0.3V to PV2 + 0.3V              | Lead Temperature Range                           | +300°C                |

Note 1: Self-protected against transient voltages exceeding these limits for ≤ 50ns under normal operation and loads up to the maximum rated output current.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Package Information**

#### 28-QFN-EP

| Package Code                           | T2855Y+12C       |

|----------------------------------------|------------------|

| Outline Number                         | <u>21-100297</u> |

| Land Pattern Number                    | 90-100102        |

| Thermal Resistance, Four-Layer Board:  |                  |

| Junction to Ambient (θ <sub>JA</sub> ) | 29°C/W           |

| Junction to Case (θ <sub>JC</sub> )    | 2°C/W            |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{SUP} = V_{EN} = 13.5V, V_{OUT1} = V_{PV2} = V_{PV4} = 3.3V, V_{BIAS} = 5.0V, T_A = T_J = -40^{\circ}C$  to +125°C unless otherwise noted, typical values are at  $T_A = 25^{\circ}C$  under normal conditions unless otherwise noted (Note 2).)

| PARAMETER            | SYMBOL                          | CONDITIONS                                   | MIN  | TYP  | MAX  | UNITS |

|----------------------|---------------------------------|----------------------------------------------|------|------|------|-------|

| O and Wallers Dance  |                                 | Fully operational, no BIAS switchover        | 3.5  |      | 36   | V     |

| Supply Voltage Range | V <sub>SUP</sub>                | < 1s                                         |      |      | 40   | ]     |

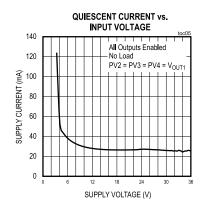

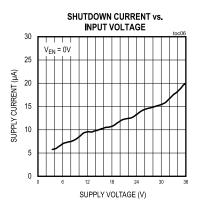

| Supply Current       | 1                               | EN = low                                     |      | 7    | 50   | μA    |

| Supply Current       | Supply Current I <sub>SUP</sub> | No load, EN = high, V <sub>OUT1</sub> = 3.3V |      | 24   |      | mA    |

| UVLO                 | UVLO <sub>R</sub>               | Rising                                       |      | 3.25 | 3.45 | V     |

| UVLO                 | UVLO <sub>F</sub>               | Falling                                      | 2.5  | 2.83 |      | V     |

| BIAS, BIASP Voltage  |                                 | No switchover, V <sub>SUP</sub> ≥ 5.5V       |      | 5    |      | V     |

| BIAS Current Limit   |                                 |                                              | 10   |      |      | mA    |

| OUT1 (HV BUCK)       |                                 |                                              |      |      |      |       |

| Voltage Accuracy     |                                 |                                              | -1.5 |      | 1.5  | %     |

| Line Regulation      |                                 | V <sub>SUP</sub> = 6V to 36V                 |      | 0.02 |      | %/V   |

$(V_{SUP} = V_{EN} = 13.5V, V_{OUT1} = V_{PV2} = V_{PV4} = 3.3V, V_{BIAS} = 5.0V, T_A = TJ = -40^{\circ}C \text{ to } +125^{\circ}C \text{ unless otherwise noted, typical values are at } T_A = 25^{\circ}C \text{ under normal conditions unless otherwise noted (Note 2).)}$

| PARAMETER                           | SYMBOL                                   | CONDITIONS                                                      | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------|------------------------------------------|-----------------------------------------------------------------|-------|------|-------|-------|

| DMOS High-Side On-<br>Resistance    |                                          | V <sub>BIAS</sub> = 5V, I <sub>LX1</sub> = 0.1A                 |       | 52   | 130   | mΩ    |

| DMOS Low-Side On-<br>Resistance     |                                          | V <sub>BIAS</sub> = 5V, I <sub>LX1</sub> = 0.1A                 |       | 47   | 110   | mΩ    |

| High-Side Current-Limit Threshold   |                                          |                                                                 | 3.5   | 4    | 4.5   | А     |

| Negative Current-Limit Threshold    |                                          |                                                                 |       | -1.6 |       | А     |

| Minimum On-Time                     |                                          |                                                                 |       | 65   | 80    | ns    |

| Max Duty Cycle                      |                                          |                                                                 | 98    | 99   |       | %     |

| Switching Phase                     |                                          |                                                                 |       | 0    |       | deg   |

| Soft-Start Time                     |                                          |                                                                 |       | 0.9  |       | ms    |

| OUT2/OUT4 (LV BUCK)                 |                                          |                                                                 |       |      |       |       |

| Supply Voltage Range                | V <sub>PV2</sub> , V <sub>PV4</sub>      |                                                                 | 3     |      | 5.5   | V     |

| Voltage Accuracy                    | V <sub>OUT2</sub> ,<br>V <sub>OUT4</sub> | $I_{LOAD}$ = 0A to $I_{MAX}$ , 3.0V $\leq V_{PV} \leq 5.5V$     | -1.5  |      | 1.5   | %     |

| HS pMOS On-<br>Resistance           |                                          | I <sub>LX</sub> _ = 0.2A                                        |       | 82   | 150   | mΩ    |

| LS nMOS On-<br>Resistance           |                                          | I <sub>LX</sub> _ = 0.2A                                        |       | 50   | 115   | mΩ    |

|                                     |                                          | Option 1 (1A)                                                   | 1.4   | 1.8  | 2.6   |       |

| HS Current-Limit<br>Threshold       |                                          | Option 2 (2A)                                                   | 2.8   | 3.5  | 4.9   | A     |

| THICSHOIL                           |                                          | Option 3 (3A)                                                   | 4.2   | 5.8  | 7.4   |       |

| LX2, LX4 Leakage<br>Current         |                                          | V <sub>PV</sub> = 5.5V, LX_ = PGND or PV, T <sub>A</sub> = 25°C |       | 1    |       | μА    |

| Negative Current-Limit<br>Threshold |                                          |                                                                 |       | -1   |       | А     |

| Minimum On Time                     |                                          |                                                                 |       | 48   | 76    | ns    |

| Maximum Duty Cycle                  |                                          |                                                                 |       |      | 100   | %     |

| LX2, LX4 Discharge<br>Resistance    |                                          | Output disabled                                                 |       | 47   | 100   | Ω     |

| Switching Phase                     |                                          |                                                                 |       | 180  |       | deg   |

| Soft-Start Time                     |                                          |                                                                 |       | 0.9  |       | ms    |

| OUT3 (BOOST)                        |                                          |                                                                 |       |      |       | '     |

| Voltage Accuracy                    | V <sub>OUT3</sub>                        | I <sub>LOAD</sub> = 0A to I <sub>MAX</sub>                      | 4.925 | 5    | 5.075 | V     |

| PMOS On-Resistance                  |                                          | I <sub>LX3</sub> = 0.19A                                        |       | 125  | 250   | mΩ    |

| NMOS On-Resistance                  |                                          | I <sub>LX3</sub> = 0.19A                                        |       | 65   | 130   | mΩ    |

| NMOS Current-Limit<br>Threshold     |                                          |                                                                 | 1.4   | 2.1  | 2.7   | А     |

| PMOS Negative Current<br>Limit      |                                          |                                                                 |       | -500 |       | mA    |

$(V_{SUP} = V_{EN} = 13.5V, V_{OUT1} = V_{PV2} = V_{PV4} = 3.3V, V_{BIAS} = 5.0V, T_A = TJ = -40^{\circ}C \text{ to } +125^{\circ}C \text{ unless otherwise noted, typical values are at } T_A = 25^{\circ}C \text{ under normal conditions unless otherwise noted (Note 2).)}$

| PARAMETER                             | SYMBOL            | CONDITIONS                                                              | MIN                        | TYP                        | MAX                        | UNITS |

|---------------------------------------|-------------------|-------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| LX3 Leakage Current                   |                   | OUT3 = 5.5 V, LX3 = PGND3 or OUT3,<br>T <sub>A</sub> = 25°C             |                            | 1                          |                            | μΑ    |

| Maximum Duty Cycle                    |                   |                                                                         |                            | 90                         |                            | %     |

| OUT3 Discharge<br>Resistance          |                   | OUT3 Disabled                                                           |                            | 340                        |                            | Ω     |

| Switching Phase                       |                   |                                                                         |                            | 30                         |                            | deg   |

| Soft-Start Time                       |                   |                                                                         |                            | 1                          |                            | ms    |

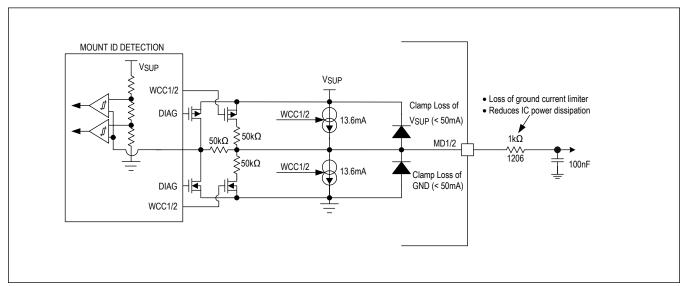

| MD1-2                                 |                   |                                                                         |                            |                            |                            |       |

| Supply Voltage Range                  |                   |                                                                         | 6                          |                            | 36                         | V     |

| High-Side Wetting<br>Current          |                   | MD_ short to ground                                                     | 10.2                       | 13.6                       | 17                         | mA    |

| Low-Side Wetting<br>Current           |                   | MD_ short to 13.5V                                                      | -10.2                      | -13.6                      | -17                        | mA    |

| Input Low Comparator<br>Threshold     |                   | 9V ≤ V <sub>SUP</sub> ≤ 16V                                             | V <sub>SUP</sub> x<br>0.35 | V <sub>SUP</sub> x<br>0.25 | V <sub>SUP</sub> x<br>0.15 | V     |

| Input High Comparator<br>Threshold    |                   | 9V ≤ V <sub>SUP</sub> ≤ 16V                                             | V <sub>SUP</sub> x<br>0.65 | V <sub>SUP</sub> x<br>0.75 | V <sub>SUP</sub> x<br>0.85 | V     |

| Pullup Resistor                       |                   |                                                                         | 25                         | 50                         | 75                         | kΩ    |

| Pulldown Resistor                     |                   |                                                                         | 25                         | 50                         | 75                         | kΩ    |

| Open Voltage                          |                   | Pin open, CONFIGM = 0x0F                                                | V <sub>SUP</sub> x<br>0.45 | V <sub>SUP</sub> x<br>0.50 | V <sub>SUP</sub> x<br>0.55 | V     |

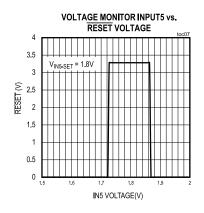

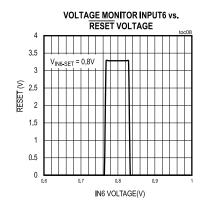

| ANALOG (IN5, IN6)                     |                   |                                                                         |                            |                            |                            |       |

| Input Current                         | I <sub>IN</sub> _ | V <sub>IN5</sub> /V <sub>IN6</sub> = 1.8V, Set point programmed to 1.8V |                            | 20                         |                            | μA    |

| V <sub>IN</sub> Programmable<br>Range |                   | 12.5 mV increments                                                      | 0.8                        |                            | 3.9875                     | V     |

| OV/UV Accuracy                        |                   | At OTP configured setpoint                                              | -1                         |                            | 1                          | . %   |

| OV/UV Accuracy                        |                   | Over full range when changing via I2C                                   | -1.5                       |                            | 1.5                        | 70    |

| OV Threshold                          |                   |                                                                         |                            | 104                        |                            | %     |

| UV Threshold                          |                   |                                                                         |                            | 96                         |                            | %     |

| Analog Delay Filter                   |                   | 10% below/above threshold                                               |                            | 2                          | 4                          | μs    |

| OSCILLATOR                            |                   |                                                                         |                            |                            |                            |       |

| Frequency                             | $f_{SW}$          | Internally Generated                                                    | 1.95                       | 2.1                        | 2.25                       | MHz   |

| Spread Spectrum                       |                   | CONFIG1.SSE = 1 (pseudo-random)                                         |                            | ±3                         |                            | %     |

| THERMAL OVERLOAD                      |                   |                                                                         |                            |                            |                            |       |

| Thermal Shutdown<br>Temperature       |                   | T <sub>J</sub> rising                                                   |                            | 175                        |                            | °C    |

| Hysteresis                            |                   |                                                                         |                            | 15                         |                            | °C    |

| RESET (OUT1-4)                        |                   |                                                                         |                            |                            |                            |       |

| OV Threshold                          |                   | Rising                                                                  | 103                        | 104                        | 105                        | %     |

| UV Threshold                          |                   | Falling                                                                 | 95                         | 96                         | 97                         | %     |

$(V_{SUP} = V_{EN} = 13.5V, V_{OUT1} = V_{PV2} = V_{PV4} = 3.3V, V_{BIAS} = 5.0V, T_A = TJ = -40^{\circ}C \text{ to } +125^{\circ}C \text{ unless otherwise noted, typical values are at } T_A = 25^{\circ}C \text{ under normal conditions unless otherwise noted (Note 2).)}$

| PARAMETER                                | SYMBOL              | CONDITIONS                | MIN | TYP  | MAX | UNITS |

|------------------------------------------|---------------------|---------------------------|-----|------|-----|-------|

|                                          |                     | HT[1:0] = 00              |     | 9.8  |     |       |

| Astiva Hald Daviad                       |                     | HT[1:0] = 01              |     | 19.5 |     | ]     |

| Active Hold Period                       | tH                  | HT[1:0] = 10              |     | 29.3 |     | ms    |

|                                          |                     | HT[1:0] = 11              |     | 39.0 |     | 1     |

| Delay Filter                             |                     | 10% below/above threshold |     | 2    | 4   | μs    |

| Output-High Leakage<br>Current           |                     | T <sub>A</sub> = 25°C     |     | 1    |     | μА    |

| Output Low Level                         |                     | Sinking -2mA              |     |      | 0.2 | V     |

| EN                                       |                     |                           | 1   |      |     | '     |

| Input High Level                         | V <sub>IH</sub>     |                           | 2.4 |      |     | V     |

| Input Low Level                          | V <sub>IL</sub>     |                           |     |      | 0.6 | V     |

| Pull-down                                |                     |                           |     | 1    |     | ΜΩ    |

| SYNC INPUT                               |                     | ·                         | 1   |      |     |       |

| Input High Level                         | V <sub>IH</sub>     |                           | 1.5 |      |     | V     |

| Input Low Level                          | V <sub>IL</sub>     |                           |     |      | 0.5 | V     |

| Input Hysteresis                         |                     |                           |     | 0.1  |     | V     |

| SYNC Input Pull-down                     |                     | EN high                   |     | 100  |     | kΩ    |

| SYNC Input Frequency<br>Range            |                     | 50% duty cycle            | 1.5 |      | 3   | MHz   |

| FPS                                      |                     |                           | -   |      |     |       |

| FPS Start Delay from SD1 Soft-Start Done | t <sub>FPSDLY</sub> |                           |     | 598  |     | μs    |

|                                          | t <sub>TS1</sub>    | TS = '00'                 |     | 2.4  |     |       |

| EDO T                                    | t <sub>TS2</sub>    | TS = '01'                 |     | 4.9  |     | 1     |

| FPS Timeslot                             | t <sub>TS3</sub>    | TS = '10'                 |     | 9.8  |     | ms    |

|                                          | t <sub>TS4</sub>    | TS = '11'                 |     | 19.5 |     | 1     |

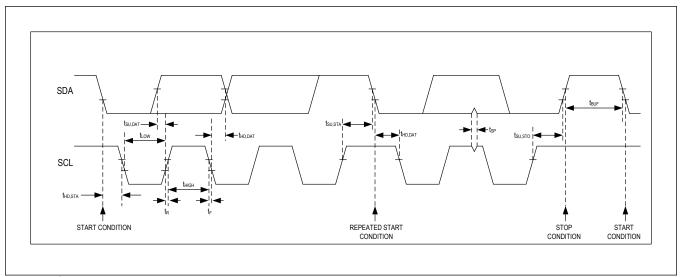

| I <sup>2</sup> C INTERFACE               |                     |                           |     |      |     | '     |

| Input High Voltage                       | V <sub>IH</sub>     |                           | 1.2 |      |     | V     |

| Input Low Voltage                        | V <sub>IL</sub>     |                           |     |      | 0.5 | V     |

| Output Low Voltage                       | V <sub>OL</sub>     | ISINK = 4mA               |     |      | 0.4 | V     |

| Clock Frequency                          | f <sub>SCL</sub>    |                           |     |      | 1.1 | MHz   |

| Setup Time (Repeated)<br>START           | t <sub>SU:STA</sub> |                           | 260 |      |     | ns    |

| Hold Time (Repeated)<br>START            | t <sub>HD:STA</sub> |                           | 260 |      |     | ns    |

| SCL Low Time                             | t <sub>LOW</sub>    |                           | 500 |      |     | ns    |

| SCL High Time                            | tHIGH               |                           | 260 |      |     | ns    |

| Data Setup Time                          | t <sub>SU:DAT</sub> |                           | 50  |      |     | ns    |

| Data Hold Time                           | t <sub>HD:DAT</sub> |                           | 0   |      |     | ns    |

$(V_{SUP} = V_{EN} = 13.5 \text{V}, V_{OUT1} = V_{PV2} = V_{PV4} = 3.3 \text{V}, V_{BIAS} = 5.0 \text{V}, T_A = TJ = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C} \text{ unless otherwise noted, typical values are at } T_A = 25 ^{\circ}\text{C} \text{ under normal conditions unless otherwise noted (Note 2).)}$

| PARAMETER                        | SYMBOL         | CONDITIONS                 | MIN | TYP | MAX | UNITS |

|----------------------------------|----------------|----------------------------|-----|-----|-----|-------|

| Setup Time for STOP<br>Condition | tsu:sto        |                            | 260 |     |     | ns    |

| Spike Suppression                |                |                            |     | 50  |     | ns    |

| Operating I/O Voltage<br>Range   |                |                            | 1.7 |     | 3.6 | V     |

|                                  |                | Fast Mode (Note 3)         |     |     | 220 |       |

| SCL/SDA Fall Time                | t <sub>f</sub> | Fast Mode Plus<br>(Note 3) |     |     | 120 | ns    |

Note 2: Limits are 100% tested at TA = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 3: Not production tested. Guaranteed by design.

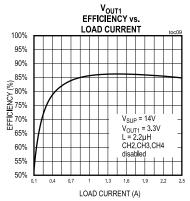

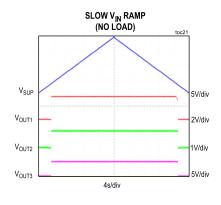

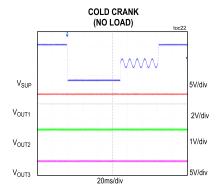

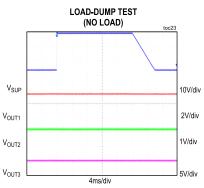

# **Typical Operating Characteristics**

$(V_{SUP} = EN = 13.5V. T_A = 25^{\circ}C, unless otherwise noted.)$

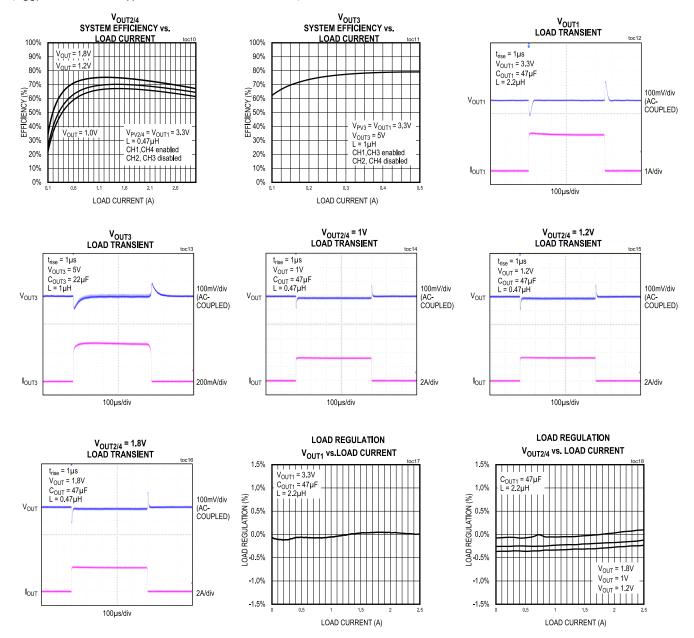

# **Typical Operating Characteristics (continued)**

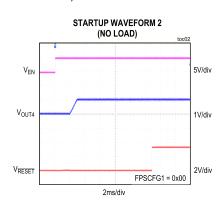

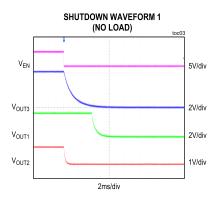

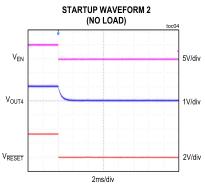

$(V_{SUP} = EN = 13.5V. T_A = 25^{\circ}C, unless otherwise noted.)$

# **Typical Operating Characteristics (continued)**

( $V_{SUP}$  = EN = 13.5V.  $T_A$  = 25°C, unless otherwise noted.)

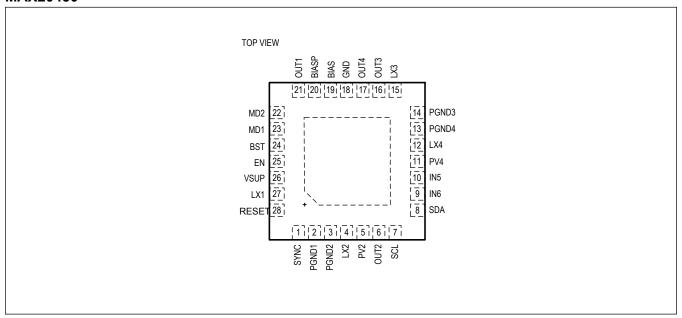

# **Pin Configuration**

## **MAX20430**

# **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                             |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SYNC  | SYNC Input. Connect SYNC to BIAS for a 2.1MHz switching frequency. Connect SYNC to an external clock if a different switching frequency is required. |

| 2   | PGND1 | Power Ground for OUT1. Connect all PGND pins together.                                                                                               |

| 3   | PGND2 | Power Ground for OUT2. Connect all PGND pins together.                                                                                               |

| 4   | LX2   | Inductor Connection for Channel 2. Connect LX2 to the switched side of the inductor.                                                                 |

| 5   | PV2   | OUT2 Power Supply Input. This must be connected to OUT1 and bypassed with a 4.7µF ceramic capacitor.                                                 |

| 6   | OUT2  | OUT2 Voltage Sense Input                                                                                                                             |

| 7   | SCL   | I <sup>2</sup> C Clock Input                                                                                                                         |

| 8   | SDA   | I <sup>2</sup> C Data I/O                                                                                                                            |

| 9   | IN6   | Voltage Monitor Input 6. Connect an external supply that is to be monitored to this input. The OV6/UV6 violation can be mapped to the RESET pin.     |

| 10  | IN5   | Voltage Monitor Input 5. Connect an external supply that is to be monitored to this input. The OV5/UV5 violation can be mapped to the RESET pin.     |

| 11  | PV4   | OUT4 Power Supply Input. This must be connected to OUT1 and bypassed with a 4.7µF ceramic capacitor.                                                 |

| 12  | LX4   | Inductor Connection for Channel 4. Connect LX4 to the switched side of the inductor.                                                                 |

| 13  | PGND4 | Power Ground for OUT4. Connect all PGND pins together.                                                                                               |

| 14  | PGND3 | Power Ground for OUT3. Connect all PGND pins together.                                                                                               |

| 15  | LX3   | Inductor Connection for Channel 3. Connect LX3 to the switched side of the inductor.                                                                 |

| 16  | OUT3  | OUT3 Voltage Output                                                                                                                                  |

| 17  | OUT4  | OUT4 Voltage-Sense Input                                                                                                                             |

# **Pin Description (continued)**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                  |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | GND              | Ground                                                                                                                                                                                                                                                    |

| 19  | BIAS             | High-Voltage LDO Output, Regulates at 5V. Connect a minimum of 2.2µF (after deration) ceramic capacitor from BIAS to GND.                                                                                                                                 |

| 20  | BIASP            | Noisy High-Voltage LDO Output, Regulates at 5V. Connect a 2.2µF ceramic capacitor from BIASP to GND. After boost converter finishes soft-start, this pin connects to OUT3.                                                                                |

| 21  | OUT1             | OUT1 Voltage Sense Input                                                                                                                                                                                                                                  |

| 22  | MD2              | Mount ID Input 2                                                                                                                                                                                                                                          |

| 23  | MD1              | Mount ID Input 1                                                                                                                                                                                                                                          |

| 24  | BST              | Bootstrap Capacitor Connection. Connect a 0.1µF ceramic capacitor from BST to LX1.                                                                                                                                                                        |

| 25  | EN               | Active-High Enable Input. Drive EN HIGH for normal operation. The IC will power sequence all outputs as factory programmed.                                                                                                                               |

| 26  | V <sub>SUP</sub> | IC Supply Input. Connect a 4.7μF or larger ceramic capacitor from V <sub>SUP</sub> to PGND1.                                                                                                                                                              |

| 27  | LX1              | Inductor Connection for Channel 1. Connect LX1 to the switched side of the inductor.                                                                                                                                                                      |

| 28  | RESET            | Open-Drain Reset Output. This output remains low for the programmed hold time after all mapped outputs have reached their regulation level (see the Electrical Characteristics table). To obtain a logic signal, pull up RESET with an external resistor. |

|     | EP               | Connect the exposed pad to the ground plane. This is the main path for thermal transfer.                                                                                                                                                                  |

# **Functional Diagrams**

# **Functional Diagram 1**

## **Detailed Description**

The MAX20430 is a high-efficiency, four-output DC-DC converter and a windowed watchdog. OUT1 is a synchronous step-down converter that converts vehicle battery voltage to 3.3V at up to 2.5A. OUT3 boosts OUT1 to 5V at up to 500mA, while OUT2 and OUT4 low-voltage synchronous step-down converters operate from OUT1 and provide a 0.8V to 3.9875V output voltage range at up to 3A.

The programmable spread-spectrum frequency modulation minimizes radiated electromagnetic emissions. Integrated low R<sub>DSON</sub> switches improve efficiency at heavy loads and make the layout much simpler with respect to discrete solutions.

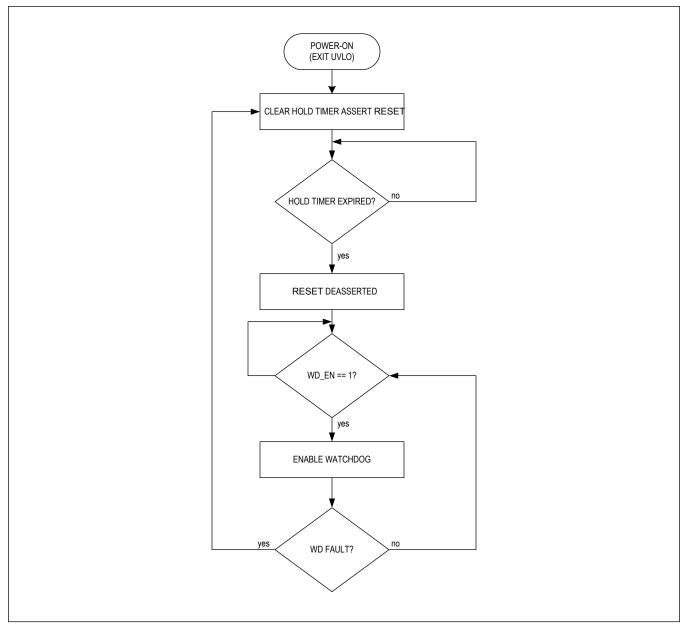

#### Challenge/Response Watchdog and Reset Control

The challenge/response watchdog uses a linear feedback shift register (LFSR) to calculate the response to the current key. The MCU can read the current key at any time from the WDKEY register. The response must be written after  $t_{WD1}$  time expires and before  $t_{WD2}$  time expires. The timing of the open and close windows is programmable through the  $t_{WD1}$  time valid watchdog refresh will terminate the open window and initialize the closed window.

Any assertion of  $\overline{\text{RESET}}$  restarts the watchdog. Upon exiting the reset condition (when  $\overline{\text{RESET}}$  de-asserts after the expiration of the hold timer), the update window is immediately opened and extended to allow the MCU time to boot before being required to update the watchdog. If the device is configured as a standard windowed watchdog (WDCDIV.SWW = 1) then writing any value to the WDKEY will result in a valid watchdog refresh signal, and the value written will be ignored.

There are three types of watchdog violations: WD\_LFSR, WD\_EXP, and WD\_UV. If configured as a challenge/response watchdog, writing the incorrect response to the WDKEY register will result in the written value being ignored and an LFSR violation. Writing the correct response in challenge/response mode during an open window will result in a refresh and the WDKEY register being updated. Writing the correct response in challenge/response mode during a closed window will result in the write being ignored and a UV violation. Not refreshing the watchdog during the open window will result in an EXP violation.

If a watchdog violation is detected, the watchdog will assert  $\overline{\mathsf{RESET}}$ , and re-start upon exiting the reset condition. The internal violation counter is reset only during power-on.

The watchdog is enabled when WD\_EN bit is 1 and the RESET pin is de-asserted. The WD\_LOCK bit must be set to 0 to configure or disable the watchdog to prevent unintended re-configuring of the watchdog.

When the watchdog is configured as a simple windowed watchdog, it can be refreshed by writing any value to the WDKEY register, though the written value will be ignored.

Figure 1. Watchdog Control

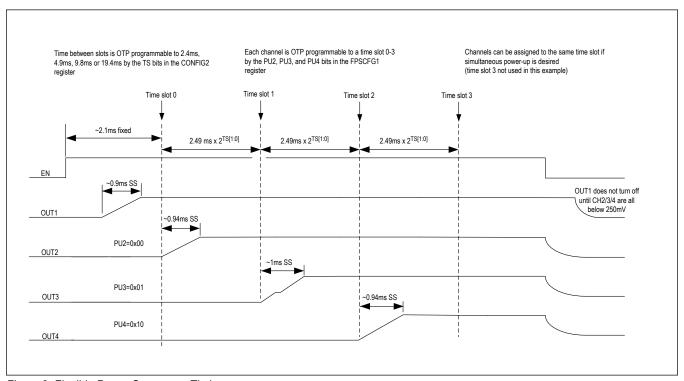

## Flexible Power Sequencer (FPS)

When EN goes high, the device is powered on and the OUT1 channel is enabled. Once the OUT1 channel has reached a nominal voltage, the flexible power sequencer (FPS) power-up sequence begins. The time between power-up time slots is factory-selectable between values of 2.5ms (typ), 4.9ms (typ), 9.8ms (typ), and 19.5ms (typ). When the EN pin goes low, the device turns off.

A POR\_RST event can re-initialize the FPS to the programmed time slots set in the PUx[1:0] registers. For this operation, the RSTMAP[6:1] bits must be cleared.

## Flexible Power Sequencer Timing

Figure 2. Flexible Power Sequencer Timing

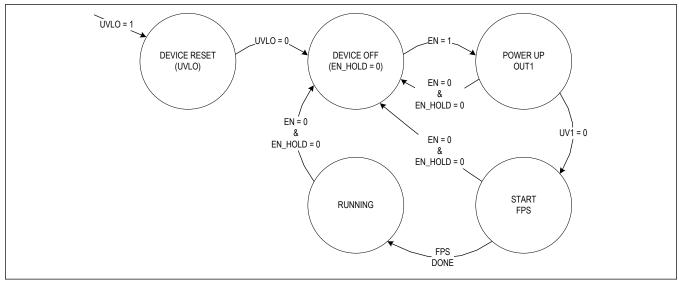

## **RESET** Output

The device features an open-drain reset output that asserts low when the corresponding mapped output voltages are outside the UV/OV window, UVLO is asserted, or a watchdog violation occurs. RESET remains asserted for a fixed hold-timeout period after the mapped inputs rise to the regulated voltage. The fixed hold-timeout period is selectable with the HT[1:0] register bits as 9.8ms (typ), 19.5ms(typ), 29.3ms(typ), or 39ms(typ). To obtain a logic signal, place a pullup resistor between the RESET pin and the system I/O voltage. The source mapping to this pin is fully programmable.

#### **Enable Input Pin (EN)**

The EN pin is an active-high enable input. When the EN pin goes high, the four DC-DC converters power up in the programmed order. OUT1 must power up first since all other DC-DC converters are cascaded from OUT1. If the EN pin is brought low before the device has finished initializing, the device will stay on for up to 1ms (typ) while a shutdown is executed. The device can be kept enabled by setting the EN\_HOLD bit to 1 in the CONFIG1 register. See Figure 3; EN HOLD is cleared to 0 when the RESET pin is asserted to prevent the power supply from getting stuck on.

Figure 3. Power-On Control State Diagram

# Mount ID Input Pins (MD1, MD2)

The MD1 and MD2 inputs are used to identify the location of the module using the connector keying method. The MAX20430 provides a wetting current of 10mA (min). The pins handle loss of ground, which is indicated by -16V(min) on the connector pin.

The procedure for reading the state and setting the wetting current of the MD1 and MD2 pins is as follows:

- 1. After power-up, set CONFIGM to 0x0F, which will enable an internal resistor-divider on MD1/MD2 pins.

- 2. Read register STATM to determine the state.

- 3. Set the wetting current according to the state of each input, and disable the internal resistor-divider. For example, if MD1 is connected to ground, then enable the high-side wetting current.

To verify that the MD1 and MD2 input is functional, complete diagnostics as follows:

- Set CONFIGM to 0x0F, which will enable an internal resistor-divider on the MD1/MD2 pins. If the MD1/MD2 pins are

open circuit, the internal resistor-divider will hold the MD1/MD2 pins at mid-rail,(50% x V<sub>SUP</sub>). Then read register

STATM to verify that both MD1/MD2 pins are either high or low, and not mid-rail. A mid-rail MD1/MD2 pin indicates

an open-circuit fault.

- 2. Set CONFIGM to 0x1F. Read the STATM register to verify that the MD2 comparator reports high and the MD1 comparator reports low.

- 3. Set CONFIGM to 0x2F. Read the STATM register to verify that the MD2 comparator reports low and the MD1 comparator reports high.

- 4. Set CONFIGM to 0x00 to disable the internal resistor-divider and complete the diagnostics.

#### **Mount ID Diagram**

Figure 4. Mount ID Detection (One Channel Shown)

#### **OFF Comparators**

The MAX20430 includes an OFF comparator for each output voltage. The comparators assert if the output voltage drops below 0.25V (typ), and are tested for proper operation at power-on. If one of the comparators fails the BIST test, the INTERR bit is set and the comparator state can be read from the status register. The OFF comparators ensure that all outputs assigned to an FPS are discharged before the FPS power-up sequence is initiated.

#### **OV Shutdown Comparators**

The MAX20430 includes OV shutdown comparators for each output voltage. If one of the comparators is asserted, then the MAX20430 will turn off all outputs and trigger a UVLO event, reloading OTP and re-running BIST on the comparators. Once power is re-applied, the device powers up normally. If an output is overloaded and the overload is released, it is possible for the output to overshoot and trigger the OV shutdown. OV shutdown comparators are gated with the CONFIGE register, and have no effect on a disabled channel.

#### **UV/OV** Comparators

The MAX20430 includes a UV and OV comparator for each output voltage and the voltage on IN5/6. The comparators are tested for proper operation at power-on. If one of the comparators fails the BIST test, the INTERR bit is set in the STATD register. The comparators have a built-in programmable filter time that is controlled by CONFIG2.DF[3:0], which prevents small transients exceeding the UV or OV comparator from triggering a RESET event. This programmable digital filter allows an application-specific setting of filter time up to 28.6µs.

OV and UV comparators are not gated by the CONFIGE register and always report the status of the channel.

#### **Internal Oscillator**

The device has a spread-spectrum oscillator that varies the internal operating frequency up by  $\pm 3\%$  relative to the internally generated operating frequency of 2.1MHz (typ). The spread frequency generated is psuedorandom with a repeat rate well below the audio band (< 20Hz). Spread spectrum is enabled when CONFIG1.SSE is set to 1.

#### **Overtemperature Protection**

Thermal overload protection limits the total power dissipation in the MAX20430. When the junction temperature exceeds

175°C, the device will immediately turn off all output channels and reset the FPS. Once the junction temperature cools by 15°C, the FPS will re-enable and start up according to the programmed sequence.

## I<sup>2</sup>C Interface

The MAX20430 features an  $I^2$ C, 2-wire serial interface consisting of a serial-data line (SDA) and a serial-clock line (SCL). SDA and SCL facilitate communication between the MAX20430 and the master at clock rates up to 1MHz. The master, typically a microcontroller, generates SCL and initiates data transfer on the bus. Figure 5 shows the 2-wire interface timing diagram.

A master device communicates to the MAX20430 by transmitting the proper address followed by the data word. Each transmit sequence is framed by a START (S) or REPEATED START (Sr) condition and a STOP (P) condition. Each word transmitted over the bus is 8 bits long and is always followed by an acknowledge clock pulse.

The MAX20430 SDA line operates as both an input and an open-drain output. The pullup resistor value on the SDA bus should be large enough to keep the open-drain pulldown current less than 4mA (max) to guarantee the MAX20430 can pull SDA below 0.4V. The MAX20430 SCL line operates as an input only. The SCL and SDA inputs suppress noise spikes to assure proper device operation, even on a noisy bus.

#### **Timing Diagram**

Figure 5. I<sup>2</sup>C Timing Diagram

## **Bit Transfer**

One data bit is transferred during each SCL cycle. The data on SDA must remain stable during the high period of the SCL pulse. Changes in SDA while SCL is high are control signals (see the START and STOP Conditions section). SDA and SCL idle high when the I<sup>2</sup>C bus is not busy.

#### **STOP and START Conditions**

A master device initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 6). A START (S) condition from the master signals the beginning of a transmission to the MAX20430. The master terminates transmission and frees the bus by issuing a STOP (P) condition. The bus remains active if a REPEATED START (Sr) condition is generated instead of a STOP condition.

# SDA ST P SDA SCL thd;STA thd;STA

## START, STOP, and REPEATED START Conditions

Figure 6. START, STOP, and REPEATED START Conditions

#### **Early STOP Condition**

The MAX20430 recognizes a STOP condition at any point during data transmission unless the STOP condition occurs in the same high pulse as a START condition.

#### **Clock Stretching**

In general, the clock signal generation for the I<sup>2</sup>C bus is the responsibility of the master device. The I<sup>2</sup>C specification allows slow slave devices to alter the clock signal by holding down the clock line, a process typically called clock stretching. The MAX20430 does not use any form of clock stretching to hold down the clock line.

#### I<sup>2</sup>C General Call Address

The MAX20430 does not implement the  $I^2C$  specification's general call address. If the MAX20430 detects the general call address (0b0000\_0000) it will not issue an acknowledge.

#### Packet Error Checking (PEC)

In order to increase fault coverage on the  $I^2C$  interface, an optional packet error checking (PEC) byte is supported. This follows the SMBus implementation, which has a CRC-8 polynomial of  $x^8 + x^2 + x + 1$ . The PEC calculation does not include ACK, NACK, START, STOP, nor Repeated START bits. This means that the PEC is computed over the entire message from the first START condition. Only 1 byte can be written per  $I^2C$  packet. Any data after the PEC byte will not be written.

If PEC is enabled (PECE = 1), the device will NACK an incorrect PEC byte and the written register data will be ignored.

#### **Slave Address**

The address is defined as the seven most significant bits (MSbs) followed by the R/W bit. Set the R/W bit to 1 to configure the device to read mode. Set the R/W bit to 0 to configure the device to write mode. The address is the first byte of information sent to the device after the START condition. The slave address is factory preset (see Ordering Information for the 7-bit address for each version). The factory-programmable I<sup>2</sup>C addresses are 0x38 through 0x3B.

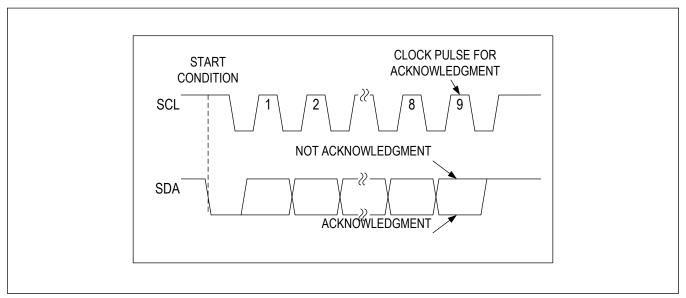

#### Acknowledge

The acknowledge bit (ACK) is a clocked ninth bit that the device uses to handshake receipt of each data byte <u>Figure 7</u>. The device pulls down SDA during the master-generated ninth clock pulse. The SDA line must remain stable and

low during the high period of the acknowledge clock pulse. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master can reattempt communication.

If packet error checking (PEC) is enabled (PECE = 1), the device will NACK an incorrect PEC byte and the written register data will be ignored.

#### **Acknowledge Condition**

Figure 7. Acknowledge Condition

#### **Write Data Format**

A write to the device includes transmission of the following:

- START condition

- Slave address with the write bit set to 0

- 1 byte of data to register address

- 1 byte of data to the command register

- STOP condition

Figure 8 illustrates the proper format for one frame.

#### **Read Data Format**

A read from the device includes the following:

- Transmission of a START condition

- Slave address with the write bit set to 0

- 1 byte of data to register address

- Restart condition

- Slave address with read bit set to 1

- 1 byte of data to the command register

- STOP condition

Figure 8 illustrates the proper format for one frame.

# Data Format of I<sup>2</sup>C Interface

| S         | Slave Address                     | 0 | Α | Register Address                  | Α |          | Data             | Α | Р |                      |          |   |     |     |

|-----------|-----------------------------------|---|---|-----------------------------------|---|----------|------------------|---|---|----------------------|----------|---|-----|-----|

| Write     | Sequenital Bytes                  | • |   |                                   |   |          |                  |   |   |                      |          |   |     |     |

| S         | Slave Address                     | 0 | Α | Register Address                  | А |          | Data             | А |   | Data Byte N          | А        | Р |     |     |

| Write     | Byte (PEC Enabled)                | • |   |                                   |   |          |                  |   |   |                      |          |   | •   |     |

| S         | Slave Address                     | 0 | Α | Register Address                  | А |          | Data 1           | А |   | PEC A P              |          |   |     |     |

|           |                                   |   |   |                                   |   |          |                  |   |   |                      | _        |   |     |     |

| Read      | Byte                              |   |   |                                   |   |          |                  |   |   |                      |          |   |     |     |

| Read      | Byte Slave Address                | 0 | А | Register Address                  | А | Sr       | Slave<br>Address | 1 | А | Data Byte            | N<br>A P |   |     |     |

| S         |                                   |   | А | Register Address                  | А | Sr       |                  | 1 | А | Data Byte            | N P      |   |     |     |

| S         | Slave Address                     |   | A | Register Address Register Address | A | Sr<br>Sr |                  | 1 |   | Data Byte  Data Byte | N P      |   | PEC | N P |

| S<br>Read | Slave Address  Byte (PEC Enabled) |   |   | <u> </u>                          |   |          | Address          |   |   | ,                    | A   「    |   | PEC |     |

Figure 8. Data Format of I<sup>2</sup>C Interface

# **Register Map**

# **USER**

| ADDRESS  | NAME               | MSB |            |                 |                 |             |             |            | LSB         |

|----------|--------------------|-----|------------|-----------------|-----------------|-------------|-------------|------------|-------------|

| USER_CME | S                  |     |            | 1               |                 |             |             | 1          |             |

| 0x00     | CID[7:0]           | R[′ | 1:0]       |                 |                 | ID[         | 5:0]        |            |             |

| 0x01     | CONFIG1[7:0]       | _   | _          | _               | - EN_HOL SSE PR |             |             |            | PECE        |

| 0x02     | CONFIG2[7:0]       | HT[ | [1:0]      | TS[1:0] DF[3:0] |                 |             |             |            |             |

| 0x03     | CONFIGE[7:0]       | _   | _          | -               | _               |             | EN[4:2]     |            | _           |

| 0x04     | CONFIGM[7:0]       | _   | _          | DIAC            | S[1:0]          | WCC         | 2[1:0]      | WCC        | 1[1:0]      |

| 0x05     | FPSCFG1[7:0]       | PU4 | [1:0]      | PU3             | [1:0]           | PU2         | [1:0]       | -          | _           |

| 0x06     | PORRST[7:0]        | _   | _          | _               | _               | _           | _           | _          | POR_RS<br>T |

| 0x07     | PINMAP1[7:0]       | _   | _          |                 |                 | RSTM        | AP[6:1]     |            |             |

| 80x0     | STATUV[7:0]        | _   | _          |                 |                 | UV[         | 6:1]        |            |             |

| 0x09     | <u>STATOV[7:0]</u> | _   | _          |                 |                 | OV          | [6:1]       |            |             |

| 0x0A     | STATOFF[7:0]       | _   | _          |                 |                 | OFF         | [6:1]       |            |             |

| 0x0B     | <u>STATD[7:0]</u>  | _   | _          | -               | RSTERR          | POR         | _           | THSD       | INTERR      |

| 0x0C     | <u>STATM[7:0]</u>  | _   | _          | _               | _               | MD2H        | MD2L        | MD1H       | MD1L        |

| 0x0D     | STATWD[7:0]        | _   | _          | _               | RESETB<br>_STAT | WD_OP<br>EN | WD_LFS<br>R | WD_UV      | WD_EX<br>P  |

| 0x0E     | <u>VOUT2[7:0]</u>  |     |            |                 | OUT             | 2[7:0]      |             |            |             |

| 0x0F     | <u>VOUT4[7:0]</u>  |     |            |                 | OUT             | 4[7:0]      |             |            |             |

| 0x10     | <u>VIN5[7:0]</u>   |     |            |                 | IN5             | [7:0]       |             |            |             |

| 0x11     | <u>VIN6[7:0]</u>   |     |            |                 | IN6             | [7:0]       |             |            |             |

| 0x12     | WDCDIV[7:0]        | _   | WD_SW<br>W |                 |                 | WD_D        | IV[5:0]     |            |             |

| 0x13     | WDCFG1[7:0]        |     | WD_O       | PN[3:0]         |                 |             | WD_C        | LO[3:0]    |             |

| 0x14     | WDCFG2[7:0]        | -   | _          | -               | _               | WD_EN       | V           | VD_1UD[2:0 | )]          |

| 0x15     | WDKEY[7:0]         |     |            |                 | WD_K            | EY[7:0]     |             |            |             |

| 0x16     | WDPROT[7:0]        | _   | _          | _               | _               | _           | _           | -          | WD_PR<br>OT |

# **Register Details**

# CID (0x0)

| BIT            | 7    | 6      | 5                | 4       | 3 | 2 | 1 | 0 |  |  |  |

|----------------|------|--------|------------------|---------|---|---|---|---|--|--|--|

| Field          | R[1  | 1:0]   |                  | ID[5:0] |   |   |   |   |  |  |  |

| Reset          | 0b   | 000    |                  |         |   |   |   |   |  |  |  |

| Access<br>Type | Read | l Only | Write, Read, Ext |         |   |   |   |   |  |  |  |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                                                                         | DECODE                                                                                   |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| R        | 7:6  | Silicon Revision Information                                                                                                                                                                                        | 00 = Pass 1 Silicon<br>01 = Pass 2 Silicon<br>10 = Pass 3 Silicon<br>11 = Pass 4 Silicon |

| ID       | 5:0  | Chip Configuration Identification. This is a unique number identifying the factory configuration of the device. This helps identify/verify the configuration without having to look at all configuration registers. | See ordering information.                                                                |

# CONFIG1 (0x1)

Configuration Register 1 (Read/Write)

| 5              | ` |   | _ |   |                     | _           | 4                   | •           |

|----------------|---|---|---|---|---------------------|-------------|---------------------|-------------|

| BIT            | 7 | 6 | 5 | 4 | 3                   | 2           | 1                   | U           |

| Field          | _ | _ | _ | _ | EN_HOLD             | SSE         | PROT                | PECE        |

| Reset          | _ | _ | _ | _ | OTP                 | OTP         | OTP                 | OTP         |

| Access<br>Type | _ | _ | _ | _ | Write,<br>Read, Ext | Write, Read | Write,<br>Read, Ext | Write, Read |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                        | DECODE                                                                           |  |  |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|

| EN_HOLD  | 3    | Enable Hold. Overrides the EN pin to keep the device enabled. This bit is cleared when RESETB is asserted.                                                         | 0 = EN pin controls power down<br>1 = Device enabled. Ignores EN pin state       |  |  |

| SSE      | 2    | Spread Spectrum Enable.                                                                                                                                            | 0 = Disabled<br>1 = Enabled                                                      |  |  |

| PROT     | 1    | Lock Protection. If this bit is set to 1 by factory default, then it can't be cleared. If 0 by default, then this bit can be changed through the I <sup>2</sup> C. | 0 = All registers can be written. 1 = Writes are ignored to protected registers. |  |  |

| PECE     | 0    | Packet Error Checking Enable. Set this bit to a 1 to enable PEC or 0 to disable PEC.                                                                               | 0 = Disabled.<br>1 = Enabled.                                                    |  |  |

# CONFIG2 (0x2)

Configuration Register 2 (Read/Write, Protected: writeable when LOCK = 0)

| BIT            | 7      | 6     | 5               | 4    | 3           | 2 | 1 | 0 |

|----------------|--------|-------|-----------------|------|-------------|---|---|---|

| Field          | НТ[    | [1:0] | TS[1:0] DF[3:0] |      |             |   |   |   |

| Reset          | 0      | TP    | 0               | TP   | OTP         |   |   |   |

| Access<br>Type | Write, | Read  | Write,          | Read | Write, Read |   |   |   |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                | DECODE                                                |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| нт       | 7:6  | RESET Hold Time Selection. This is the amount of time that the RESET pin is active (low) after the event that caused the RESET pin to activate is removed. | 00 = 9.8ms<br>01 = 19.5ms<br>10 = 29.3ms<br>11 = 39ms |

| TS       | 5:4  | Time Slot Time. These bits define the time between timeslots.                                                                                              | 00 = 2.4ms<br>01 = 4.9ms<br>10 = 9.8ms<br>11 = 19.5ms |

| DF       | 3:0  | OV/UV Digital Filter. Adds additional filtering to all OV/UV comparators.                                                                                  | Added Filter Time = DF[3:0] x 1.9µs (±1µs nom)        |

# **CONFIGE (0x3)**

Channel Enable Configuration Register (Read/Write, Protected: writeable when LOCK = 0)

| BIT            | 7 | 6 | 5 | 4 | 3 | 2           | 1 | 0 |  |

|----------------|---|---|---|---|---|-------------|---|---|--|

| Field          | _ | _ | _ | _ |   | _           |   |   |  |

| Reset          | - | - | - | - |   | OTP         |   |   |  |

| Access<br>Type | _ | _ | _ | _ |   | Write, Read |   |   |  |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                        | DECODE                                    |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| EN       | 3:1  | Main Output Enable for OUT2(EN2),<br>OUT3(EN3), and OUT4(EN4).<br>When an output is enabled, the FPS will<br>control when the output is on or off. | 0 = Output Disabled<br>1 = Output Enabled |

# CONFIGM (0x4)

Mount ID Configuration Register (Read/Write)

| BIT            | 7 | 6 | 5         | 4                       | 3         | 2           | 1         | 0      |      |

|----------------|---|---|-----------|-------------------------|-----------|-------------|-----------|--------|------|

| Field          | - | - | DIAG[1:0] |                         | WCC2[1:0] |             | WCC1[1:0] |        |      |

| Reset          | _ | _ | 0         | TP                      | OTP       |             | OTP       |        |      |

| Access<br>Type | _ | _ | Write,    | Write, Read Write, Read |           | Write, Read |           | Write, | Read |

| BITFIELD | BITS | DESCRIPTION                                                                                                                   | DECODE                                                                                                                                                                                                                                                                   |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIAG     | 5:4  | Mount ID Diagnostics. After setting the diagnostic mode, read the STATM register to check the comparator state.               | 00 = Normal mode 01 = Short MD1 comparator inputs to ground and MD2 comparator inputs to V <sub>SUP</sub> 10 = Short MD1 comparator inputs to V <sub>SUP</sub> and MD2 comparator inputs to GND 11 = Reserved                                                            |

| WCC2     | 3:2  | Mount ID 2 Control. Sets the mode of the MD2 pin. The STATM should be read when WC2 is set to 11 to ensure a correct reading. | 00 = Wetting current and resistor divider disabled<br>01 = Low-side wetting current enabled and resistor<br>divider disabled<br>10 = High-side wetting current enabled and resistor<br>divider disabled<br>11 = Resistor-divider enabled and wetting current<br>disabled |

| WCC1     | 1:0  | Mount ID 1 Control. Sets the mode of the MD1 pin. The STATM should be read when WC1 is set to 11 to ensure a correct reading. | 00 = Wetting current and resistor divider disabled 01 = Low-side wetting current enabled and resistor divider disabled 10 = High-side wetting current enabled and resistor divider disabled 11 = Resistor-divider enabled and wetting current disabled                   |

## FPSCFG1 (0x5)

Flexible Power Sequencer Configuration Register 1 (Read/Write, Protected: writeable when LOCK = 0)

| I TEXIDIE I OWE | Sequencer v | Sorniguration | ation register i (read/write, i fotected, writeable when LOCK = 0) |      |          |      |   |   |

|-----------------|-------------|---------------|--------------------------------------------------------------------|------|----------|------|---|---|

| BIT             | 7           | 6             | 5                                                                  | 4    | 3        | 2    | 1 | 0 |

| Field           | PU4         | [1:0]         | PU3[1:0]                                                           |      | PU2[1:0] |      | _ | _ |

| Reset           | 0           | TP            | OTP                                                                |      | OTP      |      | _ | _ |

| Access<br>Type  | Write,      | Read          | Write,                                                             | Read | Write,   | Read | _ | _ |

| BITFIELD | BITS | DESCRIPTION                                                           | DECODE                                                           |

|----------|------|-----------------------------------------------------------------------|------------------------------------------------------------------|

| PU4      | 7:6  | OUT4 Power-Up Time Slot. OUT4 powers up in time slot set by PU4[1:0]. | $t_{PU4} = PU4[1:0] \times 2.44 \times (2^{TS[1:0]}) \text{ ms}$ |

| PU3      | 5:4  | OUT3 Power-Up Time Slot. OUT3 powers up in time slot set by PU3[1:0]. | $t_{PU3} = PU3[1:0] \times 2.44 \times (2^{TS[1:0]}) \text{ ms}$ |

| PU2      | 3:2  | OUT2 Power-Up Time Slot. OUT2 powers up in time slot set by PU2[1:0]. | $t_{PU2}$ = PU2[1:0] x 2.44 x (2 <sup>TS[1:0]</sup> ) ms         |

## PORRST (0x6)

Power On Reset Emulation Register (Read/Write, Protected: writeable when LOCK = 0)

|                |   | ( |   |   |   | , |   |                     |

|----------------|---|---|---|---|---|---|---|---------------------|

| BIT            | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0                   |

| Field          | _ | _ | _ | _ | _ | _ | _ | POR_RST             |

| Reset          | _ | _ | - | - | - | - | _ | 0x0                 |

| Access<br>Type | _ | _ | _ | _ | _ | _ | _ | Write,<br>Read, Ext |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                      | DECODE                                       |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| POR_RST  | 0    | The POR_RST bit emulates a power-on-reset condition, re-initlaizing the FPS sequence and watchdog while retaining programmed register values and performing comparator BIST.  OTP CRC calculation is not performed when executing this command.  This bit is self-clearing, and cannot be written when LOCK = 1. | 0 = No Effect<br>1 = Initialze POR Emulation |

## **PINMAP1 (0x7)**

RESETB Pin Mapping Register (Read/Write, Protected; writeable when LOCK = 0)

|                |   | ` <b>.</b> | inte, i rotested. Witedahe Wiel 250K 0) |     |        |      |   |   |  |

|----------------|---|------------|-----------------------------------------|-----|--------|------|---|---|--|

| BIT            | 7 | 6          | 5                                       | 4   | 3      | 2    | 1 | 0 |  |

| Field          | - | -          | RSTMAP[6:1]                             |     |        |      |   |   |  |

| Reset          | _ | _          |                                         | OTP |        |      |   |   |  |

| Access<br>Type | - | _          |                                         |     | Write, | Read |   |   |  |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                                       | DECODE                                                                                       |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| RSTMAP   | 5:0  | RESETB Pin Mapping for OUT1(RSTMAP1), OUT2(RSTMAP2), OUT3(RSTMAP3), OUT4(RSTMAP4), IN5(RSTMAP5), and IN6 (RSTMAP6).  Defines which voltage monitors are mapped to the RESETB pin. | 0 = OV[x] and UV[x] not mapped to RESETB pin<br>1 = OV[x] and UV[x] are mapped to RESETB pin |

## STATUV (0x8)

UV Comparator Status Register (Read Clear)

| O V Comparate  |   | , | 73)     |     |        |           |   |   |  |

|----------------|---|---|---------|-----|--------|-----------|---|---|--|

| BIT            | 7 | 6 | 5       | 4   | 3      | 2         | 1 | 0 |  |

| Field          | _ | _ | UV[6:1] |     |        |           |   |   |  |

| Reset          | _ | _ |         | 0x0 |        |           |   |   |  |

| Access<br>Type | _ | _ |         |     | Read C | lears All |   |   |  |

| BITFIELD | BITS | DESCRIPTION                                                                                        | DECODE                                                                                               |

|----------|------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| UV       | 5:0  | UV Comparator Status for OUT1 (UV1),<br>OUT2 (UV2), OUT3 (UV3), OUT4 (UV4), IN5<br>(UV5), IN6 UV6) | 0 = UV[x] is above UV threshold<br>1 = UV[x] below UV threshold (or passed BIST<br>when exiting POR) |

## STATOV (0x9)

OV Comparator Status Register (Read Clear)

| O V Comparati  |   | ` ` | · '     |     |        |           |   |   |  |

|----------------|---|-----|---------|-----|--------|-----------|---|---|--|

| BIT            | 7 | 6   | 5       | 4   | 3      | 2         | 1 | 0 |  |

| Field          | _ | _   | OV[6:1] |     |        |           |   |   |  |

| Reset          | _ | _   |         | 0x0 |        |           |   |   |  |

| Access<br>Type | _ | _   |         |     | Read C | lears All |   |   |  |