### 3W MONO FILTER-LESS CLASS-D AUDIO POWER AMPLIFIER

June 2017

### **GENERAL DESCRIPTION**

The IS31AP2006 is a high efficiency, 3W mono Class-D audio power amplifier. A low noise, filter-less PWM architecture eliminates the output filter, reducing external component count, system cost, and simplifying design.

Operating in a single 5V supply, IS31AP2006 is capable of driving  $4\Omega$  speaker load at a continuous average output of 3W with 10% THD+N. The IS31AP2006 has high efficiency with speaker load compared to a typical Class-AB amplifier.

In cellular handsets, the earpiece, speaker phone, and melody ringer can each be driven by the IS31AP2006. The gain of IS31AP2006 is externally configurable which allows independent gain control from multiple sources by summing signals from each function.

The IS31AP2006 is available in DFN-8 (3mm×3mm) package.

#### **FEATURES**

- 5V supply at THD= 10%

- 3W into  $4\Omega$  (Typ.)

- 1.70W into 8Ω (Typ.)

- Efficiency at 5V:

- 83% at 400mW with a  $4\Omega$  speaker

- 89% at 400mW with an  $8\Omega$  speaker

- Optimized PWM output stage eliminates LC output filter

- Fully differential design reduces RF rectification and eliminates bypass capacitor

- Integrated pop-and-click suppression circuitry

- DFN-8 (3mm×3mm) package

#### **APPLICATIONS**

- Wireless or cellular handsets and PDAs

- Portable DVD player

- Notebook PC

- Portable radio

- Educational toys

- USB speakers

- Portable gaming

### **TYPICAL APPLICATION CIRCUIT**

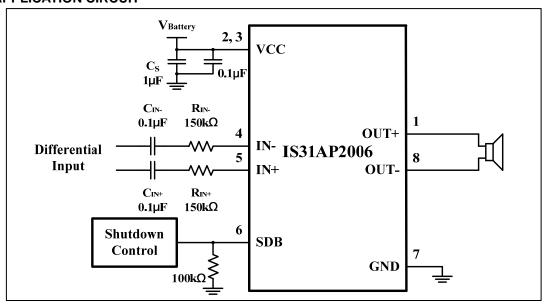

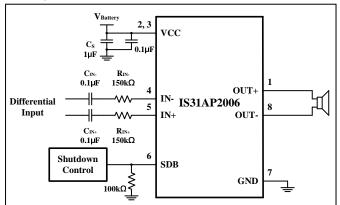

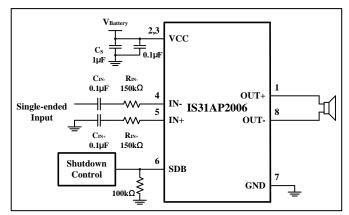

Figure 1 Typical Application Circuit (Differential Input)

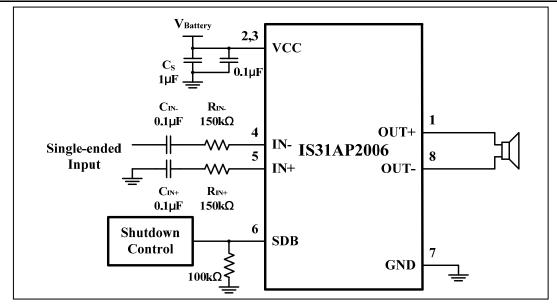

Figure 2 Typical Application Schematic (Single-ended Input)

### **PIN CONFIGURATION**

| Package | Pin Configuration (Top view) |  |  |  |

|---------|------------------------------|--|--|--|

| DFN-8   | OUT+ 1 1 OUT- VCC 2 1        |  |  |  |

### **PIN DESCRIPTION**

| No.  | Pin         | Description                         |  |

|------|-------------|-------------------------------------|--|

| 1    | OUT+        | Positive audio output.              |  |

| 2, 3 | VCC         | Power supply.                       |  |

| 4    | IN-         | Negative audio input.               |  |

| 5    | IN+         | Positive audio input.               |  |

| 6    | SDB         | Shutdown control, active low logic. |  |

| 7    | GND         | Ground.                             |  |

| 8    | OUT-        | Negative audio output.              |  |

|      | Thermal Pad | Connect to GND.                     |  |

ORDERING INFORMATION Industrial Range: -40°C to +85°C

| Order Part No.     | Package          | QTY/Reel |  |  |

|--------------------|------------------|----------|--|--|

| IS31AP2006-DLS2-TR | DFN-8, Lead-free | 2500     |  |  |

Copyright © 2017 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

- a.) the risk of injury or damage has been minimized;

- b.) the user assume all such risks; and

- c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

### **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage, V <sub>CC</sub>                 | -0.3V ~ +6.0V              |

|-------------------------------------------------|----------------------------|

| Voltage at any input pin                        | $-0.3V \sim V_{CC} + 0.3V$ |

| Maximum junction temperature, T <sub>JMAX</sub> | +150°C                     |

| Storage temperature range, T <sub>STG</sub>     | -65°C ~ +150°C             |

| Operating temperature range, T <sub>A</sub>     | -40°C ~ +85°C              |

| Thermal resistance, θ <sub>JA</sub>             | 70°C /W                    |

| ESD (HBM)                                       | ±7kV                       |

| ESD (CDM)                                       | ±500V                      |

**Note:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$V_{CC}$ = 2.7V ~ 5.5V,  $T_A$ = 25°C, unless otherwise noted.

| Symbol          | Parameter                                       | Condition                                    | Min. | Тур. | Max. | Unit |

|-----------------|-------------------------------------------------|----------------------------------------------|------|------|------|------|

| $V_{CC}$        | Supply voltage                                  |                                              | 2.7  |      | 5.5  | V    |

| V <sub>os</sub> | Output offset voltage (measured differentially) | V <sub>SDB</sub> = 0V, A <sub>V</sub> = 2V/V |      | 10   |      | mV   |

| ,               | Quiescent current                               | V <sub>CC</sub> = 5.5V, no load              |      | 2.6  |      | mΛ   |

| Icc             |                                                 | V <sub>CC</sub> = 2.7V, no load              |      | 1.2  |      | mA   |

| I <sub>SD</sub> | Shutdown current                                | V <sub>SDB</sub> = 0.4V                      |      |      | 1    | μA   |

| f <sub>SW</sub> | Switching frequency                             |                                              |      | 250  |      | kHz  |

| R <sub>IN</sub> | Input resistor                                  | Gain≤ 20V/V                                  | 15   |      |      | kΩ   |

| Gain            | Input gain                                      | R <sub>IN</sub> = 150kΩ                      |      | 2    |      | V/V  |

| V <sub>IH</sub> | High-level input voltage                        |                                              | 1.4  |      |      | V    |

| V <sub>IL</sub> | Low-level input voltage                         |                                              |      |      | 0.4  | V    |

# ELECTRICAL CHARACTERISTICS (NOTE 1) $T_A$ = 25°C, Gain= 2V/V.

| Symbol          | Parameter                    | Condition                                                                                     |                                 | Min. | Тур. | Max. | Unit  |

|-----------------|------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------|------|------|------|-------|

|                 |                              | THD+N= 10%<br>f= 1kHz, $R_L$ = $8\Omega$                                                      | V <sub>CC</sub> = 5.0V          |      | 1.70 |      | W     |

|                 |                              |                                                                                               | V <sub>CC</sub> = 4.2V          |      | 1.20 |      |       |

|                 |                              |                                                                                               | V <sub>CC</sub> = 3.6V          |      | 0.83 |      |       |

|                 |                              | THD+N= 10%<br>f= 1kHz, R <sub>i</sub> = 4Ω                                                    | V <sub>CC</sub> = 5.0V          |      | 3    |      | W     |

|                 |                              |                                                                                               | V <sub>CC</sub> = 4.2V          |      | 2.05 |      |       |

| Г               | Outrot a success             | 11112,112                                                                                     | V <sub>CC</sub> = 3.6V          |      | 1.55 |      |       |

| Po              | Output power                 | THD+N= 1% f= 1kHz, $R_L$ = $8\Omega$                                                          | V <sub>CC</sub> = 5.0V          |      | 1.45 |      | W     |

|                 |                              |                                                                                               | V <sub>CC</sub> = 4.2V          |      | 0.95 |      |       |

|                 |                              |                                                                                               | V <sub>CC</sub> = 3.6V          |      | 0.66 |      |       |

|                 |                              | THD+N=1% f= 1kHz, $R_L$ = $4\Omega$                                                           | V <sub>CC</sub> = 5.0V          |      | 2.50 |      | W     |

|                 |                              |                                                                                               | V <sub>CC</sub> = 4.2V          |      | 1.70 |      |       |

|                 |                              |                                                                                               | V <sub>CC</sub> = 3.6V          |      | 1.25 |      |       |

| TUDIN           | Total harmonic               | V <sub>CC</sub> = 5.0V, P <sub>O</sub> =1.0V                                                  | W, R <sub>L</sub> = 8Ω, f= 1kHz |      | 0.28 |      | 0/    |

| THD+N           | distortion plus noise        | $V_{CC}$ = 5.0V, $P_{O}$ =1.2W, $R_{L}$ = 4 $\Omega$ , f= 1kHz                                |                                 |      | 0.31 |      | %     |

| V <sub>N</sub>  | Output voltage noise         | $V_{CC}$ = 3.6V~5V, f= 20Hz to 20kHz, inputs ac-grounded with $C_{I}$ = 1 $\mu$ F A-Weighting |                                 |      | 68   |      | μVrms |

| t <sub>wu</sub> | Wake-up time from shutdown   | V <sub>CC</sub> = 3.6V                                                                        |                                 |      | 36   |      | ms    |

| SNR             | Signal-to-noise ratio        | $P_{O}$ =1.0W, $R_{L}$ = 8 $\Omega$ , $V_{CC}$ = 5.0V                                         |                                 |      | 92   |      | dB    |

| PSRR            | Power supply rejection ratio | V <sub>CC</sub> = 2.5V ~ 5.5V                                                                 |                                 |      | -55  |      | dB    |

Note 1: Guaranteed by design.

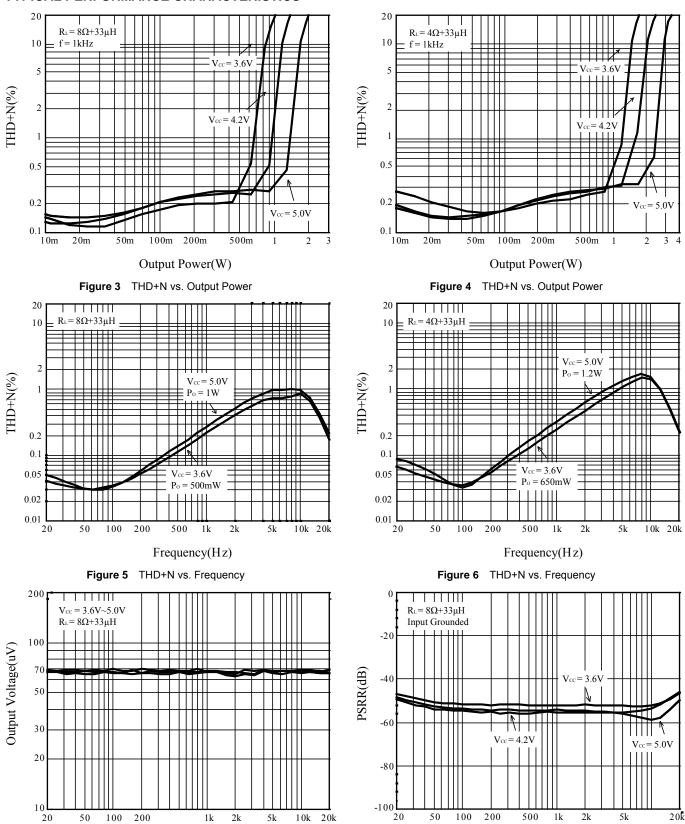

### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 8 PSRR vs. Frequency

Frequency(Hz)

Frequency(Hz)

Figure 7 Noise

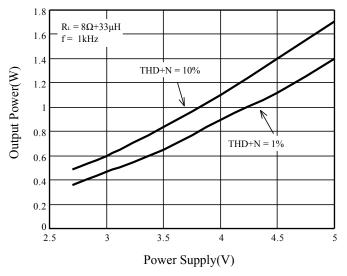

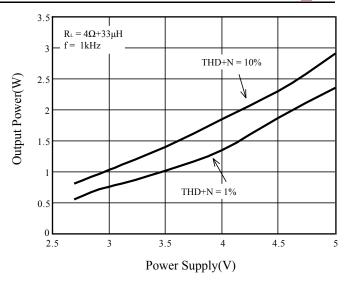

Figure 9 Output Power vs. Supply Voltage

Figure 10 Output Power vs. Supply Voltage

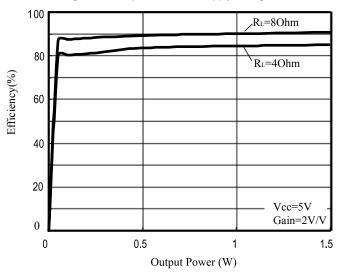

Figure 11 Efficiency vs. Output Power

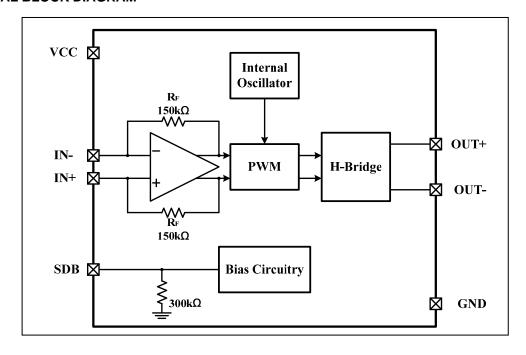

### **FUNCTIONAL BLOCK DIAGRAM**

# LUMISSIL MICROSYSTEMS A Division of [SSI]

#### APPLICATION INFORMATION

#### **FULLY DIFFERENTIAL AMPLIFIER**

The IS31AP2006 is a fully differential amplifier with differential inputs and outputs. The fully differential amplifier consists of a differential amplifier and a common-mode amplifier. The differential amplifier ensures that the amplifier outputs a differential voltage on the output that is equal to the differential input times the gain. The common-mode feedback ensures that the common-mode voltage at the output is biased around  $V_{\rm CC}/2$  regardless of the common-mode voltage at the input. The fully differential IS31AP2006 can still be used with a single-ended input; however, the IS31AP2006 should be used with differential inputs when in a noisy environment, like a wireless handset, to ensure maximum noise rejection.

# ADVANTAGES OF FULLY DIFFERENTIAL AMPLIFIERS

The fully differential amplifier does not require a bypass capacitor. This is because any shift in the midsupply affects both positive and negative channels equally and cancels at the differential output.

GSM handsets save power by turning on and shutting off the RF transmitter at a rate of 217Hz. The transmitted signal is picked-up on input and output traces. The fully differential amplifier cancels the signal much better than the typical audio amplifier.

### **COMPONENT SELECTION**

Figure 12 shows the IS31AP2006 with differential inputs and optional input capacitors. Input capacitors are used when the common mode input voltage range specs can not be guaranteed or high pass filter is considered.

Figure 13 shows the IS31AP2006 with single-ended inputs. The input capacitors have to be used in the single ended case because it is much more susceptible to noise in this case.

Figure 12 Typical Application Circuit with Differential Input

Figure 13 Typical Application Circuit with Single-Ended Input

### INPUT RESISTORS (RIN)

The input resistors  $(R_{IN})$  set the gain of the amplifier according to equation (1).

$$Gain = \frac{2 \times 150 \text{k}\Omega}{R_{IN}} \left(\frac{V}{V}\right) \tag{1}$$

Resistor matching is very important in fully differential amplifiers. The balance of the output on the reference voltage depends on matched ratios of the resistors. CMRR, PSRR, and cancellation of the second harmonic distortion diminish if resistor mismatch occurs. Therefore, it is recommended to use 1% accuracy resistors or better to keep the performance optimized. Matching is more important than overall accuracy.

Place the input resistors close to the IS31AP2006 to reduce noise injection on the high-impedance nodes.

For optimal performance the gain should be set to 2V/V or lower. Lower gain allows the IS31AP2006 to operate at its best, and keeps a high voltage at the input making the inputs less susceptible to noise.

#### **DECOUPLING CAPACITOR (Cs)**

The IS31AP2006 is a high-performance Class-D audio amplifier that requires adequate power supply decoupling to ensure high efficiency and low total harmonic distortion (THD). For higher frequency transients, spikes, or digital noises on the line, a good equivalent-series-resistance (ESR) ceramic capacitor, typically 1µF, placed as close as possible to the device V<sub>CC</sub> pin works best. Placing this decoupling capacitor close to the IS31AP2006 is also important for the efficiency of the Class-D amplifier, because any resistance or inductance in the trace between the device and the capacitor can cause a loss in efficiency. For filtering lower-frequency noise signals, a 10µF or greater capacitor placed near the audio power amplifier would also be helpful, but it is not required in most applications because of better PSRR of this device.

### INPUT CAPACITORS (CIN)

The input capacitors and input resistors form a high-pass filter with the corner frequency, f<sub>C</sub>, determined in equation (2).

$$f_C = \frac{1}{(2\pi R_{IN} C_{IN})}$$

(2)

The value of the input capacitor is important to consider as it directly affects the bass (low frequency) performance of the circuit. Speakers in wireless phones cannot usually respond well to low frequencies, so the corner frequency can be set to block low frequencies in this application.

Equation (3) is reconfigured to solve for the input coupling capacitance.

$$C_{IN} = \frac{1}{\left(2\pi R_{IN} f_C\right)} \tag{3}$$

If the corner frequency is within the audio band, the capacitors should have a tolerance of ± 10% or better. because any mismatch in capacitance causes an impedance mismatch at the corner frequency and below.

For a flat low-frequency response, use large input coupling capacitors (1µF). However, in a GSM phone the ground signal is fluctuating at 217Hz, but the signal from the codec does not have the same 217Hz fluctuation. The difference between the two signals is amplified, sent to the speaker, and heard as a 217Hz hum.

### SUMMING INPUT SIGNALS

Most wireless phones or PDAs need to sum signals at the audio power amplifier or just have two signal sources that need separate gain. The IS31AP2006 makes it easy to sum signals or use separate signal sources with different gains. Many phones now use the same speaker for the earpiece and ringer, where the wireless phone would require a much lower gain for the phone earpiece than for the ringer. PDAs and phones that have stereo headphones require summing of the right and left channels to output the stereo signal to the mono speaker.

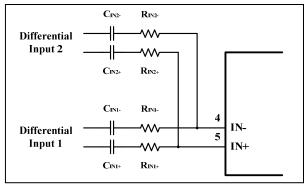

#### SUMMING TWO DIFFERENTIAL INPUT SIGNALS

Two extra resistors are needed for summing differential signals. The gain for each input source can be set independently (see equations (4) and (5), and Figure 14).

$$Gain1 = \frac{2 \times 150 k\Omega}{R_{IN1}} \left(\frac{V}{V}\right) \tag{4}$$

$$Gain 2 = \frac{2 \times 150 k\Omega}{R_{IN2}} \left(\frac{V}{V}\right)$$

(5)

Figure 14 Application Circuit with Summing Two Differential Inputs

If summing left and right inputs with a gain of 1V/V, use  $R_{IN1} = R_{IN2} = 300 k\Omega$ .

If summing a ring tone and a phone signal, set the ring-tone gain to Gain2= 2V/V, and the phone gain to Gain1= 0.1V/V. The resistor values would be.

$R_{IN1}$ = 3M $\Omega$ , and  $R_{IN2}$ = 150k $\Omega$ .

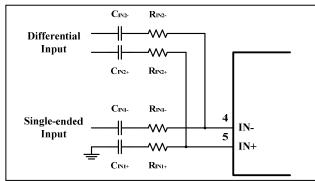

### SUMMING A DIFFERENTIAL INPUT SIGNAL AND A SINGLE-ENDED INPUT SIGNAL

Figure 15 shows how to sum a differential input signal and a single-ended input signal. Ground noise may couple in through IN- with this method. It is better to use differential inputs. The corner frequency of the single-ended input is set by C<sub>IN2</sub>, shown in equation (8). To assure that each input is balanced, the single-ended input must be driven by a low-impedance source even if the input is not in use.

$$Gain1 = \frac{2 \times 150 k\Omega}{R_{IN1}} \left(\frac{V}{V}\right)$$

(6)

$$Gain 2 = \frac{2 \times 150 k\Omega}{R_{IN2}} \left(\frac{V}{V}\right) \tag{7}$$

$$C_{IN2} = \frac{1}{\left(2\pi R_{IN2} f_{c2}\right)} \tag{8}$$

If summing a ring tone and phone signals, the phone signals should use the differential inputs while the ring tone should use the single-ended input. The phone gain is set at Gain2= 0.1V/V, and the ring-tone gain is set to Gain2= 0.1V/V, the resistor values would be

$$R_{IN1}$$

= 150k $\Omega$ , and  $R_{IN2}$ = 3M $\Omega$

The high pass corner frequency of the single-ended input is set by C<sub>IN2</sub>. If the desired corner frequency is less than 20Hz.

$$C_{IN1} = \frac{1}{2\pi R_{IN1} f_{C1}}$$

$$C_{IN2} > 53 pF$$

(10)

A Division of

Figure 15 Application Circuit with Summing Differential Input and Single-Ended Input Signals

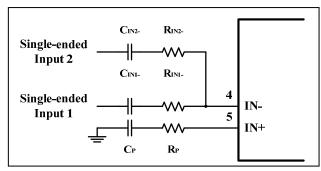

### **SUMMING TWO SINGLE-ENDED INPUT SIGNALS**

The gain and corner frequencies ( $f_{C1}$  and  $f_{C2}$ ) for each input source can be set independently (see equations (11) through (14), and Figure 16). Resistor,  $R_P$ , and capacitor,  $C_P$ , are needed on the IN+ terminal to match the impedance on the IN- terminal.

The single-ended inputs must be driven by low impedance sources.

$$Gain1 = \frac{2 \times 150 k\Omega}{R_{IN1}} \left(\frac{V}{V}\right) \tag{11}$$

$$Gain 2 = \frac{2 \times 150 k\Omega}{R_{IN2}} \left(\frac{V}{V}\right)$$

(12)

$$C_{IN1} = \frac{1}{2\pi R_{IN1} f_{C1}} \tag{13}$$

$$C_{IN2} = \frac{1}{2\pi R_{IN2} f_{C2}} \tag{14}$$

$$C_p = C_{IN1} + C_{IN2}$$

(15)

$$R_P = \frac{R_{IN1} \times R_{IN2}}{\left(R_{IN1} + R_{IN2}\right)} \tag{16}$$

Figure 16 Application Circuit with Summing Two Single-Ended Inputs

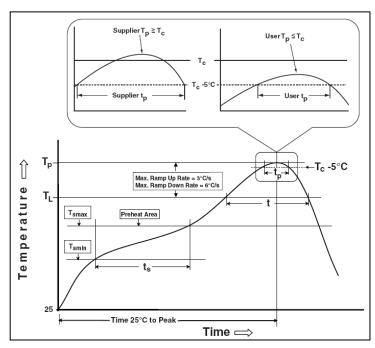

### **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                           | Pb-Free Assembly                 |  |  |

|-------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Preheat & Soak Temperature min (Tsmin) Temperature max (Tsmax) Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |  |  |

| Average ramp-up rate (Tsmax to Tp)                                                        | 3°C/second max.                  |  |  |

| Liquidous temperature (TL) Time at liquidous (tL)                                         | 217°C<br>60-150 seconds          |  |  |

| Peak package body temperature (Tp)*                                                       | Max 260°C                        |  |  |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                   | Max 30 seconds                   |  |  |

| Average ramp-down rate (Tp to Tsmax)                                                      | 6°C/second max.                  |  |  |

| Time 25°C to peak temperature                                                             | 8 minutes max.                   |  |  |

Figure 17 Classification Profile

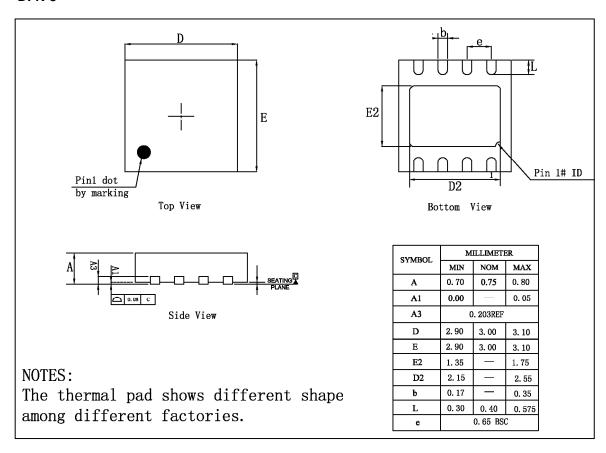

### **PACKAGING INFORMATION**

### DFN-8

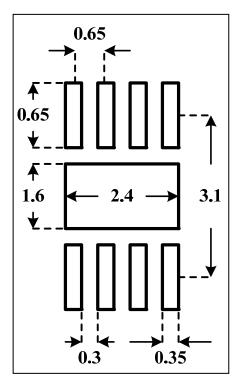

### **RECOMMENDED LAND PATTERN**

### DFN-8

### Note:

- 1. Land pattern complies to IPC-7351.

- 2. All dimensions in MM.

- 3. This document (including dimensions, notes & specs) is a recommendation based on typical circuit board manufacturing parameters. Since land pattern design depends on many factors unknown (eg. user's board manufacturing specs), user must determine suitability for use.

### **REVISION HISTORY**

| Revision | Detail Information                                              | Date       |

|----------|-----------------------------------------------------------------|------------|

| А        | Initial release                                                 | 2012.03.27 |

| В        | 1. Add ESD(CDM) 2. Add SOP-8 package 2. Add land pattern        | 2015.08.17 |

| С        | 1. Remove SOP-8 package information 2. Add $\theta_{\text{JA}}$ | 2017.06.02 |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ISSI:

IS31AP2006-DLS2-TR