#### About this document

#### Scope and purpose

This document provides the REF\_1KW\_PSU\_5G\_GaN reference board, which is a complete system solution for a 1000 W power supply unit (PSU) from Infineon targeting the new 5G specifications for outdoor small-cell telecom rectifiers.

This document also describes the converter system architecture and hardware with a summary of the experimental results.

#### **Intended audience**

This document is intended for design engineers who use the REF\_1KW\_PSU\_5G\_GaN reference board for developing the 1000 W PSU for 5G outdoor small-cell telecom rectifiers.

#### **Reference Board**

Product(s) embedded on a PCB, with focus on specific applications and defined use cases that can include software. PCB and auxiliary circuits are optimized for the requirements of the target application.

*Note:* Boards do not necessarily meet safety, EMI, and quality standards (for example UL, CE) requirements.

Important notice

#### **Important notice**

"Evaluation Boards and Reference Boards" shall mean products embedded on a printed circuit board (PCB) for demonstration and/or evaluation purposes, which include, without limitation, demonstration, reference and evaluation boards, kits and design (collectively referred to as "Reference Board").

Environmental conditions have been considered in the design of the Evaluation Boards and Reference Boards provided by Infineon Technologies. The design of the Evaluation Boards and Reference Boards has been tested by Infineon Technologies only as described in this document. The design is not qualified in terms of safety requirements, manufacturing, and operation over the entire operating temperature range or lifetime.

The Evaluation Boards and Reference Boards provided by Infineon Technologies are subject to functional testing only under typical load conditions. Evaluation Boards and Reference Boards are not subject to the same procedures as regular products regarding returned material analysis (RMA), process change notification (PCN) and product discontinuation (PD).

Evaluation Boards and Reference Boards are not commercialized products, and are solely intended for evaluation and testing purposes. In particular, they shall not be used for reliability testing or production. The Evaluation Boards and Reference Boards may therefore not comply with CE or similar standards (including but not limited to the EMC Directive 2004/EC/108 and the EMC Act) and may not fulfill other requirements of the country in which they are operated by the customer. The customer shall ensure that all Evaluation Boards and Reference Boards will be handled in a way, which is compliant with the relevant requirements and standards of the country in which they are operated.

The Evaluation Boards and Reference Boards as well as the information provided in this document are addressed only to qualified and skilled technical staff, for laboratory usage, and shall be used and managed according to the terms and conditions set forth in this document and in other related documentation supplied with the respective Evaluation Board or Reference Board.

It is the responsibility of the customer's technical departments to evaluate the suitability of the Evaluation Boards and Reference Boards for the intended application, and to evaluate the completeness and correctness of the information provided in this document with respect to such application.

The customer is obliged to ensure that the use of the Evaluation Boards and Reference Boards does not cause any harm to persons or third-party property.

The Evaluation Boards and Reference Boards and any information in this document is provided "as is" and Infineon Technologies disclaims any warranties, express or implied, including but not limited to warranties of noninfringement of third-party rights and implied warranties of fitness for any purpose, or for merchantability.

Infineon Technologies shall not be responsible for any damages resulting from the use of the Evaluation Boards and Reference Boards and/or from any information provided in this document. The customer is obliged to defend, indemnify, and hold Infineon Technologies harmless from and against any claims or damages arising out of or resulting from any use thereof.

Infineon Technologies reserves the right to modify this document and/or any information provided herein at any time without further notice.

Safety precautions

## Safety precautions

Note:

Please note the following warnings regarding the hazards associated with development systems.

| Table 1 | Safety precautions                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Warning: The DC link potential of this board is up to 1000 VDC. When measuring voltage waveforms by oscilloscope, high-voltage differential probes must be used. Failure to do so may result in personal injury or death.                                                                                                                                                                                                                         |

|         | Warning: The evaluation or reference board contains DC bus capacitors, which take<br>time to discharge after removal of the main supply. Before working on the drive<br>system, wait 5 minutes for capacitors to discharge to safe voltage levels. Failure to do<br>so may result in personal injury or death. Darkened display LEDs are not an indication<br>that capacitors have discharged to safe voltage levels.                             |

|         | Warning: The evaluation or reference board is connected to the grid input during<br>testing. Hence, high-voltage differential probes must be used when measuring voltage<br>waveforms by an oscilloscope. Failure to do so may result in personal injury or death.<br>Darkened display LEDs are not an indication that capacitors have discharged to safe<br>voltage levels.                                                                      |

|         | Warning: Remove or disconnect power from the drive before you disconnect or reconnect wires, or perform maintenance work. Wait five minutes after removing power to discharge the bus capacitors. Do not attempt to service the drive until the bus capacitors have discharged to zero. Failure to do so may result in personal injury or death.                                                                                                  |

|         | <b>Caution:</b> The heat sink and device surfaces of the evaluation or reference board may become hot during testing. Hence, necessary precautions are required while handling the board. Failure to comply may cause injury.                                                                                                                                                                                                                     |

|         | <b>Caution:</b> Only personnel familiar with the drive, power electronics and associated machinery should plan, install, commission and subsequently service the system. Failure to comply may result in personal injury and/or equipment damage.                                                                                                                                                                                                 |

|         | <b>Caution:</b> The evaluation or reference board contains parts and assemblies sensitive to electrostatic discharge (ESD). Electrostatic control precautions are required when installing, testing, servicing or repairing the assembly. Component damage may result if ESD control procedures are not followed. If you are not familiar with electrostatic control procedures, refer to the applicable ESD protection handbooks and guidelines. |

|         | <b>Caution:</b> A drive that is incorrectly applied or installed can lead to component damage or reduction in product lifetime. Wiring or application errors such as undersizing the motor, supplying an incorrect or inadequate AC supply, or excessive ambient temperatures may result in system malfunction.                                                                                                                                   |

|         | <b>Caution:</b> The evaluation or reference board is shipped with packing materials that need to be removed prior to installation. Failure to remove all packing materials that are unnecessary for system installation may result in overheating or abnormal operating conditions.                                                                                                                                                               |

Table of contents

## **Table of contents**

| Abou   | About this document1                                            |   |  |  |

|--------|-----------------------------------------------------------------|---|--|--|

| Impo   | rtant notice                                                    | 2 |  |  |

| Safet  | y precautions                                                   | 3 |  |  |

| Table  | of contents                                                     | 4 |  |  |

| 1      | Introduction                                                    | 5 |  |  |

| 1.1    | Edge computing application                                      |   |  |  |

| 1.2    | REF_1KW_PSU_5G_GaN introduction                                 |   |  |  |

| 1.3    | Features for REF_1KW_PSU_5G_GaN for edge computing application  |   |  |  |

| 2      | System description1                                             |   |  |  |

| 2.1    | Signal conditioning for digital control of totem-pole CCM PFC1  |   |  |  |

| 2.2    | Interleaved totem-pole PFC: Estimated efficiency1               |   |  |  |

| 2.2.1  | PFC magnetics                                                   |   |  |  |

| 2.2.2  | Driving CoolGaN™ and CoolMOS™ in the interleaved totem-pole PFC |   |  |  |

| 2.3    | Experimental results: Interleaved PFC steady state-operation    |   |  |  |

| 2.3.1  | Steady-state operation2                                         | 0 |  |  |

| 2.3.2  | Interleaved PFC efficiency2                                     | 3 |  |  |

| 2.4    | Half-bridge LLC                                                 | 4 |  |  |

| 2.4.1  | LLC magnetics2                                                  | 6 |  |  |

| 2.5    | Driving CoolMOS™ in the LLC converter2                          | 8 |  |  |

| 2.6    | Primary side: LLC steady-state operation2                       |   |  |  |

| 2.7    | Secondary side: LLC steady-state operation                      | 0 |  |  |

| 2.7.1  | LLC efficiency                                                  | 2 |  |  |

| 3      | Full power supply unit                                          | 3 |  |  |

| 3.1.1  | Efficiency                                                      | 3 |  |  |

| 3.1.2  | Start up3                                                       |   |  |  |

| 3.1.3  | Hold-up time                                                    |   |  |  |

| 3.1.4  | Load-jump                                                       |   |  |  |

| 3.1.5  | Thermal characterization4                                       |   |  |  |

| 3.1.6  | EMI4                                                            | 3 |  |  |

| 4      | Summary4                                                        | 5 |  |  |

| 5      | Schematics4                                                     | 6 |  |  |

| 5.1    | Main board4                                                     |   |  |  |

| 5.2    | Control cards4                                                  |   |  |  |

| 5.2.1  | PFC controller card4                                            |   |  |  |

| 5.2.2  | LLC controller card4                                            |   |  |  |

| 5.2.3  | Bias board4                                                     |   |  |  |

| 5.2.4  | Capacitor card5                                                 |   |  |  |

| 5.2.5  | EMI filter card5                                                |   |  |  |

| 5.2.6  | Assembling view5                                                |   |  |  |

| 6      | Bill of materials5                                              | 3 |  |  |

| Refer  | ences5                                                          | 8 |  |  |

| Acror  | nyms/abbreviations5                                             | 9 |  |  |

| Revis  | ion history6                                                    | 0 |  |  |

| Discla | aimer6                                                          | 1 |  |  |

Introduction

## 1 Introduction

## 1.1 Edge computing application

In the context of the upcoming 5G technology era, the development of the new generation of communications networks (5G networks, satellite networks, etc.) addresses important challenges, attempting to provide a wide variety of services and applications with unseen data rates.

5G and edge computing are two linked key elements of the modern information and communications technology (ICT) ecosystem. They both aim to significantly improve the performance of applications and enable huge amounts of data to be processed in real time. 5G increases speeds by up to ten times more than 4G, whereas mobile edge computing reduces latency by bringing compute capabilities into the network and closer to the end user.

The main focus of the present work is the edge computing. Edge computing is a distributed open platform integrating the core capabilities of network such as, computing, storage, and application, which provides intelligent services at the network edge close to devices/terminals or data sources. In other words, it directly analyzes data collected from the terminals at (or near) the device where data is generated. This eliminates the need to transmit every time data to the cloud data processing center. Edge computing then features "real-time" data processing and quicker response and therefore is ideal to support the Internet of Things (IoT) architecture.

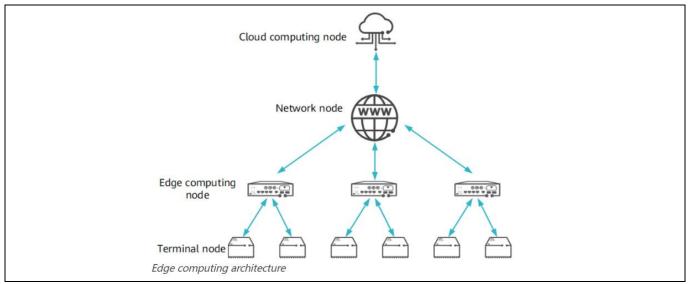

The typical edge computing architecture (Figure 1) can be described as follows:

- **Terminal:** The terminal layer consists of various IoT devices, such as sensors, cameras, and smartphones, which collect and report raw data. At this layer, the IoT devices need to provide only sensing capabilities but not computational ones.

- **Edge computing node:** Edge computing nodes enable the response to basic services by deploying and allocating the computing and storage capabilities at the network edge.

- **Network node:** A network node uploads useful data obtained through edge computing nodes to cloud computing nodes for analysis and processing.

- **Cloud computing node:** The data reported by the edge computing layer is permanently stored on cloud computing node.

Figure 1 Edge computing architecture

#### Introduction

Typically, edge computing is deployed through highly scalable and compact micro datacenters with extremely variable sizes, from the "shoebox- like" one (≤1 kW needed power) to containerized solutions up to 500 kW.

In recent signal tower installations, the edge system includes an IP65 enclosure, which can be assembled either at the telecom radio access network (RAN) tower, on buildings, or on lighting infrastructure, similar to the latest generation of 5G outdoor small cell base stations.

The success of edge computing then depends on the availability of suitable hardware, systems that can economically provide the necessary processing speed and power that can survive in the less-regulated and more unpredictable environments encountered away from the conventional datacenter. The edge computing hardware must comprise compact, energy-efficient solutions that can be widely deployed, even in space-constrained and harsh environments, to locate computing as closer as possible to sensors and other data sources. This will have an impact on the needed AC-DC power supply requirements. Compact and thin form factor is the first key feature of a PSU for this application. Efficiency must also be high, because of the ubiquitous micro-datacenters installation, either in remote locations or in areas with high population density: in both these cases, due to different reasons, the cost of the kWh is not cheap.

Also due to the ubiquitous installation, the maintenance cost of such a micro-datacenter is a significant portion of the operating expense sustained by the operator companies. The intensive use of convection cooling is an excellent way to reduce the need of maintenance (no fans and filters replacement required). In general, the outdoor operation, even though inside an IP65 enclosure, has several implications on the environmental conditions of the PSU, which is required to operate in a wide AC input voltage (typically 85–305 V AC) and ambient temperature range (–40°C/+85°C). Therefore, heat dissipation and thermal management are indeed key aspects of such a SMPS design. To conclude that a PSU for outdoor edge servers has to fulfill most of the typical requirements of a telecom rectifier, e.g., for outdoor small cells, including the compliance to standards like Telcordia GR-3108 and GR-487. The present work addresses the main challenges in the design of a compact and efficient 1 kW AC-DC power supply for edge computing outdoor applications.

All these requirements have been translated in a power supply specification for edge computing and outdoor small-cell application that has driven the design of REF\_1KW\_PSU\_5G\_GaN. The full specification is described in the following section.

Introduction

#### 1.2 REF\_1KW\_PSU\_5G\_GaN introduction

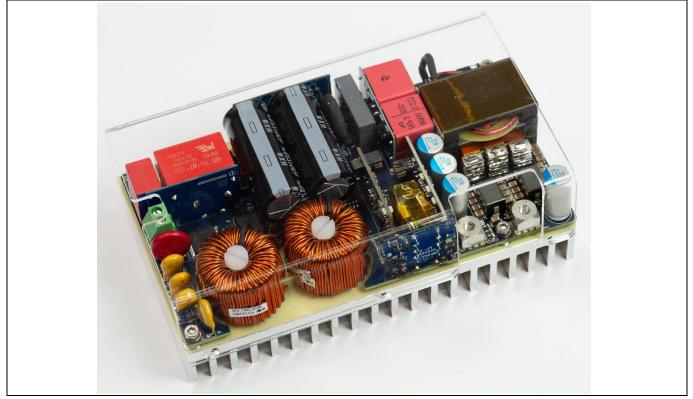

Figure 2 1000 W fanless power supply with CoolGaN<sup>™</sup> in TOLL package

- This design is developed to meet the demand for high efficiency in power supply units for modern applications.

- The power supply unit (PSU) consists of two converters:

- An interleaved totem pole power factor correction (PFC) converter.

- A DC-DC isolated half-bridge (HB) LLC converter.

- The front-end converter (Figure 3) provides PFC and total harmonic distortion (THD) control, and use as an interleaved totem-pole topology to achieve high efficiency.

- The back-end converter (Figure 3) is a DC-DC isolated half-bridge LLC converter, which provides safety isolation and a tightly regulated output voltage of 12 V DC.

- The PSU design and control system have been optimized to achieve high efficiency, with peak efficiency measured at 96.32% at 230 V AC and 95.5% at 115 V AC.

- The overall dimensions of the PSU are 150 mm x 80 mm x 27 mm, yielding a power density in the range of 50 W/inch<sup>3</sup>.

The main Infineon components used in the REF\_1KW\_PSU\_5G\_GaN are:

- CoolGaN<sup>™</sup> 600 V, 70 mΩ in TOLL package (IGT60R070D1) in the PFC high-frequency power transistors

- CoolMOS<sup>™</sup> 600 V, S7 22 mΩ in TOLL package (IPT60R022S7) in the PFC line-rectification MOSFETs

- CoolMOS<sup>™</sup> 600 V, CFD7 55 mΩ in TOLL package (IPT60R055CFD7) in the DC-DC primary-side HB

- OptiMOS<sup>™</sup> 6 40 V, 0.9 mΩ in PG-WSON-8 package (BSC009N04LSSC) in the DC-DC secondary-side bridge

- EiceDRIVER<sup>™</sup> 1EDF5673K and 1EDN8550B gate drivers for driving the PFC high- and low-side CoolGaN<sup>™</sup>, respectively

#### Introduction

- EiceDRIVER<sup>™</sup> 1EDB8275F and 1EDN8511B gate drivers for driving the PFC high- and low-side CoolMOS<sup>™</sup> MOSFETs, respectively

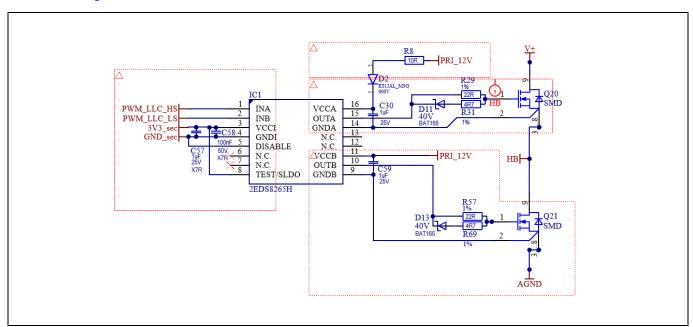

- EiceDRIVER<sup>™</sup> 2EDS8265H for driving the DC-DC primary-side CoolMOS<sup>™</sup> MOSFET

- EiceDRIVER<sup>™</sup> 1EDN7511B for driving the DC-DC secondary-side OptiMOS<sup>™</sup> MOSFET

- XMC4200 MCU for the PFC control implementation

- XMC4402 MCU for the DC-DC control implementation

- ICE2QR2280G switching controller for the bias supply implementation

## **1.3** Features for REF\_1KW\_PSU\_5G\_GaN for edge computing application

This application note provides a detailed description of the design considerations and experimental results of a high-efficiency, high-power-density, ultra-compact telecom rectifier for 5G small-cell and edge computing applications.

The key features of this reference board are:

- Attractive **compact design** in 50 W/in<sup>3</sup> form factor for a 1000 W PSU

- Low profile 27 mm maximum PSU height

- Very high efficiency for 12 V output PSU above 96 percent from 45 percent of the rated load upward when V<sub>in</sub> is equal to 230 V AC, and above 95 percent from 35 percent of the rated load upward when V<sub>in</sub> is equal to 115 V AC

- Fanless design with the possibility of attaching the reference board to a heatsink

- Fully digital control implementation using XMC<sup>™</sup> MCU

- High thermal performance achieved by using best-in-class devices in TOLL package from Infineon

- Robust and reliable operation under different abnormal conditions:

- Load-jump reaction and output regulation

- Inrush current during start-up

- Relay replacement with static switch because of CoolMOS<sup>™</sup> S7 MOSFET

Table 2 shows a summary of the main specifications and requirements of the telecom rectifier.

| Requirements                         | Conditions                               | Specification                                |  |

|--------------------------------------|------------------------------------------|----------------------------------------------|--|

| Input voltage V <sub>in</sub>        | 85 V AC to 265 V AC                      | 100 V AC to 240 V AC nominal                 |  |

| Output voltage V <sub>ref</sub>      | -                                        | 12 V DC nominal                              |  |

| Output power                         | 85 V AC to 265 V AC                      | 1000 W                                       |  |

|                                      | 12 V DC                                  |                                              |  |

| Efficiency target                    | 230 V AC input, 12 V DC output           | η≥96% (peak efficiency)                      |  |

|                                      | 115 V AC input, 12 V DC output           | η ≥ 95% (peak efficiency)                    |  |

| Steady-state V <sub>out</sub> ripple | Nominal input, 12 V DC output            | $ \Delta V_{out}  \le 50 \text{ mV}_{pk-pk}$ |  |

| Power factor and THD                 | 100 V AC to 240 V AC                     | Lower than 10% from 20% of the load          |  |

| Load transient                       | 0 A ↔ 83 A, 1 A/μs                       | $ \Delta V_{out}  < 1.2 V_{pk}$              |  |

|                                      | 83 A $\leftrightarrow$ 0 A, 1 A/ $\mu$ s |                                              |  |

| Table 2 | Summary of the requirements and specifications for the 5G PSU |

|---------|---------------------------------------------------------------|

|---------|---------------------------------------------------------------|

#### Introduction

| Requirements | Conditions                  | Specification                              |

|--------------|-----------------------------|--------------------------------------------|

| Dimensions   | Not including plastic cover | H <sub>max</sub> = 27 mm                   |

|              |                             | W <sub>max</sub> = 80 mm                   |

|              |                             | L <sub>max</sub> = 150 mm                  |

| Cooling      | _                           | Natural/convection                         |

| Hold-up time | 100% of power               | 10 ms with V DC greater or equal to 10.8 V |

| EMI          | -                           | EN55022 Class A with a 6 dB margin         |

## 2 System description

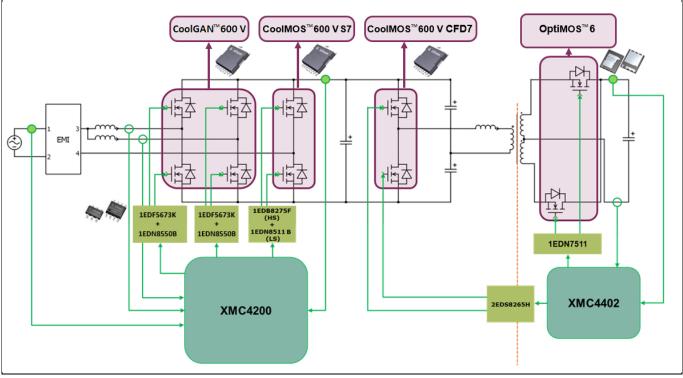

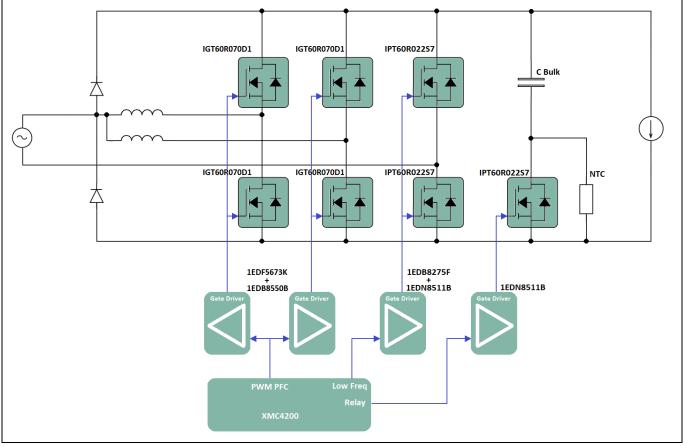

Figure 3 shows the simplified circuit diagram of the REF\_1KW\_PSU\_5G\_GaN reference board.

#### Figure 3 Simplified schematic of REF\_1KW\_PSU\_5G\_GaN reference board with Infineon components used

The PSU comprises a front-end AC-DC bridgeless interleaved totem-pole converter followed by a back-end DC-DC isolated LLC converter. The front-end converter provides power factor correction (PFC) and control of the total harmonic distortion (THD). The LLC converter provides safety isolation and a tightly regulated output voltage at 12 V DC.

The control of the interleaved totem-pole AC-DC converter is implemented with a dedicated control card PCB based on XMC4200 MCU from Infineon that includes PFC, THD, voltage regulation, input overcurrent protection (OCP), overvoltage protection (OVP), and undervoltage protection (UVP), and start up.

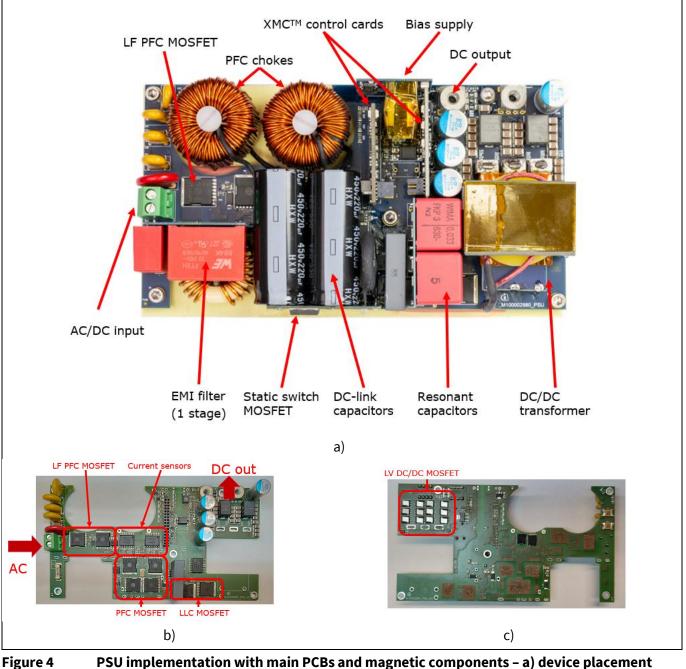

Furthermore, to increase power density, the standard inrush current relay has been replaced with CoolMOS<sup>™</sup> S7 MOSFET that is placed on the DC-link capacitor PCB as shown by the implementation view of Figure 4a. Benefits of relay replacement with a static switch MOSFETs have been described in detail in [1].

The PFC is operated in both high-line (230 V AC) and low-line (115 V AC) in continuous conduction mode (CCM) with 65 kHz of switching frequency. The bulk capacitance is designed to comply with 10 ms hold-up time at full load.

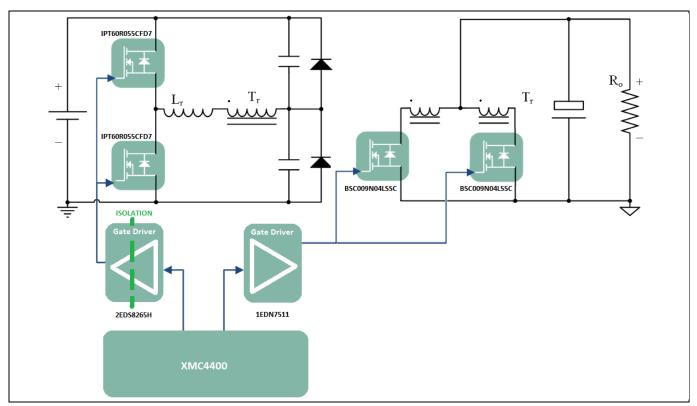

The control of the LLC is implemented with another dedicated control card PCB based on XMC4400 MCU from Infineon that includes open-loop/overload protection with extended blanking time, two levels of OCP: frequency shift and latch off, mains input UVP with adjustable hysteresis, adjustable minimum switching frequency with high accuracy, built-in digital and non-linear soft start, and burst-mode operation.

Figure 4b/c shows the placement of the different sections of the REF\_1KW\_PSU\_5G\_GaN telecom PSU with TOLL packages from Infineon. The board shown is 150 mm long with a width of 80 mm and a height of 27 mm.

Figure 4 shows the PSU with the leftmost component being the AC connector. Adjacent to the AC connector is the single-stage EMI filter. Above the filter, two PFC chokes are strategically placed on a PCB cutout to facilitate thermal connection to the metal baseplate using thermal interface material. Similar placement and thermal management techniques have been employed for the LLC main transformer, which is located on the centerright side of the PSU board.

Moving to the middle of the board, a daughter card is installed containing the bulk capacitors, the NTC, and the static switch. This compact arrangement aims to optimize the use of space and enhance the overall efficiency of the PSU. Lastly, the main switches for both stages of the PSU are found on the top-side layer of the main PCB, along with all the drivers. Additionally, the bias supply circuit and the two controllers are implemented in a daughter card. This design ensures that all crucial components are strategically placed for optimal performance and to minimize thermal issues.

igure 4 PSU implementation with main PCBs and magnetic components – a) device placement view, b) top, and c) bottom sides

#### **System description**

The Infineon devices used in the implementation of REF\_1KW\_PSU\_5G\_GAN interleaved PFC are listed as follows:

- CoolGaN<sup>™</sup> 600 V, 70 mΩ (IGT60R070D1) in TOLL package, as totem-pole PFC high frequency switches.

- CoolMOS<sup>™</sup> S7 600 V, 22 mΩ (IPT60R022S7) in TOLL package, for the totem-pole PFC return path (low frequency bridge) as well as relay replacement.

- EiceDRIVER<sup>™</sup> 1EDF5673K, 1EDN8550B, 1EDB8275F, and 1EDN8511B gate drivers.

- XMC42 MCU in QFN 48-pin package for PFC control implementation.

Figure 5 shows a simplified block diagram of the bridgeless topology with the mentioned devices from the Infineon portfolio. The diodes in front of the PFC choke are meant to be a current path for startup or surge conditions and it is not part of the current path during the steady-state converter operation.

Figure 5 Bridgeless interleaved totem-pole PFC of 1 kW fanless PSU board (REF\_1KW\_PSU\_5G\_GAN) with the Infineon components used

This document will describe the REF\_1KW\_PSU\_5G\_GAN board implementation, as well as the specifications and main test results. For further information on Infineon devices, visit the Infineon website, the Infineon evaluation board search, and the different websites for the different implemented components:

- CoolGaN<sup>™</sup> power transistor

- CoolMOS<sup>™</sup> power MOSFET

- Gate driver ICs

- XMC<sup>™</sup> MCU

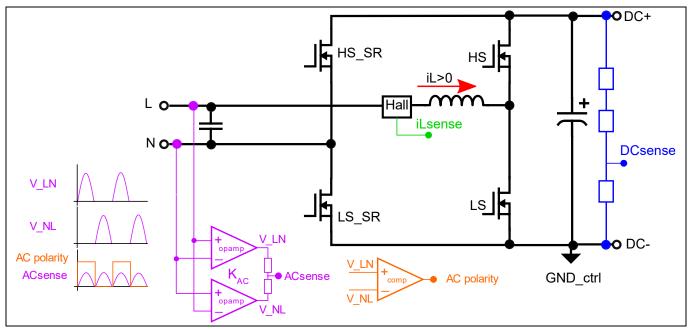

## 2.1 Signal conditioning for digital control of totem-pole CCM PFC

The interleaved PFC of REF\_1KW\_PSU\_5G\_GaN implements CCM average current mode control with duty feed-forward (DFF). Unlike the classic PFC, in which the AC voltage is rectified by the diode bridge in the bridgeless totem-pole PFC converter, the inductor current is both positive and negative. In addition, isolation or common mode rejection is required to measure the inductor current if the control ground in place in the negative rail of the bulk voltage, as it has been traditionally done in classic PFC. Therefore, a Hall-effect sensor is a good solution for this type of system.

The output of the Hall-effect sensor matches very well the analog-to-digital converter (ADC) inputs when supplied with the same voltage: positive and negative current are measured with the span of the ADC and a shift to half of the ADC range for zero current. If a sensor with proper bandwidth is selected, also the high frequency ripple can be sensed and the signal can be used for peak current limitation as well. In case of lower bandwidth (BW), the Hall-effect sensor typically offers an overcurrent detection signal which could be used for the same purpose.

Because of the control reference location, the bulk voltage sense is as simple as a resistive partition as shown in Figure 6. In the case of the of AC voltage sense, to avoid issues during AC zero crossing if no current is flowing into the PFC, both lines are sensed against ground and then added. As the total AC sensing signal is rectified, a comparison of both line and neutral sensing voltages provide the polarity signal.

Figure 6Block diagram of the sensing circuitry required for bidirectional totem-pole control with<br/>XMC™ MCU and control reference in the AC rail in series with the PFC choke

As the AC voltage is used for the current reference generation in the selected average current mode structure, the current reference is a full wave rectified sinusoidal sequence. However, the current sense after the ADC is a sinusoidal sequence with offset at half of the ADC span. Therefore, the ADC result from the current sense requires first the offset to be removed and then rectified according to the AC polarity signal. These two steps, together with extra gain, are implemented by software in the XMC<sup>™</sup> controller.

#### **System description**

## Figure 7 Current loop structure with duty cycle feed-forward and the required current manipulation

Application note

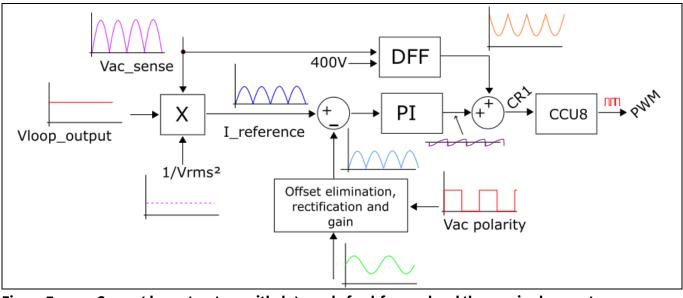

#### 2.2 Interleaved totem-pole PFC: Estimated efficiency

This section will analyze the interleaved PFC converter with 115 V and 230 V AC RMS input and operating with a switching frequency of 65 kHz.

In particular, Figure 8 presents a comparison between the estimated design efficiency of the PFC (blue plot) and the actual measured efficiency (red plot) at an input voltage of 230 V AC. The data indicates a close alignment at full-load condition, with some variances observed at light and middle load conditions.

Despite these discrepancies, the estimation provides valuable insights into the behavior of the PFC across the entire load range, offering a comprehensive understanding from light to full load conditions.

Note that the PFC unit demonstrates high peak efficiency of 99% at nearly 1000 W of output power.

Figure 8 Comparison between estimated and real efficiency of the interleaved PFC converter

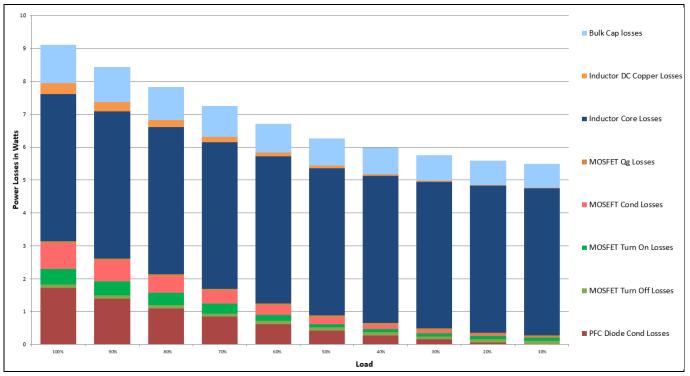

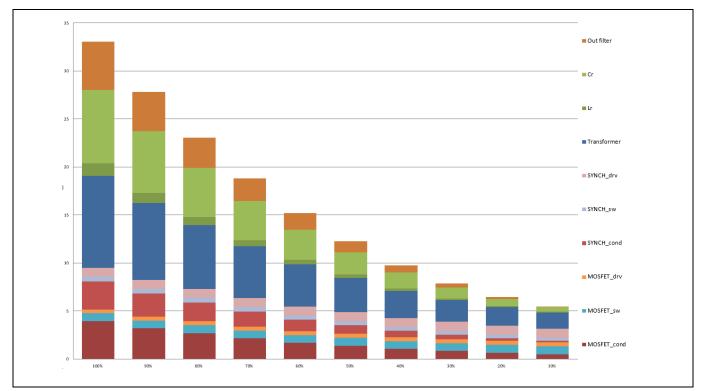

Figure 9 illustrates the distribution of losses across various devices at different operating points for the PFC. The bar plot shows the distribution of losses across the PFC components, highlighting that the majority of losses are concentrated in the main PFC inductor.

#### System description

Figure 9 Estimated distribution losses of the interleaved PFC

### 2.2.1 PFC magnetics

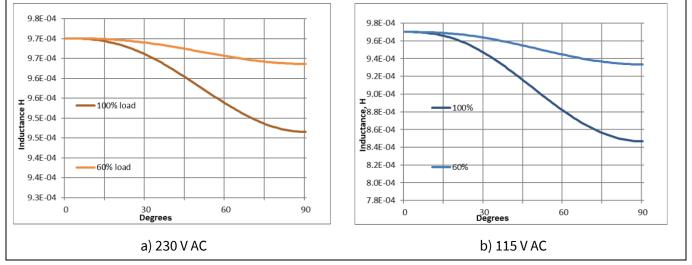

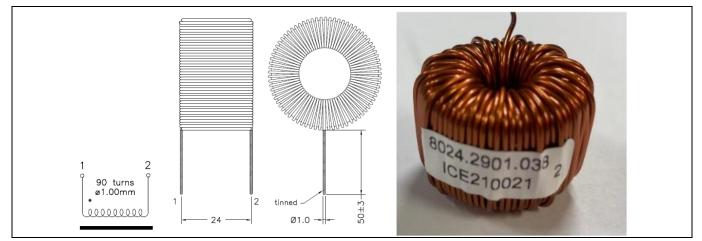

The other main contributors to the losses to consider in the design of the dual-boost AC-DC converter are the main inductor and the EMI filter. The PFC choke design is based on a toroidal high-performance magnetic powder core. Toroidal chokes have a large surface area and allow a good balance, minimizing core and winding losses, and achieving a homogeneous heat distribution without hot spots. For this reason, they are suitable for systems that are targeting the highest power density; very small choke sizes are feasible. The chosen core material CH270060GTE18 is high flux from Chang Sung Corporation (CSC), which has an excellent DC bias and good core loss behavior. The outer diameter of the core is 27 mm with a height of 19 mm. The winding was implemented using enameled AWG 18 (1.1 mm diameter) copper wire. The winding covers approximately two layers represented in Figure 11. This arrangement allows a good copper fill factor, while still having good AC characteristics, and is a preferred fill form factor for high-power toroidal inductors. There are 90 turns, taking advantage of the high permitted DC bias. The resulting small-signal bias inductance is 1 mH. The effective inductance with current bias is determined by the core material B-H characteristics, illustrated in Figure 10.

Figure 10 Angle of input current depending on the PFC choke inductance value

Figure 11 Image of PFC choke

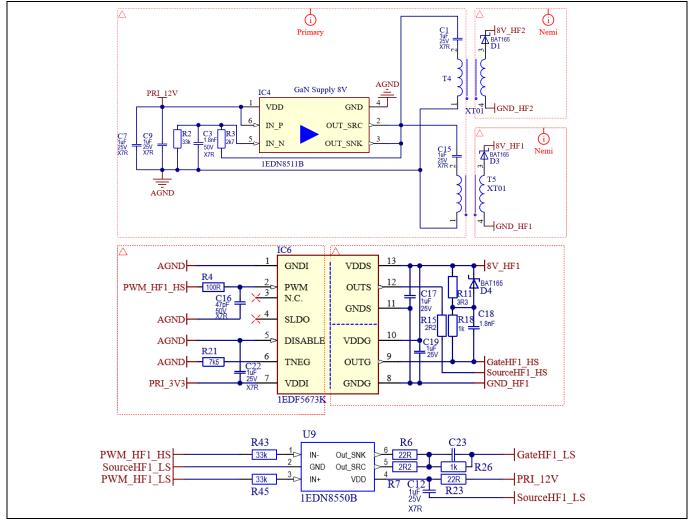

## 2.2.2 Driving CoolGaN<sup>™</sup> and CoolMOS<sup>™</sup> in the interleaved totem-pole PFC

To ensure the proper functioning of the PFC converter, the driving stage plays a critical role. In accordance with the recommended driving voltage for CoolGaN<sup>™</sup> devices, an 8 V/0 V unipolar driving voltage is used. The bias supplies are initially created by the 12 V output flyback to the 8 V with the help of the 1EDB8511B gate driver used as an oscillator plus with the help of a transformer for creating the isolation.

The gallium nitride (GaN) MOSFET cannot be driven like a conventional MOSFET because of the need for a steady-state "on" current and a negative "off" voltage. So, to avoid a dedicated driver with two separate "on" paths and bipolar supply voltage, the solution shown in Figure 12 is chosen.

Combining the 1EDF5673K gate driver and a passive RC circuit, it is easy to supply a certain amount of current during the steady-state "on" state and a negative "off" voltage for turn off the CoolGaN™.

This selected approach is both uncomplicated and cost-efficient, making it an excellent solution for implementation.

Figure 12 Driving CoolGaN<sup>™</sup> with 1EDF5673K and 1EDN8550 gate drivers

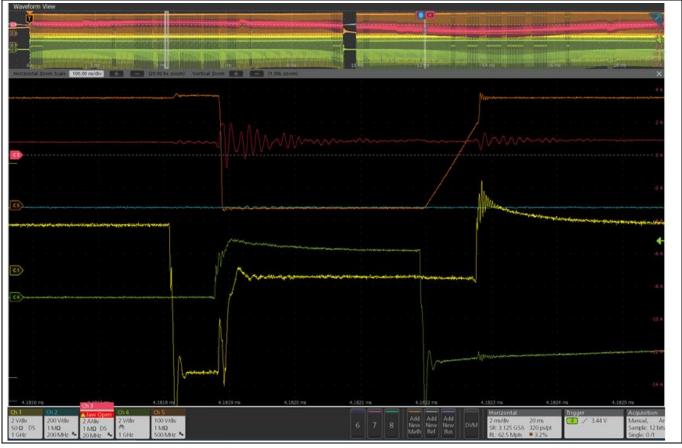

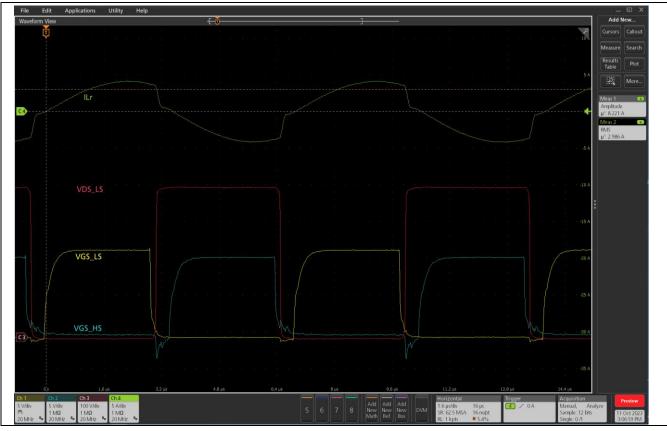

Figure 13 shows the switching sequence utilized by the 1EDF5673K gate driver. The oscilloscope image showcases the sequence applied to the Vgs of the high-side MOSFET.

- Orange color waveform represents the low-side Vds.

- Red color waveform shows the inductor current.

- Green color line corresponds to the Vgs of the totem-pole low-side CoolGaN™.

- Yellow color line representing the Vgs signal applied to the high-side CoolGaN™.

During 't0', the high-side CoolGaN<sup>™</sup> power transistor is in the "on" state. At the start of 't1', a turn-off event occurs, where the driver applies a negative voltage to the Vgs of the device for a specified dead-time, which can be configured by an external resistor in the driver. This negative voltage ensures the proper turn-off of the MOSFET. Subsequently, during 't2', the driver applies zero volts to the gate of the MOSFET, effectively reducing the driver losses. Concurrently, the green color line, the Vgs of the low-side is turned on. Finally, during 't3', the dead-time is applied by the microcontroller.

**Figure 13** Vgs voltages of CoolGaN<sup>™</sup> in the high frequency leg of a totem-pole PFC

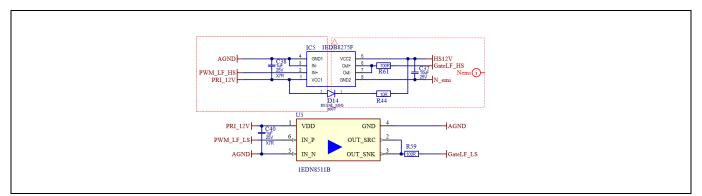

Figure 14 shows the driving of the CoolMOS<sup>™</sup> MOSFET. A hybrid driving approach with an isolated high-side and non-isolated low-side switch has been adopted. Additionally, for the four CoolMOS<sup>™</sup> MOSFETs synchronous rectification legs that are switching at 50 Hz, a bootstrap approach has been adopted to minimize costs. In this case, proper capacitor dimensioning is required to discharge and avoid hitting the UVLO threshold of the driver.

#### Figure 14 Driving CoolMoS<sup>™</sup> with hybrid driving (1EDB8275F + 1EDN8511B gate drivers)

#### 2.3 Experimental results: Interleaved PFC steady state-operation

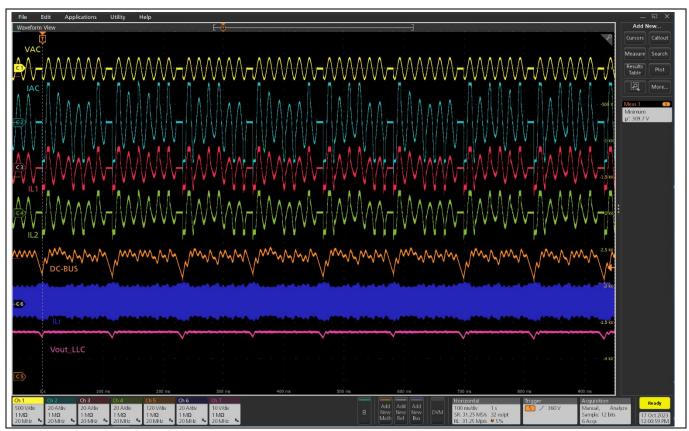

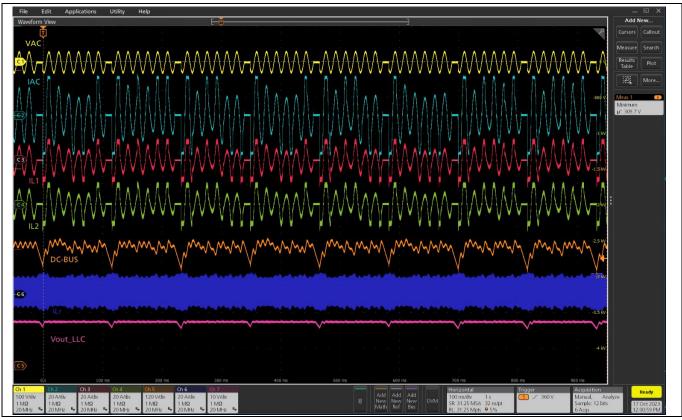

This section provides a summary of the experimental results pertaining to the steady-state operation of the interleaved PFC, with a specific focus on the steady-state waveforms at 115 V RMS and 230 V RMS AC. It will showcase the behavior of the PFC during full load operation and the efficiency of the PFC at 115 V and 230 V AC RMS.

#### 2.3.1 Steady-state operation

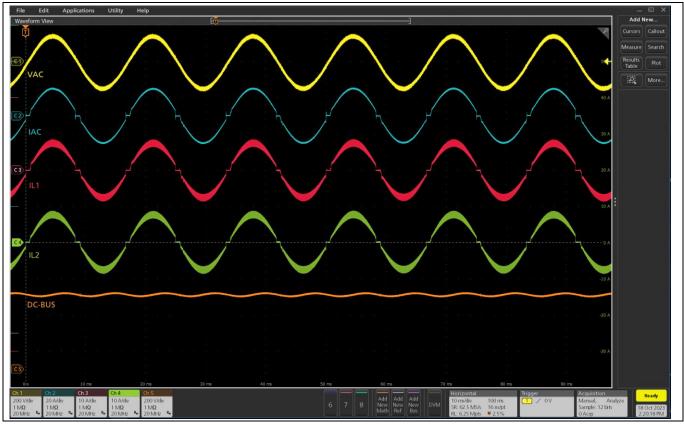

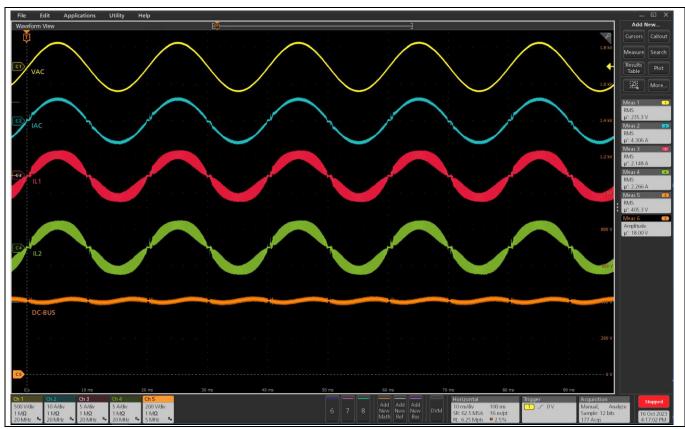

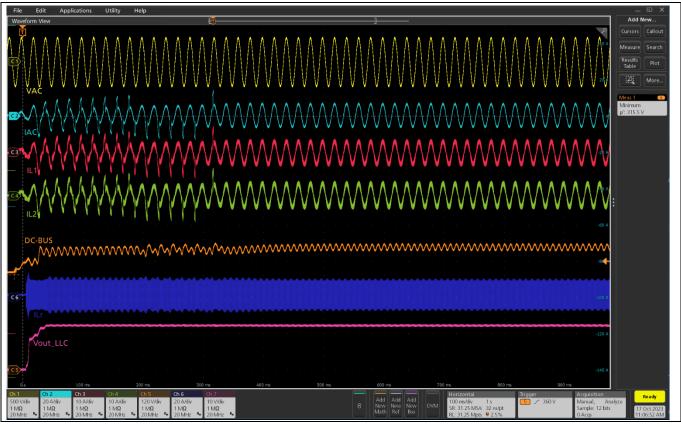

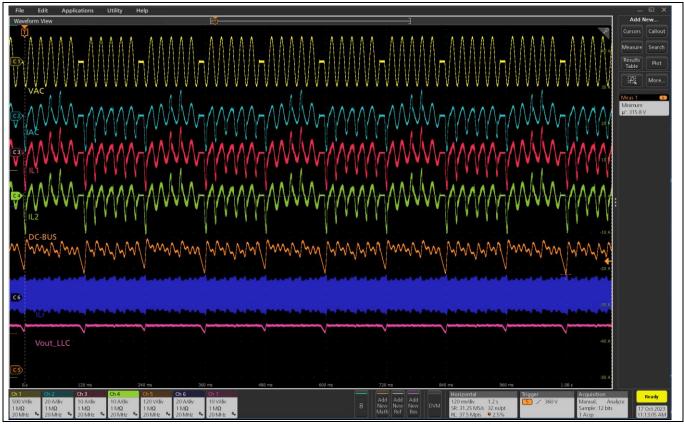

Figure 15 shows the main steady-state waveforms of the PFC for a 115 V AC at 50 Hz and Figure 16 for a 230 V AC at 50 Hz under nominal load conditions. These figures show the interleaved totem-pole PFC in a steady-state condition. The top of both figures shows the AC input voltage (Ch1), while the second channel (Ch2) represents the input current. Ch3 and Ch4 exhibit the inductor current in the first and second PFC chokes, respectively, followed by the bulk voltage (Ch5) at the end.

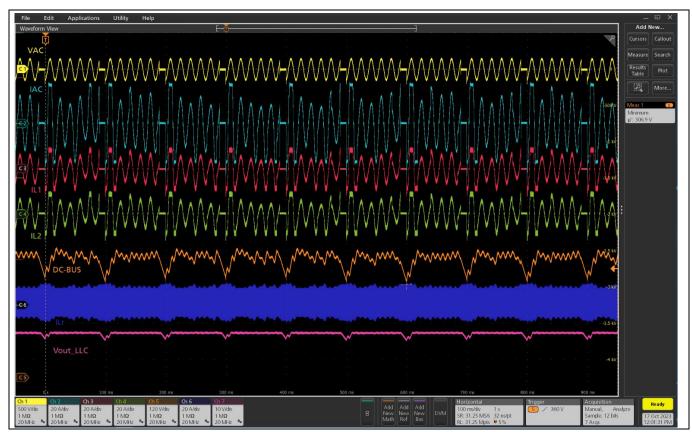

Figure 17 shows the benefit of the interleaving PFC of the AC input current of the converter.

**System description**

Figure 15 PFC steady-state waveforms at 115 V AC and at full load condition

Figure 16 PFC steady-state waveforms at 230 V AC and at full load condition

System description

Figure 17 Interleaving effect in the input current of the PFC

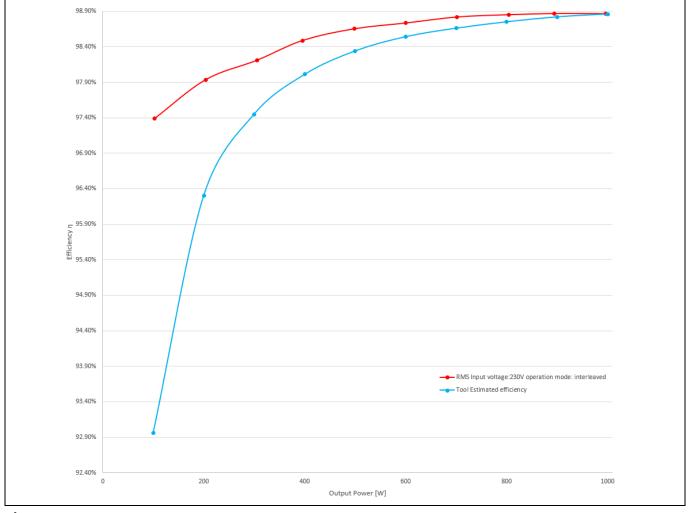

#### 2.3.2 Interleaved PFC efficiency

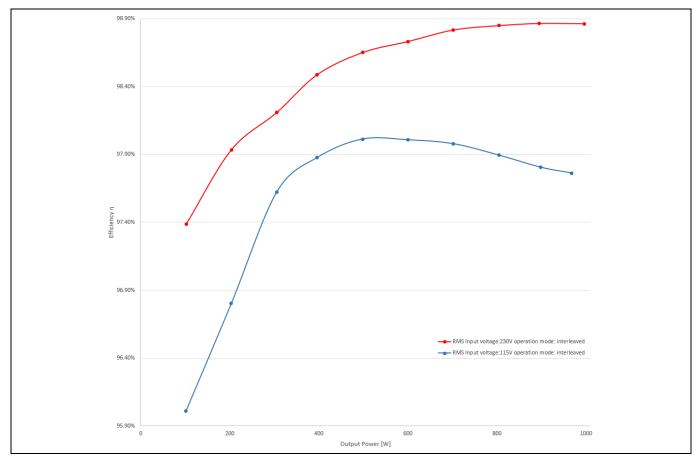

The efficiency of the single PFC stage is determined at ambient temperature, following 30 minutes of operation at full-load condition to attain a stable temperature of the PSU. Figure 18 shows the efficiency outcomes obtained at both low- and high-line conditions. In particular, the PFC is running in interleaving mode in both cases.

As shown in Figure 18, the efficiency peak is 98.86% at nearly 1000 W of output power. At 115 V AC, the efficiency level reaches a peak value of 98.01% at approximately 500 W.

Figure 18 Measured PFC efficiency in interleaving mode at 230 V and 115 V RMS AC

### 2.4 Half-bridge LLC

The efficiency of the LLC converter with 400 V input and 12 V output considering a variable switching frequency ranging from 90 kHz to 135 kHz. The resonant tank values are 132 nF for the resonant capacitor and a 15  $\mu$ H for the resonant inductor for an equivalent resonance frequency of 113 kHz.

Figure 19 Simplified schematic of the LLC HB DC-DC converter

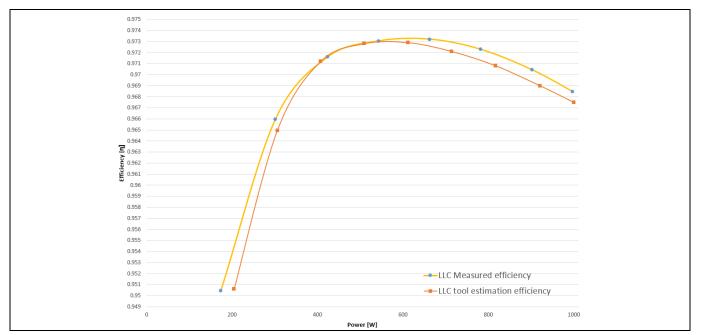

Figure 20 shows a comparison between the estimated efficiency of the LLC (orange plot) and the actual measured efficiency (yellow plot). The data indicates a close alignment at mid-load, with some variances observed at light and full-load conditions. Despite these discrepancies, the tool provides valuable insights into the behavior of the LLC converter across the entire load range, offering a comprehensive understanding from light to full load conditions.

It is worth mentioning the high peak efficiency, nearly 97.3 percent at 50 percent of the rated load condition. Note that the overall efficiency of the complete PSU is the result of multiplying the separate efficiencies of the conforming blocks and is necessarily lower than any of them separately. However, some of the loss contributions are shared between the two blocks (e.g., auxiliary bias) and therefore, the resulting overall efficiency is still expected to fall within the target specifications.

#### **System description**

Figure 20 Estimated efficiency of the LLC DC-DC converter at 400 V DC input and 12 V DC output

Figure 21 shows the distribution of losses across various devices at different operating points for the LLC. It is evident that the majority of losses are primarily concentrated on the LLC transformer, aligning with expectations.

Figure 21 Estimated distribution losses of the LLC at different loads

## 2.4.1 LLC magnetics

The resonant tank of the LLC series-parallel resonant converter comprises two equivalent inductors and one equivalent capacitor.

One of the advantages of this topology is that it is possible to realize the series resonant inductor  $(L_r)$  by the leakage of the main transformer, and the parallel resonant inductor  $(L_m)$  by the magnetizing inductance of the main transformer.

Nevertheless, the full integration approach constrains the design and compromises the performance of the converter. Therefore, in the LLC the series inductor  $(L_r)$  has been realized as discrete components, although  $L_r$  is integrated within the same magnetic structure of the main transformer.

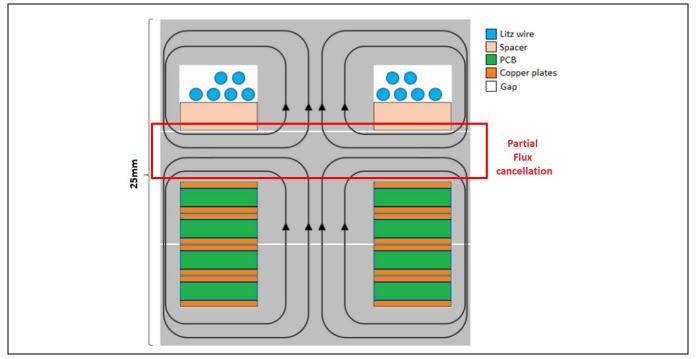

Figure 22 shows a simplified view of the construction of the resonant inductor (Lr) and the main transformer. The resonant inductor is built with a 3C95 PQ38/8/25 core from Ferroxcube, while the main transformer is built with two pieces of the same core and material. The Lr is stacked on the top of the main transformer and wound in the same direction as the primary-side winding. As a result of this, the flux in part of the volume is effectively canceled and the total core loss is partly reduced.

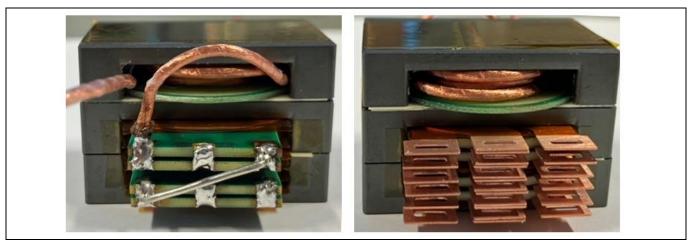

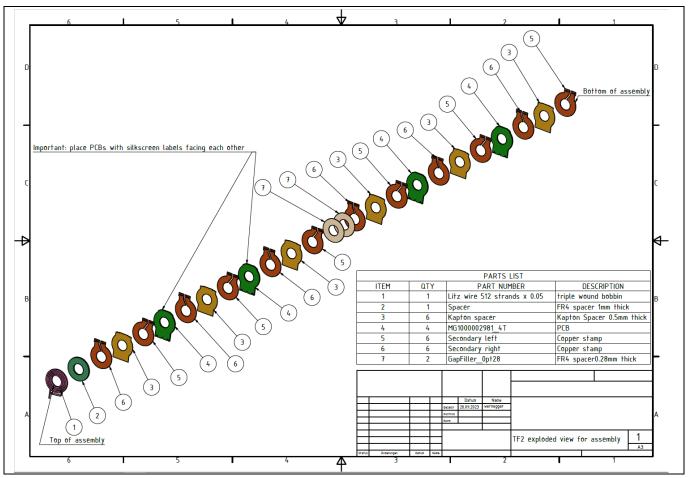

The main transformer is characterized by a 16:1 turn ratio, with the primary windings spread across four PCBs aimed at minimizing the equivalent series resistance (ESR) and optimizing efficiency. On the secondary side, 12 interleaved copper plates, arranged in a center-tapped mode as shown in Figure 22, serve two specific purposes: to accommodate high circulating currents and minimize losses while enhancing thermal dissipation. Additionally, the winding of Lr is constructed using Litz wire, comprising 512 strands of 0.05 mm diameter.

Figure 22 Simplified structure of the LLC transformer

Because of the height limitation of the PSU (27 mm), cur the main board to accommodate the height of the integrated  $L_r$  plus the main transformer structure (approximately 25 mm). The cut out helps at the same time with the thermal management due to a direct thermal connection of the magnetic core with the aluminum baseplate, by using a thermal interface.

#### **System description**

Figure 24 displays the mechanical internal construction of the LLC main transformer. The detailed figure helps to visualize the internal composition of the transformer and enhances the comprehension of its structure.

Figure 23 Detailed view of the fully assembled LLC transformer

Figure 24 Mechanical drawing of LLC main transformer winding arrangement

#### 2.5 Driving CoolMOS<sup>™</sup> in the LLC converter

The LLC converter primary side employs two CoolMOS<sup>™</sup> 55 mΩ devices in TOLL package (CoolMOS<sup>™</sup> IPT60R055CFD7).

XMC4400 MCU ground pertains to the LLC converter's secondary side so for controlling the LLC half-bridge and ensuring isolation between the primary and secondary sides, a EiceDRIVER<sup>™</sup> 2EDB8265H driver has been used as shown in Figure 25.

Figure 25 Driving LLC half-bridge CoolMoS<sup>™</sup> (using EiceDRIVER<sup>™</sup> 2EDS8265H)

## 2.6 Primary side: LLC steady-state operation

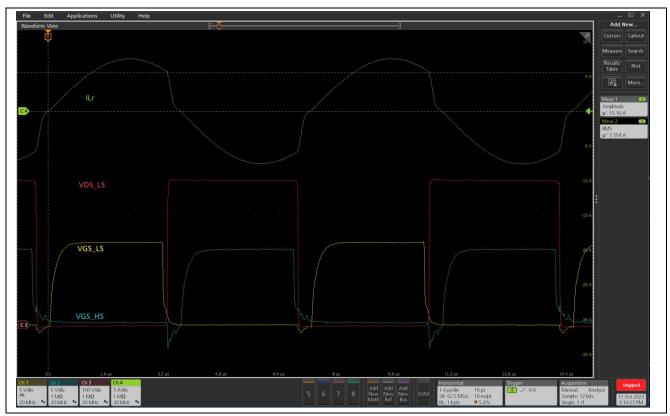

The LLC steady-state waveforms are shown in Figure 26 and Figure 27 for both 100% and 50% load conditions.

These figures showcase the resonant current waveform (Ch4), half-bridge low-side MOSFET drain-to-source voltages (Ch3), and half-bridge MOSFETs gate-to-source voltages (Ch1 and Ch2) at nominal input/output voltages. These waveforms provide a visual representation of the behavior of the LLC in steady-state operation under different load conditions.

System description

Figure 26Primary side steady-state operation at 50% of the load

Figure 27 Primary side steady-state operation at 100% of the load

#### 2.7 Secondary side: LLC steady-state operation

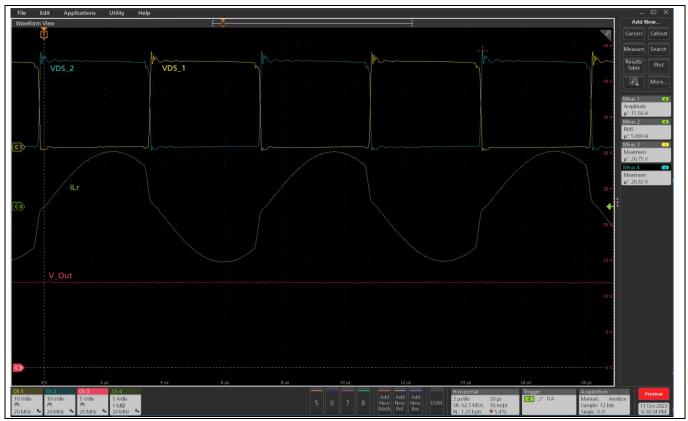

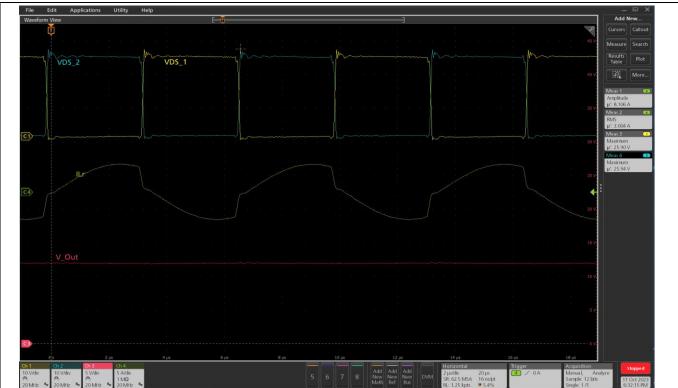

Figure 27 and Figure 28 provide a comprehensive view of the LLC converter's steady-state performance at 100% and 50% load from a secondary side perspective.

The middle of the picture displays the resonant current waveform (Ch4), while the output voltage waveform of the converter is shown at the bottom of the figure (Ch3).

Across the figures, it is evident that the maximum peak for the drain-source voltage of the synchronous secondary MOSFETs is consistently below 27 V.

Figure 28 LLC in steady-state condition when running at full load condition

System description

Figure 29 LLC in steady-state condition when running at 50 percent load

### 2.7.1 LLC efficiency

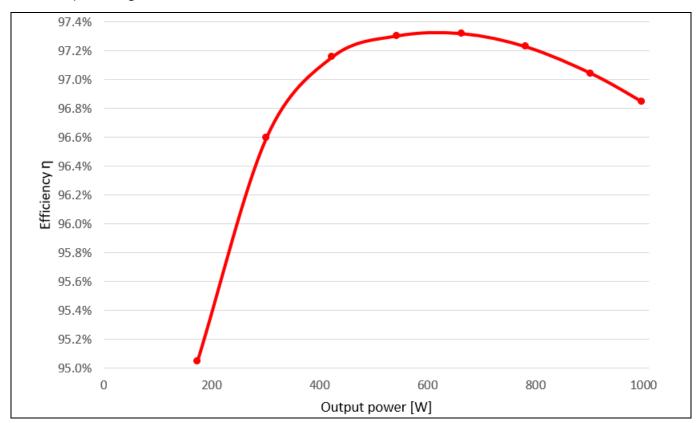

The efficiency of the only LLC stage has been measured at ambient temperature after running the converter for 60 minutes at full load condition to reach steady-state temperature of the integrated transformer. In Figure 30, the efficiency results are displayed.

The LLC efficiency reaches an outstanding peak of almost 97.35 percent near 600 W of output power in the case of 400 V input voltage.

Figure 30 Measured LLC efficiency at 400 V input and 12 V output

Full power supply unit

## 3 Full power supply unit

This section provides a summary of experimental results of the complete power supply.

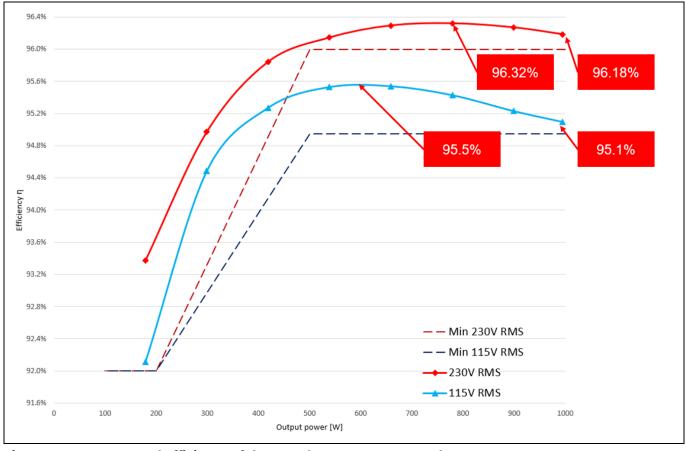

#### 3.1.1 Efficiency

The efficiency of the complete power supply is measured following a 60-minute run of the converter at full load condition.

In Figure 31, the efficiency results for 115 V and 230 V AC RMS input and 12 V DC output are presented together with the efficiency target.

Under high-line input voltage, the REF\_1KW\_PSU\_5G\_GaN board demonstrates a peak efficiency of nearly 96.32% at approximately 800 W at 230 V AC and a peak efficiency of 95.5% at 115 V AC at 600 W. The PSU fully complies with the initial specification, maintaining an efficiency above 96% from around 50% of the load to full load condition.

Similarly, when supplied with 115 V AC the PSU operates at an efficiency level above 95% from approximately 35% of the load up to full load at 115 V AC.

Figure 31 Measured efficiency of the complete PSU at 115 V and 230 V AC RMS

Full power supply unit

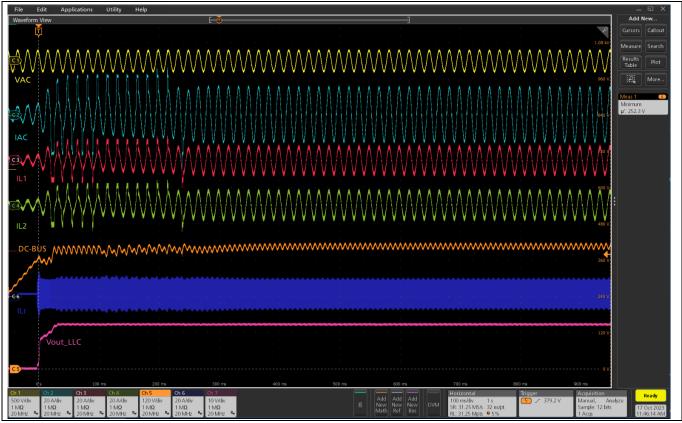

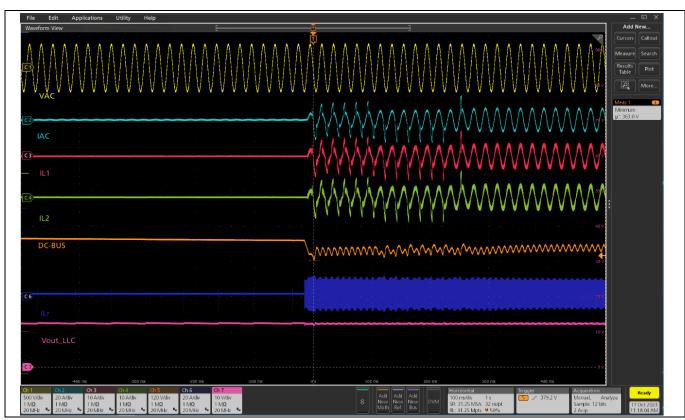

#### 3.1.2 Start up

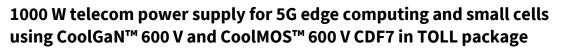

Figure 32 and Figure 33 show the PSU startup sequence at 100 V AC and 230 V AC respectively. These figures demonstrate the startup condition of the full power supply at full load conditions. The top portion of both figures displays the different parameters being measured, which includes PFC input voltage (Ch1), PFC input current (Ch2), current in the first PFC choke (Ch3), current in the second PFC choke (Ch4), LLC resonant current (Ch5), and the LLC output voltage (Ch6). At an input voltage of 100 V AC, the input current peaks at 20 A and the sharing of this current in both PFC chokes is evident in Ch3 and Ch4 channels. The last two channels, Ch5 and Ch6, show the LLC resonant current and output voltage, respectively.

Figure 32 Startup sequence of the full PSU at full load at 100 V AC

Full power supply unit

Figure 33 Startup sequence of the full PSU at full load at 230 V AC

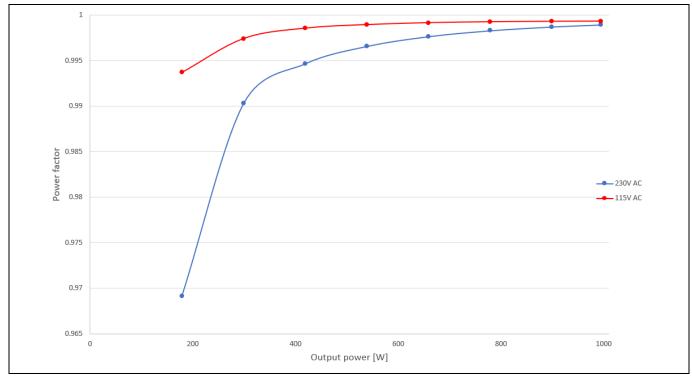

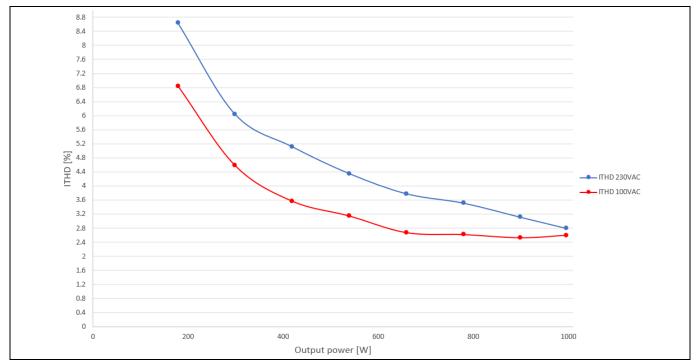

The power factor (PF) and the THD have been measured at both low- and high-line VAC, as shown in Figure 34 and Figure 35. The PF is higher than 95% from 18% of the load at 230 VAC and always above 99% at 115 VAC.

Figure 34 Measured PF of the complete power supply

#### Full power supply unit

Figure 35Measured current THD of the complete power supply

## 3.1.3 Hold-up time

The PFC response and output voltage of the PSU during a 10 ms hold-up time at 100 percent load and an input voltage of 230 V AC is captured in Figure 36, with the event repeated for ten times every 100 ms. The bulk voltage drops to a minimum of approximately 328 V DC, while the output voltage complies with the specification, exhibiting a peak-to-peak variation of 1.2 V DC.

Furthermore, Figure 37 shows the same event as Figure 36, but with a line cycle drop-out applied at 45 degrees of the input voltage.

Moreover, Figure 38 and Figure 39 exhibit the same events as depicted in Figure 36 through Figure 37<u>Figure38</u>, but with an input voltage of 115 V AC.

Full power supply unit

Figure 36 10 ms 230 V AC 50Hz line cycle drop out at 0° and 100% load

Figure 37 10 ms 230 V AC 50Hz line cycle drop out at 45° and 100% load

Full power supply unit

Figure 38 10 ms, 115 V AC 50Hz line cycle drop out at 0° and 100% load

Figure 39 10 ms, 115 V AC 50Hz line cycle drop out at 45° and 100% load

### 3.1.4 Load-jump

These graphs show the output of the PSU, which is subjected to a load increase from 0 A to 83 A (Figure 40) and then to a load decrease from 83 A back to 0 A (Figure 41). These load jump tests demonstrate the PSU ability to handle sudden changes in current load and maintain a well-regulated output. The PSU is reliable even under challenging conditions.

Figure 40 Load-jump of the complete PSU from 0% to 100% of load

Figure 41 Load-jump of the complete PSU from 100% to 0% of load

### 3.1.5 Thermal characterization

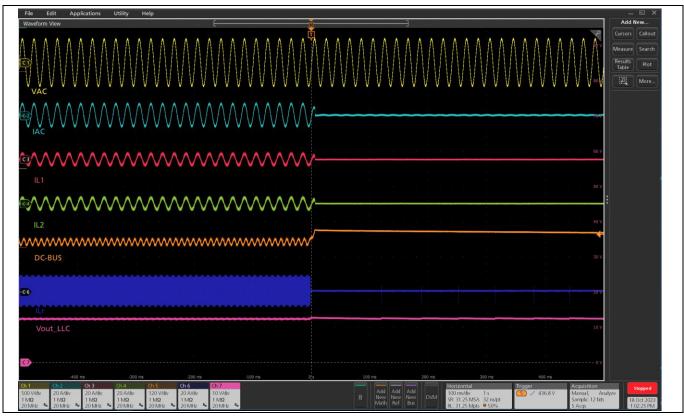

The PSU has been thermally characterized by operating it at 100% load for 30 minutes and at 230 V AC and 115 V AC. The thermal behavior of the PSU is analyzed and is shown in Figure 42, providing a detailed overview of the PSU's behavior after a warm-up period of 30 minutes at 100% load at 230 V AC.

Figure 42 Total PSU thermal characterization at 230 V AC at 100% of the load

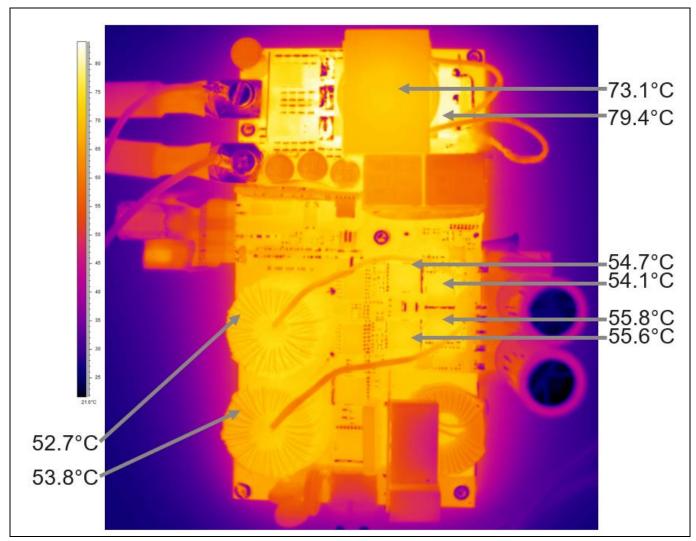

The thermal behavior of the PSU after a warm-up period of 30 minutes at 100% load and with an input voltage of 115 V is analyzed and is shown in Figure 43.

Full power supply unit

Figure 43 Total PSU thermal characterization at 115 V AC at 100% of the load

76.1°C 78.0°C 69.7°C 64.5°C

Figure 44 shows a detailed overview of the temperature for the LLC transformer stack.

#### 3.1.6 EMI

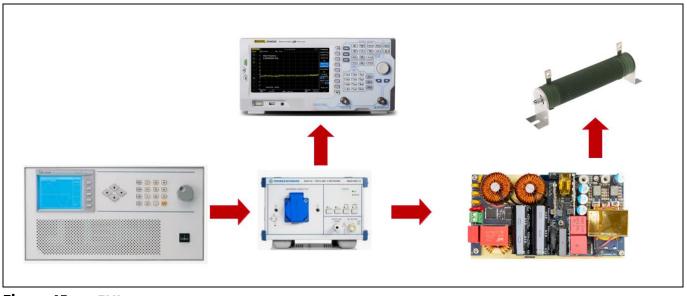

The electromagnetic interference (EMI) generated by the converter has been measured. Note that the setup used for the measurements is not a certified setup, but it still provides a valuable insight into the behavior of the board. The laboratory set up includes an AC system, specifically a Chroma model 6560 as the power source, a Rohde & Schwarz line impedance stabilization network (LISN) model ENV216, and a RIGOL spectrum analyzer model DSA832E. In this configuration, the AC source, in conjunction with the LISN, powers the board, while the output of the 1 kW reference board is connected to a resistive load. The selection of a resistive load is deliberate to minimize potential interactions between the board and the control of an active load. The output of the LISN is linked to the RIGOL spectrum analyzer for comprehensive analysis of the interference.

Figure 45 EMI setup

#### Full power supply unit

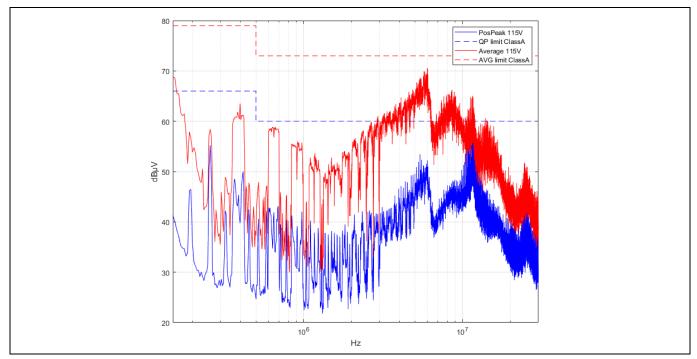

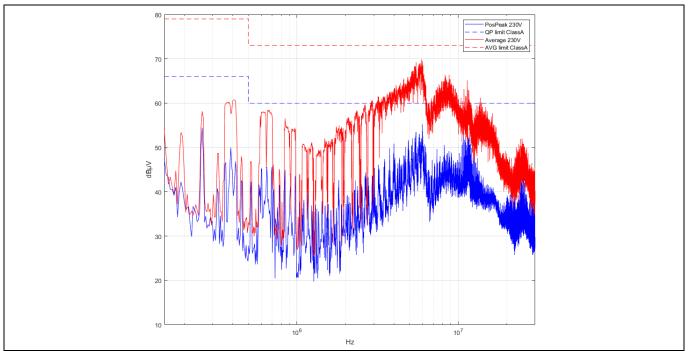

Figure 46 and Figure 47 show the results of the average and the positive peak measurements at 115 V AC and 230 V AC, respectively.

As seen, the PSU is fully compliant with Class A limits in both peak and average. Furthermore, positive peak measurements represent a worst case compared to the quasi-peak of the standard. A margin of 6 dB is always achieved.

Figure 46 Measured EMI spectrum of the complete power supply prototype at 115 V AC

Figure 47 Measured EMI spectrum of the complete power supply prototype at 230 V AC

Summary

## 4 Summary

This document provides the fanless system solution from Infineon designed for 5G edge computing and small cells. The solution incorporates a bridgeless interleaved totem-pole PFC converter and a DC-DC isolated half-bridge (HB) LLC converter, achieving efficiency levels of 96.35% at 230 V AC and 95.5% at 115 V AC, along with a power density of 50 W/in<sup>3</sup>.

REF\_1KW\_PSU\_5G\_GaN reference board utilizes CoolGaN<sup>™</sup> 600 V power transistor, CoolMOS<sup>™</sup> 600 V MOSFET in TOLL package, and the OptiMOS<sup>™</sup> 6 in WSON package. This combination of CoolGaN<sup>™</sup>, CoolMOS<sup>™</sup>, and OptiMOS<sup>™</sup> enables high performance within a compact form factor, as detailed in this application note.

The bridgeless PFC topology and the half-bridge LLC incorporate full digital control through an XMC<sup>™</sup> 4000 MCU series from Infineon.

Note that the PSU's performance excels not only in steady-state conditions, offering high efficiency, but also meets power line disturbance and hold-up time requirements.

Furthermore, the REF\_1KW\_PSU\_5G\_GaN board has been tested using a programmable AC source and electronic load. Efficiency, THD, and PF results are obtained using the WT3000 power analyzer from Yokogawa, alongside waveform analysis with the MSO58 (1 GHz; 6.25 GS/s) oscilloscope from Tektronix.

Schematics

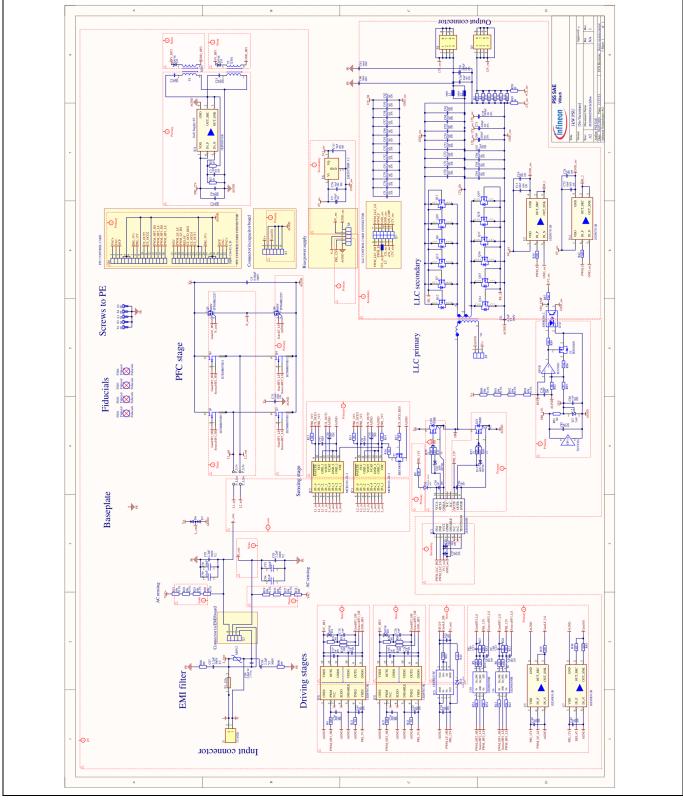

# 5 Schematics

Figure 48 Main board

Schematics

#### 5.2 Control cards

#### 5.2.1 PFC controller card

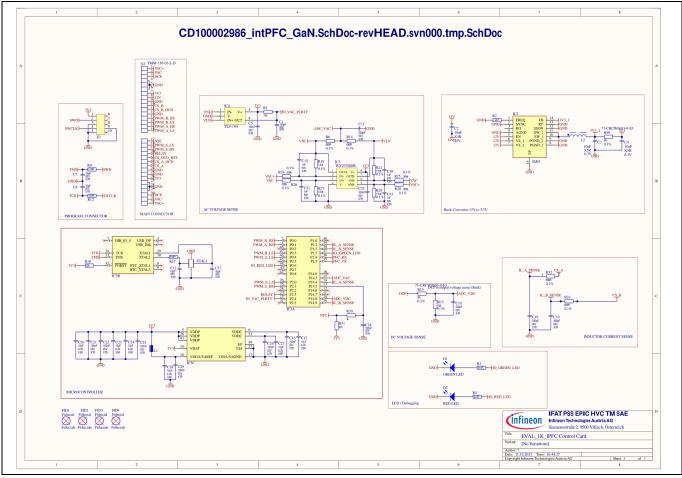

Figure 49 PFC controller card

#### Schematics

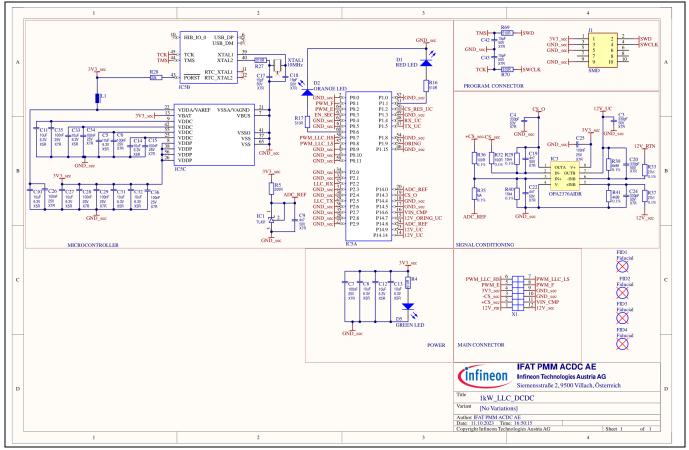

## 5.2.2 LLC controller card

Figure 50 LLC controller card

#### Schematics

#### 5.2.3 Bias board

Figure 51 Bias board

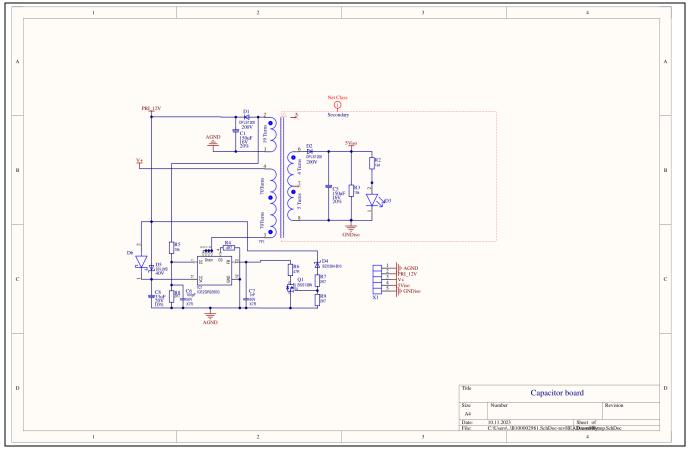

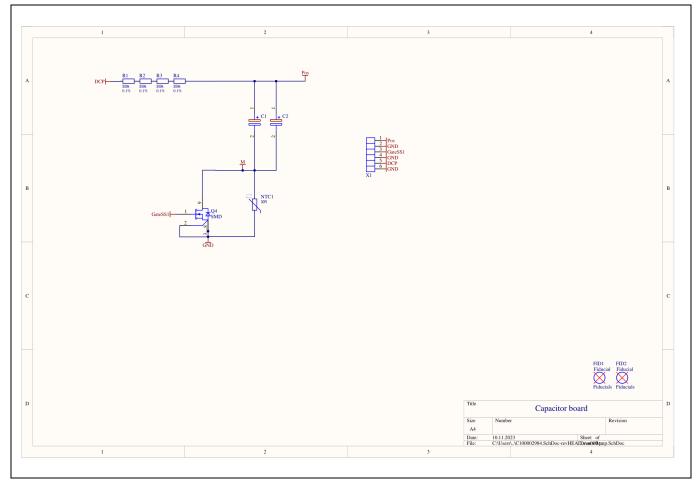

Schematics

Figure 52 Capacitor card

#### Schematics

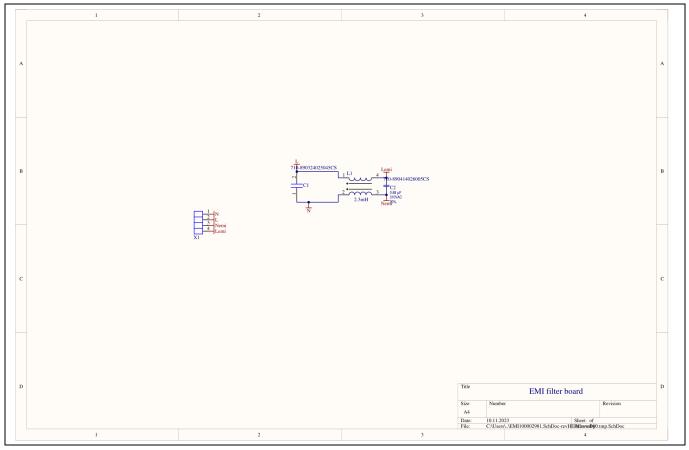

#### 5.2.5 EMI filter card

Figure 53 EMI filter card

Schematics

# 5.2.6 Assembling view

| status   status     status   status <td< th=""><th>i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i</th><th>PARTS LIST</th><th></th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i   i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PARTS LIST                                                       |                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------|

| apply thereal pathy interface nation on elevated area.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Apply thereface exterial on glocated area.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ITEM QTY PART NUMBER                                             | DESCRIPTION                                                                        |

| 3   1   100002183 scyle gales come   Active gales come     3   1   100002183 scyle   100002183 scyle   100002183 scyle     3   1   100002183 scyle   100002183 scyle   100002183 scyle   100002183 scyle     3   1   1   1   100002183 scyle   100002183 scyle   100002183 scyle     3   1   1   1   1   100002183 scyle   100002183 scyle     3   1   1   1   1   100002183 scyle   100002183 scyle     1   1   1   1   100002183 scyle   100002183 scyle   100002183 scyle     1   1   1   1   100002183 scyle   100002183 scyle <t< th=""><th>a)   a)   b)   <td< th=""><th>1 1 MP100002987 SiC</th><th>Aluminium chassis</th></td<></th></t<>                                            | a)   a)   b)   b) <td< th=""><th>1 1 MP100002987 SiC</th><th>Aluminium chassis</th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 1 MP100002987 SiC                                              | Aluminium chassis                                                                  |

| Apply thereal pathyl interface natural on elevated area:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Apply Iterface starial on glorade area.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2 1 IS100002986                                                  | Isolation toil                                                                     |

| s   1   Hard and carrow hard   The it is not conductive gluo     y   1   1   1   1   1     y   n   1   1   1   1   1     y   n   1   1   1   1   1   1   1     y   n   n   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1   1 <th>1   2   Plas B mal scree   Plas B mal scree   Plas B mal scree   Image: Sc</th> <th>4 1 M100002985 SiC</th> <th>Mainboard assembly</th> | 1   2   Plas B mal scree   Plas B mal scree   Plas B mal scree   Image: Sc | 4 1 M100002985 SiC                                               | Mainboard assembly                                                                 |

| a   b   bbs #ma cylcideriadd urw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | b   b   Pist and contractule lead     b   b   Pist and contractule lead     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c   c   c     c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                  | Must be made of non-conductive plastic                                             |

| 2 4 JP3 x Bm gliderhed stree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Y   4.   191 x film cylinderland screw     Image: Constraint of the cylinderland screw   Image: Constraint of the cylinderland screw     Image: Constraint of the cylinderland screw   Image: Constraint of the cylinderland screw     Image: Constraint of the cylinderland screw   Image: Constraint of the cylinderland screw     Image: Constraint of the cylinderland screw   Image: Constraint of the cylinderland screw     Image: Constraint of the cylinderland screw   Image: Constraint of the cylinderland screw     Image: Constraint of the cylinderland screw   Image: Constraint of the cylinderland screw     Image: Constraint of the cylinderland screw   Image: Constraint of the cylinderland screw     Image: Constraint of the cylinderland screw   Image: Constraint of the cylinderland screw     Image: Constraint of the cylinderland screw   Image: Constraint of the cylinderland screw                                                                                                                                                                                                    | 6 6 M3x6 flat countersunk head                                   | only one side pictured (3) (6)                                                     |

| Apy hend ptf/ inteface asteried on skoted area:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Apy thema paty/ interface sates on one sealed areas.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7 4 M3 x 8mm cylinderhead screw                                  |                                                                                    |