# S-8244 Series

# BATTERY PROTECTION IC FOR 1-SERIAL TO 4-SERIAL-CELL PACK (SECONDARY PROTECTION)

www.sii-ic.com

Rev.6.3\_00

© Seiko Instruments Inc., 2003-2014

The S-8244 Series is used for secondary protection of lithium-ion batteries with from one to four cells, and incorporates a high-precision voltage detector circuit and a delay circuit. Short-circuiting between cells makes it possible for serial connection of one to four cells.

### Features

(1) Internal high-precision voltage detector circuit

| Overcharge detection voltage range :               | 3.700 V to 4.550 V : Accuracy of $\pm$ 25 mV (at +25°C)                          |

|----------------------------------------------------|----------------------------------------------------------------------------------|

|                                                    | (at a 5 mV/step) Accuracy of $\pm$ 50 mV (at –40°C to +85°C)                     |

| Hysteresis :                                       | 5 types                                                                          |

|                                                    | $0.38 \pm 0.1$ V, $0.25 \pm 0.07$ V, $0.13 \pm 0.04$ V, $0.045 \pm 0.02$ V, None |

| (2) High withstand voltage device :                | Absolute maximum rating : 26 V                                                   |

| (3) Wide operating voltage range :                 | 3.6 V to 24 V (refers to the range in which the delay circuit can operate        |

|                                                    | normally after overvoltage is detected)                                          |

| (4) Delay time during detection :                  | Can be set by an external capacitor.                                             |

| (5) Low current consumption :                      | At 3.5 V for each cell : 3.0 μA max. (+25°C)                                     |

|                                                    | At 2.3 V for each cell : 2.4 µA max. (+25°C)                                     |

| (6) Output logic and form :                        | 5 types                                                                          |

|                                                    | CMOS output active "H"                                                           |

|                                                    | CMOS output active "L"                                                           |

|                                                    | Pch open drain output active "L"                                                 |

|                                                    | Nch open drain output active "H"                                                 |

|                                                    | Nch open drain output active "L"                                                 |

|                                                    | (CMOS / Nch open drain output for 0.045 V hysteresis models)                     |

| (7) Lead-free, Sn 100%, halogen-free <sup>*1</sup> | · · · · · · · ·                                                                  |

(7) Lead-free, Sn 100%, halogen-free '

\*1. Refer to "

Product Name Structure" for details.

# Applications

• Lithium ion rechargeable battery packs (secondary protection)

### Packages

- SNT-8A

- 8-Pin MSOP

- TMSOP-8

# BATTERY PROTECTION IC FOR 1-SERIAL TO 4-SERIAL-CELL PACK (SECONDARY PROTECTION) S-8244 Series Rev.6.3\_00

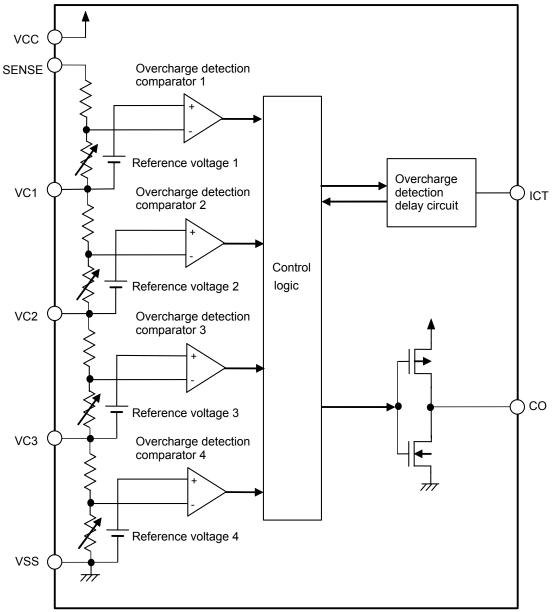

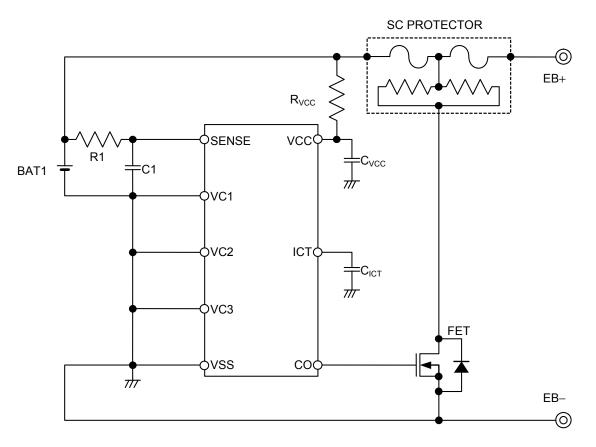

## Block Diagram

#### Figure 1

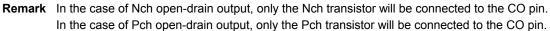

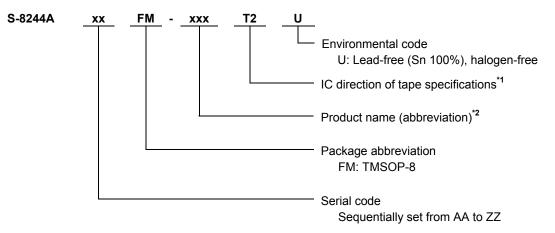

## Product Name Structure

- 1. Product Name

- (1) SNT-8A

- **\*1.** Refer to the tape specifications at the end of this book.

- \*2. Refer to the "3. Product Name List".

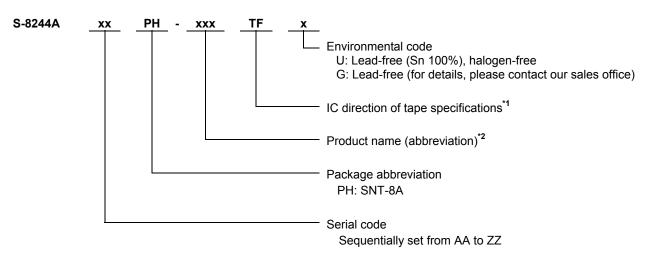

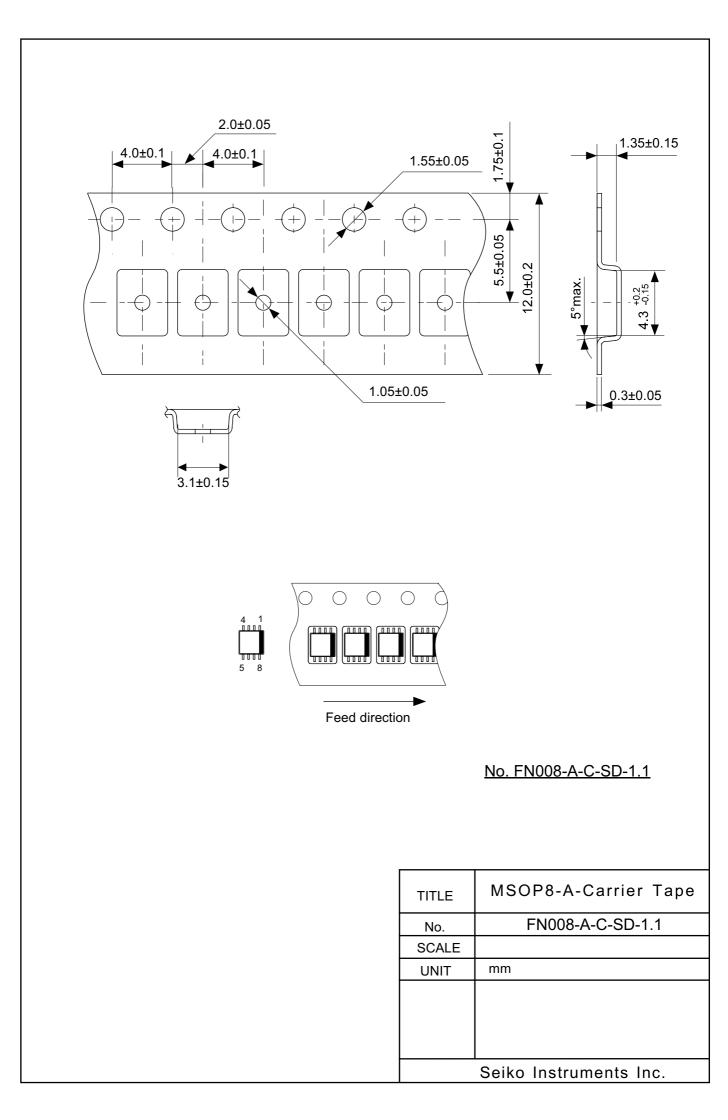

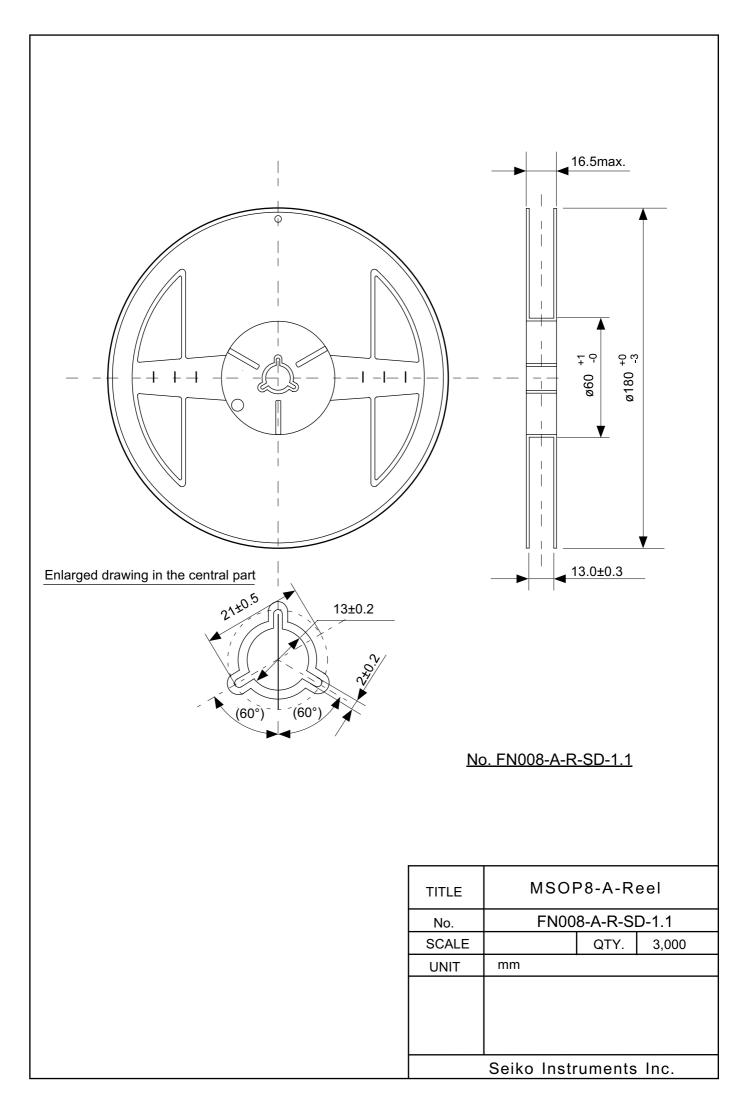

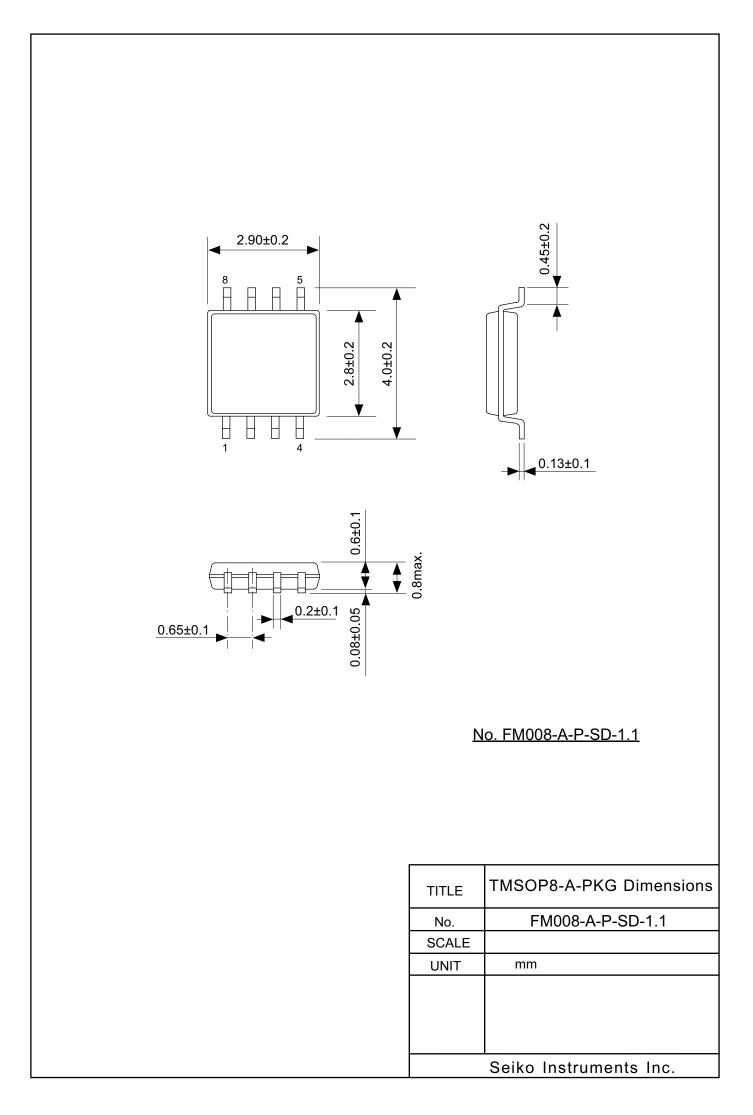

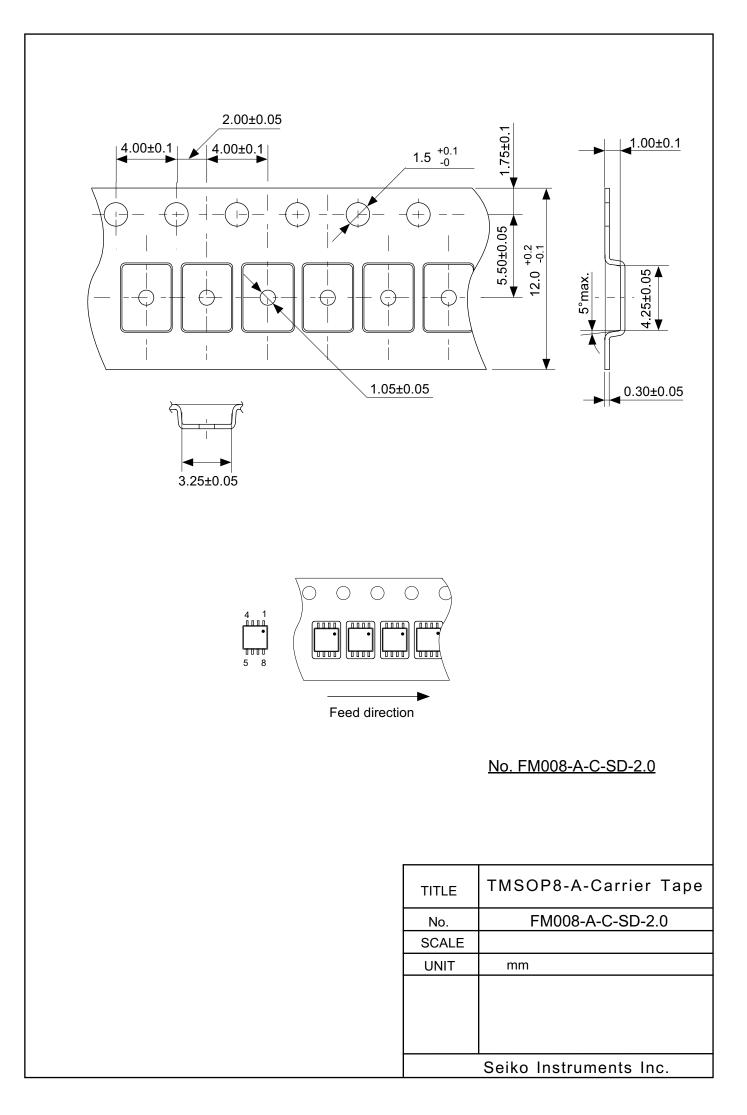

- (2) 8-Pin MSOP

- **\*1.** Refer to the tape specifications at the end of this book.

- \*2. Refer to the "3. Product Name List".

# BATTERY PROTECTION IC FOR 1-SERIAL TO 4-SERIAL-CELL PACK (SECONDARY PROTECTION) S-8244 Series Rev.6.3\_00

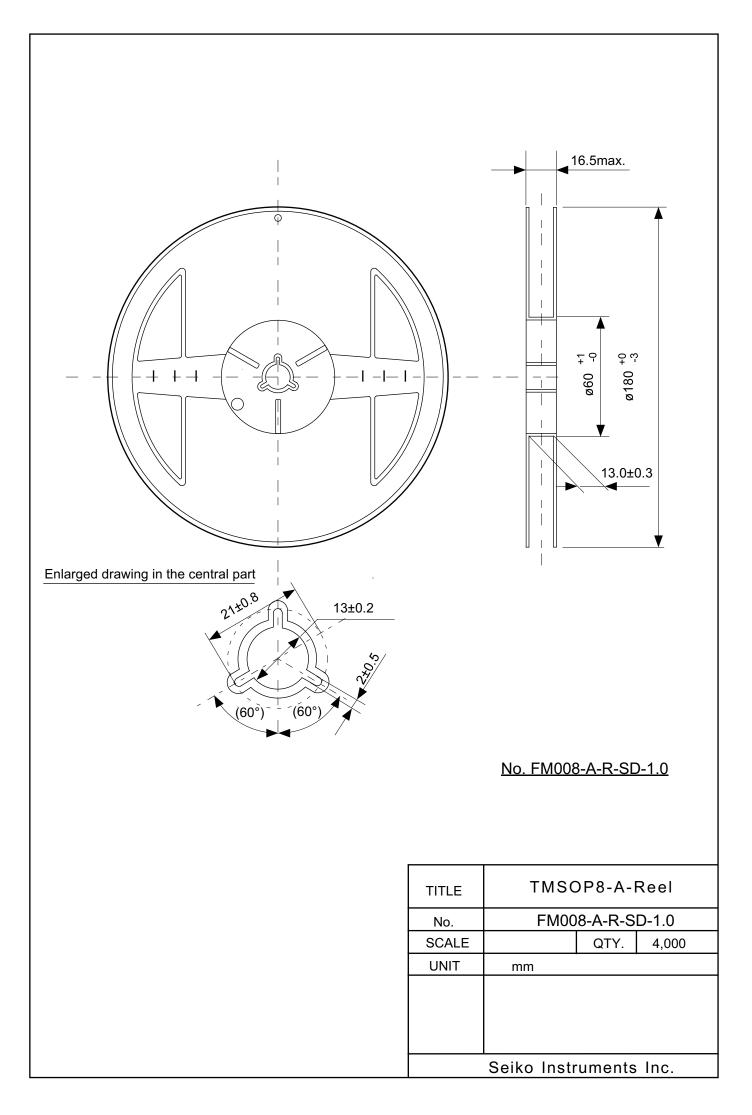

(3) TMSOP-8

- **\*1.** Refer to the tape specifications at the end of this book.

- \*2. Refer to the "3. Product Name List".

#### 2. Packages

| Deckers name | Drawing code |   |              |   |              |   |              |  |

|--------------|--------------|---|--------------|---|--------------|---|--------------|--|

| Package name | Package      | 1 | Tape         |   | Reel         |   | Land         |  |

| SNT-8A       | PH008-A-P-SD |   | PH008-A-C-SD |   | PH008-A-R-SD | į | PH008-A-L-SD |  |

| 8-Pin MSOP   | FN008-A-P-SD | 1 | FN008-A-C-SD | 1 | FN008-A-R-SD | 1 | _            |  |

| TMSOP-8      | FM008-A-P-SD | - | FM008-A-C-SD |   | FM008-A-R-SD |   | _            |  |

#### 3. Product Name List

#### (1) SNT-8A

| Table 1            |                                         |                                          |                           |  |  |  |  |

|--------------------|-----------------------------------------|------------------------------------------|---------------------------|--|--|--|--|

| Product name       | Overcharge detection voltage $[V_{CU}]$ | Overcharge hysteresis voltage $[V_{CD}]$ | Output form               |  |  |  |  |

| S-8244AAAPH-CEATFx | $4.450 \pm 0.025 \text{ V}$             | $0.38\pm0.1~\text{V}$                    | CMOS output active "H"    |  |  |  |  |

| S-8244AABPH-CEBTFx | $4.200 \pm 0.025 \text{ V}$             | 0 V                                      | Nch open drain active "H" |  |  |  |  |

| S-8244AADPH-CEDTFx | $4.200 \pm 0.025 \text{ V}$             | 0 V                                      | Pch open drain active "L" |  |  |  |  |

| S-8244AAFPH-CEFTFx | $4.350 \pm 0.025 \text{ V}$             | $0.045 \pm 0.02 \ V$                     | CMOS output active "H"    |  |  |  |  |

| S-8244AAGPH-CEGTFx | $4.450 \pm 0.025 \text{ V}$             | $0.045\pm0.02~\text{V}$                  | CMOS output active "H"    |  |  |  |  |

| S-8244AAJPH-CEJTFx | $4.500 \pm 0.025 \text{ V}$             | $0.38\pm0.1$ V                           | CMOS output active "H"    |  |  |  |  |

| S-8244AASPH-CESTFx | $4.350 \pm 0.025 \text{ V}$             | $0.38\pm0.1$ V                           | CMOS output active "H"    |  |  |  |  |

| S-8244AATPH-CETTFU | $4.200 \pm 0.025 \ V$                   | $0.25 \pm 0.07 \; V$                     | CMOS output active "H"    |  |  |  |  |

| S-8244AAVPH-CEVTFx | $4.275 \pm 0.025 \text{ V}$             | $0.045 \pm 0.02 \text{ V}$               | CMOS output active "H"    |  |  |  |  |

| S-8244AAYPH-CEYTFx | $4.300 \pm 0.025 \text{ V}$             | $0.25\pm0.07~V$                          | CMOS output active "H"    |  |  |  |  |

| S-8244AAZPH-CEZTFx | $4.280 \pm 0.025 \text{ V}$             | $0.25\pm0.07~\text{V}$                   | CMOS output active "H"    |  |  |  |  |

| S-8244ABBPH-CFBTFx | $4.380 \pm 0.025 \text{ V}$             | $0.25\pm0.07~\text{V}$                   | CMOS output active "H"    |  |  |  |  |

| S-8244ABDPH-CFDTFx | $4.150 \pm 0.025 \text{ V}$             | $0.045 \pm 0.02 \text{ V}$               | CMOS output active "L"    |  |  |  |  |

| S-8244ABEPH-CFETFx | $4.215 \pm 0.025 \text{ V}$             | 0 V                                      | Nch open drain active "L" |  |  |  |  |

| S-8244ABHPH-CFHTFx | $4.280 \pm 0.025 \text{ V}$             | $0.045 \pm 0.02 \text{ V}$               | CMOS output active "H"    |  |  |  |  |

| S-8244ABMPH-CFMTFU | $4.100 \pm 0.025 \text{ V}$             | $0.25\pm0.07~V$                          | CMOS output active "H"    |  |  |  |  |

| S-8244ABOPH-CFOTFU | $4.550 \pm 0.025 \ V$                   | $0.38\pm0.1~\text{V}$                    | CMOS output active "H"    |  |  |  |  |

**Remark 1.** Please contact our sales office for the products with the detection voltage value other than those specified above. **2.** x: G or U

3. Please select products of environmental code = U for Sn 100%, halogen-free products.

# BATTERY PROTECTION IC FOR 1-SERIAL TO 4-SERIAL-CELL PACK (SECONDARY PROTECTION) Rev.6.3\_00 S-8244 Series

#### (2) 8-Pin MSOP

|                    | Т                                                     | able 2                                              |                           |

|--------------------|-------------------------------------------------------|-----------------------------------------------------|---------------------------|

| Product name       | Overcharge detection<br>voltage<br>[V <sub>CU</sub> ] | Overcharge hysteresis voltage<br>[V <sub>CD</sub> ] | Output form               |

| S-8244AAAFN-CEAT2z | $4.450 \pm 0.025 \; \text{V}$                         | $0.38\pm0.1~\text{V}$                               | CMOS output active "H"    |

| S-8244AABFN-CEBT2z | $4.200 \pm 0.025 \; \text{V}$                         | 0 V                                                 | Nch open drain active "H" |

| S-8244AACFN-CECT2z | $4.115 \pm 0.025 \; V$                                | $0.13\pm0.04\;V$                                    | CMOS output active "H"    |

| S-8244AADFN-CEDT2z | $4.200 \pm 0.025 \; \text{V}$                         | 0 V                                                 | Pch open drain active "L" |

| S-8244AAEFN-CEET2z | $4.225\pm0.025~\textrm{V}$                            | 0 V                                                 | Nch open drain active "H" |

| S-8244AAFFN-CEFT2z | $4.350 \pm 0.025 \; \text{V}$                         | $0.045\pm0.02~\textrm{V}$                           | CMOS output active "H"    |

| S-8244AAGFN-CEGT2z | $4.450 \pm 0.025 \; \text{V}$                         | $0.045\pm0.02~\textrm{V}$                           | CMOS output active "H"    |

| S-8244AAHFN-CEHT2z | $4.300 \pm 0.025 \; \text{V}$                         | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AAIFN-CEIT2z | $4.400 \pm 0.025 \; \text{V}$                         | $0.045\pm0.02~\textrm{V}$                           | CMOS output active "H"    |

| S-8244AAJFN-CEJT2z | $4.500 \pm 0.025 \; \text{V}$                         | $0.38\pm0.1~\text{V}$                               | CMOS output active "H"    |

| S-8244AAKFN-CEKT2z | $4.475\pm0.025~\textrm{V}$                            | $0.38\pm0.1~\text{V}$                               | CMOS output active "H"    |

| S-8244AALFN-CELT2z | $4.350 \pm 0.025 \; \text{V}$                         | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AAMFN-CEMT2z | $4.300 \pm 0.025 \; \text{V}$                         | $0.25\pm0.07~\text{V}$                              | CMOS output active "L"    |

| S-8244AANFN-CENT2z | $4.150 \pm 0.025 \; V$                                | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AAOFN-CEOT2z | $4.250 \pm 0.025 \; \text{V}$                         | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AAPFN-CEPT2z | $4.050 \pm 0.025 \; \text{V}$                         | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AAQFN-CEQT2z | $4.150 \pm 0.025 \; V$                                | 0 V                                                 | Nch open drain active "H" |

| S-8244AARFN-CERT2z | $4.300 \pm 0.025 \; \text{V}$                         | $0.25\pm0.07~\text{V}$                              | Nch open drain active "H" |

| S-8244AATFN-CETT2z | $4.200 \pm 0.025 \; \text{V}$                         | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AAUFN-CEUT2z | $3.825 \pm 0.025 \; \text{V}$                         | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AAWFN-CEWT2z | $4.500 \pm 0.025 \; \text{V}$                         | $0.38\pm0.1~\text{V}$                               | CMOS output active "L"    |

| S-8244AAXFN-CEXT2z | $4.025 \pm 0.025 \ V$                                 | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AAZFN-CEZT2S | $4.280 \pm 0.025 \; \text{V}$                         | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244ABAFN-CFAT2z | $4.220 \pm 0.025 \; \text{V}$                         | $0.045\pm0.02~\textrm{V}$                           | CMOS output active "H"    |

| S-8244ABCFN-CFCT2z | $3.750 \pm 0.025 \text{ V}$                           | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244ABGFN-CFGT2S | $4.225 \pm 0.025 \; \text{V}$                         | $0.045\pm0.02~\textrm{V}$                           | Nch open drain active "L" |

| S-8244ABIFN-CFIT2S | $4.100 \pm 0.025 \text{ V}$                           | 0 V                                                 | Nch open drain active "L" |

| S-8244ABJFN-CFJT2S | $4.325 \pm 0.025 \; \text{V}$                         | $0.045 \pm 0.02 \text{ V}$                          | Nch open drain active "L" |

| S-8244ABKFN-CFKT2S | $4.175 \pm 0.025 \text{ V}$                           | 0 V                                                 | Nch open drain active "L" |

**Remark 1.** Please contact our sales office for the products with the detection voltage value other than those specified above. **2.** z: G or S

3. Please select products of environmental code = U for Sn 100%, halogen-free products.

#### BATTERY PROTECTION IC FOR 1-SERIAL TO 4-SERIAL-CELL PACK (SECONDARY PROTECTION) S-8244 Series Rev.6.3\_00

#### (3) TMSOP-8

|                    | Та                                                 | ble 3                                               |                           |

|--------------------|----------------------------------------------------|-----------------------------------------------------|---------------------------|

| Product name       | Overcharge detection voltage<br>[V <sub>cu</sub> ] | Overcharge hysteresis voltage<br>[V <sub>CD</sub> ] | Output form               |

| S-8244AAAFM-CEAT2U | $4.450 \pm 0.025 \text{ V}$                        | $0.38 \pm 0.1 \text{ V}$                            | CMOS output active "H"    |

| S-8244AABFM-CEBT2U | $4.200 \pm 0.025 \text{ V}$                        | 0 V                                                 | Nch open drain active "H" |

| S-8244AAFFM-CEFT2U | $4.350 \pm 0.025 \; \text{V}$                      | $0.045 \pm 0.02 \; V$                               | CMOS output active "H"    |

| S-8244AAGFM-CEGT2U | $4.450 \pm 0.025 \text{ V}$                        | $0.045 \pm 0.02 \; V$                               | CMOS output active "H"    |

| S-8244AAHFM-CEHT2U | $4.300 \pm 0.025 \text{ V}$                        | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AAIFM-CEIT2U | $4.400 \pm 0.025 \text{ V}$                        | $0.045\pm0.02~\text{V}$                             | CMOS output active "H"    |

| S-8244AAJFM-CEJT2U | $4.500 \pm 0.025 \text{ V}$                        | $0.38\pm0.1~\text{V}$                               | CMOS output active "H"    |

| S-8244AALFM-CELT2U | $4.350 \pm 0.025 \text{ V}$                        | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AANFM-CENT2U | $4.150 \pm 0.025 \text{ V}$                        | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AAPFM-CEPT2U | $4.050 \pm 0.025 \text{ V}$                        | $0.25\pm0.07~\text{V}$                              | CMOS output active "H"    |

| S-8244AAQFM-CEQT2U | $4.150 \pm 0.025 \text{ V}$                        | 0 V                                                 | Nch open drain active "H" |

| S-8244AAUFM-CEUT2U | $3.825 \pm 0.025 \text{ V}$                        | $0.25 \pm 0.07 \text{ V}$                           | CMOS output active "H"    |

| S-8244AAVFM-CEVT2U | $4.275 \pm 0.025 \text{ V}$                        | $0.045 \pm 0.02 \text{ V}$                          | CMOS output active "H"    |

| S-8244AAXFM-CEXT2U | $4.025 \pm 0.025 \text{ V}$                        | $0.25 \pm 0.07 \text{ V}$                           | CMOS output active "H"    |

| S-8244ABAFM-CFAT2U | $4.220 \pm 0.025 \text{ V}$                        | $0.045 \pm 0.02 \text{ V}$                          | CMOS output active "H"    |

| S-8244ABGFM-CFGT2U | $4.225 \pm 0.025 \text{ V}$                        | $0.045 \pm 0.02 \text{ V}$                          | Nch open drain active "L" |

| S-8244ABIFM-CFIT2U | $4.100 \pm 0.025 \text{ V}$                        | 0 V                                                 | Nch open drain active "L" |

| S-8244ABJFM-CFJT2U | $4.325 \pm 0.025 \text{ V}$                        | $0.045 \pm 0.02 \text{ V}$                          | Nch open drain active "L" |

| S-8244ABKFM-CFKT2U | 4.175 ± 0.025 V                                    | 0 V                                                 | Nch open drain active "L" |

| S-8244ABNFM-CFNT2U | $4.225 \pm 0.025 \text{ V}$                        | $0.38\pm0.1~\text{V}$                               | Nch open drain active "L" |

**Remark** Please contact our sales office for the products with the detection voltage value other than those specified above.

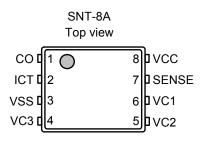

# Pin Configurations

| Table 4 |        |                                                                                                     |  |  |  |

|---------|--------|-----------------------------------------------------------------------------------------------------|--|--|--|

| Pin No. | Symbol | Description                                                                                         |  |  |  |

| 1       | CO     | FET gate connection pin for charge control                                                          |  |  |  |

| 2       | ICT    | Capacitor connection pin for overcharge detection delay                                             |  |  |  |

| 3       | VSS    | Input pin for negative power supply,<br>Connection pin for battery 4's negative voltage             |  |  |  |

| 4       | VC3    | Connection pin for battery 3's negative voltage,<br>Connection pin for battery 4's positive voltage |  |  |  |

| 5       | VC2    | Connection pin for battery 2's negative voltage,<br>Connection pin for battery 3's positive voltage |  |  |  |

| 6       | VC1    | Connection pin for battery 1's negative voltage,<br>Connection pin for battery 2's positive voltage |  |  |  |

| 7       | SENSE  | Connection pin for battery 1's positive voltage                                                     |  |  |  |

| 8       | VCC    | Input pin for positive power supply                                                                 |  |  |  |

Figure 2

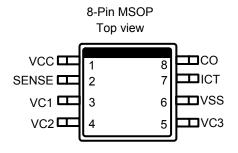

|         |        | Table 5                                                                                             |

|---------|--------|-----------------------------------------------------------------------------------------------------|

| Pin No. | Symbol | Description                                                                                         |

| 1       | VCC    | Input pin for positive power supply                                                                 |

| 2       | SENSE  | Connection pin for battery 1's positive voltage                                                     |

| 3       | VC1    | Connection pin for battery 1's negative voltage,<br>Connection pin for battery 2's positive voltage |

| 4       | VC2    | Connection pin for battery 2's negative voltage,<br>Connection pin for battery 3's positive voltage |

| 5       | VC3    | Connection pin for battery 3's negative voltage,<br>Connection pin for battery 4's positive voltage |

| 6       | VSS    | Input pin for negative power supply,<br>Connection pin for battery 4's negative voltage             |

| 7       | ICT    | Capacitor connection pin for overcharge detection delay                                             |

| 8       | CO     | FET gate connection pin for charge control                                                          |

Figure 3

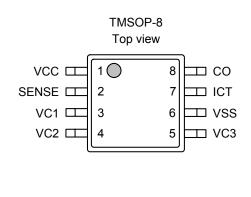

Figure 4

|         |        | Table 6                                                                                             |

|---------|--------|-----------------------------------------------------------------------------------------------------|

| Pin No. | Symbol | Description                                                                                         |

| 1       | VCC    | Input pin for positive power supply                                                                 |

| 2       | SENSE  | Connection pin for battery 1's positive voltage                                                     |

| 3       | VC1    | Connection pin for battery 1's negative voltage,<br>Connection pin for battery 2's positive voltage |

| 4       | VC2    | Connection pin for battery 2's negative voltage,<br>Connection pin for battery 3's positive voltage |

| 5       | VC3    | Connection pin for battery 3's negative voltage,<br>Connection pin for battery 4's positive voltage |

| 6       | VSS    | Input pin for negative power supply,<br>Connection pin for battery 4's negative voltage             |

| 7       | ICT    | Capacitor connection pin for overcharge detection delay                                             |

| 8       | CO     | FET gate connection pin for charge control                                                          |

### Absolute Maximum Ratings

|                     |                          | Та               | ble 7                   |                                              |            |

|---------------------|--------------------------|------------------|-------------------------|----------------------------------------------|------------|

|                     |                          |                  |                         | (Ta = 25°C unless otherwise                  | e specifie |

|                     | Item                     | Symbol           | Applied pin             | Absolute maximum ratings                     | Unit       |

| Input voltage b     | etween VCC and VSS       | V <sub>DS</sub>  | VCC                     | $V_{SS}$ –0.3 to $V_{SS}$ +26                | V          |

| Delay capacito      | r connection pin voltage | V <sub>ICT</sub> | ICT                     | $V_{\rm SS}$ –0.3 to $V_{\rm CC}$ +0.3       | V          |

| Input pin voltag    | je                       | V <sub>IN</sub>  | SENSE, VC1,<br>VC2, VC3 | $V_{\text{SS}}$ –0.3 to $V_{\text{CC}}$ +0.3 | V          |

|                     | (CMOS output)            |                  |                         | $V_{SS}$ –0.3 to $V_{CC}$ +0.3               | V          |

| CO output pin       | (Nch open drain output)  | V <sub>co</sub>  | со                      | V <sub>SS</sub> –0.3 to 26                   | V          |

| voltage             | (Pch open drain output)  |                  |                         | $V_{\rm CC}$ –26 to $V_{\rm CC}$ +0.3        | V          |

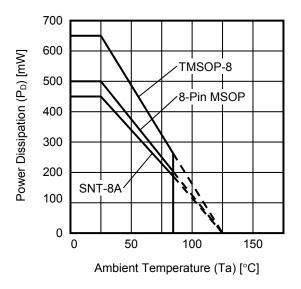

| _                   | SNT-8A                   |                  |                         | 450 <sup>*1</sup>                            | mW         |

| Power               | 8-Pin MSOP               | PD               | l _ [                   | 500 <sup>*1</sup>                            | mW         |

| dissipation         | TMSOP-8                  |                  |                         | 650 <sup>*1</sup>                            | mW         |

| Operating amb       | ient temperature         | T <sub>opr</sub> | _                       | -40 to +85                                   | °C         |

| Storage temperature |                          | T <sub>sta</sub> | _                       | -40 to +125                                  | °C         |

\*1. When mounted on board

#### [Mounted board]

(1) Board size : 114.3 mm  $\times$  76.2 mm  $\times$  t1.6 mm

(2) Name : JEDEC STANDARD51-7

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

Figure 5 Power Dissipation of Package (When Mounted on Board)

# BATTERY PROTECTION IC FOR 1-SERIAL TO 4-SERIAL-CELL PACK (SECONDARY PROTECTION) Rev.6.3\_00 S-8244 Series

# Electrical Characteristics

|                                                        |                    | Table 8                               |                            |                  |                            |          |                    |              |

|--------------------------------------------------------|--------------------|---------------------------------------|----------------------------|------------------|----------------------------|----------|--------------------|--------------|

|                                                        |                    | 1                                     |                            | (                | Ta = 25 °(                 | C unless |                    | specified)   |

| Item                                                   | Symbol             | Conditions                            | Min.                       | Тур.             | Max.                       | Unit     | Test<br>conditions | Test circuit |

| DETECTION VOLTAGE                                      | ı — — —            | i                                     |                            | ı — —            | ı —                        | ı — — —  | i                  |              |

| Overcharge detection voltage 1 *1                      | V <sub>CU1</sub>   | 3.7 V to 4.55 V Adjustment            | V <sub>CU1</sub><br>-0.025 | V <sub>CU1</sub> | V <sub>CU1</sub><br>+0.025 | V        | 1                  | 1            |

| Overcharge detection voltage 2 *1                      | V <sub>CU2</sub>   | 3.7 V to 4.55 V Adjustment            | V <sub>CU2</sub><br>-0.025 | $V_{CU2}$        | V <sub>CU2</sub><br>+0.025 | V        | 2                  | 1            |

| Overcharge detection voltage 3 *1                      | V <sub>CU3</sub>   | 3.7 V to 4.55 V Adjustment            | V <sub>CU3</sub><br>-0.025 | V <sub>CU3</sub> | V <sub>CU3</sub><br>+0.025 | V        | 3                  | 1            |

| Overcharge detection voltage 4 *1                      | $V_{CU4}$          | 3.7 V to 4.55 V Adjustment            | V <sub>CU4</sub><br>-0.025 | $V_{CU4}$        | V <sub>CU4</sub><br>+0.025 | V        | 4                  | 1            |

| Overcharge hysteresis voltage 1 *2                     | V <sub>CD1</sub>   | —                                     | 0.28                       | 0.38             | 0.48                       | V        | 1                  | 1            |

| Overcharge hysteresis voltage 2 *2                     | V <sub>CD2</sub>   | —                                     | 0.28                       | 0.38             | 0.48                       | V        | 2                  | 1            |

| Overcharge hysteresis voltage 3 *2                     | V <sub>CD3</sub>   | —                                     | 0.28                       | 0.38             | 0.48                       | V        | 3                  | 1            |

| Overcharge hysteresis voltage 4 *2                     | V <sub>CD4</sub>   | —                                     | 0.28                       | 0.38             | 0.48                       | V        | 4                  | 1            |

| Detection voltage temperature coefficient *3           | $T_{COE}$          | Ta = -40°C to +85°C <sup>*4</sup>     | -0.4                       | 0.0              | +0.4                       | mV/°C    | —                  | —            |

| DELAY TIME                                             |                    |                                       |                            |                  |                            |          |                    |              |

| Overcharge detection delay time                        | t <sub>CU</sub>    | C = 0.1 μF                            | 1.0                        | 1.5              | 2.0                        | S        | 5                  | 2            |

| OPERATING VOLTAGE                                      |                    |                                       |                            |                  |                            |          |                    |              |

| Operating voltage<br>between VCC and VSS <sup>*5</sup> | V <sub>DSOP</sub>  | —                                     | 3.6                        | _                | 24                         | V        | —                  | —            |

| CURRENT CONSUMPTION                                    | ÷                  |                                       |                            |                  |                            | ÷        |                    |              |

| Current consumption<br>during normal operation         | I <sub>OPE</sub>   | V1 = V2 = V3 = V4 = 3.5 V             | —                          | 1.5              | 3.0                        | μA       | 6                  | 3            |

| Current consumption at<br>power down                   | I <sub>PDN</sub>   | V1 = V2 = V3 = V4 = 2.3 V             | _                          | 1.2              | 2.4                        | μΑ       | 6                  | 3            |

| VC1 sink current                                       | I <sub>VC1</sub>   | V1 = V2 = V3 = V4 = 3.5 V             | -0.3                       | _                | 0.3                        | μA       | 6                  | 3            |

| VC2 sink current                                       | I <sub>VC2</sub>   | V1 = V2 = V3 = V4 = 3.5 V             | -0.3                       | _                | 0.3                        | μA       | 6                  | 3            |

| VC3 sink current                                       | I <sub>VC3</sub>   | V1 = V2 = V3 = V4 = 3.5 V             | -0.3                       | —                | 0.3                        | μA       | 6                  | 3            |

| OUTPUT VOLTAGE <sup>*6</sup>                           | i                  | · · · · · · · · · · · · · · · · · · · |                            | i                | i                          | i        | i                  |              |

| CO "H" voltage                                         | V <sub>CO(H)</sub> | at I <sub>OUT</sub> = 10 μA           | V <sub>CC</sub><br>-0.05   | —                | —                          | V        | 7                  | 4            |

| CO "L" voltage                                         | V <sub>CO(L)</sub> | at I <sub>OUT</sub> = 10 μA           | _                          | _                | V <sub>SS</sub><br>+0.05   | V        | 7                  | 4            |

\*1.  $\pm$  50 mV when Ta = -40°C to +85°C.

\*2.  $0.25 \pm 0.07$  V,  $0.13 \pm 0.04$  V,  $0.045 \pm 0.02$  V except for 0.38 V hysteresis models.

**\*3.** Overcharge detection voltage or overcharge hysteresis voltage.

\*4. Since products are not screened at high and low temperature, the specification for this temperature range is guaranteed by design, not tested in production.

\*5. After detecting the overcharge, the delay circuit operates normally in the range of operating voltage.

\*6. Output logic and CMOS or open drain output can be selected.

## Test Circuits

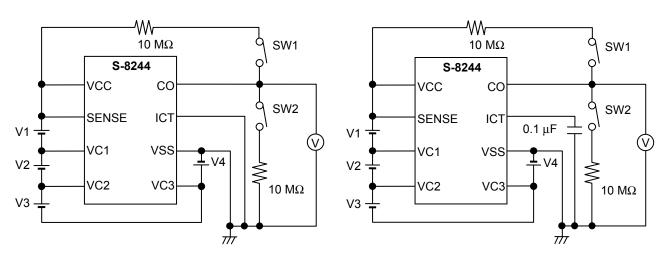

#### (1) Test Condition 1, Test Circuit 1

Set switches 1 and 2 to OFF for CMOS output product. Set switch 1 to ON and switch 2 to OFF for Nch open drain product. Set switch 1 to OFF and switch 2 to ON for Pch open drain product.

• Product with CMOS output active "H", Nch open drain output active "H"

The overcharge detection voltage 1 ( $V_{CU1}$ ) is a voltage at V1; when the CO pin's voltage is set to "H" by increasing V1 gradually, after setting V1 = V2 = V3 = V4 = 3.5 V. After that, gradually decreasing V1's voltage to set CO = "L", and the difference of this V1's voltage and  $V_{CU1}$  is the overcharge hysteresis voltage 1 ( $V_{CD1}$ ).

• Product with CMOS output active "L", Nch open drain output active "L", Pch open drain output active "L"

The overcharge detection voltage 1 ( $V_{CU1}$ ) is a voltage at V1; when the CO pin's voltage is set to "L" by increasing V1 gradually, after setting V1 = V2 = V3 = V4 = 3.5 V. After that, gradually decreasing V1's voltage to set CO = "H", and the difference of this V1's voltage and  $V_{CU1}$  is the overcharge hysteresis voltage 1 ( $V_{CD1}$ ).

#### (2) Test Condition 2, Test Circuit 1

Set switches 1 and 2 to OFF for CMOS output product. Set switch 1 to ON and switch 2 to OFF for Nch open drain product. Set switch 1 to OFF and switch 2 to ON for Pch open drain product.

• Product with CMOS output active "H", Nch open drain output active "H"

The overcharge detection voltage 2 ( $V_{CU2}$ ) is a voltage at V2; when the CO pin's voltage is set to "H" by increasing V2 gradually, after setting V1 = V2 = V3 = V4 = 3.5 V. After that, gradually decreasing V2's voltage to set CO = "L", and the difference of this V2's voltage and  $V_{CU2}$  is the overcharge hysteresis voltage 2 ( $V_{CD2}$ ).

• Product with CMOS output active "L", Nch open drain output active "L", Pch open drain output active "L"

The overcharge detection voltage 2 ( $V_{CU2}$ ) is a voltage at V2; when the CO pin's voltage is set to "L" by increasing V2 gradually, after setting V1 = V2 = V3 = V4 = 3.5 V. After that, gradually decreasing V2's voltage to set CO = "H", and the difference of this V2's voltage and  $V_{CU2}$  is the overcharge hysteresis voltage 2 ( $V_{CD2}$ ).

#### (3) Test Condition 3, Test Circuit 1

Set switches 1 and 2 to OFF for CMOS output product. Set switch 1 to ON and switch 2 to OFF for Nch open drain product. Set switch 1 to OFF and switch 2 to ON for Pch open drain product.

· Product with CMOS output active "H", Nch open drain output active "H"

The overcharge detection voltage 3 ( $V_{CU3}$ ) is a voltage at V3; when the CO pin's voltage is set to "H" by increasing V3 gradually, after setting V1 = V2 = V3 = V4 = 3.5 V. After that, gradually decreasing V3's voltage to set CO = "L", and the difference of this V3's voltage and  $V_{CU3}$  is the overcharge hysteresis voltage 3 ( $V_{CD3}$ ).

• Product with CMOS output active "L", Nch open drain output active "L", Pch open drain output active "L"

The overcharge detection voltage 3 ( $V_{CU3}$ ) is a voltage at V3; when the CO pin's voltage is set to "L" by increasing V3 gradually, after setting V1 = V2 = V3 = V4 = 3.5 V. After that, gradually decreasing V3's voltage to set CO = "H", and the difference of this V3's voltage and  $V_{CU3}$  is the overcharge hysteresis voltage 3 ( $V_{CD3}$ ).

#### (4) Test Condition 4, Test Circuit 1

Set switches 1 and 2 to OFF for CMOS output product. Set switch 1 to ON and switch 2 to OFF for Nch open drain product. Set switch 1 to OFF and switch 2 to ON for Pch open drain product.

• Product with CMOS output active "H", Nch open drain output active "H"

The overcharge detection voltage 4 ( $V_{CU4}$ ) is a voltage at V4; when the CO pin's voltage is set to "H" by increasing V4 gradually, after setting V1 = V2 = V3 = V4 = 3.5 V. After that, gradually decreasing V4's voltage to set CO = "L", and the difference of this V4's voltage and  $V_{CU4}$  is the overcharge hysteresis voltage 4 ( $V_{CD4}$ ).

• Product with CMOS output active "L", Nch open drain output active "L", Pch open drain output active "L"

The overcharge detection voltage 4 ( $V_{CU4}$ ) is a voltage at V4; when the CO pin's voltage is set to "L" by increasing V4 gradually, after setting V1 = V2 = V3 = V4 = 3.5 V. After that, gradually decreasing V4's voltage to set CO = "H", and the difference of this V4's voltage and  $V_{CU4}$  is the overcharge hysteresis voltage 4 ( $V_{CD4}$ ).

#### (5) Test Condition 5, Test Circuit 2

Set switches 1 and 2 to OFF for CMOS output product. Set switch 1 to ON and switch 2 to OFF for Nch open drain product. Set switch 1 to OFF and switch 2 to ON for Pch open drain product.

• Product with CMOS output active "H", Nch open drain output active "H"

Rise V1 to 4.7 V momentarily within 10  $\mu$ s after setting V1 = V2 = V3 = V4 = 3.5 V. The period from V1 having reached 4.7 V to CO = "H" is the overcharge detection delay time (t<sub>CU</sub>).

• Product with CMOS output active "L", Nch open drain output active "L", Pch open drain output active "L"

Rise V1 to 4.7 V momentarily within 10  $\mu$ s after setting V1 = V2 = V3 = V4 = 3.5 V. The period from V1 having reached 4.7 V to CO = "L" is the overcharge detection delay time (t<sub>CU</sub>).

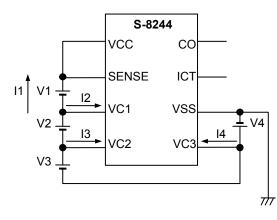

#### (6) Test Condition 6, Test Circuit 3

Measure current consumption (I1) setting V1 = V2 = V3 = V4 = 2.3 V. This I1 is current consumption at power-down ( $I_{PDN}$ ).

Measure current consumption (I1) setting V1 = V2 = V3 = V4 = 3.5 V. This I1 is current consumption during normal operation ( $I_{OPE}$ ), I2 is the VC1 sink current ( $I_{VC1}$ ), I3 is the VC2 sink current ( $I_{VC2}$ ), I4 is the VC3 sink current ( $I_{VC3}$ ).

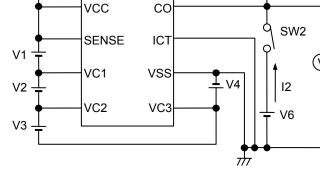

#### (7) Test Condition 7, Test Circuit 4

Measure setting switch 1 to OFF and switch 2 to ON.

• Product with CMOS output active "H"

Decrease V6 from V<sub>CC</sub> gradually after setting V1 = V2 = V3 = V4 = 4.6 V, the V6's voltage when flowing I2 = -10  $\mu$ A is the V<sub>CO(H)</sub> voltage. Increase V6 from 0 V gradually after setting V1 = V2 = V3 = V4 = 3.5 V, the V6's voltage when flowing I2 = 10  $\mu$ A is the V<sub>CO(L)</sub> voltage.

• Product with CMOS output active "L"

Decrease V6 from V<sub>CC</sub> gradually after setting V1 = V2 = V3 = V4 = 3.5 V, the V6's voltage when flowing I2 =  $-10 \mu$ A is the V<sub>CO(H)</sub> voltage. Increase V6 from 0 V gradually after setting V1 = V2 = V3 = V4 = 4.6 V, the V6's voltage when flowing I2 =  $10 \mu$ A is the V<sub>CO(L)</sub> voltage.

• Product with Pch open drain output active "L"

Decrease V6 from V<sub>CC</sub> gradually after setting V1 = V2 = V3 = V4 = 3.5 V, the V6's voltage when flowing I2 =  $-10 \mu$ A is the V<sub>CO(H)</sub> voltage.

• Product with Nch open drain output active "H"

Increase V6 from 0 V gradually after setting V1 = V2 = V3 = V4 = 3.5 V, the V6's voltage when flowing I2 = 10  $\mu$ A is the V<sub>CO(L)</sub> voltage.

· Product with Nch open drain output active "L"

Increase V6 from 0 V gradually after setting V1 = V2 = V3 = V4 = 4.6 V, the V6's voltage when flowing I2 = 10  $\mu$ A is the V<sub>CO(L)</sub> voltage.

Test Circuit 1

11

۹ swı

V5

S-8244

Test Circuit 3

Figure 6

### Operation

**Remark** Refer to " **Battery Protection IC Connection Example**".

#### 1. Overcharge Detection

• Product with CMOS output active "H", Nch open drain output active "H"

During charging in the normal status, any of battery voltages exceeds overcharge detection voltage ( $V_{CU}$ ), and this status is maintained for overcharge detection delay time ( $t_{CU}$ ) or longer, CO gets "H". This is overcharge status. Connecting an FET to the CO pin enables charge-control and the second protect.

In this case, the IC maintains the overcharge status until all battery voltages decreases, to the overcharge hysteresis voltage ( $V_{CD}$ ) from the overcharge detection voltage ( $V_{CU}$ ).

• Product with CMOS output active "L", Nch open drain output active "L", Pch open drain output active "L"

During charging in the normal status, any of battery voltages exceeds overcharge detection voltage ( $V_{CU}$ ), and this status is maintained for overcharge detection delay time ( $t_{CU}$ ) or longer, CO gets "L". This is overcharge status. Connecting an FET to the CO pin enables charge-control and the second protect.

In this case, the IC maintains the overcharge status until all battery voltages decreases, to the overcharge hysteresis voltage ( $V_{CD}$ ) from the overcharge detection voltage ( $V_{CU}$ ).

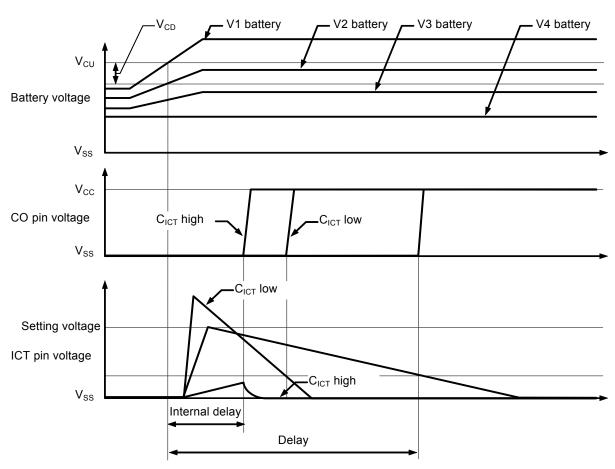

#### 2. Delay Circuit

The delay circuit rapidly charges the capacitor connected to the delay capacitor connection pin up to a specified voltage when the voltage of one of the batteries exceeds the overcharge detection voltage ( $V_{CU}$ ). Then, the delay circuit gradually discharges the capacitor at 100 nA and inverts the CO output when the voltage at the delay capacitor connection pin goes below a specified level. Overcharge detection delay time ( $t_{CU}$ ) varies depending upon the external capacitor.

Each delay time is calculated using the following equation.

$\label{eq:min.typ.} \begin{array}{ll} \mbox{Min. Typ. Max.} \\ t_{CU}[s] = \mbox{Delay Coefficient (10, 15, 20)} \times C_{ICT} \, [\mu F] \end{array}$

Because the delay capacitor is rapidly charged, the smaller the capacitance, the larger the difference between the maximum voltage and the specified value of delay capacitor pin (ICT pin). This will cause a deviation between the calculated delay time and the resultant delay time. Also, delay time is internally set in this IC to prevent the CO output from inverting until the charge to delay capacitor pin is reached to the specified voltage. If large capacitance is used, output may be enabled without delay time because charge is disabled within the internal delay time.

Please note that the maximum capacitance connected to the delay capacitor pin (ICT pin) is 1 µF.

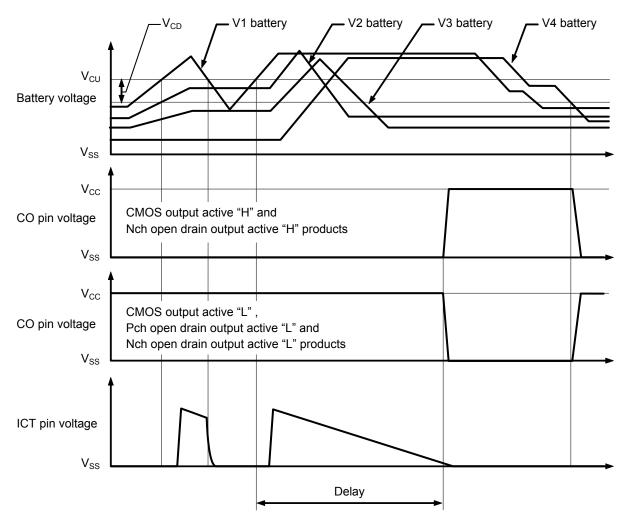

# Timing Chart

Figure 7

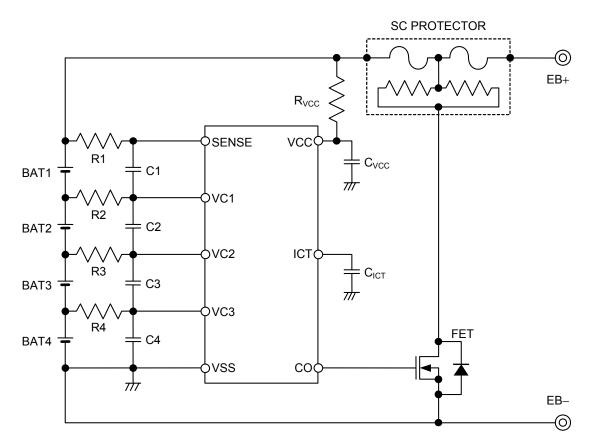

### Battery Protection IC Connection Example

(1) Connection Example 1

### Figure 8

| Symbol           | Min. | Тур. | Max. | Unit |

|------------------|------|------|------|------|

| R1 to R4         | 0    | 1 k  | 10 k | Ω    |

| C1 to C4         | 0    | 0.1  | 1    | μF   |

| R <sub>VCC</sub> | 0    | 100  | 1 k  | Ω    |

| C <sub>VCC</sub> | 0    | 0.1  | 1    | μF   |

| CICT             | 0    | 0.1  | 1    | μF   |

Table 9

Constants for External Components 1

- Caution1. The above constants may be changed without notice.

- 2. It has not been confirmed whether the operation is normal or not in circuits other than the above example of connection. In addition, the example of connection shown above and the constant do not guarantee proper operation. Perform thorough evaluation using the actual application to set the constant.

#### [For SC PROTECTOR, contact]

Advanced Device Sales Dept., Global Sales & Marketing Div., Dexerials Corporation Gate City Osaki East Tower 8F, 1-11-2 Osaki, Shinagawa-ku, Tokyo, 141-0032 Japan TEL +81-3-5435-3946 Contact Us: http://www.dexerials.jp/en/

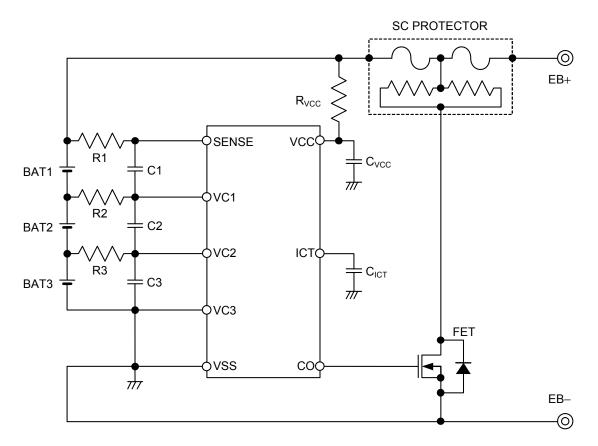

#### (2) Connection Example 2 (for 3-cells)

| Figure | 9 |

|--------|---|

|--------|---|

| Symbol           | Min. | Тур. | Max. | Unit |

|------------------|------|------|------|------|

| R1 to R3         | 0    | 1 k  | 10 k | Ω    |

| C1 to C3         | 0    | 0.1  | 1    | μF   |

| R <sub>VCC</sub> | 0    | 100  | 1 k  | Ω    |

| C <sub>VCC</sub> | 0    | 0.1  | 1    | μF   |

| CICT             | 0    | 0.1  | 1    | μF   |

| Table 10         Constants for External Components 2 |  |

|------------------------------------------------------|--|

|------------------------------------------------------|--|

Caution1. The above constants may be changed without notice.

2. It has not been confirmed whether the operation is normal or not in circuits other than the above example of connection. In addition, the example of connection shown above and the constant do not guarantee proper operation. Perform thorough evaluation using the actual application to set the constant.

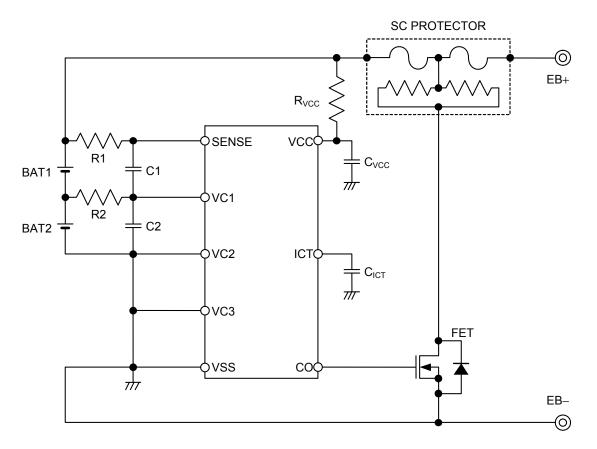

#### (3) Connection Example 3 (for 2-cells)

| Figure | 10 |

|--------|----|

|--------|----|

| Table 11 Constants for External Components 3 |      |      |      |      |

|----------------------------------------------|------|------|------|------|

| Symbol                                       | Min. | Тур. | Max. | Unit |

| R1, R2                                       | 0    | 1 k  | 10 k | Ω    |

| C1, C2                                       | 0    | 0.1  | 1    | μF   |

| R <sub>VCC</sub>                             | 0    | 100  | 1 k  | Ω    |

| C <sub>VCC</sub>                             | 0    | 0.1  | 1    | μF   |

| C <sub>ICT</sub>                             | 0    | 0.1  | 1    | μF   |

| Table 11 Constants for External Components 3 |

|----------------------------------------------|

|----------------------------------------------|

Caution1. The above constants may be changed without notice.

2. It has not been confirmed whether the operation is normal or not in circuits other than the above example of connection. In addition, the example of connection shown above and the constant do not guarantee proper operation. Perform thorough evaluation using the actual application to set the constant.

#### (4) Connection Example 4 (for 1-cell)

| Figure | 11 |

|--------|----|

|--------|----|

| Symbol           | Min. | Тур. | Max. | Unit |

|------------------|------|------|------|------|

| R1               | 0    | 1 k  | 10 k | Ω    |

| C1               | 0    | 0.1  | 1    | μF   |

| R <sub>VCC</sub> | 0    | 100  | 1 k  | Ω    |

| C <sub>VCC</sub> | 0    | 0.1  | 1    | μF   |

| C <sub>ICT</sub> | 0    | 0.1  | 1    | μF   |

| Table 12 Constants for External Components | 4 |

|--------------------------------------------|---|

|--------------------------------------------|---|

Caution1. The above constants may be changed without notice.

2. It has not been confirmed whether the operation is normal or not in circuits other than the above example of connection. In addition, the example of connection shown above and the constant do not guarantee proper operation. Perform thorough evaluation using the actual application to set the constant.

### Precautions

- This IC charges the delay capacitor through the delay capacitor pin (ICT pin) immediately when the voltage of one of batteries V1 to V4 reaches the overcharge voltage. Therefore, setting the resistor connected to the VCC pin to any value greater than the recommended level causes a reduction in the IC power supply voltage because of charge current of the delay capacitor. This may lead to a malfunction. Set up the resistor NOT to exceed the typical value. If you change the resistance, please consult us.

- DO NOT connect any of overcharged batteries. Even if only one overcharged battery is connected to this IC, the IC detects overcharge, then charge current flows to the delay capacitor through the parasitic diode between pins where the battery is not connected yet. This may lead to a malfunction. Please perform sufficient evaluation in the case of use. Depending on an application circuit, even when the fault charge battery is not contained, the connection turn of a battery may be restricted in order to prevent the output of CO detection pulse at the time of battery connection.

CMOS output active "H" and Nch open drain output active "H" products

- In this IC, the output logic of the CO pin is inverted after several milliseconds of internal delay if this IC is under the overcharge condition even ICT pin is either "V<sub>SS</sub>-short circuit," "V<sub>DD</sub>-short circuit" or "Open" status.

- Any position from V1 to V4 can be used when applying this IC for a one to three-cell battery. However, be sure to short circuit between pins not in use (SENSE–VC1, VC1–VC2, VC2–VC3, or VC3–VSS).

- The application conditions for the input voltage, output voltage, and load current should not exceed the package power dissipation.

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- SII claims no responsibility for any and all disputes arising out of or in connection with any infringement of the products including this IC upon patents owned by a third party.

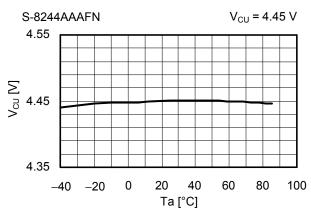

# Characteristics (Typical Data)

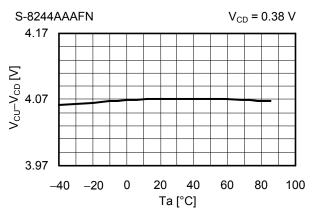

### 1. Detection Voltage vs. Temperature

Overcharge Detection Voltage vs. Temperature

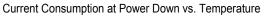

#### 2. Current Consumption vs. Temperature

S-8244AAAFN V<sub>CC</sub> = 14.0 V

Current Consumption during Normal Operation vs. Temperature

0 -40 -20 0 20 40 60 80 100 Ta [°C]

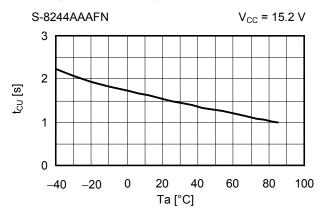

### 3. Delay Time vs. Temperature

Overcharge Detection Delay Time vs. Temperature

Caution Please design all applications of the S-8244 Series with safety in mind.

Overcharge Release Voltage vs. Temperature

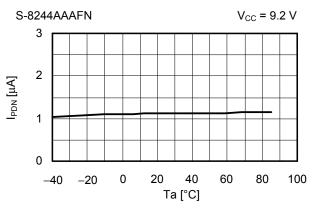

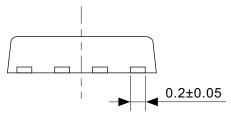

No. PH008-A-P-SD-2.0

| TITLE                  | SNT-8A-A-PKG Dimensions |

|------------------------|-------------------------|

| No.                    | PH008-A-P-SD-2.0        |

| SCALE                  |                         |

| UNIT                   | mm                      |

|                        |                         |

|                        |                         |

|                        |                         |

|                        |                         |

| Seiko Instruments Inc. |                         |

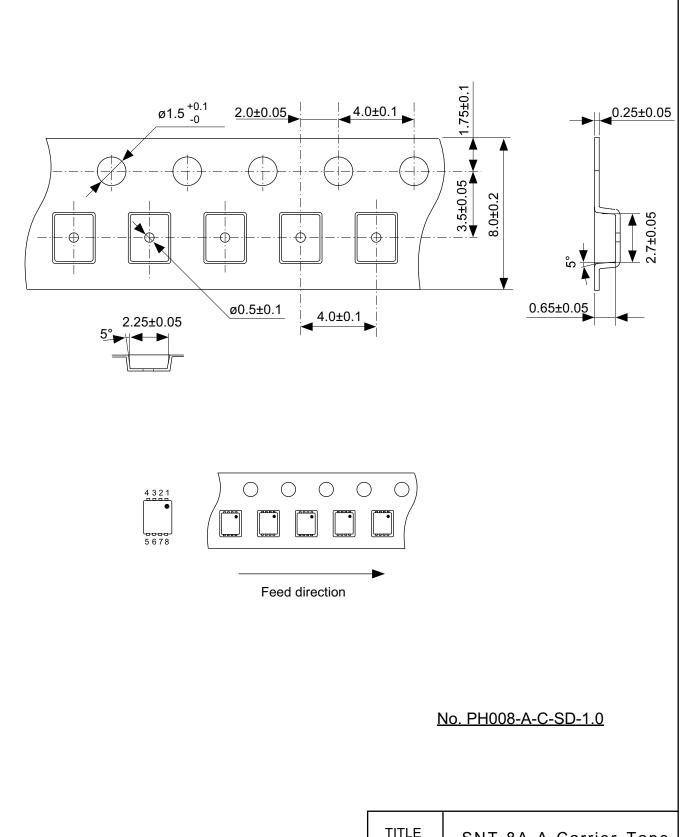

| TITLE                  | SNT-8A-A-Carrier Tape |

|------------------------|-----------------------|

| No.                    | PH008-A-C-SD-1.0      |

| SCALE                  |                       |

| UNIT                   | mm                    |

|                        |                       |

|                        |                       |

|                        |                       |

|                        |                       |

| Seiko Instruments Inc. |                       |

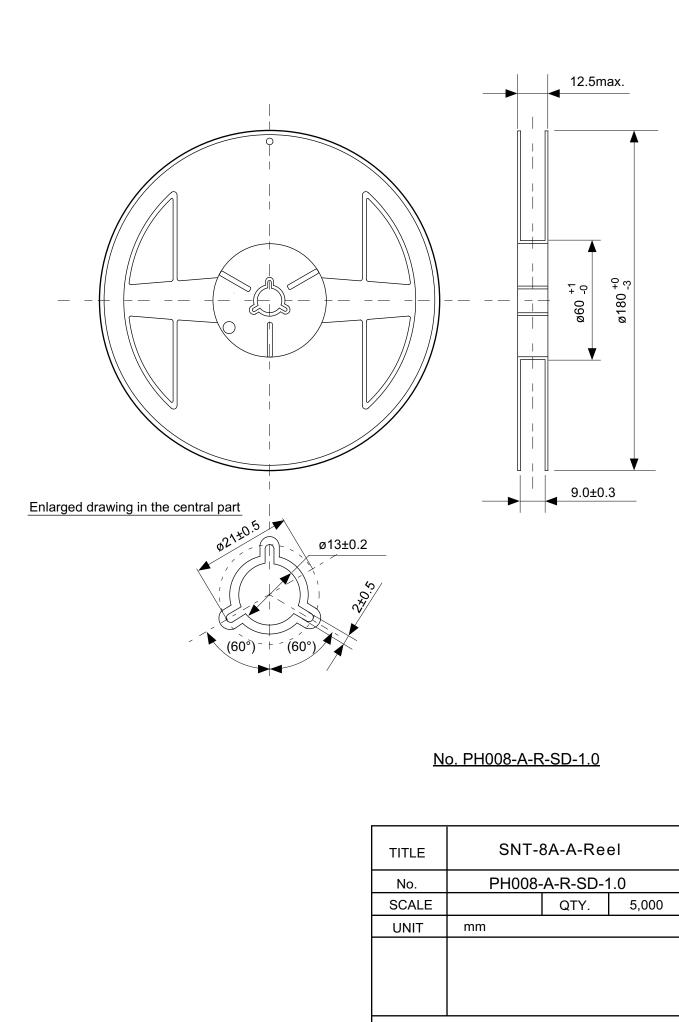

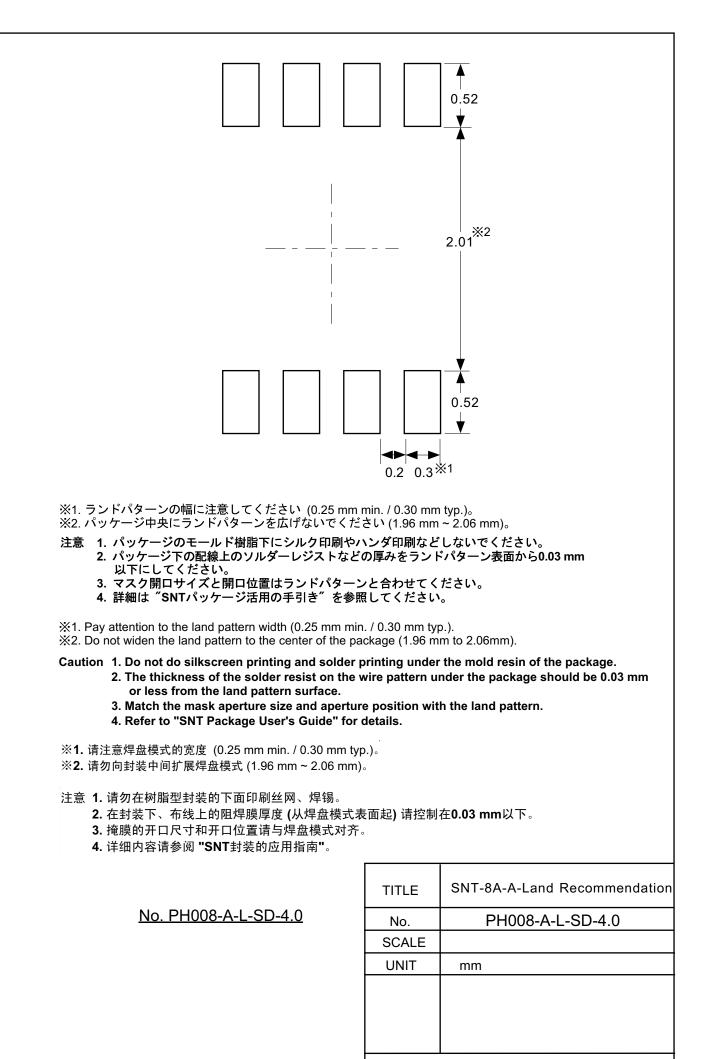

Seiko Instruments Inc.

Seiko Instruments Inc.

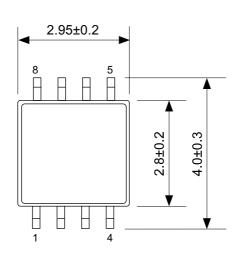

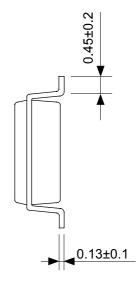

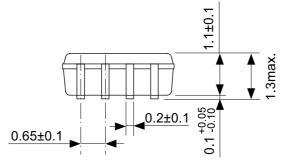

No. FN008-A-P-SD-1.1

| TITLE | MSOP8-A-PKG Dimensions |

|-------|------------------------|

| No.   | FN008-A-P-SD-1.1       |

| SCALE |                        |

| UNIT  | mm                     |

|       |                        |

|       |                        |

|       |                        |

|       | Seiko Instruments Inc. |

- The information described herein is subject to change without notice.

- Seiko Instruments Inc. is not responsible for any problems caused by circuits or diagrams described herein whose related industrial properties, patents, or other rights belong to third parties. The application circuit examples explain typical applications of the products, and do not guarantee the success of any specific mass-production design.

- When the products described herein are regulated products subject to the Wassenaar Arrangement or other agreements, they may not be exported without authorization from the appropriate governmental authority.

- Use of the information described herein for other purposes and/or reproduction or copying without the express permission of Seiko Instruments Inc. is strictly prohibited.

- The products described herein cannot be used as part of any device or equipment affecting the human body, such as exercise equipment, medical equipment, security systems, gas equipment, vehicle equipment, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment, without prior written permission of Seiko Instruments Inc.

- The products described herein are not designed to be radiation-proof.

- Although Seiko Instruments Inc. exerts the greatest possible effort to ensure high quality and reliability, the failure or malfunction of semiconductor products may occur. The user of these products should therefore give thorough consideration to safety design, including redundancy, fire-prevention measures, and malfunction prevention, to prevent any accidents, fires, or community damage that may ensue.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# ABLIC:

S-8244AASPH-CESTFG S-8244AAZPH-CEZTFG S-8244ABBPH-CFBTFG S-8244ABDPH-CFDTFG S-8244ABEPH-CFETFG S-8244ABHPH-CFHTFG S-8244AAPH-CEATFG S-8244AABPH-CEBTFG S-8244AABPH-CEBTFG S-8244AAGPH-CEGTFG