## 1200 V 65 mΩ SiC MOSFET

#### Silicon Carbide MOSFET

**Trench-Assisted Planar Technology**

$\begin{array}{llll} V_{DS} & = & 1200 \text{ V} \\ R_{DS(ON)}(Typ.) = & 65 \text{ m}\Omega \\ I_{D}(T_{C} = 100^{\circ}\text{C}) & = & 25 \text{ A} \\ \end{array}$

#### **Features**

- Gen3F (3rd Generation) Technology

- Most Stable R<sub>DS(ON)</sub> over Temperature

- Low Coss, Crss and Balanced Ciss/Crss

- Lower Q<sub>GD</sub> and Balanced R<sub>G(INT)</sub>

- Electromagnetically Optimized Design

- Robust Body Diode with Low V<sub>F</sub> and Low Q<sub>RR</sub>

- 100% Avalanche (UIL) Tested

- AEC-Q101 Qualified

#### **Advantages**

- Superior Performance and Robustness

- Lowest Conduction Losses at all Temperatures

- Lesser Switching Spikes and Lower Losses

- Faster and More Efficient Switching

- Reduced Ringing

- Ease of Paralleling without Thermal Runaway

- Excellent Power Density and System Efficiency

- Enhanced System Reliability

#### **Applications**

- xEV OBC & DC-DC

- EV Fast Charging Infrastructure

- Solar / PV

- Energy Storage Systems

- Uninterruptible Power Supply

- Motor Control

- Induction Heating & Welding

- High Voltage Converters

| Absolute Maximum Ratings (At T <sub>C</sub> = 25°C Unless Otherwise Stated) |                        |                                                  |            |      |         |  |

|-----------------------------------------------------------------------------|------------------------|--------------------------------------------------|------------|------|---------|--|

| Parameter                                                                   | Symbol                 | Conditions                                       | Values     | Unit | Note    |  |

| Drain-Source Voltage                                                        | $V_{\text{DS(max)}}$   | $V_{GS}$ = 0 V, $I_D$ = 100 $\mu A$              | 1200       | V    |         |  |

| Gate-Source Voltage (Dynamic)                                               | $V_{\text{GS(max)}}$   |                                                  | -10 / +22  | V    |         |  |

| Gate-Source Voltage (Static)                                                | $V_{GS(op)-ON}$        | Recommended Operation                            | 18         | V    | Note 1  |  |

| Gate-Source voltage (Static)                                                | $V_{GS(op)	ext{-}OFF}$ | neconinented operation                           | -5 to -3   | V    | Note i  |  |

|                                                                             |                        | $T_C = 25^{\circ}C$ , $V_{GS} = -5 / +18 V$      | 36         |      |         |  |

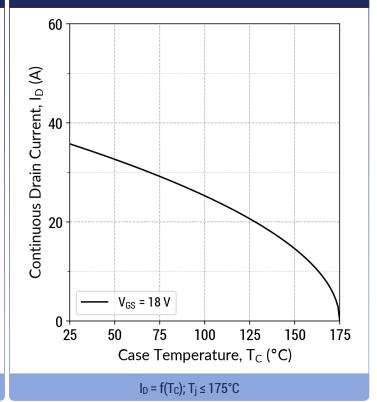

| Continuous Drain Current                                                    | $I_{D}$                | $T_C = 100$ °C, $V_{GS} = -5 / +18 V$            | 25         | Α    | Fig. 16 |  |

|                                                                             |                        | $T_C = 135^{\circ}C$ , $V_{GS} = -5 / +18 V$     | 18         |      |         |  |

| Pulsed Drain Current                                                        | I <sub>D(pulse)</sub>  | $t_P \le 3\mu s$ , $D \le 1\%$ , $V_{GS} = 18~V$ | 70         | Α    | Note 2  |  |

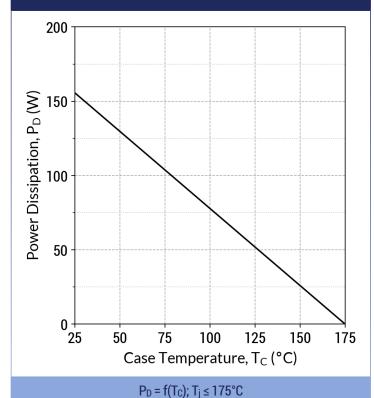

| Power Dissipation                                                           | $P_D$                  | $T_c = 25^{\circ}C$                              | 156        | W    | Fig. 17 |  |

| Non-Repetitive Avalanche Energy                                             | E <sub>AS</sub>        | $L = 8 \text{ mH}, I_{AV} = 6.5 \text{ A}$       | 169        | mJ   |         |  |

| Operating Junction and Storage Temperature                                  | $T_{j}$ , $T_{stg}$    |                                                  | -55 to 175 | °C   |         |  |

Note 1: This product can support 0V turn-off gate drive voltage with optimized PCB layout and gate drive circuit configuration.

Note 2: Pulse Width tp Limited by T<sub>j(max)</sub>

SEE IMPORTANT NOTICES AND DISCLAIMERS AT THE END OF THIS DATA SHEET REGARDING THE INFORMATION IN THIS DATA SHEET, THE USE OF OUR PRODUCTS, AND YOUR RESPONSIBILITIES RELATING TO SUCH USE.

Rev 24/Jul Page 1 of 14

| Electrical Characteristics (At T <sub>C</sub> = 25°C Unless Otherwise Stated) |                     |                                                                                                  |        |      |          |       |            |

|-------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------|--------|------|----------|-------|------------|

| Parameter                                                                     | Symbol              | Conditions                                                                                       | Values |      |          | Unit  | Note       |

|                                                                               | Syllibol            | Conditions                                                                                       | Min.   | Тур. | Max.     | Ullit | Note       |

| Drain-Source Breakdown Voltage                                                | V <sub>DSS</sub>    | $V_{GS} = 0 \text{ V, } I_D = 100  \mu\text{A}$                                                  | 1200   |      |          | V     |            |

| Zero Gate Voltage Drain Current                                               | I <sub>DSS</sub>    | $V_{DS}$ = 1200 V, $V_{GS}$ = 0 V                                                                |        | 1    | 50       | μΑ    |            |

| Gate Source Leakage Current                                                   | I <sub>GSS</sub>    | $V_{DS} = 0 \text{ V, } V_{GS} = 22 \text{ V}$                                                   |        |      | 100      | nA    |            |

|                                                                               |                     | $V_{DS}$ = 0 V, $V_{GS}$ = -10 V                                                                 |        |      | -100     |       |            |

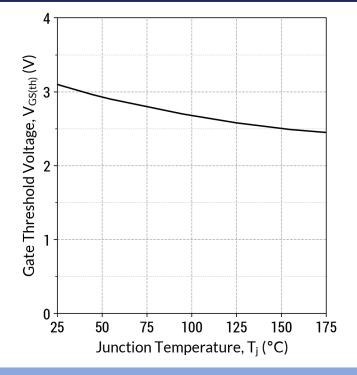

| Gate Threshold Voltage                                                        | V <sub>GS(th)</sub> | $V_{DS} = V_{GS}$ , $I_D = 10 \text{ mA}$                                                        | 2.2    | 3.1  | 4.3      | V     | Note 3     |

| Transconductance                                                              | <b>g</b> fs         | $V_{DS} = 10 \text{ V, } I_D = 13 \text{ A}$                                                     |        | 7.1  |          | S     | Fig. 5     |

| Transconductance                                                              | yıs                 | $V_{DS} = 10 \text{ V, } I_D = 13 \text{ A, } T_j = 175 ^{\circ}\text{C}$                        |        | 8.1  |          |       | 1 lg. 5    |

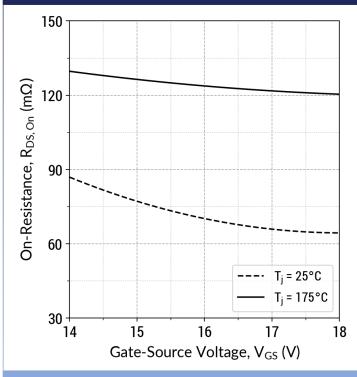

| Drain-Source On-State Resistance                                              | R <sub>DS(ON)</sub> | $V_{GS} = 18 \text{ V, } I_D = 13 \text{ A}$                                                     |        | 65   | 86       | mΩ    | Fig. 6-9   |

|                                                                               | 1 (DS(ON)           | $V_{GS} = 18 \text{ V, } I_D = 13 \text{ A, } T_j = 175 ^{\circ}\text{C}$                        |        | 122  |          | 11122 |            |

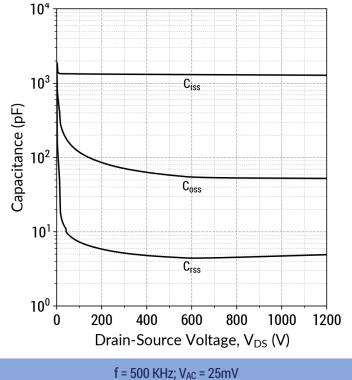

| Input Capacitance                                                             | Ciss                |                                                                                                  |        | 1298 |          |       |            |

| Output Capacitance                                                            | Coss                | _                                                                                                |        | 53   |          | pF    | Fig. 12    |

| Reverse Transfer Capacitance                                                  | C <sub>rss</sub>    | _                                                                                                |        | 4.5  |          |       |            |

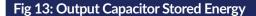

| Coss Stored Energy                                                            | E <sub>oss</sub>    | $ V_{DS} = 800 \text{ V, } V_{GS} = 0 \text{ V}$ $-$                                             |        | 20   |          | μJ    | Fig. 13    |

| Coss Stored Charge                                                            | Qoss                | _ f = 500 KHz, V <sub>AC</sub> = 25mV                                                            |        | 70   |          | nC    |            |

| Effective Output Capacitance (Energy Related)                                 | $C_{o(er)}$         | , ,,,                                                                                            |        | 62   |          | _     |            |

| Effective Output Capacitance (Time Related)                                   | C <sub>o(tr)</sub>  | -                                                                                                |        | 88   |          | pF    | Note 4     |

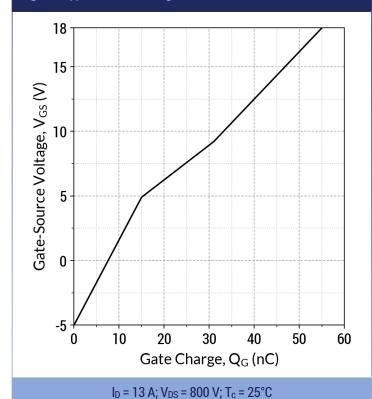

| Gate-Source Charge                                                            | Q <sub>gs</sub>     | $V_{DS} = 800 \text{ V}, V_{GS} = -5 / +18 \text{ V}$                                            |        | 15   |          |       |            |

| Gate-Drain Charge                                                             | Q <sub>gd</sub>     | I <sub>D</sub> = 13 A                                                                            |        | 16   |          | nC    | Fig. 11    |

| Total Gate Charge                                                             | Qg                  | Per JEDEC JEP-192                                                                                |        | 55   |          |       |            |

| Internal Gate Resistance                                                      | R <sub>G(int)</sub> | V <sub>GS</sub> = 18 V, f = 1 MHz, V <sub>AC</sub> = 25 mV                                       |        | 1.3  |          | Ω     |            |

| Turn-On Switching Energy<br>(Body Diode)                                      | E <sub>On</sub>     | $T_i = 25$ °C, $V_{GS} = -5/+18$ V, $R_{G(ext)} = 8 \Omega$ , L =                                |        | 1    | F: 04 07 |       |            |

| Turn-Off Switching Energy<br>(Body Diode)                                     | E <sub>Off</sub>    | 80.0 μH, I <sub>D</sub> = 20 A, V <sub>DD</sub> = 600 V                                          |        | 25   |          | μJ    | Fig. 24-27 |

| Turn-On Delay Time                                                            | t <sub>d(on)</sub>  |                                                                                                  |        | 24   |          |       | Fig. 26    |

| Rise Time                                                                     | t <sub>r</sub>      | $V_{DD} = 800 \text{ V}, V_{GS} = -5/+18 \text{ V}$                                              |        | 15   |          |       |            |

| Turn-Off Delay Time                                                           | t <sub>d(off)</sub> | $R_{G(ext)} = 8 \Omega$ , L = 80.0 μH, $I_D = 20 A$ Timing relative to $V_{DS}$ , Inductive load |        | 17   |          | ns    |            |

| Fall Time                                                                     | t <sub>f</sub>      | - Tilling relative to VDS, inductive load                                                        |        | 10   |          |       |            |

Note 3: Tested after applying 30ms pulse at Vgs= +25V

Note 4:  $C_{o(er)}$ , a lumped capacitance that gives same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 800V.  $C_{o(tr)}$ , a lumped capacitance that gives same charging times as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 800V.

Rev 24/Jul Page 2 of 14

| Reverse Diode Characteristics    |                       |                                                                                                                                                |      |        |      |      |            |

|----------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|------|------------|

| Parameter                        | Symbol                | Conditions                                                                                                                                     |      | Values |      |      | Note       |

|                                  | Syllibol              | Conditions                                                                                                                                     | Min. | Тур.   | Max. | Unit | Note       |

| Diode Forward Voltage            | $V_{SD}$              | $V_{GS}$ = -5 V, $I_{SD}$ = 6 A                                                                                                                |      | 4.1    |      | ٧    | Fig. 18-19 |

|                                  | VSD                   | $V_{GS}$ = -5 V, $I_{SD}$ = 6 A, $T_j$ = 175°C                                                                                                 |      | 3.6    |      | V    | Fig. 10-19 |

| Continuous Diode Forward Current | Is                    | $V_{GS} = -5 \text{ V, } T_c = 100^{\circ}\text{C}$                                                                                            |      |        | 16   | ٨    |            |

|                                  |                       | $V_{GS} = -5 \text{ V, } T_c = 25^{\circ}\text{C}$                                                                                             |      | 26     | Α    |      |            |

| Diode Pulse Current              | I <sub>S(pulse)</sub> | V <sub>GS</sub> = -5 V                                                                                                                         |      | 64     |      | Α    | Note 2     |

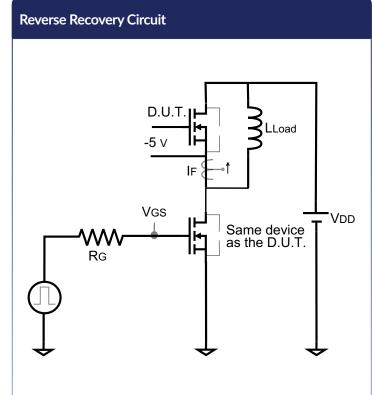

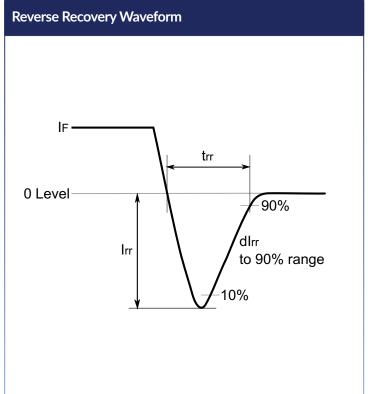

| Reverse Recovery Time            | t <sub>rr</sub>       | V 5VI 10 A V 000 V                                                                                                                             |      | 15     |      | ns   |            |

| Reverse Recovery Charge          | Qrr                   | $V_{GS} = -5 \text{ V, } I_{SD} = 13 \text{ A, } V_R = 800 \text{ V}$<br>$dif/dt = 1000 \text{ A/}\mu\text{s, } T_i = 25^{\circ}\text{C}$      |      | 64     |      | nC   |            |

| Peak Reverse Recovery Current    | Irrm                  | uii/ut - 1000 A/μs, 1 <sub>J</sub> - 25 C                                                                                                      |      | 4.6    |      | Α    |            |

| Reverse Recovery Time            | t <sub>rr</sub>       | V 5VI 10.1 V 2001                                                                                                                              |      | 23     |      | ns   |            |

| Reverse Recovery Charge          | Q <sub>rr</sub>       | $V_{GS} = -5 \text{ V, } I_{SD} = 13 \text{ A, } V_{R} = 800 \text{ V}$<br>$dif/dt = 1000 \text{ A/}\mu\text{s, } T_{i} = 175^{\circ}\text{C}$ |      | 160    |      | nC   |            |

| Peak Reverse Recovery Current    | I <sub>rrm</sub>      | uii/ut - 1000 A/μs, 1 <sub>J</sub> - 175 C                                                                                                     |      | 7      |      | Α    |            |

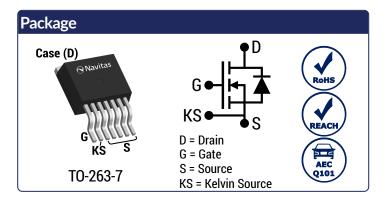

| Package Characteristics                 |                       |            |        |      |         |

|-----------------------------------------|-----------------------|------------|--------|------|---------|

| Parameter                               | Symbol                | Conditions | Values | Unit | Note    |

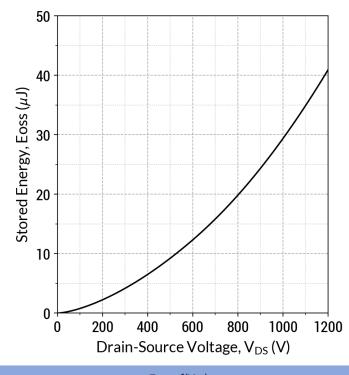

| Max Thermal Resistance, Junction - Case | R <sub>thJC-Max</sub> | Maximum    | 0.93   | °C/W | Fig. 14 |

| Weight                                  | $\mathbf{W}_{T}$      |            | 1.45   | g    |         |

| Moisture Sensitivity Level              | MSL                   |            | 1      |      |         |

| EMC Material Group                      |                       |            | II     |      |         |

Rev 24/Jul Page 3 of 14

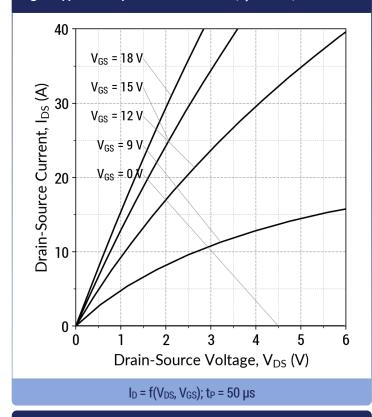

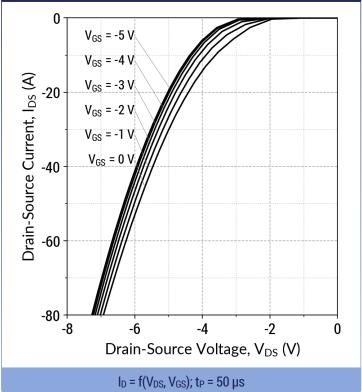

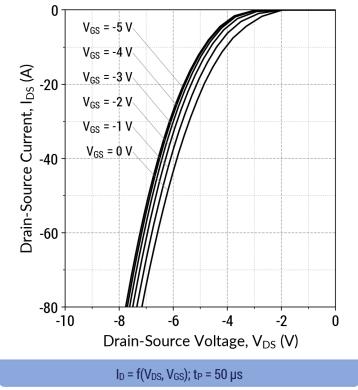

Fig 1: Typical Output Characteristics ( $T_j = 25$ °C)

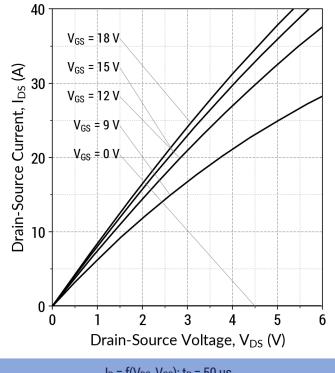

Fig 2: Typical Output Characteristics ( $T_j = 175$ °C)

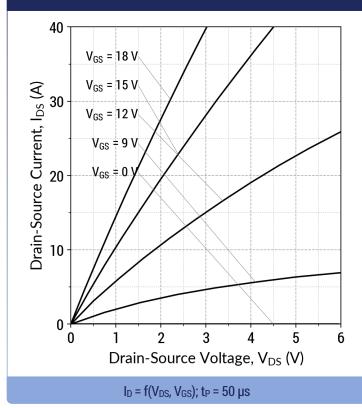

$I_D = f(V_{DS}, V_{GS}); t_P = 50 \mu s$

Fig 3: Typical Output Characteristics (T<sub>j</sub> = -55°C)

Fig 4: Typical Output Characteristics (V<sub>GS</sub> = 18 V)

Rev 24/Jul Page 4 of 14

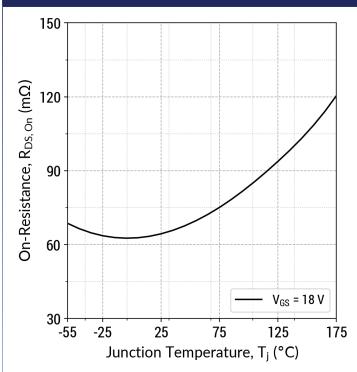

Fig 6: Typical R<sub>DS(ON)</sub> v/s Temperature

$R_{DS(ON)} = f(T_j, V_{GS}); t_P = 50 \mu s; I_D = 13 A$

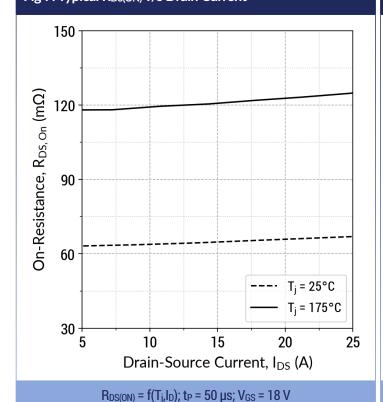

Fig 7: Typical RDS(ON) v/s Drain Current

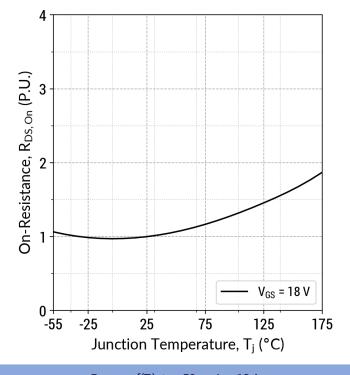

Fig 8: Typical Normalized RDS(ON) v/s Temperature

$R_{DS(ON)} = f(T_j); t_P = 50 \mu s; I_D = 13 A$

Rev 24/Jul Page 5 of 14

$R_{DS(ON)} = f(T_i, V_{GS}); t_P = 50 \mu s; I_D = 13 A$

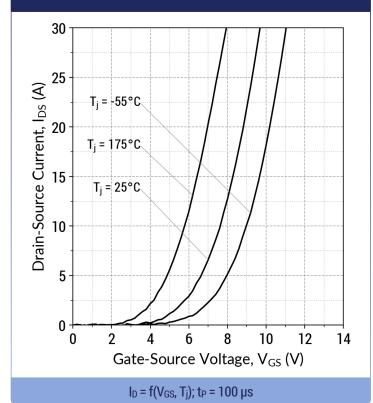

Fig 10: Typical Threshold Voltage Characteristics

$V_{GS(th)} = f(T_j)$ ;  $V_{DS} = V_{GS}$ ;  $I_D = 10 \text{ mA}$

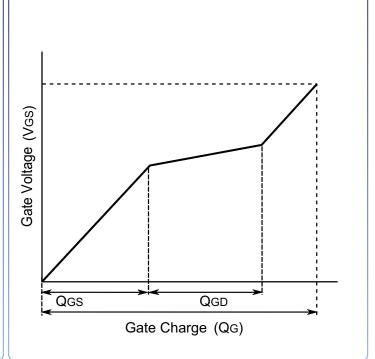

Fig 11: Typical Gate Charge Characteristics

Fig 12: Typical Capacitance v/s Drain-Source Voltage

Rev 24/Jul Page 6 of 14

$E_{oss} = f(V_{DS})$

## Fig 14: Max. Transient Thermal Impedance

$Z_{th,ic} = f(t_P,D); D = t_P/T$

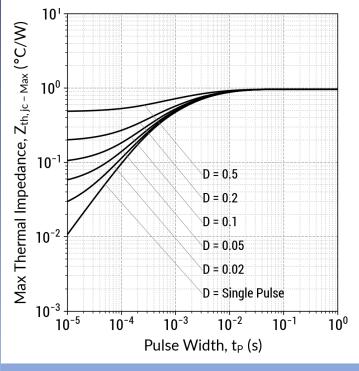

## Fig 15: Safe Operating Area ( $T_c = 25^{\circ}C$ )

$I_D = f(V_{DS}, t_P); T_i \le 175^{\circ}C; D = 0$

## Fig 16: Current De-rating Curve

Rev 24/Jul Page 7 of 14

Fig 18: Typical Body Diode Characteristics ( $T_j = 25$ °C)

Fig 19: Typical Body Diode Characteristics ( $T_j = 175$ °C)

Fig 20: Typical Body Diode Characteristics ( $T_j = -55$ °C)

Rev 24/Jul Page 8 of 14

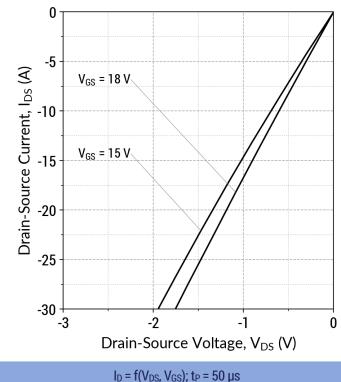

Fig 21: Typical Third Quadrant Characteristics ( $T_j = 25$ °C)

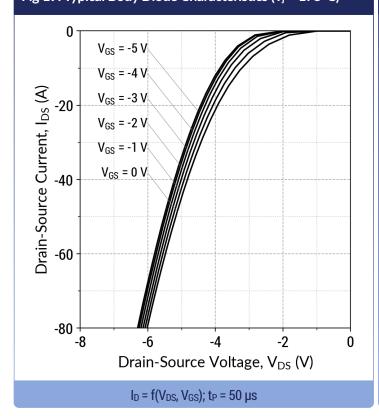

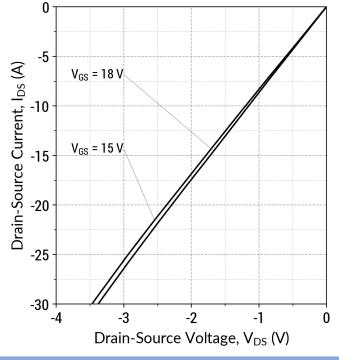

## Fig 22: Typical Third Quadrant Characteristics ( $T_j = 175^{\circ}$ C)

$I_D = f(V_{DS}, V_{GS}); t_P = 50 \mu s$

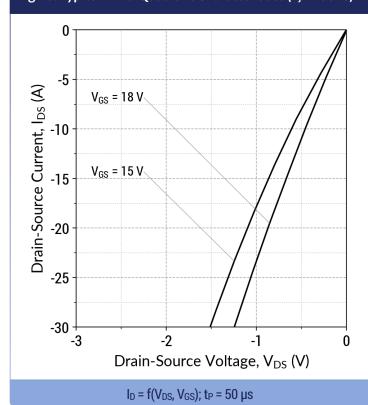

Fig 23: Typical Third Quadrant Characteristics (T<sub>j</sub> = -55°C)

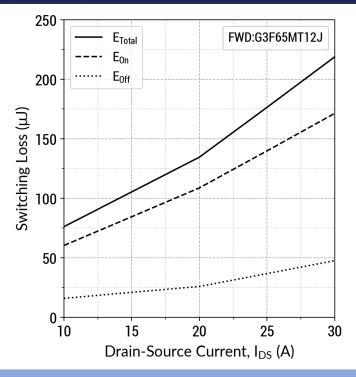

Fig 24: Inductive Switching Energy v/s Drain Current  $(V_{DD} = 600V)$

$T_i = 25$ °C;  $V_{GS} = -5/+18V$ ;  $R_{G(ext)} = 8 \Omega$ ;  $L = 80.0 \mu H$

Rev 24/Jul Page 9 of 14

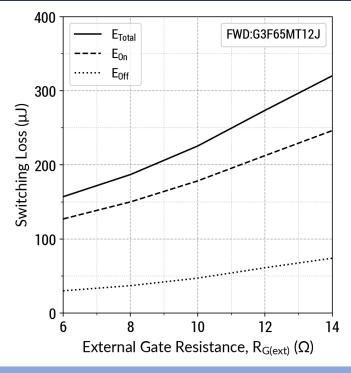

$T_i = 25$ °C;  $V_{GS} = -5/+18V$ ;  $I_{DS} = 20$  A;  $L = 80.0 \mu H$

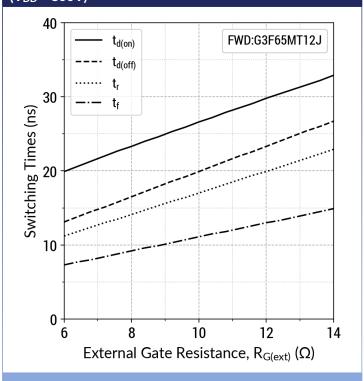

# Fig 26: Switching Time v/s R<sub>G(ext)</sub> (V<sub>DD</sub> = 800V)

$T_i = 25$ °C;  $V_{GS} = -5/+18V$ ;  $I_{DS} = 20$  A;  $L = 80.0 \mu H$

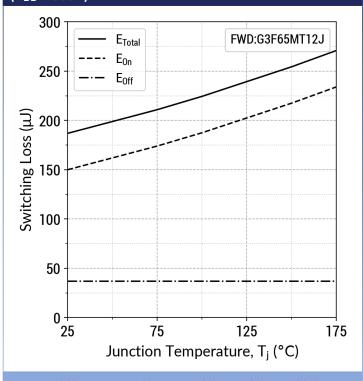

# Fig 27: Inductive Switching Energy v/s Temperature $(V_{DD} = 800V)$

$T_j$  = 25°C;  $V_{GS}$  = -5/+18V;  $R_{G(ext)}$  = 8  $\Omega$ ;  $I_{DS}$  = 20 A; L = 80.0 $\mu$ H

Rev 24/Jul Page 10 of 14

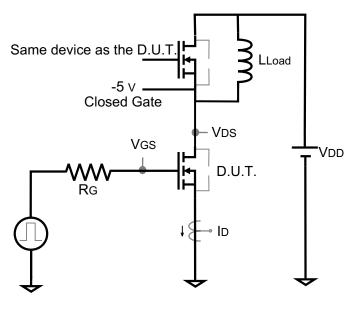

## **Dynamic Test Circuit**

Note: Gate Charge, Switching Time and Energy Circuit

## Gate Charge Waveform

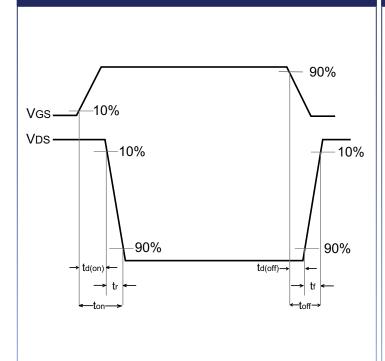

## **Switching Time Waveform**

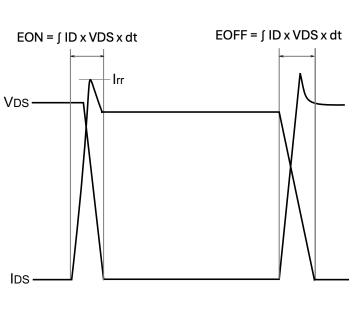

## **Switching Energy Waveform**

Rev 24/Jul Page 11 of 14

Rev 24/Jul Page 12 of 14

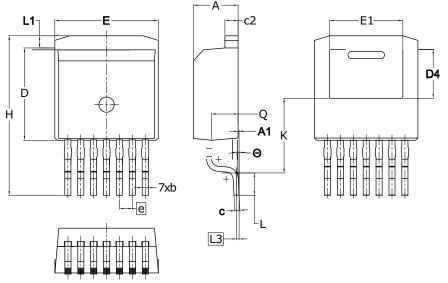

## **Package Dimensions**

## **TO-263-7 Package Outline**

- All Dimensions Are In mm.

Dimension D & E Do Not Include Mold Flash.

These Dimensions Are Measured At The Outermost

- Extreme Of The Plastic Body.

3. Thermal Pad Contour Optional Within Dimensions E, L1, D4 & E1.

4. Dimension D4 & E1 Establish A Minmum Mounting Surface for

- The Thermal Pad.

5. is Exposed Cu.

- 6. There is Exposed Cu and Molding Flash Bleeding At The Pin Which is Close To Package.

| SYMBOL | DIMENSIONS |      |  |  |  |

|--------|------------|------|--|--|--|

| STMBOL | MIN.       | MAX. |  |  |  |

| Α      | 4.30       | 4.50 |  |  |  |

| A1     | 0.00       | 0.25 |  |  |  |

| b      | 0.50       | 0.70 |  |  |  |

| С      | 0.45 0.    |      |  |  |  |

| c2     | 1.20 1.4   |      |  |  |  |

| D      | 8.93 9.3   |      |  |  |  |

| D4     | 4.65 4.    |      |  |  |  |

| Е      | 10.08 10   |      |  |  |  |

| E1     | 6.82 7.6   |      |  |  |  |

| е      | 1.27 BSC   |      |  |  |  |

| Н      | 15.00 16   |      |  |  |  |

| К      | 7.30       |      |  |  |  |

| L      | 1.90 2.5   |      |  |  |  |

| L1     | 1.00 1.40  |      |  |  |  |

| L3     | 0.25 BSC   |      |  |  |  |

| Q      | 2.45 2.75  |      |  |  |  |

| Θ      | 0° 7°      |      |  |  |  |

#### NOTE

- 1. CONTROLLED DIMENSION IS MILLIMETER.

- 2. DIMENSIONS DO NOT INCLUDE END FLASH, MOLD FLASH, MATERIAL PROTRUSIONS.

- 3. THE SOURCE AND KELVIN-SOURCE PINS ARE NOT INTERCHANGABLE. THEIR EXCHANGE MIGHT LEAD TO MALFUNCTION.

Rev 24/Jul Page 13 of 14

### **Revision History**

Rev 24/Jul: Initial Release (Rev 1.0)

#### IMPORTANT NOTICES AND DISCLAIMERS

EXCEPT TO THE EXTENT THAT INFORMATION IN THIS DATA SHEET IS EXPRESSLY AND SPECIFICALLY WARRANTED IN WRITING BY NAVITAS SEMICONDUCTOR ("NAVITAS"), EITHER PURSUANT TO THE TERMS AND CONDITIONS OF THE LIMITED WARRANTY CONTAINED IN NAVITAS' STANDARD TERMS AND CONDITIONS OF SALE OR A WRITTEN AGREEMENT SIGNED BY AN AUTHORIZED NAVITAS REPRESENTATIVE, (1) ALL INFORMATION IN THIS DATA SHEET OR OTHER RELIABILITY AND TECHNICAL DATA, AND ANY OTHER DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE OR TOOLS, SAFETY INFORMATION AND OTHER RESOURCES, ARE PROVIDED "AS IS" AND WITH ALL FAULTS; AND (2) NAVITAS MAKES NO WARRANTIES OR REPRESENTATIONS AS TO ANY SUCH INFORMATION OR RESOURCES, IN THIS DATA SHEET OR OTHERWISE, AND HEREBY DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

CUSTOMER RESPONSIBILITIES. This data sheet and other design resources and information provided by Navitas are intended only for technically trained and skilled developers designing with Navitas- or GeneSiC-branded products ("Products"). Performance specifications and the operating parameters of Products described herein are determined in the independent state and may not perform the same way when installed in customer products. The customer (or other user of this data sheet) is solely responsible for (a) designing, validating and testing the application in which Products are incorporated; (b) designing, validating and testing the application in which Products are incorporated; (c) ensuring the application meets applicable standards and any safety, security, regulatory or other requirements; (d) evaluating the suitability of Products for the intended application and the completeness of the information in this data sheet with respect to such application; (e) procuring and/or developing production firmware, if applicable; and (f) completing system qualification, compliance and safety testing, EMC testing, and any automotive, high-reliability or other system qualifications that apply.

NON-AUTHORIZED USES OF PRODUCTS. Except to the extent expressly provided in a writing signed by an authorized Navitas representative, Products are not designed, authorized or warranted for use in extreme or hazardous conditions; aircraft navigation, communication or control systems; aircraft power and propulsion systems; air traffic control systems; military, weapons, space-based or nuclear applications; life-support devices or systems, including but not limited to devices implanted into the human body and emergency medical equipment; or applications where product failure could lead to death, personal injury or severe property or environmental damage. The customer or other persons using Products in such applications without Navitas' agreement or acknowledgement, as set forth in a writing signed by an authorized Navitas representative, do so entirely at their own risk and agree to fully indemnify Navitas for any damages resulting from such improper use. In order to minimize risks associated with such applications, you should provide adequate design and operating safeguards.

CHANGES TO, AND USE OF, THIS DATA SHEET. This data sheet and accompanying information and resources are subject to change without notice. Navitas grants you permission to use this data sheet and accompanying resources only for the development of an application that uses the Products described herein and subject to the notices and disclaimers set forth above. Any other use, reproduction or display of this data sheet or accompanying resources and information is prohibited. No license is granted to any Navitas intellectual property right or to any third-party intellectual property right. Navitas disclaims any responsibility for, and you will fully indemnify Navitas and its representatives against, any claims, damages, costs, losses and liabilities arising out of your use of this data sheet and any accompanying resources and information.

TERMS AND CONDITIONS. All purchases and sales of Products are subject to <u>Navitas' Standard Terms and Conditions of Sale</u>, including the limited warranty contained therein, unless other terms and conditions have been agreed in a writing signed by an authorized Navitas representative. This data sheet, and Navitas' provision of this data sheet or other information and resources, do not expand or otherwise alter those terms and conditions.

Navitas, GeneSiC, the Navitas and GeneSiC logos, GaNFast, GaNSafe, SICPAK and other Navitas marks used herein are trademarks or registered trademarks of Navitas Semiconductor Limited or its affiliates. Other trademarks used herein are the property of their respective owners.

Copyright © 2024 Navitas Semiconductor Limited and affiliates. All rights reserved.

Rev 24/Jul Page 14 of 14

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Navitas Semiconductor:

G3F65MT12J-TR