# AK4499EX Premium Switched Resistor Stereo DAC

# 1. General Description

The AK4499EX is a new concept Premium multi-bit Stereo DAC with newly developed Switched Resistor technology, achieving the industry's leading level low distortion and low noise characteristics. It is suitable for playback of high-resolution audio sources that are becoming widespread in Network Audio and USB-DACs Audio systems. Multi-bit Modulator input for a high-precision audio source playback.

Application: AV Receivers, CD/SACD player, Network Audios, USB DACs, USB Headphones, Measurement Equipment, Control Systems, Public Audios (PA)

| 2. Features                                                                                |

|--------------------------------------------------------------------------------------------|

| Stereo Switched Resistor DAC                                                               |

| • THD+N: -124 dB                                                                           |

| <ul> <li>Dynamic Range, S/N: 138 dB (135 dB @Stereo)</li> </ul>                            |

| Multi-bit Modulator Data Interface with 5.6448, 11.2896 MHz Clock     7-bit Modulator Data |

| • Mono Mode                                                                                |

| Power Supply:                                                                              |

| TVDD = DVDD to 3.6 V, DVDD = 1.7 to 1.98 V,                                                |

| AVDD = 4.75 to 5.25 V, VDDL/R = 4.75 to 5.25 V                                             |

| Digital Input Level: CMOS                                                                  |

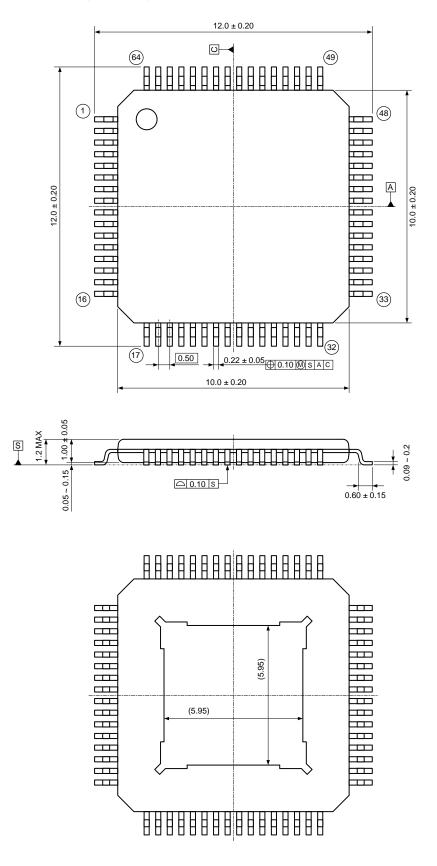

| Package: 64-pin HTQFP                                                                      |

| • Temperature: -40 to 85 °C                                                                |

# 3. Table of Contents

| 1. General Description                                                      | 1  |

|-----------------------------------------------------------------------------|----|

| 2. Features                                                                 | 1  |

| 3. Table of Contents                                                        |    |

| 4. Block Diagram and Functions                                              | 3  |

| 4.1. Block Diagram                                                          | 3  |

| 4.2. Functions                                                              |    |

| 5. Pin Configurations and Functions                                         |    |

| 5.1. Pin Configurations                                                     |    |

| 5.2. Pin Functions                                                          |    |

| 5.3. Handling of Unused Pin                                                 |    |

| 5.4. Pull-up, Pull-down Pin List                                            |    |

| 6. Absolute Maximum Ratings                                                 | 9  |

| 7. Recommended Operating Conditions                                         |    |

| 8. Electrical Characteristics                                               |    |

| 8.1. Analog Characteristics                                                 |    |

| 8.2. DC Characteristics                                                     |    |

| 8.3. Switching Characteristics                                              |    |

| 8.4. Timing Diagram                                                         |    |

| 9. Functional Descriptions                                                  |    |

| 9.1. Sampling Speed mode Setting                                            | 22 |

| 9.2. System Clock                                                           |    |

| 9.3. Audio Inerface Format                                                  |    |

| 9.4. Multi-Bit Interface Mode Select, Output Signal Select                  | 26 |

| 9.5. Phase Inversion Function (Register Control Mode)                       |    |

| 9.6. Sound Control                                                          |    |

| 9.7. Power Up Sequence of External Operational Amplifier for I-V Conversion | 29 |

| 9.8. Power Up/Down Function                                                 |    |

| 9.9. Internal State                                                         |    |

| 9.10. Register Control Interface                                            |    |

| 9.11. Register Map                                                          |    |

| 9.12. Register Definitions                                                  |    |

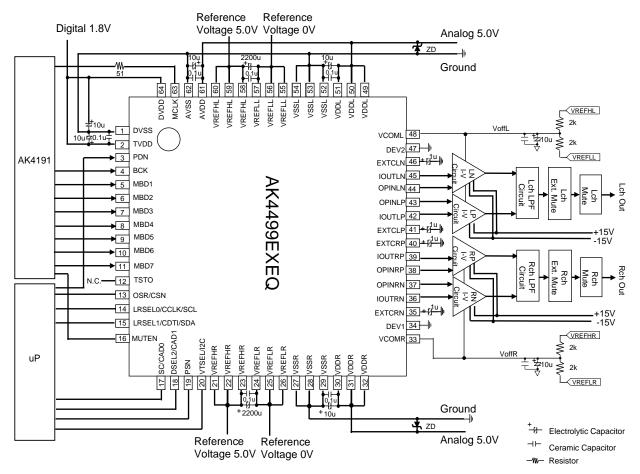

| 10. Recommended External Circuits                                           |    |

| 10.1. External Connection Example                                           |    |

| 10.2. Grounding and Power Supply Decoupling                                 |    |

| 10.3. Reference Voltage                                                     |    |

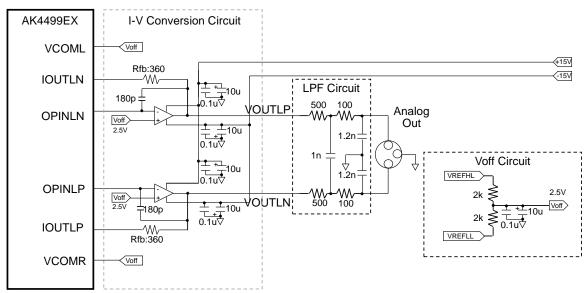

| 10.4. Analog Output                                                         |    |

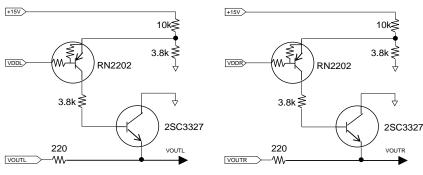

| 10.5. External Mute Circuit                                                 |    |

| 11. Package                                                                 |    |

| 11.1. Outline Dimensions                                                    |    |

| 11.2. Material & Terminal Finish                                            |    |

| 11.3. Marking                                                               |    |

| 12. Ordering Guide                                                          |    |

| 13. Revision History                                                        |    |

| IMPORTANT NOTICE                                                            | 54 |

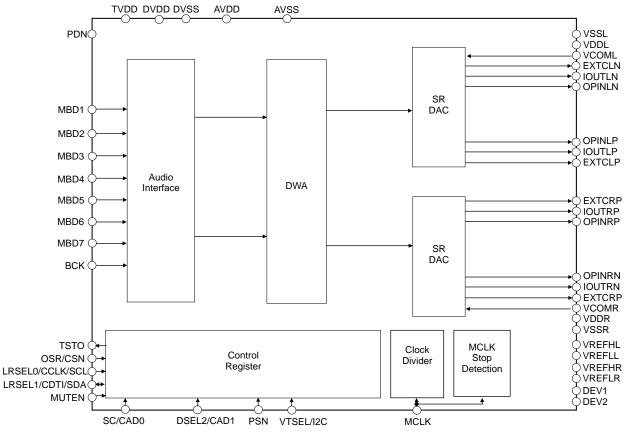

## 4. Block Diagram and Functions

#### 4.1. Block Diagram

Figure 1. Block Diagram

# 4.2. Functions

| Block               | Functions                                                                                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Audio Interface     | BCK is used to clock MBD7-1 data into the shift register.                                                                                                       |

| DWA                 | Processing two's complement MBD7-1 data by Data Weighted Average.                                                                                               |

| SR DAC              | Converting MBD7-1 data from DWA output to analog signal and that is designed by Switched Resistor DAC.                                                          |

| Control Register    | Internal registers keep its settings for each mode. Control registers are accessed in 3-wire (CSN, CCLK, CDTI) or I <sup>2</sup> C-Bus (SCL, SDA) control mode. |

| Clock Divider       | Generates the clock for SR DAC from the input clock of the MCLK pin.                                                                                            |

| MCLK Stop Detection | Detects when the master clock input is absent.                                                                                                                  |

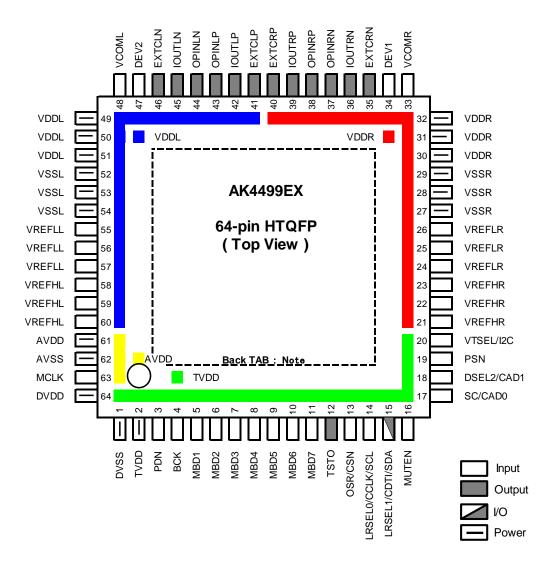

5. Pin Configurations and Functions

#### 5.1. Pin Configurations

Note. The exposed pad on the bottom surface of the package must be connected to ground.

#### 5.2. Pin Functions

| No. | Pin Name | I/O | Protection<br>Diode | Function                                                                                                                                                   | Power Down<br>State                     |

|-----|----------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1   | DVSS     | -   | -                   | Digital Ground Pin.                                                                                                                                        | -                                       |

| 2   | TVDD     | -   |                     | Digital Power Supply Pin, DVDD to 3.6 V.                                                                                                                   | -                                       |

| 3   | PDN      | I   | TVDD/DVSS           | Power Up, Power Down Pin.<br>When at "L", the AK4499EX is in power down state<br>and is held in reset. The AK4499EX must always<br>be reset upon power up. | Hi-Z<br>(PDN = "L")                     |

| 4   | BCK      |     | TVDD/DVSS           | Multi-Bit Data Clock Pin.                                                                                                                                  | Hi-Z                                    |

| 5   | MBD1     | -   | TVDD/DVSS           | Multi-Bit Data1 Input Pin.                                                                                                                                 | Hi-Z                                    |

| 6   | MBD2     | - 1 | TVDD/DVSS           | Multi-Bit Data2 Input Pin.                                                                                                                                 | Hi-Z                                    |

| 7   | MBD3     |     | TVDD/DVSS           | Multi-Bit Data3 Input Pin.                                                                                                                                 | Hi-Z                                    |

| 8   | MBD4     |     | TVDD/DVSS           | Multi-Bit Data4 Input Pin.                                                                                                                                 | Hi-Z                                    |

| 9   | MBD5     |     | TVDD/DVSS           | Multi-Bit Data5 Input Pin.                                                                                                                                 | Hi-Z                                    |

| 10  | MBD6     |     | TVDD/DVSS           | Multi-Bit Data6 Input Pin.                                                                                                                                 | Hi-Z                                    |

| 11  | MBD7     |     | TVDD/DVSS           | Multi-Bit Data7 Input Pin.                                                                                                                                 | Hi-Z                                    |

| 12  | TSTO     | 0   | TVDD/DVSS           | Test Output Pin.                                                                                                                                           | Hi-Z                                    |

| 13  | OSR      | I   | TVDD/DVSS           | PSN pin = "H": Sampling Speed Mode Setting Pin<br>in Pin Control mode.<br>"L": OSR256 mode<br>"H": OSR128 mode                                             | Hi-Z                                    |

|     | CSN      | Ι   |                     | PSN pin = "L", I2C pin = "L": Chip Select Pin in<br>Register Control mode.                                                                                 |                                         |

|     | LRSEL0   | Ι   |                     | PSN pin = "H": Audio Interface Format Select and Data Select Pin in Pin Control mode.                                                                      |                                         |

| 14  | CCLK     | I   | TVDD/DVSS           | PSN pin = "L", I2C pin = "L": Control Data Clock<br>Pin in Register Control mode.                                                                          | Hi-Z                                    |

|     | SCL      | I   |                     | PSN pin = "L", I2C pin = "H": Control Data Clock<br>Input Pin                                                                                              |                                         |

|     | LRSEL1   | I   |                     | PSN pin = "H": Audio Interface Format Select and Data Select Pin in Pin Control mode.                                                                      |                                         |

| 15  | CDTI     | I   | TVDD/DVSS           | PSN pin = "L", I2C pin = "L": Control Data Input<br>Pin in Register Control mode.                                                                          | Hi-Z                                    |

|     | SDA      | I/O |                     | PSN pin = "L", I2C pin = "H": Control Data Input<br>Pin.                                                                                                   |                                         |

| 16  | MUTEN    | I   | TVDD/DVSS           | Mute State Select Pin.<br>"L": Mute<br>"H": Normal Operation                                                                                               | Hi-Z                                    |

| 17  | SC 17    |     | TVDD/DVSS           | PSN pin = "H": Sound Control in Pin Control<br>mode.<br>"L": Measurement mode<br>"H": Sound quality mode                                                   | Hi-Z                                    |

|     | CAD0     | Ι   |                     | PSN pin = "L": Chip Address 0 Pin in Register<br>Control mode.                                                                                             |                                         |

| 10  | DSEL2    | I   | TVDD/DVSS           | PSN pin = "H": Test Input Pin. Connect to TVDD<br>in Pin Control mode.                                                                                     | Hi-Z                                    |

| 18  | CAD1     | I   | 10000000            | PSN pin = "L": Chip Address 1 Pin in Register<br>Control mode.                                                                                             |                                         |

| 19  | PSN      | Ι   | TVDD/DVSS           | Pin control mode or Register Control mode<br>Select Pin. (Internal pull-up pin)<br>"L": Register control mode<br>"H": Pin Control mode                     | Pull-Up to<br>TVDD<br>(100 kΩ,<br>typ.) |

|    |        | - |           |                                                                                                                                                                                     |                                        |

|----|--------|---|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 20 | VTSEL  | I | TVDD/DVSS | PSN pin = "H": Digital input voltage level of MCLK<br>select pin in Pin Control Mode.<br>"L": High Level = 1.36 V, Low Level = 0.34 V<br>"H": High Level = 2.2 V, Low Level = 0.8 V | Hi-Z                                   |

|    | I2C    | Ι |           | PSN pin = "L": Register Control Interface Select<br>Pin in Register Control mode.                                                                                                   |                                        |

| 21 | VREFHR | Ι | VDDR/VSSR |                                                                                                                                                                                     | Hi-Z                                   |

| 22 | VREFHR | Ι | VDDR/VSSR | Rch High Level Voltage Reference Input Pin.                                                                                                                                         | Hi-Z                                   |

| 23 | VREFHR | - | VDDR/VSSR |                                                                                                                                                                                     | Hi-Z                                   |

| 24 | VREFLR | I | VDDR/VSSR |                                                                                                                                                                                     | Hi-Z                                   |

| 25 | VREFLR | Ι | VDDR/VSSR | Rch Low Level Voltage Reference Input Pin.                                                                                                                                          | Hi-Z                                   |

| 26 | VREFLR |   | VDDR/VSSR |                                                                                                                                                                                     | Hi-Z                                   |

| 27 | VSSR   | - | -         | Analog Ground Pin.                                                                                                                                                                  | -                                      |

| 28 | VSSR   | - | -         | Analog Ground Pin.                                                                                                                                                                  | -                                      |

| 29 | VSSR   | - | -         | Analog Ground Pin.                                                                                                                                                                  | -                                      |

| 30 | VDDR   | - | -         | Rch Analog Power Supply 5.0 V(typ.) Pin.                                                                                                                                            | -                                      |

| 31 | VDDR   | - | -         | Rch Analog Power Supply 5.0 V(typ.) Pin.                                                                                                                                            | -                                      |

| 32 | VDDR   | - | -         | Rch Analog Power Supply 5.0 V(typ.) Pin.                                                                                                                                            | -                                      |

| 33 | VCOMR  | Ι | VDDR/VSSR | Rch VCOM pin. VCOMR is connected to the midpoint of resistors between VREFHR and VREFLR.                                                                                            | Hi-Z                                   |

| 34 | DEV1   | I | VDDR/VSSR | Input Pin. Connect to Analog Ground. There is a Bidirectional Diode between DEV1 and VSSR.                                                                                          | Bidirectional<br>diode to<br>VSSR      |

| 35 | EXTCRN | 0 | VDDR/VSSR | External Capacitor Connect Pin. This Pin should<br>be connected to 1 μF to VSSR.<br>(Internal pull-down pin)                                                                        | Pull-Down to<br>VSSR<br>(250 kΩ, typ.) |

| 36 | IOUTRN | 0 | VDDR/VSSR | Current Output Pin. (Rch Negative Signal)                                                                                                                                           | Connected to<br>OPINRN<br>(30 Ω, typ.) |

| 37 | OPINRN | 0 | VDDR/VSSR | Rch Negative Analog Signal Output pin. Connect to negative input pin of External OPAMP for I-V Conversion.                                                                          | Connected to<br>IOUTRN<br>(30 Ω, typ.) |

| 38 | OPINRP | 0 | VDDR/VSSR | Rch Positive Analog Signal Output pin. Connect to negative input pin of External OPAMP for I-V Conversion.                                                                          | Connected to<br>IOUTRP<br>(30 Ω, typ.) |

| 39 | IOUTRP | 0 | VDDR/VSSR | Current Output Pin. (Rch Positive Signal)                                                                                                                                           | Connected to<br>OPINRP<br>(30 Ω, typ.) |

| 40 | EXTCRP | 0 | VDDR/VSSR | External Capacitor Connect Pin. This Pin should<br>be connected to 1 µF to VSSR.<br>(Internal pull-down pin)                                                                        | Pull-Down to<br>VSSR<br>(250 kΩ, typ.) |

| -  |         | - |           |                                                  |                        |

|----|---------|---|-----------|--------------------------------------------------|------------------------|

|    |         |   |           | External Capacitor Connect Pin. This Pin should  | Pull-Down to           |

| 41 | EXTCLP  | 0 | VDDL/VSSL | be connected to 1 $\mu$ F to VSSL.               | VSSL                   |

|    |         |   |           | (Internal pull-down pin)                         | (250 kΩ, typ.)         |

| 42 | IOUTLP  | 0 | VDDL/VSSL | Current Output Pin. (Lch Positive Signal)        | Connected to<br>OPINLP |

| 42 | IOUILF  | 0 | VDDL/V33L | Current Output Fin. (Lon Fositive Signal)        | (30 Ω, typ.)           |

|    |         |   |           | Lch Positive Analog Signal Output pin. Connect   | Connected to           |

| 43 | OPINLP  | 0 | VDDL/VSSL | to negative input pin of External OPAMP for I-V  | IOUTLP                 |

|    |         |   |           | Conversion.                                      | (30 Ω, typ.)           |

|    |         |   |           | Lch Negative Analog Signal Output pin. Connect   | Connected to           |

| 44 | OPINLN  | 0 | VDDL/VSSL | to negative input pin of External OPAMP for I-V  | IOUTLN                 |

|    |         |   |           | Conversion.                                      | (30 Ω, typ.)           |

| 45 |         | ( |           |                                                  | Connected to           |

| 45 | IOUTLN  | 0 | VDDL/VSSL | Current Output Pin. (Lch Negative Signal)        | OPINLN<br>(30 Ω, typ.) |

|    |         |   |           | External Capacitor Connect Pin. This Pin should  | Pull-Down to           |

| 46 | EXTCLN  | 0 | VDDL/VSSL | be connected to 1 µF to VSSL.                    | VSSL                   |

| -  | _       |   |           | (Internal pull-down pin)                         | (250 kΩ, typ.)         |

|    |         |   |           | Input Pin. Connect to Analog Ground. There is a  | Bidirectional          |

| 47 | DEV2    | I | VDDL/VSSL | Bidirectional Diode between DEV2 and VSSL.       | diode to               |

|    |         |   |           |                                                  | VSSL                   |

| 40 | VCOML   |   |           | Lch VCOM pin. VCOML is connected to the          | 11: 7                  |

| 48 | VCOIVIL | I | VDDL/VSSL | midpoint of resistors between VREFHL and VREFLL. | Hi-Z                   |

| 49 | VDDL    | - | _         | Lch Analog Power Supply 5.0 V(typ.) Pin.         | -                      |

| 50 | VDDL    | - |           | Lch Analog Power Supply 5.0 V(typ.) Pin.         |                        |

| 51 | VDDL    | - |           | Lch Analog Power Supply 5.0 V(typ.) Pin.         | -                      |

| 52 | VSSL    | - |           | Analog Ground Pin.                               | -                      |

| 53 | VSSL    | - |           | Analog Ground Pin.                               | -                      |

| 54 | VSSL    | - | _         | Analog Ground Pin.                               | _                      |

| 55 | VREFLL  | 1 | VDDL/VSSL |                                                  | Hi-Z                   |

| 56 | VREFLL  |   | VDDL/VSSL | Lch Low Level Voltage Reference Input Pin.       | Hi-Z                   |

| 57 | VREFLL  |   | VDDL/VSSL |                                                  | Hi-Z                   |

| 58 | VREFHL  | - | VDDL/VSSL |                                                  | Hi-Z                   |

| 59 | VREFHL  |   | VDDL/VSSL | Lch High Level Voltage Reference Input Pin.      | Hi-Z                   |

| 60 | VREFHL  |   | VDDL/VSSL |                                                  | Hi-Z                   |

| 61 | AVDD    | - | -         | Analog Power Supply 5.0 V(typ.) Pin.             | -                      |

| 62 | AVSS    | - | -         | Analog Ground Pin.                               | _                      |

| 63 | MCLK    | 1 | AVDD/AVSS | Master Clock Input Pin.                          | Hi-Z                   |

| 64 | DVDD    | - | -         | 1.8 V(typ.) Power Supply Pin.                    | -                      |

|    |         |   |           | The TAB on the bottom surface of the package     |                        |

| -  | TAB     | - | -         | should be connected to Ground.                   | -                      |

|    | 1       |   |           |                                                  |                        |

Note 1. All input pins except internal pull-up pins must not be left floating.

Note 2. The AK4499EX must be powered down by the PDN pin when changing Pin Control mode or Register Control mode by the PSN pin.

# 5.3. Handling of Unused Pin

Unused I/O pins must be connected appropriately.

#### Pin Control mode

| Classification | Pin Name                                                         | Setting |

|----------------|------------------------------------------------------------------|---------|

| Analog         | IOUTLP, IOUTLN, OPINLP, OPINLN<br>IOUTRP, IOUTRN, OPINRP, OPINRN | Open    |

| Digital        | TSTO                                                             | Open    |

Register Control mode (3-wire Serial Control Mode)

| Classification | Pin Name                                                         | Setting |

|----------------|------------------------------------------------------------------|---------|

| Analog         | IOUTLP, IOUTLN, OPINLP, OPINLN<br>IOUTRP, IOUTRN, OPINRP, OPINRN | Open    |

| Digital        | TSTO                                                             | Open    |

Register Control mode (I<sup>2</sup>C-Bus Control Mode)

| Classification | Pin Name                                                         | Setting         |

|----------------|------------------------------------------------------------------|-----------------|

| Analog         | IOUTLP, IOUTLN, OPINLP, OPINLN<br>IOUTRP, IOUTRN, OPINRP, OPINRN | Open            |

| Digital        | TSTO                                                             | Open            |

| Digital        | CSN                                                              | Connect to DVSS |

#### 5.4. Pull-up, Pull-down Pin List

| Classification                         | Pin name        | Internal connection |

|----------------------------------------|-----------------|---------------------|

| Pull-up pin (Typ. = 100 kΩ)            | PSN             | TVDD                |

| Dull down rin $(T_{1})$ = 250 k(0)     | EXTCLP, EXTCLN, | VSSL                |

| Pull-down pin (Typ. = 250 k $\Omega$ ) | EXTCRP, EXTCRN  | VSSR                |

#### 6. Absolute Maximum Ratings

(AVSS = DVSS = VSSL = VSSR = 0 V; Note 3, Note 4)

| Parameter                                    |                        | Symbol   | Min. | Max.                  | Unit |

|----------------------------------------------|------------------------|----------|------|-----------------------|------|

|                                              | Digital I/O            | TVDD     | -0.3 | 4.0                   | V    |

| Dowor Supplies                               | Digital Core           | DVDD     | -0.3 | 2.35                  | V    |

| Power Supplies                               | Clock Interface        | AVDD     | -0.3 | 5.55                  | V    |

|                                              | Analog                 | VDDL/R   | -0.3 | 5.55                  | V    |

| Power Supplies                               | VSSL, VSSR, AVSS, DVSS | ΔGND     | 0    | 0.3                   | V    |

| Differences                                  | VDDL, VDDR, AVDD       | ΔVD      | 0    | 0.3                   | V    |

|                                              |                        | VREFHL   | -0.3 | VDDL + 0.3 ≤ 5.55     | V    |

|                                              | High VREF              | VREFHR   | -0.3 | VDDR + 0.3 ≤ 5.55     | V    |

| Reference                                    | Low VREF               | VREFLL   | -0.3 | +0.3                  | V    |

| Voltage                                      |                        | VREFLR   | -0.3 | +0.3                  | V    |

|                                              | Common Voltage         | VCOML    | -0.3 | VDDL + 0.3 ≤ 5.55     | V    |

|                                              |                        | VCOMR    | -0.3 | VDDR + 0.3 ≤ 5.55     | V    |

| Input Current, Any Pin Except Power Supplies |                        | IIN      | _    | ±10                   | mA   |

| and Reference Voltage                        |                        |          | -    | 10                    |      |

| Analog Output Voltage                        |                        | VOUTA    | -0.3 | VDDL/R + 0.3 ≤ 5.55   | V    |

| IOUTLP/LN/RP/RN, OPINLP/LN/RP/RN             |                        | 100 // ( | 0.0  | VDDE/IC - 0.00 - 0.00 | •    |

| Input Voltage                                |                        | VDEV     | -0.3 | +0.3                  | V    |

| DEV1, DEV2                                   |                        |          |      |                       |      |

| Digital Input Voltage                        |                        | VIND     | -0.3 | TVDD + 0.3 ≤ 4.0      | V    |

| MCLK Input Voltage                           |                        | VINMCLK  | -0.3 | AVDD + 0.3 ≤ 5.55     | V    |

| Ambient Temperature (Power applied)          |                        | Та       | -40  | 85                    | °C   |

| Storage Tempera                              | Tstg                   | -65      | 150  | °C                    |      |

Note 3. All voltages with respect to ground.

Note 4. AVSS, DVSS, VSSL, VSSR and TAB must be connected to the ground.

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed above the recommended operating voltage.

#### 7. Recommended Operating Conditions

| ( | (AVSS = DVSS = VSSL = VSSR = 0 V; Note 3, Note 4) |  |

|---|---------------------------------------------------|--|

|   |                                                   |  |

| Parameter |                 | Symbol | Min.       | Тур.                | Max. | Unit |

|-----------|-----------------|--------|------------|---------------------|------|------|

|           | Digital I/O     | TVDD   | DVDD       | 1.8/3.3             | 3.6  | V    |

| Power     | Digital Core    | DVDD   | 1.7        | 1.8                 | 1.98 | V    |

| Supplies  | Clock Interface | AVDD   | 4.75       | 5.0                 | 5.25 | V    |

|           | Analog          | VDDL/R | 4.75       | 5.0                 | 5.25 | V    |

|           |                 | VREFHL | VDDL - 0.5 | -                   | VDDL | V    |

|           | High VREF       | VREFHR | VDDR - 0.5 | -                   | VDDR | V    |

| Reference |                 | VREFLL | -          | VSSL                | -    | V    |

| Voltage   | Low VREF        | VREFLR | -          | VSSR                | -    | V    |

|           | Common          | VCOML  | -          | (VREFHL + VREFLL)/2 | -    | V    |

|           | Voltage         | VCOMR  | -          | (VREFHR + VREFLR)/2 | -    | V    |

Note 5. VDDL, VDDR and AVDD must be connected to the same voltage line.

Note 6. VDDL/R must be supplied at the same time as or before VREFHL/R.

Note 7. Regarding external circuit power up sequence refers to 9.7. Power Up Sequence of External Operational Amplifier for I-V Conversion.

\* AKM assumes no responsibility for the usage beyond the conditions in this datasheet.

#### 8. Electrical Characteristics

#### 8.1. Analog Characteristics

#### OSR128 mode (OSR pin = "H" or OSR bit = "1")

(Ta = 25 °C; TVDD = 1.8 V, DVDD = 1.8 V, AVDD = 5.0 V, AVSS = DVSS = 0 V; VDDL/R = VREFHL/R = 5.0 V, VSSL/R = VREFLL/R = 0 V; VCOML/R = (VREFHL/R + VREFLL/R)/2; MCLK = 22.5792 MHz, Sampling Frequency = BCK = 5.6448 MHz; Measurement bandwidth = 20 Hz to 20 kHz; Signal Frequency = 1 kHz; Input Signal Level = 0.805 × Full-scale = 0 dBr (Note 8); External circuit Figure 31; SC pin = "L" or SC bit = "0"

| Parameter                |                       |                      |     | Тур. | Max. | Unit   |

|--------------------------|-----------------------|----------------------|-----|------|------|--------|

| Dynamic Cha              | aracteristics (Note   | 9)                   |     |      |      |        |

| BW = 20  kHz = 0  dBr    |                       | 0 dBr                | -   | -124 | -    | dB     |

| THD<br>(Note 10)         | BW = 40 kHz           | 0 dBr                | -   | -124 | -    | dB     |

|                          | BW = 80 kHz           | 0 dBr                | -   | -124 | -    | dB     |

|                          | BW = 20 kHz           | 0 dBr                | -   | -124 | -    | dB     |

|                          |                       | -60 dBr              | -   | -72  | -    | dB     |

| THD+N                    | BW = 40 kHz           | 0 dBr                | -   | -121 | -    | dB     |

| וידטחו                   |                       | -60 dBr              | -   | -69  | -    | dB     |

|                          | BW = 80 kHz           | 0 dBr                | -   | -118 | -    | dB     |

|                          |                       | -60 dBr              | -   | -66  | -    | dB     |

| Dynamic Ran              | ige (-60 dBr; A-weigh | ted)                 | -   | 135  | -    | dB     |

| S/N (A woigh             | ted) (Note 11)        | Stereo mode          | -   | 135  | -    | dB     |

| S/N (A-weigh             |                       | Mono mode (Note 12)  | -   | 138  | -    | dB     |

| Inter-channel            | Isolation (1 kHz)     |                      | 110 | 120  | -    | dB     |

| DC Accuracy              | /                     |                      |     |      |      |        |

| Inter-channel            | Gain Mismatch         |                      | -   | -    | 0.3  | dB     |

| Gain Drift               |                       |                      | -   | 100  | -    | ppm/°C |

| Differential O           | utput Current (IOUTF  | P - IOUTN) (Note 13) | -   | 72.8 | -    | mApp   |

| Center Current (Note 14) |                       |                      | -   | 0    | -    | mA     |

| Load Capacit             | ance (Analog Output   | Pins) (Note 15)      | -   | -    | 5    | pF     |

Note 8. 0 dBr is defined as 0.805 times the level of a 7-bit full-scale in two's complement format.

Note 9. The AK4191 is used as the input source with DSMSEL[1:0] bits = "00" and OBIT[1:0] bits = "00". Note 10. Absolute resistance error of subsequent stage circuits (Figure 31) recommended to be less

than 0.1 % to meet specifications.

Note 11. 2's complement "0" signal input.

Note 12. External circuits shown in Figure 32 are used in Mono mode.

Note 13. When the input signal is 0 dBr, the output current can be calculated by the following formula: IOUTL (Typ. @ 0 dBr) = (IOUTLP) - (IOUTLN) = 72.8 mApp × (VREFHL - VREFLL)/5. IOUTR (Typ. @ 0 dBr) = (IOUTRP) - (IOUTRN) = 72.8 mApp × (VREFHR - VREFLR)/5.

Note 14. Center current is the current that flows each IOUT pin during common output. When positive input of operational amplifier in I-V Conversion = VCOML/R = (VREFHL/R + VREFLL/R)/2

Note 15. The load capacitance value of analog output pins (IOUTLP/LN/RP/RN pins, OPINLP/LN/RP/RN pins) is with respect to ground. The load capacitance should be as small as possible. (Ta = 25 °C; TVDD = 1.8 V, DVDD = 1.8 V, AVDD = 5.0 V, AVSS = DVSS = 0 V; VDDL/R = VREFHL/R = 5.0 V, VSSL/R = VREFLL/R = 0 V; VCOML/R = (VREFHL/R + VREFLL/R)/2; MCLK = 22.5792 MHz, Sampling Frequency = BCK = 5.6448 MHz; Measurement bandwidth = 20 Hz to 20 kHz; Signal Frequency = 1 kHz; Input Signal Level = 0.805 × Full-scale = 0 dBr (Note 8); External circuit Figure 31

| Po | ower Supplies                                                                  |      |      |      |      |

|----|--------------------------------------------------------------------------------|------|------|------|------|

| Pa | rameter                                                                        | Min. | Тур. | Max. | Unit |

| Po | wer Supply Current                                                             |      |      |      |      |

|    | Normal operation (PDN pin = "H")                                               |      |      |      |      |

|    | VDDL + VDDR (Note 16)                                                          | -    | 12   |      | mA   |

|    |                                                                                | -    | (16) | -    | mA   |

|    | VREFHL + VREFHR                                                                | -    | 46   | -    | mA   |

|    | AVDD                                                                           | -    | 2    | -    | mA   |

|    | TVDD                                                                           | -    | 0.1  | -    | mA   |

|    | DVDD                                                                           | -    | 2    | -    | mA   |

|    | Total power dissipation<br>VDDL/R + VREFHL/R + AVDD + TVDD + DVDD              |      | 308  | -    | mW   |

|    | Power down (PDN pin = "L") (Note 17)<br>VDDL/R + VREFHL/R + AVDD + TVDD + DVDD | -    | 10   | 150  | μA   |

|    | Standby (Note 18)<br>VDDL/R + VREFHL/R + AVDD + TVDD + DVDD                    | -    | 1000 | -    | μA   |

Note 16. The values in () at VDDL/R total power supply current indicate consumption current when there is zero input data.

Note 17. In power down state, the PSN pin = TVDD and all other digital input pins including clock pins (MCLK, BCK) are connected to DVSS.

Note 18. In the standby mode, the external clock (MCLK, BCK) is input, and the other digital input pins are connected to DVSS. The standby mode is set to STBY bit = "1" in the register control mode.

# OSR256 mode (OSR pin = "L" or OSR bit = "0")

(Ta = 25 °C; TVDD = 1.8 V, DVDD = 1.8 V, AVDD = 5.0 V, AVSS = DVSS = 0 V; VDDL/R = VREFHL/R = 5.0 V, VSSL/R = VREFLL/R = 0 V; VCOML/R = (VREFHL/R + VREFLL/R)/2; MCLK = 22.5792 MHz, Sampling Frequency = BCK = 11.2896 MHz; Measurement bandwidth = 20 Hz to 20 kHz; Signal Frequency = 1 kHz; Input Signal Level = 0.805 × Full-scale = 0 dBr (Note 8); External circuit Figure 31; SC pin = "L" or SC bit = "0"

| Parameter                                             |                       |                     |   | Тур. | Max. | Unit   |

|-------------------------------------------------------|-----------------------|---------------------|---|------|------|--------|

| Dynamic Cha                                           | aracteristics (Note   | 9)                  |   |      |      |        |

| тир                                                   | BW = 20 kHz           | 0 dBr               | - | -116 | -    | dB     |

| THD<br>(Note 10)                                      | BW = 40 kHz           | 0 dBr               | - | -116 | -    | dB     |

|                                                       | BW = 80 kHz           | 0 dBr               | - | -116 | -    | dB     |

|                                                       | BW = 20 kHz           | 0 dBr               | - | -116 | -    | dB     |

|                                                       |                       | -60 dBr             | - | -71  | -    | dB     |

| THD+N                                                 | BW = 40 kHz           | 0 dBr               | - | -113 | -    | dB     |

| ויישחו                                                |                       | -60 dB              | - | -68  | -    | dB     |

|                                                       | BW = 80 kHz           | 0 dBr               | - | -110 | -    | dB     |

|                                                       | DVV - 00 KHZ          | -60 dBr             | - | -65  | -    | dB     |

| Dynamic Ran                                           | ge (-60 dBr; A-weight | ted)                | - | 134  | -    | dB     |

| S/N (A_weigh                                          | ted) (Note 11)        | Stereo mode         | - | 134  | -    | dB     |

| S/N (A-weigh                                          |                       | Mono mode (Note 12) | - | 137  | -    | dB     |

| Inter-channel                                         | Isolation (1 kHz)     |                     | - | 120  | -    | dB     |

| DC Accuracy                                           | /                     |                     |   |      |      |        |

| Inter-channel Gain Mismatch                           |                       |                     | - | -    | 0.3  | dB     |

| Gain Drift                                            |                       |                     | - | 100  | -    | ppm/°C |

| Differential Output Current (IOUTP - IOUTN) (Note 13) |                       |                     | - | 72.8 | -    | mApp   |

| Center Current (Note 14)                              |                       |                     | - | 0    | -    | mA     |

| Load Capacit                                          | ance (Analog Output   | Pins) (Note 15)     | - | -    | 5    | pF     |

(Ta = 25 °C; TVDD = 1.8 V, DVDD = 1.8 V, AVDD = 5.0 V, AVSS = DVSS = 0 V; VDDL/R = VREFHL/R = 5.0 V, VSSL/R = VREFLL/R = 0 V; VCOML/R = (VREFHL/R + VREFLL/R)/2; MCLK = 22.5792 MHz, Sampling Frequency = BCK = 11.2896 MHz; Measurement bandwidth = 20 Hz to 20 kHz; Signal Frequency = 1 kHz; Input Signal Level = 0.805 × Full-scale = 0 dBr (Note 8); External circuit Figure 31

| Ρον | wer Supplies                                                                   |      |      |      |      |

|-----|--------------------------------------------------------------------------------|------|------|------|------|

| Par | rameter                                                                        | Min. | Тур. | Max. | Unit |

| Pov | wer Supply Current                                                             |      |      |      |      |

|     | Normal operation (PDN pin = "H")                                               |      |      |      |      |

| Γ   |                                                                                | -    | 18   |      | mA   |

|     | VDDL+VDDR (Note 16)                                                            | -    | (24) | -    | mA   |

|     | VREFHL+VREFHR                                                                  | -    | 46   | -    | mA   |

|     | AVDD                                                                           | -    | 3    | -    | mA   |

|     | TVDD                                                                           | -    | 0.1  | -    | mA   |

|     | DVDD                                                                           | -    | 4    | -    | mA   |

|     | Total power dissipation<br>VDDL/R + VREFHL/R + AVDD + TVDD + DVDD              | -    | 343  | -    | mW   |

|     | Power down (PDN pin = "L") (Note 17)<br>VDDL/R + VREFHL/R + AVDD + TVDD + DVDD | -    | 10   | 150  | μA   |

|     | Standby (Note 18)<br>VDDL/R + VREFHL/R + AVDD + TVDD + DVDD                    | -    | 1000 | -    | μA   |

# 8.2. DC Characteristics

(Ta = -40 to 85 °C; VDDL/R = 4.75 to 5.25 V, AVDD = 4.75 to 5.25 V, TVDD = DVDD to 3.6 V, DVDD = 1.7 to 1.98 V; unless otherwise specified.)

| Parameter                                                                                                                               | Symbol         | Min.          | Тур. | Max.           | Unit   |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|------|----------------|--------|

| MCLK pin (Note 19)<br>(VTSEL pin = "L" or VTSEL bit = "0")<br>High-Level Input Voltage<br>Low-Level Input Voltage                       | VIHCK<br>VILCK | 1.36<br>-     | -    | -<br>0.34      | V<br>V |

| MCLK pin (Note 19)<br>(VTSEL pin = "H" or VTSEL bit = "1")<br>High-Level Input Voltage<br>Low-Level Input Voltage                       | VIHCK<br>VILCK | 2.2           | -    | -<br>0.8       | V<br>V |

| 1.7 V ≤ TVDD < 3.0 V (except MCLK pin)<br>High-Level Input Voltage<br>Low-Level Input Voltage                                           | VIH<br>VIL     | 80 %TVDD<br>- | -    | -<br>20 %TVDD  | V<br>V |

| $3.0 V \le TVDD \le 3.6 V$ (except MCLK pin)<br>High-Level Input Voltage<br>Low-Level Input Voltage                                     | VIH<br>VIL     | 70 %TVDD<br>- | -    | -<br>30 %TVDD  | V<br>V |

| Low-Level Output Voltage<br>(SDA pin, 2.0 V < TVDD $\leq$ 3.6 V: lout = 3 mA)<br>(SDA pin, 1.7 V $\leq$ TVDD $\leq$ 2.0 V: lout = 3 mA) | VOL<br>VOL     | -<br>-        | -    | 0.4<br>20%TVDD | V<br>V |

| Input Leakage Current (Note 20)                                                                                                         | lin            | -10           | -    | +10            | μA     |

Note 19. The VTSEL pin should be changed while the PDN pin is "L", and VTSEL bit should be changed while STBY bit = "1", MCLK is stopped with MSTBYN bit = "0", MUTEN pin = "L" or MUTEN bit = "0".

Note 20. The PSN pin has internal pull-up resistors. Therefore, the PSN pin is not included in this specification.

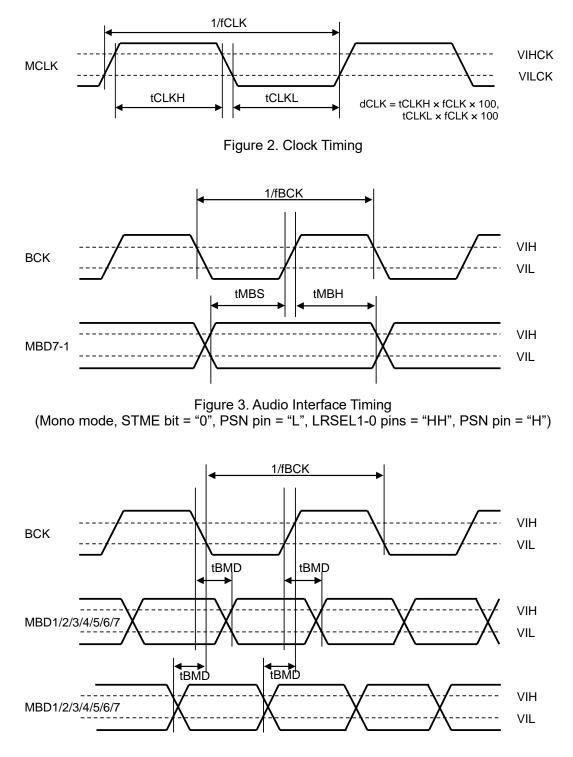

# 8.3. Switching Characteristics

(Ta = -40 to 85 °C; VDDL/R = 4.75 to 5.25 V, AVDD = 4.75 to 5.25 V, TVDD = DVDD to 3.6 V, DVDD = 1.7 to 1.98 V,  $C_L$  = 20 pF)

| Parameter |                                       | Symbol        | Min.           | Тур.        | Max    | Unit |

|-----------|---------------------------------------|---------------|----------------|-------------|--------|------|

| Maste     | er Clock Timing, 11.2896MHz (typ.)    |               |                |             |        |      |

|           | Frequency                             | fCLK          | 10             | 11.2896     | 13.824 | MHz  |

|           | Duty Cycle                            | dCLK          | 45             | 50          | 55     | %    |

| Maste     | er Clock Timing, 22.5792MHz (typ.)    |               |                |             |        |      |

|           | Frequency                             | fCLK          | 20             | 22.5792     | 27.648 | MHz  |

|           | Duty Cycle                            | dCLK          | 45             | 50          | 55     | %    |

| BCK       | Timing @ OSR pin = "H" or OSR bit =   | "1"           |                |             |        |      |

|           | Frequency                             | fBCK          | 5              | 5.6448      | 6.912  | MHz  |

|           | Duty Cycle                            | dBCK          | 45             | 50          | 55     | %    |

| BCK       | Timing @ OSR pin = "L" or OSR bit = " | "0"           |                |             |        |      |

|           | Frequency                             | fBCK          | 10             | 11.2896     | 13.824 | MHz  |

|           | Duty Cycle                            | dBCK          | 45             | 50          | 55     | %    |

| Frequ     | uency Ratio from MCLK to BCK @ OSP    | R pin = "H" c | or OSR bit = ' | "1"         |        |      |

|           | MCLK = 11.2896 MHz                    |               | -              | 2           | -      | -    |

|           | MCLK = 22.5792 MHz                    |               | -              | 4           | -      | -    |

| Frequ     | uency Ratio from MCLK to BCK @ OSF    | R pin = "L" o | r OSR bit = "  | <b>'0''</b> |        |      |

|           | MCLK = 11.2896 MHz                    |               | -              | 1           | -      | -    |

|           | MCLK = 22.5792 MHz                    |               | -              | 2           | -      | -    |

| Multi     | -bit Audio Interface Timing           |               |                |             |        |      |

|           | Multi-bit Mono mode                   |               |                |             |        |      |

|           | (STME bit = "0")                      |               |                |             |        |      |

|           | (LRSEL1-0 pins = "HH")                |               |                |             |        |      |

|           | MBD7-1 Hold Time                      | tMBH          | 5              | -           | -      | nsec |

|           | MBD7-1 Setup Time                     | tMBS          | 5              | -           | -      | nsec |

|           | Multi-bit Stereo mode                 |               |                |             |        |      |

|           | (STME bit = "1")                      |               |                |             |        |      |

|           | (LRSEL1-0 pins = "LL", "LH", "HL")    |               |                |             |        |      |

|           | BCK Edge to MBD7-1                    | tBMD          | -5             | -           | 5      | nsec |

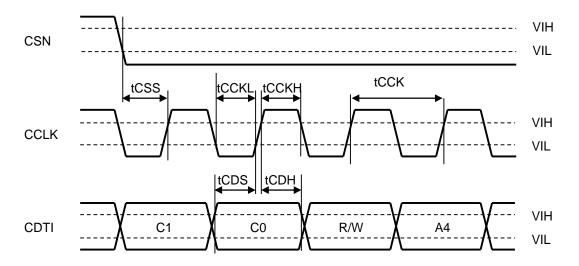

| Parameter                                                     | Symbol  | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------------|---------|------|------|------|------|

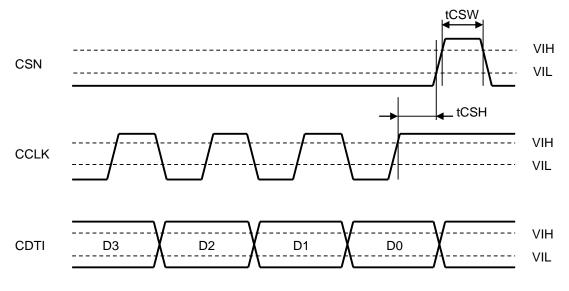

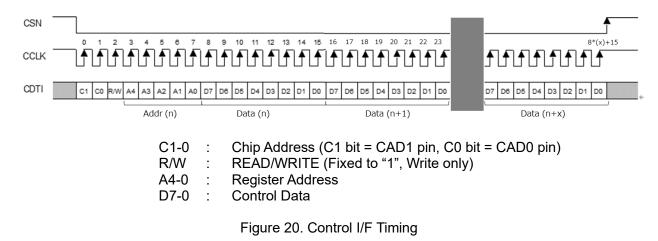

| Control Interface Timing (3-wire Serial Control Mode):        |         |      |      |      |      |

| CCLK Period                                                   | tCCK    | 200  | -    | -    | nsec |

| CCLK Pulse Width Low                                          | tCCKL   | 80   | -    | -    | nsec |

| Pulse Width High                                              | tCCKH   | 80   | -    | -    | nsec |

| CDTI Setup Time                                               | tCDS    | 40   | -    | -    | nsec |

| CDTI Hold Time                                                | tCDH    | 40   | -    | -    | nsec |

| CSN "H" Time                                                  | tCSW    | 150  | -    | -    | nsec |

| CSN "↓" to CCLK "↑"                                           | tCSS    | 50   | -    | -    | nsec |

| CCLK "↑" to CSN "↑"                                           | tCSH    | 50   | -    | -    | nsec |

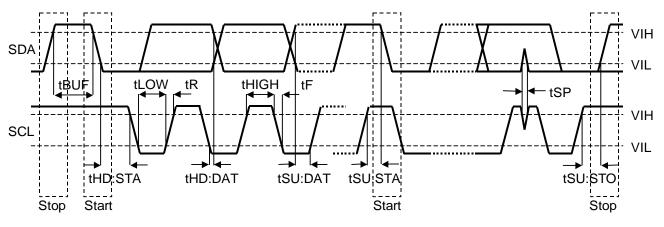

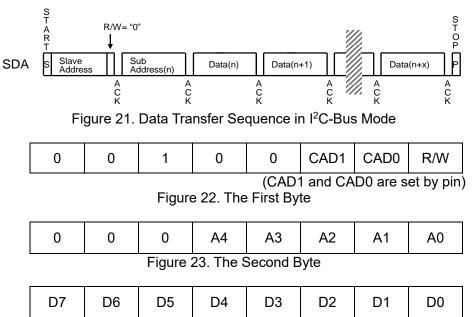

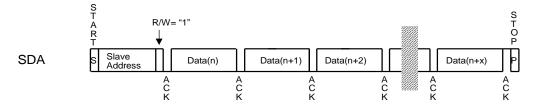

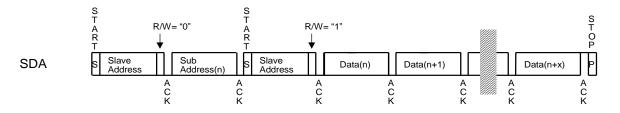

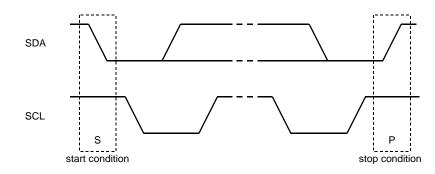

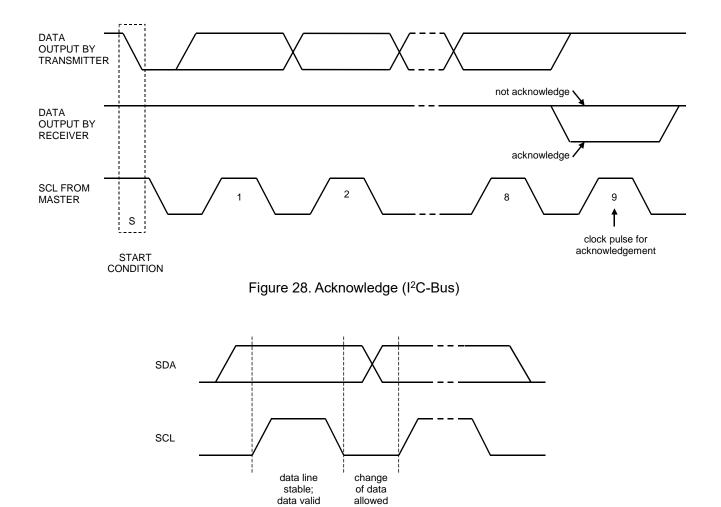

| Control Interface Timing (I <sup>2</sup> C-Bus Control Mode): |         |      |      |      |      |

| SCL Clock Frequency                                           | fSCL    | -    | -    | 400  | kHz  |

| Bus Free Time Between Transmissions                           | tBUF    | 1.3  | -    | -    | µsec |

| Start Condition Hold Time (prior to first clock pulse)        | tHD:STA | 0.6  | -    | -    | µsec |

| Clock Low Time                                                | tLOW    | 1.3  | -    | -    | µsec |

| Clock High Time                                               | tHIGH   | 0.6  | -    | -    | µsec |

| Setup Time for Repeated Start Condition                       | tSU:STA | 0.6  | -    | -    | µsec |

| SDA Hold Time from SCL Falling (Note 21)                      | tHD:DAT | 0    | -    | -    | µsec |

| SDA Setup Time from SCL Rising                                | tSU:DAT | 0.1  | -    | -    | µsec |

| Rise Time of Both SDA and SCL Lines                           | tR      | -    | -    | 0.3  | µsec |

| Fall Time of Both SDA and SCL Lines                           | tF      | -    | -    | 0.3  | µsec |

| Setup Time for Stop Condition                                 | tSU:STO | 0.6  | -    | -    | µsec |

| Pulse Width of Spike Noise Suppressed by Input Filter         | tSP     | 0    | -    | 50   | nsec |

| Capacitive load on bus                                        | Cb      | -    | -    | 400  | pF   |

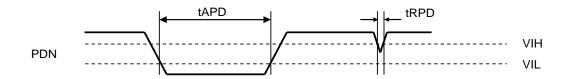

| Power down & Reset Timing (Note 22)                           |         |      |      |      |      |

| PDN Accept Pulse Width                                        | tAPD    | 600  | -    | -    | nsec |

| PDN Reject Pulse Width                                        | tRPD    | -    | -    | 30   | nsec |

Note 21. The data must be held for more than 300 nsec (the falling time of SCL). Note 22. The PDN pin must be held "L" for more than 600 nsec to ensure a reliable reset.

# 8.4. Timing Diagram

Figure 4. Audio Interface Timing (Stereo mode, STME bit = "1", PSN pin = "L", LRSEL1-0 pins = "LL", "LH", "HL", PSN pin = "H")

Figure 5. WRITE Command Input Timing

Figure 6. WRITE Data Input Timing

Figure 7. I<sup>2</sup>C-Bus mode Timing

Figure 8. Power Down & Reset Timing

#### 9. **Functional Descriptions**

Each function of the AK4499EX is controlled by pins (Pin Control mode) or registers (Register Control mode) (Table 1). Select the control mode by setting the PSN pin. The AK4499EX must be powered down by the PDN pin when changing the PSN pin setting. There is a possibility of malfunction if the device is not powered down when changing the control mode since the previous setting is not reinitialized.

Register settings are invalid in Pin Control mode, and pin settings are invalid in Register Control mode. Table 2 shows available functions of each control mode.

| la | Table T. PIN/Register Control Mode Sele |                       |  |  |  |  |  |

|----|-----------------------------------------|-----------------------|--|--|--|--|--|

|    | PSN pin                                 | Control Mode          |  |  |  |  |  |

|    | L                                       | Register Control mode |  |  |  |  |  |

|    | Н                                       | Pin Control mode      |  |  |  |  |  |

| Function                                | Pin Control mode        | Register Control mode |  |  |  |

|-----------------------------------------|-------------------------|-----------------------|--|--|--|

| Operation rates select<br>OSR256/OSR128 | OSR pin                 | OSR bit               |  |  |  |

| Stereo/Mono mode<br>Select              | LRSEL1-0 pins           | STME bit              |  |  |  |

| Output Signal Select                    |                         | LSELN, RSELN bit      |  |  |  |

| Sound Control                           | SC pin                  | SC bit                |  |  |  |

| VIH/L level select of<br>MCLK           | VTSEL pin               | VTSEL bit             |  |  |  |

| Phase Inversion                         | Not available (Note 23) | INVL/R bit            |  |  |  |

| On/off control of<br>standby by MCLK    | Not available (Note 24) | MSTBN bit             |  |  |  |

| MUTE Function                           | MUTEN pin               | MUTEN pin, MUTEN bit  |  |  |  |

#### Table 2 Function List Pin/Register Control Mode

Note 23. In Pin Control mode, the phase inversion function cannot be used. Note 24. In Pin Control mode, the standby function by MCLK is forced ON.

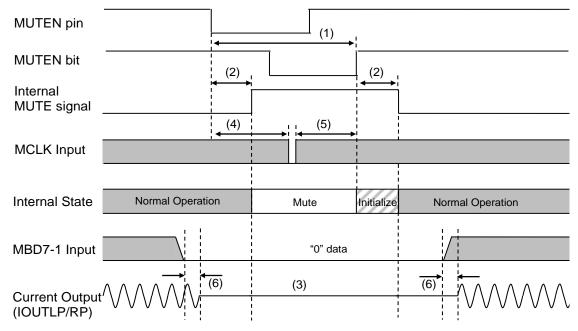

# 9.1. Sampling Speed mode Setting

The AK4499EX has two sampling speed mode, such as OSR256 mode and OSR128 mode. The AK4499EX is set OSR256 mode when setting OSR pin = "L" or OSR bit = "0", and it is set OSR128 mode when setting OSR pin = "H" or OSR bit = "1".

In case the data sample rate is changed with OSR pin or bit, the AK4499EX should be mute by MUTEN pin or bit to prevent output the noise from the AK4499EX. OSR pin or bit should be changed more than 50 µsec later MUTEN pin or bit signal down edge. MUTEN pin or bit signal should be turned up at 50 µsec later OSR pin or bit fixed setting and BCK clock frequency changing.

| MUTEN pin                                                    |                  | 4         | (1)      | ►¦                       |                  |

|--------------------------------------------------------------|------------------|-----------|----------|--------------------------|------------------|

| MUTEN bit<br>(in Register Control<br>Internal<br>MUTE signal | mode)            | (2)       |          | (2)                      |                  |

|                                                              |                  | (4)       | (5)      |                          |                  |

| BCK Input                                                    |                  |           |          |                          |                  |

|                                                              |                  | 1         | (5)      |                          |                  |

| OSR pin<br>or OSR bit                                        | Setting 1        |           | X        |                          | Setting 2        |

|                                                              |                  | <br> <br> | i        | i                        |                  |

| Internal State                                               | Normal Operation | on        | Mute     | Initialize               | Normal Operation |

| MBD7-1 Input                                                 |                  |           | "0" data |                          |                  |

| Current Output<br>(IOUTLP/RP)                                | ~/////           |           | (3)      | <br> <br> <br> <br> <br> |                  |

Notes:

- (1) Both MUTEN pin and MUTEN bit are enable in Register Control mode. The period of MUTEN pin = "L" or MUTEN bit = "0" must be 100 µsec or more continuously.

- (2) It takes up to 77 μsec until the internal MUTE signal is changed when changing MUTEN pin or MUTEN bit.

- (3) The AK4499EX output "0" data via Current Output pins (IOUTLP, IOUTLN, IOUTRP, IOUTRN) when the internal MUTE signal is "1".

- (4) MCLK frequency should be changed more than 77 µsec later from setting MUTEN pin = "L" or MUTEN bit = "0". This sequence avoids noisy data output caused by the frequency ratio of MCLK to BCK being out of the normal range.

- (5) When MUTEN is released, the initialization sequence is executed. The period between the switching of the BCK clock frequency or OSR setting and the release of MUTEN pin or MUTEN bit is at least 50 µsec to execute the initialization sequence correctly.

Figure 9. OSR pin and bit setting sequence

# 9.2. System Clock

The external clocks, which are required to operate the AK4499EX, are MCLK and BCK. In OSR256 mode, the MCLK speed is same or twice against BCK speed. In OSR128 mode, the MCLK speed is twice or quadruple against BCK speed. The AK4499EX will detect the MCLK and BCK frequency ratio to generate the internal operation clock from MCLK automatically. The phase between MCLK and BCK is not critical. The frequency of operating SR DAC is same as that of BCK.

The frequency of MCLK should be changed in Power Down, Standby or Mute states. This sequence avoids noisy data output caused by the frequency ratio of MCLK to BCK being out of the normal range. Refer to 9.9.3. Mute Function for the detailed sequence.

The AK4499EX is automatically placed in standby state when MCLK is stopped for more than 1 µsec during a normal operation, and the analog output becomes floating state. When MCLK is input again, the AK4499EX exits standby state and starts operation. This standby function will be disable by setting MSTBN bit = "1" in Register Control mode. The AK4499EX is in power down state until MCLK and BCK are supplied, and the analog output is floating state when power down is released (PDN pin = "L"  $\rightarrow$  "H").

| Sampling              |        | 44.1 kHz base |             | 48 kH      | Frequency  |             |

|-----------------------|--------|---------------|-------------|------------|------------|-------------|

| OSR pin<br>or OSR bit | Speed  | BCK           | MCLK        | BCK        | MCLK       | Ratio from  |

|                       | Mode   | frequency     | frequency   | frequency  | frequency  | MCLK to BCK |

| L or 0                | OSR256 | 11.2896 MHz   | 11.2896 MHz | 12.288 MHz | 12.288 MHz | 1           |

| LOIU                  | U3R200 |               | 22.5792 MHz |            | 24.576 MHz | 2           |

| H or 1                | 050120 | 5.6448 MHz    | 11.2896 MHz | 6.144MHz   | 12.288 MHz | 2           |

|                       | OSR128 | 0.0446 MI⊓Z   | 22.5792 MHz | 0.144IVINZ | 24.576 MHz | 4           |

#### Table 3. BCK, MCLK frequency and Sampling Speed Mode

# 9.3. Audio Inerface Format

Two audio interface format modes, such as Multi-bit Mono mode and Multi-bit Stereo mode, are selectable by using the LRSEL1-0 pins in Pin Control mode and STME bit in Register Control mode.

| Table 4. Audio Interface Format Select (Pin Control mode) |            |                        |  |  |  |

|-----------------------------------------------------------|------------|------------------------|--|--|--|

| LRSEL1 pin                                                | LRSEL0 pin | Audio Interface Format |  |  |  |

| L                                                         | L          |                        |  |  |  |

| L                                                         | Н          | Multi-Bit Stereo       |  |  |  |

| Н                                                         | L          |                        |  |  |  |

| Н                                                         | Н          | Multi-Bit Mono         |  |  |  |

#### Table 4 Audia Interface Fa act Salact (Din Control . .

Table 5. Audio Interface Format Select (Register Control mode)

| STME bit | Audio Interface Format |  |  |

|----------|------------------------|--|--|

| 0        | Multi-Bit Mono         |  |  |

| 1        | Multi-Bit Stereo       |  |  |

#### 9.3.1. Multi-Bit Mono Interface mode (single channel mode, no adding)

In this mode, the AK4499EX receives one channel of audio data. The data is two's complement format, each of which must be input to the MBD7-1 pins in synchronizing to BCK. The data is read out the rising edge of BCK input. Figure 10 shows the data format in Multi-bit Mono mode. D0[7:1], D1[7:1], D2[7:1] and D3[7:1] in the figure are one channel data.

|     | ВСК  |       |       | f     |       |

|-----|------|-------|-------|-------|-------|

| MSB | MBD7 | D0[7] | D1[7] | D2[7] | D3[7] |

| Î   | MBD6 | D0[6] | D1[6] | D2[6] | D3[6] |

|     | MBD5 | D0[5] | D1[5] | D2[5] | D3[5] |

|     | MBD4 | D0[4] | D1[4] | D2[4] | D3[4] |

|     | MBD3 | D0[3] | D1[3] | D2[3] | D3[3] |

| ļ   | MBD2 | D0[2] | D1[2] | D2[2] | D3[2] |

| LSB | MBD1 | D0[1] | D1[1] | D2[1] | D3[1] |

Figure 10. Multi-Bit Mono Interface mode

#### 9.3.2. Multi-Bit Stereo Interface mode

In this mode, the AK4499EX receives stereo audio data. The data is two's complement format, each of which must be input to the MBD7-1 pins in synchronizing to BCK. The data is read out by the BCK input. Figure 11 shows the data format in Multi-bit Stereo mode. R0[7:1], L1[7:1], R1[7:1], L2[7:1], R2[7:1] and L3[7:1] in the figure are one channel data.

|          | BCK  |       | Lch   | Rch   |       |       |       |

|----------|------|-------|-------|-------|-------|-------|-------|

|          |      |       |       |       |       |       |       |

| MSB      | MBD7 | R0[7] | L1[7] | R1[7] | L2[7] | R2[7] | L3[7] |

| <b>A</b> |      |       |       |       |       |       |       |

|          | MBD6 | R0[6] | L1[6] | R1[6] | L2[6] | R2[6] | L3[6] |

|          |      |       |       |       |       |       |       |

|          | MBD5 | R0[5] | L1[5] | R1[5] | L2[5] | R2[5] | L3[5] |

|          |      |       |       |       |       |       |       |

|          | MBD4 | R0[4] | L1[4] | R1[4] | L2[4] | R2[4] | L3[4] |

|          |      |       |       |       |       |       |       |

|          | MBD3 | R0[3] | L1[3] | R1[3] | L2[3] | R2[3] | L3[3] |

|          |      |       |       |       |       |       |       |

| ¥        | MBD2 | R0[2] | L1[2] | R1[2] | L2[2] | R2[2] | L3[2] |

| LSB      |      |       |       |       |       |       |       |

| LOD      | MBD1 | R0[1] | L1[1] | R1[1] | L2[1] | R2[1] | L3[1] |

|          |      |       |       |       |       |       |       |

Figure 11. Multi-Bit Stereo Interface mode

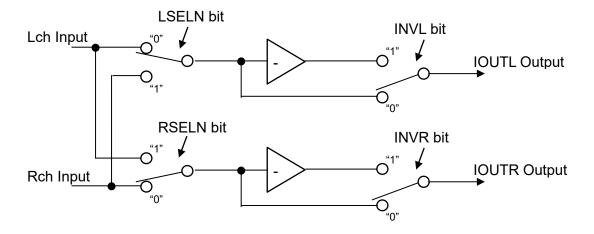

# 9.4. Multi-Bit Interface Mode Select, Output Signal Select

#### (1) Register Control Mode (PSN pin = "L")

Input and output combination of the AK4499EX can be changed by LSELN bit and RSELN bit (Table 6). These functions are available on Multi-bit Stereo Interface audio format (STME bit = "1").

| LSELN bit | RSELN bit | IOUTLP/N  | IOUTRP/N  |           |  |

|-----------|-----------|-----------|-----------|-----------|--|

| 0         | 0         | Lch Input | Rch Input | (default) |  |

| 0         | 1         | Lch Input | Lch Input |           |  |

| 1         | 0         | Rch Input | Rch Input |           |  |

| 1         | 1         | Rch Input | Lch Input |           |  |

Table 6. Output Signal Selection (Register Control mode)

# (2) Pin Control Mode (PSN pin = "H")

Audio interface format mode and Input/output combination of the AK4499EX can be changed by the LRSEL1-0 pins (Table 7).

Table 7. Audio Interface Format and Output Signal Selection (Pin Control mode)

|   | LRSEL0 pin | Audio Interface  | Output Selection |            |  |

|---|------------|------------------|------------------|------------|--|

|   |            | Format           | IOUTLP/N         | IOUTRP/N   |  |

| L | L          |                  | Lch Input        | Rch Input  |  |

| L | Н          | Multi-Bit Stereo | Lch Input        | Lch Input  |  |

| Н | L          |                  | Rch Input        | Rch Input  |  |

| Н | Н          | Multi-Bit Mono   | Mono Input       | Mono Input |  |

#### 9.5. Phase Inversion Function (Register Control Mode)

The output signal phase can be inverted by INVL bit and INVR bit (Table 8).

| Table 8. Phase Inversion Function |          |          |          |           |  |  |

|-----------------------------------|----------|----------|----------|-----------|--|--|

| INVL bit                          | INVR bit | IOUTLP/N | IOUTRP/N |           |  |  |

| 0                                 | 0        | Normal   | Normal   | (default) |  |  |

| 0                                 | 1        | Normal   | Invert   |           |  |  |

| 1                                 | 0        | Invert   | Normal   |           |  |  |

| 1                                 | 1        | Invert   | Invert   |           |  |  |

\_

Figure 12. Output Signal Select and Phase Inversion Block Diagram

# 9.6. Sound Control

The AK4499EX has a function to control the sound quality by setting SC pin or SC bit (Table 9). The analog characteristics of the AK4499EX are specified in Setting 1, and the characteristics are not guaranteed at Setting 2.

| SC pin (bit) | Sound                          |  |  |  |

|--------------|--------------------------------|--|--|--|

| L (0)        | Measurement Mode (Setting 1)   |  |  |  |

| H (1)        | Sound Quality Mode (Setting 2) |  |  |  |

Table 9. Sound Quality Select Mode

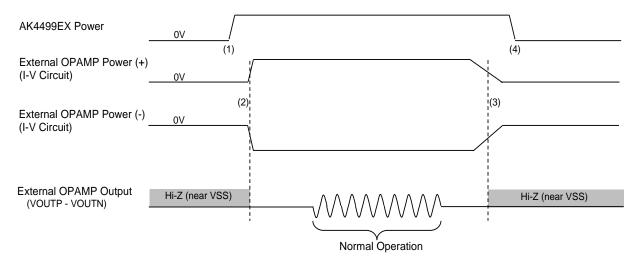

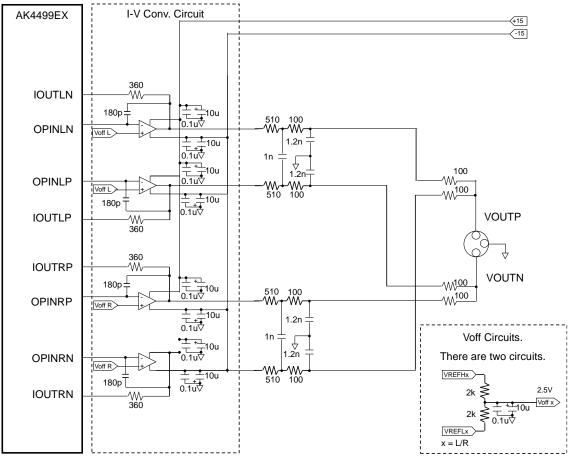

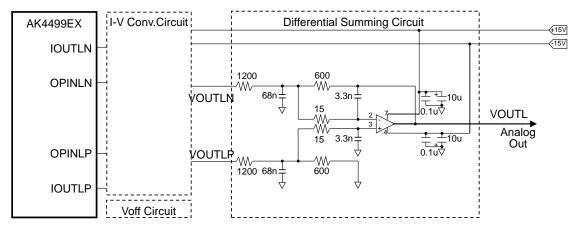

# 9.7. Power Up Sequence of External Operational Amplifier for I-V Conversion

The output current of the AK4499EX is converted voltage by external I-V conversion circuit. The operational amplifier used in this I-V conversion circuit must be powered up or stopped while the AK4499EX is powered up. By doing this, a feedback path of the operational amplifier is maintained, and it can protect the AK4499EX from fatal damage caused by excessive voltage input.

Notes:

- (1) Power up the AK4499EX. Refer to 9.8. Power Up/Down Function.

- (2) Power up an external operational amplifier after power up the AK4499EX.

- (3) When power down the system, the external amplifier must be powered down before the AK4499EX.

- (4) Power down the AK4499EX after the external amplifier. Refer to 9.8. Power Up/Down Function.

Figure 13. Power Up Sequence of External Operational Amplifier for I-V Conversion

There is a possibility of IC destruction due to breakdown of the withstanding voltage of the analog output pins (IOUTLP/LN/RP/RN) if the power supply of the external operational amplifier is turned on before power up the AK4499EX. Therefore, connect a Zener diode ( $V_{RWM}$  = 6 to 7 V) between each VDDL/R and VSSL/R if the power up/down sequence shown in Figure 13 cannot be followed.

If the power supply of the external amplifier is turned on before power up the AK4499EX, there is a possibility that click noise occurs due to DC difference. Connect an external mute circuit to the analog signal line to prevent this click noise (Figure 35).

#### 9.8. Power Up/Down Function

The AK4499EX is powered down by setting the PDN pin to "L". In power down state, all circuits stop operation and initialized, and the analog output becomes floating (Hi-Z) state. The PDN pin must be held "L" for more than 600 nsec to ensure a reliable reset. There is a possibility of malfunctions with the "L" pulse less than 600 nsec. Power down is released by setting the PDN pin to "H" from "L".

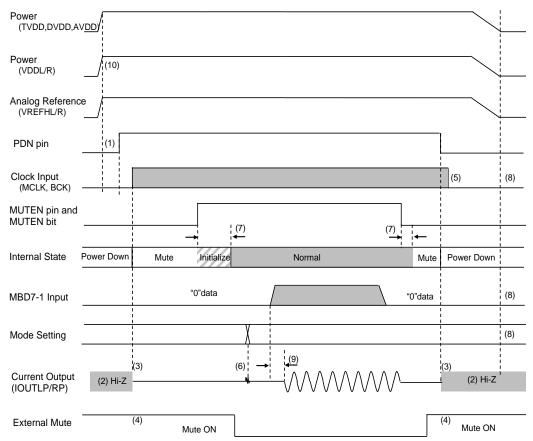

# (1) Register Control mode (PSN pin = "L")

The PDN pin = "H" and MSTBN bit = "0", the AK4499EX is started to output analog signal by inputting MCLK. If the MSTBN bit is changed from "0" to "1" after the PDN pin sets to "H", the analog outputs of the AK4499EX are "0" data outputs, not Hi-Z, even when MCLK is not supplied. After that all internal circuits are turned on and the AK4499EX is set in normal operating state, after the MUTEN pin = "H" and MUTEN bit = "1" is set and BCK is input. Figure 14 shows system timing example of power down/up.

Notes:

- (1) The PDN pin must be held "L" for more than 600 nsec after supplying TVDD, DVDD, AVDD and VDDL/R reached 90 %.

- (2) Analog outputs are floating (Hi-Z) in power down state.

- (3) Click noise occurs at the edge of PDN signal. This noise is output even if "0" data is input.

- (4) Mute the analog output externally if click noise (3) adversely affect system performance.

- (5) Clock inputs (MCLK and BCK) can be stopped in power down state.

- (6) Click noise occurs at the edge of mode setting signals (LRSELN bit, LRSELN bit and SC bit). This noise is output even if "0" data is input.

- (7) Setting MUTEN pin = "H" and MUTEN bit = "1", it is available to output signal and all circuit is powered up. When MUTEN is released, the initialization sequence is executed. It takes up to 77 µsec until the internal MUTE signal is changed when changing MUTEN pin and MUTEN bit.

- (8) Do not input all clocks, data and mode setting signals when power supplies are powered down.

- (9) It takes about 7-BCK cycles to output the analog signal corresponding to the digital input.

- (10) VDDL/R must be supplied at the same time as or before VREFHL/R.

Figure 14. Power up/down sequence example in Register Control mode

[AK4499EX]

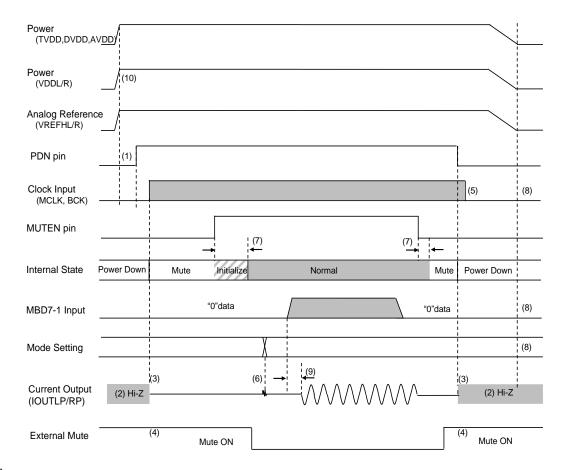

# (2) Pin Control mode (PSN pin = "H")

The PDN pin = "H", the AK4499EX is started to output analog signal by inputting MCLK. After that all internal circuits are turned on and the AK4499EX is set in normal operating state, after the MUTEN pin = "H" is set and BCK is input. Figure 15 shows system timing example of power down/up.

Notes:

- (1) The PDN pin must be held "L" for more than 600 nsec after supplying TVDD, DVDD, AVDD and VDDL/R reached 90 %.

- (2) Analog outputs are floating (Hi-Z) in power down state.

- (3) Click noise occurs at the edge of PDN signal. This noise is output even if "0" data is input.

- (4) Mute the analog output externally if click noise (3) adversely affect system performance.

- (5) Clock inputs (MCLK and BCK) can be stopped in power down state.

- (6) Click noise occurs at the edge of mode setting signals (LRSEL0 pin, LRSEL1 pin and SC pin). This noise is output even if "0" data is input.

- (7) Setting the MUTEN pin = "H", it is available to output signal and all circuit is powered up. When MUTEN is released, the initialization sequence is executed. It takes up to 77 μsec until the internal MUTE signal is changed when changing the MUTEN pin.

- (8) Do not input all clocks, data and mode setting signals when power supplies are powered down.

- (9) It takes about 7-BCK cycles to output the analog signal corresponding to the digital input.

- (10) VDDL/R must be supplied at the same time as or before VREFHL/R.

Figure 15. Power up/down sequence example in Pin Control mode

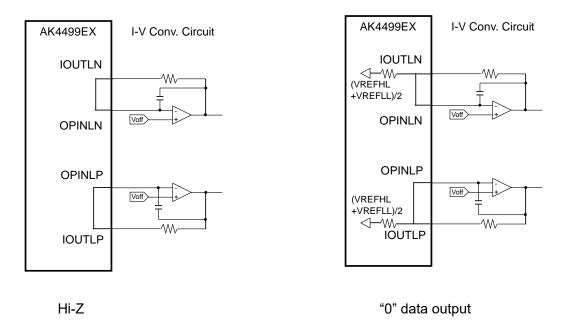

#### 9.9. Internal State

The AK4499EX has five states shown in Table 10. Power Down, Standby and Mute states are controlled by PDN pin, STBY bit, MCLK input, MUTEN pin and MUTEN bit.

| Table 10. Internal States        |            |             |                 |                                 |                            |           |                                |

|----------------------------------|------------|-------------|-----------------|---------------------------------|----------------------------|-----------|--------------------------------|

| State                            | PDN<br>pin | STBY<br>bit | MCLK<br>input   | MUTEN<br>pin (bit)<br>(Note 26) | Audio<br>Interface,<br>DWA | SR<br>DAC | IOUTLP/N,<br>IOUTRP/N<br>state |

| Power Down                       | L          | - (*)       | - (*)           | - (*)                           | OFF                        | OFF       | Hi-Z                           |

| Standby                          | Н          | 1           | - (*)           | - (*)                           | OFF                        | OFF       | Hi-Z                           |

| Standby (MCLK Stop)<br>(Note 25) | H          | 0           | Not<br>Supplied | - (*)                           | OFF                        | OFF       | Hi-Z                           |

| Mute                             | Н          | 0           | Supplied        | L (0)                           | OFF                        | ON        | "0" data                       |

| Normal Operation                 | Н          | 0           | Supplied        | H (1)                           | ON                         | ON        | Signal output                  |

Table 10. Internal States

(\*); - means "Do not care"

Note 25. In Register Control mode, this function is valid by MSTBN bit = "0" setting. Output pins and internal state depends on the PDN pin, STBY bit and the MUTEN pin setting, in case MSTBN bit = "1".

Note 26. The internal state depends only on the setting of the MUTEN pin in Pin Control mode, and it depends on the setting of the MUTEN pin and MUTEN bit in Register Control mode (Table 11).

#### 9.9.1. Standby Sequence by MCLK Input

The AK4499EX detects a clock stop and all circuits except MCLK stop detection circuit and Control Register stops operation if MCLK is not input for more than 1 µsec during operation (PDN pin = "H"). In this case, the analog output goes floating state (Hi-Z). The AK4499EX returns to normal operation after starting to supply MCLK again. This function is disabled to set MSTBN bit = "1" in Register Control mode.

| PDN pin                       |                  |                   | (4)             |                  |

|-------------------------------|------------------|-------------------|-----------------|------------------|

| MCLK Input                    |                  | MCLK Stop         |                 |                  |

|                               | →¦               | <b>;</b> ← (1) (1 | 1) <b>→</b> ¦ ¦ | ←                |

| Internal State                | Normal Operation | Standby           |                 | Normal Operation |

| MBD7-1 Input                  |                  | (3)               |                 |                  |

| Output Current<br>(IOUTLP/RP) |                  | (2) Hi-Z          |                 |                  |

Notes:

- (1) The AK4499EX detects MCLK stop and becomes standby state when MCLK edge is not detected for more than 1 µsec during operation.

- (2) The analog output goes to floating state (Hi-Z).

- (3) Click noise can be reduced by inputting "0" data when stopping and resuming MCLK supply.