AL58221

#### 12-CHANNEL RGB LED DRIVER

### Description

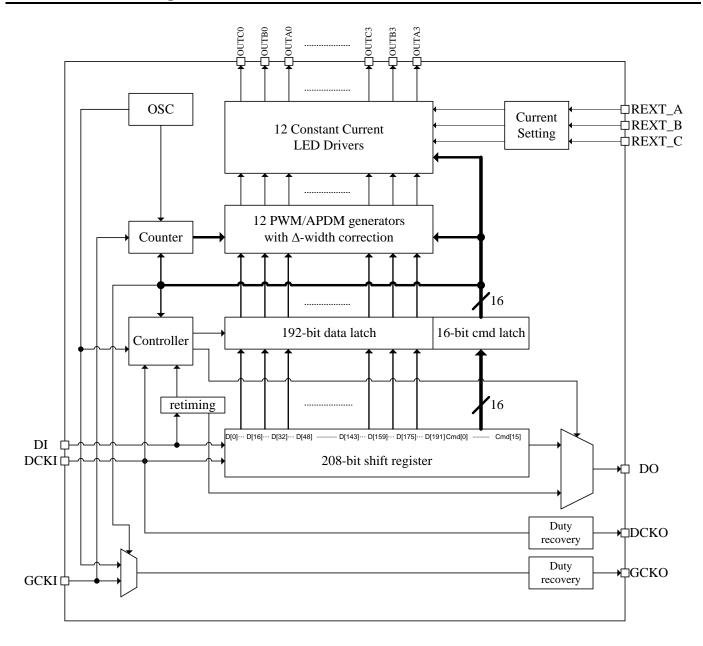

The AL58221 is a 12-channel (R/G/B x 4), constant-current, Adaptive Pulse Density Modulation (APDM) LED driver which operates over a 3V~5.5V input voltage range. The device provides 12 open-drain constant-current sinking outputs that are rated to 24V and delivers up to 60mA of high-accuracy current to each string of LED. Each channel's average output current can be individually programmable through a digital interface. The current at each output is set by three external current-setting resistors.

The AL58221 features a 10MHz double-edge trigger data clock input to reduce EMI. It offers a 2-wire serial interface to send grayscale data, control commands including 16/14/12/8-bit grayscale selection, grayscale clock frequency division selection, output polarity selection for high-power LED driving, output Trise and Tfall timing selection, current output waveform selection, and internal-latch function.

The device provides an adaptive pulse density modulation method to increase the visual refresh rate up to 1000 Hz @ 16-bit grayscale. It reduces flickers and provides output current bilateral processing for EMI reduction.

The AL58221 utilizes a clock duty recovery technique and pulse retiming to support longer distance connection and multiple devices' cascading applications. It also provides typical ±1% channel-to-channel LED current accuracy. Additional features include a ±0.1% regulated output current capability and fast output transient response.

The AL58221 is available in the TSSOP-24EP (Type A1-B) package and is specified over the -40°C to +85°C ambient temperature range.

#### **Features**

- Input Voltage VDD: 3V to 5.5V

- Constant Current Output Range

- 3~60mA@5V

- 3~35mA@3.3V

- 12 Constant-Current Sink (R/G/B x 4) Output Channels

- RGB Output Current setting by 3 external resistors

- 24V Rated output channels for long LED strings

- ±1% (typ.) LED Current accuracy between channels

- ±2% (typ.) LED Current accuracy between devices

- 16 / 14 / 12 / 8-bit grayscale selection

- Grayscale clock source selection: internal or external

- PWM or APDM control selection

- Programmable Output Current Trise / Tfall time

- Output Current Bilateral Processing for EMI reduction

- Diagnosis and Protections

- Built-in internal grayscale clock supports refresh rate >1000Hz@16-bit grayscale, >256KHz@8-bit grayscale

- Internal Grayscale clock frequency selection for High-Power LED driving application (min. 33.6KHz)

- 2-Wire Serial Interface (DI, DCKI)

- 20Mbps (max.) ~ 140 Kbps(min.) data rate for EMI reduction data transfer

- Cascaded capability (Max 1,030 devices)

- Clock duty recovery for cascading applications

- Schmitt trigger input

- Totally Lead-Free & Fully RoHS Compliant (Notes 1& 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative. <a href="https://www.diodes.com/quality/product-definitions/">https://www.diodes.com/quality/product-definitions/</a>

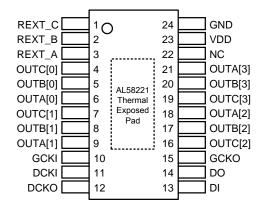

### **Pin Assignments**

(3D Photo - Not to Scale)

(3D Step file available upon request)

(Top View - Not to Scale)

TSSOP-24EP (Type A1-B)

### **Applications**

- Indoor and outdoor LED video displays

- Architectural and decorative lighting

- Digital signage and billboard applications

- LCD display backlighting

- Transportation signs

Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

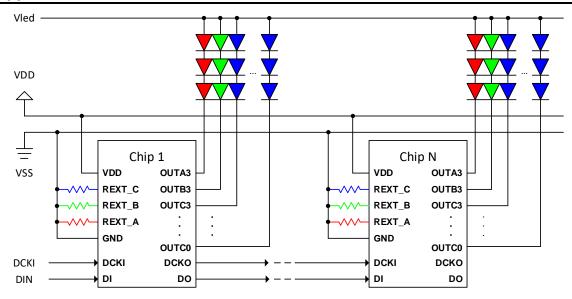

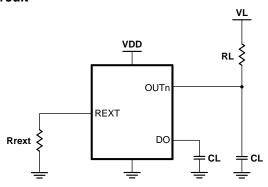

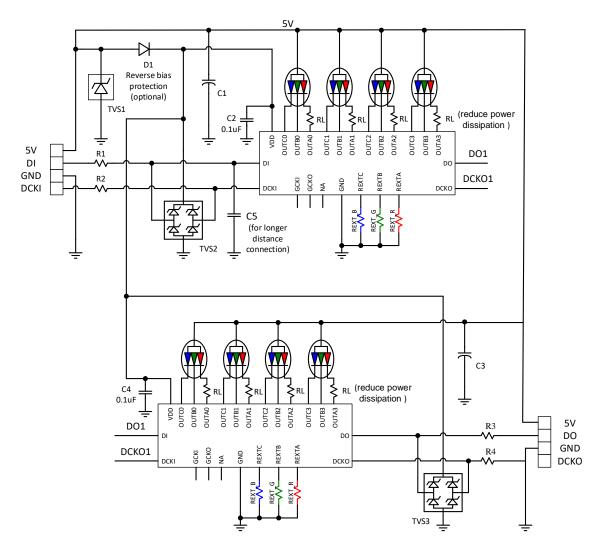

## **Typical Applications Circuit**

### **Pin Descriptions**

| PIN NUMBER   | PIN NAME               | DESCRIPTION                                                                                                                            |

|--------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3      | REXT_C, REXT_B, REXT_A | External resistors connected between REXT and GND for individual output current value setting.                                         |

| 4, 7, 16,19  | OUTC[0:3]              |                                                                                                                                        |

| 5, 8, 17, 20 | OUTB[0:3]              | Constant current outputs                                                                                                               |

| 6, 9, 18, 21 | OUTA[0:3]              |                                                                                                                                        |

| 10           | GCKI                   | External grayscale clock input for PWM/APDM operation.                                                                                 |

| 11           | DCKI                   | Clock input terminal for serial data transfer. Data is sampled at both rising edge and falling edge of DCKI.                           |

| 12           | DCKO                   | Clock output terminal for serial data transfer.                                                                                        |

| 13           | DI                     | Serial data input terminal.                                                                                                            |

| 14           | DO                     | Serial data output terminal.                                                                                                           |

| 15           | GCKO                   | Grayscale clock output When command data "osc" = 'L', GCKO comes from internal osc When command data "osc" = 'H', GCKO comes from GCKI |

| 22           | NC                     | No connect                                                                                                                             |

| 23           | VDD                    | Supply voltage terminal.                                                                                                               |

| 24           | GND                    | Ground terminal                                                                                                                        |

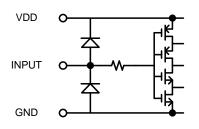

## **Equivalent Circuit of Inputs and Outputs**

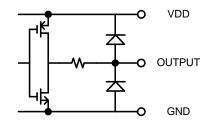

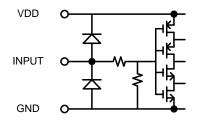

### 1. DI, DCKI terminals

### 2. DO, DCKO, GCKO terminals

#### 3. GCKI terminal

## **Functional Block Diagram**

### Absolute Maximum Ratings (@TA = +25°C, Tj (max) = 150°C unless otherwise specified.) (Note 4, 5, 6)

| Symbol                                                  | Parameters                      | Ratings        | Unit |

|---------------------------------------------------------|---------------------------------|----------------|------|

| VDD                                                     | Supply Voltage                  | -0.3 ~ 7.0     | V    |

| V <sub>DI</sub> , V <sub>DCKI</sub> , V <sub>GCKI</sub> | Input Voltage                   | -0.3 ~ VDD+0.3 | V    |

| IOUT                                                    | Output Current                  | 62             | mA   |

| VOUT_off                                                | Output Voltage @ Turn-off       | -0.3 ~ 24      | V    |

| VOUT_on                                                 | Output Voltage @ Turn-on        | -0.3 ~ 5.5     | V    |

| FDCK                                                    | Input Data Clock Frequency      | 0.07 ~ 10      | MHz  |

| FGCK                                                    | Input Grayscale Clock Frequency | 10             | MHz  |

| IGND                                                    | GND Terminal Current            | 750            | mA   |

Notes:

### **ESD Ratings**

| Symbol | Parameter                  | Rating | Unit |

|--------|----------------------------|--------|------|

| V      | Human-Body Model (HBM)     | 2000   | V    |

| Vesd   | Charged-Device Model (CDM) | 750    | V    |

### Package Thermal Data (Note 7)

| Package                | θ <sub>JC</sub> Thermal Resistance<br>Junction-to-Case (°C/W) | θ <sub>JA</sub> Thermal Resistance<br>Junction-to-Ambient (°C/W) | $P_{DIS}$ $T_{A} = +25^{\circ}C, T_{J} = +105^{\circ}C$ |  |

|------------------------|---------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------|--|

| TSSOP-24EP (Type A1-B) | 15                                                            | 28                                                               | 2.86                                                    |  |

Note:

## Recommended Operating Conditions (@TA = +25°C, unless otherwise specified.)

| Symbol           | Parameter                    | Min | Тур | Max  | Unit |

|------------------|------------------------------|-----|-----|------|------|

| $V_{DD}$         | Operating supply voltage     | 3.0 | 3.3 | 5.5  | V    |

| I <sub>оит</sub> | Output Current (Note 8)      | 3   | _   | 60   | mA   |

| V <sub>OUT</sub> | Output Voltage               | 1   | _   | 24   | V    |

| T <sub>A</sub>   | Ambient temperature (Note 8) | -40 | _   | +85  | °C   |

| $T_J$            | Junction temperature         | -40 | _   | +125 | °C   |

| Tstg             | Storage Temperature          | -55 | _   | +150 | °C   |

Note:

8. Dependent on ambient temperature, LED voltage, package thermal limitation, and PCB layout.

<sup>4.</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only and functional operation of the device at these or any other condition beyond those specified is not supported.

<sup>5.</sup> All voltage values are with respect to ground terminal.

<sup>6.</sup> Operation at Tj(max) = 150°C may reduce the device reliability; therefore, the suggested junction temperature of the device is under 125 °C.

<sup>7.</sup> Test condition: Device mounted on FR-4 PCB (51mm x 51mm 2oz copper, minimum recommended pad layout on top layer and thermal vias to bottom layer with maximum area ground plane. For better thermal performance, larger copper pad for heat-sink is needed

## Electrical Characteristics (VDD=5.0V @TA = +25°C, unless otherwise specified.)

| CHARACTERISTIC                                    | SYMBOL                | CONDITION                                    | MIN.   | TYP.  | MAX.   | UNIT     |

|---------------------------------------------------|-----------------------|----------------------------------------------|--------|-------|--------|----------|

| Input Voltage "H" Level                           | VIH                   | CMOS logic level                             | 0.7VDD | _     | VDD    | V        |

| Input Voltage "L" Level                           | VIL                   | CMOS logic level                             | GND    | _     | 0.3VDD | v        |

| Output Leakage Current                            | ILK                   | VOUT = 24 V                                  | _      | _     | 0.2    | uA       |

| Driving Correct (DO)                              | IOL                   | VOL = 0.4V                                   | 3.5    | 4.6   | 8      | A        |

| Driving Current (DO)                              | IOH                   | VOH= VDD-0.4                                 | -8     | -4.6  | -3     | mA       |

| Output Current Skew (Channel-to-Channel) (Note 9) | dIOUT1                | VOUT = 1.0 V                                 | _      | ±1    | ±3     | %        |

| Output Current Skew (Chip-to-Chip) (Note 10)      | dIOUT2                | Rrext = 2340 $\Omega$                        | _      | ±2    | ±6     | %        |

| Output Voltage Regulation (Note 11)               | % / VOUT              | Rrext = 2340 Ω<br>VOUT = 1 V ~ 3 V           | _      | ±.0.1 | _      | 0/ / ) / |

| Supply Voltage Regulation (Note 12)               | % / VDD               | Rrext = 2340 Ω<br>VDD = 3 V ~ 5.5 V          | _      | ±0.6  | ±1     | %/V      |

|                                                   | I <sub>DD1(off)</sub> | Rrext = 2340 $\Omega$ all outputs turn off   | _      | 5.73  | _      |          |

| Comple Coursest (Nata 42)                         | I <sub>DD2(on)</sub>  | Rrext = $2340 \Omega$<br>all outputs turn on | 2.93   | 5.85  | 11.5   | ^        |

| Supply Current (Note 13)                          | I <sub>DD3(off)</sub> | Rrext = 19.5 K $\Omega$ all outputs turn off | _      | 2.84  | _      | mA       |

|                                                   | I <sub>DD4(on)</sub>  | Rrext = 19.5 K $\Omega$ all outputs turn on  | 1.42   | 2.84  | 8      |          |

Notes: 9. Channel-to-channel skew is defined by the formula below:

$$\Delta(\%) = \left[\begin{array}{c} Iout_n \\ \hline (Iout_0 + Iout_1 + ... + Iout_3) \\ 4 \end{array} - 1\right] * 100\%$$

10. Chip-to-Chip skew is defined by the formula below:

$$\Delta(\%) = \left[\begin{array}{c} (\underbrace{Iout_0 + Iout_1 + ... + Iout_3})_{-} - (Ideal \ Output \ Current) \\ \hline (Ideal \ Output \ Current) \end{array}\right] * 100\%$$

11. Output voltage regulation is defined by the formula below:

$$\Delta \left( \% \ / V \right) = \left[ \begin{array}{c} Iout_n(@Vout_n = 3V) - Iout_n(@Vout_n = 1V) \\ Iout_n(@Vout_n = 3V) \end{array} \right] * \frac{100\%}{3V - 1V}$$

12. Supply voltage regulation is defined by the formula below:

$$\Delta \left( \% \, / V \right) = \left[ \begin{array}{c} Iout_n(@\, V_{DD} = 5.5 V) - Iout_n(@\, V_{DD} = 3 V) \\ Iout_n(@\, Vcc = 3 V) \end{array} \right] * \frac{100\%}{5.5 V - 3 V}$$

13. IO excluded.

## Electrical Characteristics (VDD=3.3V @TA = +25°C, unless otherwise specified.)

| CHARACTERISTIC                                     | SYMBOL                | CONDITION                                    | MIN.   | TYP. | MAX.   | UNIT    |

|----------------------------------------------------|-----------------------|----------------------------------------------|--------|------|--------|---------|

| Input Voltage "H" Level                            |                       | CMOS logic level                             | 0.7VDD | _    | VDD    | V       |

| Input Voltage "L" Level                            | VIL                   | CMOS logic level                             | GND    | _    | 0.3VDD | V       |

| Output Leakage Current                             | ILK                   | VOUT = 24 V                                  | _      | _    | 0.2    | uA      |

| Driving Current (DO)                               | IOL                   | VOL = 0.4V                                   | 2      | 3.0  | _      | A       |

| (Guarantee by design)                              | IOH                   | VOH= VDD-0.4                                 | _      | -2.9 | -2     | mA      |

| Output Current Skew (Channel-to-Channel) (Note 14) | dIOUT1                | VOUT = 1.0 V                                 |        | ±1   | ±3     | %       |

| Output Current Skew (Chip-to-Chip) (Note 15)       | dIOUT2                | Rrext = 2340 $\Omega$                        | _      | ±2   | ±6     | %       |

| Output Voltage Regulation (Note 16)                | % / VOUT              | Rrext = 2340 Ω<br>VOUT = 1 V ~ 3 V           | _      | ±0.1 | _      | 0/ / \/ |

| Supply Voltage Regulation (Note 17)                | % / VDD               | Rrext = 2340 Ω<br>VDD = 3 V ~ 5.5 V          | _      | ±0.6 | ±1     | %/V     |

|                                                    | I <sub>DD1(off)</sub> | Rrext = 2340 $\Omega$ all outputs turn off   | _      | 5.22 | _      |         |

| Supply Current/Note 19)                            | I <sub>DD2(on)</sub>  | Rrext = 2340 $\Omega$ all outputs turn on    | 2.61   | 5.22 | 8      | ^       |

| Supply Current (Note 18)                           | I <sub>DD3(off)</sub> | Rrext = 19.5 K $\Omega$ all outputs turn off | _      | 2.74 | _      | mA      |

|                                                    | I <sub>DD4(on)</sub>  | Rrext = 19.5 K $\Omega$ all outputs turn on  | 1.4    | 2.79 | 7      |         |

Notes: 14. Channel-to-channel skew is defined by the formula below:

$$\Delta(\%) = \left[ \begin{array}{c} Iout_n \\ -\underline{(Iout_0 + Iout_1 + ... + Iout_3)} \\ 4 \end{array} \right] * 100\%$$

15. Chip-to-Chip skew is defined by the formula below:

$$\Delta \big(\% \big) = \Big[ \begin{array}{c|cccc} \underbrace{(Iout_0 + Iout_1 + \ldots + Iout_3)}_{} - (Ideal & Output & Current) \\ \hline & \underbrace{(Ideal & Output & Current)}_{} \\ \end{array} \Big] * 100\%$$

16. Output voltage regulation is defined by the formula below:

$$\Delta \left( \% \ / V \right) = \left[ \begin{array}{c} Iout_n(@Vout_n = 3V) - Iout_n(@Vout_n = 1V) \\ Iout_n(@Vout_n = 3V) \end{array} \right] * \frac{100\%}{3V - 1V}$$

17. Supply voltage regulation is defined by the formula below:

$$\Delta \left( \% \, / V \right) = \left[ \begin{array}{c} Iout_n(@V_{DD} = 5.5V) - Iout_n(@V_{DD} = 3V) \\ Iout_n(@Vcc = 3V) \end{array} \right] * \frac{100\%}{5.5V - 3V}$$

18. IO excluded.

## **Switching Characteristics** (VDD = 5.0V @T<sub>A</sub> = +25°C, unless otherwise specified.) (Guarantee by design)

| CHARACTERISTIC                     |                                         | SYMBOL              | CONDITION                               | MIN. | TYP. | MAX. | UNIT |

|------------------------------------|-----------------------------------------|---------------------|-----------------------------------------|------|------|------|------|

|                                    | DCKI-to-DO                              | tpLH1               |                                         | _    | 29   | 39   |      |

| Propagation Delay<br>('L to 'H')   | DCKI-to-DCKO                            | tpLH2               |                                         |      | 6.3  | 19   |      |

|                                    | GCKI-to-GCKO                            | tpLH3               |                                         |      | 10.5 | 19   |      |

|                                    | DI-to-DO @ Internal-latch control cycle | tpLH4               |                                         | _    | 12   | _    |      |

|                                    | DCKI-to-DO                              | tpHL1               | \/// \// \// \// \// \// \// \// \// \/ |      | 39   | 59   |      |

| Propagation Delay<br>('H' to 'L')  | DCKI-to-DCKO                            | tpHL2               | VIH = VDD<br>VIL = GND                  |      | 6.3  | 19   |      |

| (** ** = /                         | GCKI-to-GCKO                            | tpHL3               | Rrext = 2340 $\Omega$                   |      | 9    | 19   |      |

|                                    | DCKI                                    | tw <sub>(DCK)</sub> | VL = 5.0 V<br>RL = 150 Ω                | 50   | _    | 7200 | ns   |

|                                    | GCKI                                    | tw <sub>(GCK)</sub> | CL = 13 pF                              | 50   | _    |      |      |

| Pulse Duration                     | DI @ Internal-latch control cycle       | twH <sub>(DI)</sub> |                                         | 70   | _    | _    |      |

|                                    | DI @ Internal-latch control cycle       | twL <sub>(DI)</sub> |                                         | 230  | _    | _    |      |

| Setup Time                         |                                         |                     |                                         | 10   | _    |      |      |

| Hold Time                          | DI                                      | th <sub>(D)</sub>   |                                         | 10   | _    |      |      |

| DI Retiming @ Interna              | I-latch control cycle                   | Tw_re               | _                                       | 70   | 90   | 110  |      |

| Internal-latch Start Tim           | Internal-latch Start Time               |                     | _                                       | 220  |      |      | us   |

| Internal-latch Stop Time (Note 19) |                                         | Tstop               | _                                       | 200  |      |      | ns   |

| DCKI Freq.                         |                                         | F <sub>DCKI</sub>   | _                                       | 0.07 |      | 10   | MHz  |

| Internal OSC Freq.                 |                                         | Fosc                | _                                       | 6.4  | 8.1  | 9.8  | MHz  |

| GCKI Freq.                         |                                         | F <sub>GCKI</sub>   | _                                       | _    | _    | 10   | MHz  |

Note: 19. Tstop (min.) for cascade application must > "200ns + N\*10ns" (N is the cascade number of drivers)

## **Switching Characteristics** (VDD = 3.3V @T<sub>A</sub> = +25°C, unless otherwise specified.) (Guarantee by design)

| CHARACTERISTIC                     |                                         | SYMBOL              | CONDITION               | MIN. | TYP. | MAX. | UNIT |

|------------------------------------|-----------------------------------------|---------------------|-------------------------|------|------|------|------|

|                                    | DCKI-to-DO                              | tpLH1               |                         | _    | 34   | 39   |      |

| Propagation Delay                  | DCKI-to-DCKO                            | tpLH2               |                         | _    | 7.9  | 19   |      |

| ('L to 'H')                        | GCKI-to-GCKO                            | tpLH3               |                         | _    | 12   | 19   |      |

|                                    | DI-to-DO @ Internal-latch control cycle | tpLH4               |                         | _    | 18   | _    |      |

|                                    | DCKI-to-DO                              | tpHL1               | \(\(\)\(\)              | _    | 40   | 59   |      |

| Propagation Delay<br>('H' to 'L')  | DCKI-to-DCKO                            | tpHL2               | VIH = VDD<br>VIL = GND  |      | 8.2  | 19   |      |

| ( 15 _)                            | GCKI-to-GCKO                            | tpHL3               | Rrext = 2340 $\Omega$   | _    | 10.5 | 19   |      |

|                                    | DCKI                                    | tw <sub>(DCK)</sub> | VL =5.0 V<br>RL = 150 Ω | 50   | _    | 7200 | ns   |

|                                    | GCKI                                    | tw <sub>(GCK)</sub> | CL = 13 pF              | 50   | _    | _    |      |

| Pulse Duration                     | DI @ Internal-latch control cycle       | twH <sub>(DI)</sub> |                         | 70   | _    | _    |      |

|                                    | DI @ Internal-latch control cycle       | twL <sub>(DI)</sub> |                         | 230  | _    | _    |      |

| Setup Time                         |                                         |                     |                         | 10   | _    |      |      |

| Hold Time                          | DI                                      | th <sub>(D)</sub>   |                         | 10   |      | _    |      |

| DI Retiming @ Interna              | I-latch control cycle                   | Tw_re               | _                       | 90   | 110  | 130  |      |

| Internal-latch Start Tim           | Internal-latch Start Time               |                     | _                       | 220  | _    | _    | us   |

| Internal-latch Stop Time (Note 20) |                                         | Tstop               | _                       | 200  | _    |      | ns   |

| DCKI Freq.                         |                                         | F <sub>DCKI</sub>   | _                       | 0.07 |      | 10   | MHz  |

| Internal OSC Freq.                 |                                         | Fosc                | _                       | 6.25 | 7.95 | 9.65 | MHz  |

| GCKI Freq.                         |                                         | F <sub>GCKI</sub>   | _                       | _    | _    | 10   | MHz  |

Note: 20. Tstop (min.) for cascade application must > "200ns + N\*10ns" (N is the cascade number of drivers)

### **Switching Characteristics Test Circuit**

Switching Characteristics Test Circuit

## Timing Characteristics (@T<sub>A</sub> = +25°C, unless otherwise specified.)

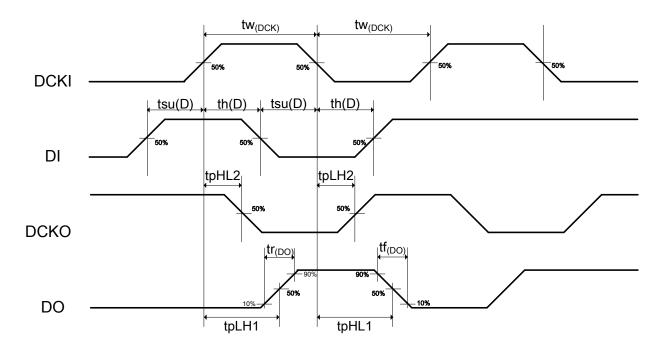

### 1. DCKI, DCKO - DI, DO

## Switching Characteristics (@T<sub>A</sub> = +25°C, unless otherwise specified.)

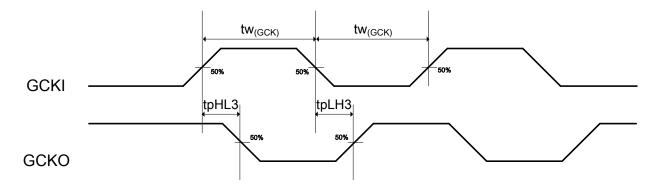

### 2. GCKI-GCKO

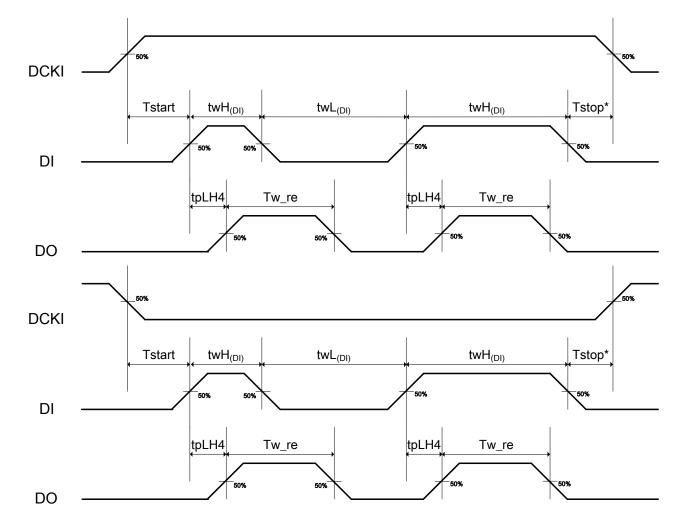

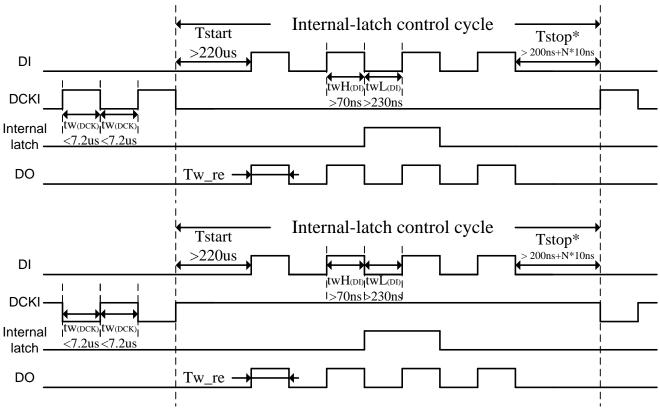

### 3. DCKI-DI & DI-DO @ Internal-latch control cycle

<sup>\*</sup> Tstop (min.) for cascade application must > "200ns + N\*10ns" (N is the cascade number of drivers)

## **Functional Description**

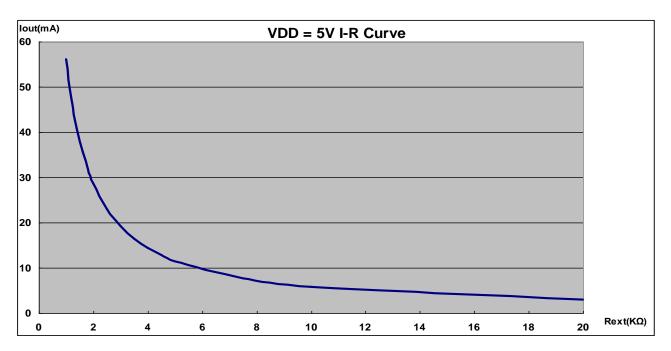

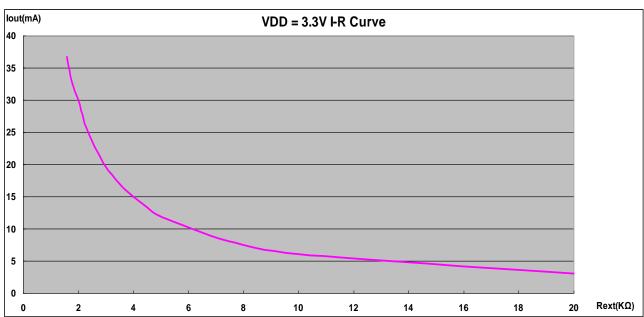

#### Reference Resistor

The constant current values are determined by an external resistor placed between REXT pin and GND pin. The following formula is utilized to calculate the current value:

$$Iout(mA) = \frac{1.28*45.5}{Rrext (K\Omega)}$$

Where Rrext is a resistor placed between REXT and GND

For example, lout is 25mA when Rrext=2340  $\!\Omega$  and lout is 3mA when Rrext=19.5  $K\Omega$

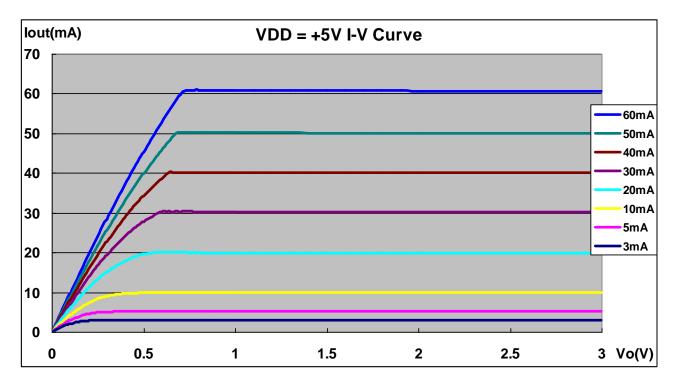

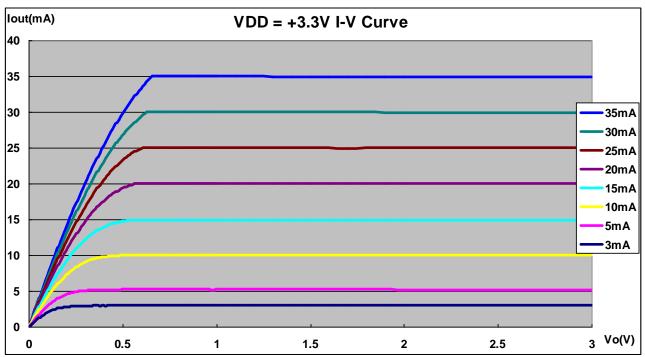

#### **Constant-Current Output**

The current characteristics may be invariable in the influence of the loading voltage. Therefore, the AL58221 can minimize the interference of different LED forward voltages and produce constant current. The following figures illustrate the suitable output voltage, which should be determined in order to maintain excellent performance.

#### **Serial Data Interface**

The AL58221 transmits data from the DI pin on both rising and falling edge of the data clock (DCKI). After the whole given serial data are shifted into the 208-bit shift register, the data can then be loaded into the latch register by the internal-latch function. The serial data will be shifted out from the DO pin on the synchronization of the rising and falling edge of DCKI.

#### **Data Format**

16-bit command data and 12x16-bit PWM data. (Total: 208-bit)

**16-bit Command Data Description** (CMD[15:0]) = D[207:192]) (Note 21)

| BIT No.    | Name     | DESCRIPTION                      | FUNCTION                                                                                                                                                                                                                         |

|------------|----------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD[15:11] | Temp     | Not used                         | Please filled with all "0"                                                                                                                                                                                                       |

| CMD[10]    | hspd     | lout Tr/Tf select                | 0 : lout slow mode<br>1 : lout fast mode                                                                                                                                                                                         |

| CMD[9:8]   | bs[1:0]  | Grayscale resolution select      | 00 : 8-bit grayscale application 01 : 12-bit grayscale application 10 : 14-bit grayscale application 11 : 16-bit grayscale application                                                                                           |

| CMD[7:5]   | gck[2:0] | Internal oscillator freq. select | 000 : original freq (8.6MHz) 001 : original freq/2 010 : original freq/4 011 : original freq/8 100 : original freq/16 101 : original freq64 110 : original freq/128 111 : original freq/256 If CMD[3]=1, please set CMD[7:5]=000 |

| CMD[4]     | sep      | Output waveform select           | 0 : MY-PWM output waveform (similar to traditional waveform) 1 : APDM output waveform                                                                                                                                            |

| CMD[3]     | osc      | Grayscale clock source select    | 0 : internal oscillator (8.6MHz) (internal GCK source) 1 : external clock from GCKI pin (external GCK source)                                                                                                                    |

| CMD[2]     | pol      | Output polarity select           | 0 : work as LED driver<br>1 : work as MY-PWM/APDM generator                                                                                                                                                                      |

| CMD[1]     | cntset   | Counter reset select             | 0 : free running mode<br>1 : counter reset mode (Only usable when osc = "1")                                                                                                                                                     |

| CMD[0]     | onest    | One-shot select                  | frame cycle repeat mode     frame cycle One-shot mode (Only usable when cntset = "1")                                                                                                                                            |

Note:

21. For information about command data settings, please refer to page 19.

#### **Grayscale data format**

16-bit grayscale data for per channel (D[191:176], D[175:160], D[159:144], D[143:128]...D[15:0])

| bs[1:0] | DESCRIPTION           | PWM DATA FORMAT                                                                                                   |  |  |  |  |  |

|---------|-----------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 00      |                       | Fill the eight most significant bits with "0", Fill the eight least significant bits with 8-bit grayscale data.   |  |  |  |  |  |

| 01      |                       | Fill the four most significant bits with "0", Fill the twelve least significant bits with 12-bit grayscale data.  |  |  |  |  |  |

| 10      |                       | Fill the two most significant bits with "0", Fill the fourteen least significant bits with 14-bit grayscale data. |  |  |  |  |  |

| 11      | 16-bit grayscale mode | Filled 16-bit grayscale data directly.                                                                            |  |  |  |  |  |

#### Functional Description (continued) Data Format of 8-bit grayscale mode (bs[1:0]=00) D[207] D[192] 0 $bs[0] \chi gck[2] \chi gck[1] \chi gck[0]$ hspd bs[1] pol cntset X onest D[191] D[176] 0 0 0 0 A3[6] X A3[5] \ XA3[4]XA3[3]XA3[2] (A3[1]XA3[0] LSB D[0] D[15] 0 0 0 C0[7] (C0101) Data Format of 12-bit grayscale mode (bs[1:0]=01) D[207] D[192] 0 bs[0] $\chi_{gck[2]\chi_{gck[1]\chi_{gck[0]}}$ pol bs[1] cntset onest hspd sep osc D[176] D[191] 0 A3[11]XA3[10]XA3[9]XA3[8]XA3[7]XA3[6]XA3[5] (A3[0] LSB D[0] D[15] (C0[11])(C0[10])(C0[9])(C0[8])(C0[7])(C0[6])(C0[5])(C0[4])(C0[3])(C0[2])(C0[1])(C0[0]) Data Format of 14-bit grayscale mode (bs[1:0]=10) D[207] D[192] 0 0 bs[0] \gck[2]\gck[1]\gck[0] sep pol 0 hspd bs[1] osc cntset onest D[191] D[176] (A3[13](A3[12](A3[11](A3[10](XA3[9])(XA3[8])(XA3[7])(XA3[6])(XA3[5])(XA3[4])(XA3[3])(XA3[2])(XA3[1])(XA3[0]) LSB D[0] D[15] XC0[13]XC0[12]XC0[11]XC0[10]XC0[9]XC0[8]XC0[7]XC0[6]XC0[5]XC0[4]XC0[3] 0 (C0[2] (C0[1]) (C0[0]) Data Format of 16-bit grayscale mode (bs[1:0]=11) D[207] D[192] 0 hspd bs[1] bs[0] gck[2]Xgck[1]Xgck[0] pol cntset) onest sep osc D[191] D[176] (A3[15]XA3[14]XA3[13]XA3[12]XA3[11]XA3[10]XA3[9]XA3[8]XA3[7]XA3[6]XA3[5]XA3[4]XA3[3]XA3[2] (A3[1]XA3[0] LSB D[0] D[15] (C0[15])(C0[14])(C0[13])(C0[12])(C0[11])(C0[10])(C0[9])(C0[8])(C0[7])(C0[6])(C0[5])(C0[4])(C0[3] C0[2]

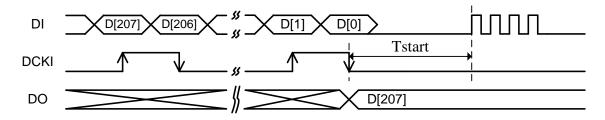

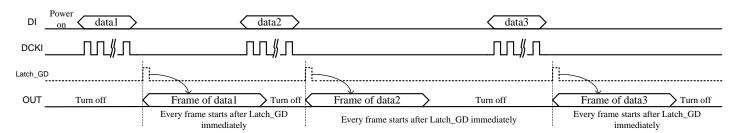

#### Internal-latch control cycle timing diagram

The steps to trigger internal-latch function are shown below:

- 1. After the entire given serial data shifts into the shift register, keep DCKI at a fixed level (no matter "high" or "low") for more than 220us. (Tstart > 220us).

- 2. Send 4 DI pulses ( $twH_{(DI)}$ >70ns,  $twL_{(DI)}$ > 230ns, Tstop\*).

- Data is loaded into the latch register at the 2<sup>nd</sup> falling edge of the DI pulse.

<sup>\*</sup>Tstop (min.) for cascade application must > "200ns + N\*10ns" (N is the cascade number of drivers)

#### Pulse retiming at Internal-latch control cycle

The AL58221 provides DO signal retiming function, which is fixed at Tw\_re = 90ns@VDD=5V under the internal-latch control cycle. This prevents variation of the duty ratio caused by long cascading.

AL58221 16 of 26

Document number: DS46476 Rev. 2 - 2 **www.diodes.com**

<sup>\*</sup>For tw(DCK) > 7.2us application, please refer to the document "AN-AL58221-05-Solution for tw\_DCK\_ longer than 7.2us.pdf"

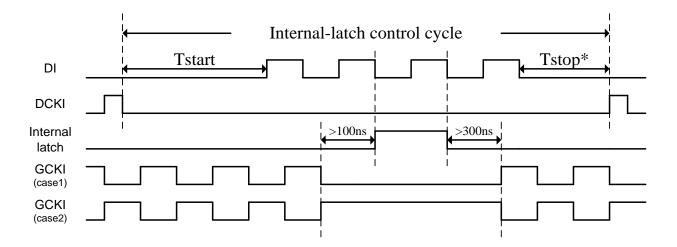

#### **External Grayscale Clock Mode** (CMD[3]=osc = "1")

When osc="1", users may use the external grayscale clock function. The grayscale clock is controlled by the GCKI pin. Both the rising and falling edge of the GCKI pulse can increase the grayscale counter by one. The AL58221 compares the grayscale data of each output with the grayscale counter value. If the grayscale data is larger than the grayscale counter value, the OUT will switch on. The frequency of the external clock cannot be controlled by CMD[7:5]; please set CMD[7:5]=000 if CMD[3] = "1". Some timing constrains must be obeyed, which are shown below:

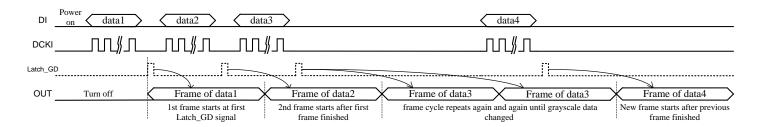

#### Free Running Mode

The first frame cycle after power-on will synchronize with the first Latch\_GD signal (Latch\_GD is the latch signal for grayscale data.). A new frame cycle for the new grayscale data will start after the previous frame cycle is finished. If the grayscale data does not change, the frame cycle will repeat automatically. This mode ensures every frame cycle will be performed completely.

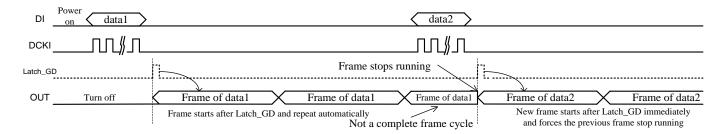

#### **Grayscale Counter Reset Mode** (Only usable when osc = "1": external grayscale clock mode)

Every new frame cycle of the new grayscale data will synchronize with the Latch\_GD signal. Frame cycles of the same grayscale data will repeat automatically until the next grayscale data is loaded. When the next grayscale data is loaded, it will force the previous frame to stop running. This means that the previous frame cycle may not perform completely.

#### **One-shot Mode** (Only usable when cntset = "1": grayscale counter reset mode)

Every new frame cycle of new grayscale data will synchronize with the Latch\_GD signal. One grayscale data will only perform one complete frame cycle. After one complete cycle, the output current will turn off until the next grayscale data is loaded.

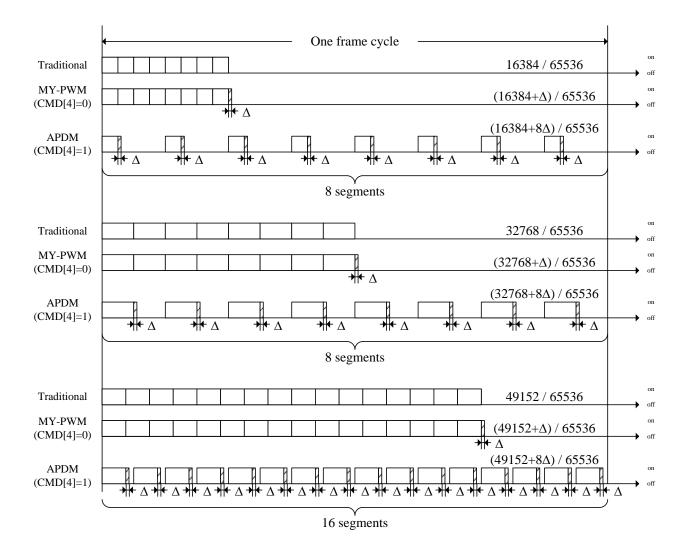

#### Adaptive Pulse Density Modulation with ∆-Width Correction

Adaptive Pulse Density Modulation (APDM) with  $\Delta$ -Width Correction is a technique to improve output current waveform distortion and increase visual refresh rate. The adaptive output waveform is controlled by the grayscale value automatically. When all outputs operate at high grayscale resolution (grayscale resolution  $\geq$  75%), the output waveform is divided into more segments to increase visual refresh rate. Otherwise, the output waveform is divided into less segments at low grayscale resolution to improve output current linearity (grayscale resolution < 75%). The  $\Delta$ -Width Correction ( $\Delta \neq 0$ ) is used to compensate the non-ideal output current transient response.

(e.g. 16-bit grayscale application,  $\Delta \neq 0$ )

## **Application Information**

### **Command Data Setting for Different Applications** (Note 22)

### 1. Grayscale Clock from Internal Oscillator

|           | CMD[15:11] | CMD[10] | CMD[9:8] | CMD[7:5] | CMD[4] | CMD[3] | CMD[2] | CMD[1] | CMD[0] | Image refresh |

|-----------|------------|---------|----------|----------|--------|--------|--------|--------|--------|---------------|

| Grayscale | temp       | hspd    | bs[1:0]  | gck[2:0] | sep    | osc    | pol    | cntset | onest  | Rate(Hz)      |

| 16-bit    | 00000      | d       | 11       | 000      | 1      | 0      | d      | 0      | 0      | 1,001         |

| 16-bit    | 00000      | d       | 11       | 011      | 1      | 0      | d      | 0      | 0      | 125           |

| 14-bit    | 00000      | d       | 10       | 000      | 1      | 0      | d      | 0      | 0      | 4,004         |

| 14-bit    | 00000      | d       | 10       | 011      | 1      | 0      | d      | 0      | 0      | 500           |

| 12-bit    | 00000      | d       | 01       | 000      | 1      | 0      | d      | 0      | 0      | 16,016        |

| 12-bit    | 00000      | d       | 01       | 100      | 1      | 0      | d      | 0      | 0      | 1,001         |

| 12-bit    | 00000      | d       | 01       | 101      | 1      | 0      | d      | 0      | 0      | 250           |

| 8-bit     | 00000      | d       | 00       | 000      | 1      | 0      | d      | 0      | 0      | 256,250       |

| 8-bit     | 00000      | d       | 00       | 100      | 1      | 0      | d      | 0      | 0      | 16,016        |

| 8-bit     | 00000      | d       | 00       | 101      | 1      | 0      | d      | 0      | 0      | 4,004         |

| 8-bit     | 00000      | d       | 00       | 111      | 1      | 0      | d      | 0      | 0      | 1,001         |

| 8-bit     | 00000      | d       | 00       | 000      | 0      | 0      | d      | 0      | 0      | 32,031        |

| 8-bit     | 00000      | d       | 00       | 011      | 0      | 0      | d      | 0      | 0      | 4,004         |

## 2. Grayscale Clock from External GCKI Pin

| Grayscale | CMD[15:11] | CMD[10] | CMD[9:8] | CMD[7:5] | CMD[4] | CMD[3] | CMD[2] | CMD[1] | CMD[0] | GCKI Freq.<br>(MHz) | Image refresh<br>Rate(Hz) |

|-----------|------------|---------|----------|----------|--------|--------|--------|--------|--------|---------------------|---------------------------|

|           | temp       | hspd    | bs[1:0]  | gck[2:0] | sep    | osc    | pol    | cntset | onest  |                     | ` ,                       |

| 16-bit    | 00000      | d       | 11       | 000      | 1      | 1      | d      | 0      | 0      | 10                  | 2,441                     |

| 16-bit    | 00000      | d       | 11       | 000      | 1      | 1      | d      | 0      | 0      | 2                   | 488                       |

| 14-bit    | 00000      | d       | 10       | 000      | 1      | 1      | d      | 0      | 0      | 10                  | 9,766                     |

| 14-bit    | 00000      | d       | 10       | 000      | 1      | 1      | d      | 0      | 0      | 2                   | 1,953                     |

| 12-bit    | 00000      | d       | 01       | 000      | 1      | 1      | d      | 0      | 0      | 10                  | 39,063                    |

| 12-bit    | 00000      | d       | 01       | 000      | 1      | 1      | d      | 0      | 0      | 2                   | 7,813                     |

| 8-bit     | 00000      | d       | 00       | 000      | 1      | 1      | d      | 0      | 0      | 10                  | 625,000                   |

| 8-bit     | 00000      | d       | 00       | 000      | 1      | 1      | d      | 0      | 0      | 2                   | 125,000                   |

| 8-bit     | 00000      | d       | 00       | 000      | 0      | 1      | d      | 0      | 0      | 10                  | 78,125                    |

| 8-bit     | 00000      | d       | 00       | 000      | 0      | 1      | d      | 0      | 0      | 2                   | 15,625                    |

Note: 22. "d" means "don't care" (dependent on application).

### **Application Information** (continued)

Work as LED driver with system supply voltage = 5V (Set CMD[2] = "L")

Use internal grayscale clock & Internal-latch function

| Symbol         | Value<br>(just for reference) | Description                                     |

|----------------|-------------------------------|-------------------------------------------------|

| R1, R2, R3, R4 | 33~100Ω                       | resistor for hot-plug protection                |

| C1, C3         | 4.7~47uF                      | capacitor for voltage stability                 |

| C2, C4         | 0.1uF                         | decoupling capacitor                            |

| C5             | 33~130pF                      | capacitor for longer distance connection        |

| D1             | _                             | diode for reverse bias protection (optional)    |

| RL             | _                             | used to reduce the power dissipation of AL58221 |

<sup>\*</sup> Users may use suitable value for different applications.

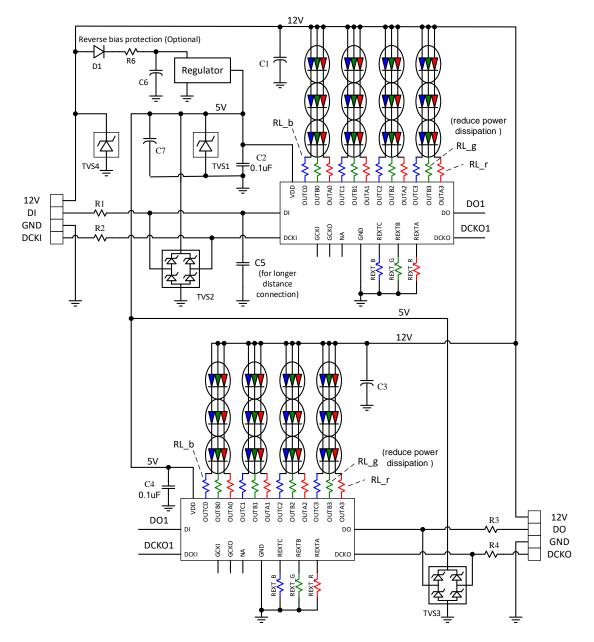

### **Application Information** (continued)

2. Work as LED driver with system supply voltage = 12V (Set CMD[2] = "L") Use internal grayscale clock & Internal-latch function

| Symbol           | Value<br>(just for reference) | Description                                     |

|------------------|-------------------------------|-------------------------------------------------|

| R1, R2, R3, R4   | 33~100Ω                       | resistor for hot-plug protection                |

| R6               | 33~100Ω                       | resistor for the regulator                      |

| C1, C3           | 4.7~47uF                      | capacitor for voltage stability                 |

| C2, C4           | 0.1uF                         | decoupling capacitor                            |

| C5               | 33~130pF                      | capacitor for longer distance connection        |

| C6, C7           | 1.0~3.3uF                     | capacitor for the regulator                     |

| D1               | _                             | diode for reverse bias protection (optional)    |

| RL_r, RL_g, RL_b | _                             | used to reduce the power dissipation of AL58221 |

<sup>\*</sup> Users may use suitable value for different applications.

### **Application Information (continued)**

#### **Power Dissipation**

When the 12 output channels are turned on, the practical power dissipation is determined by the following equation: ("Vout" is the output voltage @ turn-on and "Duty" is the max. percentage of turn-on.)

In secure operating conditions, the power consumption of an integrated chip should be less than the maximum permissible power dissipation, which is determined by the package type and ambient temperature. The formula for maximum power dissipation is described as follows:

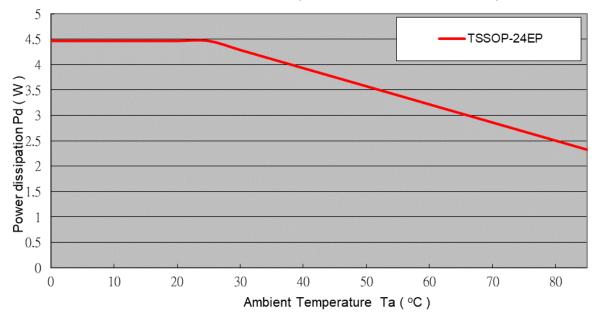

The PD(max) declines as the ambient temperature rises. Therefore, suitable operating conditions should be designed with caution according to the chosen package and the ambient temperature. The following figure illustrates the relation between the maximum power dissipation and the ambient temperature in the TSSOP-24EP package.

## Maximum Power Dissipation v.s. Ambient Temperature

#### **Design Tools** (Note 23)

- AL58221 Demo Board

- Demo Board Gerber File for PCB Layout Reference

Note: 23. Diodes' design tools can be found on our website at https://www.diodes.com/design/tools/.

AL58221 23 of 26

Document number: DS46476 Rev. 2 - 2 www.diodes.com

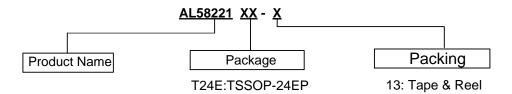

## **Ordering Information** (Note 24)

| Orderable Part Number | Paskaga                | Packing  |             |                    |  |

|-----------------------|------------------------|----------|-------------|--------------------|--|

| Orderable Fart Number | Package                | Quantity | Carrier     | Part Number Suffix |  |

| AL58221T24E-13        | TSSOP-24EP (Type A1-B) | 2500     | Tape & Reel | -13                |  |

Note: 24. For packaging details, go to our website at https://www.diodes.com/design/support/packaging/diodes-packaging/.

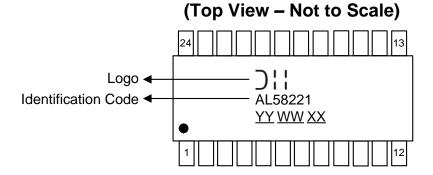

### **Marking Information**

Package: TSSOP-24EP (Type A1-B)

<u>YY</u>: Year: 23, 24, 25~ <u>WW</u>: Week: 01~52; 52

represents 52 and 53 week

XX : Internal Code

| Orderable Part Number | Package                | Identification Code |  |

|-----------------------|------------------------|---------------------|--|

| AL58221T24E-13        | TSSOP-24EP (Type A1-B) | AL58221             |  |

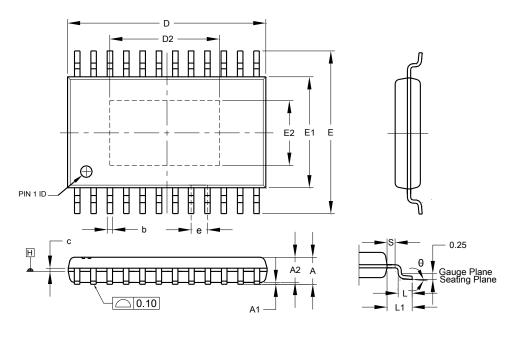

## **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

#### TSSOP-24EP (Type A1-B)

| TSSOP-24EP (Type A1-B) |          |      |      |  |  |

|------------------------|----------|------|------|--|--|

| Dim                    | Min      | Max  | Тур  |  |  |

| Α                      |          | 1.20 |      |  |  |

| A1                     | 0.00     | 0.15 |      |  |  |

| A2                     | 0.80     | 1.05 | 1.00 |  |  |

| b                      | 0.19     | 0.30 |      |  |  |

| С                      | 0.09     | 0.20 |      |  |  |

| D                      | 7.70     | 7.90 | 7.80 |  |  |

| D2                     | 3.70     | 4.62 |      |  |  |

| Е                      | 6.40 BSC |      |      |  |  |

| E1                     | 4.30     | 4.50 | 4.40 |  |  |

| E2                     | 2.28     | 2.85 |      |  |  |

| е                      | 0.65 BSC |      |      |  |  |

| L                      | 0.45     | 0.75 | 060  |  |  |

| L1                     | 1.00 REF |      |      |  |  |

| S                      | 0.20     |      |      |  |  |

| θ                      | 0°       | 8°   |      |  |  |

| All Dimensions in mm   |          |      |      |  |  |

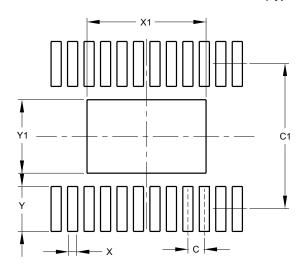

### **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

#### TSSOP-24EP (Type A1-B)

| Dimensions | Value<br>(in mm) |  |  |

|------------|------------------|--|--|

| С          | 0.650            |  |  |

| C1         | 5.600            |  |  |

| X          | 0.400            |  |  |

| X1         | 4.225            |  |  |

| Υ          | 1.800            |  |  |

| Y1         | 2.640            |  |  |

#### **Mechanical Data**

- Moisture Sensitivity: Level 3 per J-STD-020

- Terminals: Finish Matte Tin Plated Leads, Solderable per MIL-STD-202, Method 208 @3

- Weight: 0.096 grams (Approximate)

#### IMPORTANT NOTICE

- DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, guality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and

- Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- provided subject Diodes' Standard (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

- 9. This Notice may be periodically updated with the most recent version available at https://www.diodes.com/about/company/terms-andconditions/important-notice

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners. © 2024 Diodes Incorporated, All Rights Reserved.

www.diodes.com

26 of 26 AL58221 **April 2024** © 2024 Copyright Diodes Incorporated. All Rights Reserved. Document number: DS46476 Rev. 2 - 2 www.diodes.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**Diodes Incorporated:**

AL58221T24E-13