#### **FEATURES AND BENEFITS**

- · AEC-Q100 Grade 1 qualified

- Functional safety capable: Documentation available to aid functional safety system design

- $V_{IN}$  operating range: 5 to 72 V

- Continuous output current: 1.5 A

- V<sub>OUT</sub> selectable: 3.3 V, 5 V, 5.35 V, or 12 V

- Integrated V<sub>IN</sub> and boot capacitor to reduce component count and achieve ultra-low EMI

- Thermally enhanced and space saving 4 mm × 4 mm × 2.1 mm wettable-flank QFN package

- 28  $\mu$ A no-load quiescent current (48  $V_{IN}$  to 12  $V_{OUT}$ )

- $< 2 \mu A V_{IN}$  shutdown current

- 2.15 MHz internally fixed and adjustable from 400 kHz to 2.4 MHz

- Average-current mode control

- · Selectable frequency dithering to reduce EMI

- · Accurate enable threshold

- Robust protection against:

- □ Adjacent pin-to-pin short

- □ Pin-to-ground short

- □ Component open/short faults

#### **APPLICATIONS**

#### 48 V Automotive Systems:

- Electric power steering

- DC-DC converters

- Battery-management systems

- · Inverter and motor control

- · Lighting and infotainment

#### **PACKAGE**

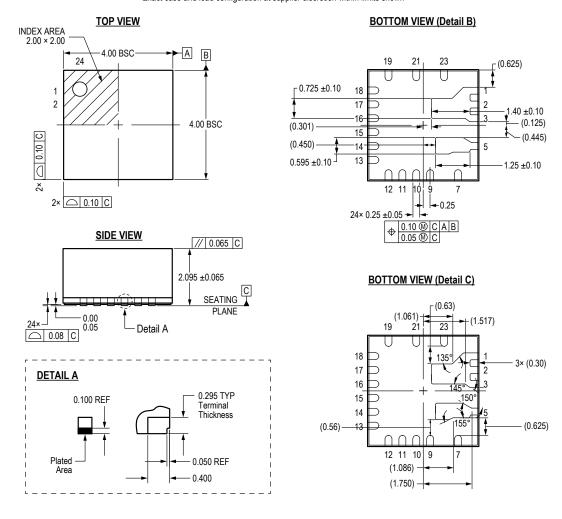

24-pin, 4 mm × 4 mm x 2.1 mm QFN with exposed thermal pads and wettable flank (suffix NB)

Not to scale

#### **DESCRIPTION**

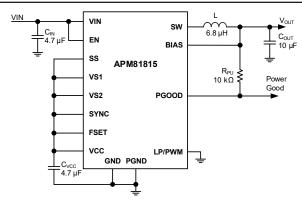

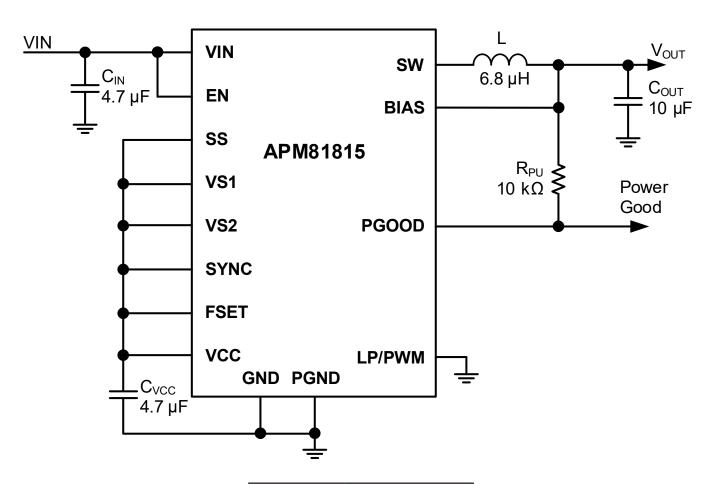

The APM81815 is a highly integrated DC-DC regulator with very low electromagnetic interference (EMI) and an ultra-compact footprint. It is optimized to power low-voltage automotive electronics directly from the 48 V battery bus. The simple regulator design requires only a few external components. Critical power paths are contained within the package itself, which leads to very minimal EMI and ease of printed circuit board (PCB) layout. The bootstrap and high-frequency input capacitors are contained within the APM81815, which simplifies PCB design and improves EMI. The control-loop compensation is also internal, which further simplifies the PCB design. The APM81815 delivers up to 1.5 A at 3.3 V, 5 V, 5.35 V, or 12 V output voltages, selectable through pin configuration.

Flexibility to adjust functions—such as soft-start, switching frequency, or frequency dithering—is possible through pin configurations; alternatively, these pins can be tied to VCC or GND to minimize external components. The synchronous, low-EMI average-current mode-control scheme assures practical operation at the high ambient temperatures that are typical of the automotive under-hood environment. EMI mitigation and electromagnetic compatibility (EMC) are achieved with minimal filtering, and the frequency-dithering feature offers further reductions to easily achieve CISPR25 Class 5 compliance.

The comprehensive array of built-in protection and monitoring features include thermal shutdown, power good, output overvoltage/undervoltage (OV/UV), pulse-by-pulse current limit, and output short-circuit protection.

The APM81815 is offered in a space-saving 4 mm  $\times$  4 mm  $\times$  2.1 mm quad-flat no-lead (QFN) package with wettable flanks and exposed thermal pads.

Figure 1: APM81815 Typical Application Circuit

# 80 V, 1.5 A, Synchronous Buck Regulator with Low EMI and 28 μA Quiescent Current

#### **SELECTION GUIDE**

| Part Number    | Description                                                      | Packing [1]                     | Lead Finish |

|----------------|------------------------------------------------------------------|---------------------------------|-------------|

| APM81815KNBJTR | 24-pin, 4 mm × 4 mm × 2.1 mm QFN package<br>with wettable flanks | 3000 pieces<br>per 13-inch reel | Matte Tin   |

<sup>[1]</sup> For additional packing options, contact Allegro.

#### **ABSOLUTE MAXIMUM RATINGS** [1]

| Characteristic                        | Symbol                            | Notes                             | Rating                                         | Unit |

|---------------------------------------|-----------------------------------|-----------------------------------|------------------------------------------------|------|

| VIN, EN                               | V <sub>IN</sub> , V <sub>EN</sub> |                                   | -0.3 to 80                                     | V    |

| SW                                    | \/                                | Continuous                        | -0.3 to (V <sub>IN</sub> + 0.3) <sup>[2]</sup> | V    |

| Svv                                   | $V_{SW}$                          | V <sub>IN</sub> ≤ 72 V, t < 50 ns | –1 V, V <sub>IN</sub> + 2                      | V    |

| BIAS                                  | V <sub>BIAS</sub>                 |                                   | -0.3 to 26                                     | V    |

| PGOOD                                 | V <sub>PGOOD</sub>                |                                   | –0.3 to 17                                     | V    |

| VCC, VS1, VS2, SYNC, SS, FSET, LP/PWM |                                   |                                   | -0.3 to 4                                      | V    |

| Junction Temperature                  | T <sub>J</sub>                    |                                   | -40 to 150                                     | °C   |

| Storage Temperature Range             | T <sub>STG</sub>                  |                                   | -55 to 150                                     | °C   |

<sup>[1]</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS

| Characteristic                              | Symbol                   | Test Conditions [1]                          | Value | Unit |

|---------------------------------------------|--------------------------|----------------------------------------------|-------|------|

| Package Thermal Resistance R <sub>θJA</sub> | В                        | Package, 4-layer PCB based on JEDEC standard | 56    | °C/W |

|                                             | Allegro evaluation board | 28                                           | °C/W  |      |

<sup>[1]</sup> Additional thermal information available on the Allegro website.

<sup>[2]</sup> This voltage is a function of temperature.

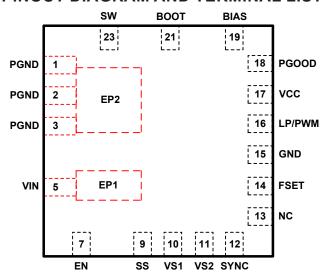

### PINOUT DIAGRAM AND TERMINAL LIST

Figure 2: QFN-24 Pinout Diagram—24-Pin 4 mm × 4 mm × 2.1 mm Wettable Flank QFN Package

| Num-<br>ber | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3     | PGND   | Power ground pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5           | VIN    | Input voltage pin. Place a 4.7 μF ceramic bypass capacitor from VIN to PGND very close to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7           | EN     | Enable pin. Pull this pin high to enable the part. Connect EN directly to VIN for "always-on" applications.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9           | SS     | To use the internal soft-start ramp, connect SS to VCC. To configure a different soft-start time, connect a capacitor between SS and GND.                                                                                                                                                                                                                                                                                                                                                                                    |

| 10          | VS1    | Output voltage selection pin 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11          | VS2    | Output voltage selection pin 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12          | SYNC   | Synchronization clock input and the frequency dither (spread spectrum) mode selection input.  Internal clock with dither: To use internal 2.15 MHz clock and enable frequency dithering, connect SYNC to VCC.  Internal clock without dither: To use internal 2.15 MHz clock without frequency dithering, connect SYNC to GND.  External clock without dither: To synchronize the switching frequency to an external clock between 400 kHz and 2.5 MHz, apply an external clock to SYNC. Dithering is disabled in this mode. |

| 13          | NC     | Connect this pin to ground or VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14          | FSET   | Switching-frequency programming pin. To set the switching frequency, connect a resistor, R <sub>FSET</sub> , from this pin to GND. To program a fixed 2.15 MHz (typical) frequency, connect FSET directly to VCC.                                                                                                                                                                                                                                                                                                            |

| 15          | GND    | Analog ground pin. Connect to PGND at the pad under the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16          | LP/PWM | Low-power mode/fixed-frequency PWM mode pin.  Low: Allows the device to enter low-power (LP) mode at light loads.  High: Forces fixed-frequency PWM mode.                                                                                                                                                                                                                                                                                                                                                                    |

| 17          | VCC    | Internal voltage regulator bypass capacitor pin. Connect a 4.7 µF ceramic capacitor from VCC to GND very close to this pin.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18          | PGOOD  | Power-good open-drain output signal. Connect a pull-up resistor to this pin. If the output voltage is out of range (undervoltage or overvoltage), this pin asserts low.                                                                                                                                                                                                                                                                                                                                                      |

| 19          | BIAS   | Connect this pin to the output of the regulator. Provides output voltage feedback and powers the internal LDO when the output voltage level is in regulation.                                                                                                                                                                                                                                                                                                                                                                |

| 21          | воот   | Do not connect external components to BOOT. This pin is provided for testing purposes.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 23          | SW     | Regulator switch-node output pin. Connect this pin to the power inductor and keep this node small to minimize EMI.                                                                                                                                                                                                                                                                                                                                                                                                           |

| EP1         | Pad 1  | This exposed back pad is connected to VIN. To optimize thermal dissipation, connect it to a plane under the device.                                                                                                                                                                                                                                                                                                                                                                                                          |

| EP2         | Pad 2  | This exposed back pad is connected to PGND. To optimize thermal dissipation, connect it to a plane under the device.                                                                                                                                                                                                                                                                                                                                                                                                         |

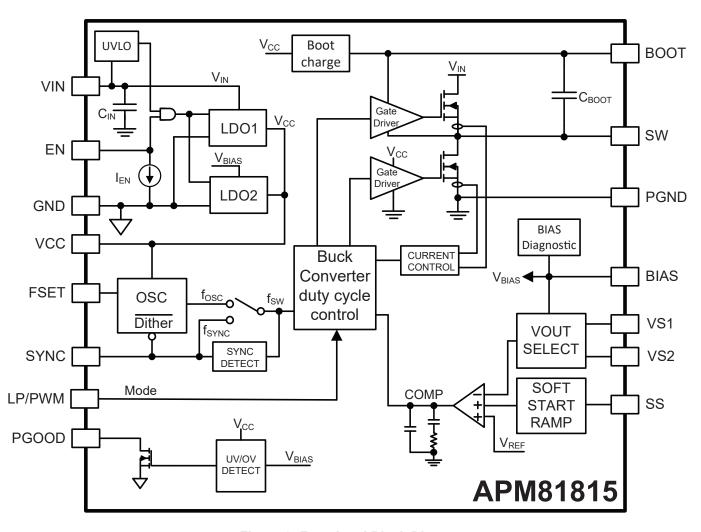

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 3: Functional Block Diagram

# 80 V, 1.5 A, Synchronous Buck Regulator with Low EMI and 28 $\mu$ A Quiescent Current

# **ELECTRICAL CHARACTERISTICS:** Valid for 5 V $\leq$ V<sub>VIN</sub> $\leq$ 72 V, $-40^{\circ}$ C $\leq$ T<sub>J</sub> $\leq$ 150°C, with typical values at 25°C, unless otherwise noted

| Characteristics                      | Characteristics Symbol Test Conditions |                                                                                                                            | Min.  | Тур.                       | Max.  | Unit               |

|--------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|----------------------------|-------|--------------------|

| INPUT SUPPLY                         |                                        |                                                                                                                            |       |                            |       |                    |

| Input Voltage Range                  | V <sub>VIN</sub>                       | V <sub>EN</sub> ≥ 2.5 V, after V <sub>VIN</sub> > V <sub>UVLO(ON,MAX)</sub>                                                | 5     | _                          | 72    | V                  |

| Undervoltage Lockout (UVLO) Start    | V <sub>UVLO(ON)</sub>                  | V <sub>VIN</sub> rising                                                                                                    | 4.2   | 4.8                        | 5.4   | V                  |

| Undervoltage Lockout (UVLO) Stop     | V <sub>UVLO(OFF)</sub>                 | V <sub>VIN</sub> falling                                                                                                   | 3.8   | 4.3                        | 5     | V                  |

| Undervoltage Lockout Hysteresis      | V <sub>UVLO(HYS)</sub>                 |                                                                                                                            | 300   | 450                        | 600   | mV                 |

| LP MODE INPUT SUPPLY CURRENT         | , , ,                                  |                                                                                                                            |       |                            | ,     |                    |

|                                      |                                        | $V_{VIN}$ = 12 V, $V_{EN} \ge 2.5$ V, $V_{OUT}$ = 3.3 V, no load, L = 6.8 $\mu$ H                                          | _     | 24                         | _     | μA                 |

| Input Supply Current, LP Mode [1][2] | I <sub>VIN(LP)</sub>                   | $V_{VIN}$ = 12 V, $V_{EN}$ $\geq$ 2.5 V, $V_{OUT}$ = 5 V, no load, L = 6.8 $\mu$ H                                         | -     | 31                         | _     | μА                 |

|                                      |                                        | $V_{VIN}$ = 48 V, $V_{EN}$ $\geq$ 2.5 V, $V_{OUT}$ = 12 V, no load, L = 6.8 $\mu$ H                                        | _     | 28                         | _     | μA                 |

| Input Supply Current, PWM Mode [1]   | I <sub>IN(PWM)</sub>                   | $V_{VIN} = 48 \text{ V}, V_{EN} \ge 2.5 \text{ V}, V_{OUT} = 5 \text{ V},$<br>$f_{SW} = 2.15 \text{ MHz}, \text{ no load}$ | -     | 6                          | _     | mA                 |

| Input Shutdown Current [1]           | I <sub>VIN(SD)</sub>                   | V <sub>VIN</sub> = 48 V, V <sub>EN</sub> = 0 V, T <sub>J</sub> = 25°C                                                      | _     | 2                          | 3     | μΑ                 |

| REGULATION ACCURACY                  |                                        |                                                                                                                            |       |                            |       |                    |

|                                      | V <sub>VOUT1</sub>                     | VS1 = 0, VS2 = 0                                                                                                           | 3.234 | 3.3                        | 3.366 | V                  |

| Output Voltage Accuracy              | V <sub>VOUT2</sub>                     | VS1 = 0, VS2 = 1                                                                                                           | 4.9   | 5                          | 5.1   | V                  |

| Output Voltage Accuracy              | V <sub>VOUT3</sub>                     | VS1 = 1, VS2 = 0                                                                                                           | 5.243 | 5.35                       | 5.457 | V                  |

|                                      | V <sub>VOUT4</sub>                     | VS1 = 1, VS2 = 1                                                                                                           | 11.76 | 12                         | 12.24 | V                  |

| SWITCHING FREQUENCY AND DITH         | ERING                                  |                                                                                                                            |       |                            |       |                    |

| Switching Frequency                  | f <sub>SW(I)</sub>                     | V <sub>FSET</sub> = V <sub>VCC</sub>                                                                                       | 1.9   | 2.15                       | 2.4   | MHz                |

| Switching Frequency                  | f <sub>SW(E)</sub>                     | Resistor from FSET to GND = 220 kΩ                                                                                         | 360   | 400                        | 440   | kHz                |

| Frequency Dither Range               | $\Delta f_{SW}$                        | V <sub>SYNC</sub> = V <sub>VCC</sub>                                                                                       | -6.5  | _                          | 6.5   | % f <sub>OSC</sub> |

| Minimum PWM Frequency with Dither    | f <sub>SW(MIN)</sub>                   | V <sub>FSET</sub> = V <sub>VCC</sub>                                                                                       | 1.8   | _                          | _     | MHz                |

| Dither Modulation Frequency          | f <sub>MOD(I)</sub>                    | V <sub>SYNC</sub> = V <sub>VCC</sub> , V <sub>FSET</sub> = V <sub>VCC</sub>                                                | _     | f <sub>SW(I)</sub><br>/256 | _     | MHz                |

| - Dianor modulusion resquency        | f <sub>MOD(E)</sub>                    | V <sub>SYNC</sub> = V <sub>VCC</sub> , frequency set by resistor                                                           | _     | f <sub>SW(E)</sub><br>/128 | _     | kHz                |

| SYNCHRONIZATION INPUT (SYNC PI       |                                        |                                                                                                                            |       |                            | 1     |                    |

| Synchronization Frequency Range      | f <sub>SW(SYNC)</sub>                  | V <sub>FSET</sub> = V <sub>VCC</sub>                                                                                       | 0.4   | -                          | 2.4   | MHz                |

| SYNC Duty Cycle [3]                  | D <sub>SYNC</sub>                      | V <sub>FSET</sub> = V <sub>VCC</sub>                                                                                       | -     | -                          | 90    | %                  |

| SYNC Pulse Width [3]                 | t <sub>PWSYNC</sub>                    | V <sub>FSET</sub> = V <sub>VCC</sub>                                                                                       | 30    | -                          | -     | ns                 |

| SYNC Voltage Threshold [3]           | V <sub>SYNC(HI)</sub>                  | V <sub>SYNC</sub> rising                                                                                                   | -     | -                          | 1.5   | V                  |

| CVAIC Die legest Commont [1]         | V <sub>SYNC(LO)</sub>                  | V <sub>SYNC</sub> falling                                                                                                  | 0.5   | - 0.4                      | -     | V                  |

| SYNC Pin Input Current [1]           | I <sub>SYNC</sub>                      | V <sub>SYNC</sub> = 5 V                                                                                                    | _     | 0.1                        | 1     | μA                 |

| PULSE WIDTH MODULATION (PWM)         | I INIING AND                           |                                                                                                                            |       | Ι                          | 0.5   | 1                  |

| Minimum Controllable SW On-Time [2]  | t <sub>ON(MIN)</sub>                   | V <sub>VIN</sub> = 12 V, I <sub>OUT</sub> = 1 A                                                                            | _     | _                          | 35    | ns                 |

| Minimum Controllele CIM OF Time [2]  |                                        | $V_{VIN} = 48 \text{ V, } I_{OUT} = 1 \text{ A}$                                                                           |       | -                          | 60    | ns                 |

| Minimum Controllable SW Off-Time [2] | t <sub>OFF(MIN)</sub>                  | V <sub>VIN</sub> = 12 V, I <sub>OUT</sub> = 1 A                                                                            | _     | 80                         | 140   | ns                 |

| LOW-POWER (LP) MODE                  |                                        | 0.7.17. 140.7.0 17. 5.15                                                                                                   |       | 0.5                        | l     |                    |

| LP Output Voltage Ripple [2]         | V <sub>PP(HLP)</sub>                   | $8 \text{ V} < \text{V}_{\text{VIN}} < 16 \text{ V}, \text{C}_{\text{OUT}} = 47 \mu\text{F}, \text{LP mode}$               | _     | 65                         | _     | mV                 |

Continued on the next page...

# 80 V, 1.5 A, Synchronous Buck Regulator with Low EMI and 28 $\mu$ A Quiescent Current

# ELECTRICAL CHARACTERISTICS (continued): Valid for 5 V $\leq$ V<sub>VIN</sub> $\leq$ 72 V, $-40^{\circ}$ C $\leq$ T<sub>J</sub> $\leq$ 150°C, with typical values at 25°C, unless otherwise noted

| Characteristics                                   | Symbol                   | Symbol Test Conditions                                                                        |       | Тур. | Max.  | Unit                    |  |

|---------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------|-------|------|-------|-------------------------|--|

| INTERNAL MOSFET PARAMETERS                        | 3                        |                                                                                               |       |      |       |                         |  |

| High Side On Besistance                           | В                        | $V_{BOOT} - V_{SW} = 3.3 \text{ V}, I_{DS} = 1 \text{ A}, T_{J} = 25^{\circ}\text{C}$         | _     | 150  | 190   | mΩ                      |  |

| High-Side On Resistance                           | R <sub>DSON(HS)</sub>    | $V_{BOOT} - V_{SW} = 3.3 \text{ V}, I_{DS} = 1 \text{ A}, T_{J} = 150^{\circ}\text{C}$ [2]    | _     | _    | 325   | mΩ                      |  |

| Law Cida On Basistanas                            | Б                        | V <sub>VCC</sub> = 3.3 V, I <sub>DS</sub> = 1 A, T <sub>J</sub> = 25°C                        | _     | 110  | 140   | mΩ                      |  |

| Low-Side On Resistance                            | R <sub>DSON(LS)</sub>    | V <sub>VCC</sub> = 3.3 V, I <sub>DS</sub> = 1 A, T <sub>J</sub> = 150°C [2]                   | _     | _    | 240   | mΩ                      |  |

| High-Side Leakage Current [2]                     | I <sub>LKG(HS)</sub>     | V <sub>VIN</sub> = 48 V, V <sub>EN</sub> = 0 V, V <sub>SW</sub> = 0 V, T <sub>J</sub> = 25°C  | _     | _    | 3.5   | μA                      |  |

| Low-Side Leakage Current [2]                      | I <sub>LKG(LS)</sub>     | V <sub>VIN</sub> = 48 V, V <sub>EN</sub> = 0 V, V <sub>SW</sub> = 48 V, T <sub>J</sub> = 25°C | _     | _    | 1.5   | μA                      |  |

| Gate Drive Nonoverlap Time [2]                    | t <sub>NO</sub>          | $V_{BOOT} - V_{SW} = 3.3 \text{ V}$                                                           | 0.5   | 1.75 | _     | ns                      |  |

| Switch Node Rising Slew Rate [2]                  | SRHS                     | 24 V ≤ V <sub>VIN</sub> ≤ 48 V, V <sub>BOOT</sub> − V <sub>SW</sub> = 3.3 V                   | _     | 3    | _     | V/ns                    |  |

| MOSFET CURRENT PROTECTION                         | THRESHOLDS               |                                                                                               |       |      | •     |                         |  |

| Pulse-By-Pulse High-Side Current Limit [3]        | I <sub>LIM(HS)</sub>     |                                                                                               | 2.1   | 2.6  | 3.2   | А                       |  |

| Pulse-By-Pulse Low-Side Valley<br>Current Limit   | I <sub>LIM(LS)</sub>     | LS remains on until current reduces to less than I <sub>LIM(LS)</sub>                         | _     | 2.75 | _     | А                       |  |

| Pulse-by-Pulse Low-Side Negative<br>Current Limit | I <sub>LIM(NEG)</sub>    |                                                                                               | _     | -1   | _     | А                       |  |

| INDUCTOR CURRENT LIMITS                           | '                        |                                                                                               | •     |      | ,     | •                       |  |

| Maximum Average Inductor Current Limit [1][2]     | I <sub>LIM(MAX)</sub>    | V <sub>OUT</sub> in regulation                                                                | _     | 2    | _     | А                       |  |

| Minimum Average Inductor Current Limit [1][2]     | I <sub>LIM(MIN)</sub>    | PWM mode                                                                                      |       | -0.6 | _     | А                       |  |

| SOFT-START                                        | ,                        |                                                                                               |       |      | ,     |                         |  |

| Soft-Start Delay Time [2]                         | t <sub>dSS</sub>         | C <sub>SS</sub> = 2.2 nF                                                                      | _     | 440  | _     | μs                      |  |

|                                                   | t <sub>SS(I)</sub>       | V <sub>SS</sub> = V <sub>VCC</sub><br>Soft-start time is measured from 0 to 1.2 V             | _     | 0.7  | _     | ms                      |  |

| Soft-Start Ramp Time [2]                          | t <sub>SS(E)</sub>       | C <sub>SS</sub> = 47 nF<br>Soft-start time is measured from 0 to 1.2 V                        | _     | 12   | _     | ms                      |  |

| Soft-Start Pin Current                            | I <sub>SS</sub>          | V <sub>SS</sub> = 0 V to 1.2 V                                                                | 4.5   | 5    | 5.5   | μA                      |  |

| OUTPUT VOLTAGE PROTECTION 1                       | THRESHOLDS (             | (BIAS OV/UV)                                                                                  | •     | •    |       | •                       |  |

| OV Threshold Rising                               | V <sub>VOUT(OVH)</sub>   |                                                                                               | 105.5 | 107  | 108.5 |                         |  |

| OV Threshold Falling                              | V <sub>VOUT(OVL)</sub>   |                                                                                               | _     | 104  | _     | - %<br>V <sub>OUT</sub> |  |

| OV Hysteresis                                     | V <sub>VOUT(OVHYS)</sub> |                                                                                               | _     | 3    | _     | VOUI                    |  |

| UV Threshold Rising                               | V <sub>VOUT(UVH)</sub>   |                                                                                               | _     | 98   | _     |                         |  |

| UV Threshold Falling                              | V <sub>VOUT(UVL)</sub>   |                                                                                               | 93.5  | 95   | 96.5  | V <sub>OUT</sub>        |  |

| UV Hysteresis                                     | V <sub>VOUT(UVHYS)</sub> |                                                                                               | _     | 3    | _     | OUT                     |  |

Continued on the next page...

# 80 V, 1.5 A, Synchronous Buck Regulator with Low EMI and 28 $\mu A$ Quiescent Current

# ELECTRICAL CHARACTERISTICS (continued): Valid for 5 V $\leq$ V<sub>VIN</sub> $\leq$ 72 V, $-40^{\circ}$ C $\leq$ T<sub>J</sub> $\leq$ 150°C, with typical values at 25°C, unless otherwise noted

| Characteristics                            | Characteristics Symbol Test Condition |                                                                                               | Min. | Тур. | Max. | Unit |

|--------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

| POWER GOOD OUTPUT (PGOOD                   | PIN)                                  |                                                                                               |      | ,    |      |      |

| OV Deglitch Time, V <sub>OUT</sub> Rising  | t <sub>PGOOD(OVR)</sub>               | Delay from V <sub>VOUT</sub> = V <sub>VOUT(OVH)</sub> to PGOOD high-to-low                    | 75   | 150  | 225  | μs   |

| OV Deglitch Time, V <sub>OUT</sub> Falling | t <sub>PGOOD(OVF)</sub>               | Delay from V <sub>VOUT</sub> = V <sub>VOUT(OVL)</sub> to PGOOD high-to-low                    | 20   | 40   | 60   | μs   |

| UV Deglitch Time, V <sub>OUT</sub> Rising  | t <sub>PGOOD(UVR)</sub>               | Delay from V <sub>VOUT</sub> = V <sub>VOUT(UVH)</sub> to PGOOD high-to-low                    | 125  | 250  | 375  | μs   |

| UV Deglitch Time, V <sub>OUT</sub> Falling | t <sub>PGOOD(UVF)</sub>               | Delay from V <sub>VOUT</sub> = V <sub>VOUT(UVL)</sub> to PGOOD high-to-low                    | 30   | 85   | 140  | μs   |

| PGOOD Initialization at Low VIN            | V <sub>PGOOD(INIT)</sub>              | V <sub>VIN</sub> = 1.5 V, V <sub>EN</sub> = 0 V, I <sub>PGOOD</sub> = 330 μA                  | _    | _    | 400  | mV   |

| PGOOD Low-Output Voltage                   | V <sub>PGOOD(L)</sub>                 | $V_{VIN} \ge 2.5 \text{ V}, V_{EN} \ge 2.5 \text{ V}, I_{PGOOD} = 4 \text{ mA}$               | _    | 150  | 400  | mV   |

| PGOOD Leakage Current [1]                  | I <sub>PGOOD</sub>                    |                                                                                               | _    | 0.1  | 6    | μA   |

| ENABLE INPUT                               |                                       |                                                                                               |      |      |      |      |

| EN High Threshold                          | V <sub>EN(HI)</sub>                   | V <sub>EN</sub> rising                                                                        | 1.15 | 1.2  | 1.25 | V    |

| EN Low Threshold                           | V <sub>EN(LO)</sub>                   | V <sub>EN</sub> falling                                                                       | _    | 1.05 | _    | V    |

| EN Input Hysteresis                        | V <sub>EN(HYS)</sub>                  | $V_{EN(HI)} - V_{EN(LO)}$                                                                     | _    | 150  | _    | mV   |

| Disable Delay                              | t <sub>DIS</sub>                      | V <sub>EN</sub> transitions low to when SW stops                                              | _    | 60   | _    | μs   |

| EN Pin Input Current [1]                   | I <sub>EN</sub>                       | V <sub>EN</sub> = 5 V                                                                         | _    | 100  | _    | nA   |

| INTERNAL REGULATOR (VCC PIN                | 1)                                    |                                                                                               |      |      |      |      |

| VCC Regulation Voltage                     | V <sub>cc</sub>                       | I <sub>VCC</sub> ≤ 10 mA, external loading                                                    | 3.1  | 3.3  | 3.5  | V    |

| VCC Maximum Load                           | I <sub>VCC(CL)</sub>                  |                                                                                               | _    | -    | 10   | mA   |

| BIAS Pin Input Threshold                   | V <sub>VOUT(TH)</sub>                 | If $V_{OUT}$ exceeds this threshold and $V_{IN}$ is greater than 6 V, the BIAS pin powers VCC | 2.9  | 3.05 | 3.2  | V    |

| BIAS Pin Input Current [1]                 | I <sub>VOUT</sub>                     | V <sub>VOUT</sub> < V <sub>VOUT(TH)</sub> (2.7 V <sub>MIN</sub> )                             | _    | 4    | -    | μA   |

| THERMAL SHUTDOWN PROTECT                   | ION (TSD)                             |                                                                                               |      |      |      |      |

| Thermal Shutdown Threshold [2]             | T <sub>TSD</sub>                      | T <sub>J</sub> rising                                                                         | 160  | 175  | 190  | °C   |

| Thermal Shutdown Hysteresis [2]            | T <sub>HYS</sub>                      |                                                                                               | _    | 20   | _    | °C   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), and positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Limits ensured by design, characterization, and statistical correlation. Only functionally tested in production.

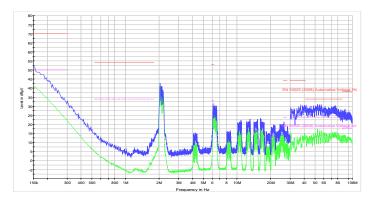

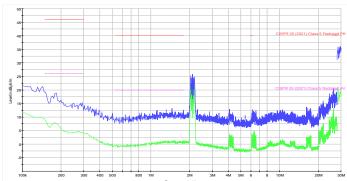

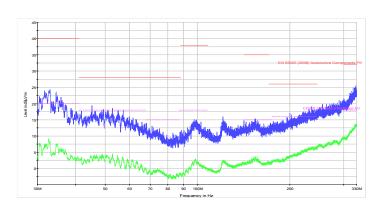

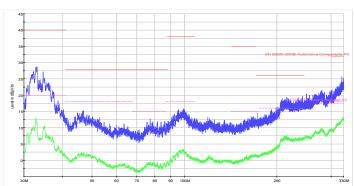

### **EMI/EMC PERFORMANCE CHARACTERISTICS**

$V_{IN} = 48 \text{ V}, V_{OUT} = 12 \text{ V}, f_{SW} = 2.15 \text{ MHz}$

Conducted Emissions (150 kHz to 30 MHz)

Radiated Emissions (150 kHz to 30 MHz) (Monopole)

Radiated Emissions (30 MHz to 330 MHz) (Horizontal Biconical)

Radiated Emissions (30 MHz to 330 MHz) (Vertical Biconical)

NOTE: Allegro is not an accredited EMC laboratory. The information presented here is for reference only.

# 80 V, 1.5 A, Synchronous Buck Regulator with Low EMI and 28 μA Quiescent Current

#### **FUNCTIONAL DESCRIPTION**

#### Overview

The APM81815 is a 72 V operational and 1.5 A maximum output current, high performance synchronous buck regulator designed specifically for demanding automotive, industrial, and commercial applications. The device simplifies regulator design by minimizing the number of required external components and therefore minimizing PCB area. The regulator combines on-board high-frequency input filtering and switching frequency dithering to significantly reduce its EMI/EMC signature. The APM818185 provides excellent output voltage accuracy, uses average current-mode control to deliver quite low minimum on-times, and is capable of jitter-free operation.

The APM81815 can be pin configured for 3.3 V, 5 V, 5.35 V, or 12 V and uses internal compensation. The input voltage can be as high as 72 V and the switching frequency can be programmed from 400 kHz to 2.4 MHz or can be synchronized to an external clock. The regulator has a high-voltage tolerant input on the EN pin that can be tied directly to VIN and has very accurate enable and disable voltage thresholds. It has an internally fixed soft-start time of 0.7 ms when SS pin is connected to VCC and can be programmed for longer times as required by adding capacitor from SS pin to GND.

Protection features include VIN undervoltage lockout, cycle-by-cycle current limit, average current limit, short-circuit protection, output overvoltage and undervoltage protection, and thermal shutdown.

### **Output Voltage Accuracy and Selection**

The APM81815 provides an output voltage accuracy of  $\pm 2\%$  over the entire rated junction temperature,  $-40^{\circ}\text{C} < \text{TJ} < 150^{\circ}\text{C}$ . It also monitors VOUT directly, so its accuracy is not compromised by an external resistor divider between VOUT and a feedback pin. This exceeds the traditional approach of using a  $\pm 1\%$  reference and an external resistor divider created with two  $\pm 1\%$  resistors.

The APM81815 offers the most common output voltages: 3.3 V, 5 V, 5.35 V, and 12 V. The output voltage is determined by setting the VS1 and VS2 pins as shown in Table 1. The VS1 and VS2 pins are sampled at power-up and the output voltage is internally latched at that time; the output voltage cannot change during operation, which prevents noise or transients from erroneously altering the output voltage.

Table 1: APM81815 Output Voltage Configuration

| VS1 | VS2 | VOUT (V) |

|-----|-----|----------|

| GND | GND | 3.3      |

| GND | VCC | 5.0      |

| VCC | GND | 5.35     |

| VCC | VCC | 12.0     |

## **Average-Current Mode Control**

The APM81815 uses average-current mode control to provide excellent noise immunity and very short minimum on-times, and it can deliver pulse widths that are virtually jitter free:

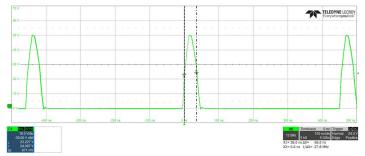

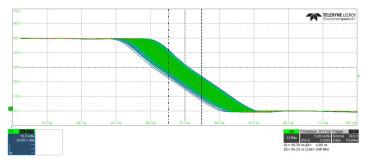

- Repeatable, closed-loop control with on-times of only 36 ns is demonstrated in Figure 4.

- Pulse-width jitter of 4.8 ns is shown in Figure 5.

The APM81815 employs internal compensation. This makes it very easy to use, reduces PCB area, and lowers cost. For optimal control-loop stability, select the external output LC filter components as follows:

Equation 1:  $C_{OUT} = 164/(V_{OUT} \times f_{SW})$

where,  $C_{OUT}$  is in  $\mu F$

Equation 2:  $L = 7.25/f_{SW}$

where L is in  $\mu H$  and  $f_{SW}$  is in MHz. A minimal inductance value must be selected so that the inductor current ripple does not reach the high/low-side current peak limits at full load. To avoid this instability, the inductance value must not exceed 18  $\mu H$ .

Compared to voltage mode control, current mode control is advantageous because it:

- Compensates for the effect of the output inductor, which reduces the order of the output filter.

- · Offers better line and load regulation.

- Simplifies control-loop compensation.

Peak-current mode control:

- Suffers from subharmonic oscillations, typically when the power switch duty cycle exceeds 50%, where additional slope compensation is needed to stabilize the converter.

- Provides poor noise immunity because the peak current is measured and compared to a DC reference level, and noise on the peak current measurement or DC reference can result in jitter.

- Requires a blanking time on the rising edge of the switch current to prevent false triggering upon diode reverse recovery.

This limits the minimum on-time and, therefore, how wide the conversion ratio can be.

In average-current mode control, these limitations are resolved, making it possible to regulate  $V_{OUT}$  with a constant switching frequency across a wide  $I_{OUT}$  and  $V_{IN}$  range.

Figure 4: Repeatable, Controlled On-Times of Only 36 ns, 48 V<sub>IN</sub>, 3.3 V<sub>OUT</sub>, 2.2 MHz at 400 mA Load

Figure 5: Pulse-Width Jitter with Dither Off, 48  $V_{IN}$ , 5  $V_{OUT}$ , 2.2 MHz at 1 A Load

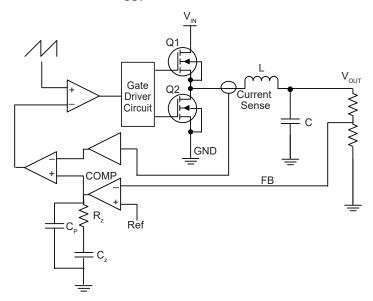

Figure 6:Typical Block Diagram of Average-Current Control Mode

#### **Low-Power Mode**

Use the LP/PWM pin to configure the light-load operation of the APM81815. Set the LP/PWM pin to logic low to allow the APM81815 to enter low power (LP) mode when in a light load condition. Connect the LP/PWM pin to a logic high, such as to the VCC pin, to prevent automatic low-power mode operation and always force PWM mode.

The part switches from PWM mode to LP mode when all the following conditions are satisfied for at least three consecutive clock cycles:

- Soft-start is complete

- The output voltage is 3% higher than the nominal output voltage and lower than the overvoltage threshold.

- The compensation voltage (COMP in Figure 6) reduces to less than 0.5 V

The part switches back from LP mode to PWM mode when at least one of the following conditions is satisfied:

- The overvoltage condition is triggered

- The compensation voltage (COMP in Figure 6) exceeds 0.55 V for at least 200 ns

While in LP mode, the output voltage is regulated in a hysteretic manner within a  $\pm 3\%$  window. When  $V_{OUT}$  reduces to less than 97% of the nominal value, the converter operates in critical-conduction mode, in which the inductor peak current is limited to 600 mA. When  $V_{OUT}$  reaches 103% of the nominal value, the converter stops switching until  $V_{OUT}$  again reduces to less than 97% of the nominal value.

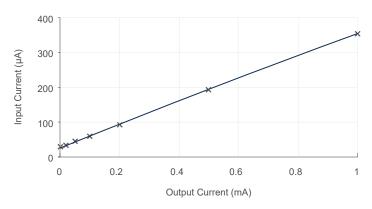

Low-power mode improves light-load efficiency with a tradeoff for higher output voltage ripple. The input current as a function of  $I_{OUT}$  from 0 to 1 mA is reported in Figure 7. To prevent the device from ever entering LP mode, force the mode to PWM mode by tying the LP/PWM pin high.

Figure 7: Low-Power Mode Input Current ( $V_{IN}$  = 48 V,  $V_{OUT}$  = 12 V, L = 6.8  $\mu$ H)

### Switching Frequency and Dithering

The switching frequency of the APM81815 can be set to an internally generated 2.15 MHz by connecting the FSET pin to VCC; or it can configured to a frequency between 400 kHz and 2.4 MHz with a resistor from the FSET pin to GND.

The value of the RFSET resistor connected from FSET pin to GND as a function of the switching frequency can be evaluated according to:

Equation 3:

$$R_{FSET} = [79200/(f_{SW} - 27)] - 7.3$$

where  $R_{FSET}$  is in  $k\Omega$  and  $f_{SW}$  is in kHz.

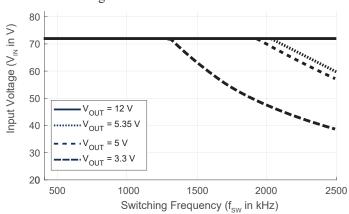

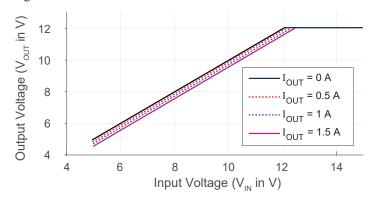

While choosing the PWM switching frequency, the designer should be aware of the minimum controllable on-time,  $t_{\rm ON(MIN)}$ , of the APM81815. If the required on-time of the system is less than the minimum controllable on-time, pulse-skipping occurs and the output voltage exhibits increased ripple. The constant-frequency input voltage region for the four output voltage selection cases is shown in Figure 8.

A typical fixed-frequency PWM regulator creates distinct and narrow peaks of energy at the switching frequency and at the harmonics of the switching frequency. The APM81815 dithering feature spreads the spectrum across a wider frequency band, which reduces the peak magnitude of each harmonic.

The dithering sweep is internally set at  $\pm 5\%$  typical  $(\Delta f_{SW}).$  This means the PWM switching frequency ramps from 0.95 to 1.05 times the internal switching frequency. However, the lowest switching frequency when using the FSET pin tied to VCC for  $f_{SW}=2.15$  MHz,  $f_{SW(I)(min)}-\Delta f_{SW(max)},$  is guaranteed not to reduce to less than 1.8 MHz; thus, the harmonics are kept out of the AM band. The dither-modulation frequency  $(f_{MOD})$  sweeps a triangular pattern that operates at approximately:  $f_{SW}/256$  when the FSET pin is tied to VCC; or  $f_{SW}/128$  when the FSET pin is tied to GND through a resistor.

Figure 8: Input Voltage Limit to Prevent Pulse-Skipping Measured at I<sub>OUT</sub> = 100 mA

# 80 V, 1.5 A, Synchronous Buck Regulator with Low EMI and 28 μA Quiescent Current

## **Synchronization Input**

The SYNC pin has three possible operating states:

- To use the internal clock with frequency dithering, tie the SYNC pin high.

- To use the internal clock without dithering, tie the SYNC pin low.

- To synchronize the APM81815 switching frequency with an external clock, drive the SYNC pin with an external clock.

If the SYNC pin is connected to GND or if an external clock is applied to the SYNC pin, frequency dithering is disabled.

For the internal control-loop compensation to operate properly when the SYNC pin is driven with an external clock, the FSET pin must be configured to a switching frequency similar to that of the external clock.

**Table 2: SYNC and FSET Configuration Truth Table**

| FSET Pin        | SYNC Pin       | Switching<br>Frequency | Dither   |

|-----------------|----------------|------------------------|----------|

| VCC             | VCC            | 2.15 MHz               | Enabled  |

| VCC             | GND            | 2.15 NITZ              | Disabled |

| Resistor to     | VCC            | Configurable,          | Enabled  |

| GND             | GND            | 400 kHz – 2.4 MHz      | Disabled |

| Resistor to GND | External Clock | External Clock         | Disabled |

# Dropout

The APM81815 is designed to operate at extremely low switching frequency during dropout conditions (low input voltage) in such a way as to minimize output voltage drop. The measured output voltage when  $V_{OUT}$  is set at 12 V in the forced PWM condition at 2.15 MHz with  $V_{IN}$  reducing to UVLO is shown in Figure 9.

Figure 9: 12 V Output Voltage Dropout at Low V<sub>IN</sub>

#### Soft-Start

If a fault is not present and EN transitions high, the regulator begins its soft-start routine. When the SS pin is connected to VCC, the soft-start time is internally fixed at 0.7 ms. Longer soft-start times can be achieved with a capacitor from the SS pin to GND. The SS pin sources a 5  $\mu$ A (typical) current to charge the external capacitor. The soft-start time can be set based on:

Equation 4:

$$t_{SS} = 0.22 \times C_{SS}$$

where,  $t_{SS}$  is in ms, and  $C_{SS}$  is in nF. The total range for  $C_{SS}$  is 1 nF to 100 nF.

During soft-start, the APM81815 does not check the state of the LP/PWM pin and is forced into PWM mode; the device may operate in burst mode or discontinuous mode.

# Undervoltage Lockout (UVLO)

An undervoltage lockout (UVLO) comparator continuously monitors the voltage at the VIN pin and keeps the regulator disabled if the voltage is less than the lockout threshold,  $V_{\rm UVLO(ON)}$ . The UVLO comparator incorporates enough hysteresis, 450 mV (typical), to prevent on/off cycling of the regulator due to voltage drop in the  $V_{\rm IN}$  path during heavy loading or during startup.

## **Enable/Undervoltage Lockout Function**

The enable/undervoltage input (EN) pin allows the system to selectively enable and disable the regulator. The EN pin is rated to 80 V, so the regulator can be tied directly to VIN or the output of another regulator. If the EN pin is floating, an internal pull-down current pulls the voltage down and disables the regulator.

The enable input leads to a hysteretic comparator with a threshold to enable the device of 1.2 V (typical). Once enabled, the EN comparator has a typical hysteresis of 150 mV. If EN reduces to less than the turn-off threshold for a duration longer than t<sub>DIS</sub> (disable delay), the APM81815 enters shutdown.

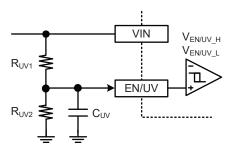

The EN pin can be used with a voltage divider from VIN to create a configurable undervoltage lockout threshold, as shown in Figure 10.

CEN is recommended to filter out any transients on the input line.

Select a convenient value for REN2 and calculate REN1 to estimate the rising enable threshold level using:

Equation 5:

$$R_{EN1} = \frac{V_{INTH(RISE)} - V_{EN(HI)}}{I_{EN} + \frac{V_{EN(HI)}}{R_{EN2}}}$$

where  $V_{\rm INTH(RISE)}$  is the desired threshold of rising input voltage to enable the APM81815 and  $I_{\rm EN}$  is the EN pin input current.

Once both resistors are known, estimate the falling input voltage threshold level using:

Equation 6:

$$V_{INTH(FALL)} = (V_{EN(HI)} - V_{EN(HYS)}) \left(\frac{R_{EN1} + R_{EN2}}{R_{EN2}}\right) + I_{EN}R_{EN1}$$

For  $V_{EN(HI)},\,V_{EN(HYS)},$  and  $I_{EN},$  refer to the Electrical Characteristics table.

Figure 10: Input Undervoltage Lockout with EN Pin

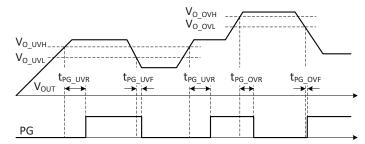

## **Power Good (PGOOD)**

PGOOD is an open-drain output that drives its output low when  $V_{OUT}$  is out of regulation. To enable the  $V_{OUT}$  status to be signaled, PGOOD must be pulled up to another voltage rail with a resistor:

- If V<sub>OUT</sub> is within regulation, the PGOOD pin is in a highimpedance state and the output signal is pulled up to the external voltage.

- If V<sub>OUT</sub> is out of regulation, PGOOD is pulled low to alert the system.

- If PGOOD is not used, the PGOOD pin can be left floating or grounded.

PGOOD operation is shown in detail in Figure 11. For time and voltage values, refer to the Electrical Characteristics table.

**Figure 11: Power Good Operation**

# Pulse-by-Pulse Current Limit

The current in the high-side MOSFET is monitored on a cycle-by-cycle basis. If the high-side current exceeds  $I_{LIM(HS)}$ , the high-side MOSFET is turned off. Similarly, the current in the low-side MOSFET is monitored on a cycle-by-cycle basis. If the low-side current exceeds  $I_{LIM(LS)}$ , the low-side MOSFET is turned off. This protects the MOSFETs from excessive current, overheating, and possible damage.

# **Output Short-Circuit Protection**

The APM81815 incorporates an output short-circuit protection to prevent device damage.

Referring to the Fault Mode Table, for the output short-circuit condition, the inductor should not saturate, given the highest peak current limit  $(I_{LIM(HS)})$  at minimum duty cycle.

When this fail occurs, the device latches up; to restore the typical regulation behavior, it is necessary to toggle the EN pin.

# 80 V, 1.5 A, Synchronous Buck Regulator with Low EMI and 28 μA Quiescent Current

#### **SW Pin Protection**

If the SW pin is shorted to ground, very high current occurs in the high-side MOSFET. When the regulator detects this unusually high current (I<sub>LIM(HS)</sub>), it instantly turns off the high-side MOSFET and latches-off the device. To restart the device, the enable or the input voltage must be cycled.

#### **BOOT Pin Protections**

To detect BOOT related faults, the APM81815 monitors the voltage across the internal BOOT capacitor. During faulty conditions, the converter remains off.

### Overvoltage Protection (OVP)

The APM81815 provides a fundamental level of overvoltage protection. If  $V_{OUT}$  exceeds the overvoltage threshold (107%,  $V_{OUT(OVH)})$  for longer than the deglitch time  $(t_{PGOOD(OVR)})$ , the high-side MOSFET shuts off. Also, to correct the overvoltage condition, the low-side MOSFET turns on and sinks current from VOUT. Each PWM cycle, the low-side MOSFET is allowed to be on until the inductor current reaches the negative current limit  $(-1\ A,\ I_{LIM(NEG)})$  of the low-side MOSFE .

### **Thermal Protection**

The device protects itself from overheating by means of an internal thermal monitoring circuit. If the junction temperature exceeds the thermal shutdown threshold ( $T_{TSD}$ , 175°C, typical), the high-side and low-side MOSFETs are shut off, the BOOT charger is shut down, and the internal control circuits are reset. When the junction temperature decreases more than the thermal shutdown hysteresis ( $T_{HYS}$ , 20°C, typical), the regulator automatically restarts.

# Pin-to-Ground and Adjacent Pin Short Protections

The APM81815 is designed to satisfy the most demanding applications. For example, the device is designed to withstand a short circuit to ground at each pin without sustaining damage. In addition, care was taken when defining the device pinout to optimize protection against adjacent pin-to-pin short circuits. For example, logic pins and high-voltage pins are separated as much as possible. Inevitably, some low-voltage pins are located adjacent to high-voltage pins; however, in these instances, the low-voltage pins are designed to withstand unusually high voltages with clamps and/or series input resistance to prevent damage to the device.

A comprehensive summary of all fault conditions and the response of the regulator in each case is shown in the Fault Mode Table.

# 80 V, 1.5 A, Synchronous Buck Regulator with Low EMI and 28 $\mu A$ Quiescent Current

### **FAULT MODE TABLE**

|                                                      | Internal                                                                             | During Fault Counting          |                                      | Boot                                            | Power                                               | Latched | Reset                                                            |

|------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------|--------------------------------------|-------------------------------------------------|-----------------------------------------------------|---------|------------------------------------------------------------------|

| Fault Mode                                           | Soft-Start                                                                           | High-Side<br>MOSFET            | Low-Side<br>MOSFET                   | Charging                                        | Good                                                | Fault?  | Condition                                                        |

| VIN Undervoltage                                     | Pulled low via 2 kΩ resistor, no hiccup                                              | Forced turn-off                | Forced turn-off                      | Disabled                                        | Depends on V <sub>OUT</sub>                         | NO      | Automatic,<br>V <sub>IN</sub> exceeds UV start<br>threshold      |

| Output/BIAS Pin<br>Shorted to<br>Ground              | Not affected                                                                         | Forced turn-off                | Forced turn-off                      | Not affected                                    | Pulled low                                          | YES     | Toggle VIN or EN                                                 |

| Output<br>Overcurrent                                | · INOTATION                                                                          |                                | Turned-on if boot voltage is too low | Not affected                                    | Depends on V <sub>OUT</sub>                         | NO      | Automatic                                                        |

| High-Side MOSFET<br>Overcurrent<br>(SW Short to GND) | Not affected                                                                         | Forced turn-off                | Forced turn-off                      | Not affected                                    | Pulled low                                          | YES     | Toggle VIN or EN                                                 |

| Low-Side MOSFET                                      | Not affected                                                                         | Forced turn-off                | Forced turn-off                      | Not affected                                    | Pulled low                                          | NO      | Automatic, short removed                                         |

| (SW Short to VIN)                                    | For high V <sub>IN</sub> values                                                      | , the IC could be da           | amaged                               |                                                 |                                                     |         |                                                                  |

| Boot Pin Fault                                       | Not affected                                                                         | Forced turn-off                | Forced turn-off                      | The device tries to recharge the boot capacitor | Depends on V <sub>OUT</sub>                         | NO      | Automatic,<br>fault removed                                      |

| Output<br>Overvoltage                                | Not affected                                                                         | Turned-off by regulation       | Pulsed with minimum off-time         | Disabled when V <sub>BIAS</sub> is too high     | Pulled low<br>when V <sub>BIAS</sub> is<br>too high | NO      | Automatic,<br>after V <sub>OUT</sub> returns to<br>typical range |

| Output<br>Undervoltage                               | Not affected                                                                         | Active, responds to regulation | Turned-on if boot voltage is too low | Not affected                                    | Pulled low<br>when V <sub>OUT</sub> is<br>too low   | NO      | Automatic,<br>after V <sub>OUT</sub> returns to<br>typical range |

| BIAS Pin Open                                        | Not affected                                                                         | Turned-off by regulation       | Pulsed with minimum off-time         | Disabled                                        | Pulled low                                          | NO      | Automatic,<br>after V <sub>BIAS</sub> pin fault is<br>removed    |

| Thermal<br>Shutdown<br>(TSD)                         | Pulled low<br>until V <sub>SS</sub> < V <sub>SSRST</sub><br>and T <t<sub>TSD</t<sub> | Forced turn-off                | Forced turn-off                      | Disabled                                        | Pulled low                                          | NO      | Automatic,<br>part cools down                                    |

### **APPLICATION CIRCUIT**

| VIN             | 5 – 72   | V   |

|-----------------|----------|-----|

| VOUT            | 12       | V   |

| LP Mode         | Disabled |     |

| f <sub>SW</sub> | 2.15     | MHz |

| Dithering       | Enabled  |     |

| Soft-Start Time | 0.7      | ms  |

Figure 12: Application Circuit

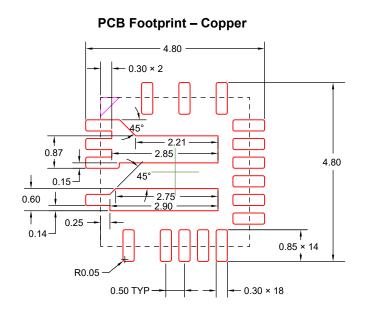

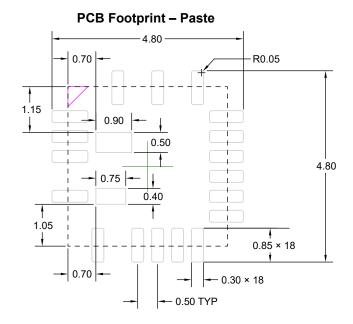

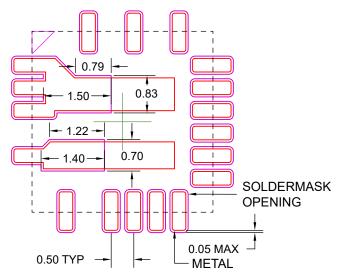

# PACKAGE OUTLINE DRAWING AND RECOMMENDED PCB FOOTPRINT For Reference Only – Not for Tooling Use

(Reference Allegro DWG-0000820, Rev. 2, incl. Appendix: APM81815)

NOT TO SCALE

Dimensions in millimeters

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

#### STANDARD BRANDING REFERENCE VIEW

Line 1: Part Number

Line 2: Logo A, 4 digit Date Code

Line 3: Assembly Lot Number

Figure 13: 24-Lead 4 mm × 4 mm QFN (Suffix NB)

### **PCB LAYOUT GUIDELINES**

### PCB Footprint - Soldermask

Figure 14: Recommended PCB Footprint

Altium and Cadence schematic and layout library files for the APM81815 are provided on the APM81815 product page on Allegromicro.com.

# 80 V, 1.5 A, Synchronous Buck Regulator with Low EMI and 28 μA Quiescent Current

#### **Revision History**

| Number | Date             | Description     |

|--------|------------------|-----------------|

| _      | October 17, 2024 | Initial release |

Copyright 2024, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Allegro MicroSystems:

APM81815KNBJTR