# Low-Noise, High-Precision, Programmable Linear Hall-Effect Sensor IC with Regulated Supply, Advanced Temperature Compensation, and High-Bandwidth (240 kHz) Analog Output

#### **FEATURES AND BENEFITS**

- 240 kHz nominal bandwidth achieved via proprietary packaging and chopper stabilization techniques

- On-board supply regulator with reverse-battery protection

- Proprietary segmented linear temperature compensation (TC) technology provides a typical accuracy of 1% over the full operating temperature range

- Customer-programmable, high-resolution offset and sensitivity trim

- Factory-programmed sensitivity and quiescent output voltage TC with extremely stable temperature performance

- High-sensitivity Hall element for maximum accuracy

- Extremely low noise and high resolution achieved via proprietary Hall element and low-noise amplifier circuits

Continued on the next page...

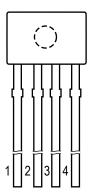

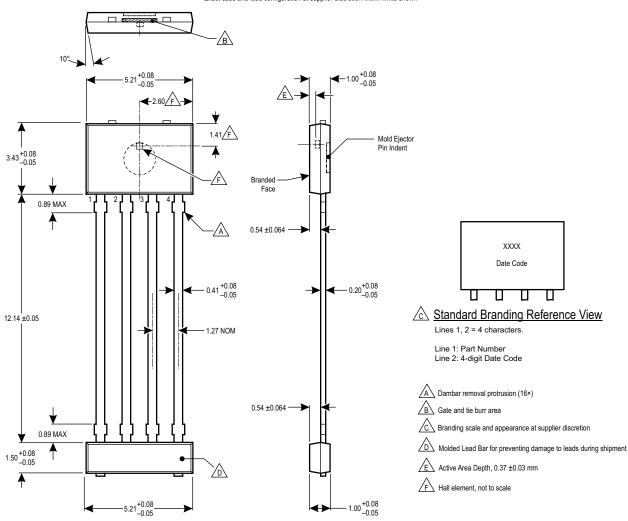

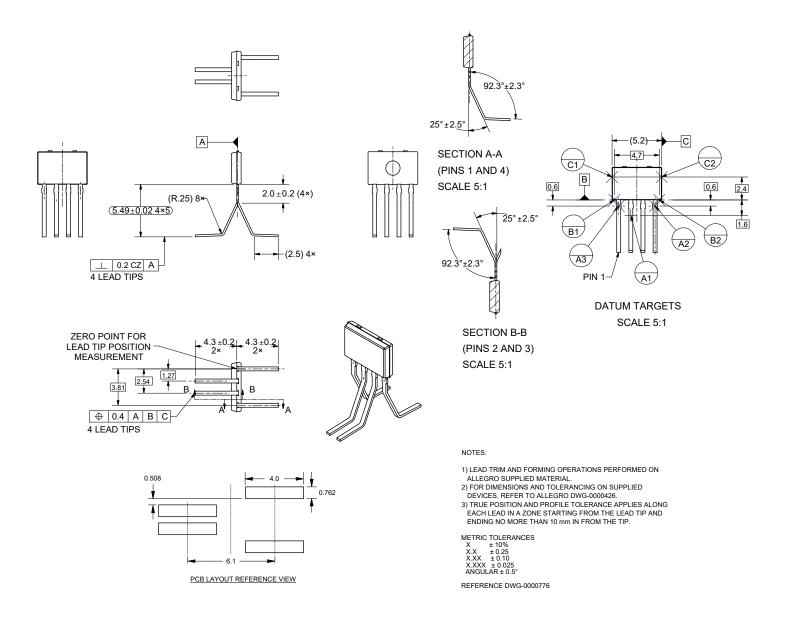

### PACKAGE: 4-pin SIP (suffix KT)

Not to scale

Contact Allegro about legacy leadform options

**TH Leadform**

#### **DESCRIPTION**

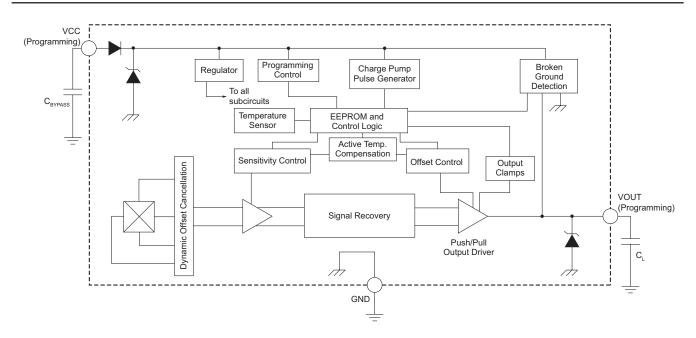

The Allegro<sup>TM</sup> A1367 programmable linear Hall-effect current sensor IC has been designed to achieve high accuracy and resolution without compromising bandwidth. This goal is achieved through new proprietary linearly interpolated temperature compensation technology that is programmed at the Allegro factory and provides sensitivity and offset that are virtually flat across the full operating temperature range. Temperature compensation is performed in the digital domain with integrated EEPROM technology while maintaining a 240 kHz bandwidth analog signal path, making this device ideal for HEV inverter, DC-to-DC converter, and electric power steering (EPS) applications.

This ratiometric Hall-effect sensor IC provides a voltage output that is proportional to the applied magnetic field. The customer can configure the sensitivity and quiescent (zero field) output voltage through programming on the VCC and output pins, to optimize performance in the end application. The quiescent output voltage is user-adjustable, around 50% (bidirectional configuration) or 10% (unidirectional configuration) of the supply voltage,  $V_{\rm CC}$ , and the output sensitivity is adjustable within the range of 0.6 to 6.4 mV/G.

The sensor IC incorporates a highly sensitive Hall element with a BiCMOS interface integrated circuit that employs a low-

Continued on the next page...

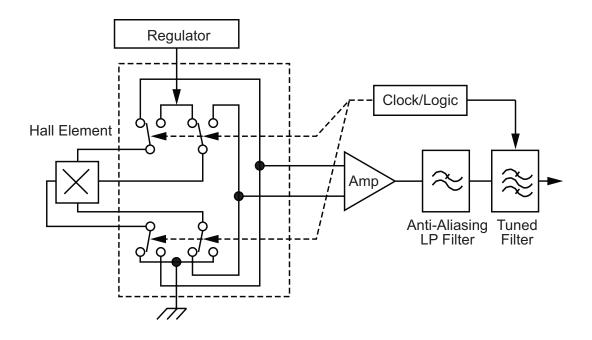

**Functional Block Diagram**

### FEATURES AND BENEFITS (continued)

- Patented circuits suppress IC output spiking during fast current step inputs

- Open circuit detection on ground pin (broken wire)

- Selectable sensitivity range between 0.6 and 6.4 mV/G through use of coarse sensitivity program bits

- User-selectable ratiometric behavior of sensitivity, quiescent voltage, and clamps (ratiometry can be disabled), for simple interface with application A-to-D converter (ADC)

- Precise recoverability after temperature cycling

- Output voltage clamps provide short-circuit diagnostic capabilities

- Wide ambient temperature range: -40°C to 150°C

- · Immune to mechanical stress

- Extremely thin package: 1 mm case thickness

- · AEC-Q100 automotive qualified

# **DESCRIPTION** (continued)

noise small-signal high-gain amplifier, a clamped low-impedance output stage, and a proprietary, high-bandwidth dynamic offset cancellation technique. These advances in Hall-effect technology work together to provide an industry-leading sensing resolution at the full 240 kHz bandwidth. Broken ground wire detection as well as user-selectable output voltage clamps also are built into this device for high reliability in automotive applications.

Device parameters are specified across an extended ambient temperature range: -40°C to 150°C. The A1367 sensor IC is provided in an extremely thin case (1 mm thick), 4-pin SIP (single in-line package, suffix KT) that is lead (Pb) free, with 100% matte-tin leadframe plating.

#### **SELECTION GUIDE**

| Part Number [1]     | Leadform      | Package   | Packing [2]                  | Sensitivity Range <sup>[3]</sup><br>(mV/G) |

|---------------------|---------------|-----------|------------------------------|--------------------------------------------|

| A1367LKTTN-1B-T     | TN (Straight) | 4-pin SIP | 4000 pieces per 13-inch reel | SENS_COARSE 00: 0.6 to 1.3                 |

| A1367LKTTN-2B-T [4] | TN (Straight) | 4-pin SIP | 4000 pieces per 13-inch reel | SENS_COARSE 01: 1.3 to 2.9                 |

| A1367LKTTN-2U-T [5] | TN (Straight) | 4-pin SIP | 4000 pieces per 13-inch reel | SENS_COARSE 01: 1.3 to 2.9                 |

| A1367LKTTN-5B-T [4] | TN (Straight) | 4-pin SIP | 4000 pieces per 13-inch reel | SENS COARSE 10: 2.9 to 6.4                 |

<sup>[1]</sup> TH package leadform options available.

### **Table of Contents**

| Features and Benefits    | 1 | Pinout Diagram and Terminal List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4              |

|--------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Description              | 1 | Operating Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| Package                  |   | Characteristic Performance Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Functional Block Diagram |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12             |

| Selection Guide          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1              |

| Specifications           | 3 | Programming Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2 <sup>-</sup> |

| Absolute Maximum Ratings |   | Package Outline Drawings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2              |

| Thermal Characteristics  |   | , and the second |                |

<sup>[2]</sup> Contact Allegro for additional packing options

<sup>[3]</sup> Allegro recommends against changing Coarse Sensitivity settings when programming devices that will be used in production. Each A1367 has been factory temperature compensated at a specific sensitivity range, and changing the coarse bits setting could cause sensitivity drift through temperature range (ΔSens<sub>TC</sub>) to exceed specified limits.

<sup>[4]</sup> Part variants A1367LKTTN-2B-T and A1367LKTTN-5B-T are in production but have been determined to be LAST TIME BUY. This classification indicates that the product is obsolete and notice has been given. Sale of this device is currently restricted to existing customer applications. The device should not be purchased for new design applications because of obsolescence in the near future. Samples are no longer available. Status change date: April 1, 2024. Last-time buy date: July 31, 2024.

<sup>[5]</sup> Part variant A1367LKTTN-2U-T is no longer in production. The device should not be purchased for new design applications. Samples are no longer available. Status change date: September 30, 2024.

# **SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                        | Symbol                   | Notes                                                                | Rating     | Unit  |

|---------------------------------------|--------------------------|----------------------------------------------------------------------|------------|-------|

| Forward Supply Voltage                | V <sub>CC</sub>          |                                                                      | 15         | V     |

| Reverse Supply Voltage                | V <sub>RCC</sub>         | T <sub>J</sub> (max) should not be exceeded                          | -15        | V     |

| Forward Output Voltage                | V <sub>OUT</sub>         | V <sub>OUT</sub> < V <sub>CC</sub> + 2 V                             | 16         | V     |

| Reverse Output Voltage                | V <sub>ROUT</sub>        | Difference between V <sub>CC</sub> and output should not exceed 20 V | -6         | V     |

| Output Source Current                 | I <sub>OUT(source)</sub> | VOUT to GND                                                          | 2.8        | mA    |

| Output Sink Current                   | I <sub>OUT(sink)</sub>   | VCC to VOUT                                                          | 10         | mA    |

| Maximum Number of EEPROM Write Cycles | EEPROM <sub>w(max)</sub> |                                                                      | 100        | cycle |

| Operating Ambient Temperature         | T <sub>A</sub>           | L temperature range                                                  | –40 to 150 | °C    |

| Storage Temperature                   | T <sub>stg</sub>         |                                                                      | -65 to 165 | °C    |

| Maximum Junction Temperature          | T <sub>J(max)</sub>      |                                                                      | 165        | °C    |

#### **ESD RATINGS**

| Characteristic       | Symbol           | Test Conditions | Value | Unit |

|----------------------|------------------|-----------------|-------|------|

| Human Body Model     | $V_{HBM}$        | Per AEC-Q100    | ±4.5  | kV   |

| Charged Device Model | V <sub>CDM</sub> | Per AEC-Q100    | ±1    | kV   |

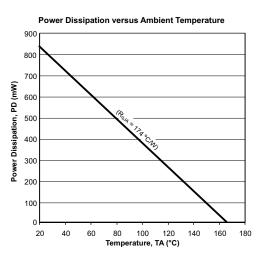

### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol          | Test Conditions*                                          | Value | Unit |

|----------------------------|-----------------|-----------------------------------------------------------|-------|------|

| Package Thermal Resistance | $R_{\theta JA}$ | On 1-layer PCB with exposed copper limited to solder pads | 174   | °C/W |

<sup>\*</sup>Additional thermal information available on the Allegro website

### PINOUT DIAGRAM AND TERMINAL LIST

### **KT Package Pinout Diagram**

(Ejector pin mark on opposite side)

### **Terminal List Table**

| Number | Name | Function                                                                                 |

|--------|------|------------------------------------------------------------------------------------------|

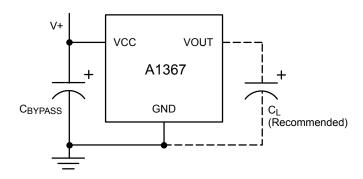

| 1      | VCC  | Input Power Supply, use bypass capacitor to connect to ground; also used for programming |

| 2      | VOUT | Output Signal, also used for programming                                                 |

| 3      | NC   | No connection; connect to GND for optimal ESD performance                                |

| 4      | GND  | Ground                                                                                   |

# A1367

# OPERATING CHARACTERISTICS: Valid through the full operating temperature range, $T_A$ , $C_{BYPASS}$ = 0.1 $\mu$ F, $V_{CC}$ = 5 V, unless otherwise specified

| Characteristic                             | Symbol                 | Test Conditions                                                                                                                         | Min. | Тур.            | Max.  | Unit [1]          |

|--------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|-------|-------------------|

| ELECTRICAL CHARACTERISTICS                 | ·\                     |                                                                                                                                         |      |                 |       |                   |

| Supply Voltage                             | V <sub>CC</sub>        |                                                                                                                                         | 4.5  | 5               | 5.5   | V                 |

| Supply Current                             | I <sub>CC</sub>        | No load on VOUT                                                                                                                         | _    | 11              | 16.25 | mA                |

| Power-On Time [2]                          | t <sub>PO</sub>        | T <sub>A</sub> = 25°C, C <sub>BYPASS</sub> = open, C <sub>L</sub> = 1 nF,<br>Sens = 2 mV/G, constant magnetic field<br>of 400 G         | -    | 80              | _     | μs                |

| Temperature Compensation Power-On Time [2] | t <sub>TC</sub>        | $T_A$ = 150°C, $C_{BYPASS}$ = open, $C_L$ = 1 nF,<br>Sens = 2 mV/G, constant magnetic field<br>of 400 G                                 | _    | 146             | _     | μs                |

| Dower On Boost Voltage [2]                 | V <sub>PORH</sub>      | T <sub>A</sub> = 25°C, V <sub>CC</sub> rising                                                                                           | 3.75 | 4               | 4.2   | V                 |

| Power-On Reset Voltage [2]                 | V <sub>PORL</sub>      | T <sub>A</sub> = 25°C, V <sub>CC</sub> falling                                                                                          | _    | 3.5             | _     | V                 |

| Power-On Reset Hysteresis                  | V <sub>PORHYS</sub>    | T <sub>A</sub> = 25°C                                                                                                                   | -    | 500             | -     | mV                |

| Power-On Reset Release Time [2]            | t <sub>PORR</sub>      | T <sub>A</sub> = 25°C, V <sub>CC</sub> rising                                                                                           | _    | 32              | _     | μs                |

| Power-On Reset Analog Delay                | t <sub>PORA</sub>      | T <sub>A</sub> = 25°C, V <sub>CC</sub> rising                                                                                           | -    | 46              | _     | μs                |

| Supply Zener Clamp Voltage                 | V <sub>z</sub>         | T <sub>A</sub> = 25°C, I <sub>CC</sub> = 30 mA                                                                                          | 18   | 21              | _     | V                 |

| Internal Bandwidth                         | BWi                    | Small signal –3 dB, C <sub>L</sub> = 1 nF, T <sub>A</sub> = 25°C                                                                        | _    | 240             | _     | kHz               |

| Chopping Frequency [3]                     | f <sub>C</sub>         | T <sub>A</sub> = 25°C                                                                                                                   | _    | 1               | _     | MHz               |

| OUTPUT CHARACTERISTICS                     | ·                      |                                                                                                                                         |      | •               |       |                   |

| Propagation Delay Time [2]                 | t <sub>pd</sub>        | T <sub>A</sub> = 25°C, magnetic field step of 400 G,<br>C <sub>L</sub> = 1 nF, Sens = 2 mV/G                                            | _    | 1.1             | _     | μs                |

| Rise Time [2]                              | t <sub>r</sub>         | T <sub>A</sub> = 25°C, magnetic field step of 400 G,<br>C <sub>L</sub> = 1 nF, Sens = 2 mV/G                                            | _    | 2.4             | _     | μs                |

| Danaga Tima [2]                            |                        | T <sub>A</sub> = 25°C, magnetic field step of 400 G,<br>C <sub>L</sub> = 1 nF, Sens = 2 mV/G, measurement of<br>80% input to 80% output | -    | 1.8             | _     | μs                |

| Response Time [2]                          | <sup>t</sup> RESPONSE  | T <sub>A</sub> = 25°C, magnetic field step of 400 G,<br>C <sub>L</sub> = 1 nF, Sens = 2 mV/G, measurement of<br>90% input to 90% output | _    | 2.2             | _     | μs                |

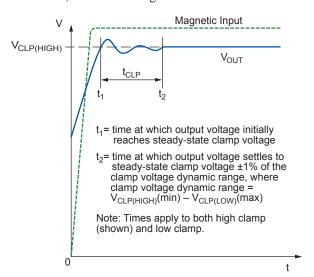

| Delay to Clamp [2]                         | t <sub>CLP</sub>       | T <sub>A</sub> = 25°C, magnetic field step from 800 to 1200 G, C <sub>L</sub> = 1 nF, Sens = 2 mV/G                                     | _    | 10              | _     | μs                |

| Output Valtage Clamp [4]                   | V <sub>CLP(HIGH)</sub> | $T_A$ = 25°C, $R_{L(PULLDWN)}$ = 10 kΩ to GND                                                                                           | 4.55 | _               | 4.85  | V                 |

| Output Voltage Clamp [4]                   | V <sub>CLP(LOW)</sub>  | $T_A$ = 25°C, $R_{L(PULLUP)}$ = 10 kΩ to VCC                                                                                            | 0.15 | _               | 0.45  | V                 |

| Outrot Cotunation Valtage [2]              | V <sub>SAT(HIGH)</sub> | $T_A$ = 25°C, $R_{L(PULLDWN)}$ = 10 kΩ to GND                                                                                           | 4.7  | _               | _     | V                 |

| Output Saturation Voltage [2]              | V <sub>SAT(LOW)</sub>  | $T_A$ = 25°C, $R_{L(PULLDWN)}$ = 10 kΩ to VCC                                                                                           | _    | _               | 400   | mV                |

| Dualitary Wine Malka and [2]               | V <sub>BRK(HIGH)</sub> | $T_A$ = 25°C, $R_{L(PULLUP)}$ = 10 kΩ to VCC                                                                                            | _    | V <sub>CC</sub> | _     | V                 |

| Broken Wire Voltage [2]                    | V <sub>BRK(LOW)</sub>  | $T_A$ = 25°C, $R_{L(PULLDWN)}$ = 10 kΩ to GND                                                                                           | _    | 100             | _     | mV                |

|                                            | ` `                    | $T_A = 25$ °C, CL = 1 nF, BW <sub>f</sub> = BW <sub>i</sub>                                                                             | _    | 1.4             | _     | mG/√(Hz)          |

| Noise [5]                                  | V <sub>N</sub>         | $T_A$ = 25°C, CL = 1 nF, Sens = 2 mV/G, BW <sub>f</sub> = BW <sub>i</sub>                                                               | _    | 12.6            | -     | mV <sub>p-p</sub> |

|                                            |                        | $T_A$ = 25°C, CL = 1 nF, Sens = 2 mV/G, BW <sub>f</sub> = BW <sub>i</sub>                                                               | _    | 2.1             | -     | mV <sub>RMS</sub> |

Continued on the next page...

# A1367

# OPERATING CHARACTERISTICS (continued): Valid through the full operating temperature range, $T_A$ , $C_{BYPASS}$ = 0.1 $\mu$ F, $V_{CC}$ = 5 V, unless otherwise specified

| Characteristic                                                        | Symbol                          | Test Conditions                                           | Min. | Тур.                              | Max. | Unit [1] |

|-----------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------|------|-----------------------------------|------|----------|

| <b>OUTPUT CHARACTERISTICS (cont</b>                                   | inued)                          |                                                           |      |                                   |      |          |

| DC Output Resistance                                                  | R <sub>OUT</sub>                |                                                           | -    | 3                                 | -    | Ω        |

| Outrott and Desistance                                                | R <sub>L(PULLUP)</sub>          | VOUT to VCC                                               | 4.7  | _                                 | _    | kΩ       |

| Output Load Resistance                                                | R <sub>L(PULLDWN)</sub>         | VOUT to GND                                               | 4.7  | _                                 | _    | kΩ       |

| Output Load Capacitance [6]                                           | C <sub>L</sub>                  | VOUT to GND                                               | _    | 1                                 | 10   | nF       |

| Output Slew Rate [7]                                                  | SR                              | Sens = 2 mV/G, C <sub>L</sub> = 1 nF                      | -    | 480                               | -    | V/ms     |

| QUIESCENT VOLTAGE OUTPUT (V                                           | ουτ( <b>Q</b> )) <sup>[2]</sup> |                                                           |      |                                   |      |          |

| Initial Unprogrammed Quiescent                                        | V <sub>OUT(QBI)init</sub>       | T <sub>A</sub> = 25°C                                     | 2.4  | 2.5                               | 2.6  | V        |

| Voltage Output [2][8]                                                 | V <sub>OUT(QU)init</sub>        | T <sub>A</sub> = 25°C                                     | 0.45 | 0.5                               | 0.55 | V        |

| Quiescent Voltage Output                                              | V <sub>OUT(QBI)PR</sub>         | T <sub>A</sub> = 25°C                                     | 2.35 | _                                 | 2.65 | V        |

| Programming Range [2][4][9]                                           | V <sub>OUT(QU)PR</sub>          | T <sub>A</sub> = 25°C                                     | 0.4  | _                                 | 0.6  | V        |

| Quiescent Voltage Output<br>Programming Bits [10]                     | QVO                             |                                                           | _    | 9                                 | -    | bit      |

| Average Quiescent Voltage Output<br>Programming Step Size [2][11][12] | Step <sub>VOUT(Q)</sub>         | T <sub>A</sub> = 25°C                                     | 0.95 | 1.15                              | 1.4  | mV       |

| Quiescent Voltage Output<br>Programming Resolution [2][13]            | Err <sub>PGVOUT(Q)</sub>        | T <sub>A</sub> = 25°C                                     | _    | ±0.5 ×<br>Step <sub>VOUT(Q)</sub> | -    | mV       |

| SENSITIVITY (Sens) [2]                                                | ,                               |                                                           |      |                                   |      |          |

|                                                                       |                                 | SENS_COARSE = 00, T <sub>A</sub> = 25°C                   | _    | 1                                 | _    | mV/G     |

| Initial Unprogrammed Sensitivity [8]                                  | Sens <sub>init</sub>            | SENS_COARSE = 01, T <sub>A</sub> = 25°C                   | _    | 2.2                               | _    | mV/G     |

|                                                                       |                                 | SENS_COARSE = 10, T <sub>A</sub> = 25°C                   | _    | 4.7                               | -    | mV/G     |

|                                                                       |                                 | SENS_COARSE = 00, T <sub>A</sub> = 25°C                   | 0.6  | _                                 | 1.3  | mV/G     |

| Sensitivity Programming Range [4][9]                                  | Sens <sub>PR</sub>              | SENS_COARSE = 01, T <sub>A</sub> = 25°C                   | 1.3  | _                                 | 2.9  | mV/G     |

|                                                                       |                                 | SENS_COARSE = 10, T <sub>A</sub> = 25°C                   | 2.9  | _                                 | 6.4  | mV/G     |

| Coarse Sensitivity Programming Bits [14]                              | SENS_COARSE                     |                                                           | _    | 2                                 | -    | bit      |

| Fine Sensitivity Programming Bits [10]                                | SENS_FINE                       |                                                           | _    | 9                                 | -    | bit      |

| Average Fine Sensitivity and                                          |                                 | SENS_COARSE = 00, T <sub>A</sub> = 25°C                   | 2.4  | 3.2                               | 4.1  | μV/G     |

| Temperature Compensation                                              | Step <sub>SENS</sub>            | SENS_COARSE = 01, T <sub>A</sub> = 25°C                   | 5    | 6.6                               | 8.5  | μV/G     |

| Programming Step Size [2][14][15]                                     |                                 | SENS_COARSE = 10, T <sub>A</sub> = 25°C                   | 11   | 14.2                              | 18   | μV/G     |

| Sensitivity Programming Resolution [2][13]                            | Err <sub>PGSENS</sub>           | T <sub>A</sub> = 25°C                                     | ı    | ±0.5 ×<br>Step <sub>SENS</sub>    | -    | μV/G     |

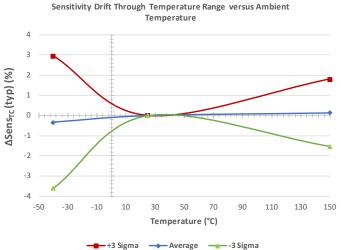

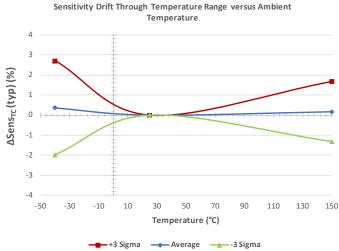

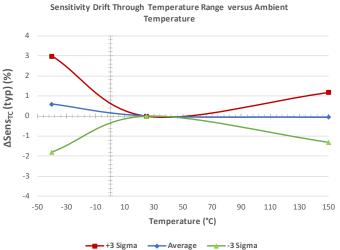

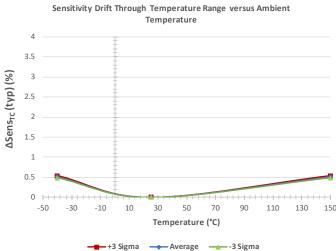

| FACTORY-PROGRAMMED SENSITI                                            | VITY TEMPE                      | RATURE COEFFICIENT                                        |      |                                   |      |          |

| Sensitivity Temperature Coefficient [2]                               | TC <sub>SENS</sub>              | $T_A$ = 150°C, $T_A$ = -40°C, calculated relative to 25°C | -    | 0                                 | -    | %/°C     |

| Sensitivity Drift Through Temperature                                 | ASono                           | T <sub>A</sub> = 25°C to 150°C                            | -2   | _                                 | 2    | %        |

| Range <sup>[2][9][15]</sup>                                           | ∆Sens <sub>TC</sub>             | $T_A = -40$ °C to 25°C                                    | -3.5 | _                                 | 3.5  | %        |

| Average Sensitivity Temperature<br>Compensation Step Size             | Step <sub>SENSTC</sub>          | T <sub>A</sub> = -40°C to 150°C                           |      | 2 × Step <sub>SENS</sub>          |      | μV/G     |

Continued on the next page...

#### OPERATING CHARACTERISTICS (continued): Valid through the full operating temperature range, T<sub>A</sub>, C<sub>BYPASS</sub> = 0.1 μF, V<sub>CC</sub> = 5 V, unless otherwise specified

| Characteristic                                                            | Symbol                    | Test Conditions                                                                             | Min. | Тур.    | Max. | Unit [1] |

|---------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------|------|---------|------|----------|

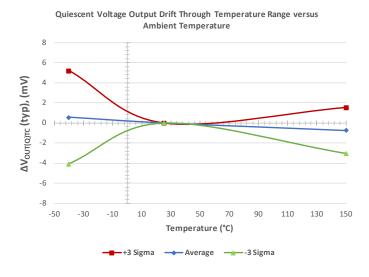

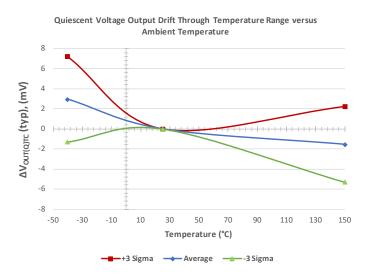

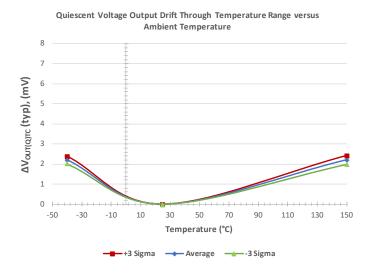

| FACTORY-PROGRAMMED QUIESC                                                 | ENT VOLTAG                | E OUTPUT TEMPERATURE COEFFICIENT                                                            |      |         |      |          |

| Quiescent Voltage Output<br>Temperature Coefficient [2]                   | TC <sub>QVO</sub>         | $T_A = 150$ °C, $T_A = -40$ °C, calculated relative to 25°C                                 | -    | 0       | _    | mV/°C    |

| Quiescent Voltage Output Drift                                            |                           | T <sub>A</sub> = 25°C to 150°C; SENS_COARSE = 00 or 01                                      | -10  | _       | 10   | mV       |

| Through Temperature Range [2][9][15]                                      | $\Delta V_{OUT(Q)TC}$     | T <sub>A</sub> = 25°C to 150°C; SENS_COARSE = 10                                            | -15  | _       | 15   | mV       |

|                                                                           |                           | $T_A = -40$ °C to 25°C                                                                      | -30  | _       | 30   | mV       |

| Average Quiescent Voltage<br>Output Temperature Compensation<br>Step Size | Step <sub>QVOTC</sub>     |                                                                                             | -    | 2.3     | -    | mV       |

| LOCK BIT PROGRAMMING                                                      |                           |                                                                                             |      |         |      |          |

| EEPROM Lock Bit                                                           | EELOCK                    |                                                                                             | -    | 1       | _    | bit      |

| ERROR COMPONENTS                                                          |                           |                                                                                             |      |         |      |          |

| Linearity Sensitivity Error [2][16]                                       | Lin <sub>ERR</sub>        |                                                                                             | -1   | < ±0.25 | 1    | %        |

| Symmetry Sensitivity Error [2]                                            | Sym <sub>ERR</sub>        |                                                                                             | -1   | < ±0.25 | 1    | %        |

|                                                                           |                           | Through supply voltage range (relative to V <sub>CC</sub> = 5 V ±5%); SENS_COARSE = 00      | -0.8 | ±0.15   | 0.8  | %        |

| Ratiometry Quiescent Voltage Output<br>Error [2][17]                      | Rat <sub>ERRVOUT(Q)</sub> | Through supply voltage range (relative to V <sub>CC</sub> = 5 V ±5%); SENS_COARSE = 01      | -0.9 | ±0.15   | 0.9  | %        |

|                                                                           |                           | Through supply voltage range (relative to V <sub>CC</sub> = 5 V ±5%); SENS_COARSE = 10      | -1.2 | ±0.25   | 1.2  | %        |

| Ratiometry Sensitivity Error [2][17]                                      | Rat <sub>ERRSens</sub>    | Through supply voltage range (relative to V <sub>CC</sub> = 5 V ±5%)                        | -1   | < ±0.5  | 1    | %        |

| Ratiometry Clamp Error [2][18]                                            | Rat <sub>ERRCLP</sub>     | Through supply voltage range (relative to V <sub>CC</sub> = 5 V ±5%), T <sub>A</sub> = 25°C | _    | < ±1    | _    | %        |

| Sensitivity Drift Due to Package<br>Hysteresis [2]                        | ΔSens <sub>PKG</sub>      | T <sub>A</sub> = 25°C, after temperature cycling, 25°C to 150°C and back to 25°C            | -    | ±0.6    | _    | %        |

| Sensitivity Drift Over Lifetime [19]                                      | ΔSens <sub>LIFE</sub>     | T <sub>A</sub> = 25°C, shift after AEC Q100 grade 0 qualification testing                   |      | ±1      |      | %        |

- [1] 1 G (gauss) = 0.1 mT (millitesla).

- [2] See Characteristic Definitions section.

- $^{[3]}$  f<sub>C</sub> varies up to approximately  $\pm 20\%$  over the full operating ambient temperature range, T<sub>A</sub>, and process.

- [4] Sens,  $V_{OUT(Q)}$ ,  $V_{CLP(LOW)}$ , and  $V_{CLP(HIGH)}$  scale with  $V_{CC}$  due to ratiometry. [5] Noise, measured in mV<sub>PP</sub> and in mV<sub>RMS</sub>, is dependent on the sensitivity of the device.

- [6] Output stability is maintained for capacitive loads as large as 10 nF.

- [7] High-to-low transition of output voltage is a function of external load components.

- [8] Raw device characteristic values before any programming.

- [9] Exceeding the specified ranges will cause sensitivity and Quiescent Voltage Output drift through the temperature range to deteriorate beyond the specified values.

- [10] Refer to Functional Description section.

- [11] Step size is larger than required, in order to provide for manufacturing spread. See Characteristic Definitions section.

- [12] Non-ideal behavior in the programming DAC can cause the step size at each significant bit rollover code to be greater than twice the maximum specified value of Step<sub>VOUT(Q)</sub> or Step<sub>SENS</sub>.

- [13] Overall programming value accuracy. See Characteristic Definitions section.

- [14] Each A1367 part number is factory programmed and temperature compensated at a different coarse sensitivity setting. Changing coarse bits setting could cause sensitivity drift through temperature range, $\Delta Sens_{TC}$ , to exceed specified limits

- [15] Allegro will be testing and temperature compensating each device at 150°C. Allegro will not be testing devices at -40°C. Temperature compensation codes will be applied based on characterization data.

- [16] Linearity applies to output voltage ranges of ±2 V from the quiescent output for bidirectional devices.

- [17] Percent change from actual value at  $V_{CC} = 5 \text{ V}$ , for a given temperature, through the supply voltage operating range.

- [18] Percent change from actual value at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C, through the supply voltage operating range.

[19] Based on characterization data obtained during standardized stress test for Qualification of Integrated Circuits. Cannot be guaranteed. Drift is a function of customer application conditions. Please contact Allegro MicroSystems for further information.

### CHARACTERISTIC PERFORMANCE DATA

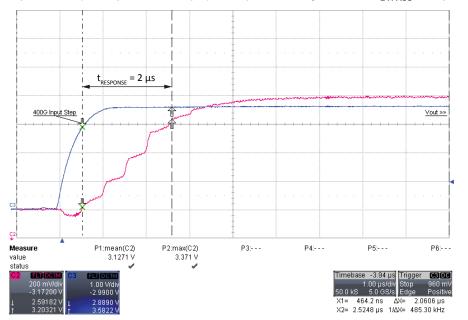

# Response Time (t<sub>RESPONSE</sub>)

400 G Excitation Signal with 10%-90% rise time = 1  $\mu$ s Response time (80% input to 80% output) = 2.06  $\mu$ s, Sensitivity = 2 mV/G,  $C_{BYPASS}$  = 0.1  $\mu$ F,  $C_L$  = 1 nF

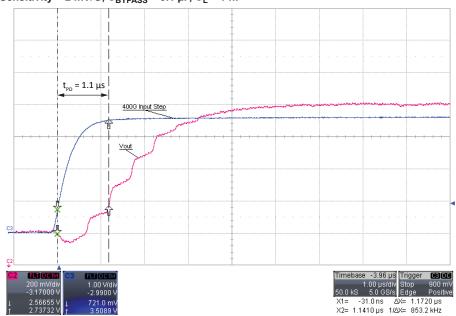

### Propagation Delay (t<sub>PD</sub>)

400 G Excitation Signal with 10%-90% rise time = 1  $\mu s$  Sensitivity = 2 mV/G,  $C_{BYPASS}$  = 0.1  $\mu F,\, C_L$  = 1 nF

### CHARACTERISTIC PERFORMANCE DATA (continued)

#### Rise Time (t<sub>r</sub>)

400 G Excitation Signal with 10%-90% rise time = 1  $\mu s$  Sensitivity = 2 mV/G,  $C_{BYPASS}$  = 0.1  $\mu F,\,C_L$  = 1 nF

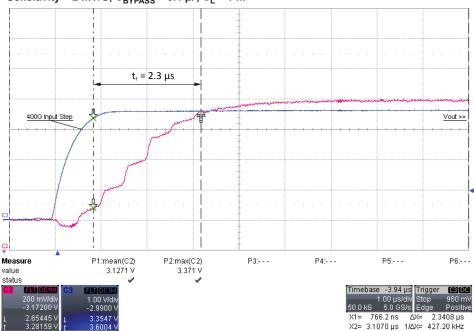

### Power-On Time (t<sub>PO</sub>)

400 G Constant Excitation Signal with  $t_{PO} = 81 \mu s$

7/16/2015 4:59:28 PM

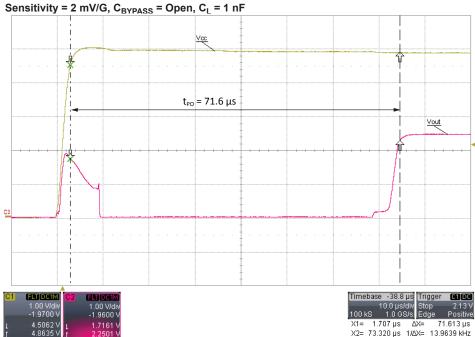

# CHARACTERISTIC PERFORMANCE DATA (continued)

### A1367LKTTN-1B-T

### A1367LKTTN-2B-T

### CHARACTERISTIC PERFORMANCE DATA (continued)

### A1367LKTTN-5B-T

### A1367LKTTN-2U-T

#### CHARACTERISTIC DEFINITIONS

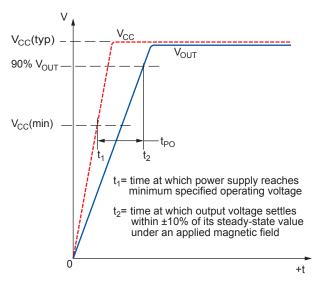

# Power-On Time (t<sub>PO</sub>)

When the supply is ramped to its operating voltage, the device requires a finite time to power its internal components before responding to an input magnetic field.

Power-On Time ( $t_{PO}$ ) is defined as: the time it takes for the output voltage to settle within  $\pm 10\%$  of its steady-state value under an applied magnetic field, after the power supply has reached its minimum specified operating voltage ( $V_{CC(min)}$ ) as shown in Figure 1.

# Temperature Compensation Power-On Time $(t_{TC})$

After Power-On Time  $(t_{PO})$  elapses,  $t_{TC}$  is also required before a valid temperature compensated output.

# Propagation Delay (t<sub>pd</sub>)

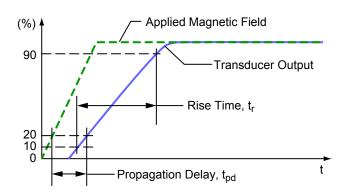

The time interval between a) when the applied magnetic field reaches 20% of its final value, and b) when the output reaches 20% of its final value (see Figure 2).

# Rise Time (t<sub>r</sub>)

The time interval between a) when the sensor IC reaches 10% of its final value, and b) when it reaches 90% of its final value (see Figure 2).

# Response Time (t<sub>RESPONSE</sub>)

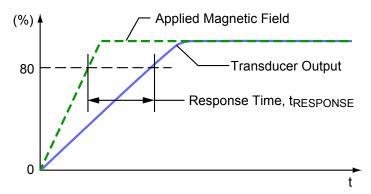

The time interval between a) when the applied magnetic field reaches 80% of its final value, and b) when the sensor reaches 80% of its output corresponding to the applied magnetic field (see Figure 3). The 90%-90% is also shown in the Electrical Characteristics table.

Figure 1: Power-On Time Definition

Figure 2: Propagation Delay and Rise Time Definitions

**Figure 3: Response Time Definition**

# Delay to Clamp (t<sub>CLP</sub>)

A large magnetic input step may cause the clamp to overshoot its steady-state value. The Delay to Clamp ( $t_{CLP}$ ) is defined as: the time it takes for the output voltage to settle within  $\pm 1\%$  of its steady-state value, after initially passing through its steady-state voltage, as shown in Figure 4.

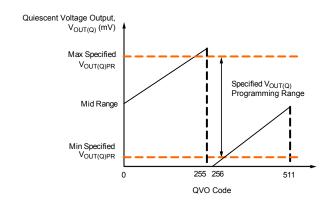

# Quiescent Voltage Output (V<sub>OUT(Q)</sub>)

In the quiescent state (no significant magnetic field: B=0~G), the output  $(V_{OUT(Q)})$  has a constant ratio to the supply voltage  $(V_{CC})$  throughout the entire operating ranges of  $V_{CC}$  and ambient temperature  $(T_A).$

# Initial Unprogrammed Quiescent Voltage Output (V<sub>OUT(Q)init</sub>)

Before any programming, the Quiescent Voltage Output  $(V_{OUT(O)})$  has a nominal value of  $V_{CC}$  /2, as shown in Figure 5.

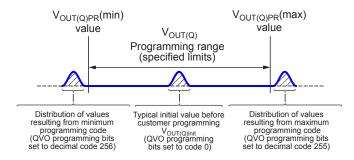

# Quiescent Voltage Output Programming Range (V<sub>OUT(Q)PR</sub>)

The Quiescent Voltage Output  $(V_{OUT(Q)})$  can be programmed within the Quiescent Voltage Output Range limits:  $V_{OUT(Q)PR(min)}$  and  $V_{OUT(Q)PR(max)}$ . Exceeding the specified Quiescent Voltage Output Range will cause Quiescent Voltage Output Drift Through Temperature Range  $(\Delta V_{OUT(Q)TC})$  to deteriorate beyond the specified values, as shown in Figure 5.

Figure 4: Delay to Clamp definition

# Average Quiescent Voltage Output Programming Step Size (Step<sub>VOUT(Q)</sub>)

The Average Quiescent Voltage Output Progamming Step Size  $(Step_{VOUT(Q)})$  is determined using the following calculation:

$$Step_{VOUT(Q)} = \frac{V_{OUT(Q)maxcode} - V_{OUT(Q)mincode}}{2^{n} - 1} , \qquad (1)$$

where n is the number of available programming bits in the trim range, 9 bits,  $V_{OUT(Q)maxcode}$  is at decimal code 255, and  $V_{OUT(Q)mincode}$  is at decimal code 256.

# Quiescent Voltage Output Programming Resolution (Err<sub>PGVOUT(Q)</sub>)

The programming resolution for any device is half of its programming step size. Therefore, the typical programming resolution will be:

$$Err_{PGVOUT(O)}(typ) = 0.5 \times Step_{VOUT(O)}(typ)$$

(2)

# Quiescent Voltage Output Temperature Coefficient (TC<sub>OVO</sub>)

Device  $V_{OUT(Q)}$  changes as temperature changes, with respect to its programmed Quiescent Voltage Output Temperature Coefficient,  $TC_{QVO}$ .  $TC_{QVO}$  is programmed at 150°C and calculated relative to the nominal  $V_{OUT(Q)}$  programming temperature of 25°C.  $TC_{QVO}$  (mV/°C) is defined as:

$$TC_{QVO} = [V_{OUT(Q)T2} - V_{OUT(Q)T1}][1/(T2 - T1)] \tag{3}$$

where T1 is the nominal V<sub>OUT(Q)</sub> programming temperature of

Figure 5: Quiescent Voltage Output Range definition

$25^{\circ}$ C, and T2 is the TC<sub>OVO</sub> programming temperature of  $150^{\circ}$ C.

$$V_{OUT(O)EXPECTED}(T_A) = V_{OUT(O)TI} + TC_{OVO}(T_A - TI)$$

(4)

$V_{OUT(Q)EXPECTED(TA)}$  should be calculated using the actual measured values of  $V_{OUT(Q)T1}$  and  $TC_{QVO}$  rather than programming target values.

The expected V<sub>OUT(O)</sub> through the full ambient temperature range

(V<sub>OUT(O)EXPECTED(TA)</sub>) is defined as:

# Quiescent Voltage Output Drift Through Temperature Range (ΔV<sub>OUT(Q)TC</sub>)

Due to internal component tolerances and thermal considerations, the Quiescent Voltage Output  $(V_{OUT(Q)})$  may drift from its nominal value through the operating ambient temperature  $(T_A).$  The Quiescent Voltage Output Drift Through Temperature Range  $(\Delta_{VOUT(Q)TC})$  is defined as:

$$D_{VOUT(O)TC} = V_{OUT(O)(TA)} - V_{OUT(O)EXPECTED(TA)}$$

(5)

$\Delta V_{OUT(Q)TC}$  should be calculated using the actual measured values of  $\Delta V_{OUT(Q)(TA)}$  and  $\Delta V_{OUT(Q)EXPECTED(TA)}$  rather than programming target values.

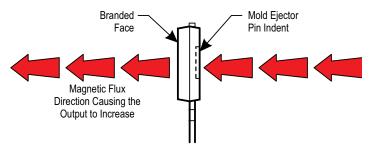

# Sensitivity (Sens)

The presence of a south polarity magnetic field, perpendicular to the branded surface of the package face, increases the output voltage from its quiescent value toward the supply voltage rail. The amount of the output voltage increase is proportional to the magnitude of the magnetic field applied.

Conversely, the application of a north polarity field decreases the output voltage from its quiescent value. This proportionality is specified as the magnetic sensitivity, Sens (mv/G), of the device, and it is defined as:

$$Sens = \frac{V_{OUT(BPOS)} - V_{OUT(BNEG)}}{RPOS - RNFG}, \tag{6}$$

Figure 6: Magnetic Flux Polarity

where BPOS and BNEG are two magnetic fields with opposite polarities.

# Initial Unprogrammed Sensitivity (Sensinit)

Before any programming, Sensitivity has a nominal value that depends on the SENS\_COARSE bits setting. Each A1367 variant has a different SENS\_COARSE setting.

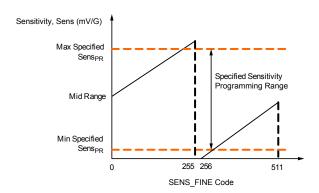

# Sensitivity Programming Range (Sens<sub>PR</sub>)

The magnetic sensitivity (Sens) can be programmed around its initial value within the sensitivity range limits:  $Sens_{PR}(min)$  and  $Sens_{PR}(max)$ . Exceeding the specified Sensitivity Range will cause Sensitivity Drift Through Temperature Range ( $\Delta Sens_{TC}$ ) to deteriorate beyond the specified values. Refer to the Quiescent Voltage Output Range section for a conceptual explanation of how value distributions and ranges are related.

# Average Fine Sensitivity Programming Step Size (Step<sub>SENS</sub>)

Refer to the Average Quiescent Voltage Output Programming Step Size section for a conceptual explanation.

# Sensitivity Programming Resolution (Err<sub>PGSENS</sub>)

Refer to the Quiescent Voltage Output Programming Resolution section for a conceptual explanation.

# Sensitivity Temperature Coefficient (TC<sub>SENS</sub>)

Device sensitivity changes as temperature changes, with respect to its programmed sensitivity temperature coefficient,  $TC_{SENS}$ .  $TC_{SENS}$  is programmed at 150°C and is calculated relative to the nominal sensitivity programming temperature of 25°C.  $TC_{SENS}$  (%/°C) is defined as:

$$TC_{SENS} = \left(\frac{Sens_{T2} - Sens_{TI}}{Sens_{TI}} \times 100\% \right) \left(\frac{1}{T2 - TI}\right), \tag{7}$$

where T1 is the nominal Sens programming temperature of 25°C, and T2 is the TC<sub>SENS</sub> programming temperature of 150°C. The expected value of Sens over the full ambient temperature range, Sens<sub>EXPECTED(TA)</sub>, is defined as:

$$Sens_{EXPECTED(TA)} = Sens_{TI} \times \left[ 100\% + \frac{TC_{SENS} (T_A - T1)}{100} \right]$$

(8)

Sens<sub>EXPECTED(TA)</sub> should be calculated using the actual measured values of Sens<sub>T1</sub> rather than programming target values.

# Sensitivity Drift Through Temperature Range ( $\Delta Sens_{TC}$ )

Second-order sensitivity temperature coefficient effects cause the magnetic sensitivity, Sens, to drift from its expected value over the operating ambient temperature range  $(T_A)$ . The Sensitivity Drift Through Temperature Range  $(\Delta Sens_{TC})$  is defined as:

$$\Delta Sens_{TC} = \frac{Sens_{TA} - Sens_{EXPECTED(TA)}}{Sens_{EXPECTED(TA)}} \times 100\% \quad . \tag{9}$$

# Sensitivity Drift Due to Package Hysteresis $(\Delta Sens_{PKG})$

Package stress and relaxation can cause the device sensitivity at  $T_A = 25^{\circ}\text{C}$  to change during and after temperature cycling. The sensitivity drift due to package hysteresis ( $\Delta \text{Sens}_{PKG}$ ) is defined as:

$$\Delta Sens_{PKG} = \frac{Sens_{(25^{\circ}C)2} - Sens_{(25^{\circ}C)1}}{Sens_{(25^{\circ}C)1}} \times 100\% , \qquad (10)$$

where  $Sens_{(25^{\circ}C)1}$  is the programmed value of sensitivity at  $T_A = 25^{\circ}C$ , and  $Sens_{(25^{\circ}C)2}$  is the value of sensitivity at  $T_A = 25^{\circ}C$ , after temperature cycling  $T_A$  up to 150°C and back to 25°C.

# Linearity Sensitivity Error (Lin<sub>ERR</sub>)

The A1367 is designed to provide a linear output in response to a ramping applied magnetic field. Consider two magnetic fields, B1 and B2. Ideally, the sensitivity of a device is the same for both fields, for a given supply voltage and temperature. Linearity error is present when there is a difference between the sensitivities measured at B1 and B2.

# **Linearity Error**

Linearity error is calculated separately for the positive (Lin<sub>ERRPOS</sub>) and negative (Lin<sub>ERRNEG</sub>) applied magnetic fields. Linearity Error (%) is measured and defined as:

$$\operatorname{Lin}_{\text{ERRPOS}} = \left(1 - \frac{\operatorname{Sens}_{\text{BPOS2}}}{\operatorname{Sens}_{\text{BPOS1}}}\right) \times 100\% ,$$

$$\operatorname{Lin}_{\text{ERRNEG}} = \left(1 - \frac{\operatorname{Sens}_{\text{BNEG2}}}{\operatorname{Sens}_{\text{BNEG1}}}\right) \times 100\% , \qquad (11)$$

where:

$$Sens_{Bx} = \frac{|V_{OUT(Bx)} - V_{OUT(Q)}|}{B_x} , \qquad (12)$$

and BPOSx and BNEGx are positive and negative magnetic fields, with respect to the quiescent voltage output such that  $|BPOS2| = 2 \times |BPOS1|$  and  $|BNEG2| = 2 \times |BNEG1|$ .

Then:

$$Lin_{ERR} = max(Lin_{ERRPOS}, Lin_{ERRNEG})$$

. (13)

# Symmetry Sensitivity Error (Sym<sub>FRR</sub>)

The magnetic sensitivity of an A1367 device is constant for any two applied magnetic fields of equal magnitude and opposite polarities. Symmetry Error,  $\text{Sym}_{\text{ERR}}$  (%), is measured and defined as:

$$Sym_{ERR} = \left(1 - \frac{Sens_{BPOS}}{Sens_{BNEG}}\right) \times 100\% , \qquad (14)$$

where  $Sens_{Bx}$  is as defined in equation 12, and BPOSx and BNEGx are positive and negative magnetic fields such that |BPOSx| = |BNEGx|.

# Ratiometry Error (Rater )

The A1367 device features ratiometric output. This means that the Quiescent Voltage Output ( $V_{OUT(Q)}$ ) magnetic sensitivity, Sens, and Output Voltage Clamp ( $V_{CLP(HIGH)}$ ) and  $V_{CLP(LOW)}$ ) are proportional to the Supply Voltage ( $V_{CC}$ ). In other words, when the supply voltage increases or decreases by a certain percentage, each characteristic also increases or decreases by the same percentage. Error is the difference between the measured change in the supply voltage relative to 5 V, and the measured change in each characteristic.

The ratiometric error in Quiescent Voltage Output,  $Rat_{ERRVOUT(Q)}$  (%), for a given supply voltage ( $V_{CC}$ ) is defined as:

$$Rat_{ERRVOUT(QBI)} = \left[1 - \frac{\left(\frac{V_{OUT(QBI)(VCC)}}{V_{OUT(QBI)(5V)}}\right)}{\frac{V_{CC}}{5 \text{ V}}}\right] \times 100\%$$

(15)

Rat<sub>ERRVOUT(QU)</sub> is defined in the same way as Rat<sub>ERRVOUT(QBI)</sub> with a factor of 1/5 multiplied.

$$Rat_{ERRVOUT(QU)} = \left[1 - \frac{\left(\frac{V_{OUT(QU)(VCC)}}{V_{OUT(QU)(5V)}}\right)}{\frac{V_{CC}}{5 \text{ V}}}\right] \times \frac{1}{5} \times 100\%$$

(16)

This is to scale the ratiometry error of the unidirectional device so that it can be compared with the bidirectional device.

The ratiometric error in magnetic sensitivity,  $Rat_{ERRSens}$  (%), for a given Supply Voltage ( $V_{CC}$ ) is defined as:

$$Rat_{ERRSens} = \left(1 - \frac{Sens_{(VCC)} / Sens_{(5V)}}{V_{CC} / 5 V}\right) \times 100\% \quad . \tag{17}$$

The ratiometric error in the clamp voltages,  $Rat_{ERRCLP}$  (%), for a given supply voltage ( $V_{CC}$ ) is defined as:

$$Rat_{ERRCLP} = \left(1 - \frac{V_{CLP(VCC)} / V_{CLP(5V)}}{V_{CC} / 5 V}\right) \times 100\% , \qquad (18)$$

where  $V_{CLP}$  is either  $V_{CLP(HIGH)}$  or  $V_{CLP(LOW)}$ .

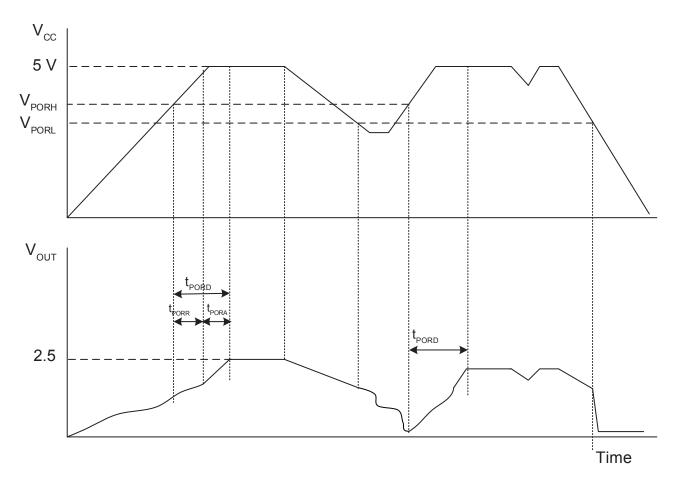

# Power-On Reset Voltage (V<sub>POR</sub>)

On power-up, to initialize to a known state and avoid current spikes, the A1367 is held in Reset state. The Reset signal is disabled when  $V_{CC}$  reaches  $V_{PORH}$  and time  $t_{PORR}$  has elapsed, allowing the output voltage to go from a high-impedance state into normal operation. During power-down, the Reset signal is enabled when  $V_{CC}$  reaches  $V_{PORL}$ , causing the output voltage to go into a high-impedance state. (Note that a detailed description of POR can be found in the Functional Description section).

# Power-On Reset Release Time (t<sub>PORR</sub>)

When  $V_{CC}$  rises to  $V_{PORH}$ , the Power-On Reset Counter starts. The A1367 output voltage will transition from a high-impedance state to normal operation only when the Power-On Reset Counter has reached  $t_{PORR}$  and  $V_{CC}$  has been maintained above  $V_{PORH}$ .

# Output Saturation Voltage (V<sub>SAT</sub>)

When output voltage clamps are disabled, the output voltage can swing to a maximum of  $V_{SAT(HIGH)}$  and to a minimum of  $V_{SAT(LOW)}$ .

# Broken Wire Voltage (V<sub>BRK</sub>)

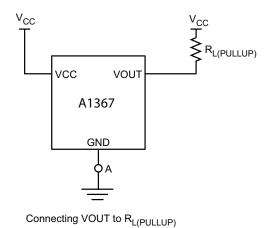

If the GND pin is disconnected (broken wire event), output voltage will go to  $V_{BRK(HIGH)}$  (if a load resistor is connected to VCC) or to  $V_{BRK(LOW)}$  (if a load resistor is connected to GND).

### **FUNCTIONAL DESCRIPTION**

# Programming Sensitivity and Quiescent Voltage Output

Sensitivity and  $V_{OUT(Q)}$  can be adjusted by programming SENS FINE and QVO bits, as illustrated in Figure 7 and Figure 8.

Customers should not program sensitivity or  $V_{OUT(Q)}$  beyond the maximum or minimum programming ranges specified in the Operating Characteristics table. Exceeding the specified limits will cause the sensitivity and  $V_{OUT(Q)}$  drift over the temperature range ( $\Delta Sens_{TC}$  and  $\Delta V_{OUT(Q)TC}$ ) to deteriorate beyond the specified values.

Programming sensitivity might cause a small drift in  $V_{OUT(Q)}$ . As a result, Allegro recommends programming sensitivity first, then  $V_{OUT(Q)}$ .

### **Coarse Sensitivity**

Each A1367 variant is programmed to a different coarse sensitivity setting. Devices are tested, and temperature compensation is factory programmed under that specific coarse sensitivity setting. If the coarse sensitivity setting is changed by programming SENS\_COARSE bits, Allegro cannot guarantee the specified sensitivity drift through temperature range limits ( $\Delta$ Sens<sub>TC</sub>).

Figure 7: Device Sensitivity versus SENS\_FINE Programmed Value

### **Memory-Locking Mechanisms**

The A1367 is equipped with two distinct memory-locking mechanisms:

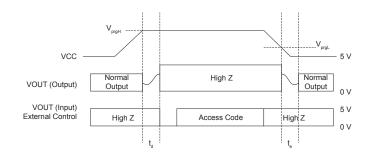

- **Default Lock** At power-up, all registers of the A1367 are locked by default. EEPROM and volatile memory cannot be read or written. To disable Default Lock, a specific 30 bit customer access code has to be written to address 0x24 within Access Code Timeout (t<sub>ACC</sub> = 8 ms) from power-up. After doing so, registers can be accessed. If VCC is power-cycled, the Default Lock will automatically be re-enabled. This ensures that during normal operation, memory content will not be altered due to unwanted glitches on VCC or the output pin.

- Lock Bit After EEPROM has been programmed by the user, the EELOCK bit can be set high and VCC power-cycled to permanently disable the ability to write any register. This will prevent the ability to disable Default Lock using the method described above. Note that after the EELOCK bit is set high and the VCC pin is power-cycled, you will not have the ability to clear the EELOCK bit or write any register.

Figure 8: Device V<sub>OUT(Q)</sub> versus QVO Programmed Value

# Power-On Reset (POR) Operation

The descriptions in this section assume temperature =  $25^{\circ}$ C, no output load ( $R_{\rm I}$ ,  $C_{\rm L}$ ), and no significant magnetic field is present.

- **Power-Up.** At power-up, as  $V_{CC}$  ramps up, the output is in a high-impedance state. When  $V_{CC}$  crosses  $V_{PORH}$ , the output will go to  $V_{CC}/2$  after  $t_{PORD}$ , where  $t_{PORD}$  = POR Release counter  $t_{PORR}$  + POR Analog delay  $t_{PORA}$ .

- V<sub>CC</sub> drops below V<sub>CC(min)</sub> = 4.5 V. If V<sub>CC</sub> drops below V<sub>PORL</sub>, the output will be in a high-impedance state. If V<sub>CC</sub> recovers and exceeds V<sub>PORH</sub>, the output will go back to normal operation after t<sub>PORD</sub>.

Figure 9: POR Operation

# **Detecting Broken Ground Wire**

If the GND pin is disconnected, node A becoming open (see Figure 11), the VOUT pin will go to a high-impedance state. The output voltage will go to  $V_{BRK(HIGH)}$  if a load resistor  $R_{L(PULLUP)}$  is connected to  $V_{CC}$  or to  $V_{BRK(LOW)}$  if a load resistor  $R_{L(PULLDWN)}$  is connected to GND. The device will not respond to any applied magnetic field.

If the ground wire is reconnected, the A1367 will resume normal operation.

**Figure 10: Typical Application Drawing**

VCC VOUT

A1367

GND

GND

A

A

Connecting VOUT to R<sub>L(PULLDWN)</sub>

Figure 11: Connections for Detecting Broken Ground Wire

# **Chopper Stabilization Technique**

When using Hall-effect technology, a limiting factor for total accuracy is the small signal voltage developed across the Hall element. This voltage is disproportionally small relative to the offset that can be produced at the output of the Hall sensor. This makes it difficult to process the signal while maintaining an accurate, reliable output over the specified operating temperature and voltage ranges. Chopper stabilization is a unique approach used to minimize Hall offset on the chip.

The technique removes key sources of the output drift induced by thermal and mechanical stresses. This offset reduction technique is based on a signal modulation-demodulation process. The undesired offset signal is separated from the magnetic field-induced signal in the frequency domain through modulation. The subsequent demodulation acts as a modulation process for the offset, causing the magnetic field-induced signal to recover its

original spectrum at base band, while the DC offset becomes a high-frequency signal. The magnetic-sourced signal can then pass through a low-pass filter, while the modulated DC offset is suppressed. This high-frequency operation allows a greater sampling rate that results in higher accuracy and faster signal-processing capability. This approach desensitizes the chip to the effects of thermal and mechanical stresses, and produces devices that have extremely stable quiescent Hall output voltages and precise recoverability after temperature cycling. This technique is made possible through the use of a BiCMOS process, which allows the use of low-offset, low-noise amplifiers in combination with high-density logic integration and a proprietary, dynamic notch filter. The new Allegro filtering techniques are far more effective at suppressing chopper-induced signal noise compared to the previous generation of Allegro chopper-stabilized devices.

Figure 12: Concept of Chopper Stabilization

#### PROGRAMMING GUIDELINES

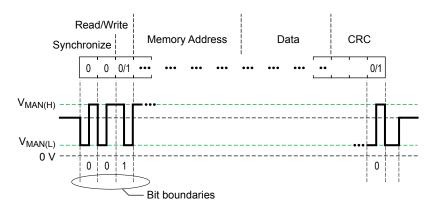

#### **Serial Communication**

The serial interface allows an external controller to read and write registers, including EEPROM, in the A1367 using a point-to-point command/acknowledge protocol. The A1367 does not initiate communication; it only responds to commands from the external controller. Each transaction consists of a command from the controller. If the command is a write, there is no acknowledging from the A1367. If the command is a read, the A1367 responds by transmitting the requested data.

Serial interface timing parameters can be found in the Program-

ming Levels table on page 22. Note that the external controller must avoid sending a Command frame that overlaps a Read Acknowledge frame.

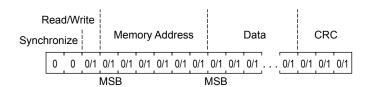

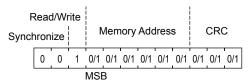

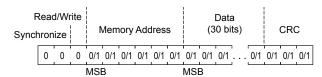

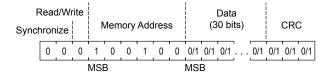

The serial interface uses a Manchester-encoding-based protocol per G.E. Thomas (0 = rising edge, 1 = falling edge), with address and data transmitted MSB first. Four commands are recognized by the A1367: Write Access Code, Write to Volatile Memory, Write to Non-Volatile Memory (EEPROM) and Read. One frame type, Read Acknowledge, is sent by the A1367 in response to a Read command.

Figure 13: General Format for Serial Interface Commands

The A1367 device uses a three-wire programming interface, where VCC is used to control the program enable signal, data is transmitted on VOUT, and all signals are referenced to GND. This three-wire interface makes it possible to communicate with multiple devices with shared VCC and GND lines.

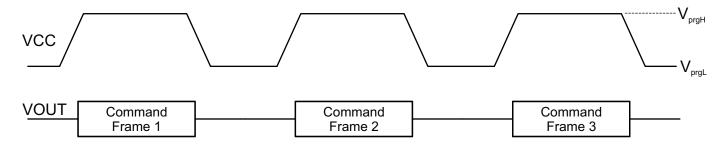

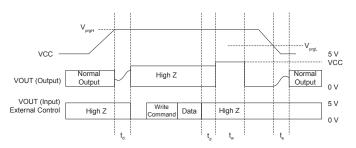

The four transactions (Write Access, Write to EEPROM, Write to Volatile Memory, and Read) are show in the figures on the following pages. To initialize any communication,  $V_{CC}$  should be increased to a level above  $V_{prgH}(min)$  without exceeding  $V_{prgH}(max)$ . At this time, VOUT is disabled and acts as an input.

After program enable is asserted, the external controller must drive the output low in a time less than  $t_d$ . This prevents the device interpreting any false transients on VOUT as data pulses. After the command is completed,  $V_{CC}$  is reduced below  $V_{prgL}$ ,

back to normal operating level. Also, the output is enabled and responds to magnetic input.

When performing a Write to EEPROM transaction, the A1367 requires a delay of  $t_{\rm w}$  to store the data into the EEPROM. The device will respond with a high-to-low transition on VOUT to indicate the Write to EEPROM sequence is complete.

When sending multiple command frames, it is necessary to toggle the program enable signal on VCC. After the first command frame is completed, and  $V_{CC}$  remains at  $V_{prgH}$ , the device will ignore any subsequent pulses on the output. When the program enable signal is brought below  $V_{prgL(max)}$ , the output will respond to the magnetic input. To send the next command, the program enable signal is increased to  $V_{prgH}$ .

| Quantity of Bits | Name            | Values | Description                                                                                                                                                                                                                                                                                 |

|------------------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                | Synchronization | 00     | Used to identify the beginning of a serial interface command                                                                                                                                                                                                                                |

| 4                | Read / Write    | 0      | [As required] Write operation                                                                                                                                                                                                                                                               |

| '                | Read / Write    | 1      | [As required] Read operation                                                                                                                                                                                                                                                                |

| 6                | Address         | 0/1    | [Read/Write] Register address (volatile memory or EEPROM)                                                                                                                                                                                                                                   |

| 30               | Data            | 0/1    | 24 data bits and 6 ECC bits. For a read command frame the data consists of 30 bits: [29:26] Don't Care, [25:24] ECC Pass/Fail, and [23:0] Data. Where bit 0 is the LSB. For a write command frame the data consists of 30 bits: [29:24] Don't Care and [23:0] Data. Where bit 0 is the LSB. |

| 3                | CRC             | 0/1    | Bits to check the validity of frame.                                                                                                                                                                                                                                                        |

**Figure 14: Command Frame General Format**

Figure 15: Format for Sending Multiple Transactions

### Programming Parameters, $C_{BYPASS} = 0.1 \mu F$ , $V_{CC} = 5 \text{ V}$

| Characteristics               | Symbol              | Note                                                                                 | Min.            | Тур. | Max.     | Unit |

|-------------------------------|---------------------|--------------------------------------------------------------------------------------|-----------------|------|----------|------|

| Program Enable Voltage (High) | $V_{prgH}$          | Program enable signal high level on VCC                                              | 8               | 8.25 | 8.5      | V    |

| Program Enable Voltage (Low)  | $V_{prgL}$          | Program enable signal low level on VCC                                               | V <sub>CC</sub> | _    | 6        | V    |

| Output Enable Delay           | t <sub>e</sub>      | External capacitance (C <sub>LX</sub> ) on VOUT may increase the Output Enable Delay | -               | 125  | -        | μs   |

| Program Time Delay            | t <sub>d</sub>      |                                                                                      | -               | 15   | _        | μs   |

| Program Write Delay           | t <sub>w</sub>      |                                                                                      | -               | 20   | _        | ms   |

| Manchester High Voltage       | V <sub>MAN(H)</sub> | Data pulses on VOUT                                                                  | 4               | 5    | $V_{CC}$ | V    |