## Highly Versatile, Regulated Single-Output, Buck-Boost Ambient Energy Manager For Up to 7-cell Solar Panels

#### **Feature**

#### Ultra-low power start-up

- Cold start from 275 mV input voltage and 3  $\mu$ W input power (typical).

#### Very efficient energy extraction

- Open-circuit voltage sensing for Maximum Power Point Tracking (MPPT).

- Selectable open-circuit voltage ratios from 60% to 90% or fixed impedance.

- Programmable MPPT sensing period.

- MPPT voltage operation range from 100 mV to 4.5 V.

#### Adaptive and smart energy management

- DCDC switches automatically between boost, buckboost and buck operation, according to input and output voltages, to maximize energy transfer.

- DCDC automatically handles multiple inputs and outputs:

- Keeps the internal supply and the load voltages regulated while storing the excess of energy in the storage element.

- The storage element can be used as an input to keep the load and internal voltages regulated when no energy is available on the source.

#### Load supply voltage

- Selectable load voltage from 1.2 V to 3.3 V.

- Current drive capability: 30 mA in low power mode, 60 mA in high power mode.

#### Battery protection features

- Selectable over-charge and over-discharge protection for any type of rechargeable battery or (super-)capacitor.

- Fast super-capacitor charging.

- Dual cell super-capacitor balancing circuit.

#### Smallest footprint, smallest BOM

- Only four external components are required.

- One 10 μH inductor.

- Three capacitors: one 10  $\mu\text{F},$  one 22  $\mu\text{F}$  and one at least 40  $\mu\text{F}.$

## **Description**

The AEM10330 is an integrated energy management circuit that extracts DC power from an ambient energy harvesting source to simultaneously supply an application and store energy in a storage element. The AEM10330 allows to extend battery lifetime and ultimately eliminates the primary energy storage element in a large range of applications.

Thanks to its Maximum Power Point Tracking system, the AEM10330 extracts the maximum energy available from the source. It integrates an ultra-low power DCDC converter which operates with input voltages ranging from 100 mV to 4.5 V.

At start-up, user can choose between charging the storage element first to accumulate energy before the application circuit starts, or charge the load decouplinwg capacitor first to start the application circuit faster.

With its unique cold start circuit, the AEM10330 can start harvesting with an input voltage as low as 275 mV and from an input power of 3  $\mu W$ . The preset protection levels determine the storage element voltages protection thresholds to avoid over-charging and over-discharging the storage element and thus avoiding damaging it. Those are set through configuration pins. Moreover, custom threshold voltages can be obtained at the expense of a few configuration resistors.

The load voltage can be selected to cover most application needs, with a maximum available load current of 60 mA.

The chip integrates all active elements for powering a typical wireless sensor. Only three capacitors and one inductor are required.

### **Applications**

| Asset Tracking/Monitoring | Industrial applications |

|---------------------------|-------------------------|

| Retail ESL/Smart sensors  | Aftermarket automotive  |

| Smart home/Building       |                         |

#### **Device Information**

| Part Number     | Package    | Body size [mm] |

|-----------------|------------|----------------|

| 10AEM10330J0000 | QFN 40-pin | 5x5mm          |

### **Evaluation Board**

| Part Number     |  |

|-----------------|--|

| 2AAEM10330J0010 |  |

## **Table of Contents**

| 1. Introduction                                                      | 6  |

|----------------------------------------------------------------------|----|

| 2. Pin Configuration and Functions                                   | 7  |

| 3. Absolute Maximum Ratings                                          | 9  |

| 4. Thermal Resistance                                                | 9  |

| 5. Typical Electrical Characteristics at 25 °C                       | 10 |

| 6. Recommended Operation Conditions                                  | 11 |

| 7. Functional Block Diagram                                          | 12 |

| 8. Theory of Operation                                               | 13 |

| 8.1. DCDC Converter                                                  | _  |

| 8.2. Cold-Start Circuit                                              |    |

| 8.3. AEM10330 States Description                                     |    |

| 8.4. Maximum Power Point Tracking                                    |    |

| 8.5. Balancing for Dual-Cell Supercapacitor                          |    |

| 9. System Configuration                                              | 17 |

| 9.1. High Power / Low Power Mode                                     |    |

| 9.2. Storage Element Configuration                                   |    |

| 9.3. Load Configuration                                              |    |

| 9.4. Custom Mode Configuration                                       |    |

| 9.5. Disable Storage Element Charging                                | 20 |

| 9.6. MPPT Configuration                                              | 21 |

| 9.7. ZMPP Configuration                                              | 21 |

| 9.8. Source to Storage Element Feed-Through                          | 21 |

| 9.9. External Components                                             | 22 |

| 10. Typical Application Circuits                                     | 23 |

| 10.1. Example Circuit 1                                              | 23 |

| 10.2. Example Circuit 2                                              | 24 |

| 11. Circuit Behavior                                                 | 26 |

| 11.1. Wake-up state, Start state and Supply state                    | 26 |

| 11.2. Supply state, Shutdown state and Reset state                   | 27 |

| 12. Performance Data                                                 | 28 |

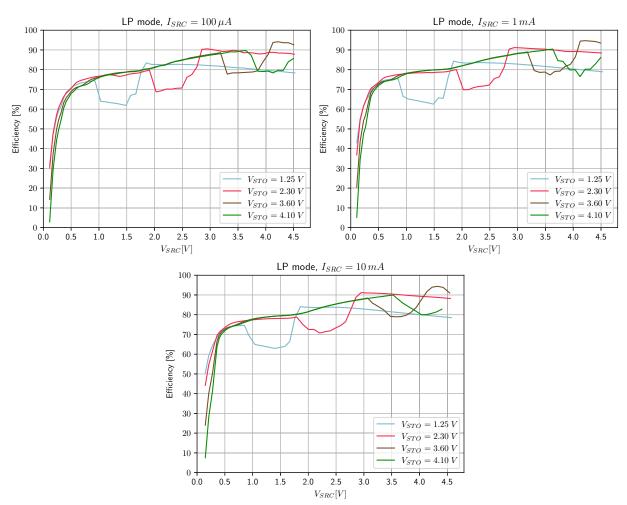

| 12.1. DCDC Conversion Efficiency From SRC to STO in Low Power Mode   |    |

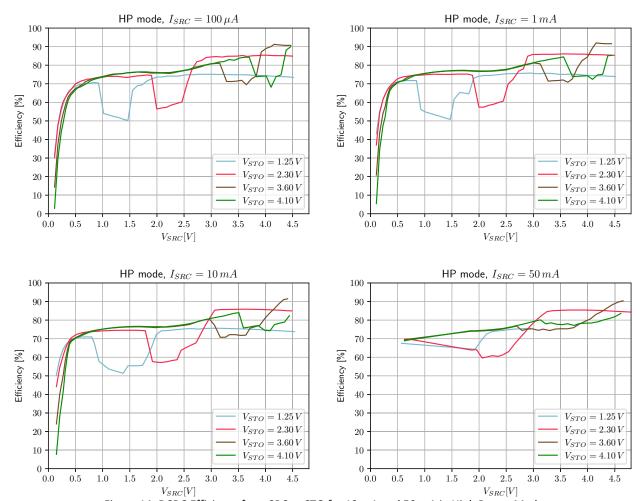

| 12.2. DCDC Conversion Efficiency From SRC to STO in High Power Mode  |    |

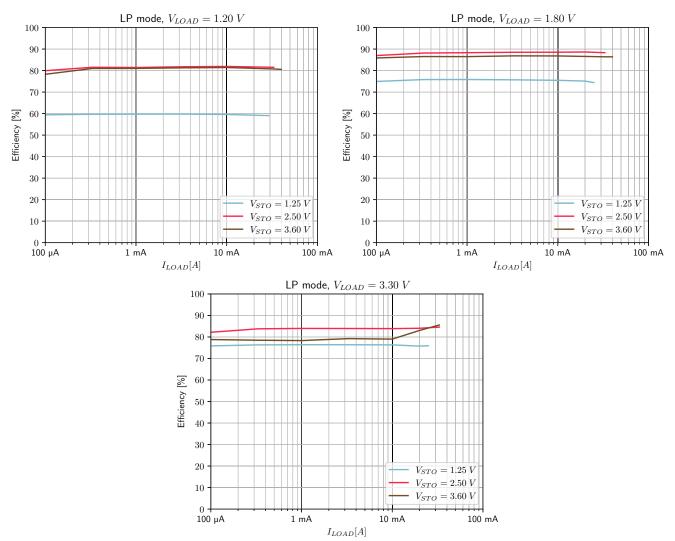

| 12.3. DCDC Conversion Efficiency From STO to LOAD in Low Power Mode  |    |

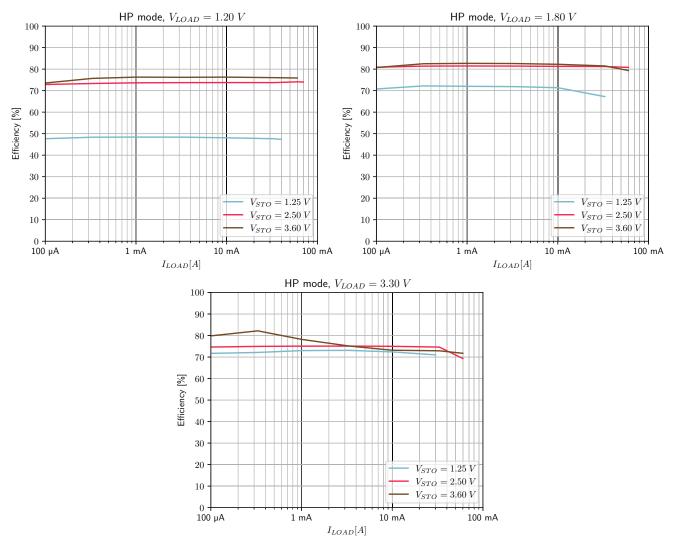

| 12.4. DCDC Conversion Efficiency From STO to LOAD in High Power Mode |    |

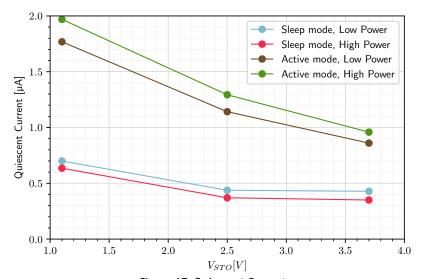

| 12.5. Quiescent Current                                              |    |

| 13. Schematic                                                        | 33 |

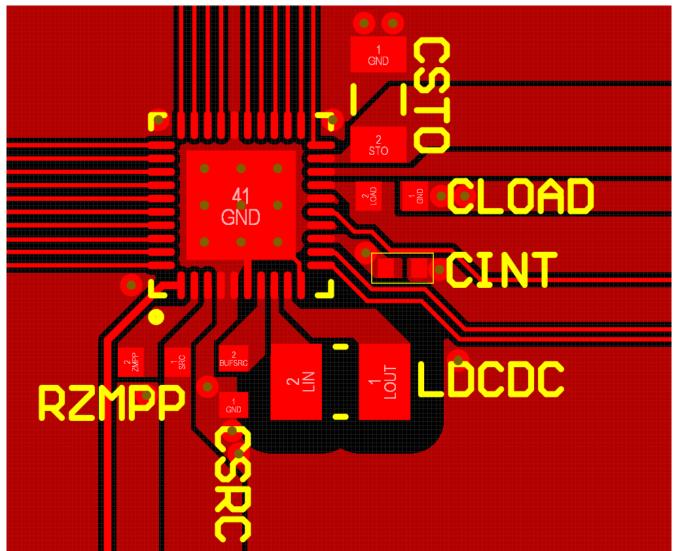

| 14. Layout                                                           | 34 |

| 14.1. Guidelines                                                     |    |

|                                                                      | 35 |

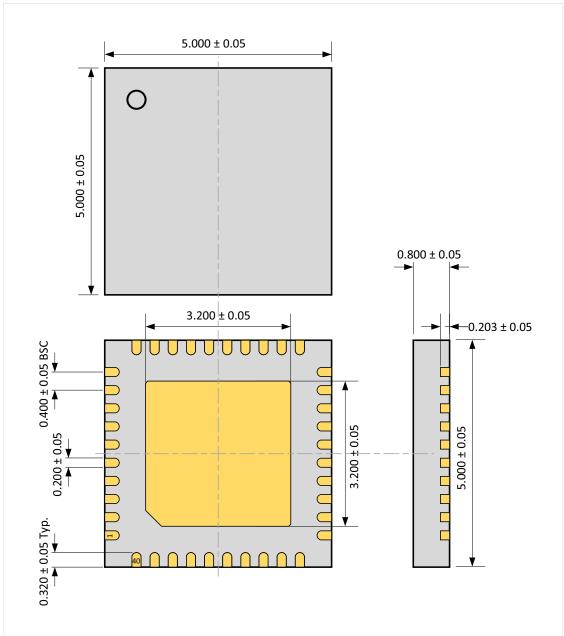

| 15. Package Information                                              | 36 |

| 15.1. Plastic Quad Flatpack No-Lead (QFN 40-pin 5x5mm)               | 36 |

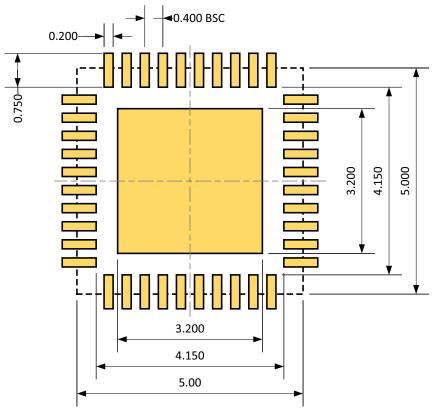

| 15.2. Board Layout                                                   | 37 |

# 16. Revision History 38

### **DATASHEET**

# **List of Figures**

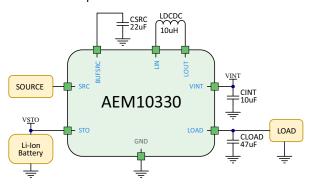

| Figure 1: Simplified Schematic View                                                   | 6  |

|---------------------------------------------------------------------------------------|----|

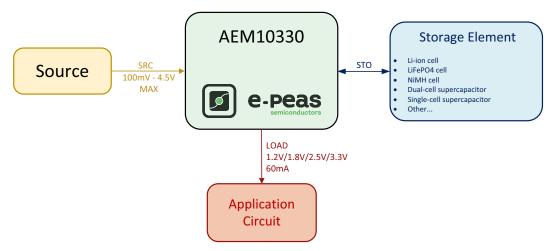

| Figure 2: Pinout Diagram QFN 40-pin                                                   | 7  |

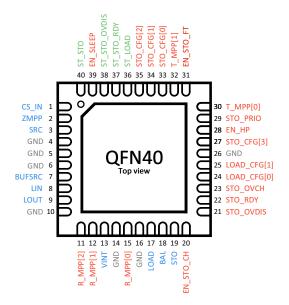

| Figure 3: Functional Block Diagram                                                    | 12 |

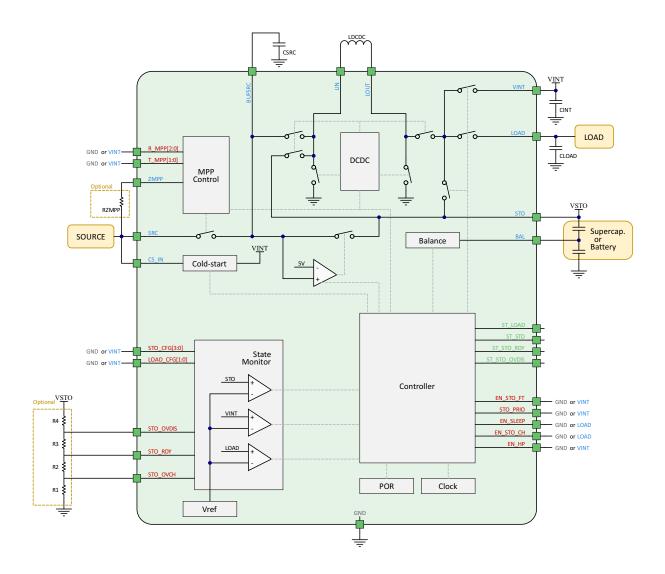

| Figure 4: Simplified Schematic View of the AEM10330                                   | 13 |

| Figure 5: Diagram of the AEM10330 States                                              | 14 |

| Figure 6: Maximum LOAD Current Depending on V <sub>STO</sub> and on V <sub>LOAD</sub> | 17 |

| Figure 7: Custom Mode Settings                                                        | 19 |

| Figure 8: R <sub>ZMPP</sub> Connection to the AEM10330                                | 21 |

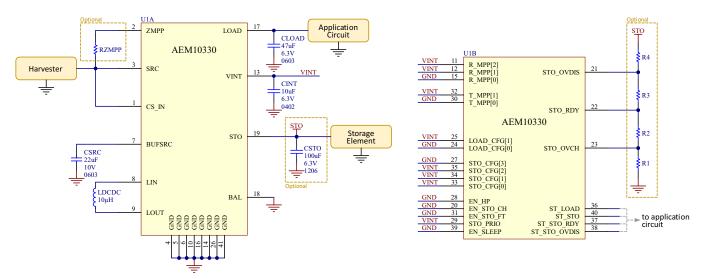

| Figure 9: Typical Application Circuit 1                                               | 23 |

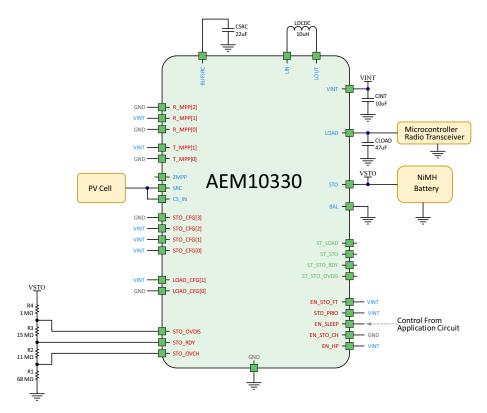

| Figure 10: Typical Application Circuit 2                                              | 24 |

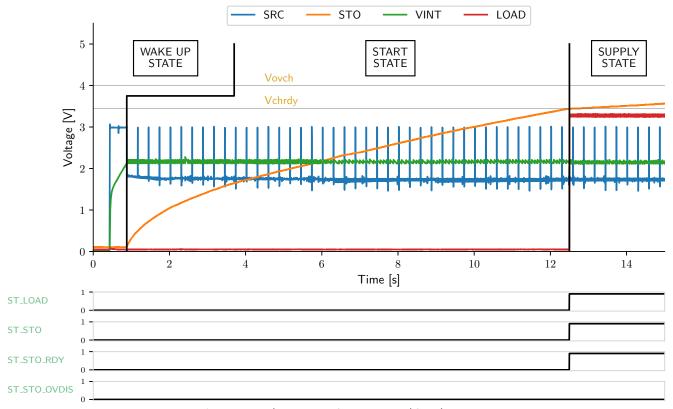

| Figure 11: Wake-up state, Start state and Supply state                                | 26 |

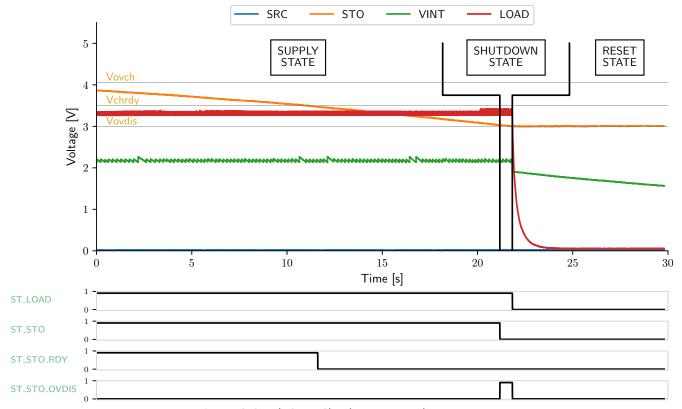

| Figure 12: Supply State, Shutdown state and Reset state                               | 27 |

| Figure 13: DCDC Efficiency from SRC to STO for 1 mA and 10 mA in Low Power Mode       | 28 |

| Figure 14: DCDC Efficiency from SRC to STO for 10 mA and 50 mA in High Power Mode     | 29 |

| Figure 15: DCDC Efficiency from STO to LOAD in Low Power Mode                         | 30 |

| Figure 16: DCDC Efficiency from STO to LOAD in High Power Mode                        | 31 |

| Figure 17: Quiescent Current                                                          | 32 |

| Figure 18: Schematic Example                                                          | 33 |

| Figure 19: Layout Example for the AEM10330 and its Passive Components                 | 35 |

| Figure 20: QFN 40-pin 5x5mm Drawing (All Dimensions in mm)                            | 36 |

| Figure 21: Recommended Board Layout for OEN40 nackage (All Dimensions in mm)          | 37 |

### **DATASHEET**

# **List of Tables**

| Table 1: Power and Status Pins              | 7  |

|---------------------------------------------|----|

| Table 2: Configuration and Ground Pins      | 8  |

| Table 3: Absolute Maximum Ratings           | 9  |

| Table 4: Thermal Resistance                 | 9  |

| Table 5: Typical Electrical Characteristics | 10 |

| Table 6: Recommended Operation Conditions   | 11 |

| Table 7: DCDC Converter Modes               | 13 |

| Table 8: Storage Element Configuration Pins | 18 |

| Table 9: Load Configuration Pins            | 19 |

| Table 10: MPP Ratio Configuration Pins      | 21 |

| Table 11: MPP Timing Configuration Pins     | 21 |

| Table 12: Minimal Bill of Materials         | 33 |

| Table 13: Revision History                  | 38 |

#### 1. Introduction

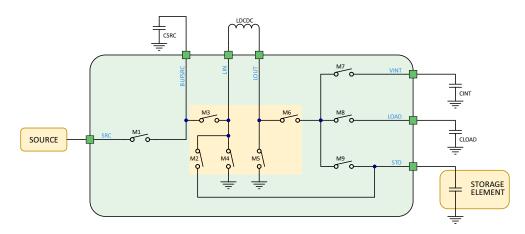

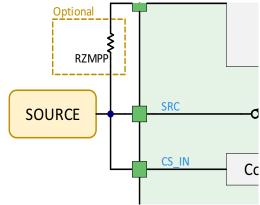

Figure 1: Simplified Schematic View

The AEM10330 is a full-featured energy efficient power management circuit able to harvest energy from an energy source (connected to SRC) to supply an application circuit (connected to LOAD) and use any excess of energy to charge a storage element (connected to STO). This is done with a minimal bill of material: only capacitors and one inductor are needed for a basic setup.

The heart of the AEM10330 is a regulated switching DCDC converter with high power conversion efficiency.

At first start-up, as soon as a required cold-start voltage of 275 mV and a sparse amount of power of at least 3  $\mu W$  is available at the source, the AEM10330 coldstarts. After the cold start, the AEM extracts the power available from the source if the working input voltage is at least 100 mV.

Through four configuration pins (STO\_CFG[3:0]), the user can select a specific operating mode out of 15 modes that cover most application requirements without any dedicated external component. Those operating modes define the protection levels of the storage element. If none of those 15 modes fit the user's storage element, a custom mode is also available to allow the user to define a mode with custom specifications.

Status pins ST\_STO, ST\_STO\_RDY and ST\_STO\_OVDIS provide information about the voltage levels of the storage element. ST\_STO is HIGH when the voltage of the storage element  $V_{STO}$  is above  $V_{CHRDY}$  and is reset when the voltage drops below  $V_{OVDIS}$ . ST\_STO\_RDY is HIGH when  $V_{STO}$  is above  $V_{CHRDY}$ , and reset when  $V_{STO}$  drops below  $V_{CHRDY}$ . ST\_STO\_OVDIS is HIGH when  $V_{STO}$  drops below  $V_{OVDIS}$  and reset when  $V_{STO}$  is above  $V_{OVDIS}$ . Status pin ST\_LOAD is HIGH when the load voltage  $V_{LOAD}$  rises above  $V_{LOAD,TYP}$ , and is reset when  $V_{LOAD,MIN}$ .

The Maximum Power Point (MPP) ratio is configurable thanks to three configuration pins (R\_MPP[2:0]) and ensures an optimum biasing of the harvester to maximize power extraction. Depending on the harvester, it is possible to adapt the timings of the MPP evaluations with the two configuration pins (T\_MPP[1:0]) that sets the periodicity and the duration of the MPP evaluation.

Once started, if at any time the load requires more power than can be harvested from the energy source, the AEM10330 automatically uses the storage element to keep the load supplied.

The AEM10330's DCDC converter can work in two modes: LOW POWER MODE and HIGH POWER MODE, each one of these being optimized for a power range on SRC and LOAD.

The charging of the storage element can be prevented by pulling EN\_STO\_CH to GND, typically to protect the storage element if the temperature is too low/high to safely charge it.

The AEM10330 also implements a SLEEP STATE, which reduces the quiescent current to avoid wasting the energy stored on the storage element when EN\_SLEEP is HIGH.

At start-up, user can choose to prioritize starting the application circuit connected on LOAD, or charging the storage element connected on STO. This is set by the STO PRIO pin.

# 2. Pin Configuration and Functions

Figure 2: Pinout Diagram QFN 40-pin

| NAME         | PIN<br>NUMBER | FUNCTION                                                                                                                                                                                                     |                            |                                                                                                                                           |

|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Power Pins   |               |                                                                                                                                                                                                              |                            |                                                                                                                                           |

| CS_IN        | 1             | Input for                                                                                                                                                                                                    | the etern                  | al cold start circuit.                                                                                                                    |

| ZMPP         | 2             | Used for t                                                                                                                                                                                                   | he config                  | guration of the ZMPP (optional). Must be left floating if not used.                                                                       |

| SRC          | 3             | Connectio                                                                                                                                                                                                    | on to the                  | harvested energy source.                                                                                                                  |

| BUFSRC       | 7             | Connectio                                                                                                                                                                                                    | on to an e                 | external capacitor buffering the DCDC converter input.                                                                                    |

| LIN          | 8             | DCDC ind                                                                                                                                                                                                     | uctance c                  | connection.                                                                                                                               |

| LOUT         | 9             | DCDC ind                                                                                                                                                                                                     | uctance c                  | connection.                                                                                                                               |

| VINT         | 13            | Internal v                                                                                                                                                                                                   | oltage su                  | pply.                                                                                                                                     |

| LOAD         | 17            | Output vo                                                                                                                                                                                                    | oltage to                  | supply on application load.                                                                                                               |

| BAL          | 18            | Connection to mid-point of a dual-cell supercapacitor (optional).  Must be connected to GND if not used.                                                                                                     |                            |                                                                                                                                           |

| STO          | 19            | Connection to the energy storage element - battery or (super-)capacitor. Cannot be left floating. Must be connected to a minimum capacitance of $100~\mu F$ or to a rechargeable battery.                    |                            |                                                                                                                                           |

| Status Pins  |               |                                                                                                                                                                                                              |                            |                                                                                                                                           |

| ST_LOAD      | 36            | Logic<br>Output                                                                                                                                                                                              | HIGH:<br>V <sub>LOAD</sub> | HIGH when the LOAD voltage $V_{LOAD}$ rises above the $V_{LOAD,TYP}$ threshold. LOW when $V_{LOAD}$ drops below $V_{LOAD,MIN}$ threshold. |

| ST_STO_RDY   | 37            | Logic HIGH: HIGH when V <sub>STO</sub> is above V <sub>CHRDY</sub> . Output V <sub>LOAD</sub> LOW when V <sub>STO</sub> drops below V <sub>CHRDY</sub> .                                                     |                            |                                                                                                                                           |

| ST_STO_OVDIS | 38            | Logic HIGH: HIGH when the AEM10330 state is SHUTDOWN STATE. Output V <sub>LOAD</sub> LOW when in any other state.                                                                                            |                            |                                                                                                                                           |

| ST_STO       | 40            | Logic HIGH: HIGH when the storage device voltage V <sub>STO</sub> rises above V <sub>CHRDY</sub> threshold.  Output V <sub>STO</sub> LOW when V <sub>STO</sub> drops below the V <sub>OVDIS</sub> threshold. |                            |                                                                                                                                           |

Table 1: Power and Status Pins

| NAME                                                                                                                                                                                                                         | PIN<br>NUMBER | HIGH<br>LEVEL                                | FLOATING<br>STATE                | FUNCTION                                                                                                                                                                           |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Configuration Pins                                                                                                                                                                                                           |               |                                              |                                  |                                                                                                                                                                                    |  |  |

| R_MPP[0]                                                                                                                                                                                                                     | 15            |                                              |                                  |                                                                                                                                                                                    |  |  |

| R_MPP[1]                                                                                                                                                                                                                     | 12            | V <sub>VINT</sub>                            | HIGH                             | Used for the configuration of the MPP ratio.  Read as HIGH when left floating.                                                                                                     |  |  |

| R_MPP[2]                                                                                                                                                                                                                     | 11            |                                              |                                  | nead as more when the housing.                                                                                                                                                     |  |  |

| T_MPP[0]                                                                                                                                                                                                                     | 30            | V                                            | HIGH                             | Used for the configuration of the MPP timings.                                                                                                                                     |  |  |

| T_MPP[1]                                                                                                                                                                                                                     | 32            | V <sub>VINT</sub>                            | півп                             | Read as HIGH when left floating.                                                                                                                                                   |  |  |

| LOAD_CFG[0]                                                                                                                                                                                                                  | 24            | V                                            | HIGH                             | Used for the configuration of LOAD output voltage V <sub>LOAD</sub> .                                                                                                              |  |  |

| LOAD_CFG[1]                                                                                                                                                                                                                  | 25            | V <sub>VINT</sub>                            | Read as HIGH when left floating. |                                                                                                                                                                                    |  |  |

| STO_CFG[0]                                                                                                                                                                                                                   | 33            |                                              |                                  |                                                                                                                                                                                    |  |  |

| STO_CFG[1]                                                                                                                                                                                                                   | 34            | V <sub>VINT</sub>                            | HIGH                             | Used for the configuration of the threshold voltages for the energy storage element V <sub>OVDIS</sub> , V <sub>CHRDY</sub> and V <sub>OVCH</sub> .                                |  |  |

| STO_CFG[2]                                                                                                                                                                                                                   | 35            | VVINT                                        | 111011                           | Read as HIGH when left floating.                                                                                                                                                   |  |  |

| STO_CFG[3]                                                                                                                                                                                                                   | 27            |                                              |                                  | _                                                                                                                                                                                  |  |  |

| STO_PRIO                                                                                                                                                                                                                     | 29            | V <sub>VINT</sub>                            | HIGH                             | <ul> <li>Pulled up to VINT or floating: storage device (STO) has highest priority at start-up</li> <li>Pulled down to GND: load (LOAD) has highest priority at start-up</li> </ul> |  |  |

| STO_OVCH                                                                                                                                                                                                                     | 23            |                                              |                                  |                                                                                                                                                                                    |  |  |

| Used for the configuration of the threshold voltages (V <sub>OVDIS</sub> , V <sub>CHRDY</sub> and V <sub>OVCH</sub> ) for the energy when STO_CFG[3:0] are set to custom mode (optional). Must be left floating if not used. |               |                                              |                                  |                                                                                                                                                                                    |  |  |

| STO_OVDIS                                                                                                                                                                                                                    | 21            | , which s                                    | 0_0.0[0.0] 0.                    | e set to castom mode (optional). Must be left houring if not asea.                                                                                                                 |  |  |

| EN_SLEEP                                                                                                                                                                                                                     | 39            | V <sub>LOAD</sub>                            | Cannot be<br>left<br>floating    | <ul> <li>Pulled up to LOAD: SLEEP STATE enabled</li> <li>Pulled down to GND: SLEEP STATE disabled</li> </ul>                                                                       |  |  |

| EN_STO_FT                                                                                                                                                                                                                    | 31            | V <sub>VINT</sub>                            | HIGH                             | <ul> <li>Pulled up to VINT or floating: allows charges flowing directly from SRC to STO when SRC is above 5V.</li> <li>Pulled down to GND: normal operation.</li> </ul>            |  |  |

| EN_STO_CH                                                                                                                                                                                                                    | 20            | V <sub>LOAD</sub>                            | HIGH                             | <ul> <li>Pulled up to LOAD or floating: enables the charging of the battery</li> <li>Pulled down to GND: disables the charging of the battery</li> </ul>                           |  |  |

| EN_HP                                                                                                                                                                                                                        | 28            | V <sub>VINT</sub>                            | HIGH                             | <ul> <li>Pulled up to VINTor floating: HIGH POWER MODE enabled</li> <li>Pulled down to GND: HIGH POWER MODE disabled</li> </ul>                                                    |  |  |

| Other                                                                                                                                                                                                                        |               |                                              |                                  |                                                                                                                                                                                    |  |  |

| 4, 5, 6,<br>10, 14,<br>GND 16, 26 Ground connection, best possible connection to PCB ground plane.                                                                                                                           |               | est possible connection to PCB ground plane. |                                  |                                                                                                                                                                                    |  |  |

|                                                                                                                                                                                                                              | Exposed pad   | Exposed                                      |                                  | ,                                                                                                                                                                                  |  |  |

Table 2: Configuration and Ground Pins

### 3. Absolute Maximum Ratings

#### Parameter Value Voltage on LOAD, STO, SRC, BUFSRC, LIN, LOUT, ZMPP, BAL, CS\_IN, EN\_SLEEP, -0.3 V to 5.5 V EN\_STO\_CH Voltage on VINT, T\_MPP[1:0], R\_MPP[2:0], LOAD\_CFG[1:0], STO\_CFG[3:0], STO\_PRIO, -0.3 V to 2.75 V STO\_OVCH, STO\_OVDIS, STO\_RDY, EN\_HP Operating junction temperature -40 °C to 125 °C -65 °C to 150 °C Storage temperature > 2000 V ESD HBM voltage ESD CDM voltage > 500 V

### Table 3: Absolute Maximum Ratings

### 4. Thermal Resistance

| Package        | θЈА | θЈС | Unit |

|----------------|-----|-----|------|

| QFN 40-<br>pin | TBD | TBD | °C/W |

Table 4: Thermal Resistance

#### **ESD CAUTION**

#### ESD (ELECTROSTATIC DISCHARGE) SENSITIVE DEVICE

These devices have limited built-in ESD protection and damage may thus occur on devices subjected to high-energy ESD. Therefore, proper EESD precautions should be taken to avoid performance degradation or loss of functionality

# 5. Typical Electrical Characteristics at 25 °C

| Symbol                   | Parameter                                                                           | Conditions                                                                       | Min                                   | Тур                                 | Max                 | Unit      |

|--------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|-------------------------------------|---------------------|-----------|

| Power Conversion         | on                                                                                  |                                                                                  |                                       |                                     |                     |           |

| D                        | Source power required for cold                                                      | V <sub>STO</sub> > Vchrdy                                                        |                                       | 3                                   |                     | μW        |

| P <sub>SRC,CS</sub>      | start                                                                               |                                                                                  |                                       | 6                                   |                     | μW        |

| V                        |                                                                                     |                                                                                  |                                       | 0.275                               | 4.5                 | V         |

| V <sub>SRC</sub>         | Input voltage of the energy source                                                  | After cold start                                                                 | 0.1                                   |                                     | 4.5                 | V         |

| R <sub>ZMPP</sub>        | MPPT ratio                                                                          | See Table 10                                                                     |                                       | 5, 80, 85 or 90,<br>PP[2:0] configu |                     | %         |

| Timing                   |                                                                                     |                                                                                  |                                       |                                     |                     |           |

| T <sub>MPP,EVAL</sub>    | Duration of a MPP evaluation                                                        |                                                                                  | 50% of<br>Table 11                    |                                     | 200% of<br>Table 11 | ms        |

| T <sub>MPP,PERIOD</sub>  | Time between two MPP evaluations                                                    |                                                                                  | 50% of<br>Table 11                    |                                     | 200% of<br>Table 11 | S         |

| Storage element          | t                                                                                   |                                                                                  | '                                     |                                     | '                   |           |

| V <sub>OVCH</sub>        | Maximum voltage accepted on the storage element before disabling its charging       |                                                                                  |                                       |                                     |                     | V         |

| V <sub>CHRDY</sub>       | Minimum voltage required on the storage element before asserting the ST_STO         | see Table 8                                                                      | Depends on STO_CFG[3:0] configuration |                                     |                     | V         |

| V <sub>OVDIS</sub>       | Minimum voltage accepted on the storage element before entering into SHUTDOWN STATE |                                                                                  |                                       |                                     |                     | V         |

| Load Output Vo           | ltage                                                                               |                                                                                  |                                       |                                     |                     |           |

|                          |                                                                                     | V <sub>LOAD</sub> = 1.8V<br>V <sub>STO</sub> > 1.6V<br>HP_EN = H                 |                                       | 60                                  |                     |           |

| I <sub>LOAD,MAX</sub>    | LOAD current drive capability                                                       | V <sub>LOAD</sub> = 2.5V<br>V <sub>STO</sub> > 1.6V<br>HP_EN = H                 |                                       | 60                                  |                     | mA        |

|                          |                                                                                     | V <sub>LOAD</sub> = 3.3V<br>V <sub>STO</sub> > 1.8V<br>HP_EN = H                 |                                       | 60                                  |                     |           |

| V <sub>LOAD</sub>        | Output voltage                                                                      | see Table 9                                                                      | Depends on L                          | OAD_CFG[1:0]                        | configuration       | V         |

|                          | & Quiescent Current                                                                 |                                                                                  |                                       |                                     |                     | ·         |

| V <sub>VINT</sub>        | Internal voltage supply                                                             |                                                                                  |                                       | 2.2                                 |                     | V         |

|                          |                                                                                     | <del>                                     </del>                                 |                                       |                                     |                     |           |

| $I_Q$                    | Quiescent current on STO                                                            | V <sub>STO</sub> = 3.7V<br>V <sub>LOAD</sub> = 2.5V<br>EN_SLEEP = L<br>EN_HP = L |                                       | 875                                 |                     | nA        |

| l <sub>Q</sub><br>Symbol | Quiescent current on STO  Logic Level                                               | V <sub>LOAD</sub> = 2.5V<br>EN_SLEEP = L                                         | LC                                    | 875<br>DW                           | н                   | nA<br>GH  |

|                          | Logic Level                                                                         | V <sub>LOAD</sub> = 2.5V<br>EN_SLEEP = L                                         | LC                                    |                                     | н                   |           |

| Symbol                   | Logic Level                                                                         | V <sub>LOAD</sub> = 2.5V<br>EN_SLEEP = L<br>EN_HP = L                            |                                       |                                     |                     |           |

| Symbol Logic output pin  | Logic Level                                                                         | V <sub>LOAD</sub> = 2.5V<br>EN_SLEEP = L<br>EN_HP = L                            | GI                                    | DW .                                | V                   | GH<br>sto |

| Symbol Logic output pin  | Logic Level  S  Logic output levels on the status STO                               | V <sub>LOAD</sub> = 2.5V<br>EN_SLEEP = L<br>EN_HP = L                            | GI<br>GI                              | <b>DW</b>                           | V <sub>2</sub>      | GH        |

Table 5: Typical Electrical Characteristics

# **6. Recommended Operation Conditions**

| Symbol              | Parameter                                                                          | Min                                 | Тур            | Max  | Unit      |  |

|---------------------|------------------------------------------------------------------------------------|-------------------------------------|----------------|------|-----------|--|

| External Components |                                                                                    |                                     |                |      |           |  |

| L <sub>DCDC</sub>   | Inductor of the DCDC converter                                                     |                                     | 10             |      | μН        |  |

| C <sub>SRC</sub>    | Capacitor decoupling the SRC terminal                                              | 13 <sup>1</sup>                     | 22             |      | μF        |  |

| C <sub>INT</sub>    | Capacitor decoupling the VINT terminal                                             | 5 <sup>1</sup>                      | 10             |      | μF        |  |

| C <sub>LOAD</sub>   | Capacitor decoupling the LOAD terminal                                             | 13 <sup>1</sup>                     | 47             |      | μF        |  |

| C <sub>STO</sub>    | Optional - Capacitor on STO if no storage element is connected (see Section 9.9.1) | 100 <sup>1</sup>                    |                |      | μF        |  |

| R <sub>ZMPP</sub>   | Optional - Used for the configuration of the ZMPP tracking function                | 10                                  | Section<br>9.7 | 100K | Ω         |  |

| STO_OVCH            | Configuration of V <sub>OVCH</sub> in custom mode                                  |                                     |                |      |           |  |

| STO_OVDIS           | Configuration of V <sub>OVDIS</sub> in custom mode                                 | 1                                   | 1 Section 9.4  |      | $M\Omega$ |  |

| STO_RDY             | Configuration of V <sub>CHRDY</sub> in custom mode                                 |                                     |                |      |           |  |

| Symbol              | Logic Level                                                                        | LOW                                 |                | HIGH |           |  |

| Logic input pins    |                                                                                    |                                     |                |      |           |  |

| R_MPP[2:0]          | Configuration pins for the MPP evaluation                                          | GND                                 |                | VINT |           |  |

| T_MPP[1:0]          | Configuration pins for the MPP timing                                              | GI                                  | VD             | VINT |           |  |

| LOAD_CFG[1:0]       | Configuration pins for the LOAD voltage                                            | GI                                  | VD             | VINT |           |  |

| STO_CFG[3:0]        | Configuration pins for the STO voltage                                             | ration pins for the STO voltage GND |                | VINT |           |  |

| STO_PRIO            | Configuration pin for the controller                                               | pin for the controller GND          |                | VINT |           |  |

| EN_STO_FT           | Configuration pin for the controller                                               | GND                                 |                | VINT |           |  |

| EN_SLEEP            | Configuration pin for the controller                                               | GND                                 |                | LOAD |           |  |

| EN_STO_CH           | Configuration pin for the controller                                               | GI                                  | ND             | LO   | AD        |  |

| EN_HP               | Configuration pin for the controller                                               | GI                                  | ND.            | VINT |           |  |

Table 6: Recommended Operation Conditions

<sup>1.</sup>Consider all component tolerance and deratings. Typically, DC-bias derating has a major impact on capacitance on ceramic capacitors.

# 7. Functional Block Diagram

Figure 3: Functional Block Diagram

Figure 4: Simplified Schematic View of the AEM10330

### 8. Theory of Operation

#### 8.1. DCDC Converter

The DCDC converter converts the voltage available at BUFSRC or at STO to a level suitable for charging the storage element STO or to regulate the LOAD and the internal supply VINT. The switching transistors of the DCDC converter are M2 or M3, M4, M5 and M6. Thanks to M7, M8 and M9, the controller selects between LOAD, STO and VINT respectively as the converter output. M1 selects the source as main input of energy. The internal supply VINT is regulated with priority over LOAD. STO is selected as an output only when neither VINT nor LOAD needs to be supplied. The converter has two possible inputs: BUFSRC or STO. BUFSRC is used by default as an input via M3. If the energy available on SRC is not sufficient to maintain the LOAD or VINT voltage, for instance because of a sudden current peak on LOAD, the converter uses STO instead as an input via M2 to keep LOAD and VINT regulated.

The reactive power component of this converter is the external inductor  $L_{DCDC}.$  Periodically, the MPP control circuit disconnects the source from the BUFSRC pin with the transistor M1 in order to let the harvester on SRC rise to its open-circuit voltage  $V_{OC}$  and measure it. This is done to define the optimal voltage level  $V_{MPP},$  which is determined by applying the MPP ratio on  $V_{OC}.$  BUFSRC is decoupled by the capacitor  $C_{SRC},$  which smooths the voltage against the current pulses pulled by the DCDC converter. The storage element is connected to the STO pin.

Depending on its input voltage and its output voltage, the DCDC converter will work as a boost converter, a buck converter or a buck-boost converter. The maximum power that can be harvested and supplied to the output LOAD depends on the power mode (HIGH POWER MODE or LOW POWER MODE), which is configured through the EN\_HP pin (see Section 9.1).

| DCDC Converter Mode | Input Voltage / Output Voltage                                                            |  |

|---------------------|-------------------------------------------------------------------------------------------|--|

| Boost               | <b>V<sub>IN</sub> &lt; V<sub>OUT</sub></b> - 250 mV                                       |  |

| Buck                | <b>V<sub>IN</sub> &gt; V<sub>OUT</sub> +</b> 250 mV                                       |  |

| Buck - Boost        | <b>V<sub>OUT</sub></b> - 250 mV < <b>V<sub>IN</sub></b> < <b>V<sub>OUT</sub></b> + 250 mV |  |

Table 7: DCDC Converter Modes

#### 8.2. Cold-Start Circuit

The AEM10330 is able to coldstart if the voltage on CS\_IN is above 0.275 V. The minimum available power is:

- 3  $\mu W$  if  $V_{STO}$  is above  $V_{CHRDY}$ .

- $6 \mu W$  if  $V_{STO}$  is below  $V_{CHRDY}$ .

CS\_IN is typically connected to SRC to allow the AEM10330 to coldstart from the energy available on the harvester. Nevertheless, any other energy source can be connected to CS\_IN as long as it meets the electrical specifications constraints described in Sections 5 and 6.

#### 8.3. AEM10330 States Description

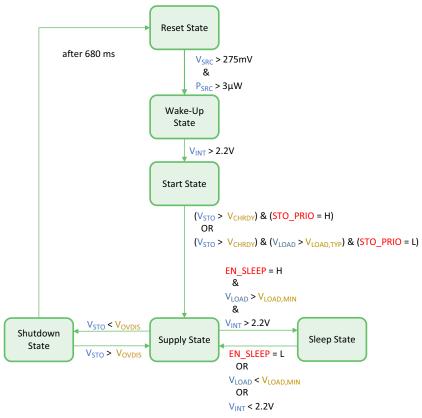

Figure 5: Diagram of the AEM10330 States

#### 8.3.1. Reset, Wake Up and Start States

The RESET STATE is a state where all nodes are deeply discharged and there is no available energy to be harvested. As soon as the required cold start voltage of 275 mV and a sparse amount of power of just 3 µW become available on CS\_IN (usually connected to SRC), the AEM10330 switches to WAKE-UP STATE, and energy is extracted from SRC to make V<sub>VINT</sub> rise to 2.2 V. When V<sub>VINT</sub> reaches those 2.2 V, the AEM10330 switches to START STATE. In START STATE, two scenarios are possible: in the first scenario, STO\_PRIO is HIGH, the storage element connected to STO has the priority on the one connected to LOAD. In the second scenario, STO\_PRIO is reset and the LOAD has the priority.

When the AEM10330 is in RESET STATE, WAKE-UP STATE or START STATE, the DCDC converter's input is always BUFSRC: STO is never used as input. This guarantees that the storage element is not used until a minimum amount of energy has been stored in it.

#### 8.3.1.1. Storage Element Priority

This paragraph covers the AEM10330 behavior when STO\_PRIO is pulled up to VINT, so that the storage element connected on STO has priority over LOAD.

#### **Supercapacitor as a Storage Element**

If the storage element is a supercapacitor, it may be fully discharged at first and thus need to be charged from 0 V. The DCDC converter charges STO from the input source (SRC). When  $V_{STO}$  reaches  $V_{CHRDY}$ , the circuit enters SUPPLY STATE.

#### **Battery as a Storage Element**

If the storage element is a battery, but its voltage is lower than  $V_{CHRDY}$ , then the storage element needs to be charged first until it reaches  $V_{CHRDY}$ . Once  $V_{STO}$  reaches  $V_{CHRDY}$ , or if the battery was initially charged above  $V_{CHRDY}$ , the circuit enters SUPPLY STATE.

#### 8.3.1.2. Load Priority

If STO\_PRIO is connected to GND, the AEM charges first the LOAD to V<sub>LOAD,MAX</sub> (see Table 9) using energy from the source (SRC). This allows to first supply the application circuit connected to LOAD. If the storage element was initially charged above V<sub>CHRDY</sub>, the circuit enters SUPPLY STATE as soon as LOAD reaches V<sub>LOAD,TYP</sub>. If the storage element is a supercapacitor or a battery which voltage is lower than V<sub>CHRDY</sub>, the AEM keeps regulating LOAD between V<sub>LOAD,MAX</sub> and V<sub>LOAD,TYP</sub>. Meanwhile, any excess charges on the source is used to charge the storage element until it reaches V<sub>CHRDY</sub>. Once V<sub>STO</sub> exceeds V<sub>CHRDY</sub>, the circuit enters into SUPPLY STATE.

This configuration is useful when a large storage element is connected to STO and a smaller one is connected to LOAD: the application starts as soon as  $C_{LOAD}$  is charged and does not have to wait for the large storage element on STO to be charged.

#### 8.3.2. Supply State

In SUPPLY STATE, four scenarios are possible:

- There is enough power provided by the source (SRC) to keep V<sub>LOAD</sub> near V<sub>LOAD,TYP</sub> with a small hysteresis and V<sub>VINT</sub> at 2.2 V. The excessive power is used to charge the storage element on STO. In that case, the circuit remains in SUPPLY STATE. If STO is fully charged, LOAD will be maintained at V<sub>LOAD,MAX</sub> instead of V<sub>LOAD,TYP</sub>. If all nodes are fully charged, the DCDC converter is disabled to prevent over-charging the storage element, and the SRC pin is set to high impedance.

- If the circuit connected to LOAD consumes more energy than the energy that the AEM10330 is able to extract from the source, the LOAD circuit will be supplied by the storage element connected to the STO terminal. In this case, the circuit stays in SUPPLY STATE.

- Due to a lack of power from the source, V<sub>STO</sub> falls below V<sub>OVDIS</sub>. In this case, the circuit enters SHUTDOWN STATE as explained in Section 8.3.3.

- If EN\_SLEEP is HIGH and conditions (shown on Figure 5) on V<sub>LOAD</sub> and V<sub>VINT</sub> are satisfied, the AEM enters SLEEP STATE (see section 8.3.4).

#### 8.3.3. Shutdown State

If the storage element gets depleted ( $V_{STO} < V_{OVDIS}$ ), the AEM10330 goes to SHUTDOWN STATE. As long as the AEM10330 is in this state, the ST\_STO\_OVDIS is HIGH. In SHUTDOWN STATE, if  $V_{STO}$  recovers within 680 ms, the AEM10330 goes back to SUPPLY STATE. This prevents false detection of the storage element being empty because of a LOAD current peak.

#### 8.3.4. Sleep State

SLEEP STATE reduces the AEM10330 guiescent current by disabling the DCDC converter and by reducing the controller clock frequency. If V<sub>VINT</sub> or V<sub>LOAD</sub> fall below their regulation value, the AEM10330 temporarily exits SLEEP STATE to wake up the DCDC converter and supply VINT or LOAD. Exiting SLEEP STATE and waking up the DCDC converter takes up to 1 ms. Depending on the expected LOAD current, CLOAD value must be adapted to act as an energy buffer during the 1 ms required to wake up the DCDC converter. Therefore, this state may be enabled when LOAD current is small, and be disabled if a high LOAD current is expected. As the DCDC is disabled, no energy is harvested from SRC while in SLEEP STATE, so that the storage element connected to STO is no longer charged. LOAD and VINT are the only nodes that are still supplied and regulated when the AEM10330 is in SLEEP STATE. This mode is useful to limit the current drawn on STO when the application circuit has detected that the power available on SRC is so low that it wouldn't compensate the AEM10330 internal circuit power consumption (see Table 5).

The AEM10330 enters SLEEP STATE if all the following conditions are satisfied:

- EN\_SLEEP pin pulled up to LOAD (H)

- $V_{VINT} > 2.2 V$

- V<sub>LOAD</sub> > V<sub>LOAD,TYP</sub>

The AEM10330 leaves SLEEP STATE and switches back to SUPPLY STATE if one of the following conditions is satisfied:

- EN\_SLEEP pin pulled down to GND (L)

- V<sub>VINT</sub> < 2.2 V

- V<sub>LOAD</sub> < V<sub>LOAD.TYP</sub>

The AEM10330 will then stay in SUPPLY STATE until the SLEEP STATE conditions are all satisfied again.

### 8.4. Maximum Power Point Tracking

During SUPPLY STATE, SHUTDOWN STATE and START STATE, the voltage on SRC is regulated by an internal Maximum Power Point Tracking (MPPT) module. The MPPT module evaluates  $V_{MPP}$ , the voltage at which the source provides the highest possible power, as a given fraction of the open-circuit voltage of the source  $V_{OC}$ . This ratio is set by the R\_MPP[2:0]

terminals according to Table 10. The sampling period and duration are set according to Table 11 by the T\_MPP[1:0] terminals. The AEM10330 supports any  $V_{MPP}$  levels in the range from 100 mV to 4.5 V. It offers a choice of seven values for the  $V_{MPP}$  /  $V_{OC}$  fraction. It can also match the input impedance of the DCDC converter with an impedance connected to the ZMPP terminal as explain as explained in section 9.7.

### 8.5. Balancing for Dual-Cell Supercapacitor

The balancing circuit allows the user to balance the internal voltage of the dual-cell supercapacitor connected to STO in order to avoid damaging the supercapacitor because of excessive voltage on one cell.

If BAL is connected to GND, the balancing circuit is disabled. This configuration must be used if a battery, a capacitor or a single-cell supercapacitor is connected on STO.

If BAL is connected to the node between both cells of a supercapacitor, the balancing circuit compensates for any mismatch of the two cells that could lead to the over-charge of one of two cells. The balancing circuit ensures that BAL remains close to V<sub>STO</sub> / 2. This configuration must be used if a dual-cell supercapacitor is connected to STO, and that this supercapacitor requires cells balancing.

The balancing circuit works as follows, with  $V_{\text{BAL}}$  the voltage on the BAL pin:

- $V_{BAL} > \frac{V_{STO}}{2}$ : the AEM10330 enables a switch between BAL and GND to discharge the bottom supercapacitor cell to GND (up to 20 mA).

- $V_{BAL} < \frac{V_{STO}}{2}$ : the AEM10330 enables a switch between STO and BAL to discharge the top supercapacitor cell to the bottom supercapacitor cell (up to 20 mA).

NOTE: the balancing feature is optimized for supercapacitors, for use with other storage elements (batteries, etc.), please contact e-peas support.

### 9. System Configuration

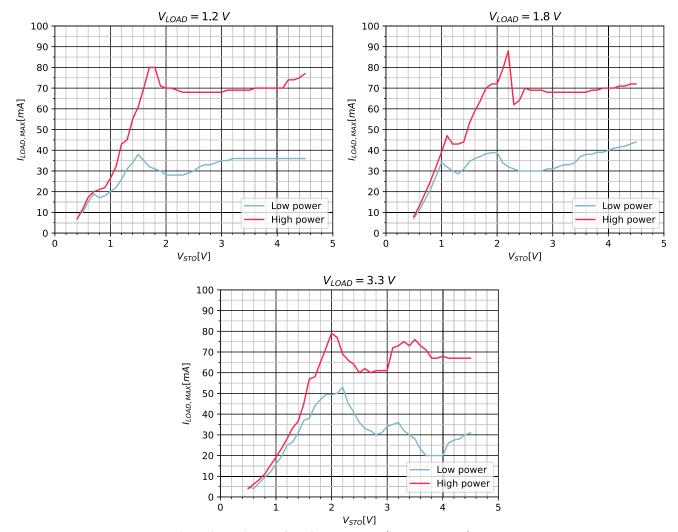

### 9.1. High Power / Low Power Mode

When EN\_HP is pulled to VINT, the DCDC converter is configured to HIGH POWER MODE. This allows higher currents to be extracted from the DCDC converter input (SRC or STO) to the DCDC converter output (LOAD or STO). Figure 6 shows the maximum current that the DCDC converter can supply to LOAD, depending on the storage voltage V<sub>STO</sub>, for every available load voltage V<sub>LOAD</sub>, for both HIGH POWER MODE and LOW POWER MODE.

Figure 6: Maximum LOAD Current Depending on  $V_{STO}$  and on  $V_{LOAD}$

### 9.2. Storage Element Configuration

Through four configuration pins (STO\_CFG[3:0]), the user can set a particular operating mode from a range that covers most application requirements, without any dedicated external component as shown in Table 8. The three threshold levels are defined as:

- V<sub>OVCH</sub>: maximum voltage accepted on the storage element before disabling its charging.

- V<sub>CHRDY</sub>: minimum voltage required on the storage element before starting to supply the LOAD (if STO\_PRIO is HIGH) and entering supply state after start-up.

V<sub>OVDIS</sub>: minimum voltage accepted on the storage element before considering the storage element as depleted, thus setting ST\_STO LOW.

A large-size storage element is not mandatory on STO:

- If the harvested energy source is permanently available and covers the application needs or

- If the application does not need to store energy when the harvested energy source is not available

The storage element may then be replaced by an external capacitor  $C_{\text{STO}}$  with a minimum value of 100  $\mu F.$

Caution: running the AEM10330 without this 100  $\mu\text{F}$  minimum capacitance on STO will permanently damage the circuit.

| Cor | Configuration pins |   |   | Storage element threshold voltages                    |                                                                                       |                                        | Typical use                                                                              |

|-----|--------------------|---|---|-------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------|

| S   | STO_CFG[3:0]       |   |   | V <sub>OVDIS</sub>                                    | V <sub>CHRDY</sub>                                                                    | V <sub>OVCH</sub>                      |                                                                                          |

| L   | L                  | L | L | 3.00 V                                                | 3.50 V                                                                                | 4.05 V                                 | LiCoO <sub>2</sub> battery, Li-Po battery, Lithium Titanate (3.8 V) battery (long life). |

| L   | L                  | L | Н | 2.80 V                                                | 3.10 V                                                                                | 3.60 V                                 | LiFePO <sub>4</sub> battery, Lithium capacitor (LiC).                                    |

| L   | L                  | Н | L | 1.85 V                                                | 2.40 V                                                                                | 2.70 V                                 | Dual-cell NiMH battery, Lithium-Titanate (2.4V) battery.                                 |

| L   | L                  | Н | Н | 0.20 V                                                | 1.00 V                                                                                | 4.65 V                                 | Dual-cell supercapacitor.                                                                |

| L   | Н                  | L | L | 0.20 V 1.00 V 2.60 V                                  |                                                                                       | 2.60 V                                 | Single-cell supercapacitor.                                                              |

| L   | Н                  | L | Н | 1.00 V 1.20 V 2.95 V                                  |                                                                                       | 2.95 V                                 | Single-cell supercapacitor.                                                              |

| L   | Н                  | Н | L | 1.85 V 2.30 V 2.60 V Lithium-Titanate battery (2.4V). |                                                                                       |                                        |                                                                                          |

| L   | Н                  | Н | Н | Cı                                                    |                                                                                       | Cı                                     | ustom Mode (single-cell NiMH battery, LiC, etc.) <sup>1</sup> .                          |

| Н   | L                  | L | L | 1.10 V                                                | 1.25 V                                                                                | 25 V 1.50 V Ni-Cd single-cell battery. |                                                                                          |

| Н   | L                  | L | Н | 2.20 V 2.50 V 3.00 V                                  |                                                                                       | 3.00 V                                 | Ni-Cd dual-cell battery.                                                                 |

| Н   | L                  | Н | L | 1.45 V 2.00 V 4.65 V                                  |                                                                                       | 4.65 V                                 | Dual-cell supercapacitor.                                                                |

| Н   | L                  | Н | Н | 1.00 V                                                | .00 V 1.20 V 2.60 V Single-cell superc                                                |                                        | Single-cell supercapacitor.                                                              |

| Н   | Н                  | L | L | 2.00 V                                                | 2.30 V                                                                                | 2.60 V                                 | Solid State battery.                                                                     |

| Н   | Н                  | L | Н | 3.00 V                                                | 3.00 V 3.50 V 4.35 V LiCoO <sub>2</sub> battery, Li-Po battery, Lithium Titanate (3.8 |                                        | LiCoO <sub>2</sub> battery, Li-Po battery, Lithium Titanate (3.8 V) battery.             |

| Н   | Н                  | Н | L | 2.60 V 2.70 V 4.00 V                                  |                                                                                       | 4.00 V                                 | Tadiran TLI.                                                                             |

| Н   | Н                  | Н | Н | 2.60 V 3.50 V 3.90 V                                  |                                                                                       | 3.90 V                                 | Tadiran HLC.                                                                             |

**Table 8: Storage Element Configuration Pins**

<sup>1.</sup> An example of a single-cell NiMH batteries optimized custom mode setting can be found at Section 10.2.

### 9.3. Load Configuration

The LOAD output voltage V<sub>LOAD</sub> can be configured thanks to the LOAD\_CFG[1:0] configuration pins covering most application cases (see Table 9).  $V_{\mbox{\scriptsize LOAD}}$  is regulated to  $V_{LOAD,TYP}$ . However, if  $V_{LOAD}$  falls below  $V_{LOAD,MID}$ , the controller forces STO as an input of the DCDC converter to supply LOAD.

When the AEM10330 is in SUPPLY STATE:

- V<sub>LOAD</sub> < V<sub>LOAD,MID</sub>: the AEM10330 charges C<sub>LOAD</sub> by transferring the energy available on the storage element STO (if V<sub>STO</sub> is above V<sub>OVDIS</sub>), even if energy is available on SRC.

- V<sub>LOAD,MID</sub> < V<sub>LOAD</sub> < V<sub>LOAD,MAX</sub>:

- If energy is available on SRC, the AEM10330 uses it to charge C<sub>LOAD</sub>.

- If no energy is available on SRC, the AEM10330 uses the energy available on STO to charge C<sub>LOAD</sub>.

- $V_{LOAD,TYP}$  is the typical average voltage to be expected on the LOAD pin.

- $ST_LOAD$  reflects  $V_{LOAD}$ , with an hysteresis between V<sub>LOAD,MIN</sub> and V<sub>LOAD,TYP</sub>:

- ST\_LOAD is HIGH when V<sub>LOAD</sub> > V<sub>LOAD</sub> TVP.

- ST\_LOAD is LOW when V<sub>LOAD</sub> < V<sub>LOAD,MIN</sub>.

- As a reminder, the order of priority in which the nodes are recharged is as follows:

- VINT always has the highest priority, as it is mandatory to keep the AEM10330 internal circuit supplied.

- LOAD has the second highest priority, to keep the application circuit supplied.

- STO has the lowest priority, as the storage element is used to store the excessive energy from SRC.

| Configura | ation pins | LOAD output voltage   |                       |                       |                       |

|-----------|------------|-----------------------|-----------------------|-----------------------|-----------------------|

| LOAD_C    | CFG[1:0]   | V <sub>LOAD,MIN</sub> | V <sub>LOAD,MID</sub> | V <sub>LOAD,TYP</sub> | V <sub>LOAD,MAX</sub> |

| L         | L          | 3.15 V                | 3.23 V                | 3.28 V                | 3.34 V                |

| L         | Н          | 2.35 V                | 2.47 V                | 2.50 V                | 2.53 V                |

| Н         | L          | 1.64 V                | 1.75 V                | 1.79 V                | 1.82 V                |

| Н         | Н          | 1.14 V                | 1.16 V                | 1.20 V                | 1.23 V                |

Table 9: Load Configuration Pins

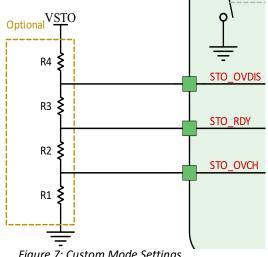

### 9.4. Custom Mode Configuration

Figure 7: Custom Mode Settings

When STO\_CFG[3:0] = LHHH, the custom mode is selected and all four configuration resistors must be wired as shown in Figure 7.

V<sub>OVCH</sub>, V<sub>CHRDY</sub> and, V<sub>OVDIS</sub> are defined thanks to R1, R2, R3 and R4, which can be determined within the following constraints:

$$- R_{T} = R_{1} + R_{2} + R_{3} + R_{4}$$

$$- 1M\Omega \le R_{T} \le 100M\Omega$$

$$- R_1 = R_T \cdot \frac{1V}{V_{OVCH}}$$

$$- R_2 = R_T \cdot \left( \frac{1V}{V_{CHRDY}} - \frac{1V}{V_{OVCH}} \right)$$

$$- R_3 = R_T \cdot \left(\frac{1V}{V_{OVDIS}} - \frac{1V}{V_{CHRDY}}\right)$$

$$- R_4 = R_T \cdot \left(1 - \frac{1V}{V_{OVDIS}}\right)$$

The resistors should have high values to make the additional power consumption negligible. Moreover, the following constraints must be respected to ensure the functionality of the chip:

-

$$V_{CHRDY} + 0.05 V \le V_{OVCH} \le 4.5 V$$

-

$$V_{OVDIS} + 0.05V \le V_{CHRDY} \le V_{OVCH} - 0.05V$$

### 9.5. Disable Storage Element Charging

Pulling down EN\_STO\_CH pin to GND disables the charging of the storage element connected to STO from SRC. This can be done for example to protect the storage element when the system detects that the environment temperature is too low or too high to safely charge the storage element.

While EN\_STO\_CH is pulled down, VINT and LOAD can still be supplied either from SRC or from STO.

To enable charging the storage element on STO, EN\_STO\_CH must be pulled up to LOAD or left floating (pin is pulled up internally).

Please note that STO will still be charged to  $V_{\text{CHRDY}}$  during the START STATE

### 9.6. MPPT Configuration

The MPPT module is configured through the following pins:

- R\_MPP[2:0] allows for configuring the V<sub>MPP</sub> / V<sub>OC</sub> tracking ratio, that has to be chosen according to the characteristics of the source. Please note that if the selected mode is ZMPP, an external resistor must be added to the circuit as explained in Section 9.7.

- T\_MPP[1:0] allows for configuring the duration of an MPP evaluation and the time between two MPP evaluations.

| Co | nfiguration p | MPPT ratio                         |      |

|----|---------------|------------------------------------|------|

|    | R_MPP[2:0]    | V <sub>MPP</sub> / V <sub>OC</sub> |      |

| L  | L             | L                                  | 60%  |

| L  | L             | Н                                  | 65%  |

| L  | Н             | L                                  | 70%  |

| L  | Н             | Н                                  | 75%  |

| Н  | L             | L                                  | 80%  |

| Н  | L             | Н                                  | 85%  |

| Н  | Н             | L                                  | 90%  |

| Н  | Н             | Н                                  | ZMPP |

Table 10: MPP Ratio Configuration Pins

| Configur | ation pins | MPPT timing       |                 |  |

|----------|------------|-------------------|-----------------|--|

| T_MF     | PP[1:0]    | Sampling duration | Sampling period |  |

| L        | L          | 5.19 ms           | 280 ms          |  |

| L        | Н          | 70.8 ms           | 4.5 s           |  |

| Н        | L          | 280 ms            | 17.9 s          |  |

| Н        | Н          | 1.12 s            | 71.7 s          |  |

Table 11: MPP Timing Configuration Pins

### 9.7. ZMPP Configuration

Instead of working at a ratio of the open-circuit voltage, the AEM10330 can regulate the input impedance of the DCDC converter so that it matches a constant impedance  $R_{ZMPP}$  connected to the ZMPP pin. In this case, the AEM10330 regulates  $V_{SRC}$  at a voltage that is the product of the ZMPP resistance  $R_{ZMPP}$  and the current available at the SRC input.

- 10 Ω ≤  $R_{ZMPP}$  ≤ 100 KΩ

Figure 8: R<sub>ZMPP</sub> Connection to the AEM10330

### 9.8. Source to Storage Element Feed-Through

When the harvester connected to SRC delivers a high amount of power, the AEM might not be able to pull enough current to regulate  $V_{SRC}$  to the MPP voltage. The voltage on SRC thus increases, eventually above 5V. To maximize the energy extracted in that case, the AEM30330 can be configured to create a direct feed-through current path from SRC to STO when  $V_{SRC}$  is above 5V. This is measured when the AEM is pulling current from the source (not during an MPP evaluation).

If the MPPT module detects that  $V_{SRC}$  is higher than 4 V and EN\_STO\_FT is set, the SRC is monitored. From that moment, if the AEM10330 detects that  $V_{SRC}$  rises above 5 V and if the storage element is not fully charged, the switch between the SRC and STO pins is closed until  $V_{SRC}$  drops below 5 V or until the storage element is fully charged.

This feature is enabled by pulling up EN\_STO\_FT pin to VINT. However, it is disabled if the storage element is fully charged, or when a MPP evaluation is occurring. Therefore the circuit must still be protected from any overshoot voltage on SRC above 5.5 V, for instance by a zener diode.

### 9.9. External Components

Refer to Figure 18 to have an illustration of the external components wiring.

#### 9.9.1. Storage Element Information

The energy storage element of the AEM10330 can be a rechargeable battery, a supercapacitor or a capacitor. The size of the storage element must be determined so that its voltage does not fall below V<sub>OVDIS</sub> even during current peaks pulled by the application circuit connected to LOAD. If the internal resistance of the storage element cannot sustain this voltage limit, it is advisable to decouple the battery with a capacitor.

If the application expects a disconnection of the battery (e.g. because of a user removable connector), the PCB should include a capacitor  $C_{STO}$  of at least 100  $\mu F$  connected between STO and GND. The leakage current of the storage element should be small as leakage currents directly impact the quiescent current of the whole subsystem.

#### 9.9.2. External Inductor Information

The AEM10330 operates with one standard miniature inductor. L\_DCDC must sustain a peak current of at least 1 A and a switching frequency of at least 10 MHz. Low equivalent series resistance (ESR) favors the power conversion efficiency of the DCDC converter. The recommended value is 10  $\mu\text{H}.$

#### 9.9.3. External Capacitors Information

### 9.9.3.1. C<sub>SRC</sub>

This capacitor acts as an energy buffer at the input of the DCDC converter. It prevents large voltage fluctuations when the DCDC converter is switching. The recommended nominal value is 22  $\mu\text{F}.$

### 9.9.3.2. C<sub>INT</sub>

This capacitor acts as an energy buffer for the internal voltage supply. The recommended nominal value is 10  $\mu\text{F}.$

### 9.9.3.3. C<sub>LOAD</sub>

This capacitor acts as an energy buffer for LOAD. It also reduces the voltage ripple induced by the current pulses inherent to the switched behavior of the converter. The recommended value is at least 13  $\mu F$  (considering derating and tolerance).

### 10. Typical Application Circuits

### 10.1. Example Circuit 1

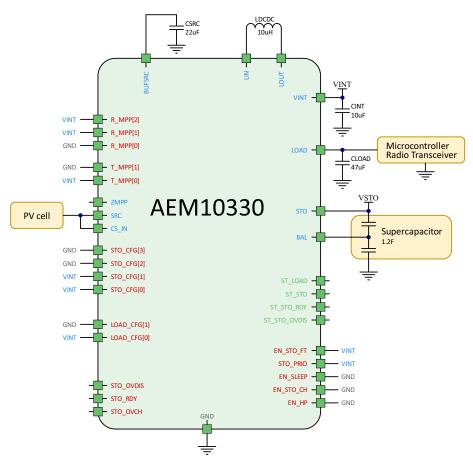

Figure 9: Typical Application Circuit 1

The circuit is an example of a system with solar energy harvesting. It uses a pre-defined operating mode that uses standard components, and a supercapacitor as energy storage.

- Energy source: PV cell.

- R\_MPP[2:0] = HHL: the MPP tracker ratio is set to

- T\_MPP[1:0] = LH: the MPP sampling period is 4.5 s and the MPP sampling duration is 70.8 ms.