# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

# 144-Mbit QDR<sup>®</sup> II+ SRAM Two-Word Burst Architecture with ODT and RadStop™ Technology

#### Radiation Performance

#### **Radiation Data**

- Total Dose = 200 Krad

- Soft error rate (both Heavy Ion and proton)

Heavy ions ≤ 1 × 10<sup>-10</sup> upsets/bit-day with an external SECDED EDAC Controller

- Dose rate =  $> 1.0 \times 10^9 \text{ rad(Si)/sec}$

- Dose rate survivability (rad(Si)/sec) = > 1.4 x 10<sup>10</sup> rad(Si)/sec

- Dose rate latchup (rad(Si)/sec) > 3.0 x 10<sup>9</sup> (125 °C)

- Latch up immunity = > 120 MeV.cm2/mg (125 °C)

### **Prototyping Options**

■ Non qualified CYPT2642KV18 and CYPT2644KV18 devices with same functional and timing characteristics in a 165-ball Ceramic Column Grid Array (CCGA) package

#### **Features**

- Separate independent read and write data ports

□ Supports concurrent transactions

- 250 MHz clock for high bandwidth

- Two-word burst for reducing address bus frequency

- Double data rate (DDR) interfaces on both read and write ports (data transferred at 500 MHz) at 250 MHz

- Available in 2.0 clock cycle latency

- Two input clocks (K and K) for precise DDR timing

□ SRAM uses rising edges only

- Echo clocks (CQ and CQ) simplify data capture in high-speed systems

- Data valid pin (QVLD) to indicate valid data on the output

- On-die termination (ODT) feature □ Supported for  $D_{[x:0]}$ , BWS $_{[x:0]}$ , and K/ $\overline{K}$  inputs

- Single multiplexed address input bus latches address inputs for both read and write ports

- Separate port selects for depth expansion

- Quad <u>data rate</u> (QDR<sup>®</sup>) II+ operates with 2.0 cycle read latency when DOFF is asserted high

- Operates similar to QDR I device with one cycle read latency when DOFF is asserted low

- Core  $V_{DD}$  = 1.8 V± 0.1 V; I/O  $V_{DDQ}$  = 1.4 V to  $V_{DD}$  [1]

□ Supports both 1.5 V and 1.8 V I/O supply

- High-speed transceiver logic (HSTL) inputs and variable drive HSTL output buffers

- Available in 165-ball CCGA (21 × 25 × 2.83 mm)

- JTAG 1149.1 compatible test access port

- Phase Locked Loop (PLL) for accurate data placement

### Configurations

With Read Cycle Latency of 2.0 cycles:

CYRS2642KV18 – 8M × 18 CYRS2644KV18 – 4M × 36

### **Functional Description**

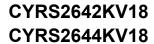

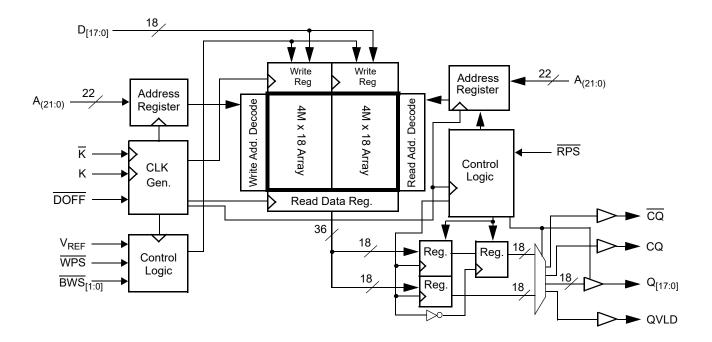

The CYRS2642KV18 and CYRS2644KV18 are 1.8 V synchronous pipelined SRAMs, equipped with QDR II+ architecture. Similar to QDR II architecture, QDR II+ architecture consists of two separate ports: the read port and the write port to access the memory array. The read port has dedicated data outputs to support read operations and the write port has dedicated data inputs to support write operations. QDR II+ architecture has separate data inputs and data outputs to completely eliminate the need to "turn around" the data bus that exists with common I/O devices. Access to each port is through a common address bus. Addresses for read and write addresses are latched on alternate rising edges of the input (K) clock. Accesses to the QDR II+ read and write ports are completely independent of one another. To maximize data throughput, both read and write ports are equipped with DDR interfaces. Each address location is associated with two 18-bit words (CYRS2642KV18) or 36-bit words (CYRS2644KV18) that burst sequentially into or out of the device. Because data can be transferred into and out of the device on every rising edge of both input clocks (K and K), memory bandwidth is maximized while simplifying system design by eliminating bus "turn arounds".

These devices have an ODT feature supported for  $D_{[x:0]}$ ,  $BWS_{[x:0]}$ , and K/K inputs, which helps eliminate external termination resistors, reduce cost, reduce board area, and simplify board routing.

Depth expansion is accomplished with port selects, which enables each port to operate independently.

All synchronous inputs pass through input registers controlled by the K or K input clocks. All data outputs pass through output registers controlled by the K or K input clocks. Writes are conducted with on-chip synchronous self-timed write circuitry.

Note

1. The Cypress QDR II+ devices surpass the QDR consortium specification and can support  $V_{DDQ} = 1.4 \text{ V}$  to  $V_{DD}$ .

### **Selection Guide**

| Description                    |      | 250 MHz | Unit |

|--------------------------------|------|---------|------|

| Maximum operating frequency    |      | 250     | MHz  |

| Maximum operating current      | × 18 | 900     | mA   |

| IMAXIIIIUIII Operating Current | × 36 | 1080    | ША   |

# **Logic Block Diagram - CYRS2642KV18**

# Logic Block Diagram - CYRS2644KV18

### **Contents**

| Pin Configurations                      | 5  |  |  |  |  |

|-----------------------------------------|----|--|--|--|--|

| Manufacturing Flow                      | 6  |  |  |  |  |

| Pin Definitions                         | 7  |  |  |  |  |

| Functional Overview                     | 9  |  |  |  |  |

| Read Operations                         | 9  |  |  |  |  |

| Write Operations                        |    |  |  |  |  |

| Byte Write Operations                   | 9  |  |  |  |  |

| Concurrent Transactions                 | 9  |  |  |  |  |

| Depth Expansion                         | 9  |  |  |  |  |

| Programmable Impedance                  | 9  |  |  |  |  |

| Echo Clocks                             | 10 |  |  |  |  |

| Valid Data Indicator (QVLD)             | 10 |  |  |  |  |

| On-Die Termination (ODT)                | 10 |  |  |  |  |

| PLL                                     |    |  |  |  |  |

| Qualification and Screening             | 10 |  |  |  |  |

| Application Example                     | 11 |  |  |  |  |

| Truth Table                             |    |  |  |  |  |

| Write Cycle Descriptions                |    |  |  |  |  |

| Write Cycle Descriptions                | 13 |  |  |  |  |

| IEEE 1149.1 Serial Boundary Scan (JTAG) |    |  |  |  |  |

| Disabling the JTAG Feature              |    |  |  |  |  |

| Test Access Port                        |    |  |  |  |  |

| Performing a TAP Reset                  | 14 |  |  |  |  |

| TAP Registers                           |    |  |  |  |  |

| TAP Instruction Set                     |    |  |  |  |  |

| TAP Controller State Diagram            |    |  |  |  |  |

| TAP Controller Block Diagram            | 17 |  |  |  |  |

| TAP Electrical Characteristics          |    |  |  |  |  |

| TAP AC Switching Characteristics        | 18 |  |  |  |  |

| TAP Timing and Test Conditions          |    |  |  |  |  |

| Identification Register Definitions20   |    |  |  |  |  |

| Scan Register Sizes20                   |    |  |  |  |  |

|-----------------------------------------|----|--|--|--|--|

| Instruction Codes                       | 20 |  |  |  |  |

| Boundary Scan Order                     | 21 |  |  |  |  |

| Power Up Sequence in QDR II+ SRAM       | 22 |  |  |  |  |

| Power Up Sequence                       |    |  |  |  |  |

| PLL Constraints                         | 22 |  |  |  |  |

| Maximum Ratings                         | 23 |  |  |  |  |

| Operating Range                         | 23 |  |  |  |  |

| Neutron Soft Error Immunity             | 23 |  |  |  |  |

| Electrical Characteristics              | 23 |  |  |  |  |

| DC Electrical Characteristics           | 23 |  |  |  |  |

| AC Electrical Characteristics           | 24 |  |  |  |  |

| Capacitance                             | 24 |  |  |  |  |

| Radiation Performance                   | 24 |  |  |  |  |

| Thermal Resistance                      |    |  |  |  |  |

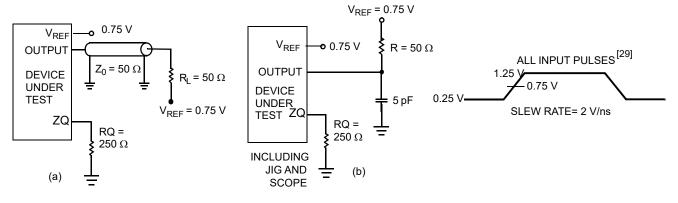

| AC Test Loads and Waveforms             | 24 |  |  |  |  |

| Switching Characteristics               | 25 |  |  |  |  |

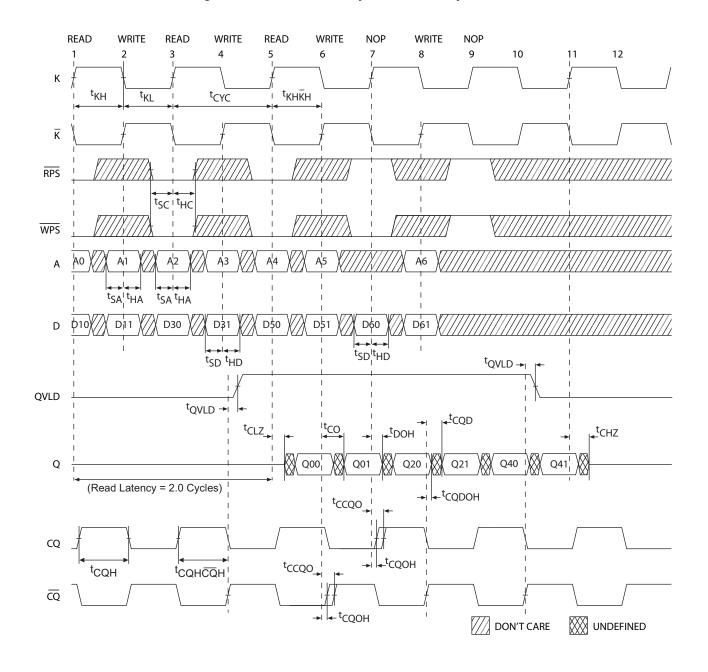

| Switching Waveforms                     | 26 |  |  |  |  |

| Read/Write/Deselect Sequence            | 26 |  |  |  |  |

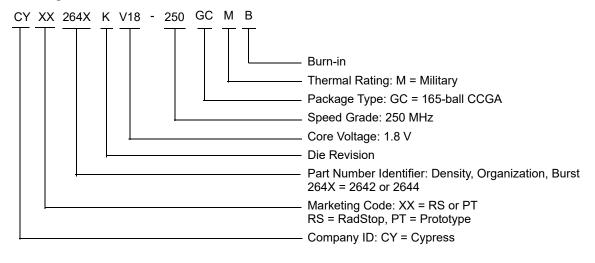

| Ordering Information                    | 27 |  |  |  |  |

| Ordering Code Definitions               | 27 |  |  |  |  |

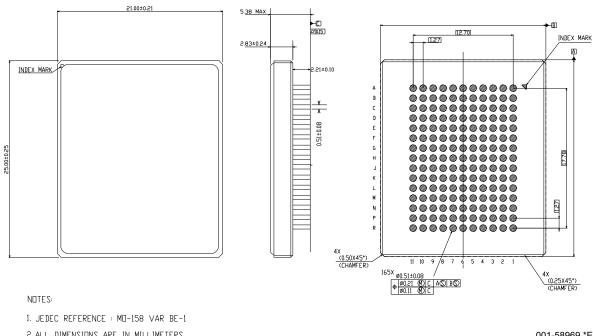

| Package Diagram                         | 28 |  |  |  |  |

| Acronyms                                | 29 |  |  |  |  |

| Document Conventions                    | 29 |  |  |  |  |

| Units of Measure                        |    |  |  |  |  |

| Document History Page                   |    |  |  |  |  |

| Sales, Solutions, and Legal Information |    |  |  |  |  |

| Worldwide Sales and Design Support      | 31 |  |  |  |  |

| Products                                |    |  |  |  |  |

| PSoC® Solutions                         |    |  |  |  |  |

| Cypress Developer Community             |    |  |  |  |  |

| Technical Support                       | 31 |  |  |  |  |

# **Pin Configurations**

The pin configurations for CYRS2642KV18, and CYRS2644KV18 follow. [2]

Figure 1. 165-ball CCGA (21 × 25 × 2.83 mm) Pinout CYRS2642KV18 (8M × 18)

|   | 1    | 2         | 3         | 4               | 5                | 6               | 7                | 8               | 9         | 10        | 11  |

|---|------|-----------|-----------|-----------------|------------------|-----------------|------------------|-----------------|-----------|-----------|-----|

| Α | CQ   | Α         | Α         | WPS             | BWS <sub>1</sub> | K               | NC/288M          | RPS             | А         | Α         | CQ  |

| В | NC   | Q9        | D9        | Α               | NC               | K               | BWS <sub>0</sub> | Α               | NC        | NC        | Q8  |

| С | NC   | NC        | D10       | V <sub>SS</sub> | Α                | Α               | Α                | V <sub>SS</sub> | NC        | Q7        | D8  |

| D | NC   | D11       | Q10       | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | NC        | NC        | D7  |

| E | NC   | NC        | Q11       | $V_{DDQ}$       | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | $V_{DDQ}$       | NC        | D6        | Q6  |

| F | NC   | Q12       | D12       | $V_{DDQ}$       | $V_{DD}$         | V <sub>SS</sub> | $V_{DD}$         | $V_{DDQ}$       | NC        | NC        | Q5  |

| G | NC   | D13       | Q13       | $V_{DDQ}$       | $V_{DD}$         | V <sub>SS</sub> | $V_{DD}$         | $V_{DDQ}$       | NC        | NC        | D5  |

| Н | DOFF | $V_{REF}$ | $V_{DDQ}$ | $V_{DDQ}$       | $V_{DD}$         | V <sub>SS</sub> | $V_{DD}$         | $V_{DDQ}$       | $V_{DDQ}$ | $V_{REF}$ | ZQ  |

| J | NC   | NC        | D14       | $V_{DDQ}$       | $V_{DD}$         | V <sub>SS</sub> | $V_{DD}$         | $V_{DDQ}$       | NC        | Q4        | D4  |

| K | NC   | NC        | Q14       | $V_{DDQ}$       | $V_{DD}$         | V <sub>SS</sub> | $V_{DD}$         | $V_{DDQ}$       | NC        | D3        | Q3  |

| L | NC   | Q15       | D15       | $V_{DDQ}$       | $V_{SS}$         | V <sub>SS</sub> | V <sub>SS</sub>  | $V_{DDQ}$       | NC        | NC        | Q2  |

| М | NC   | NC        | D16       | $V_{SS}$        | $V_{SS}$         | V <sub>SS</sub> | V <sub>SS</sub>  | $V_{SS}$        | NC        | Q1        | D2  |

| N | NC   | D17       | Q16       | V <sub>SS</sub> | Α                | Α               | Α                | V <sub>SS</sub> | NC        | NC        | D1  |

| Р | NC   | NC        | Q17       | Α               | Α                | QVLD            | Α                | Α               | NC        | D0        | Q0  |

| R | TDO  | TCK       | Α         | Α               | Α                | ODT             | А                | Α               | Α         | TMS       | TDI |

### CYRS2644KV18 (4M × 36)

|   | 1    | 2         | 3         | 4               | 5                | 6               | 7                | 8                  | 9         | 10        | 11  |

|---|------|-----------|-----------|-----------------|------------------|-----------------|------------------|--------------------|-----------|-----------|-----|

| Α | CQ   | NC/288M   | Α         | WPS             | BWS <sub>2</sub> | K               | BWS <sub>1</sub> | RPS                | Α         | Α         | CQ  |

| В | Q27  | Q18       | D18       | Α               | BWS <sub>3</sub> | K               | BWS <sub>0</sub> | Α                  | D17       | Q17       | Q8  |

| С | D27  | Q28       | D19       | V <sub>SS</sub> | Α                | Α               | Α                | V <sub>SS</sub>    | D16       | Q7        | D8  |

| D | D28  | D20       | Q19       | $V_{SS}$        | $V_{SS}$         | V <sub>SS</sub> | $V_{SS}$         | $V_{SS}$           | Q16       | D15       | D7  |

| E | Q29  | D29       | Q20       | $V_{DDQ}$       | $V_{SS}$         | V <sub>SS</sub> | V <sub>SS</sub>  | $V_{\mathrm{DDQ}}$ | Q15       | D6        | Q6  |

| F | Q30  | Q21       | D21       | $V_{DDQ}$       | $V_{DD}$         | V <sub>SS</sub> | $V_{DD}$         | $V_{\mathrm{DDQ}}$ | D14       | Q14       | Q5  |

| G | D30  | D22       | Q22       | $V_{DDQ}$       | $V_{DD}$         | V <sub>SS</sub> | $V_{DD}$         | $V_{DDQ}$          | Q13       | D13       | D5  |

| Н | DOFF | $V_{REF}$ | $V_{DDQ}$ | $V_{DDQ}$       | $V_{DD}$         | $V_{SS}$        | $V_{DD}$         | $V_{DDQ}$          | $V_{DDQ}$ | $V_{REF}$ | ZQ  |

| J | D31  | Q31       | D23       | $V_{DDQ}$       | $V_{DD}$         | V <sub>SS</sub> | $V_{DD}$         | $V_{DDQ}$          | D12       | Q4        | D4  |

| K | Q32  | D32       | Q23       | $V_{DDQ}$       | $V_{DD}$         | V <sub>SS</sub> | $V_{DD}$         | $V_{DDQ}$          | Q12       | D3        | Q3  |

| L | Q33  | Q24       | D24       | $V_{DDQ}$       | $V_{SS}$         | V <sub>SS</sub> | V <sub>SS</sub>  | $V_{DDQ}$          | D11       | Q11       | Q2  |

| M | D33  | Q34       | D25       | $V_{SS}$        | $V_{SS}$         | V <sub>SS</sub> | V <sub>SS</sub>  | $V_{SS}$           | D10       | Q1        | D2  |

| N | D34  | D26       | Q25       | V <sub>SS</sub> | Α                | Α               | Α                | V <sub>SS</sub>    | Q10       | D9        | D1  |

| Р | Q35  | D35       | Q26       | Α               | Α                | QVLD            | Α                | Α                  | Q9        | D0        | Q0  |

| R | TDO  | TCK       | Α         | Α               | Α                | ODT             | Α                | Α                  | Α         | TMS       | TDI |

Note

2. NC/288M is not connected to the die and can be tied to any voltage level.

# **Manufacturing Flow**

| Step | Screen                                        | Method                                                                                               | Requirement    |

|------|-----------------------------------------------|------------------------------------------------------------------------------------------------------|----------------|

| 1    | Wafer lot acceptance test                     | TM 5007                                                                                              | _              |

| 2    | Internal visual                               | 2010, Condition A                                                                                    | 100%           |

| 3    | Serialization                                 |                                                                                                      | 100%           |

| 4    | Temperature cycling                           | 1010, Condition C, 50 cycles minimum                                                                 | 100%           |

| 5    | Constant acceleration                         | 2001, YI orientation only                                                                            | 100%           |

| 6    |                                               | Condition TBD (package in design)                                                                    |                |

| 7    | Particle impact noise detection (PIND)        | 2020 Condition A                                                                                     | 100%           |

| 8    | Radiographic (X-ray)                          | 2012, one view (Y-1 orientation) only                                                                |                |

| 9    | Pre burn in electrical parameters             | In accordance with applicable Cypress specification                                                  | 100%           |

| 10   | Dynamic burn in                               | 1015, Condition D                                                                                    | 100%           |

| 10   |                                               | 240 hours at 125 °C or 120 hours at 150 °C minimum                                                   |                |

| 11   | Interim (post dynamic burn in) electricals    | In accordance with applicable Cypress device specifications                                          | 100%           |

| 12   | Static burn in                                | 1015, Condition C, 72 hours at 150 $^{\circ}\text{C}$ or 144 hours at 125 $^{\circ}\text{C}$ minimum | 100%           |

| 13   | Interim (post static burn in) electricals     | In accordance with applicable Cypress device specifications                                          | 100%           |

| 14   | Percent defective allowable (PDA) calculation | 5% overall, 3% functional parameters at 25 °C                                                        | All lots       |

| 15   | Final electrical test                         | In accordance with applicable Cypress device specifications                                          | 100%           |

|      | a. Static tests                               |                                                                                                      |                |

|      | (1) 25 °C                                     | 5005, Table I, Subgroup 1                                                                            |                |

|      | (2) –55 °C and +125 °C                        | 5005, Table I, Subgroup 2, 3                                                                         |                |

|      | b. Functional tests                           |                                                                                                      |                |

|      | (1) 25 °C                                     | 5005, Table I, Subgroup 7                                                                            |                |

|      | (2) –55 °C and +125 °C                        | 5005, Table I, Subgroup 8a, 8b                                                                       |                |

|      | c. Switching test at 25 °C                    | 5005, Table I, Subgroup 9                                                                            |                |

| 16   | Seal (fine and gross leak test)               | 1014                                                                                                 | 100%           |

| 17   | External visual                               | 2009                                                                                                 | 100%           |

| 18   | Wafer lot specific life test (Group C)        | Mil-PRF 38535, Appendix B, section B.4.2.c                                                           | All wafer lots |

|      |                                               |                                                                                                      |                |

# **Pin Definitions**

| Pin Name                                                                  | I/O                                | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|---------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D <sub>[x:0]</sub>                                                        | Input-<br>Synchronous              | <b>Data input signals</b> . Sampled on the rising edge of K and $\overline{K}$ clocks during valid write operations. CYRS2642KV18 – D <sub>[17:0]</sub> CYRS2644KV18 – D <sub>[35:0]</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| WPS                                                                       | Input-<br>Synchronous              | <b>ite port select</b> – <b>Active low</b> . Sampled on the rising edge of the K clock. When asserted active te operation is initiated. Deasserting deselects the write port. Deselecting the write port ignores $D_{[i]}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| BWS <sub>0</sub> , BWS <sub>1</sub> , BWS <sub>2</sub> , BWS <sub>3</sub> | Input-<br>Synchronous              | Byte write select 0, 1, 2, and 3 – Active low. Sampled on the rising edge of the K and $\overline{K}$ clocks during write operations. Used to select which byte is written into the device during the current portion of the write operations. Bytes not written remain unaltered. $CYRS2642KV18 - \underline{BWS_0} \text{ controls } D_{[8:0]} \text{ and } \underline{BWS_1} \text{ controls } D_{[17:9]}.$ $CYRS2644KV18 - \underline{BWS_0} \text{ controls } D_{[8:0]}, \ \underline{BWS_1} \text{ controls } D_{[17:9]}, \ \underline{BWS_2} \text{ controls } D_{[26:18]} \text{ and } \underline{BWS_3} \text{ controls } D_{[35:27]}.$ All the byte write selects are sampled on the same edge as the data. Deselecting a byte write select ignores the corresponding byte of data and it is not written into the device. |  |  |  |  |  |

| A                                                                         | Input-<br>Synchronous              | Address inputs. Sampled on the rising edge of the K (read address) and $\overline{K}$ (write address) clocks during active read and write operations. These address inputs are multiplexed for both read and write operations. Internally, the device is organized as $8M \times 18$ (2 arrays each of $4M \times 18$ ) for CYRS2642KV18, and $4M \times 36$ (2 arrays each of $2M \times 36$ ) for CYRS2644KV18. Therefore, only 22 address inputs for CYRS2642KV18, and 21 address inputs for CYRS2644KV18. These inputs are ignored when the appropriate port is deselected.                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Q <sub>[x:0]</sub>                                                        | Output-<br>Synchronous             | <b>Data output signals</b> . These pins drive out the requested data during a read operation. Valid data is driven out on the rising edge of the K and $\overline{K}$ clocks during read operations. When the read port is deselected, $Q_{[x:0]}$ are automatically tri-stated.<br>$CYRS2642KV18 - Q_{[17:0]} \\ CYRS2644KV18 - Q_{[35:0]}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| RPS                                                                       | Input-<br>Synchronous              | Read port select – Active low. Sampled on the rising edge of positive input clock (K). When active, a read operation is initiated. Deasserting deselects the read port. When deselected, the pending access is allowed to complete and the output drivers are automatically tri-stated following the next rising edge of the K clock. Each read access consists of a burst of two sequential transfers.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| QVLD                                                                      | Valid output indicator             | Valid output indicator. The Q Valid indicates valid output data. QVLD is edge aligned with CQ and CQ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| ODT <sup>[3]</sup>                                                        | On-die<br>termination<br>input pin | <b>On-die termination input</b> . This pin is used for On-Die termination of the input signals. ODT range selection is made during power up initialization. A low on this pin selects a low range that follows RQ/3.33 for $175~\Omega \le RQ \le 350~\Omega$ (where RQ is the resistor tied to ZQ pin). A high on this pin selects a high range that follows RQ/1.66 for $175~\Omega \le RQ \le 250~\Omega$ (where RQ is the resistor tied to ZQ pin). When left floating, a high range termination value is selected by default.                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

$<sup>\</sup>label{eq:odd_equation} \textbf{Note} \\ 3. \ \ \text{On-Die Termination (ODT) feature is supported for D}_{[x:0]}, \ \text{BWS}_{[x:0]}, \ \text{and K/K inputs.}$

# Pin Definitions (continued)

| Pin Name         | I/O                 | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| К                | Input Clock         | <b>Positive input clock input</b> . The rising edge of K is used to capture synchronous inputs to the device and to drive out data through $Q_{[x:0]}$ . All accesses are initiated on the rising edge of K.                                                                                                                                                                                                                                                                  |  |  |  |  |

| ĸ                | Input Clock         | gative input clock input. $\overline{K}$ is used to capture synchronous inputs being presented to the device and lrive out data through $Q_{[x:0]}$ .                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| CQ               | Echo Clock          | nchronous echo clock outputs. This is a free-running clock and is synchronized to the input clock of the QDR II+. The timing for the echo clocks is shown in Switching Characteristics on page 25.                                                                                                                                                                                                                                                                            |  |  |  |  |

| CQ               | Echo Clock          | <b>Synchronous echo clock outputs</b> . This is a free-running clock and is synchronized to the input clock (K) of the QDR II+. The timing for the echo clocks is shown in the Switching Characteristics on page 25.                                                                                                                                                                                                                                                          |  |  |  |  |

| ZQ               | Input               | <b>Output impedance matching input</b> . This input is used to tune the device outputs to the system data bus impedance. CQ, CQ, and $Q_{[x:0]}$ output impedance are set to $0.2 \times RQ$ , where RQ is a resistor connected between ZQ and ground. Alternatively, connect this pin directly to $V_{DDQ}$ , which enables the minimum impedance mode. This pin cannot be connected directly to GND or left unconnected.                                                    |  |  |  |  |

| DOFF             | Input               | <b>PLL turn off</b> – <b>Active low</b> . Connecting this pin to ground turns off the PLL inside the device. The timing in the operation with the PLL turned off differs from those listed in this data sheet. For normal operation, connect this pin to a pull up through a 10 K $\Omega$ or less pull up resistor. The device behaves in QDR I mode when the PLL is turned off. In this mode, the device can be operated at a frequency of up to 167 MHz with QDR I timing. |  |  |  |  |

| TDO              | Output              | Test data-out (TDO) pin for JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| TCK              | Input               | Test clock (TCK) pin for JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| TDI              | Input               | Test data-in (TDI) pin for JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| TMS              | Input               | Test mode select (TMS) pin for JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| NC               | N/A                 | Not connected to the die. Can be tied to any voltage level.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| NC/288M          | Input               | Not connected to the die. Can be tied to any voltage level.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| V <sub>REF</sub> | Input-<br>Reference | Reference voltage input. Static input used to set the reference level for HSTL inputs, outputs, and AC measurement points.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| $V_{DD}$         | Power Supply        | Power supply inputs to the core of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| V <sub>SS</sub>  | Ground              | Ground for the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| $V_{DDQ}$        | Power Supply        | Power supply inputs for the outputs of the device.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

#### Functional Overview

The CYRS2642KV18, and CYRS2644KV18 are synchronous pipelined Burst SRAMs equipped with a read port and a write port. The read port is dedicated to read operations and the write port is dedicated to write operations. Data flows into the SRAM through the write port and flows out through the read port. These devices multiplex the address inputs to minimize the number of address pins required. By having separate read and write ports, the QDR II+ completely eliminates the need to "turn around" the data bus and avoids any possible data contention, thereby simplifying system design. Each access consists of two 18-bit data transfers in the case of CYRS2642KV18, and two 36-bit data transfers in the case of CYRS2644KV18 in one clock cycle.

<u>These</u> devices operate with a <u>read</u> latency of two cycles when DOFF pin is tied high. When DOFF pin is set low or connected to  $V_{SS}$  then the device behaves in QDR I mode with a read latency of one clock cycle.

Accesses for both ports are initiated on the rising edge of the positive input clock (K). All synchronous input and output timing are referenced from the rising edge of the input clocks (K and K).

All synchronous data inputs  $(D_{[x:0]})$  pass through input registers controlled by the input clocks (K and K). All synchronous data outputs  $(Q_{[x:0]})$  pass through output registers controlled by the rising edge of the input clocks (K and K) as well.

All synchronous control ( $\overline{RPS}$ ,  $\overline{WPS}$ ,  $\overline{BWS}_{[x:0]}$ ) inputs pass through input <u>registers</u> controlled by the rising edge of the input clocks (K and  $\overline{K}$ ).

CYRS2642KV18 is described in the following sections. The same basic descriptions apply to CYRS2644KV18.

#### Read Operations

The CYRS2642KV18 is organized internally as two arrays of 4M × 18. Accesses are completed in a burst of two sequential 18-bit data words. Read operations are initiated by asserting RPS active at the rising edge of the positive input clock (K). The address is latched on the rising edge of the K clock. The address presented to the address inputs is stored in the read address register. Following the next two K clock rise, the corresponding lowest order 18-bit word of data is driven onto the  $Q_{[17:0]}$  using K as the output timing reference. On the subsequent rising edge of K, the next 18-bit data word is driven onto the  $Q_{[17:0]}$ . The requested data is valid 0.45 ns from the rising edge of the input clock (K and  $\overline{K}$ ).

When the read port is deselected, the CYRS2642KV18 first completes the pending read transactions. Synchronous internal circuitry automatically tri-states the outputs following the next rising edge of the positive input clock (K). This enables for a seamless transition between devices without the insertion of wait states in a depth expanded memory.

### **Write Operations**

Write operations are initiated by asserting WPS active at the rising edge of the positive input clock (K). On the same K clock rise the data presented to  $D_{[17:0]}$  is latched and stored into the lower 18-bit write data register, provided  $\overline{BWS}_{[1:0]}$  are both asserted active. On the subsequent rising edge of the negative input clock (K), the address is latched and the information presented to  $D_{[17:0]}$  is also stored into the write data register, provided  $\overline{BWS}_{[1:0]}$  are both asserted active. The 36 bits of data are then written into the memory array at the specified location.

When deselected, the write port ignores all inputs after the pending write operations have been completed.

#### **Byte Write Operations**

Byte write operations are supported by the CYRS2642KV18. A write operation is initiated as described in the Write Operations section. The bytes that are written are determined by BWS<sub>0</sub> and BWS<sub>1</sub>, which are sampled with each set of 18-bit data words. Asserting the appropriate Byte Write Select input during the data portion of a write latches the data being presented and writes it into the device. Deasserting the Byte Write Select input during the data portion of a write enables the data stored in the device for that byte to remain unaltered. This feature can be used to simplify read, modify, or write operations to a byte write operation.

#### **Concurrent Transactions**

The read and write ports on the CYRS2642KV18 operate completely independently of one another. As each port latches the address inputs on different clock edges, the user can read or write to any location, regardless of the transaction on the other port. The user can start reads and writes in the same clock cycle. If the ports access the same location at the same time, the SRAM delivers the most recent information associated with the specified address location. This includes forwarding data from a write cycle that was initiated on the previous K clock rise.

#### **Depth Expansion**

The CYRS2642KV18 has a port select input for each port. This enables for easy depth expansion. Both port selects are sampled on the rising edge of the positive input clock only (K). Each port select input can deselect the specified port. Deselecting a port does not affect the other port. All pending transactions (read and write) are completed before the device is deselected.

### Programmable Impedance

An external resistor, RQ, must be connected between the ZQ pin on the SRAM and  $V_{SS}$  to enable the SRAM to adjust its output driver impedance. The value of RQ must be 5 × the value of the intended line impedance driven by the SRAM. The allowable range of RQ to guarantee impedance matching with a tolerance of ±15% is between 175  $\Omega$  and 350  $\Omega$ , with  $V_{DDQ}$  = 1.5 V. The output impedance is adjusted every 1024 cycles upon power up to account for drifts in supply voltage and temperature.

#### **Echo Clocks**

Echo clocks are provided on the QDR II+ to simplify data capture on high speed systems. Two echo clocks are generated  $\underline{by}$  the QDR II+. CQ is referenced with respect to K and  $\overline{CQ}$  is referenced with respect to K. These are free-running clocks and are synchronized to the input clock of the QDR II+. The timing for the echo clocks is shown in the Switching Characteristics on page 25.

#### Valid Data Indicator (QVLD)

QVLD is provided on the QDR II+ to simplify data capture on high speed systems. The QVLD is generated by the QDR II+ device along with data output. This signal is also edge-aligned with the echo clock and follows the timing of any data pin. This signal is asserted half a cycle before valid data arrives.

#### **On-Die Termination (ODT)**

These devices have an on-die termination feature for data inputs  $(D_{[X:0]})$ , Byte Write Selects  $(BWS_{[X:0]})$ , and Input Clocks (K) and (K). The termination resistors are integrated within the chip. The ODT range selection is enabled through ball R6 (ODT) pin. The ODT termination tracks value of RQ where RQ is the resistor tied to the ZQ pin. ODT range selection is made during power up initialization. A low on this pin selects a low range that follows RQ/3.33 for  $175 \Omega \leq RQ \leq 350 \Omega$  (where RQ is the resistor tied to ZQ pin). A high on this pin selects a high range that follows RQ/1.66 for  $175 \Omega \leq RQ \leq 250 \Omega$  (where RQ is the resistor tied to ZQ pin). When left floating, a high range termination value is selected by default. For a detailed description of ODT implementation, refer to the application note, (AN42468, CN)-Die Termination for (AN42468, CN)-Die Terminati

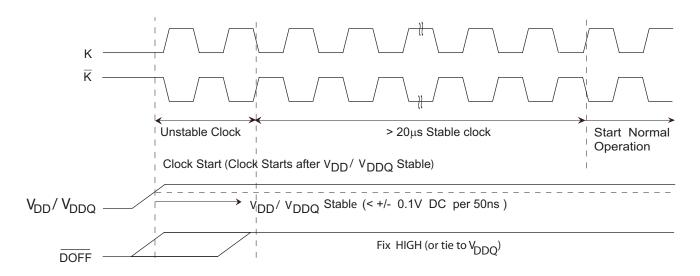

#### **PLL**

These chips use a PLL that is designed to function between 120 MHz and the specified maximum clock frequency. During power up, when the DOFF is tied high, the PLL is locked after 20  $\mu$ s of stable clock. The PLL can also be reset by slowing or stopping the input clocks K and  $\overline{K}$  for a minimum of 30 ns. However, it is not necessary to reset the PLL to lock to the desired frequency. The PLL automatically locks 20  $\mu$ s after a stable clock is presented. The PLL may be disabled by applying ground to the DOFF pin. When the PLL is turned off, the device behaves in QDR I mode (with one cycle latency and a longer access time). For information refer to the application note AN46982 - "PLL Considerations in QDR-II/QDR-II+/DDR-II/DDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-II/PDR-I

#### **Qualification and Screening**

The 65-nm RadStop technology was qualified by Cypress after meeting the criteria of the General Manufacturing Standards. The test flow includes screening units with the defined flow (Class Q, Class V) and the appropriate periodic or lot conformance testing (Groups B, C, D, and E). Both the 90-nm process and the SRAM products are subject to period or lot-based technology conformance inspection (TCI) and quality conformance inspection (QCI) tests, respectively. Cypress offers both prototyping models and flight units of these product configurations.

**Table 1. Qualification Tests**

| <b>Group Test</b> | Feature                                                                                                                                          |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Group A           | General electrical tests                                                                                                                         |

| Group B           | Mechanical - Dimensions, bond strength, solvents, die shear, solderability, lead Integrity, seal, and acceleration                               |

| Group C           | Life tests - 1000 hours at 125 °C or equivalent                                                                                                  |

| Group D           | Package related mechanical tests - shock, vibration, accel, salt, seal, lead finish adhesion, lid torque, thermal shock, and moisture resistance |

| Group E           | Radiation tests                                                                                                                                  |

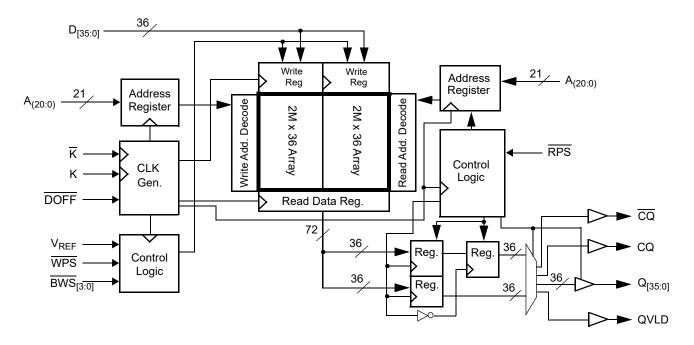

## **Application Example**

Figure 2 shows two QDR II+ used in an application.

Figure 2. Application Example (Width Expansion)

### **Truth Table**

The truth table for CYRS2642KV18, and CYRS2644KV18 follows.  $^{[4,\;5,\;6,\;7,\;8,\;9]}$

| Operation                                                                                                                 | K       | RPS | WPS | DQ                 | DQ                                     |

|---------------------------------------------------------------------------------------------------------------------------|---------|-----|-----|--------------------|----------------------------------------|

| Write Cycle: Load address on the rising edge of K; input write data on K and K rising edges.                              | L-H     | X   | L   | D(A) at K(t) ↑     | D(A + 1) at $\overline{K}(t) \uparrow$ |

| Read Cycle: (2.0 cycle Latency) Load address on the rising edge of K; wait two cycles; read data on K and K rising edges. | L–H     | L   | Х   | Q(A) at K(t + 2) ↑ | Q(A + 1) at K(t + 2) ↑                 |

| NOP: No Operation                                                                                                         | L–H     | Н   |     |                    | D = X<br>Q = High Z                    |

| Standby: Clock Stopped                                                                                                    | Stopped | Х   | Х   | Previous State     | Previous State                         |

### **Write Cycle Descriptions**

The write cycle description table for CYRS2642KV18 follows. [4, 10]

| BWS <sub>0</sub> | BWS <sub>1</sub> | K   | K   | Comments                                                                                                                                                                    |

|------------------|------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L                | L                | L-H | ı   | During the data portion of a write sequence:<br>CYRS2642KV18 – both bytes (D <sub>[17:0]</sub> ) are written into the device.                                               |

| L                | L                | _   | L–H | During the data portion of a write sequence: CYRS2642KV18 – both bytes (D <sub>[17:0]</sub> ) are written into the device.                                                  |

| L                | Н                | L–H | -   | During the data portion of a write sequence: CYRS2642KV18 – only the lower byte $(D_{[8:0]})$ is written into the device, $D_{[17:9]}$ remains unaltered.                   |

| L                | Н                | _   | L–H | During the data portion of a write sequence: CYRS2642KV18 – only the lower byte (D <sub>[8:0]</sub> ) is written into the device, D <sub>[17:9]</sub> remains unaltered.    |

| Н                | L                | L–H | -   | During the data portion of a write sequence: CYRS2642KV18 – only the upper byte (D <sub>[17:9]</sub> ) is written into the device, D <sub>[8:0]</sub> remains unaltered.    |

| Н                | L                | _   | L–H | During the data portion of a write sequence:<br>CYRS2642KV18 – only the upper byte (D <sub>[17:9]</sub> ) is written into the device, D <sub>[8:0]</sub> remains unaltered. |

| Н                | Н                | L–H | _   | No data is written into the devices during this portion of a write operation.                                                                                               |

| Н                | Н                |     | L–H | No data is written into the devices during this portion of a write operation.                                                                                               |

#### Notes

- 4. X = "Don't Care," H = Logic HIGH, L = Logic LOW, ↑ represents rising edge.

5. Device powers up deselected with the outputs in a tri-state condition.

- "A" represents address location latched by the devices when transaction was initiated. A + 1 represents the internal address sequence in the burst.

"t" represents the cycle at which a Read/Write operation is started. t + 1, and t + 2 are the first, and second clock cycles respectively succeeding the "t" clock cycle.

Data inputs are registered at K and K rising edges. Data outputs are delivered on K and K rising edges as well.

- 9. It is recommended that K = K = HIGH when clock is stopped. This is not essential, but permits most rapid restart by overcoming transmission line charging symmetrically. 10. Is based on a write cycle that was initiated in accordance with the Truth Table. BWS<sub>0</sub>, BWS<sub>1</sub>, BWS<sub>2</sub> and BWS<sub>3</sub> can be altered on different portions of a write cycle, as long as the setup and hold requirements are achieved.

# **Write Cycle Descriptions**

The write cycle description table for CYRS2644KV18 follow. [11, 12]

| BWS <sub>0</sub> | BWS <sub>1</sub> | BWS <sub>2</sub> | BWS <sub>3</sub> | K   | ĸ   | Comments                                                                                                                                                 |  |

|------------------|------------------|------------------|------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| L                | L                | L                | L                | L–H | ı   | During the data portion of a write sequence, all four bytes $(D_{[35:0]})$ are written into the device.                                                  |  |

| L                | L                | L                | L                | -   | L–H | During the data portion of a write sequence, all four bytes ( $D_{[35:0]}$ ) are written into the device.                                                |  |

| L                | Н                | Η                | Н                | L–H | ı   | – During the data portion of a write sequence, only the lower byte $(D_{[8:0]})$ is wrinto the device. $D_{[35:9]}$ remains unaltered.                   |  |

| L                | Н                | Н                | Н                | -   | L–H | L–H During the data portion of a write sequence, only the lower byte $(D_{[8:0]})$ is wrinto the device. $D_{[35:9]}$ remains unaltered.                 |  |

| Н                | L                | Η                | Н                | L–H | ı   | During the data portion of a write sequence, only the byte $(D_{[17:9]})$ is written into the device. $D_{[8:0]}$ and $D_{[35:18]}$ remains unaltered.   |  |

| Н                | L                | Ι                | Н                | -   | Ŧ   | During the data portion of a write sequence, only the byte $(D_{[17:9]})$ is written into the device. $D_{[8:0]}$ and $D_{[35:18]}$ remains unaltered.   |  |

| Н                | Н                | L                | Н                | L–H | -   | During the data portion of a write sequence, only the byte $(D_{[26:18]})$ is written into the device. $D_{[17:0]}$ and $D_{[35:27]}$ remains unaltered. |  |

| Н                | Н                | L                | Н                | -   | L–H | During the data portion of a write sequence, only the byte $(D_{[26:18]})$ is written into the device. $D_{[17:0]}$ and $D_{[35:27]}$ remains unaltered. |  |

| Н                | Н                | Ι                | L                | L–H | 1   | During the data portion of a write sequence, only the byte $(D_{[35:27]})$ is written into the device. $D_{[26:0]}$ remains unaltered.                   |  |

| Н                | Н                | Η                | L                | -   | L–H | During the data portion of a write sequence, only the byte $(D_{[35:27]})$ is written into the device. $D_{[26:0]}$ remains unaltered.                   |  |

| Н                | Н                | Н                | Н                | L–H | -   | No data is written into the device during this portion of a write operation.                                                                             |  |

| Н                | Н                | Н                | Н                | -   | L–H | No data is written into the device during this portion of a write operation.                                                                             |  |

Notes

11. X = "Don't Care," H = Logic HIGH, L = Logic LOW, ↑represents rising edge.

12. Is based on a write cycle that was initiated in accordance with the Truth Table on page 12. BWS<sub>0</sub>, BWS<sub>1</sub>, BWS<sub>2</sub> and BWS<sub>3</sub> can be altered on different portions of a write cycle, as long as the setup and hold requirements are achieved.

### IEEE 1149.1 Serial Boundary Scan (JTAG)

These SRAMs incorporate a serial boundary scan Test Access Port (TAP) in the CCGA package. This part is fully compliant with IEEE Standard #1149.1-2001. The TAP operates using JEDEC standard 1.8 V I/O logic levels.

#### Disabling the JTAG Feature

It is possible to operate the SRAM without using the JTAG feature. To disable the TAP controller, TCK must be tied low ( $V_{SS}$ ) to prevent clocking of the device. TDI and TMS are internally pulled up and may be unconnected. They may alternatively be connected to  $V_{DD}$  through a pull up resistor. TDO must be left unconnected. Upon power up, the device comes up in a reset state, which does not interfere with the operation of the device.

#### **Test Access Port**

#### Test Clock

The test clock is used only with the TAP controller. All inputs are captured on the rising edge of TCK. All outputs are driven from the falling edge of TCK.

#### Test Mode Select (TMS)

The TMS input is used to give commands to the TAP controller and is sampled on the rising edge of TCK. This pin may be left unconnected if the TAP is not used. The pin is pulled up internally, resulting in a logic HIGH level.

#### Test Data-In (TDI)

The TDI pin is used to serially input information into the registers and can be connected to the input of any of the registers. The register between TDI and TDO is chosen by the instruction that is loaded into the TAP instruction register. For information on loading the instruction register, see the TAP Controller State Diagram on page 16. TDI is internally pulled up and can be unconnected if the TAP is unused in an application. TDI is connected to the most significant bit (MSB) on any register.

#### Test Data-Out (TDO)

The TDO output pin is used to serially clock data out from the registers. The output is active, depending upon the current state of the TAP state machine (see Instruction Codes on page 20). The output changes on the falling edge of TCK. TDO is connected to the least significant bit (LSB) of any register.

#### Performing a TAP Reset

A Reset is performed by forcing TMS high  $(V_{DD})$  for five rising edges of TCK. This Reset does not affect the operation of the SRAM and can be performed while the SRAM is operating. At power up, the TAP is reset internally to ensure that TDO comes up in a High Z state.

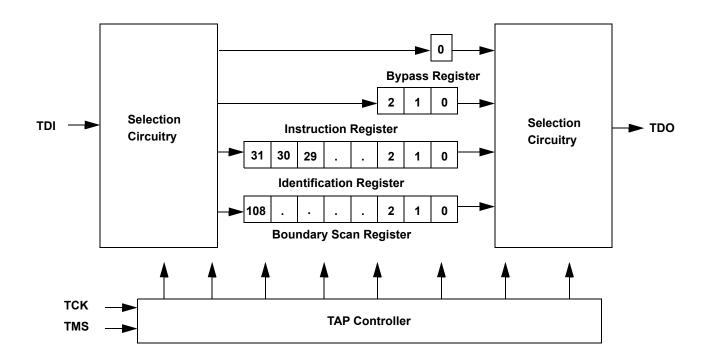

#### **TAP Registers**

Registers are connected between the TDI and TDO pins to scan the data in and out of the SRAM test circuitry. Only one register can be selected at a time through the instruction registers. Data is serially loaded into the TDI pin on the rising edge of TCK. Data is output on the TDO pin on the falling edge of TCK.

#### Instruction Register

Three-bit instructions can be serially loaded into the instruction register. This register is loaded when it is placed between the TDI and TDO pins, as shown in TAP Controller Block Diagram on page 17. Upon power up, the instruction register is loaded with the IDCODE instruction. It is also loaded with the IDCODE instruction if the controller is placed in a reset state, as described in the previous section.

When the TAP controller is in the Capture-IR state, the two least significant bits are loaded with a binary "01" pattern to allow for fault isolation of the board level serial test path.

#### Bypass Register

To save time when serially shifting data through registers, it is sometimes advantageous to skip certain chips. The bypass register is a single-bit register that can be placed between TDI and TDO pins. This enables shifting of data through the SRAM with minimal delay. The bypass register is set low ( $V_{SS}$ ) when the BYPASS instruction is executed.

#### Boundary Scan Register

The boundary scan register is connected to all of the input and output pins on the SRAM. Several No Connect (NC) pins are also included in the scan register to reserve pins for higher density devices

The boundary scan register is loaded with the contents of the RAM input and output ring when the TAP controller is in the Capture-DR state and is then placed between the TDI and TDO pins when the controller is moved to the Shift-DR state. The EXTEST, SAMPLE/PRELOAD, and SAMPLE Z instructions can be used to capture the contents of the input and output ring.

The Boundary Scan Order on page 21 shows the order in which the bits are connected. Each bit corresponds to one of the bumps on the SRAM package. The MSB of the register is connected to TDI, and the LSB is connected to TDO.

#### Identification (ID) Register

The ID register is loaded with a vendor-specific, 32-bit code during the Capture-DR state when the IDCODE command is loaded in the instruction register. The IDCODE is hardwired into the SRAM and can be shifted out when the TAP controller is in the Shift-DR state. The ID register has a vendor code and other information described in Identification Register Definitions on page 20.

#### **TAP Instruction Set**

Eight different instructions are possible with the three-bit instruction register. All combinations are listed in Instruction Codes on page 20. Three of these instructions are listed as RESERVED and must not be used. The other five instructions are described in this section in detail.

Instructions are loaded into the TAP controller during the Shift-IR state when the instruction register is placed between TDI and TDO. During this state, instructions are shifted through the instruction register through the TDI and TDO pins. To execute the instruction after it is shifted in, the TAP controller must be moved into the Update-IR state.

#### **IDCODE**

The IDCODE instruction loads a vendor-specific, 32-bit code into the instruction register. It also places the instruction register between the TDI and TDO pins and shifts the IDCODE out of the device when the TAP controller enters the Shift-DR state. The IDCODE instruction is loaded into the instruction register at power up or whenever the TAP controller is supplied a Test-Logic-Reset state.

#### SAMPLE Z

The SAMPLE Z instruction connects the boundary scan register between the TDI and TDO pins when the TAP controller is in a Shift-DR state. The SAMPLE Z command puts the output bus into a High Z state until the next command is supplied during the Update IR state.

#### SAMPLE/PRELOAD

SAMPLE/PRELOAD is a 1149.1 mandatory instruction. When the SAMPLE/PRELOAD instructions are loaded into the instruction register and the TAP controller is in the Capture-DR state, a snapshot of data on the input and output pins is captured in the boundary scan register.

The user must be aware that the TAP controller clock can only operate at a frequency up to 20 MHz, while the SRAM clock operates more than an order of magnitude faster. Because there is a large difference in the clock frequencies, it is possible that during the Capture-DR state, an input or output undergoes a transition. The TAP may then try to capture a signal while in transition (metastable state). This does not harm the device, but there is no guarantee as to the value that is captured. Repeatable results may not be possible.

To guarantee that the boundary scan register captures the correct value of a signal, the SRAM signal must be stabilized long enough to meet the TAP controller's capture setup plus hold times ( $t_{CS}$  and  $t_{CH}$ ). The SRAM clock input might not be captured correctly if there is no way in a design to stop (or slow) the clock during a SAMPLE/PRELOAD instruction. If this is an issue, it is still possible to capture all other signals and simply ignore the value of the CK and  $\overline{CK}$  captured in the boundary scan register.

After the data is captured, it is possible to shift out the data by putting the TAP into the Shift-DR state. This places the boundary scan register between the TDI and TDO pins.

PRELOAD places an initial data pattern at the latched parallel outputs of the boundary scan register cells before the selection of another boundary scan test operation.

The shifting of data for the SAMPLE and PRELOAD phases can occur concurrently when required, that is, while the data captured is shifted out, the preloaded data can be shifted in.

#### **BYPASS**

When the BYPASS instruction is loaded in the instruction register and the TAP is placed in a Shift-DR state, the bypass register is placed between the TDI and TDO pins. The advantage of the BYPASS instruction is that it shortens the boundary scan path when multiple devices are connected together on a board.

#### **EXTEST**

The EXTEST instruction drives the preloaded data out through the system output pins. This instruction also connects the boundary scan register for serial access between the TDI and TDO in the Shift-DR controller state.

#### EXTEST OUTPUT BUS TRI-STATE

IEEE Standard 1149.1 mandates that the TAP controller be able to put the output bus into a tri-state mode.

The boundary scan register has a special bit located at bit #108. When this scan cell, called the "extest output bus tri-state", is latched into the preload register during the Update-DR state in the TAP controller, it directly controls the state of the output (Q-bus) pins, when the EXTEST is entered as the current instruction. When high, it enables the output buffers to drive the output bus. When low, this bit places the output bus into a High Z condition.

This bit can be set by entering the SAMPLE/PRELOAD or EXTEST command, and then shifting the desired bit into that cell, during the Shift-DR state. During Update-DR, the value loaded into that shift-register cell latches into the preload register. When the EXTEST instruction is entered, this bit directly controls the output Q-bus pins. Note that this bit is pre-set low to enable the output when the device is powered up, and also when the TAP controller is in the Test-Logic-Reset state.

#### Reserved

These instructions are not implemented but are reserved for future use. Do not use these instructions.

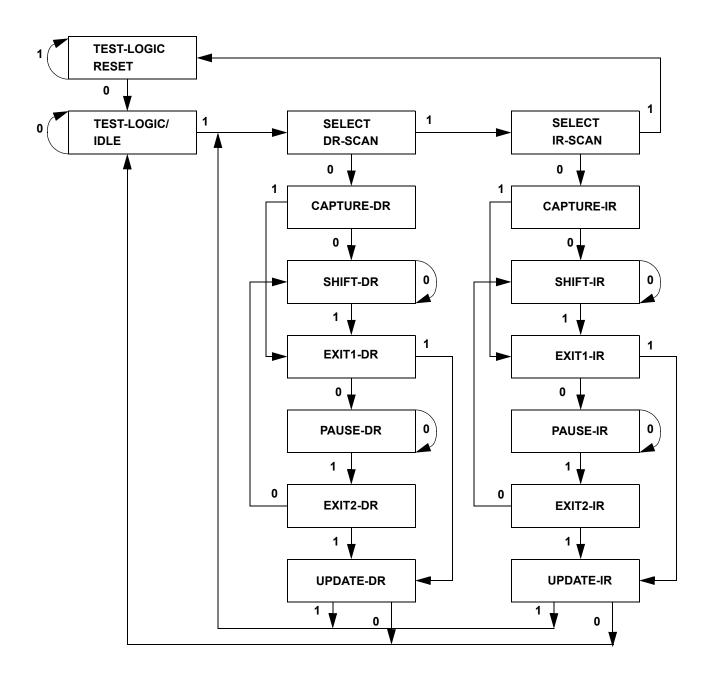

## **TAP Controller State Diagram**

The state diagram for the TAP controller follows. [13]

#### Note

13. The 0/1 next to each state represents the value at TMS at the rising edge of TCK.

## **TAP Controller Block Diagram**

### **TAP Electrical Characteristics**

Over the Operating Range

| Parameter [14, 15, 16] | Description                   | Test Conditions           | Min                  | Max                   | Unit |

|------------------------|-------------------------------|---------------------------|----------------------|-----------------------|------|

| V <sub>OH1</sub>       | Output high voltage           | I <sub>OH</sub> = -2.0 mA | 1.4                  | -                     | V    |

| V <sub>OH2</sub>       | Output high voltage           | I <sub>OH</sub> = -100 μA | 1.6                  | _                     | V    |

| V <sub>OL1</sub>       | Output low voltage            | I <sub>OL</sub> = 2.0 mA  | -                    | 0.4                   | V    |

| $V_{OL2}$              | Output low voltage            | I <sub>OL</sub> = 100 μA  | _                    | 0.2                   | V    |

| $V_{IH}$               | Input high voltage            | _                         | $0.65 \times V_{DD}$ | V <sub>DD</sub> + 0.3 | V    |

| $V_{IL}$               | Input low voltage             | _                         | -0.3                 | $0.35 \times V_{DD}$  | V    |

| $I_X$                  | Input and output load current | $GND \le V_I \le V_{DD}$  | -10                  | 10                    | μΑ   |

<sup>14.</sup> These characteristics pertain to the TAP inputs (TMS, TCK, TDI and TDO). Parallel load levels are specified in the Electrical Characteristics on page 23.

<sup>15.</sup> Overshoot:  $V_{IH(AC)} \le V_{DDQ} + 0.35 \text{ V}$  (Pulse width less than  $t_{CYC}/2$ ), Undershoot:  $V_{IL(AC)} > -0.3 \text{ V}$  (Pulse width less than  $t_{CYC}/2$ ). 16. All voltage referenced to ground.

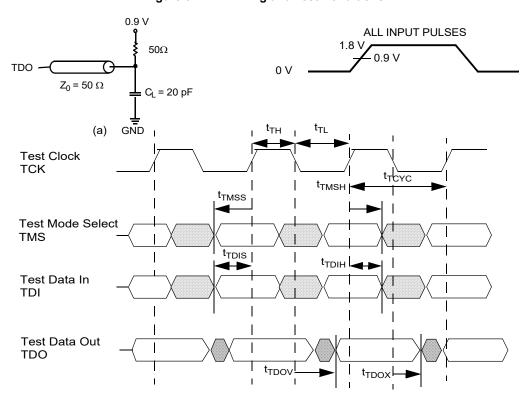

# **TAP AC Switching Characteristics**

Over the Operating Range

| Parameter [17, 18] | Description                   | Min | Max | Unit |

|--------------------|-------------------------------|-----|-----|------|

| t <sub>TCYC</sub>  | TCK clock cycle time          | 50  | -   | ns   |

| t <sub>TF</sub>    | TCK clock frequency           | _   | 20  | MHz  |

| t <sub>TH</sub>    | TCK clock high                | 20  | _   | ns   |

| t <sub>TL</sub>    | TCK clock low                 | 20  | _   | ns   |

| Setup Times        |                               |     |     |      |

| t <sub>TMSS</sub>  | TMS setup to TCK clock rise   | 5   | _   | ns   |

| t <sub>TDIS</sub>  | TDI setup to TCK clock rise   |     | _   | ns   |

| t <sub>CS</sub>    | Capture setup to TCK rise     |     | _   | ns   |

| Hold Times         |                               |     |     |      |

| t <sub>TMSH</sub>  | TMS hold after TCK clock rise | 5   | _   | ns   |

| t <sub>TDIH</sub>  | TDI hold after clock rise     | 5   | _   | ns   |

| t <sub>CH</sub>    | Capture hold after clock rise |     | _   | ns   |

| Output Times       |                               | •   | •   | •    |

| t <sub>TDOV</sub>  | TCK clock low to TDO valid    | _   | 10  | ns   |

| t <sub>TDOX</sub>  | TCK clock low to TDO invalid  | 0   | -   | ns   |

<sup>17.</sup>  $t_{\rm CS}$  and  $t_{\rm CH}$  refer to the setup and hold time requirements of latching data from the boundary scan register. 18. Test conditions are specified using the load in TAP AC Test Conditions.  $t_{\rm R}/t_{\rm F}$  = 1 ns.

# **TAP Timing and Test Conditions**

Figure 3 shows the TAP timing and test conditions. [19]

Figure 3. TAP Timing and Test Conditions

<sup>19.</sup> Test conditions are specified using the load in TAP AC Test Conditions.  $t_R/t_F$  = 1 ns.

# **Identification Register Definitions**

| Instruction Field         | Va                | - Description             |                                              |

|---------------------------|-------------------|---------------------------|----------------------------------------------|

| mstruction Field          | CYRS2642KV18      | CYRS2642KV18 CYRS2644KV18 |                                              |

| Revision Number (31:29)   | 000               | 000                       | Version number.                              |

| Cypress Device ID (28:12) | 11010010100010011 | 11010010100100011         | Defines the type of SRAM.                    |

| Cypress JEDEC ID (11:1)   | 00000110100       | 00000110100               | Allows unique identification of SRAM vendor. |

| ID Register Presence (0)  | 1                 | 1                         | Indicates the presence of an ID register.    |

# **Scan Register Sizes**

| Register Name | Bit Size |

|---------------|----------|

| Instruction   | 3        |

| Bypass        | 1        |

| ID            | 32       |

| Boundary Scan | 109      |

## **Instruction Codes**

| Instruction    | Code | Description                                                                                                                                      |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST         | 000  | Captures the input and output ring contents.                                                                                                     |

| IDCODE         | 001  | Loads the ID register with the vendor ID code and places the register between TDI and TDO. This operation does not affect SRAM operation.        |

| SAMPLE Z       | 010  | Captures the input and output contents. Places the boundary scan register between TDI and TDO. Forces all SRAM output drivers to a High Z state. |

| RESERVED       | 011  | Do Not Use: This instruction is reserved for future use.                                                                                         |

| SAMPLE/PRELOAD | 100  | Captures the input and output contents. Places the boundary scan register between TDI and TDO. Does not affect the SRAM operation.               |

| RESERVED       | 101  | Do Not Use: This instruction is reserved for future use.                                                                                         |

| RESERVED       | 110  | Do Not Use: This instruction is reserved for future use.                                                                                         |

| BYPASS         | 111  | Places the bypass register between TDI and TDO. This operation does not affect SRAM operation.                                                   |

# **Boundary Scan Order**

| Bit # | Bump ID |  |  |

|-------|---------|--|--|

| 0     | 6R      |  |  |

| 1     | 6P      |  |  |

| 2     | 6N      |  |  |

| 3     | 7P      |  |  |

| 4     | 7N      |  |  |

| 5     | 7R      |  |  |

| 6     | 8R      |  |  |

| 7     | 8P      |  |  |

| 8     | 9R      |  |  |

| 9     | 11P     |  |  |

| 10    | 10P     |  |  |

| 11    | 10N     |  |  |

| 12    | 9P      |  |  |

| 13    | 10M     |  |  |

| 14    | 11N     |  |  |

| 15    | 9M      |  |  |

| 16    | 9N      |  |  |

| 17    | 11L     |  |  |

| 18    | 11M     |  |  |

| 19    | 9L      |  |  |

| 20    | 10L     |  |  |

| 21    | 11K     |  |  |

| 22    | 10K     |  |  |

| 23    | 9J      |  |  |

| 24    | 9K      |  |  |

| 25    | 10J     |  |  |

| 26    | 11J     |  |  |

| 27    | 11H     |  |  |

| Bit # | Bump ID |

|-------|---------|

| 28    | 10G     |

| 29    | 9G      |

| 30    | 11F     |

| 31    | 11G     |

| 32    | 9F      |

| 33    | 10F     |

| 34    | 11E     |

| 35    | 10E     |

| 36    | 10D     |

| 37    | 9E      |

| 38    | 10C     |

| 39    | 11D     |

| 40    | 9C      |

| 41    | 9D      |

| 42    | 11B     |